# TUNED HIGH-FREQUENCY TRANSISTOR POWER AMPLIFIERS AND FREQUENCY MULTIPLIERS

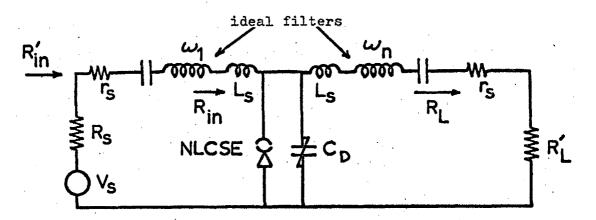

A Thesis Presented By

Ronald Harvey Johnston

For the Degree of

DOCTOR OF PHILOSOPHY of the UNIVERSITY OF LONDON

### ABSTRACT

This investigation is concerned with transistorised power amplifiers and frequency multipliers operating at high frequencies with maximisied power outputs. An important feature of the work is the derivation of circuit models from which performance characteristics are found. Nonlinear circuit behavior, essential for power amplification and frequency multiplication, is found in the charge storage properties of the input and output junctions of the transistor.

The input nonlinearity is employed, characterised, and analysed for purposes of power amplification and frequency multiplication. The analysis facilitates a comparison of the multiplier and amplifier accounting for transistor limitations. Amplifiers and multipliers, using the input nonlinearity are practicable, the multiplier showing a loss in power gain compared with an amplifier at a given output frequency.

Multiplier circuits utilising the output nonlinearity, have shown excellent performances and demonstrated the inadequacy of previous theoretical treatments. A new theory for the multiplication mechanism developed here, assists in the successful understanding of the transistor multiplier and provides an analysis for diode (step recovery) frequency multipliers. Multiplication at the transistor output can increase the maximum frequency of usefulness by a factor of two or more. Output powers of 2.5 watts (0.80 GHz) and 1.2 watts (1.20 GHz) have been obtained by doubling and tripling, respectively.

Multiplication using the nonlinear output is superior to the nonlinear input particularly at the transistor upper frequency limit.

### ACKNOWLEDGEMENT

The author wishes to express his appreciation for the supervision, guidance and support of Professor A.R. Boothroyd.

Thanks are extended to friends and colleagues for the interest shown in this work. In particular, thanks are given to Dr. R.G. Harrison and Dr. A. Singhakowinta, Mr. A. Dutta Roy, Mr. D.McG. Luke, Mr. J.L. May and Mr. V. Roengpithya. The assistance of the typists, Mrs. H. Armstrong and Mrs. I. Ross, is gratefully noted.

The author is indebted to the Board of Trade (UK) for maintenance in the form of an Athlone Fellowship, the Ministry of Aviation (UK) for a Research Assistantship and research funds and the National Research Council (Canada) for a Special Scholarship for personal maintenance.

### TABLE OF CONTENTS

|                                                  | Page |

|--------------------------------------------------|------|

| Abstract                                         | 2    |

| Acknowledgements                                 | 3    |

| Table of Contents                                | 4    |

| Location of Figures and Tables                   | 9    |

| List of Principle Symbols                        | 11   |

|                                                  | · .  |

| CHAPTER ONE                                      |      |

| INTRODUCTION                                     |      |

| 1.1 Object of Investigation                      | 16   |

| 1.2 Historical Background                        | 16   |

| 1.2.1 Power amplifiers and frequency multipliers | 16   |

| 1.2.2 The transistor                             | 18   |

| 1.2.3 The transistor power amplifier and         | •    |

| frequency multiplier                             | 20   |

| 1.3 Application for Transistor Power Amplifiers  |      |

| and Frequency Multipliers                        | 21   |

| 1.4 Analytical Goals and Approach to Transistor  |      |

| Amplifiers and Frequency Multipliers             | 22   |

| 1.4.1 Nonlinear input power amplification        | 23   |

| 1.4.2 Transistor frequency multiplication        |      |

| capability                                       | 23   |

| 1.4.3 Nonlinear input frequency multiplication   | 24   |

| 1.4.4 Nonlinear output frequency multiplication  | 26   |

| 1.5 Originality                                           | 27         |

|-----------------------------------------------------------|------------|

|                                                           | •          |

| CHAPTER TWO                                               |            |

| POWER AMPLIFICATION AND FREQUENCY MULTIPLICATION USING    |            |

| THE TRANSISTOR NONLINEAR INPUT MODE                       |            |

| 2.1 Assumed Circuit Configuration                         | 28         |

| 2.2 General Relationships of Output Voltage, Current      |            |

| and Power in Power Amplifiers and Frequency               |            |

| Multipliers                                               | 30         |

| 2.3 Low Frequency Graphical Analysis                      | 33         |

| 2.4 Assumed High Frequency Waveforms                      | 36         |

| 2.5 Collector Current Efficiency                          | 47         |

| 2.6 Input Power Requirements                              | 53         |

| 2.7 Maximum Harmonic Current Flow                         | 60         |

| 2.8 Peak Input and Output Currents                        | 63         |

| 2.9 Concluding Comments                                   | 65         |

|                                                           | •          |

| CHAPTER THREE                                             |            |

| EFFECTS OF TRANSISTOR STRAYS ON NONLINEAR INPUT OPERATION |            |

| OF MULTIPLIERS AND AMPLIFIERS AND DESIGN METHODS          |            |

| 3.1 Complete Equivalent Circuit and Simplifications       | 6 <b>6</b> |

| 3.2 Effect of Input Depletion Layer Capacitance           | 69         |

| 3.3 Analysis of Effect of Collector Depletion Layer       |            |

| Canacitance                                               | 78         |

| 3.3.1 Analysis of transistor performance with         |     |

|-------------------------------------------------------|-----|

| capacitive feedback                                   | 82  |

| 3.4 Practical Circuits                                | 98  |

| 3.5 Design Approach and Examples                      | 101 |

| 3.5.1 Maximising transistor performance               | 101 |

| 3.5.2 Amplifier design example                        | 104 |

| 3.5.3 Doubler design example                          | 108 |

| 3.6 Conclusions                                       | 111 |

|                                                       |     |

| CHAPTER FOUR                                          |     |

| CHARGE STORAGE FREQUENCY MULTIPLIERS                  |     |

| 4.1 Introduction                                      | 114 |

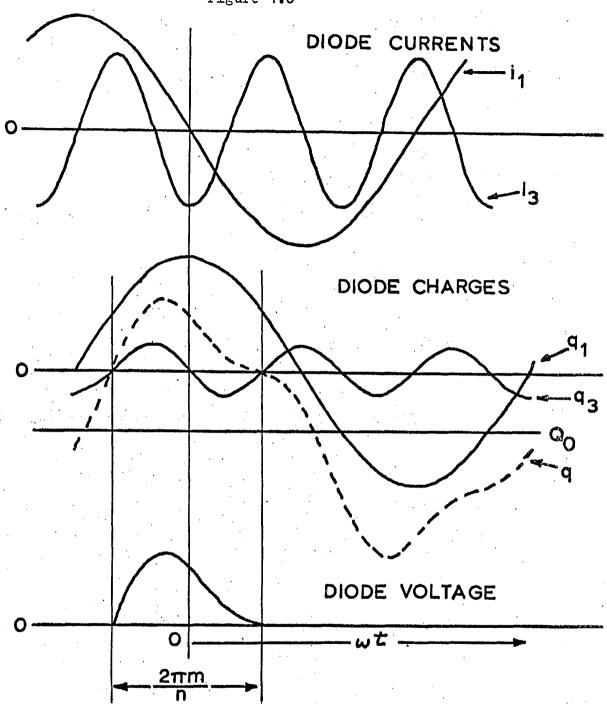

| 4.2 Modes of Operation and Approach to Analysis       | 117 |

| 4.3 Circuit Characteristic Calculations               | 123 |

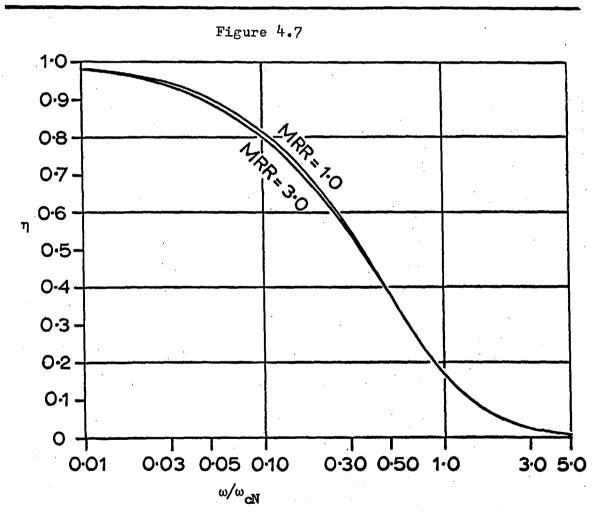

| 4.4 Diode Losses and Efficiency                       | 128 |

| 4.5 Maximum Power Conversion                          | 133 |

| 4.5.1 Reverse breakdown limitation                    | 133 |

| 4.5.2 Figure of merit                                 | 139 |

| 4.5.3 Limit due to diode power dissipation            | 142 |

| 4.6 Design Example                                    | 143 |

| 4.7 Discussion and Conclusions                        | 146 |

| CHAPTER FIVE                                          | £ , |

| TRANSISTORISED NONLINEAR OUTPUT FREQUENCY MULTIPLIERS |     |

| 5 1 Introduction                                      | 150 |

|                                               |     | 7 |

|-----------------------------------------------|-----|---|

| 5.1.1 Available output nonlinearities         | 150 |   |

| 5.1.2 Merits of using an output nonlinearity  | 151 |   |

| 5.1.3 Nonlinear output multiplier assumptions |     |   |

| for analysis                                  | 152 |   |

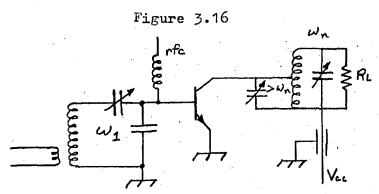

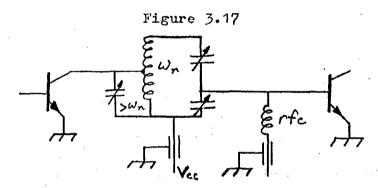

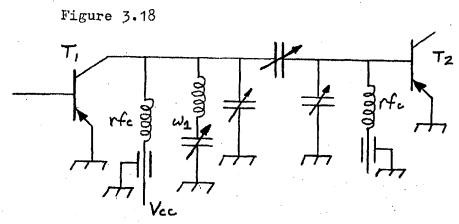

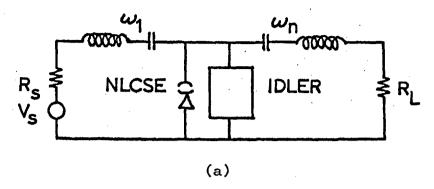

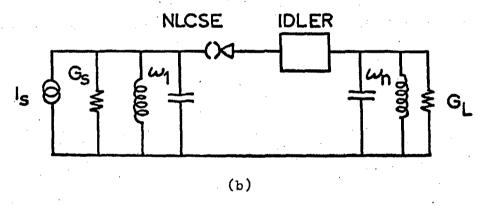

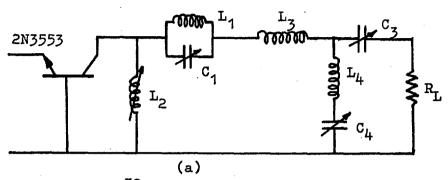

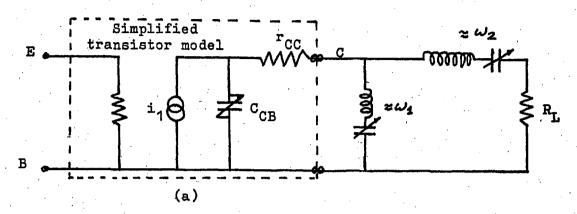

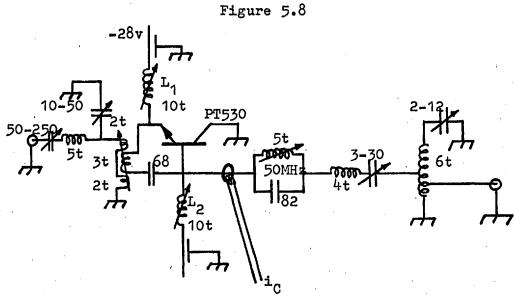

| 5.1.4 Typical NOM circuits                    | 153 |   |

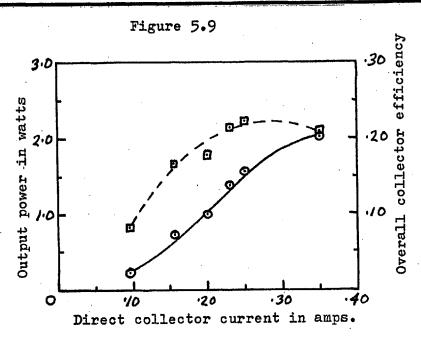

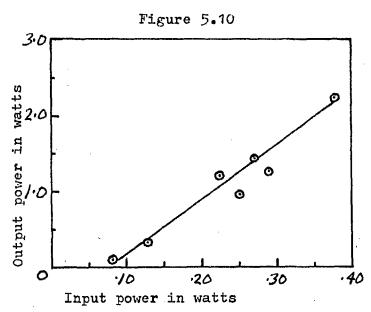

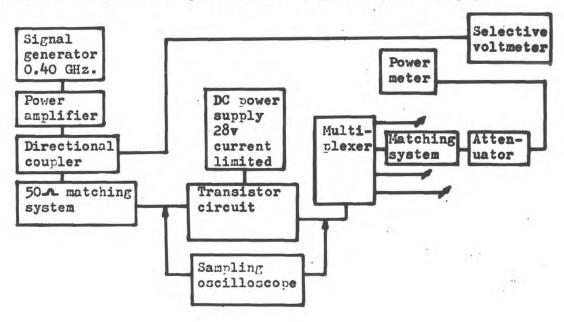

| 5.2 A VHF Amplifier and Doubler               | 156 |   |

| 5.2.1 The vhf amplifier and circuit           | 158 | • |

| 5.2.2 The vhf doubler circuit circuit and     |     |   |

| performance                                   | 162 |   |

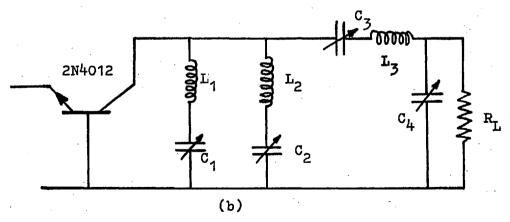

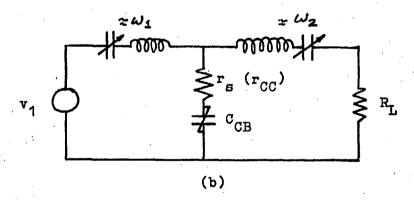

| 5.2.3 Analysis of the vhf doubler performance | 166 |   |

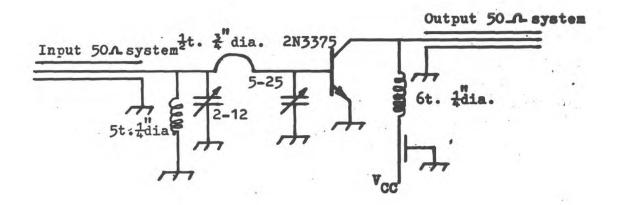

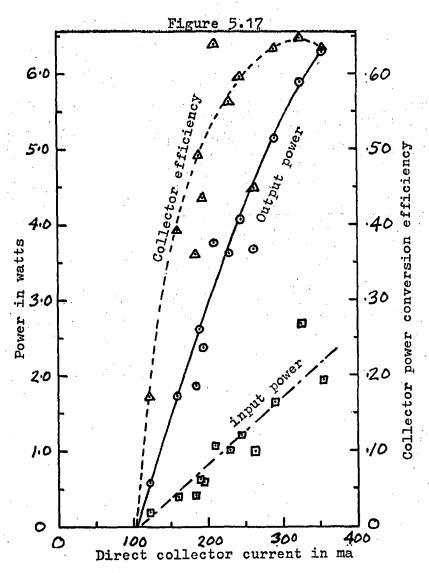

| 5.3 Transistor UHF Amplifier and Multipliers  | 171 |   |

| 5.3.1 Circuit techniques                      | 172 |   |

| 5.3.2 The common emitter amplifier            | 174 |   |

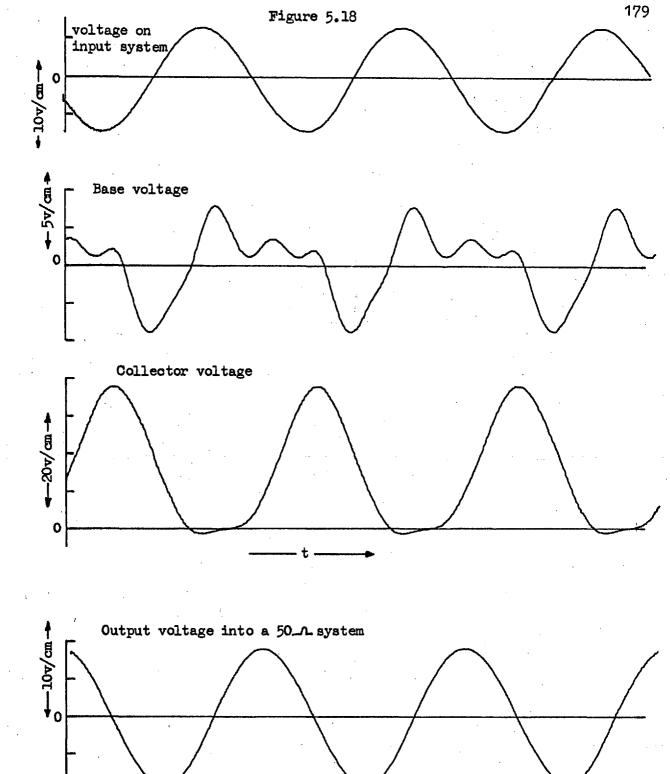

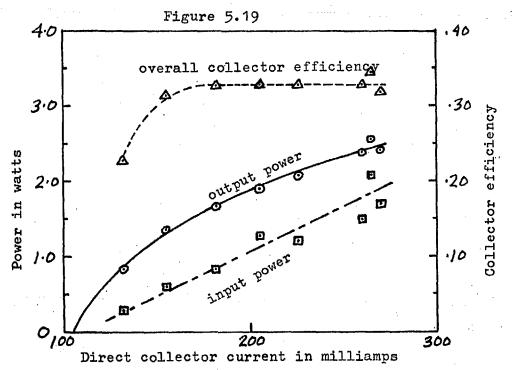

| 5.3.3 The common emitter doubler              | 178 |   |

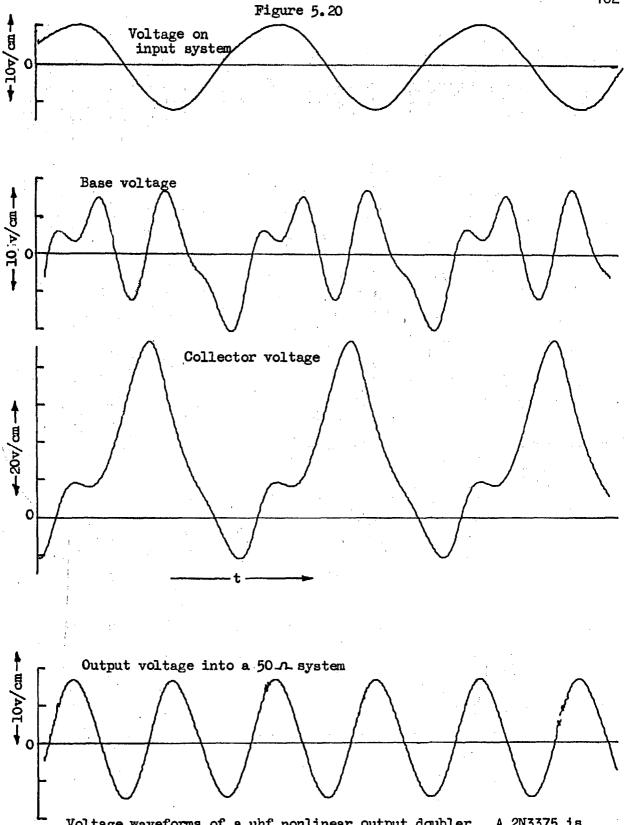

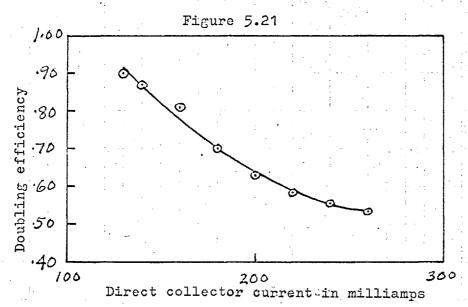

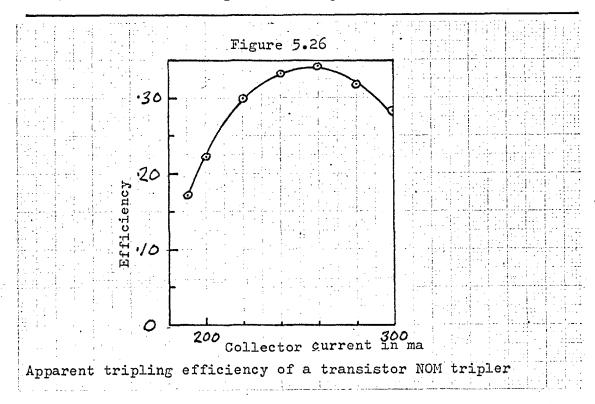

| 5.3.4 The common emitter tripler              | 185 |   |

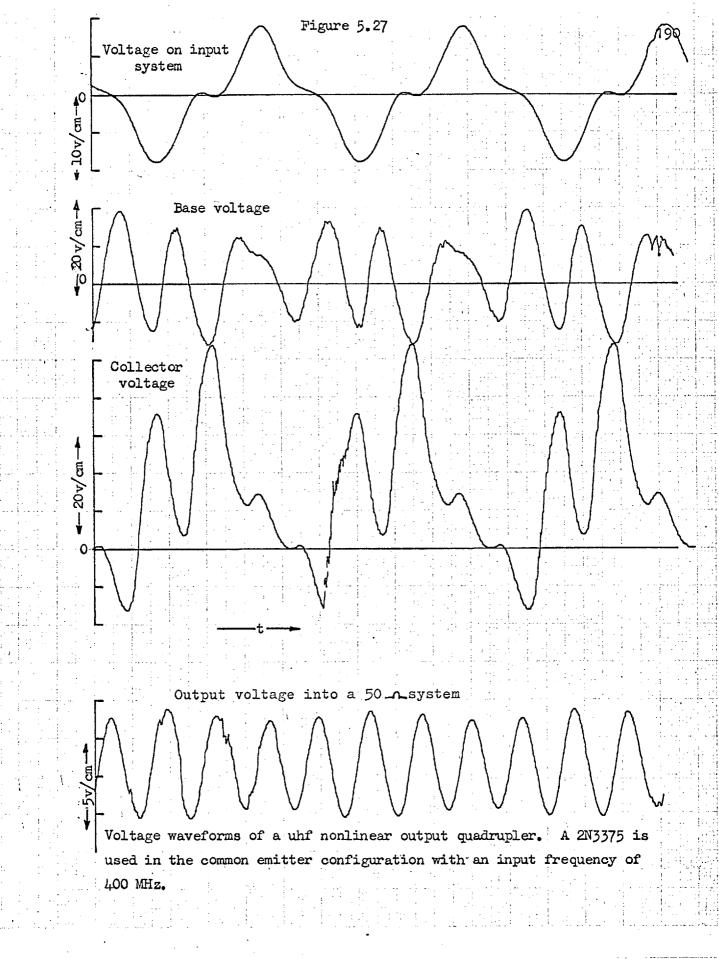

| 5.3.5 The common emitter quadrupler           | 189 |   |

| 5.3.6 The common base doubler                 | 191 |   |

| 5.4 Output Power of the Transistor NOM        | 195 |   |

| 5.5 Discussion of the Transistor NOM          | 198 |   |

| CHAPTER SIX                                   |     |   |

| CONCLUSIONS                                   | 201 |   |

|                                               |     | - |

|                                               | • ' |   |

|                                               |     |   |

|                                               | •   |   |

|                                               |     |   |

|                                               |     |   |

### APPENDICES

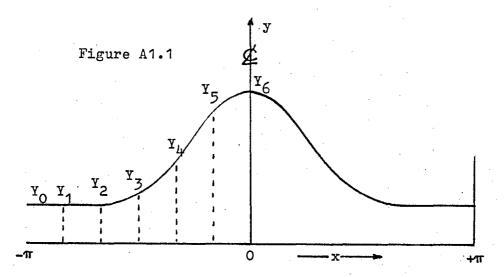

| Appendix 1 | Graphical Fourier Analysis of     |     |

|------------|-----------------------------------|-----|

|            | Symmetrical Waveforms             | 209 |

| Appendix 2 | Computer Program for the Solution |     |

|            | of Transistor Amplifier and       |     |

|            | Multiplier Equations              | 210 |

| Appendix 3 | The Harmonic Multiplexer          | 215 |

|            |                                   | 007 |

| REFERENCES | •                                 | 223 |

### Location of Figures and Tables

| Figure | Page       | Figure | Page | Figure | Page |

|--------|------------|--------|------|--------|------|

| 1.1    | 19         | 3.2    | 68   | 4.9    | 134  |

| 1.2    | 24         | 3•3    | 70   | 4.10   | 138  |

| 2.1    | 29         | 3.4    | 71   | 4.11   | 140  |

| 2.2    | 31         | 3•5    | 76   | 5.1    | 155  |

| 2.3    | 35         | 3.6    | 77   | 5.2    | 157  |

|        |            | •      |      |        |      |

| 2.4    | 37         | 3•7    | 79   | 5•3    | 159  |

| 2.5    | <b>3</b> 8 | 3.8    | 81   | 5.4    | 159  |

| 2.6    | 40         | 3.9    | 91   | 5•5    | 160  |

| 2.7    | 41         | 3.10   | 92   | 5.6    | 160  |

| 2.8    | 43         | 3.11   | 93   | 5.7    | 161  |

|        | • _        | 7.40   | ol.  | 5.8    | 163  |

| 2.9    | 45         | 3.12   | 94   |        | 163  |

| 2.10   | 46         | 3.13   | 95   | 5•9    | 164  |

| 2.11   | 47         | 3 • 14 | 96   | 5.10   | 165  |

| 2.12   | 50         | 3.15   | 96   | 5.11   |      |

| 2•13   | 51         | 3.16   | 99   | 5.12   | 167  |

| 2.14   | 52         | 3.17   | 100  | 5.13   | 167  |

| 2.15   | 54         | 3.18   | 101  | 5.14   | 170  |

| 2.16   | <b>57</b>  | 4.1    | 115  | 5.15   | 175  |

| 2.17   | 58         | 4.2    | 116  | 5.16   | 176  |

| 2.18   | 58         | 4.3    | 118  | 5.17   | 177  |

|        |            |        |      |        |      |

| 2.19   | 59         | 4.4    | 119  | 5.18   | 179  |

| 2.20   | 60         | 4.5    | 120  | 5•19   | 180  |

| 2.21   | 62         | 4.6    | 124  | 5.20   | 182  |

| 2.22   | 64         | 4.7    | 130  | 5.21   | 183  |

| 3.1    | 67         | 4.8    | 132  | 5.22   | 183  |

|        |      |        |      | ,      | •    |

|--------|------|--------|------|--------|------|

| Figure | Page | Figure | Page | Figure | Page |

| 5.23   | 185  | 5.27   | 190  | A3.3   | 218  |

| 5.24   | 186  | A1.1   | 209  | A3.4   | 218  |

| 5.25   | 187  | A3.11  | 215  | A3.5   | 220  |

| 5.26   | 188  | A3.2   | 217  | A3.6   | 222  |

| Table | Page |

|-------|------|

| 3.1   | 107  |

| 3.2   | 112  |

| 4.1   | 149  |

| 5.1   | 192  |

| 5.2   | 194  |

### List of Principal Symbols

| Symbol                                          | Page of first useage | Definition                                                                                                         |

|-------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------|

| <b>BV</b> , , , , , , , , , , , , , , , , , , , | 61                   | Breakdown voltage of a diode or a transistor junction.                                                             |

| C                                               | 68                   | Capacitance.                                                                                                       |

| c <sub>BE1</sub> , c <sub>BC1</sub>             | 68                   | Depletion layer capacitance located, elect-<br>rically, under the extrinsic base resistance<br>rbb°                |

| CBE2, CBC2                                      | 68                   | Depletion layer capacitance located externally to the extrinsic base resistnace rbb.                               |

| C <sub>CBmin</sub>                              | 170                  | Minimum collector-base capacitance                                                                                 |

| C <sub>CB</sub> (v)                             | 197                  | Collector-base capacitance as a function of applied voltage.                                                       |

| C <sub>Ext</sub>                                | 139                  | A capacitance added to a diode for multiplication.                                                                 |

| D                                               | 68                   | Diode                                                                                                              |

| <b>f</b>                                        | 52                   | Frequency                                                                                                          |

| f <sub>max</sub>                                | 26                   | Maximum frequency of oscillation of a transistor.                                                                  |

| fp                                              | 20                   | Frequency at which the current gain of a common emitter transistor falls to 3 db less than the low frequency value |

| f <sub>1</sub> ( e', n, E                       | ) 85                 | Function relating feedback modified harmonic output current to input voltage.                                      |

| f <sub>2</sub> («', n,&                         | ) 87                 | Function relating feedback modified direct collector current to input voltage.                                     |

| f <sub>3</sub> ( w', n,E                        | ) 89                 | Function relating feedback modified input power to input voltage.                                                  |

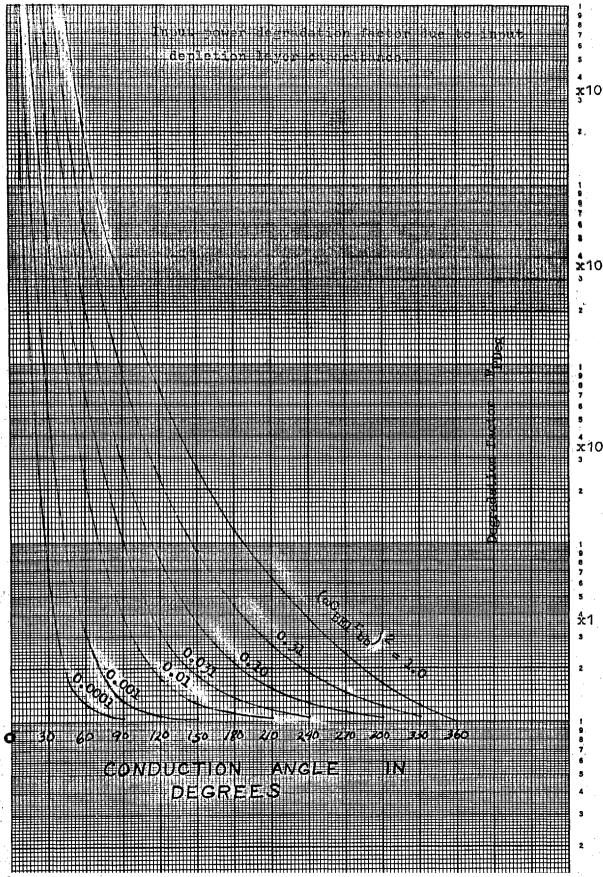

| $^{ m F}_{ m PDeg}$                             | 74                   | Input power degradation factor.                                                                                    |

| FT                                              | 24                   | Unity gain frequency of a transistor in common emitter configuration.                                              |

| i                   | 29             | Current, all harmonic components specified.                                            |

|---------------------|----------------|----------------------------------------------------------------------------------------|

| f                   | <b>79</b>      | Feedback current due to depletion layer capacitance.                                   |

| i"1 - i"83          | 73             | Base currents flowing into the input depletion layer capacitance.                      |

| i.c                 | 80             | Collector current modified by feedback.                                                |

| i,                  | 79             | Transistor input diode current modified by feedback.                                   |

| I                   | 32             | Peak current.                                                                          |

| I'B1inphase         | 88             | Peak fundamental base current inphase with base voltage.                               |

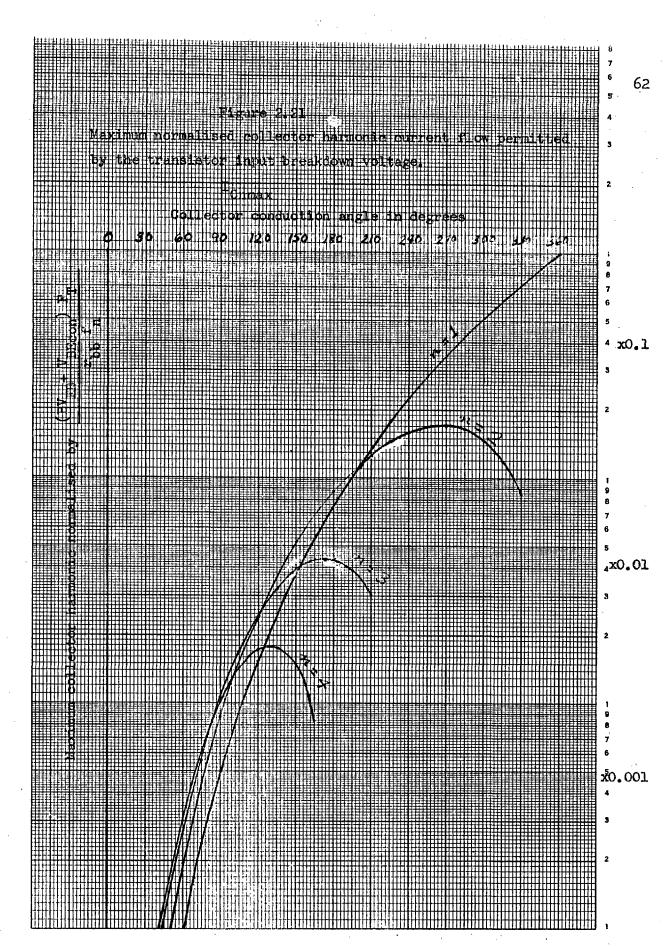

| ICnmax              | 62             | Maximum harmonic collector current permitted by input breakdown voltage.               |

| I'Cnmax             | 110            | I Cnmax including the effect of capacitive feedback.                                   |

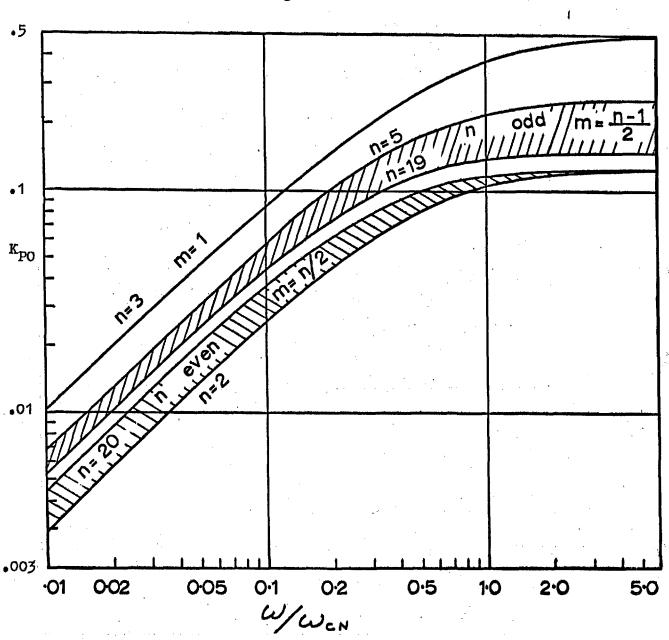

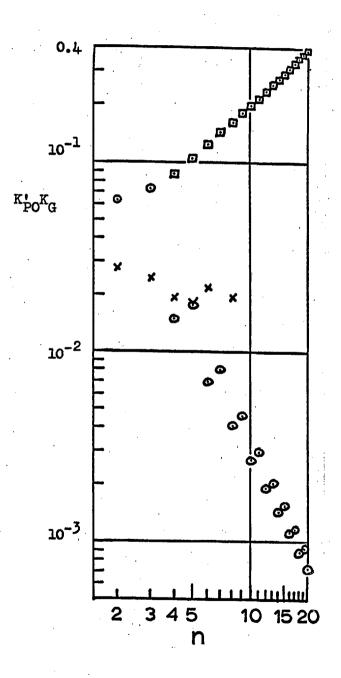

| $K_{FM}$            | 141            | Multiplier diode figure of merit.                                                      |

| К <sub>G</sub>      | 126            | Constant relating the input and output resistances of a diode multiplier.              |

| K <sub>G</sub> K'PO | 139            | Low frequency, normalised output power of a diode.multiplier.                          |

| K <sub>PO</sub>     | 136            | Maximum normalised output power of a diode multiplier.                                 |

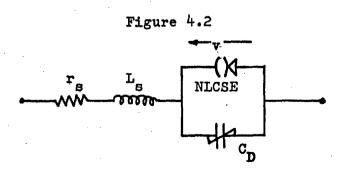

| L <sub>s</sub>      | 116            | Diode series inductance.                                                               |

| m                   | 123            | An integer representing diode conduction angle.                                        |

| MRR                 | 127            | Minimum resistance ratio of a diode multiplier.                                        |

| n                   | 48             | An integer representing the output harmonic.                                           |

| P                   | 32             | Electrical power.                                                                      |

| P<br>BinDeg         | 7 <sup>4</sup> | Fundamental power input to the base degraded by the input depletion layer capacitance. |

|                     |                | · ·                                                                                    |

| P!<br>Bin           | 89   | Input power to base modified by feedback.               |

|---------------------|------|---------------------------------------------------------|

| PDis                | 104  | Power dissipation capability of device.                 |

| Pindc               | 32   | Transistor dc input power.                              |

| Pnorm               | 168  | Varactor normalised power.                              |

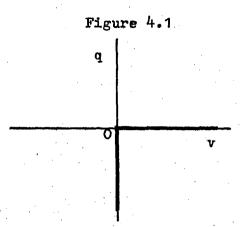

| q                   | 68   | Charge, including all harmonic components.              |

| Q                   | 123  | Peak value of charge components.                        |

| rbb                 | 55   | Extrinsic base resistance of a transistor.              |

| rcc                 | 79   | Collector series resistance.                            |

| rs                  | 116  | Diode series resistance.                                |

| R!<br>in            | 120  | Apparent input resistance of a diode multiplier.        |

| $^{ m R}_{ m L}$    | 38   | Load resistance of an amplifier or a multiplier.        |

| R <sub>L</sub>      | 120  | Useful load resistance of a diode multiplier.           |

| R <sub>o</sub>      | 78   | Output resistance of a common emitter transistor.       |

| t                   | 31   | Time in secounds.                                       |

| v                   | 29   | Voltage, with all harmonic components specified.        |

| v"IB                | 70   | Intrinsic base voltage.                                 |

| v                   | 31   | Peak value of voltage components.                       |

| $v_{\mathtt{Bcon}}$ | 61   | Threshold conduction voltage of the transistor base.    |

| v <sub>CC</sub>     | . 31 | Collector supply voltage.                               |

| V <sub>Csat</sub>   | 31   | Collector saturation voltage.                           |

| a                   | 39   | One half of the transistor collector conduction period. |

| a'                   | 81  | One half of the transistor collector conduction period modified by feedback. |

|----------------------|-----|------------------------------------------------------------------------------|

| Υ                    | 170 | Exponent of the depletion layer capacitance law.                             |

| 8                    | 83  | Matching factor of a transistor amplifier or multiplier.                     |

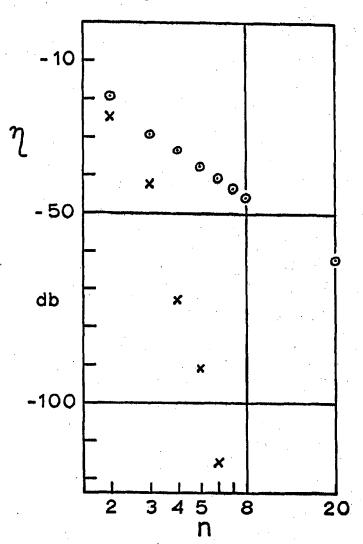

| η                    | 128 | Diode multiplier power conversion efficiency.                                |

| ησι                  | 32  | Collector current efficiency.                                                |

| <sup>¶</sup> CP      | 32  | Transistor collector power conversion efficiency.                            |

| η <sub>C▼</sub>      | 32  | Collector voltage efficiency.                                                |

| $\eta_{\mathrm{LF}}$ | 131 | Low frequency diode multiplication efficiency.                               |

| $\eta_{\mathrm{HF}}$ | 131 | High frequency diode multiplication efficiency.                              |

| $	au_{\mathbf{f}}$   | 39  | Forward injection charge-control parameter.                                  |

| . <b>b</b>           | 135 | Angle of maximum reverse diode voltage.                                      |

| Y                    | 170 | Barrier potential of a varactor diode.                                       |

| <b>w</b>             | 29  | Angular frequency.                                                           |

| ω <sub>o</sub>       | 131 | Angular cutoff frequency of a step recovery diode or a varactor diode.       |

| w <sub>G</sub>       | 129 | Normalised angular cutoff frequency of a step recovery diode.                |

### Principle Subscripts

| В | • . | Base      |

|---|-----|-----------|

| C |     | Collector |

| מ |     | Diode     |

| E |     | Emitter   |

in input

max maximum value attained

n an integer representing a particular harmonic

o output

0,1,2,3 etc. denotes an average, a fundamental or

0,1,2,3 etc.

denotes an average, a fundamental or a harmonic, respectively.

### CHAPTER ONE

### INTRODUCTION

### 1.1 Object of Investigation

This thesis is concerned with the theory, design and experimental investigation of high frequency transistor frequency multipliers. A comprehensive study of transistorised frequency multipliers has, hitherto, been absent. The investigation is extended to include transistor power amplifiers. The extension is relevant to the treatment of transistors employing output frequency multiplication, which involves power amplification as part of the total mechanism. In addition, the comparison of frequency multiplier and power amplifier performances is facilitated.

The aim of this study is to establish theoretically sound methods for the design of amplifiers and frequency multipliers, which are both accurate and simple. The various possible modes of frequency multiplication are investigated theoretically and their relative merits are assessed. The emphasis is on circuit analysis, the transistor being represented by the simplest adequate model.

### 1.2 <u>Historical Background</u>

### 1.2.1 Power amplifiers and frequency multipliers

The functions of power amplification and frequency multiplication are almost as old as the first significant active electronic device.

Class C amplifiers in valve form first made an appearance in 1923;

the valve frequency multiplier was developed a few years later<sup>2, 3</sup>.

These two valve circuits have been associated ever since. The association of these circuits has stemmed from the similarity of operation and application in communication and broadcast transmitters. Usually a crystal controlled oscillator produced a low frequency that was increased in a chain of valve frequency multipliers. The chain drove a power amplifier which was likely to be the output stage of the transmitter. This configuration allowed the oscillator to operate at low frequencies (and hence attain good frequency stabilities) and also reduce the likelihood of transmitter oscillation. the chain the frequency multipliers were operated, and the power amplifiers were most likely operated in the "Class C mode". The "Class C mode" of operation depends upon a nonlinearity in the valve transfer characteristic. The drive on the input of the valve is adjusted and biased so that the anode current flow takes the form of pulses occuring at the input frequency rate. The voltage on the anode is sinusoidal and tuned so that the anode voltage is a minimum during the short interval of the high anode current. This mode of operation minimises the anode power dissipation allowing a high conversion efficiency of direct power to radio frequency power.

The operation of the valve multiplier is very similar to the power amplifier. The anode current pulses have a considerable harmonic content and a tuned circuit is chosen so that one of these current harmonics energise the load. Thus the nonlinear transfer characteristic that is used to increase the power conversion effic-

iency of the power amplifier also provides the harmonic generation necessary in the frequency multiplier. The mechanisms used in frequency multiplication and power amplification in the valve are so similar that most of the design equations are the same and certainly the same design approach is used. The Class C method of harmonic generation formed the most important basis for frequency multiplication for a long time. Multipliers using rectifying diodes and nonlinear inductive elements were known but did not gain widespread acceptance.

#### 1.2.2 The transistor

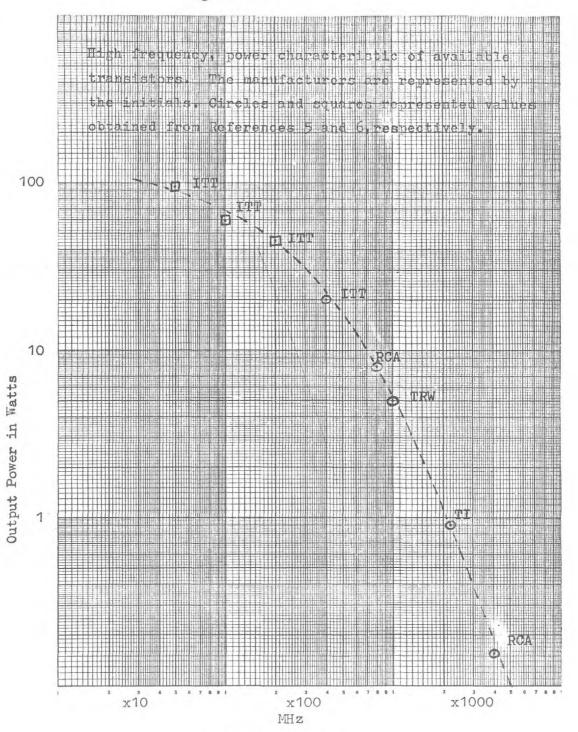

The junction transistor, first developed in 1951, was capable of a gain up to about fifteen megacycles and an audio frequency power output of about twenty milliwatts. The frenetic research and development into semiconductors has raised the power and frequency capability of the transistor by several orders of magnitude. The power-frequency capability progressed with each of the following transistor types: point-contact transistor, grown-junction transistor, alloy-junction power transistor, diffused-junction transistor, silicon planar transistor. Today most of the high frequency power transistors are of a double-diffused, epitaxial, multi-emitter, silicon planar structure. Shown in Fig. 1.1 are state-of-art transistor power and frequency output capabilities<sup>5,6</sup>. These output capabilities have promoted an intense interest in transistor power

Figure 1.1

Output Frequency

amplifiers and frequency multipliers for use in solid state radio frequency sources in a manner very similar to the valve amplifiers and multipliers used in early transmitters.

1.2.3 The transistor power amplifier and frequency multiplier

The similarity (real and imagined) of the transistor to the valve

made it intuitively obvious that the transistor would operate (as a

power amplifier or frequency multiplier) in the same circuit as a valve.

The transistor did work as an amplifier and as a multiplier and it was

assumed that the analysis was the same 7, 8, 9. The charge storage

characteristics of the base were neglected 10, thus inadvertently

limiting accurate application of the analysis to frequencies less than

f<sub>\beta</sub>. Recently the base charge storage effect was recognised and

accounted for in a transistorised Class C amplifier 11, 12.

Another practical method of harmonic generation in the transistor became known 13 recently. In this new method the transistor operates as an amplifier and fundamental power is prevented from leaving the transistor. The fundamental power operates on the nonlinear capacitance of the collector and it is efficiently converted into a harmonic power 14, 15. This method extends the upper frequency of usefulness of the transistor by a factor of two or three. Other methods of transistor frequency multiplication exist but do not perform better than the above mentioned methods 16.

## 1.3 Application for Transistor Power Amplifiers and Frequency Multipliers

The newly acquired frequency and power performance of the transistor has caused energetic studies and development of solid state radio frequency power sources. The transistor is often employed in these sources for frequency multiplication and power amplification stages in the way the valve was (and is) used in broadcast transmitters. The transistor converts the direct power into rf power which may be increased in frequency in a varactor (or a multiple varactor) frequency multiplier. These power sources may find application in both the transmitting and receiving sections of transponders, light radar, telecommunication and telemetry systems. Transistors are useful in the above applications, not because of their superior frequency and power output performance (compared with travelling-wave tubes, klystrons and magnetrons), but because of their superior electrical reliability, mechanical ruggedness, size and weight, and power conversion efficiency. These other characteristics ensure the utilisation of the transistor in many demanding environments even where its power and frequency output capabilities are marginal for the application concerned.

Some semiconductor devices, other than the bipolar junction transistor, have shown a great deal of promise for similar applications. Devices such as the avalanche transit time diodes, Gunn effect diodes, and tunnel diodes are most useful for frequencies higher than those easily met by the transistor. Varactor diodes and step recovery diodes

are best thought of as adjuvants to the transistor rather than as substitutes. The two diodes cannot convert direct power into radio frequency power but can change the rf power into a more useful frequency with low loss. The diodes effectively extend the useful frequency range of the transistor.

The junction transistor is the best solid state device for conversion of direct power into a significant quantity of radio frequency power (viz. more than 0.1 watts) in the frequency range of 1.0 MHz to 1.0 GHz. The indications are that the junction transistor will occupy this position for a long time to come.

### 1.4 Goals and Approach to Analysis of Transistor Amplifiers and Frequency Multipliers

The circuit of a transistor amplifier or frequency multiplier may be modified at will without affecting a given analysis providing that the assumed input and output operating conditions are maintained. Transistors employed in push-pull or parallel configurations can be treated in terms of a "single transistor analysis". The analyses developed in this thesis deal specifically with transistors operated in the common emitter mode. However, much of the following theory applies to common base operation as well.

### 1.4.1 Nonlinear input power amplification

The transistor is normally employed for power amplification in a method very analogous to the way the valve is used. A sinusoidal voltage is applied to the transistor input with bias. A sinusoidal voltage of the input frequency is maintained at the transistor output. The output tuned circuit and the load is energised by collector current pulses. This method (frequently called Class C operation, irrespective of collector conduction angle) of operating the transistor as a power amplifier is the most universal and is the most versatile. Other methods of transistor power amplification are known but will not be considered here.

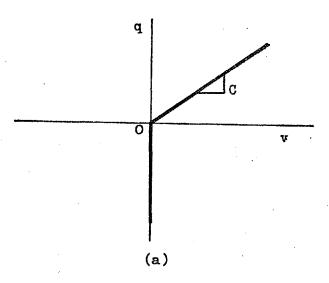

### 1.4.2 Transistor frequency multiplication capability

For successful frequency multiplication the transistor must contain some nonlinear characteristic. The transistor contains a number of the necessary nonlinearities. It contains two diode sections (the emitter-base diode and the collector-base diode) and each of these diodes contains a nonlinear resistance (with discontinuities from reverse bias to forward bias and from low reverse bias to reverse bias into avalanche breakdown) and a nonlinear capacitance (the nonlinear capacitance (the nonlinear depletion layer capacitance and also nonlinear minority carrier charge storage). Normally either the nonlinear capacitance or the nonlinear resistance predominates depending upon the frequency of operation.

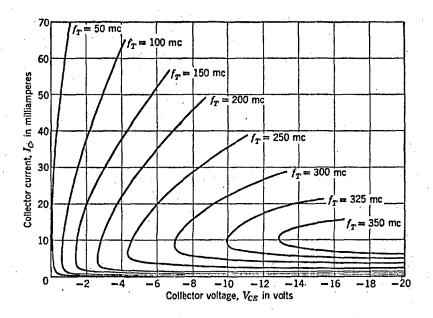

These nonlinearities are the predominant ones, and provide plenty of

scope for frequency multiplication. Other nonlinearities, less pronounced, are also found in the transistor. For example, the high frequency current gain is dependent upon the collector operating conditions. See Fig. 1.2.

Figure 1.2

Typical variation of  $F_T$  (and hence high frequency common emitter current gain) as a function of collector operating conditions. The transistor is a silicon planar type  $2N2401^{41}$ .

### 1.4.3 Nonlinear input frequency multiplication

It has been found that the input nonlinearity (base-emitter nonlinear resistance or nonlinear capacitance depending on operating frequency) can be used effectively for frequency multiplication. Two

different analyses are required for the nonlinear resistance mode and for the nonlinear charge storage mode. The nonlinear resistance mode is in control at frequencies lower than  $f_{\beta}$  and the nonlinear charge storage mode is in control at frequencies above; the two modes merge at approximately  $f_{\beta}$ . Many authors  $^{9}$ ,  $^{10}$  have assumed that the nonlinear resistance mode is applicable at all operating frequencies. Frequency multiplication, using the input nonlinearity, is very similar to power amplification, and for this reason the two will be analysed together. Analyses  $^{9}$  are presented by other authors which deal with amplifier and multipliers with operating frequencies of less than  $f_{\beta}$ . For the purposes of this study (i.e. maximum power, high frequency) a transistor operated at frequencies of less than  $f_{\beta}$  is not being fully utilised. For these two reasons a full analysis of this frequency range will not be made. Instead a rudimentary graphical analysis is presented in Chapter Two.

For operating frequencies higher than  $f_{\beta}$  a comprehensive analysis is carried out in terms of the nonlinear input charge storage. The analysis is presented in Chapter Two and provides the first analysis, of any kind, of high frequency nonlinear input transistorised frequency multipliers operating in the nonlinear input mode. A charge storage analysis is also developed for the high frequency power amplifier; while this analysis is not the first of its kind, it is believed that it is superior to previous approaches. Nonlinear input amplification or multiplication, using the transistor, shall henceforth be referred to by NIAM.

Chapter Three deals with the effect of depletion layer capacitance on the operation of the power amplifier and frequency multiplier. In this way the limitation of f<sub>max</sub> (of the transistor) is introduced and the analysis is applicable up to the maximum frequency of usefulness of the transistor. Finally, a complete design procedure is presented for this kind of power amplifier and frequency multiplier.

1.4.4 Nonlinear output frequency multiplication

The transistor has been operated very successfully 13, 14, 15 using the capacitive nonlinearity of the collector diode (in the output circuit). The transistor input circuit is constructed and behaves in a way similar to a conventional amplifier but at the output, the fundamental power is prevented from leaving the transistor. The fundamental power is converted into a harmonic power, by the output nonlinear capacitance, which is dissipated in the load via tuned circuits. Multiplying factors of up to four are attainable with practical power conversion efficiencies. Frequency multiplication using the transistor output nonlinearly will be called NOM (nonlinear output multiplication).

It has, hitherto, been assumed that the nonlinear capacitance of the collector diode depends on the depletion layer charge storage only. Measurements and calculations in this study indicate, however, that the effect of the nonlinear depletion layer capacitance is insufficient to be responsible for the level of harmonic output power actually obtained. Observations of the collector voltage waveforms

indicate that the collector voltage "bottoms" for a large part of the fundamental cycle. These two occurrences suggest strongly that minority carrier charge storage takes place in the collector-base diode. For this reason, an analysis is made of frequency multiplying circuit utilising a minority carrier nonlinear charge storage device. This analysis is presented in Chapter Four and is used, together with another recent work in the later treatment of the high frequency transistor NOM. The analysis of Chapter Four is also important because of its application to frequency multipliers employing step recovery diodes.

In Chapter Five nonlinear output transistor frequency multipliers are constructed and the performance is measured. The minority carrier charge storage multiplication theory is supported by measurements. The operation of the overall stage is treated and then an outline of design and construction methods is presented.

### 1.5 Originality

Except where reference is made to the work of others, the research and the conclusions reported in this thesis are original as far as the author is aware.

### CHAPTER TWO

## POWER AMPLIFICATION AND FREQUENCY MULTIPLICATION USING THE TRANSISTOR NONLINEAR INPUT

### 2.1 Assumed Circuit Configuration

The operation of the historically developed valve frequency multiplier and power amplifier depends upon one nonlinear characteristic; namely the dependance of anode current on grid voltage in a common cathode circuit. If a sine wave of voltage is applied to the grid of the valve, with proper biasing, a distorted sine wave of current is obtained at the anode. Power may then be extracted at a fundamental or harmonic frequency. Analysis of this method of power amplification or frequency multiplication is facilitated by assuming that the grid and anode voltages consist of sine waves at the input and output frequencies, respectively. The above mode of circuit operation is very frequently assumed to be applicable to transistor power amplifiers and frequency multipliers. The fundamental voltage (filtering ensures that only the fundamental is present) is applied to the transistor input (assumed for the moment to be operating in the common emitter configuration) along with a biasing voltage or current. The biasing is set so that both the base and the collector of the transistor conduct for a fractional part of the fundamental cycle. The base-emitter nonlinear diode characteristic is thus utilised. circuit can operate with an infinite number of variations of input

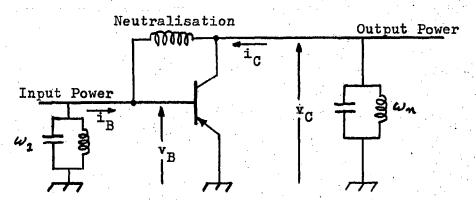

voltage waveshapes and output voltage waveshapes. However, it is assumed that the input and output voltage waveforms are sinusoidal, purely in the interests of analytic convenience. The circuit is then constructed with a view to meeting the above assumptions but experience shows that actual input and output waveshapes may deviate appreciably (from the sinusoidal input and output voltage assumptions) without affecting the performance of the circuit significantly. A simple example of a circuit that will meet the above assumptions is shown in Fig. 2.1.

Figure 2.1

Amplifying and multiplying circuit designed to meet assumptions of sinousoidal voltages on input and output. Biasing omitted.

Although transistor circuits may in practice take a completely different configuration, analysis, based on the above circuit, will

be applicable to any circuit that maintains sinusoidal voltages on the input and the output. For example, multipliers and amplifiers using a number of transistors (i.e. push-pull, push-push or parallel circuits) may be treated with the following analysis providing the sinusoidal voltage assumptions are met. The following analysis is based on the common emitter configuration because this is the most widely employed and may be used over a broad range of frequencies. Much of the above investigation and analysis is applicable to the common base configuration. The extent of the possible application will be indicated.

### 2.2 General Relationships of Output Voltage, Current and Power in Power Amplifiers and Frequency Multipliers

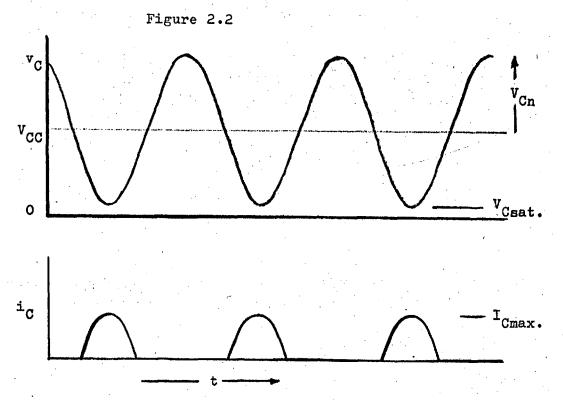

The assumption that a sinusoidal voltage is maintained at the transistor output permits the development of some general relationships that partially describe the performance of the transistorised power amplifier and frequency multiplier. The output voltage and a hypothetical current of the transistor are illustrated in Fig. 2.2.

The transistor produces current pulses at a repetition rate equal to the fundamental frequency. The output tuned circuit filters the desired and available harmonic current and transfers harmonic power to the load. The direct input power to the transistor and load is,

Transistor collector voltage and a hypothetical collector current of a tuned power amplifier.

$$P_{inde} = V_{CC} \cdot I_{CO}$$

2.1

where  $V_{CC}$  is the supply voltage and  $I_{CO}$  is the direct current drawn by the transistor. If the output tuned circuit is adjusted to resonance, the output power is,

$$P_{oC} = 0.5 \cdot V_{Cn} \cdot I_{Cn}$$

2.2

where  $V_{\rm Cn}$  and  $I_{\rm Cn}$  are the peak nth harmonic voltage and current of the collector respectively. The power conversion efficiency of the transistor may be calculated from the above two expressions.

$$\eta_{\rm CP} = \frac{I_{\rm Cn} V_{\rm Cn}}{2 I_{\rm CO} V_{\rm CC}}$$

2.3

This power conversion efficiency may be separated into two parts, one a current conversion efficiency, and the other a voltage conversion efficiency. Explanation of the separation will follow.

$$\eta_{\text{CI}} = \frac{I_{\text{Cn}}}{2 I_{\text{CO}}}$$

and

$$\eta_{CV} = \frac{V_{Cn}}{V_{CC}}$$

where

$$V_{Cn} \leq V_{CC} - V_{Csat}$$

2.6

The voltage efficiency of Eqn. 2.5 can, for most transistors, be made to exceed .80. The exact value of it depends very much on the transistor in use. The maximum voltage efficiency may be determined very quickly if the appropriate transistor collector characteristics are available and the peak collector current is known. Normally the voltage efficiency will vary between .70 and 1.00 and depends

largely on the transistor in use. The maximum voltage efficiency must be determined or estimated for each application by the designer.

The current conversion efficiency of Eqn. 2.4 has a broad range of possible values. For an amplifier it can vary from 0.50 to 1.00. For a multiplier it can vary between zero and 1.00. It is shown experimentally that the current efficiency is a definite function (albeit a complicated one) of transistor conduction angle. At the same time, current efficiency is essentially independent of the type of or individual transistor employed in the circuit. Since current efficiency can not be easily evaluated and is very important, it will receive a comprehensive study.

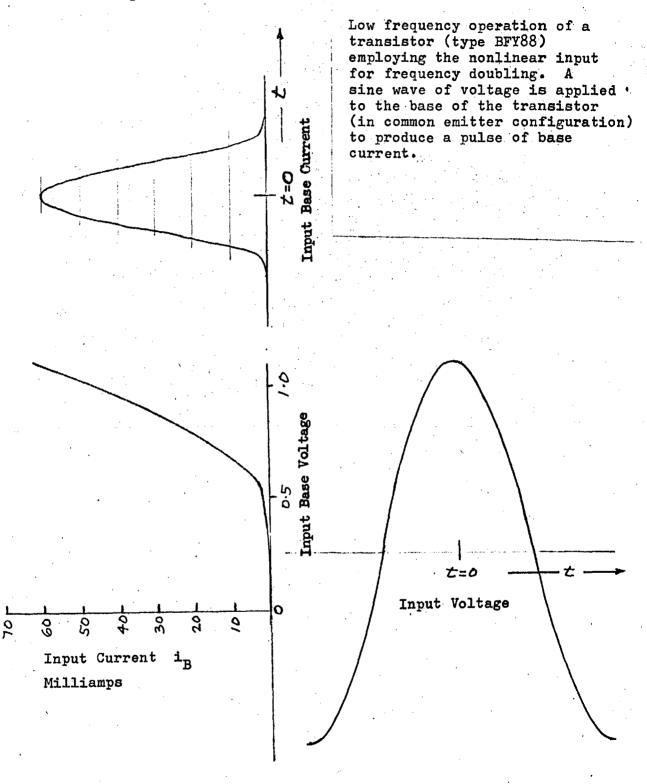

### 2.3 Low Frequency Graphical Analysis

NIAM operation of the transistor at low frequencies is similar to frequency multipliers and power amplifiers using the valve. The similarity is widely recognised that has received excessive attention. It is frequently assumed, incorrectly, to exist at high frequencies. Because design methods are already available (being converted from valve methods that also developed specifically for transistors 10, 20) only a rudimentary graphical method will be presented here.

The transistor characteristic at low frequencies (less than  $f_{\beta}/2$ ) may be specified quite simply. At low frequencies, the transistor terminal currents are single valued functions of the terminal

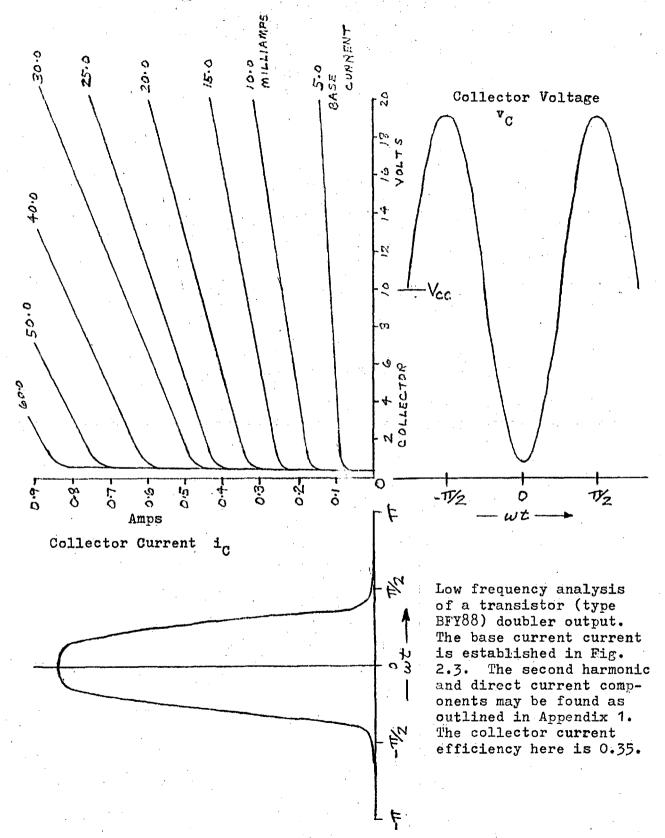

voltages, permitting the transistor action to be defined graphically on a current versus voltage basis. An example will be given dealing with a common emitter doubler. The same approach will deal with power amplifiers through to times-six frequency multipliers. The analysis may be applied to a common base circuit with the proper choice of transistor characteristics. As with valve circuits, the analysis of this circuit is best initiated by examining the effect of the applied sinusoidal voltage on the input. The input voltage, with biasing, is set so as to produce a particular peak collector current and a certain conduction angle. High factors of frequency multiplication or high current efficiencies  $(\eta_{CT})$  in amplifiers require small conduction angles. The input characteristic of the transistor, employed as a doubler, is shown in Fig. 2.3. After the shape of the input current pulse is determined the fundamental component of the input current may be determined using a graphical Fourier analysis. Equations for determining harmonic components of a symmetrical (about a particular time axis) waveform are given in Appendix 1. The fundamental current to the input of the transistor may be calculated, permitting the power input to the transistor to be evaluated. Since the transistor input behaves like a nonlinear resistance, the input current is in phase with the input This is true for the input and output currents and voltages of the transistor at low frequencies (viz. all phase angles are zero). The input operating characteristics such as, biasing voltage on input and

input impedance, may now be determined. From the peak base current we may find the peak collector current using the appropriate plot of collector characteristics (see Fig. 2.4). Once the peak collector current is determined, the minimum collector voltage may be found (see Eqn. 2.6). The peak harmonic collector voltage may be evaluated after the minimum collector voltage is known and the supply voltage V<sub>CC</sub> is set. The harmonic voltage must be sketched in, permitting the collector current to be determined as shown in Fig. 2.4. The collector current pulse may then be determined as a function of base current. collector voltage and time. The appropriate harmonic and the direct components of current of the collector current pulse may be determined graphically by the method outlined in Appendix 1. The evaluation of  $\mathbf{I}_{\mathrm{CO}}$  and  $\mathbf{I}_{\mathrm{Cn}}$  permits the calculation of the harmonic output power, the direct power input to the collector, the collector efficiency, the transistor power dissipation and the load resistance. Equations 2.1 through to 2.5 may be used to advantage in these calculations.

The important parameters of a low frequency power amplifier may thus be determined.

### 2.4 Assumed High Frequency Current Waveforms

It is intended here to first find the harmonic current generating characteristics of the intrinsic base at high frequencies when the assumed sinusoidal voltages are applied. The high frequency conditions

Figure 2.4

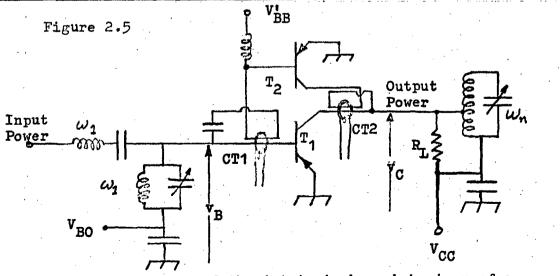

exist if the input frequency is greater than 3fg. Stray effects may be very important but the intrinsic base is essentially the active portion of the transistor providing the power gain and the conversion of direct power into rf power. The effects of the strays are best assessed after the basic multiplication and energy conversion processes are understood. The depletion layer capacitances of the transistor obscure the operation of the base without necessarily degrading the frequency multiplying or amplifying performance. For observation of the current waveforms in actual transistors, a method of balancing out the depletion layer capacitance currents is developed. Two balanced transistors are used, one under normal conditions and the other always reversed biased. In this way the capacitive current flow in the inactive transistor may be subtracted electrically from the current flow in the active transistor. Thus the measurement circuits show only the current flow into the intrinsic base of active transistor. This circuit is shown in Fig. 2.5.

Measurement of currents of the intrinsic base behaviour of a transistor NIAM. The depletion layer capacitance currents of  $T_2$  cancel those of  $T_1$ , the transistor being examined.

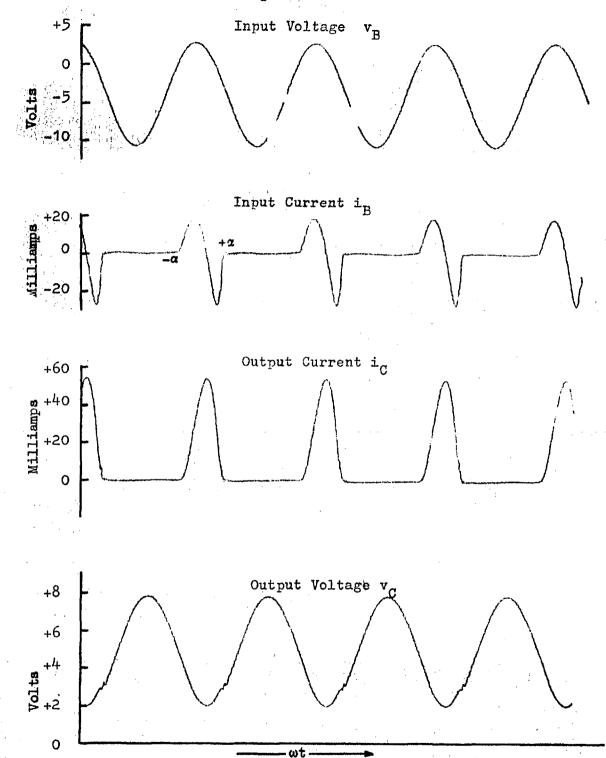

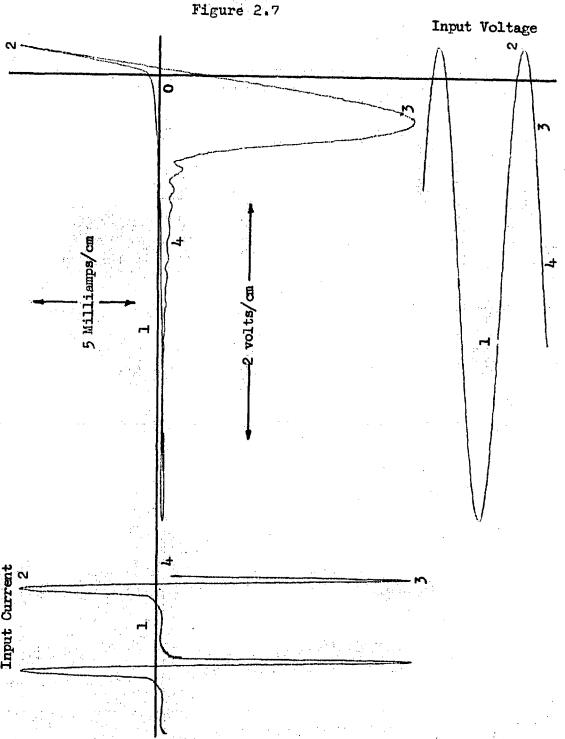

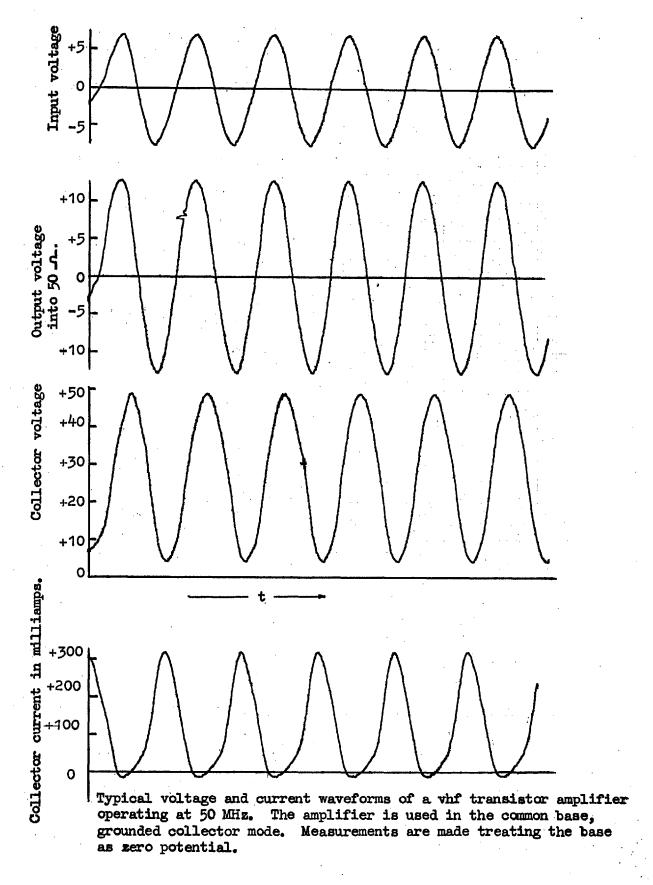

Insight into the multiplying operation of the intrinsic base may be gained most quickly by a study of the relations between the input voltage and current waveforms as presented in Fig. 2.6. The collector current is proportional to the integral of the base current. From the charge control relations<sup>21</sup> we may write.

$$i_{C} = \frac{1}{\tau_{f}} \int i_{B} dt$$

2.7

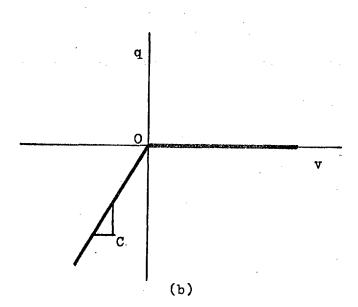

This equation follows from the more usual charge control relations under the present high frequency conditions, where minority carrier recombination is negligible. The clue to the operation of the whole circuit is the behaviour of the base current. The base current is a scaled replica of the input voltage, for a large part of the active cycle (i.e. where  $-\alpha < wt < \alpha/2$ ). A detailed knowledge of the input impedance characteristic of the transistor can be obtained from the voltage-current relationship measured at the base terminal and plotted in Fig. 2.7. Input voltage is plotted on the vertical axis, current on the horizontal. Numbers 1 to 4 are marked in Fig. 2.7 to indicate various regions of operation. Small allowances must be made for the incompletely balanced-out depletion layer capacitance currents. region between numbers 1 and 2 is very similar to that found at very low frequencies in a diode and will be called the exponential region; charge being stored in the base. The region between numbers 2 and 3 is called the "linear charge-discharge" region. The slope of this line is

Typical amplifier (or multiplier) voltage and current waveforms, using the nonlinear input. The measurements were made at 2.0 MHz on an OC42. Note that the input current is roughly a scaled replica of the input voltage over the region  $-\alpha < \omega t < \alpha/2$ .

The relationship of input current and voltage of a transistor (type OC42) NIAM at 2.0 MHz. input. The measurement was obtained using a dual channel sampling oscilloscope (HP 185B with a 187B plugin unit). One channel measured i<sub>B</sub> and the other  $v_C$ . This plot was then obtained using an x-y recorder. The measured circuit is shown in Figure 2.5.

controlled by the extrinsic base resistance of the transistor. The region from numbers 3 to 4 is called the "residual charge removal" region. The "residual charge" typically amounts to about one half of the maximum stored charge. Many transistors have been examined and the first two regions, namely the "exponential" and the "linear chargedischarge" region are very consistent. However, the shape and the duration of the last region is very changeable. In diffusion transistors (where impurity doping is essentially constant across the base) the shape of the "residual charge removal" region has been found to vary considerably even among transistors of the same type number. In planar, double diffused transistors (with both retarding and aiding fields in the base) the "residual charge removal" region is found to vary considerably both in shape and duration with a changing conduction angle; the other two regions maintaining their shape. It has been found experimentally that a planar transistor may exhibit a step recovery characteristic for small conduction angles and exhibit an exponential recovery (with a relatively long time constant) for large conduction angles.

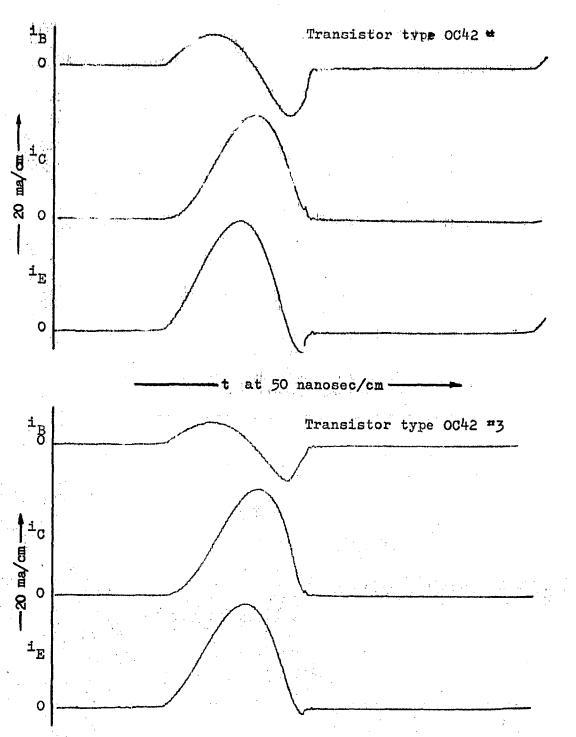

In Fig. 2.8 the three terminal currents of two diffusion transistors of the same type have been noted in detail. The charge control relationship between the base current and collector current, described in Eqn. 2.7, may be verified in these figures. The variation in the time delay of the collector current pulse, the emitter current recovery, and the shape of the base "residual charge removal" may be seen to be significant.

Transistor currents of NIAM operation. Note the differences in the base currents and in the emitter currents. The differences are attributed to different electric fields in the base.

The charge removal problem here is very similar to the charge removal problem in diodes at high frequencies. The charge recovery characteristics are dependant upon operating voltages and currents as well as the electrical and physical construction of the diode or transistor. Analysis of diodes is only partially successful and yet these are much simpler to analyse than transistors. Due to the impossibility of accurate analysis, simplifying assumptions must be made.

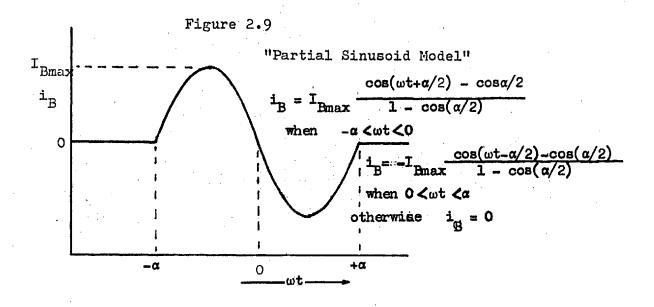

Since charge control relations apply at our operating frequencies, we need only assume a certain current waveshape for either the base or collector and the other is implied. The method adopted here assumes a certain base current and then the collector current is determined using the charge control relations. We see that if the transistor is forward biased by the sine wave of voltage on the base, the base current has a waveshape virtually identical to the voltage waveshape. Thus for about one half of the complete cycle the input current is a truncated sine wave. The other half of the input current pulse is extremely variable and one particular current waveshape will not accurately describe all the possibilities. It is advantageous in the following analysis to have a symmetrical waveform. For these reasons it is felt best to assume that the second part of the current pulse has the same shape but opposite sign to the first part of the current pulse. The assumed base current waveshape may be seen in Fig. 2.9.

The base current may be defined algebraically, as follows.

$$i_{B} = I_{Bmax} \left( \frac{\cos(\omega t + \alpha/2) - \cos^{\alpha}/2}{1 - \cos^{\alpha}/2} \right)$$

when  $-\alpha < \omega t < 0$

and

$$i_{B} = -I_{Bmax} \left( \frac{\cos(\omega t - \alpha/2) - \cos^{\alpha}/2}{1 - \cos^{\alpha}/2} \right)$$

when  $0 < \omega t < \alpha$

otherwise  $i_{B} = 0$

This waveshape will be called the partial sinusoid model.

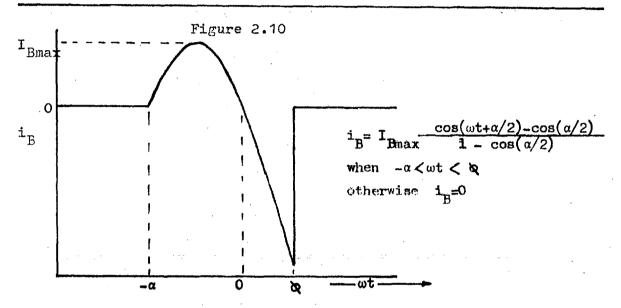

Two other workers 11,12 on transistorised class C amplifiers have made approximations to the transistor current waveforms.

Slatter 12 developed an approach much the same as above but assumed a step-recovery characteristic for the base current as shown in Fig. 2.10.

Base current exhibiting a step-recovery characteristic. Ther is no net charge input to the transistor, and  $\alpha$  is related to  $\alpha$  on this basis.

Such a characteristic is accurate for some planar transistors operated at small conduction angles. It is, however, inaccurate for the majority of transistors. This approach also has the disadvantage that the harmonic components of the input current waveform contain an associated phase angle.

In the partial sinusoid model, the phase angle of any harmonic current is zero due to the symmetry of the waveform. Scott li in an

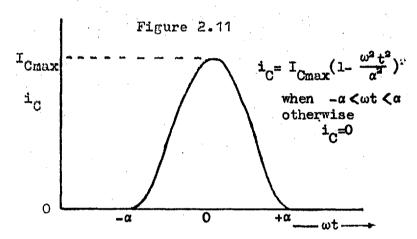

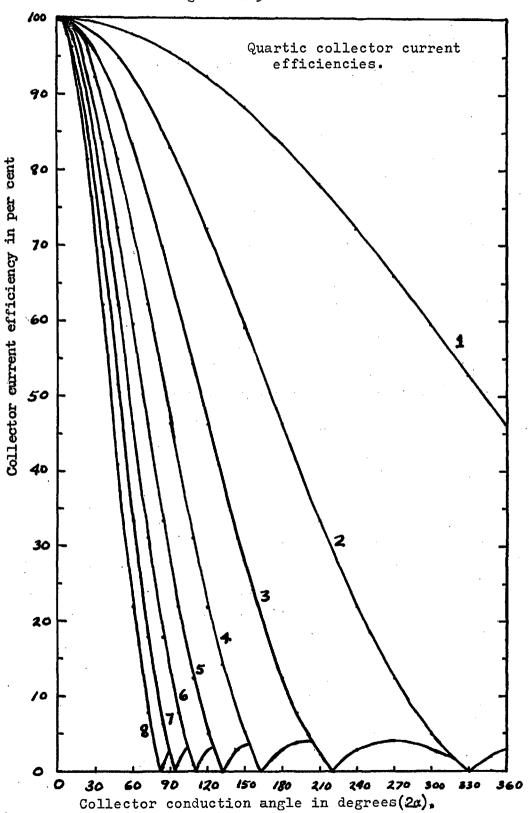

earlier analysis of a transistor class C amplifier assumed a "quartic" output current waveform, shown in Fig. 2.11.

Assumed collector current pulse shape referred to as the "quartic model".

We shall see later that calculated collector efficiencies from this model are good but not as accurate as those produced by the "partial sinusoid model". Other workers have considered idealised collector currents with truncated sine waves or rectangular pulses. These models have only convenience to recommend them for they bear little resemblance to the actual waveforms found in transistor NIAM. The last models will receive no further consideration.

# 2.5 Collector Current Efficiency

To determine the collector current efficiency we need only

determine I<sub>Cn</sub> and I<sub>CO</sub> and by using Eqn. 2.4 the required efficiency can be determined. It may be shown, using Eqn. 2.7, that

$$I_{Cn} = \frac{I_{Bn}}{n\omega \tau_{e}}$$

2.9

Thus, in order to determine I<sub>Cn</sub>, we may do a Fourier analysis on the input base current. That is,

$$I_{Bn} = \frac{I_{Bmax}}{\pi} \int_{-\alpha}^{0} \frac{\cos(\omega t + \alpha/2) - \cos^{\alpha}/2}{1 - \cos^{\alpha}/2} \sin(n\omega t) d\omega t$$

$$-\frac{I_{Bmax}}{\pi} \int_{0}^{+\alpha} \frac{\cos(\omega t - \alpha/2) - \cos^{\alpha}/2}{1 - \cos^{\alpha}/2} \sin(n\omega t) d\omega t$$

$$= \frac{I_{Bmax}}{\pi(1 - \cos^{\alpha}/2)} \left\{ \frac{\cos(n\alpha + \alpha/2) - \cos^{\alpha}/2}{n + 1} + \frac{\cos(n\alpha - \alpha/2) - \cos^{\alpha}/2}{n - 1} + \frac{2\cos^{\alpha}/2}{n} (1 - \cos^{\alpha}n) \right\}$$

$$+ \frac{2\cos^{\alpha}/2}{n} (1 - \cos^{\alpha}n)$$

2.10

It is now possible to determine  $I_{Cn}$ . Next  $I_{CQ}$  must be evaluated.

Using Eqn. 2.7 and part of Eqn. 2.8 we may write,

$$\hat{\mathbf{1}}_{\mathbf{C}} = \frac{\mathbf{I}_{\mathrm{Bmax}}}{\mathbf{w}^{\mathsf{T}}_{\mathbf{f}}} \int_{0}^{\frac{\cos(\mathbf{w}t + \alpha/2) - \cos^{\alpha/2}}{1 - \cos^{\alpha/2}}} d\mathbf{w}t$$

$$= \frac{\mathbf{I}_{\mathrm{Bmax}}}{\mathbf{w}^{\mathsf{T}}_{\mathbf{f}}} \left[ \frac{\sin(\mathbf{w}t + \alpha/2) - \mathbf{w}t \cos^{\alpha/2}}{1 - \cos^{\alpha/2}} \right]_{0}^{\mathbf{w}t}$$

$$i_{C} = \frac{I_{Bmax}}{\omega \tau_{f}} \left( \frac{\sin(\omega t + \alpha/2) - \omega t \cos^{\alpha}/2 + \sin^{\alpha}/2 - \alpha \cos^{\alpha}/2}{1 - \cos^{\alpha}/2} \right)$$

in the interval of  $-\alpha < \omega t < 0$

Due to the symmetry of the collector current waveshape we may say that

$$i_{C}(\omega t) = i_{C}(-\omega t)$$

$$i_{C} = \frac{I_{Bmax}}{\omega \tau_{f}} \frac{\sin(-\omega t + \alpha/2) + \omega t \cos^{\alpha}/2 + \sin^{\alpha}/2 - \alpha \cos^{\alpha}/2}{1 - \cos^{\alpha}/2}$$

in the interval of 0 <  $\omega t$  <  $\alpha$

Otherwise  $i_{C} = 0$

To find the collector direct current, it is only necessary to average the collector current. Therefore,

$$I_{CO} = \frac{2I_{Bmax}}{2\pi\omega\tau_{f}} \int_{-\alpha}^{0} (\sin(\omega t + \alpha/2) - \omega t \cos^{\alpha}/2 + \sin^{\alpha}/2 - \alpha\cos^{\alpha}/2) d\omega t$$

$$= \frac{I_{Bmax}}{\pi\omega\tau_{f}} \left[ \frac{-\cos(\omega t + \alpha/2) - (\omega^{2}\tau^{2})\cos^{\alpha}/2 + \omega t \sin^{\alpha}/2 - \omega t \cos^{\alpha}/2}{1 - \cos^{\alpha}/2} \right]_{-\alpha}^{0}$$

$$I_{CO} = \frac{I_{Bmax}}{\pi\omega\tau_{f}} \frac{\alpha\cos^{\alpha}/2 - (\alpha^{2}/2)\cos^{\alpha}/2}{1 - \cos^{\alpha}/2}$$

$$2.12$$

The collector current efficiency may be determined through the manipulation of Eqns. 2.9, 2.10 and 2.12.

$$\eta_{CI} = \frac{\frac{\cos(n\alpha + \alpha/2) - \cos^{\alpha}/2}{n+1} + \frac{\cos(n\alpha - \alpha/2) - \cos^{\alpha}/2}{n-1} + \frac{2\cos^{\alpha}/2}{n} (1-\cos n\alpha)}{2n(\alpha\sin^{\alpha}/2 - \frac{\alpha^2}{2}\cos^{\alpha}/2)}$$

2.13

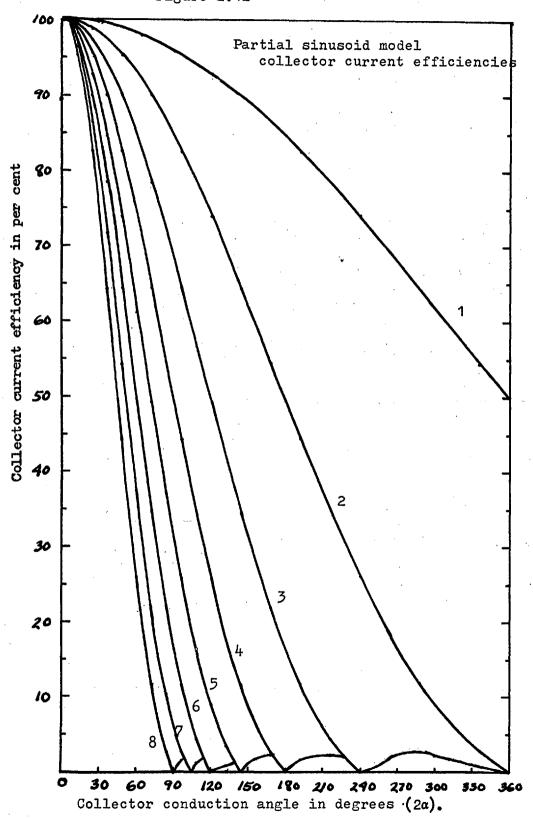

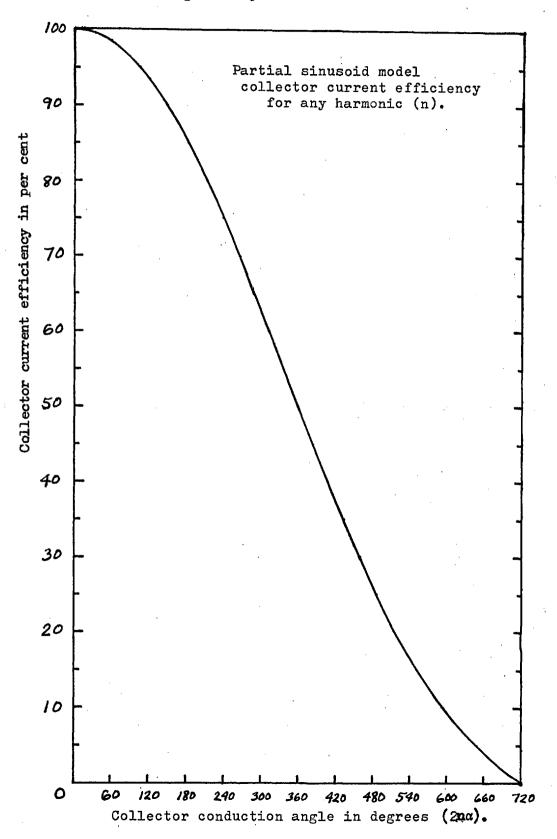

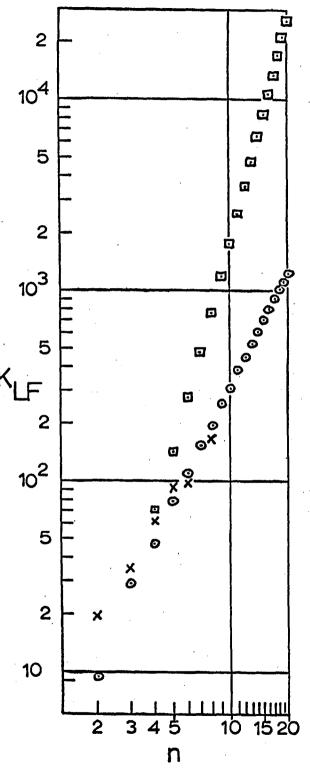

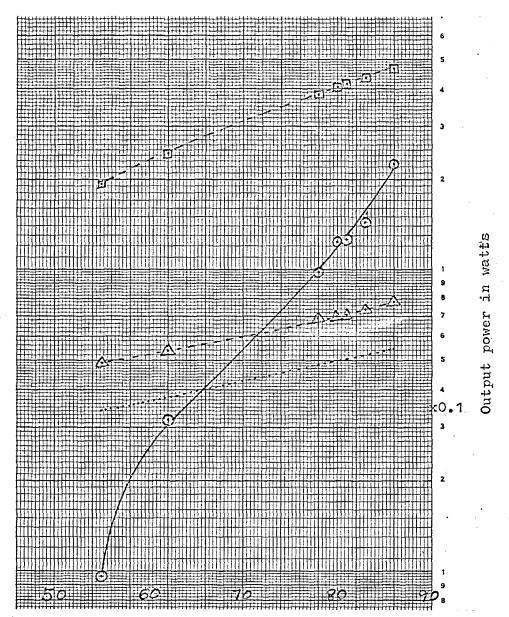

This efficiency is plotted as a function of n and 2a in Fig. 2.12.

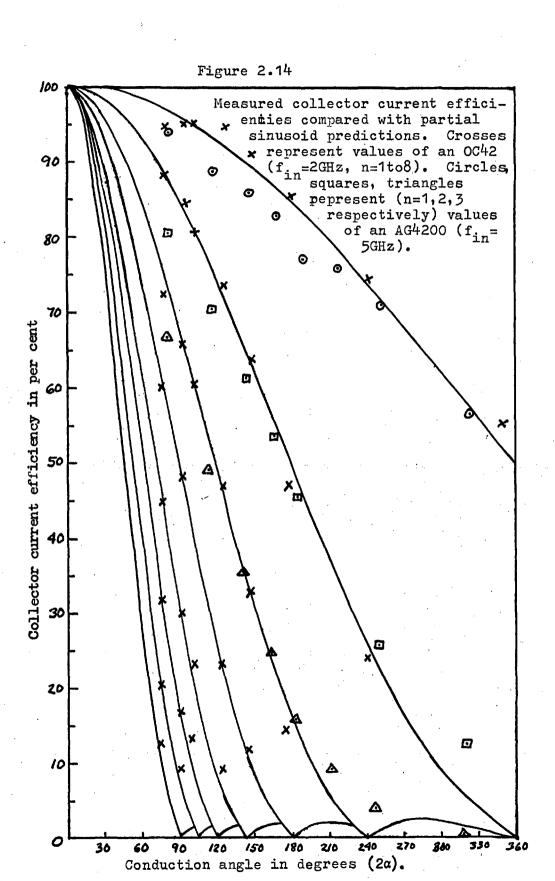

A comparison may be made with efficiency calculations, obtained by Scott\*, which are plotted in Fig. 2.13. In Fig. 2.14, the efficiencies are plotted for the partial sinusoidal model and compared with measured

<sup>\*</sup>The calculations are extrapolations on Scott's amplifier analysis for application to frequency multipliers.

Figure 2.12

Figure 2.13

current efficiencies on two kinds of transistors. Agreement between the calculated and measured values is well within the accuracy of the instruments used. The "partial sinusoid" model is in closer agreement with the measured results than the "quartic" model. The circuit used for the measurements is shown in Fig. 2.5. The circuit measures the harmonic output without feedback and hence permits the measurement of the collector current efficiency. Thus the collector current efficiency has been calculated using Eqn. 2.5. This equation may be used to evaluate the ability of a transistor to convert direct power into radio frequency power.

A careful examination of Fig. 2.12 shows that the efficiency of any harmonic may be found with no and one equation. That is if  $\eta_{CI1} = f_1(\alpha)$  then  $\eta_{CIn} = f_1(n\alpha)$ , with an accuracy of about 0.1%. This is useful since we now require only one equation or graph to determine the current efficiency of any particular harmonic. If a multiplier is to have a practical collector conversion efficiency no must be less than  $360^{\circ}$ . The single graph is shown in Fig. 2.15.

The foregoing analysis may be applied to an amplifier or a frequency multiplier in the common base configuration without any modification.

# 2.6 Input Power Requirements

In a power amplifier or a frequency multiplier the input power requirement is of prime interest. High efficiency amplifying or

Figure 2.15

frequency multiplying can only be attained at the expense of increased input power. The transistor input voltage and current waveforms are already idealised and calculation of the input power is thus facilitated. The input power requirement is calculated by multiplying the input voltage with the fundamental input current and the appropriate phase angle. This is somewhat different from assuming that all of the input power is dissipated in the base resistance, as previous analyses 11,12 have done.

$$P_{Bin} = \frac{-I_{B1}}{2} V_{B1} \cos(90 - \alpha/2)$$

2.14

From Figs. 2.6 and 2.9 it may be seen that,

$$V_{B1} = \frac{I_{Bmax} r_{bb}}{1 - \cos^{\alpha}/2}$$

Using Eqn. 2.9, with some manipulation, it may be shown that,

$$I_{Bl} = \frac{I_{Bmax}}{\pi(1-\cos^{\alpha}/2)} \left(\frac{-\cos^{3\alpha}/2 + \cos^{\alpha}/2}{2} - \alpha \sin^{\alpha}/2\right) \qquad 2.16$$

The input power of the multiplier or amplifier may now be calculated through the manipulation of Eqns. 2.14, 2.15 and 2.16.  $P_{Bin} = \frac{-I^2_{Bmax}}{(1-\cos^{\alpha}/2)^2} \times \frac{\dot{r}_{bb}}{2^{\pi}} \times \left(\frac{-\cos^{3\alpha}/2 + \cos^{\alpha}/2}{2} - \alpha \sin^{\alpha}/2\right) \sin^{\alpha}/2 \quad 2.17$

The input power of Eqn. 2.17 is more usefully expressed in normalised form; using Eqn. 2.17 and 2.9 we obtain;

$$P_{\text{Bin}} = \frac{I^2_{\text{Bn}} r_{\text{bb}}}{2} \times \frac{\pi \left(\frac{-\cos 3^{\alpha}/2 + \cos^{\alpha}/2}{2} - \alpha \sin^{\alpha}/2\right) \sin^{\alpha}/2}{\left(\frac{\cos(n\alpha + \alpha/2) - \cos^{\alpha}/2}{n+1} + \frac{\cos(n\alpha - \alpha/2) - \cos^{\alpha}/2}{n-1} + \frac{2\cos^{\alpha}/2}{n} (1 - \cos^{\alpha}/2)\right)}$$

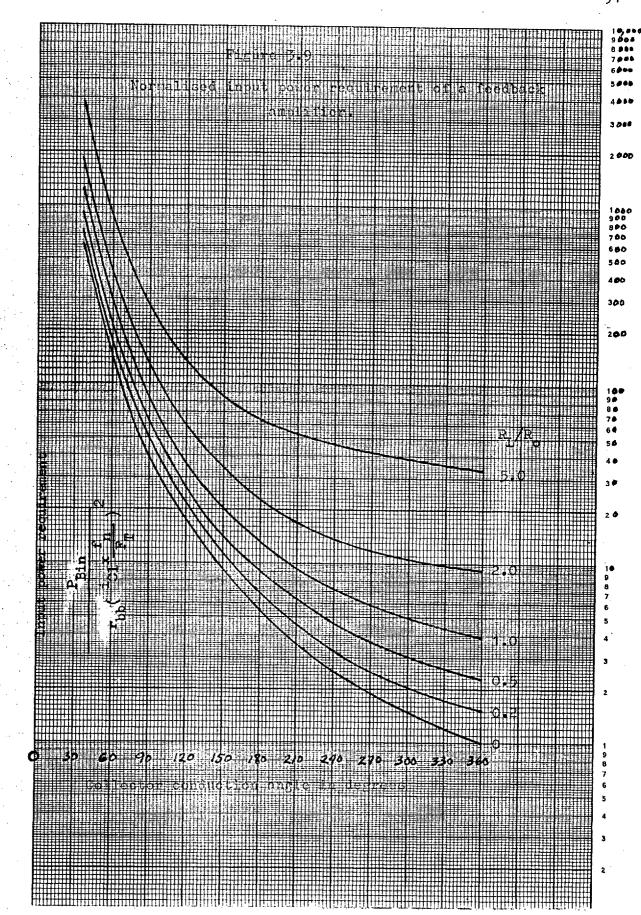

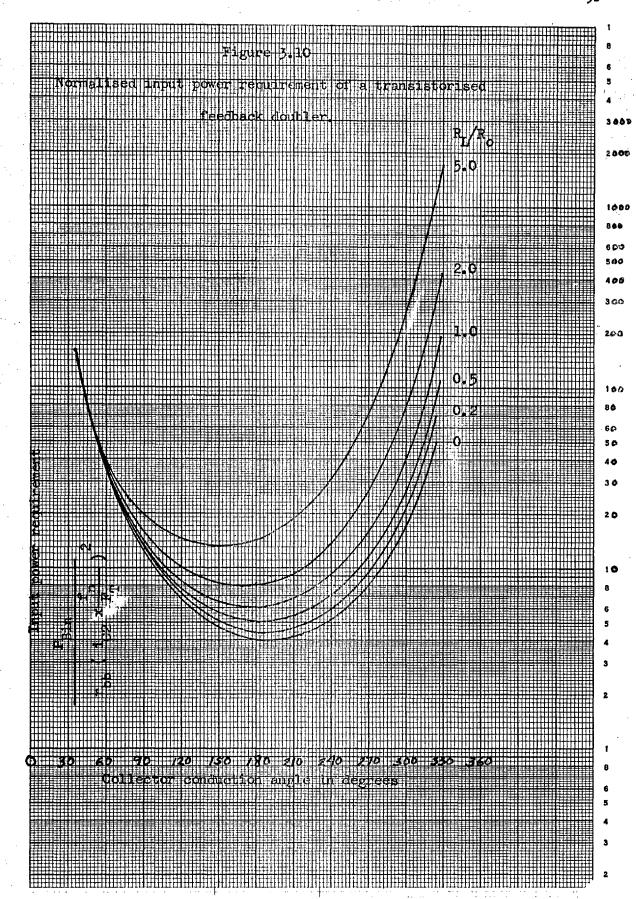

This expression is plotted in Fig. 2.16 as a function of conduction angle  $(2\alpha)$  and of n. It may be noted that there is a very definite conduction angle at which the normalised input power may be minimised for each harmonic. The optimum conduction angle is approximately 360°/n. This value is obtained from examination of Fig. 2.16, and corresponds to a realistic collector efficiency of .50 for each harmonic. Fig. 2.16 permits the comparison of power amplifiers and multipliers that have the same output frequency. By maintaining a constant output frequency, identical output conditions and a constant current gain at the frequency of interest are maintained. The loss in gain, to obtain frequency multiplication for any practical conduction angle may be found in Fig. 2.16. The minimum loss in gain (with respect to that of a class A amplifier) is found to be a factor of (3.0n - 2.0). input power must be increased by this amount, when the input frequency is decreased by a factor of n. to obtain the same output current magni-The output current determines the power output when the other output parameters (such as V<sub>CC</sub> and R<sub>L</sub>) are fixed. In a multiplier, the conduction angle may be decreased, from above, to improve the collector efficiency with an attendant decrease in gain. It is normally bad design to make the conduction angle larger, than that just recommended, since both the power gain and collector efficiency are degraded by doing so.

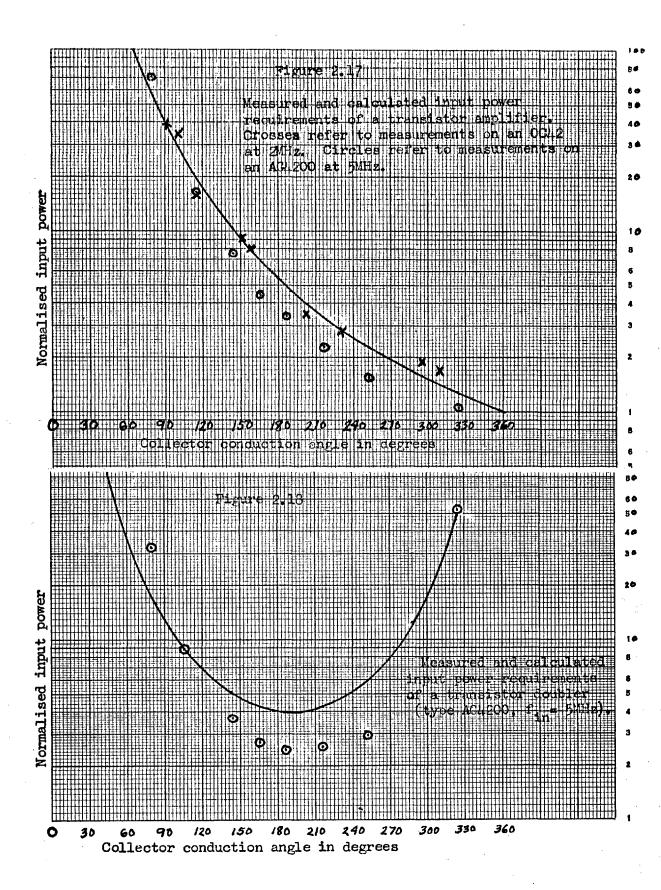

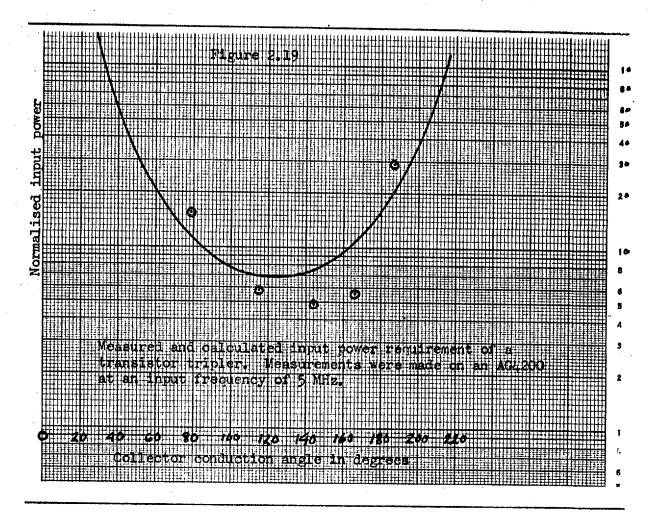

The curves of Fig. 2.16 have been verified by measuring the input power to a transistor. Figs. 2.17, 2.18 and 2.19 verify

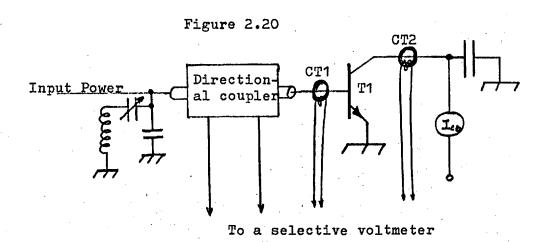

experimentally input power requirements for an amplifier, a doubler, and a tripler respectively. The agreement is good although it appears that the assumed value of extrinsic base resistance was slightly large. In Fig. 2.17 the measured input power is lower than that predicted by theory for large conduction angles. However, for small conduction angles the measured input power is larger. The latter effect will be explained in the next chapter. Shown in Fig. 2.20 is the circuit

A setup for measuring the input power to a transistor amplifier or multiplier. This method avoids losses in the input tuned circuit. The selective voltmeter indicates the forward and reverse power flow in the directional coupler and also the harmonic current flow in the base and collector. The collector is earthed to avoid capacitive feedback.

diagram of the measurement set-up. The input power to the transistor is measured with a directional coupler. This method eliminates the input tuned circuit losses which become significant over a large part of the range of conduction angle.

# 2.7 Maximum Harmonic Current Flow

Frequently transistors have a very low emitter-base breakdown potential. It is a serious limitation on transistor power amplifiers and frequency multipliers where large reverse bias voltages are necessary to obtain high efficiencies by small conduction angles. The

input voltage may be found using Eqn. 2.8 and adding the threshold conduction voltage  $(V_{\rm Bcon})$  of the transistor input. Thus,

$$v_{B} = I_{Bmax} r_{bb} \left( \frac{\cos(\omega t + \alpha/2) - \cos^{\alpha}/2}{1 - \cos^{\alpha}/2} \right) + V_{Bcon}$$

2.19

The maximum reverse voltage of  $v_B$  is obtained when wt =  $\pi = \alpha/2$ .

$$BV_{EB} - V_{Bcon} = \frac{I_{Bmax} r_{bb}}{2} \times \left(\frac{-1 - \cos^{\alpha}/2}{1 - \cos^{\alpha}/2}\right)$$

Note that  $BV_{EB}$  and  $V_{Bcon}$  are always of opposite sign and hence are normally added. Manipulation of the above equation and Eqn. 2.13 makes it possible to obtain,

$$\frac{I_{Bn}(BV_{EB}-V_{Beon})}{r_{bb}} = \frac{-0.5\pi(1+\cos^{\alpha}/2)}{\frac{\cos(n\alpha+\alpha/2)-\cos^{\alpha}/2}{n+1} + \frac{\cos(n\alpha-\alpha/2)-\cos^{\alpha}/2}{n-1}} + \frac{2\cos^{\alpha}/2}{n} (1-\cos n\alpha)$$

The equation is plotted in Fig. 2.21 as a function of n and of conduction angle. Measurements have verified Fig. 2.21 to a high degree of accuracy, although they are not shown. If the emitter reverse voltage limitation is very serious, it may be desirable to choose a conduction angle that provides the maximum possible harmonic current. For an amplifier the best angle is 360° and for any harmonic the best conduction angle is 512°/n. This conduction angle is substantially greater than the conduction angle that results in best gain and results in a collector current efficiency of only 0.21. The limitation itself is best avoided either by choosing a transistor with a large reverse

breakdown voltage or by using a low multiplication factor. It is evident from Fig. 2.21 that the input reverse breakdown limitation is most serious for the higher harmonics.

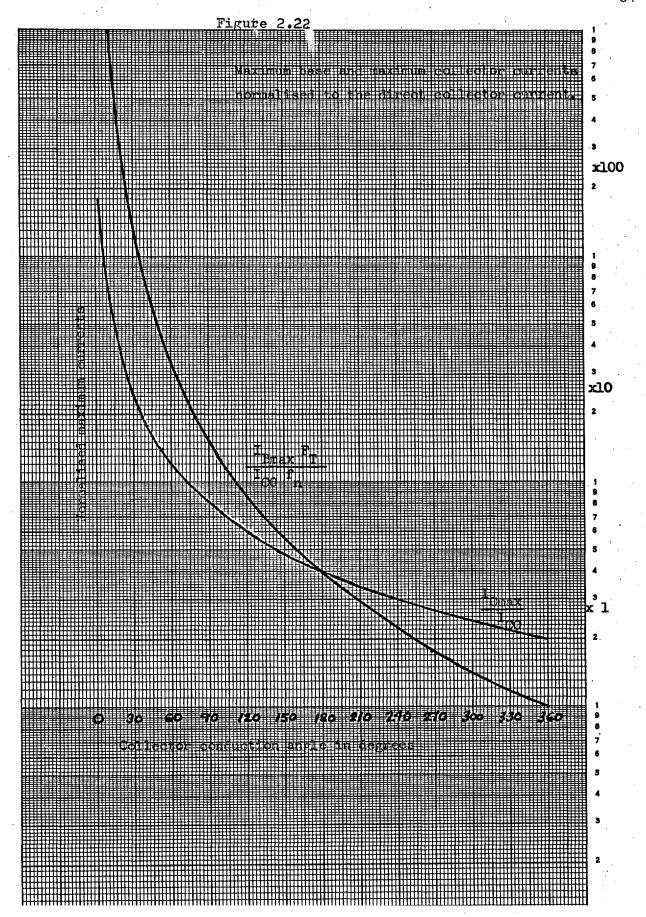

#### 2.8 Peak Input and Output Currents

In order that a transistor power amplifier or frequency multiplier may be designed, it is necessary to determine the peak collector

and peak base currents. The peak collector current may be determined

by evaluating Eqn. 2.11 when set = 0.

We have.

$$I_{\text{Cmax}} = \frac{I_{\text{Bmax}}}{\omega \tau_{\rho} (1 - \cos^{\alpha}/2)} \quad (2 \sin^{\alpha}/2 - \alpha \cos^{\alpha}/2) \quad 2.21$$

$I_{Cmax}$  is most useful if it is normalised to the direct collector current. Hence, using Eqn. 2.12 we have,

$$\frac{I_{\text{Gmax}}}{I_{\text{CO}}} = \frac{2\sin\alpha/2 - \alpha \cos\alpha/2}{\pi(\alpha\sin^2/2 - \alpha^2/2\cos^2/2)}$$

2.22

This equation is displayed in Fig. 2.22.

Now to determine the relationship between the peak base current and the collector current, Eqn. 2.12 must be examined.

$$\frac{I_{\text{Bmax}}}{I_{\text{CO}}\omega^{\tau_{\text{f}}}} = \frac{(1-\cos/2)}{\alpha\sin^{\alpha/2} - \alpha^{2}/2\cos^{\alpha/2}}$$

2.23

This relationship is also presented in Fig. 2.22.

It is useful to determine the biasing voltage necessary to obtain a certain desired conduction angle by finding the voltage at which the transistor is turned on. Substituting  $\omega t = 90^{-\alpha/2}$  into

Eqn. 2.19, we have,

$$V_{BO} = I_{Bmax} r_{bb} \left( \frac{-\cos^{\alpha}/2}{1-\cos^{\alpha}/2} \right) + V_{Beon}$$

2.24

The input tuned circuit can be designed most effectively after the input impedance of the transistor is determined from the input power and the input voltage (Eqn. 2.15).

$$V_{B1} = \frac{I_{Bmax} r_{bb}}{1 - \cos^{\alpha}/2}$$

Real

$$Y_{in} = \frac{2P_{Bin}}{v_{B1}^2}$$

2.25

### 2.9 Concluding Comments

In the foregoing chapter theory has been developed, neglecting the effect of depletion layer capacitance currents. Such an approximation for frequencies much lower than  $\mathbf{F}_T$  and the above theory could be used for many applications at frequencies greater than  $\mathbf{f}_\beta$  but much lower than  $\mathbf{F}_{T^*}$ .

The effects of the depletion layer capacitances are treated in the next chapter allowing the theory to be applied up to frequencies of about f<sub>max</sub>. A design example will be given in the next chapter to illustrate a design method. The above theory will be incorporated into this method.

#### CHAPTER THREE

# Effects of Transistor Strays on Nonlinear Input Operation of Multipliers and Amplifiers and Design Methods

#### 3.1 Complete Equivalent Circuit and Simplifications

The basic frequency multiplying and power amplifying characteristics of the intrinsic transistor (in common emitter configuration with sinusoidally applied input and output voltages) has been analysed in Chapter Two. In that analysis the extrinsic base resistance  $(r_{bb})$  was taken into account in conjunction with the intrinsic base. This was most expedient because the limitations caused by  $r_{bb}$  are of a very fundamental nature.

In Chapter Two it was found that current flow in the two depletion layer capacitances of the transistor were sometimes quite appreciable. The chief effect of these, if they are small, is only to obscure the intrinsic base behaviour. However, if these currents are large, there is a degradation of the multiplier or amplifier performance.

In this chapter the most significant extrinsic electrical characteristics of the transistor are investigated, the serious ones are determined and their effects are analysed. Some strays cause the transistor current and voltage waveforms to deviate from the theoretical ones without degrading the performance while others degrade the performance, as well. The latter strays will receive the most attention since the performance

of the resultant transistor circuit is of most interest.

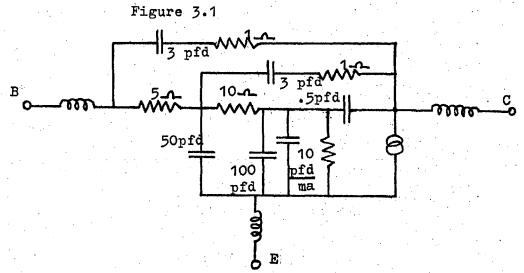

All transistors are electrically distributed devices but can be approximated, with respect to electrical performance, by a network of lumped elements. It is useful to examine a comprehensive equivalent circuit before one is chosen for analysis here. The equivalent circuit shown in Figure 3.1 is much more involved than is necessary for most

An equivalent circuit of a 2N3375. This transistor will produce 5 watts at 400 MHz as an amplifier. The circuit was derived by A.P. Anderson<sup>22</sup>. The transistor is of a planar construction with 156 separate emitters diffused into a common base and collector structure, permitting high frequency, high power operation.

applications. Normally, strays such as depletion layer capacitances and lead inductances become important in a planar transistor operating at a high frequency and high power. Many of the "strays" depicted in Figure 3.1 will become insignificant if, for example, a low frequency

alloy transistor is examined.

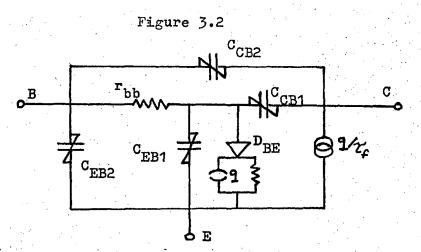

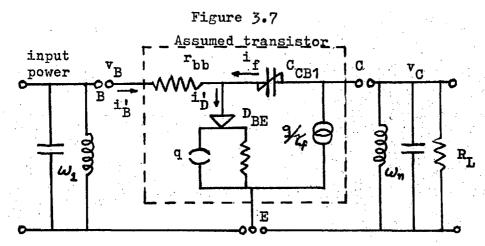

In almost all transistors the base resistance is distributed with capacitive loading from the emitter and collector depletion layers. For a practical circuit it is very difficult to carry out an analysis if the extrinsic base resistance is represented by more than one lump. In transistor data sheets one is fortunate to obtain an equivalent resistance value for a single lump representation (let alone more than one). Further lumping would complicate the analysis and increase difficulty in practical application. The equivalent circuit of Figure 3.1 is simplified by reducing the base resistance to a single lump. An input diode indicates 23 charge storage in the intrinsic base. We then obtain the circuit shown in Figure 3.2. The charge storage characteristic of the

Simplified equivalent circuit of a transistor. The charge storage characteristics of the intrinsic base  $(D_{\underline{b}e})$  is defined in Chapter Two.

intrinsic base (DBE) is assumed to behave according to the "partial sinusoid" idealisation made in Chapter Two. The equivalent circuit

is still quite involved but further reduction is possible. The two capacitances  $C_{\rm BE2}$  and  $C_{\rm BC2}$  are completely accessible, electrically. We are dealing with narrow-band amplifiers and multipliers, and therefore the two capacitances may be "tuned out" by external inductances at the fundamental or harmonic frequencies of interest. The external inductances required for this neutralisation in practice, cause some loss but for analytical purposes the loss is neglected. The effect of the other two depletion layer capacitances,  $C_{\rm BE1}$  and  $C_{\rm BC1}$ , must be considered separately if a tractable analysis is to result. The simplifying assumption, that the effects of the two capacitances are additive, is made.

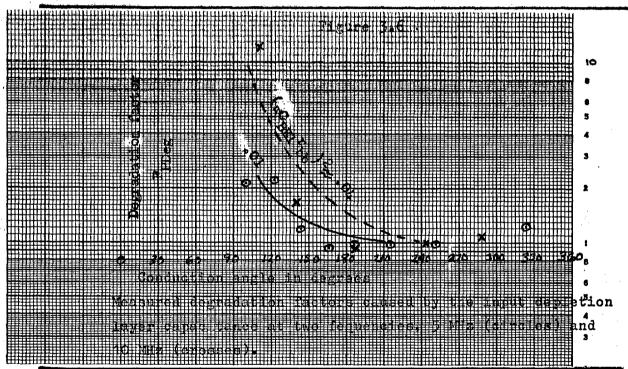

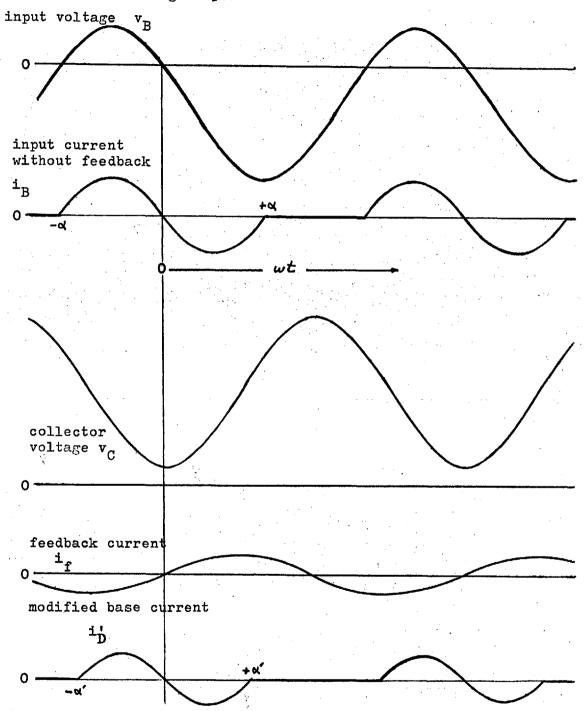

### 3.2 Effect of Input Depletion Layer Capacitance

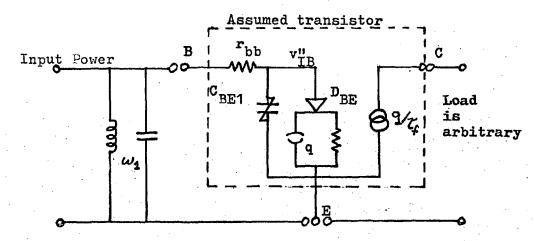

In evaluating the effect of the input depletion layer capacitance  $C_{\rm BE1}$ , the amplifier and multiplier operating assumptions, of sinusoidal input and output voltages and the partial sinusoid recovery of the base, are maintained. The effect of the depletion layer capacitance is treated as a small deviation from the previous theory. The circuit of Figure 3.3 forms the basis of the analysis.

The input capacitance C<sub>BEl</sub> is nonlinear but for simplicity in analysis it is assumed linear and in the analysis some further approximations are adopted. First, it is assumed that the effect of the capacitance is small, and the degradation of performance in regard to the power input requirement is calculated on this basis; the capacitance is then allowed to become large with the realisation that the analysis

Figure 3.3

Assumed equivalent circuit to evaluate effect of input depletion layer capacitance.

is approximate for this latter situation. The analysis is approached by calculating the voltage ( $v_{IB}^{"}$  in Figure 3.3) excursions across the capacitance and then deducing the current flow through the capacitance  $C_{BE1}$  as a result of the voltage excursions. The power dissipation in the base resistance due to this current flow is then calculated. This method neglects the modification of the voltage ( $v_{IB}^{"}$ ) due to the capacitance ( $C_{BE1}$ ) current flow through the base resistance. This is likely to be justifiable as long as  $0.1 > r_{bb} \omega c_{BE1}$ . It is assumed that the extrinsic base current ( $i_{D}$ ) and the input voltage ( $v_{B}$ ) are not modified by this capacitance current flow and these last two assumptions are in fact, verified to be well founded.

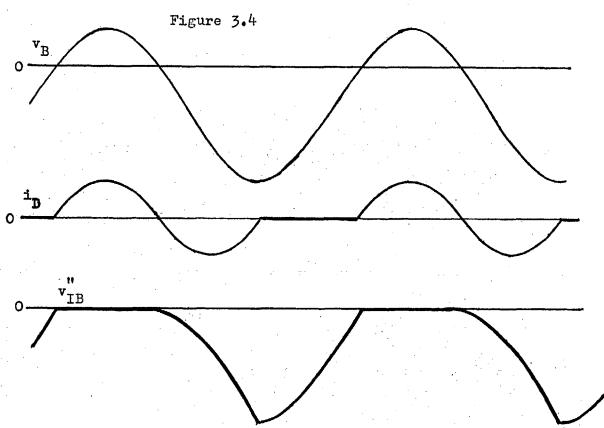

The input voltages that develop and cause the voltage variation on the input capacitance  $C_{\rm BE1}$  are shown in Figure 3.4.

$$v_B = i_B r_{bb} + v_{IB}^{"}$$

(3.1)

where  ${f v}_{

m B}$  and  ${f v}_{

m IB}^{

m H}$  are illustrated in Figures 3.3 and 3.4.  ${f i}_{

m D}$  is

The voltage drop across the extrinsic base resistance is subtracted from the input voltage to obtain the intrinsic base voltage.

the base charging current as defined by the "partial sinusoid" assumption of Chapter Two. We may find the fundamental input voltage (without the direct voltage term) from Eqn. 2.19.

$$v_B = r_{bb} I_{max} \left( \frac{\cos(\omega t + \alpha/2) - \cos \alpha/2}{1 - \cos \alpha/2} \right)$$

From Figure 3.4, we may see that,

$$v_{IB}^{"} = 0$$

in the interval of  $-\alpha < \omega t < 0$

$$(3.2)$$

Now we must find  $v_{IB}^{tt}$  in the interval of 0 <  $\omega t$  <  $\alpha$  From Eqn. 2.8

$$i_D = I_{B_{max}} \left( \frac{-\cos(\omega t - \alpha/2) + \cos \alpha/2}{1 - \cos \alpha/2} \right)$$

Substituting this equation and  $v_{\rm p}$  into Eqn. 3.1 we write,

$$v_{IB}^{m} = r_{bb} I_{B_{max}} \left[ \frac{\cos(\omega t + \alpha/2) + \cos(\omega t - \alpha/2) - 2 \cos \alpha/2}{1 - \cos \alpha/2} \right]$$

in the interval of 0 <  $\omega t$  <  $\alpha$

Now in the interval of  $-\alpha > \omega t$  and  $\omega t > \alpha$  the base current is essentially zero (the current in the depletion layer capacitance is assumed to be negligibly small for this) and therefore,

$$v_{IB}^{"} = v_{B}$$

$$-\alpha > \omega t \quad \text{and} \quad \omega t > \alpha$$

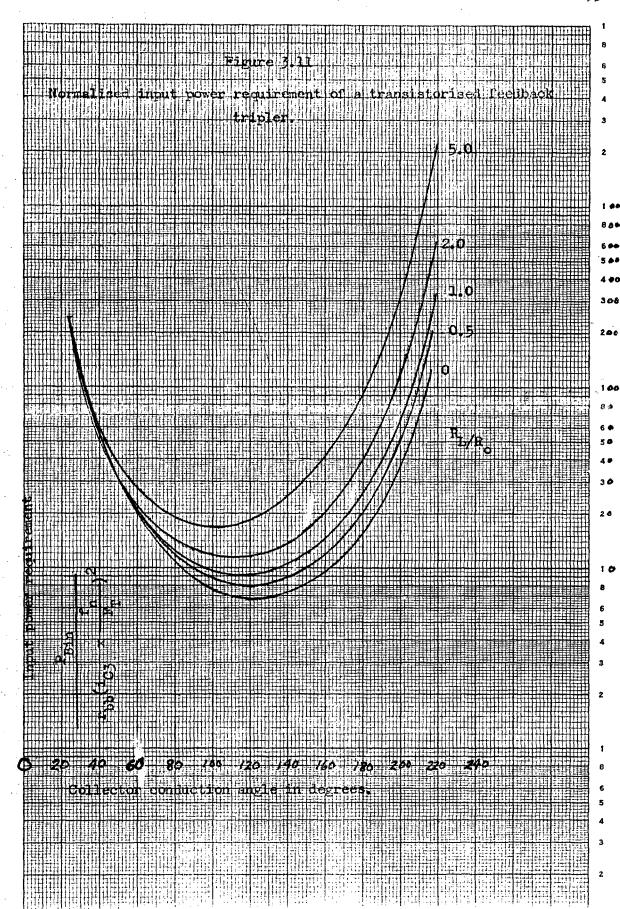

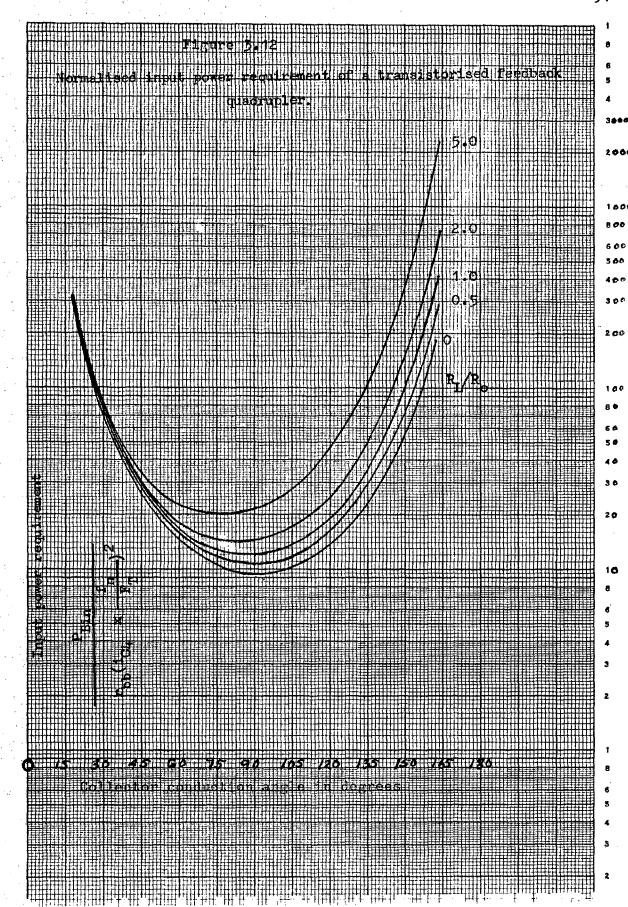

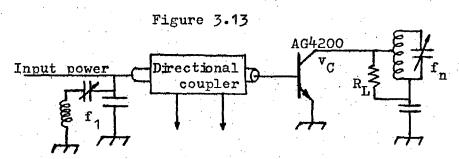

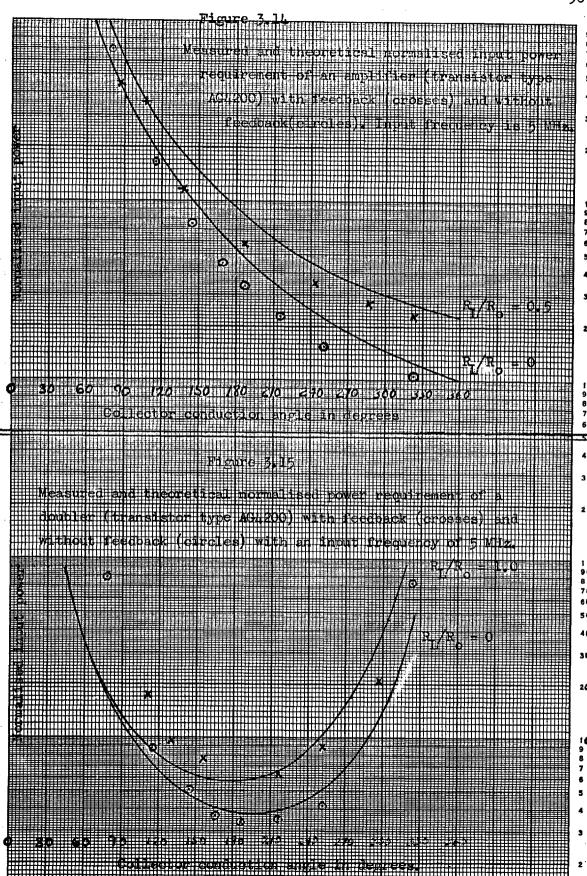

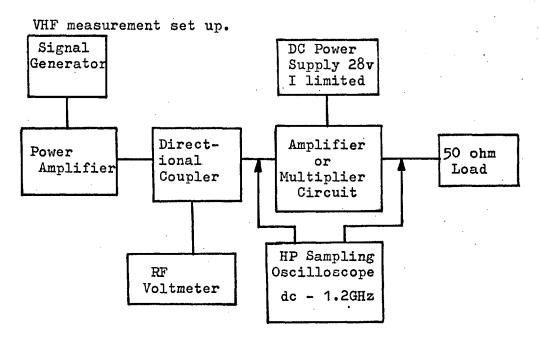

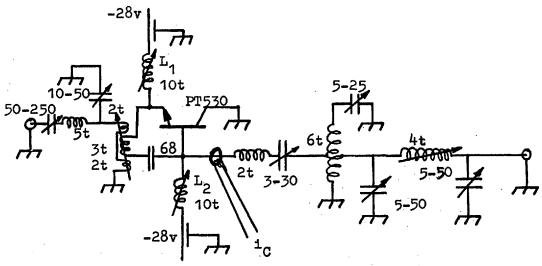

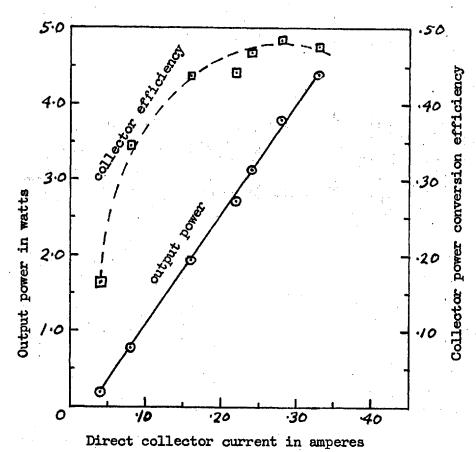

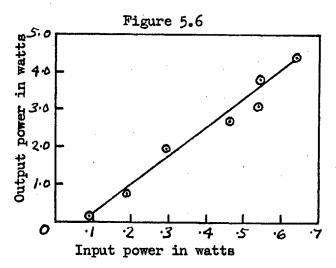

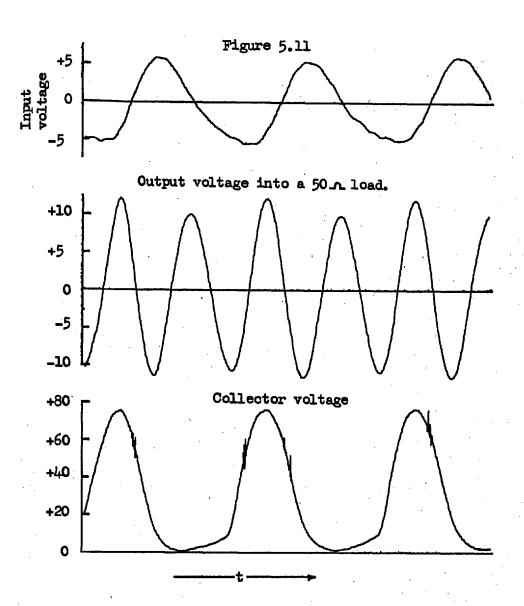

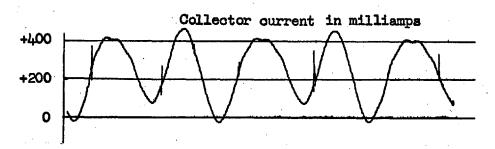

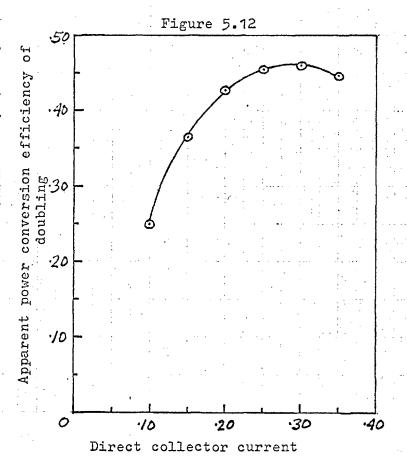

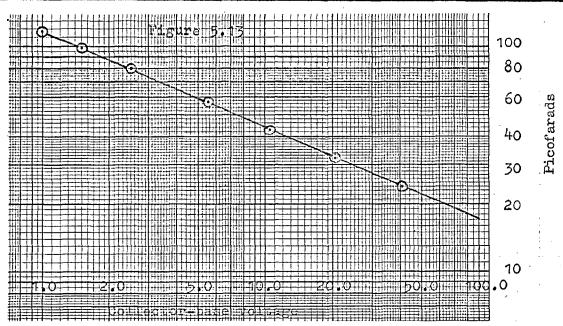

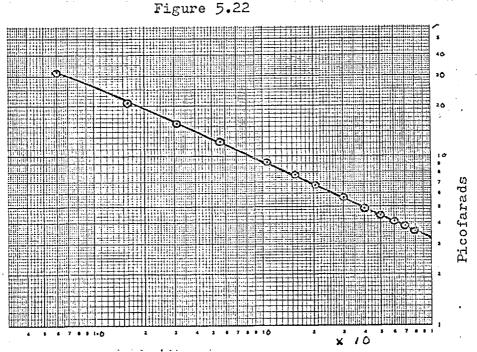

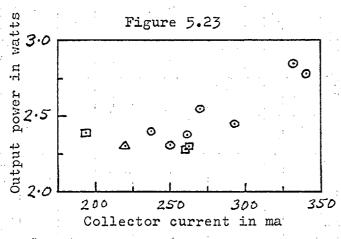

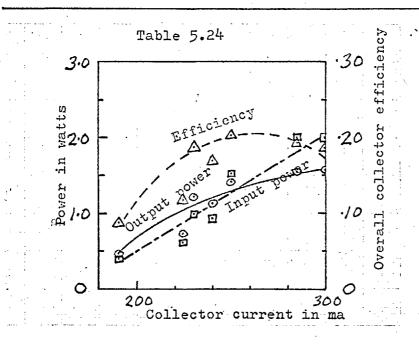

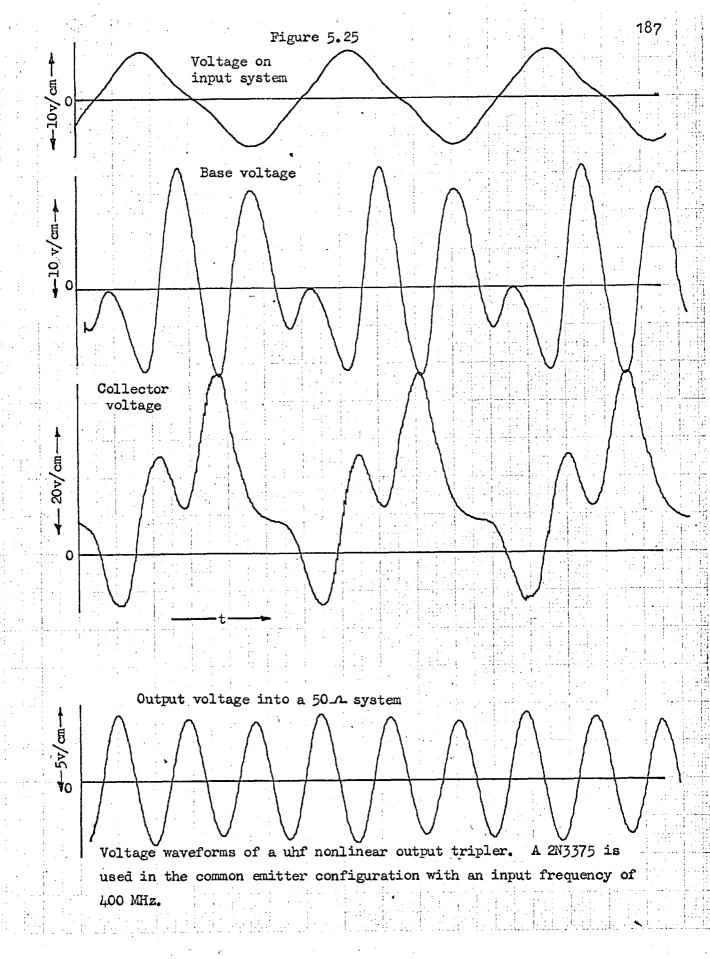

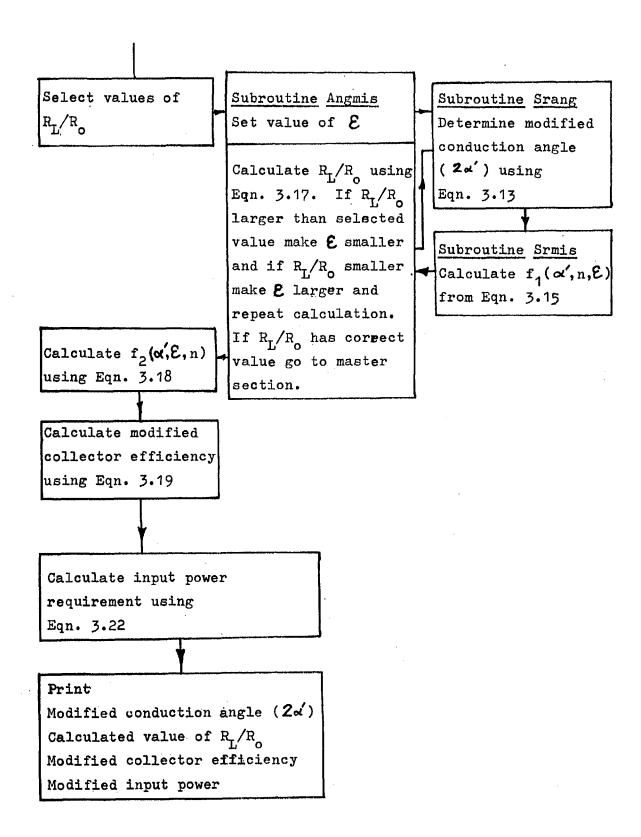

(3.4)