Li, Ke and Evans, Paul and Johnson, Christopher Mark (2016) Developing power semiconductor device model for virtual prototyping of power electronics systems. In: 13th IEEE Vehicle Power and Propulsion Conference (VPPC 2016), 17-20 Oct 2016, Hangzhou, China.

## Access from the University of Nottingham repository:

http://eprints.nottingham.ac.uk/38779/1/Developing%20Power%20Semiconductor %20Device%20Model%20for%20Virtual%20Prototyping%20of%20Power%20Electronics %20Systems.pdf

## Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

This article is made available under the University of Nottingham End User licence and may be reused according to the conditions of the licence. For more details see: http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf

## A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact eprints@nottingham.ac.uk

# Developing Power Semiconductor Device Model for Virtual Prototyping of Power Electronics Systems

Ke Li, Paul Evans, Mark Johnson Power Electronics, Machine and Control group University of Nottingham, UK Email: ke.li@nottingham.ac.uk, paul.evans@nottingham.ac.uk, mark.johnson@nottingham.ac.uk

Abstract—Virtual prototyping (VP) is very important for power electronics systems design. A virtual prototyping design tool based on different modelling technology and model order reduction is proposed in the paper. In order to combine circuit electromagnetic model with power semiconductor device models, a SiC-JFET behavioural model is presented and implemented in the design tool. A half bridge circuit using SiC-JFET devices is thus represented in the VP software. The presented SiC-JFET behavioural model is then validated by comparing with experimental measurements on switching waveforms.

*Keywords*—Virtual prototyping; Model order reduction; Power semiconductor device modelling; Behavioural model; Switching waveforms

#### I. INTRODUCTION

Power electronics systems are essential in the drivetrain of hybrid and electrical vehicles. Optimising the design of these systems is important in increasing performance, such as reducing overall drivetrain weight and size, improving efficiency so as to increase range, and ensuring a robust and reliable drivetrain [1].

Optimising system design through the construction and testing of physical prototypes can be time-consuming and expensive. Thus, virtual prototyping (VP) techniques offer one solution to eliminate the requirement for construction and testing of physical prototypes, which could reduce design time and costs so as to realize highly optimised system designs. A key requirement for VP is the ability to predict the performance of a design by using only simulation, which could help designers to obtain reliable results in a quick way.

Thermal design and electromagnetic compatibility design are very important for power electronics systems used in electrical vehicles, in which automotive drivetrain could reach more than 100kW power rating. At one side, even at system efficiencies greater than 95%, the large quantities of waste heat produced require an efficient thermal design. Thus, it is necessary that power devices (passive and active) losses and heat path from each heat source to the cooling equipment could be accurately and fast simulated in order to evaluate system thermal performance. At another side, the switching nature of the power semiconductor devices introduce high dI/dt and dV/dt which necessitates careful consideration in terms of electromagnetic performance. Thus, it is necessary that both electromagnetic interference (EMI) source and its propagation loop could be well represented, so power semiconductor device dI/dt, dV/dt transition and parasitic elements

shall be accurately and efficiently simulated. Moreover, the fast time-constants (nanoseconds) associated with the power semiconductor devices, slow time-constants (minutes) associated with thermal effects, and requirement for 3D modelling of the system design, mean that novel, efficient simulation techniques and design tools are required to avoid excessively long simulation times.

Developing a VP design tool which can predict the above performance could help designers to previously validate their prototype prior to experimental measurements. A VP design tool has been proposed by authors in [2], [3], where power electronics system thermal performance has been validated. However, accurate modelling of the power semiconductor device was found to be a limitation in the above papers. Thus, in this work, it will be presented that how efficient behavioural semiconductor models can be when they are combined with model order reduction techniques for 3D system simulation to allow rapid virtual prototyping of power electronic systems.

The paper is structured with following parts. At first, modelling techniques of the proposed VP design tool for power electronics systems will be reviewed. Then, power semiconductor device behavioural model will be presented. Afterwards, a half bridge circuit using SiC-JFET is represented by the VP design tool. Simulation results and experimental measurements of device switching current and voltage are compared, which is followed by the conclusion.

## II. MODELLING TECHNIQUES OF VIRTUAL PROTOTYPING DESIGN TOOL

#### A. Efficient Device Modelling

Different components within a power electronic system require different modelling techniques. Power semiconductor devices could be either physically modelled or behaviourally modelled. Physical model accounts for the internal structure and physical processes of the device. However, it is notoriously complex and can result in extremely slow simulation times [4]. By contrast, behavioural model represents electrical and thermal behaviour of the device, which is flexible and easy to implement in simulation tool. As power semiconductor device is usually fixed when designers use them in power electronics systems, developing their behavioural models is suitable in a VP design tool. Behavioural models could also be used to represent passive device and active device driver circuit. Components whose physical location will influence system performance such as bus-bars, PCBs and heatsinks, cannot use simplistic behavioural models. The 3D geometry of these components influences system performance and will be changed during the system optimisation process by designers, so a simulation model capable of capturing the effect of these changes must be used. Accelerating these physical, 3D simulations is essential to allow fast simulation times, which will be presented in the next part.

#### B. Efficient Modelling of the 3D Design Geometry

To fully evaluate the performance of a design, numerical methods must be used to translate design details such as geometry and construction materials into an equivalent mathematical model. One most used technique is spatial discretisation (meshing) which generates a large system of Ordinary Differential Equations (ODE) by dividing the design geometry into many small sections or elements over which a solution describing the effects of interest can be written. Thus, thousands of elements, resulting in a system of thousands of ODEs, can be necessary to obtain accurate results. In the software developed, the approach based on Finite-Difference Method (FDM) is used for thermal simulation and that based on Partial Element Equivalent Circuit method (PEEC) is used for electromagnetic simulation.

In order to increase simulation speed, Model Order Reduction (MOR) techniques to reduce the number of equations generated by the discretisation is applied in the VP design tool. The principle of MOR techniques is that if a discretisation produces n ODEs, which give rise to n eigenvalues spread over the model frequency response range, the solution can in fact be accurately represented using a much smaller number of m eigenvalues. Krylov subspace project algorithms are used to find a much smaller system of m ODEs which accurately capture the original dominant eigenvalues, where  $m \ll n$ . As expressed in eq. (1), the algorithm produces an  $m \times n$  matrix H and its transpose  $H^T$  with orthonormal rows which can be used to link original state vectors x to its reduced order vector  $x_r$ .

$$\begin{aligned} x_{\rm r} &= [H]x\\ x &= [H]^T x_{\rm r} \end{aligned} \tag{1}$$

Thus, a reduced order system with following new equations linking the input u of size a and output y of size b of the original system could be obtained by applying eq. (1).

$$[H]M[H]^T \dot{x}_{\rm r} = [H]A[H]^T x_{\rm r} + [H]Bu$$

$$y = C[H]^T x_{\rm r}$$

(2)

$$[M_{\rm r}]\dot{x}_{\rm r} = [A_{\rm r}]x_{\rm r} + [B_{\rm r}]u$$

$$y = [C_{\rm r}]x_{\rm r}$$

(3)

The reduced ordered matrices  $M_r$ ,  $A_r$ ,  $B_r$  and  $C_r$  are  $m \times m$ ,  $m \times m$ ,  $m \times a$  and  $b \times m$  matrices, of which the size is much

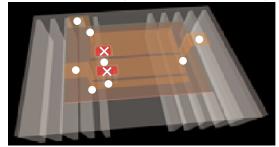

#### ★ Thermal boundary ● Electrical boundary

Fig. 1: Defined boundaries in geometrical model

Fig. 2: Equivalent circuit of a transistor

smaller than their original ones  $M(n \times n)$ ,  $A(n \times n)$ ,  $B(n \times a)$ and  $C(b \times n)$ . Thus, only m equations need to be solved at each time-step. No spatial information is lost, as variables such as the voltage, current, temperature and heat-flux values at any node in the original model can be calculated from the reduced order states using the  $H^T$  matrix (eq. (1)). Therefore full 3D graphical analysis, at any time-step, is still possible. The volume of data required to be stored and processed for long simulations is also significantly reduced.

The software applies an Arnoldi MOR algorithm [5] for thermal order reduction, and the related PRIMA [6] algorithm for electromagnetic order reduction. The accuracy of these techniques when applied to a typical power electronic simulation is shown in [3].

#### C. Coupled Physical and Behavioural Model Description

The 3D design geometry is defined in terms of building blocks such as 3D solids, along with a set of electrical and thermal boundaries. These basic building blocks can be grouped to form components such as power modules, substrate tiles, heat-sinks or bus-bars. The boundaries serve as points to which the behavioural models of the remainder of the system can be connected for design evaluation, which is shown in Fig. 1. Electrical boundary can be used to connect with other electrical part for electrical simulation while thermal boundary can be used to connect with other thermal part for thermal simulation.

As shown in [3], the proposed VP design tool is capable of both thermal and electromagnetic model generation. Electromagnetic model and its interaction with power semiconductor models will be focused in this paper. Thus, power semiconduc-

Fig. 3: SiC-JFET static characteristics comparison of different  $V_{\text{GS}}$  voltages

tor device behavioural model will be presented in the next section.

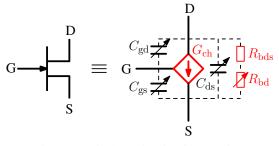

#### **III. POWER SEMICONDUCTOR DEVICES MODELLING**

A unipolar power transistor can be generally modelled with the equivalent circuit shown in Fig. 2, which is presented by authors in [7]–[9] to model SiC-JFET, SiC-MOSFET and GaN-HEMT. Current source  $G_{\rm ch}$  represent power transistor forward static characteristics, which is controlled by both  $V_{\rm DS}$  and  $V_{\rm GS}$  voltages. Body diode static characteristic is represented by a non-linear resistor  $R_{\rm bd}$  and a constant resistor  $R_{\rm bds}$ . The dynamic behaviour is modelled by three non-linear capacitors  $C_{\rm gd}$ ,  $C_{\rm ds}$  and  $C_{\rm gs}$  and each capacitor is only dependent on the voltage across it. Depending on device structure and packaging type, internal gate resistor and parasitic inductances could be added in this model.

#### A. Static characteristics modelling

A "Normally-on" SiC-JFET (IJW120R070T1, 1200V/35A,  $V_{\rm th} \approx -13.5$ V) is modelled in this subsection.

When  $V_{\rm GS} > V_{\rm th}$ , at one  $V_{\rm GS}$  voltage, the following equation can be used to represent the  $V_{\rm DS}$ - $I_{\rm D}$  curve. All the parameters a, b and c in the above equation could be obtained based on datasheet or the measured values through fitting method by using *fmincon* function in MATLAB.

$$I_{\rm D} = a - \frac{a}{1 + \left(\frac{V_{\rm DS}}{b}\right)^c} \tag{4}$$

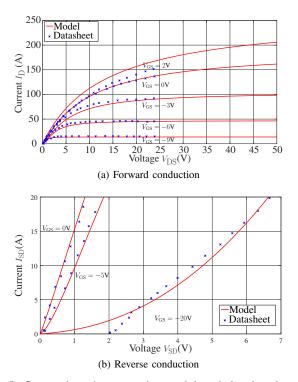

The comparison between the model and the datasheet is shown in Fig. 3 at different  $V_{GS}$  voltages. It is shown that the chosen simple function can represent well the device static

Fig. 4: Comparison between the function and the obtained parameters in eq.(4)

characteristics. The value of the parameters in eq.(4) can then be obtained on different  $V_{\rm GS}$  voltage values. Following equation eq.(5) could represent the evolution of each parameter (when  $V_{\rm GS} > V_{\rm th}$ ), where s indicates parameter a, b, c. The values of  $s_1$ - $s_4$  are given in TABLE. I.

$$s = \frac{s_1}{1 + \left(\frac{V_{\rm GS} - V_{\rm th}}{s_2}\right)^{s_3}} + s_4 \tag{5}$$

TABLE I:  $s_1$ - $s_4$  values in eq.(5) for each parameter (various units without physical meaning)

| s | $s_1$                 | $s_2$ | $s_3$ | $s_4$                |

|---|-----------------------|-------|-------|----------------------|

| a | $-1.05 \times 10^{4}$ | 71.46 | 2.4   | $1.05 \times 10^{4}$ |

| b | $-1.3 \times 10^{4}$  | 321.3 | 2.27  | $1.3 \times 10^{4}$  |

| c | 6.13                  | 1.98  | 0.8   | 0                    |

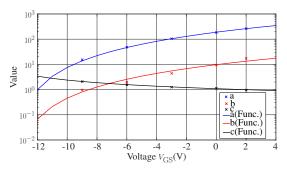

The comparison between eq.(5) and the obtained parameters in eq.(4) is shown in Fig. 4. The value of each parameter out of the datasheet range is obtained by extrapolation of the eq.(5). When device is reverse conducted, conduction current  $I_{\rm SD}$  could be represented by the sum of the device channel current  $I_{\rm ch}$  and body diode current  $I_{\rm bd}$ , where non-linear resistor  $R_{\rm bd}$  could be represented by the following equation, in which  $V_{\rm bd}$  is the voltage across  $R_{\rm bd}$ . Parameters  $a_{\rm bd} = 2.66\Omega$ ,  $b_{\rm bd} = 1.38V$ ,  $c_{\rm bd} = 1.244$  and  $R_{\rm bds} = 0.001\Omega$  are used to model body diode static characteristic. Thus, the comparison between the datasheet and the model is shown in Fig. 5, where it is shown that the model represents well the device static characteristics. However, the difference between the model and the datasheet relies mainly on the difference between the chosen function and the parameters in Fig. 4.

$$R_{\rm bd} = \frac{a_{\rm bd}}{1 + \left(\frac{V_{\rm bd}}{b_{\rm bd}}\right)^{c_{\rm bd}}} \tag{6}$$

#### B. Dynamic characteristics modelling

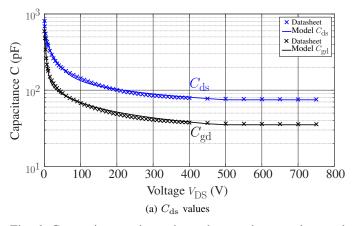

The nonlinearity of both  $C_{\rm gd}$  and  $C_{\rm ds}$  are expressed by following mathematical function when  $V_{\rm x}$  is inferior to 500V:

$$C_{\rm x} = \frac{a}{1 + \left(\frac{V_{\rm x}}{b}\right)^c} + d \times \exp\left(-e \times V_{\rm x}\right) \tag{7}$$

Fig. 5: Comparison between the model and the datasheet on SiC-JFET static characteristics

where  $C_x$  is the capacitance value and  $V_x$  is the voltage across the capacitor. In the range where  $V_x$  is superior to 500V,  $C_x$ is expressed by a constant capacitance value.

Fig. 6: Comparison on inter-electrode capacitance values and their models

The comparison between inter-electrode capacitances datasheet values and their values are shown in Fig. 6, which shows that both  $C_{\rm gd}$  and  $C_{\rm ds}$  are expressed well by the chosen functions. For  $C_{\rm gd}$  capacitance, the used parameters are  $a = 2.5 \times 10^4 (p{\rm F}), b = 3.58 \times 10^{-4} ({\rm V}), c = 0.464, d = 2 \times 10^4 (p{\rm F}), e = 0.22 ({\rm V}^{-1})$  and for  $C_{\rm ds}$  capacitance, the used parameters are  $a = 647 (p{\rm F}), b = 3 ({\rm V}), c = 0.398, d = 210.4 (p{\rm F}), e = 0.038 ({\rm V}^{-1}).$

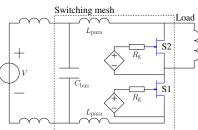

(a) JFET half bridge electrical circuit

(b) JFET half bridge switching circuit

(c) JFET half bridge switching circuit representation

Fig. 7: JFET half bridge circuit and its representation

$C_{\rm gs}$  is assumed to be a constant capacitor and its value is the same as given in datasheet: 1.6nF.

The presented SiC-JFET model will then be implemented in the presented VP design tool. Device switching waveforms of the simulation will be compared with experimental measurements.

#### IV. EXPERIMENTAL VALIDATION

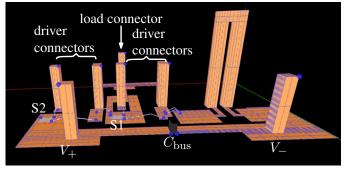

#### A. SiC-JFET half bridge circuit representation

The SiC-JFET half bridge electrical circuit is shown in Fig. 7a, which is mainly constructed by a bus capacitor  $C_{\text{bus}}$ , two SiC-JFETs S1 and S2, driver circuit of each device and an air-core inductor as the load.

The switching mesh of the circuit is shown in Fig. 7b, where parasitic inductances could be found not only in the switching current loop, but also in the driver circuit.

The switching circuit is then represented in the VP design tool, in which the PCB track of the switching mesh is represented with their geometric information. The power supply,  $C_{\text{bus}}$ , SiC-JFETs S1 and S2, device driver circuits and load are represented by their corresponding behavioural models in the simulation circuit through electrical boundaries, which are shown as blue points in Fig. 7c, where switching loop parasitic inductance  $L_{\text{para}}$  values are determined by the 3D meshed model.

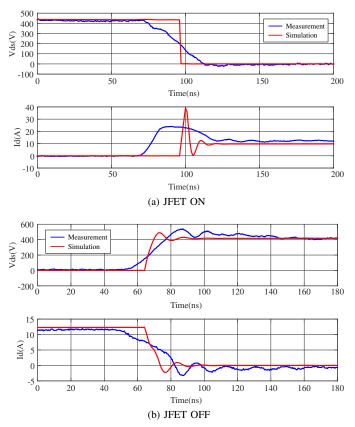

SiC-JFET S1 switching current  $I_D$  and switching voltage  $V_{DS}$  are compared between the measurement and simulation, of which the results are presented in the following subsection.

#### B. Comparison results

Current  $I_{\rm D}$  and voltage  $V_{\rm DS}$  are compared in the three conditions below. In condition 1, simple SiC-JFET device model (ideal switch with a parallel RC branch) as that presented in [3] is used and parasitic inductance values are extracted by the software. In condition 2, the presented SiC-JFET model is used, however there is no parasitic inductance values extracted. In condition 3, the presented SiC-JFET model is used while parasitic inductance values are extracted and used in the simulation.

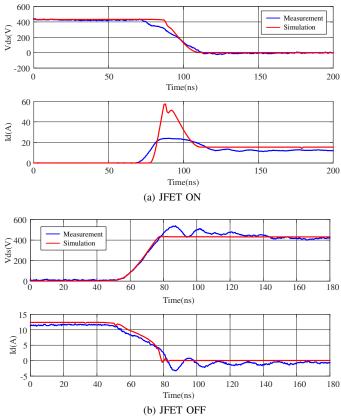

1) Condition 1: The comparison between the measurement and the simulation in this condition is shown in Fig. 8. The simple device model could not represent good  $I_{\rm D}$  and  $V_{\rm DS}$ switching transitions, because the capacitance value in the model is constant and there is no capacitive coupling (Miller effect) between drain and gate of the device. The obtained switching energies of the simulation are:  $E_{\rm on} = 0.5 \mu J$  and  $E_{\rm off} = 11 \mu J$ , which is far from those of the measurement:  $E_{\rm on} = 165 \mu J$  and  $E_{\rm off} = 25 \mu J$ . Thus, the ideal model yields an inaccurate switching loss as the measurement.

Fig. 8: JFET switching waveforms comparison of condition 1

2) Condition 2: The comparison between the measurement and the simulation in this condition is shown in Fig. 9. As parasitic inductances in the circuit are not extracted, LCresonance at the end of the turn-ON and turn-OFF switching are not represented in the simulation. Meanwhile, device turn-ON dI/dt transition is much faster than measurement, which yields a bigger turn-ON  $I_{\rm D}$  peak current. The obtained switching energies of the simulation are:  $E_{\rm on} = 218 \mu \text{J}$  and  $E_{\rm off} = 34 \mu \text{J}$ , which is close than ideal model but still different from the measurement.

Fig. 9: JFET switching waveforms comparison of condition 2

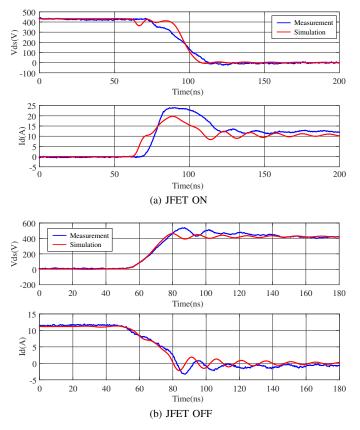

3) Condition 3: The comparison between the measurement and the simulation in this condition is shown in Fig. 10, where it shows that device switching waveforms are closer to the measurement by adding parasitic inductances and the presented device behavioural model. The simulation represents generally well the measurement on both current, voltage transition and LC resonance at the end of the switching. LCresonance frequency is accurately represented, which demonstrates that device output capacitance value  $C_{oss}$  and switching loop parasitic inductances are well simulated. Device turn-OFF dI/dt and dV/dt are represented well by the simulation. The main difference between the measurement and the simulation is the turn-ON switching transition, which is mainly due to the inaccurate representation of the stored charge in the simulation when upper device S2 is reverse conducted. Future work will be focused on how to correctly represent this parameter in the model. The obtained switching energies of the simulation are:  $E_{\rm on} = 148 \mu {\rm J}$  and  $E_{\rm off} = 28 \mu {\rm J},$  which are closer to the measurement than above two conditions.

Simulation time to obtain the above results is within 1 minute, which includes the generation of inductance equations from 3D model, MOR and simulation time of  $71\mu$ s with 1*n*s time step. The MOR method helps to reduce the original 723

equation model to 23 equation model in order to accelerate simulation speed. The presented device model could be also used in circuit simulation software such as PSPICE. However, as parasitic inductances could influence on device switching waveforms, their values including mutual inductances of the switching mesh are necessary to be extracted and added in simulation circuit, which might consume lots of time.

Fig. 10: JFET switching waveforms comparison of condition 3

#### V. CONCLUSION

A virtual prototyping (VP) design tool using power semiconductor device behavioural models is presented in the paper. Different modelling techniques are used to model different components in the design tool and by using model order reduction algorithms, simulation speed could be increased.

A behavioural model of a SiC-JFET is then presented, in which device static and dynamic characteristics are represented by mathematical functions. The model is then implemented in the VP design tool, where a SiC-JFET based half bridge circuit is represented. By comparing with the simulation of a simple device model and the simulation without parasitic inductances extraction, it is shown that circuit electromagnetic model together with power semiconductor device behavioural model could represent well device switching waveforms, so device switching losses can be accurately calculated. Future work will include thermal model based on the presented results, so as to evaluate device electrical thermal performance.

### ACKNOWLEDGMENT

The authors would like to thank UK Engineering and Physical Sciences Research Council (EPSRC) power electronics center for the financial support and all the partners of the project Multidomain Optimization and Virtual Prototyping for High-Density Power Electronics Systems for technical discussions.

#### REFERENCES

- A. Emadi, S. S. Williamson, and A. Khaligh, "Power electronics intensive solutions for advanced electric, hybrid electric, and fuel cell vehicular power systems," *IEEE Transactions on Power Electronics*, vol. 21, pp. 567–577, May 2006.

- [2] P. Evans, A. Castellazzi, and C. Johnson, "A multi-disciplinary virtual prototyping design tool for power electronics," in *Integrated Power Systems (CIPS), 2014 8th International Conference on*, pp. 1–7, Feb 2014.

- [3] P. Evans, A. Castellazzi, and C. Johnson, "Design tools for rapid multidomain virtual prototyping of power electronic systems," *Power Electronics*, *IEEE Transactions on*, vol. 31, pp. 2443–2455, March 2016.

- [4] H. Wu, R. Dougal, and C. Jin, "Modeling power diode by combining the behavioral and the physical model," in 31st Annual Conference of IEEE Industrial Electronics Society, 2005. IECON 2005., pp. 6 pp.-, Nov 2005.

- [5] T. Bechtold, E. B. Rudnyi, and J. G. Korvink, *Fast Simulation of Electro-Thermal MEMs*. Freiburg: Springer, 2006.

- [6] A. Odabasioglu, M. Celik, and L. T. Pileggi, "Prima: passive reducedorder interconnect macromodeling algorithm," in *Computer-Aided De*sign, 1997. Digest of Technical Papers., 1997 IEEE/ACM International Conference on, pp. 58–65, Nov 1997.

- [7] T. Funaki, A. Kashyap, H. Mantooth, J. Balda, F. Barlow, T. Kimoto, and T. Hikihara, "Characterization of SiC JFET for Temperature Dependent Device Modeling," in *Power Electronics Specialists Conference*, 2006. *PESC '06. 37th IEEE*, pp. 1–6, june 2006.

- [8] K. Sun, H. Wu, J. Lu, Y. Xing, and L. Huang, "Improved Modeling of Medium Voltage SiC MOSFET Within Wide Temperature Range," *Power Electronics, IEEE Transactions on*, vol. 29, no. 5, pp. 2229–2237, 2014.

- [9] X. Huang, Q. Li, Z. Liu, and F. Lee, "Analytical Loss Model of High Voltage GaN HEMT in Cascode Configuration," *Power Electronics, IEEE Transactions on*, vol. 29, no. 5, pp. 2208–2219, 2014.