# Investigation of Variation in Organic Thin-film Transistors (OTFT) and Design of Variation-aware Organic Circuits

Untersuchung von Parameterschwankungen in organischen Dünnfilmtransitoren und der Entwurf von schwankungstoleranten Schaltungen Zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.) genehmigte Dissertation von M.Sc. Ramkumar Ganesan aus Surulipatty, Indien April 2016 – Darmstadt – D 17

Fachbereich 18 Eletrotechnik und Informationstechnik Institut für Datentechnik Forschungsgruppe Mikroelektronische Systeme Investigation of Variation in Organic Thin-film Transistors (OTFT) and Design of Variationaware Organic Circuits Untersuchung von Parameterschwankungen in organischen Dünnfilmtransitoren und der Entwurf von schwankungstoleranten Schaltungen

Genehmigte Dissertation von M.Sc. Ramkumar Ganesan aus Surulipatty, Indien

1. Gutachten: Prof. Dr. Dr. h.c. mult. Manfred Glesner

- 2. Gutachten: Prof. Dr.-Ing. Herbert De Gersem

- 3. Gutachten: Prof. Dr.-Ing. Thomas Hollstein

Tag der Einreichung: 28.10.2014 Tag der Prüfung: 29.04.2015

Darmstadt – D 17

Bitte zitieren Sie dieses Dokument als: URN: urn:nbn:de:tuda-tuprints-49930 URL: http://tuprints.ulb.tu-darmstadt.de/4993

Dieses Dokument wird bereitgestellt von tuprints, E-Publishing-Service der TU Darmstadt http://tuprints.ulb.tu-darmstadt.de tuprints@ulb.tu-darmstadt.de

Die Veröffentlichung steht unter folgender Creative Commons Lizenz: Namensnennung – Keine kommerzielle Nutzung – Keine Bearbeitung 3.0 Deutschland http://creativecommons.org/licenses/by-nc-nd/3.0/de/

# **Erklärung zur Dissertation**

Hiermit versichere ich, die vorliegende Dissertation ohne Hilfe Dritter nur mit den angegebenen Quellen und Hilfsmitteln angefertigt zu haben. Alle Stellen, die aus Quellen entnommen wurden, sind als solche kenntlich gemacht. Diese Arbeit hat in gleicher oder ähnlicher Form noch keiner Prüfungsbehörde vorgelegen.

Darmstadt, den April 4, 2016

(Ramkumar Ganesan)

III

I dedicate this to my caring wife and our baby girl Shanvitta. I also dedicate this work to my mom, dad and my brother.

"Live as if you were to die tomorrow. Learn as if you were to live forever."

- Mahatma Gandhi

## Acknowledgments

First of all, I would like to express my heartfelt thanks to Professor Manfred Glesner for being my PhD advisor. Since the day when I first met him, he has been always supportive and helped me to have a big picture in my research. The past 4 years were a crucial period in my life that shaped my personality. His advices have been and still guide me in my scientific and professional path. I would also like to thank my project mate Dr.Ing. Sebastian Pankalla for the fruitful discussions we have had that helped me better my understanding of the semiconductor physics and modelling of organic devices. I am also grateful to Professor Edgar Doersam from the Institute of Printing Science and Technology (IDD) at TU Darmstadt for coordinating the PolyTOS project. I also thank Dr.Ing. Dieter Spiehl, Dr.Ing. Hans Martin Sauer, Simone Ganz and other colleagues from IDD institute for helping me understand the various aspects involved in the printing process.

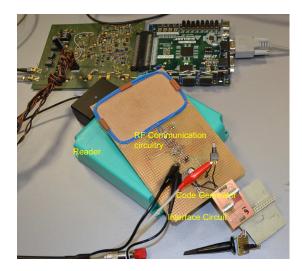

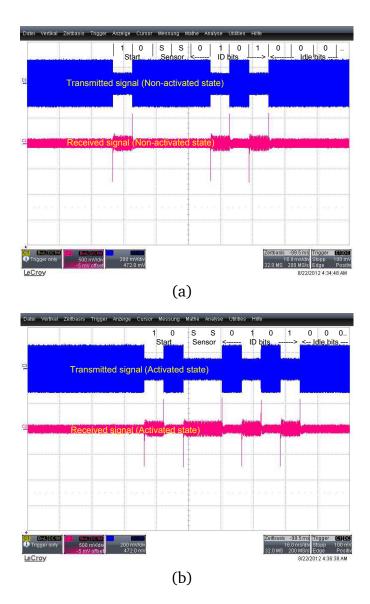

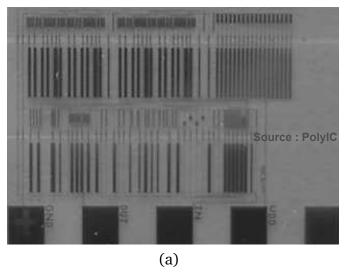

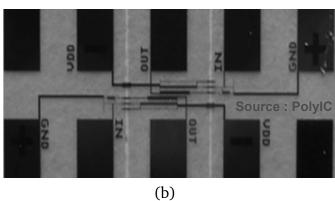

I would also like to express my sincere thanks to Dr.Ing. Juergen Krumm and Klaus Ludwig from PolyIC GmbH for their support with the fabrication of organic circuits. I also thank Dr.Ing. Oliver Hoerer and Erwin Schmidt from Pepperl+Fuchs GmbH, for providing the silicon based RFID test environment containing a front-end circuit and its reader. I would also like to thank all my friends and colleagues at TU Darmstadt. The list would be too long to fit here. But I want to thank Dr.Ing. Christopher Spies, Dr.Ing. Surapong, Dr.Ing. Ashok Jaiswal, Dr.Ing. Yuan Fang, Dr.Ing. Francois Philipp, Rakash Sivasiva Ganesan and Dr.Ing. Harish Balasubramaniam in particular. They generously provided me suggestions and gratitudes when I encountered challenges during the course of my research.

Finally, I would like to thank my wife, Swathi, for her patience and support throughout this work. She was always there to support me through all my ups and downs and often helped in taking away the stress involved in my research. I am also deeply grateful to my parents in India whose encouraging words kept me motivated. Their sacrifices have made me what I am today.

## Abstract

This work investigates the key sources of variability in Organic Thin-film Transistor (OTFT) namely process variations and bias-stress induced variation, and presents circuit design techniques to build robust variation-aware digital and analog circuits using OTFTs. OTFTs suffer from a relatively large  $V_T$  variation due to the bias stress effects, and process mismatch variations. Though these effects are also prevalent in silicon based transistors, their magnitude is comparatively larger in the case of OTFTs. This renders the well-established silicon based circuits unsuitable for organic electronics. Therefore, direct adaptation of the silicon based circuits for realising organic circuits does not effectively handle the relatively large parameter and mismatch variations associated with OTFTs. In this work, we first investigate the bias-stress induced threshold voltage  $(V_T)$  variation and process variations to understand the impact of these variations on the performance of organic circuits. Then, two different strategies were employed to design robust organic circuits. The first method involves designing new load topologies that are more robust to the threshold voltage variations without compromising on gain. The other strategy was to realize the essential analog circuit functionalities like comparator, Analog to Digital Converter (ADC) using digital circuit blocks. In this direction, a digital comparator and digital A/D converter circuits were developed. Finally to demonstrate the system integration, a temperature sensing organic smart label system was designed.

### Kurzfassung

Diese Dissertation untersucht die Hauptursachen von Parameterabweichungen in organischen Dünnschichttransistoren (engl.: Organic Thin-film Transistor, OTFT), wie Prozessvariationen und durch Vorspannungsbelastung verursachte Variationen. Weiterhin werden Entwurfstechniken für digitale und analoge Schaltungen mit OTFTs unter Berücksichtigung dieser Variabilitäten präsentiert. Aufgrund von Vorspannungsbelastungen und Prozessvariationen leiden OTFTs viel stärker unter Variationen der Schwellspannung VT als Siliziumtransistoren. Dies führt dazu, dass gängige Schaltungstechniken für Siliziumtransistoren nicht direkt auf organische Elektronik anwendbar sind, da diese für solch grosse Variationen nicht ausgelegt sind.

In dieser Arbeit werden die Einflüsse der oben genannten Variationen der Schwellspannung auf die Leistungsfähigkeit organischer Schaltungen untersucht. Anschliessend werden zwei Entwurfsmethoden für robuste organische Schaltungen vorgestellt. Die erste Methode berücksichtigt den Entwurf von optimalen Lasttopologien, durch welche die Auswirkung der Schwellspannungsvariation auf die Verstärkung der Schaltung minimiert wird. Der zweite Ansatz ist die Realisierung von essentiellen analogen Blöcken, wie Komparatoren oder Analog-zu-Digital Wandlern (engl.: Analog-to-Digital Converter, ADC), durch digitale Blöcke. Ein digitaler Komparator sowie ein digitaler ADC wurden entwickelt. Schliesslich wurde ein sogenanntes Smart Label mit Temperatursensor auf Basis organischer Elektronik entworfen, um die Systemintegration zu demonstrieren.

### Contents

| Af  | ffidav                   | it                                                                                                                                                                                                                                                               | I                                             |

|-----|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Ad  | cknov                    | vledgments                                                                                                                                                                                                                                                       | v                                             |

| Ał  | bstrad                   | t N                                                                                                                                                                                                                                                              | /11                                           |

| Κι  | urzfas                   | sung                                                                                                                                                                                                                                                             | IX                                            |

| Та  | able o                   | f Contents                                                                                                                                                                                                                                                       | XI                                            |

| Lis | st of S                  | Symbols >                                                                                                                                                                                                                                                        | ٨V                                            |

| Li  | st of /                  | Acronyms XV                                                                                                                                                                                                                                                      | /11                                           |

| Lis | st of I                  | Figures X                                                                                                                                                                                                                                                        | IX                                            |

| Li  | st of 1                  | Tables XX                                                                                                                                                                                                                                                        | ٢V                                            |

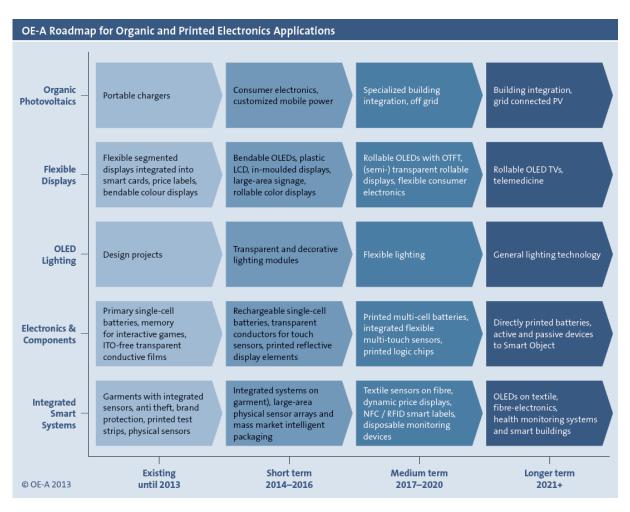

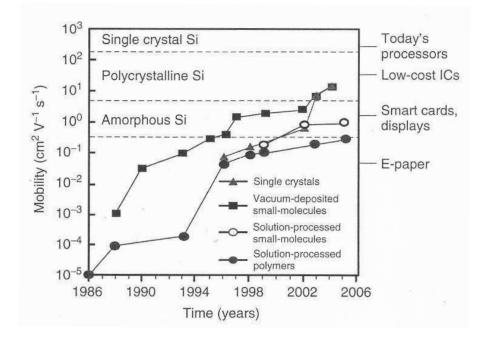

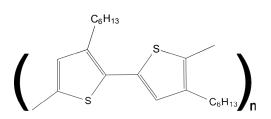

| 1   | 1.1<br>1.2               | OductionMotivation1.1.1Potential Applications of Organic ElectronicsReview of Progress in Organic CircuitsResearch ObjectivesOrganization of this Dissertation                                                                                                   | <b>1</b><br>3<br>5<br>5                       |

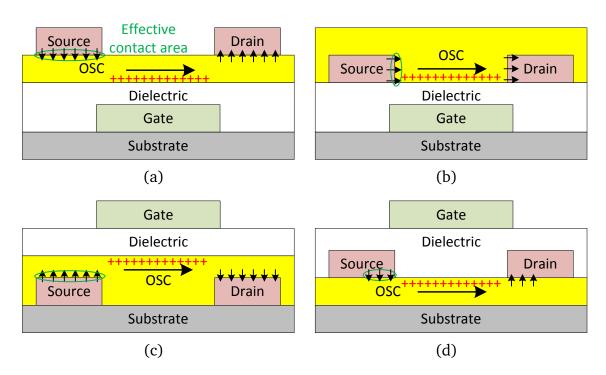

| 2   | Org<br>2.1<br>2.2<br>2.3 | 2.1.1Review of Organic Semiconducting Materials2.1.2Poly(3-hexylthiophene) (P3HT)Charge Transport Models2.2.1Band Transport Model2.2.2Multiple Trapping and Release Model2.2.3Variable Range Hopping ModelOTFT Architecture and Fabrication2.3.1Device Structure | 7<br>7<br>8<br>9<br>9<br>10<br>10<br>10<br>11 |

|     | 2.4                      | OTFT Operation                                                                                                                                                                                                                                                   | 12<br>13<br>14                                |

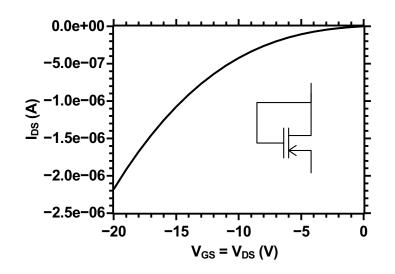

|     | 2.5                      | Electrical Characteristics of OTFTs                                                                                                                                                                                                                              | 14                                            |

|   | 2.6                                                                                                                                 | Modelling of OTFTs for Circuit Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17                                                                                                              |

|---|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|   | 2.7                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20                                                                                                              |

|   | 2.8                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20                                                                                                              |

|   |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                 |

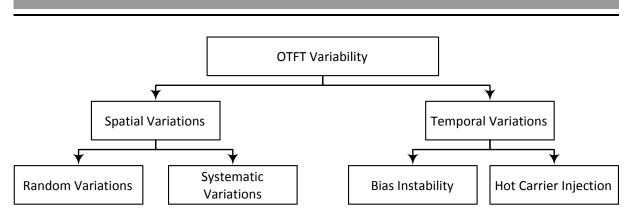

| 3 | Vari                                                                                                                                | ability in OTFTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21                                                                                                              |

|   | 3.1                                                                                                                                 | Sources of Variability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21                                                                                                              |

|   |                                                                                                                                     | 3.1.1 Spatial Variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22                                                                                                              |

|   |                                                                                                                                     | 3.1.2 Temporal Variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23                                                                                                              |

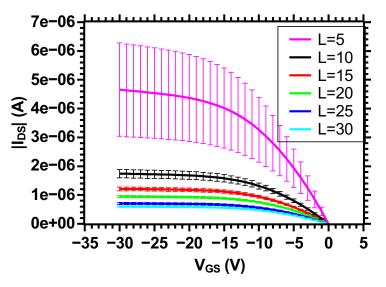

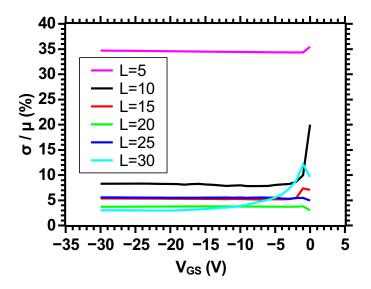

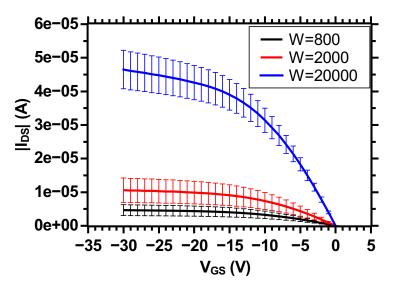

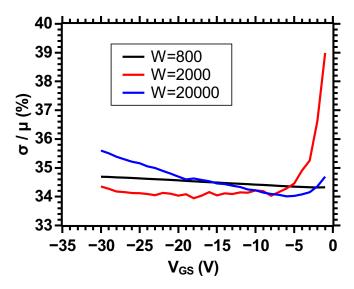

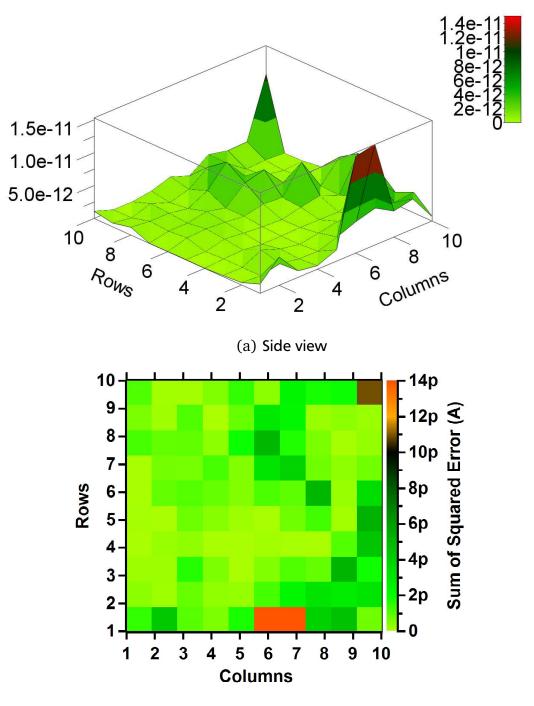

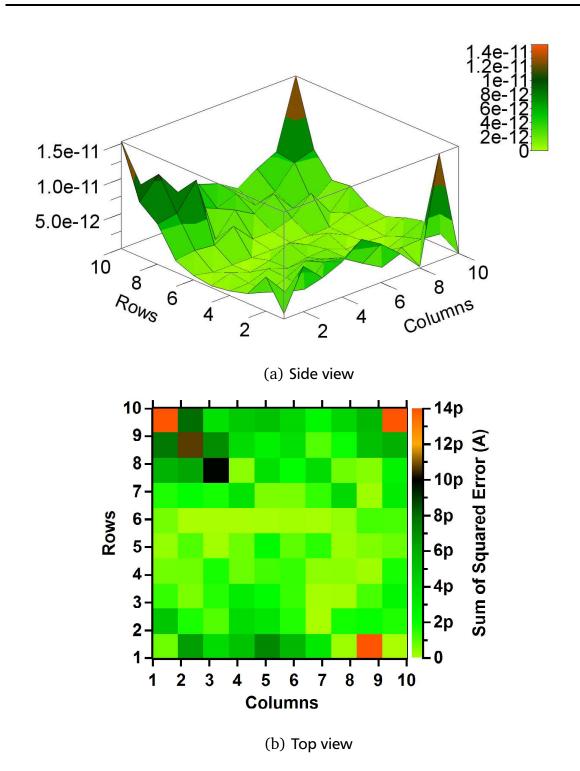

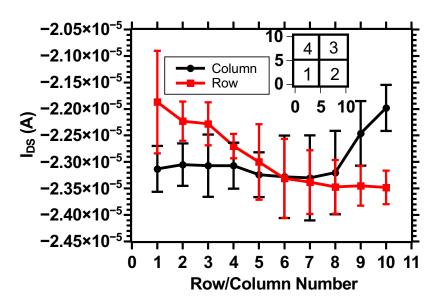

|   | 3.2                                                                                                                                 | Spatial Variability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23                                                                                                              |

|   |                                                                                                                                     | 3.2.1 Characterization of Process Variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26                                                                                                              |

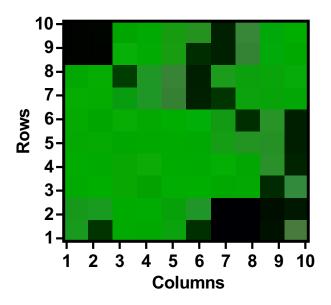

|   |                                                                                                                                     | 3.2.1.1 Intra-Substrate Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26                                                                                                              |

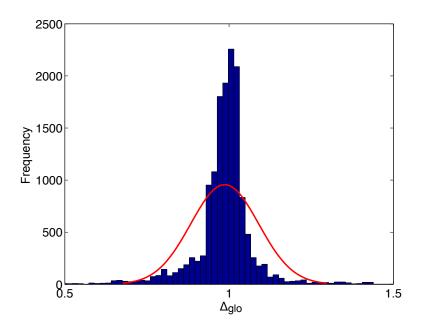

|   |                                                                                                                                     | 3.2.1.2 Inter-Substrate Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27                                                                                                              |

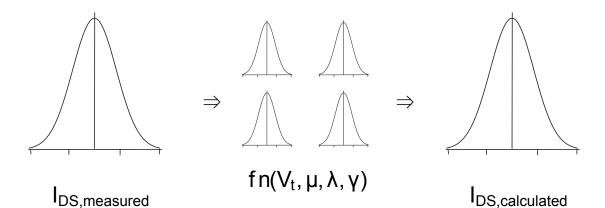

|   |                                                                                                                                     | 3.2.2 Statistical Model for Process Variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29                                                                                                              |

|   |                                                                                                                                     | 3.2.2.1 Generalized Statistical Model for OTFT Process Variabil-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |

|   |                                                                                                                                     | ity Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30                                                                                                              |

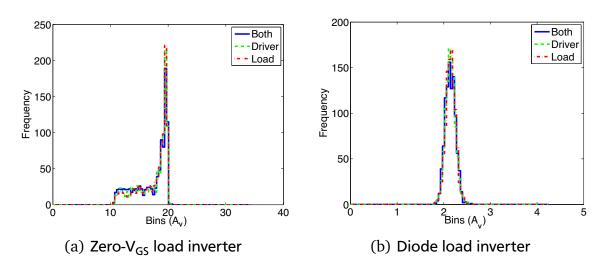

|   | 3.3                                                                                                                                 | Impact of Process Variations on Organic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33                                                                                                              |

|   | 3.4                                                                                                                                 | Temporal Variability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                                                                                                              |

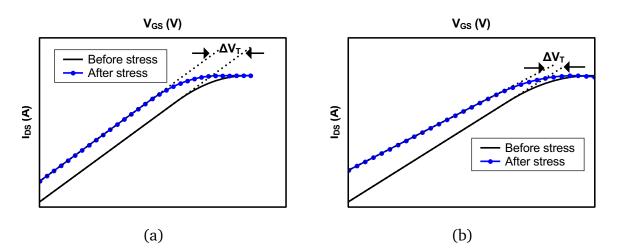

|   |                                                                                                                                     | 3.4.1 Charge Trapping in OTFTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35                                                                                                              |

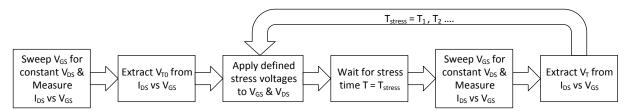

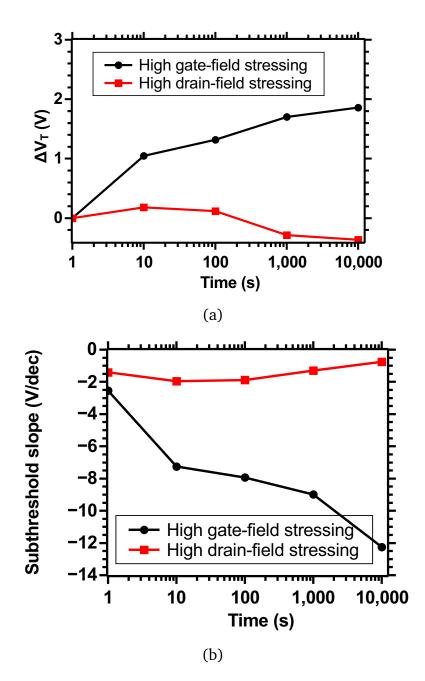

|   |                                                                                                                                     | 3.4.2 Characterization of Bias-Stress Instability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37                                                                                                              |

|   |                                                                                                                                     | 3.4.2.1 Measurement Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37                                                                                                              |

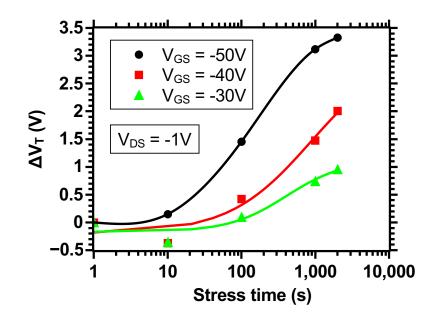

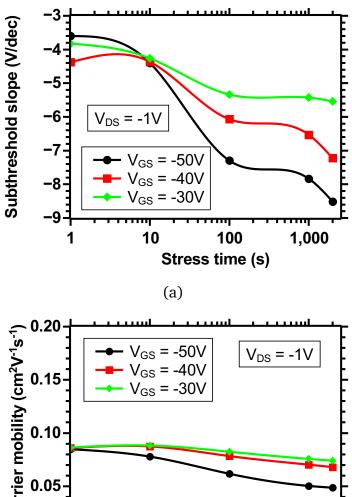

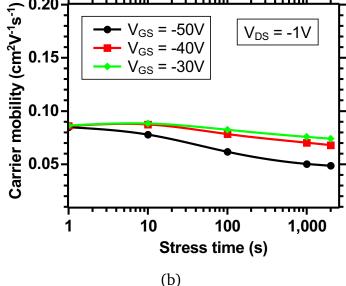

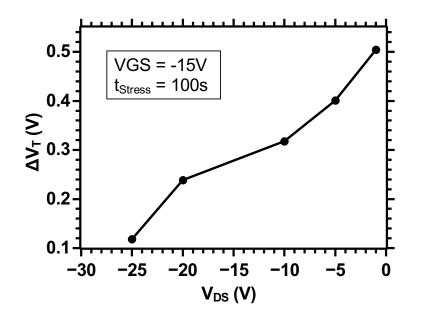

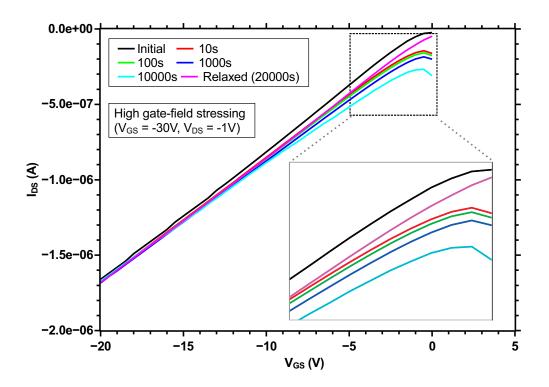

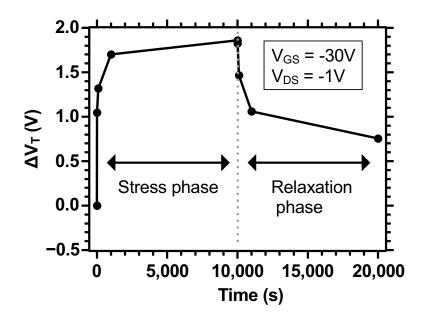

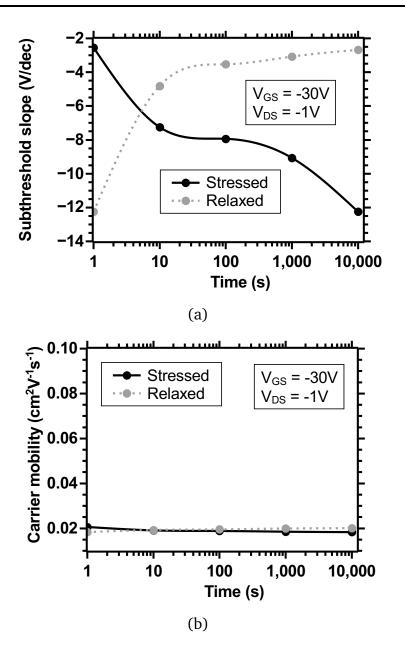

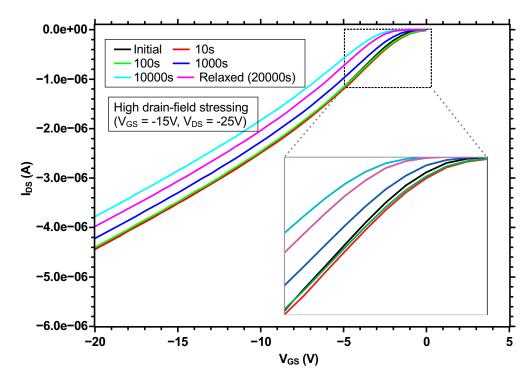

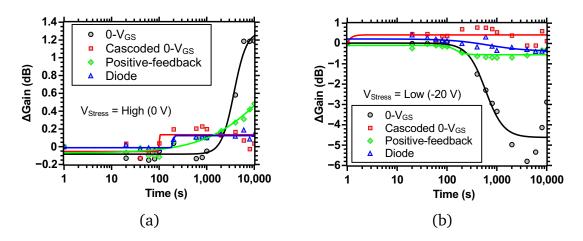

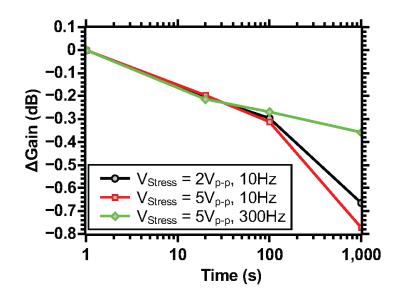

|   |                                                                                                                                     | 3.4.2.2 Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37                                                                                                              |

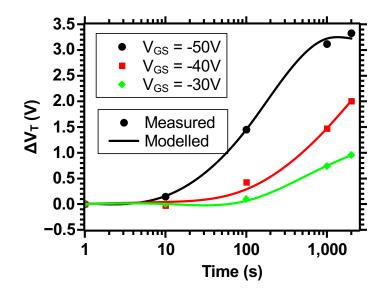

|   |                                                                                                                                     | 3.4.3 Modelling Bias-Stress Instability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43                                                                                                              |

|   | 3.5                                                                                                                                 | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44                                                                                                              |

|   |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                 |

|   |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                 |

| 4 | Star                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49                                                                                                              |

| 4 | 4.1                                                                                                                                 | Design Considerations for Organic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49                                                                                                              |

| 4 |                                                                                                                                     | Design Considerations for Organic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49<br>50                                                                                                        |

| 4 | 4.1                                                                                                                                 | Design Considerations for Organic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49<br>50<br>50                                                                                                  |

| 4 | 4.1<br>4.2                                                                                                                          | Design Considerations for Organic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49<br>50<br>50                                                                                                  |

| 4 | 4.1<br>4.2                                                                                                                          | Design Considerations for Organic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49<br>50<br>50                                                                                                  |

| 4 | 4.1<br>4.2                                                                                                                          | Design Considerations for Organic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49<br>50<br>50<br>51<br>52                                                                                      |

| 4 | 4.1<br>4.2                                                                                                                          | Design Considerations for Organic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49<br>50<br>50<br>51<br>52                                                                                      |

| 4 | 4.1<br>4.2                                                                                                                          | Design Considerations for Organic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49<br>50<br>50<br>51<br>52<br>53                                                                                |

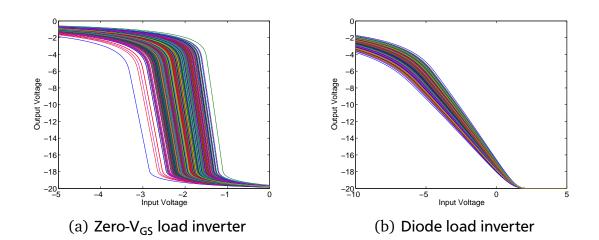

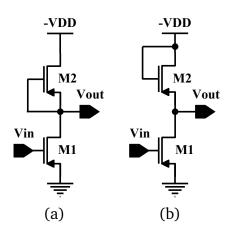

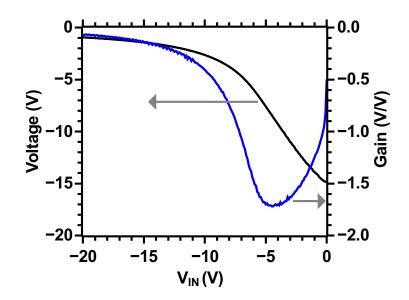

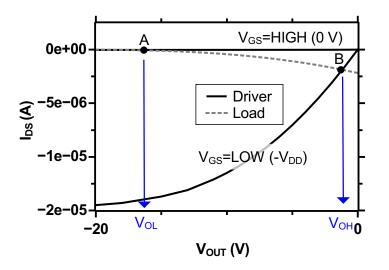

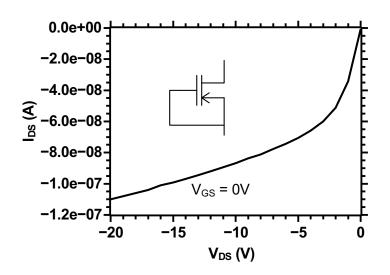

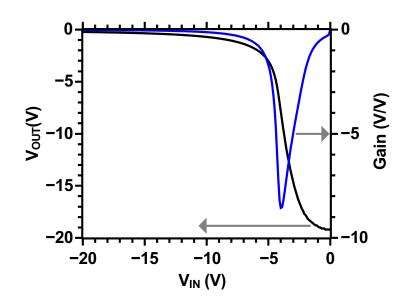

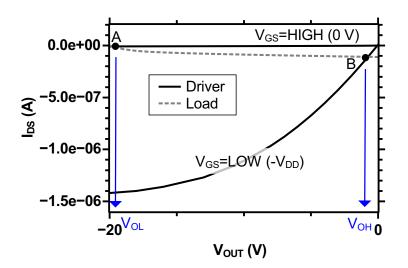

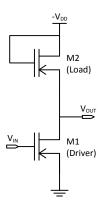

| 4 | 4.1<br>4.2                                                                                                                          | Design Considerations for Organic CircuitsStandard Cell ConfigurationMono-type Static Inverter4.3.1Diode Inverter4.3.1.1DC Transfer Characteristics4.3.2Qutput Signal Levels4.3.2.1DC Transfer Characteristics                                                                                                                                                                                                                                                                                                                                                                                | 49<br>50<br>50<br>51<br>52<br>53<br>56                                                                          |

| 4 | 4.1<br>4.2                                                                                                                          | Design Considerations for Organic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49<br>50<br>51<br>52<br>53<br>56<br>57                                                                          |

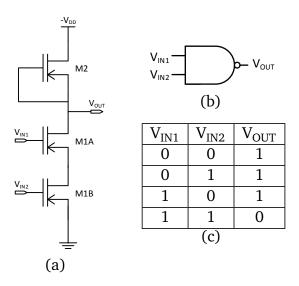

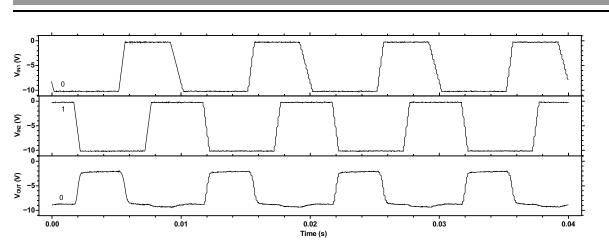

| 4 | 4.1<br>4.2<br>4.3                                                                                                                   | Design Considerations for Organic CircuitsStandard Cell ConfigurationMono-type Static Inverter4.3.1Diode Inverter4.3.1.1DC Transfer Characteristics4.3.1.2Output Signal Levels4.3.2.1DC Transfer Characteristics4.3.2.1DC Transfer Characteristics4.3.2.2Output Signal LevelsA.3.2.2Output Signal LevelsA.3.2.3NAND                                                                                                                                                                                                                                                                           | 49<br>50<br>51<br>52<br>53<br>56<br>57<br>58                                                                    |

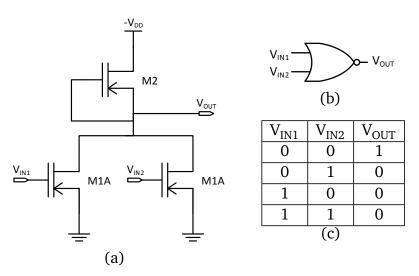

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                                                           | Design Considerations for Organic CircuitsStandard Cell ConfigurationMono-type Static Inverter4.3.1Diode Inverter4.3.1.1DC Transfer Characteristics4.3.1.2Output Signal Levels4.3.2Zero- $V_{GS}$ Inverter4.3.2.1DC Transfer Characteristics4.3.2.2Output Signal LevelsNANDNOR                                                                                                                                                                                                                                                                                                                | 49<br>50<br>50<br>51<br>52<br>53<br>56<br>57<br>58<br>60                                                        |

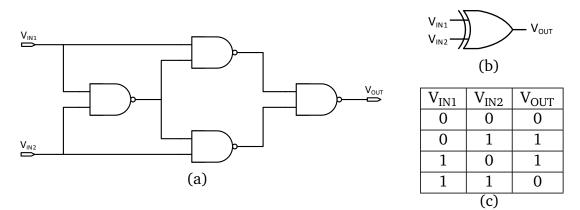

| 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>                                                         | Design Considerations for Organic CircuitsStandard Cell ConfigurationMono-type Static Inverter4.3.1Diode Inverter4.3.1.1DC Transfer Characteristics4.3.1.2Output Signal Levels4.3.2.1DC Transfer Characteristics4.3.2.2Output Signal LevelsNANDNORXOR                                                                                                                                                                                                                                                                                                                                         | 49<br>50<br>51<br>52<br>53<br>56<br>57<br>58<br>60<br>61                                                        |

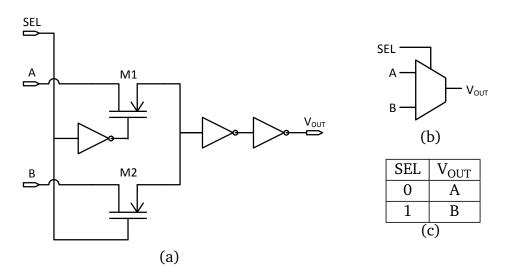

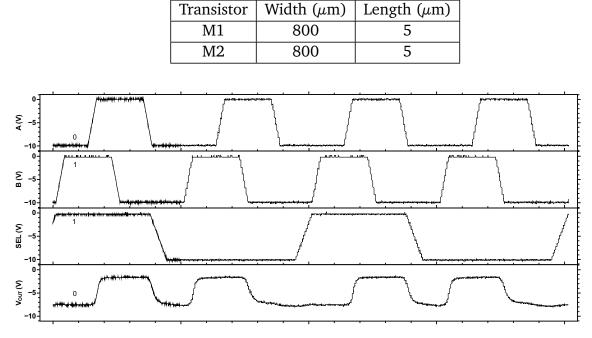

| 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>                                            | Design Considerations for Organic CircuitsStandard Cell ConfigurationMono-type Static Inverter4.3.1Diode Inverter4.3.1.1DC Transfer Characteristics4.3.2Output Signal Levels4.3.2.1DC Transfer Characteristics4.3.2.2Output Signal LevelsNANDNORXORMUX                                                                                                                                                                                                                                                                                                                                        | 49<br>50<br>50<br>51<br>52<br>53<br>56<br>57<br>58<br>60<br>61<br>62                                            |

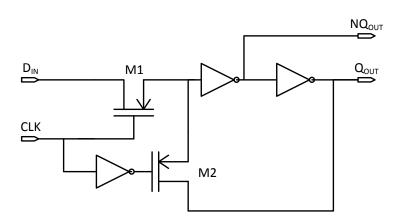

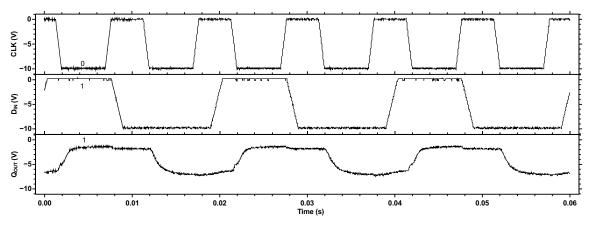

| 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ul>                               | Design Considerations for Organic CircuitsStandard Cell ConfigurationMono-type Static Inverter4.3.1Diode Inverter4.3.1.1DC Transfer Characteristics4.3.1.2Output Signal Levels4.3.2Zero- $V_{GS}$ Inverter4.3.2.2Output Signal LevelsA.3.2.2Output Signal LevelsNANDNORMUXD-Latch                                                                                                                                                                                                                                                                                                             | 49<br>50<br>50<br>51<br>52<br>53<br>56<br>57<br>58<br>60<br>61<br>62<br>63                                      |

| 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ul>     | Design Considerations for Organic CircuitsStandard Cell ConfigurationMono-type Static Inverter4.3.1Diode Inverter4.3.1.1DC Transfer Characteristics4.3.1.2Output Signal Levels4.3.2Zero- $V_{GS}$ Inverter4.3.2.1DC Transfer Characteristics4.3.2.2Output Signal LevelsA.3.2.2Output Signal LevelsNANDNORXORMUXD-LatchConclusion                                                                                                                                                                                                                                                              | 49<br>50<br>51<br>52<br>53<br>56<br>57<br>58<br>60<br>61<br>62<br>63<br>64<br>65                                |

| 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ul> Des | Design Considerations for Organic Circuits<br>Standard Cell Configuration<br>Mono-type Static Inverter<br>4.3.1 Diode Inverter<br>4.3.1.1 DC Transfer Characteristics<br>4.3.1.2 Output Signal Levels<br>4.3.2 Zero-V <sub>GS</sub> Inverter<br>4.3.2.1 DC Transfer Characteristics<br>4.3.2.2 Output Signal Levels<br>NAND<br>NOR<br>NOR<br>MUX<br>D-Latch<br>Conclusion<br>gn of Robust Organic Circuits                                                                                                                                                                                    | 49<br>50<br>51<br>52<br>53<br>56<br>57<br>58<br>60<br>61<br>62<br>63<br>64<br>65<br><b>67</b>                   |

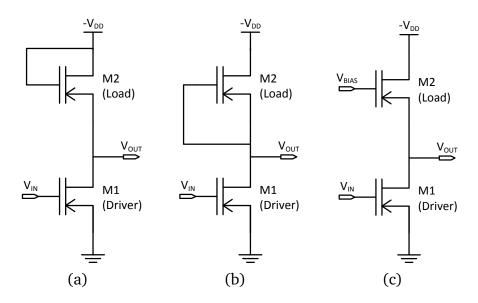

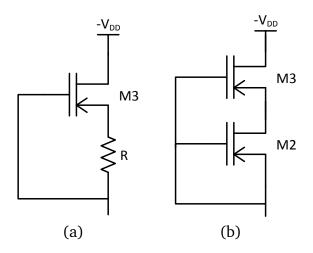

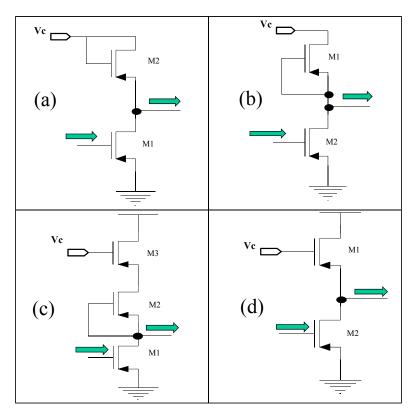

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ul>     | Design Considerations for Organic Circuits         Standard Cell Configuration         Mono-type Static Inverter         4.3.1 Diode Inverter         4.3.1 Diode Inverter         4.3.1.1 DC Transfer Characteristics         4.3.1.2 Output Signal Levels         4.3.2 Zero- $V_{GS}$ Inverter         4.3.2.1 DC Transfer Characteristics         4.3.2.2 Output Signal Levels         4.3.2.2 Output Signal Levels         NAND         NOR         MUX         D-Latch         Conclusion         gn of Robust Organic Circuits         Existing Organic Mono-type Active Load Circuits | 49<br>50<br>51<br>52<br>53<br>56<br>57<br>58<br>60<br>61<br>62<br>63<br>64<br>65<br><b>67</b><br>68             |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ul> Des | Design Considerations for Organic CircuitsStandard Cell ConfigurationMono-type Static Inverter4.3.1Diode Inverter4.3.1.1DC Transfer Characteristics4.3.1.2Output Signal Levels4.3.2Zero- $V_{GS}$ Inverter4.3.2.1DC Transfer Characteristics4.3.2.2Output Signal Levels4.3.2.2Output Signal LevelsNANDNORNORMUXD-LatchConclusionStatic Organic CircuitsExisting Organic Mono-type Active Load Circuits5.1.1Issues with Diode Load Circuits                                                                                                                                                    | 49<br>50<br>50<br>51<br>52<br>53<br>56<br>57<br>58<br>60<br>61<br>62<br>63<br>64<br>65<br><b>67</b><br>68<br>68 |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ul> Des | Design Considerations for Organic Circuits         Standard Cell Configuration         Mono-type Static Inverter         4.3.1 Diode Inverter         4.3.1 Diode Inverter         4.3.1.1 DC Transfer Characteristics         4.3.1.2 Output Signal Levels         4.3.2 Zero- $V_{GS}$ Inverter         4.3.2.1 DC Transfer Characteristics         4.3.2.2 Output Signal Levels         4.3.2.2 Output Signal Levels         NAND         NOR         MUX         D-Latch         Conclusion         gn of Robust Organic Circuits         Existing Organic Mono-type Active Load Circuits | 49<br>50<br>50<br>51<br>52<br>53<br>56<br>57<br>58<br>60<br>61<br>62<br>63<br>64<br>65<br>68<br>68<br>69        |

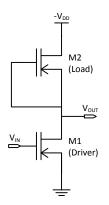

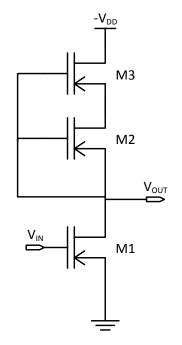

|               | 5.2                                                                                                                             | Proposed Positive-feedback Load Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

|---------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

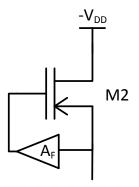

|               | 5.3                                                                                                                             | Proposed Cascaded Zero-V <sub>GS</sub> Load Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

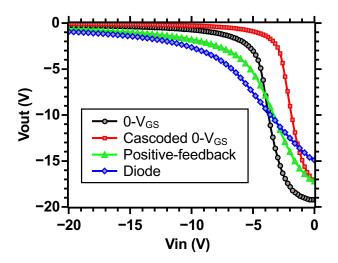

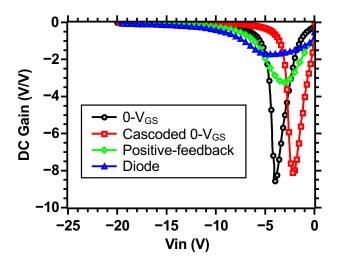

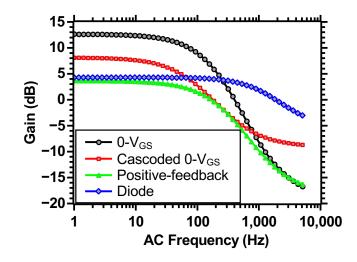

|               | 5.4                                                                                                                             | Performance Comparison of Various Load Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

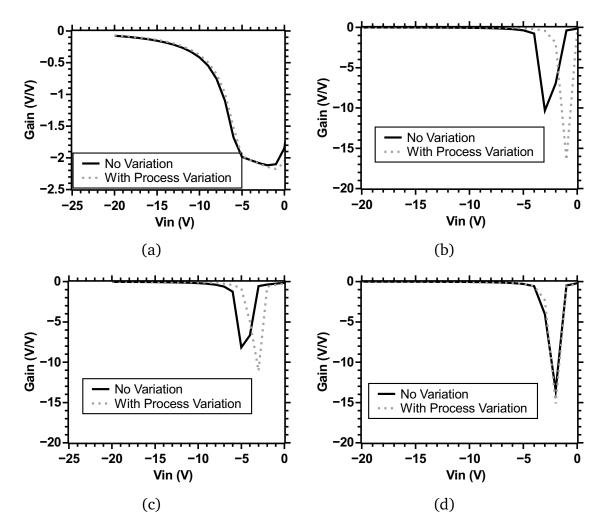

|               |                                                                                                                                 | 5.4.1 Tolerance to OTFT Variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76                                                                                      |

|               |                                                                                                                                 | 5.4.1.1 $V_T$ Variation due to Process Mismatch Variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 77                                                                                      |

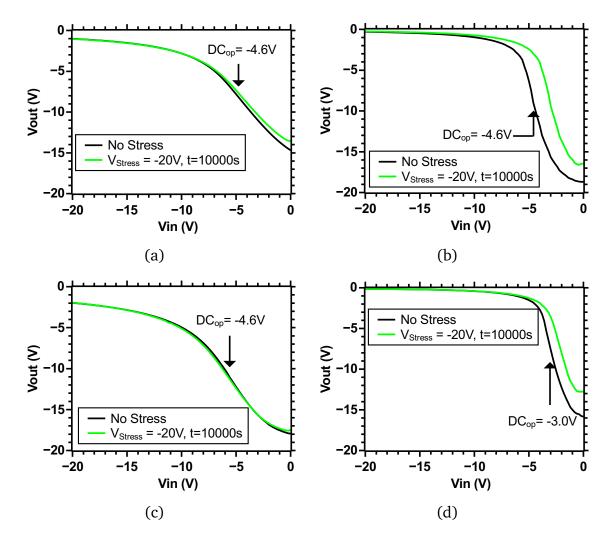

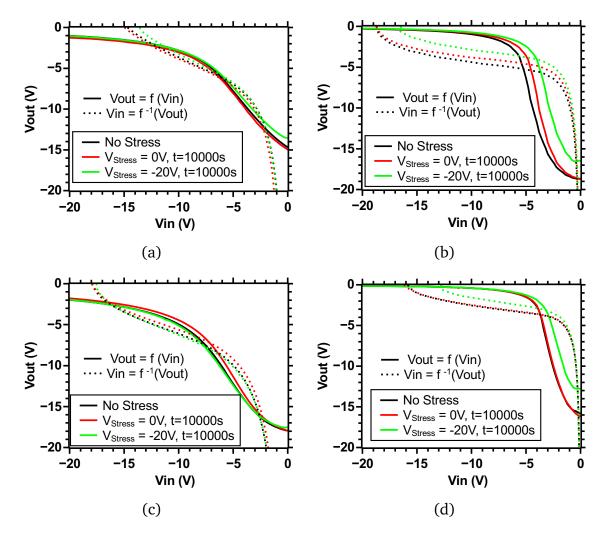

|               |                                                                                                                                 | 5.4.1.2 $V_T$ Variation due to Bias-Stress Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                         |

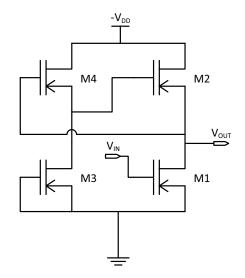

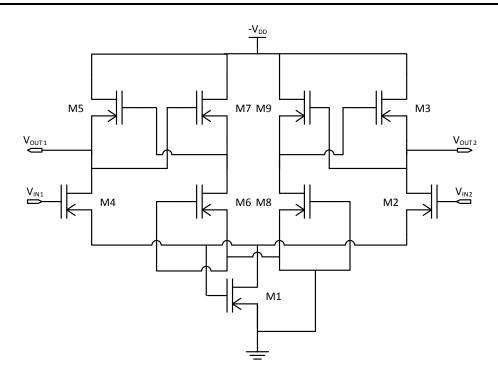

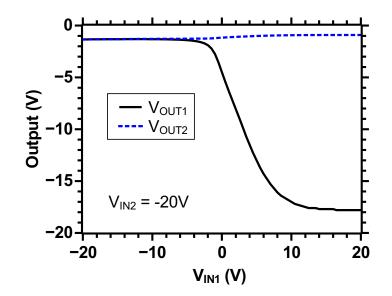

|               | 5.5                                                                                                                             | Organic Differential Amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 82                                                                                      |

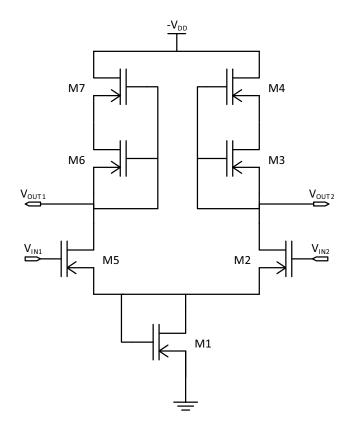

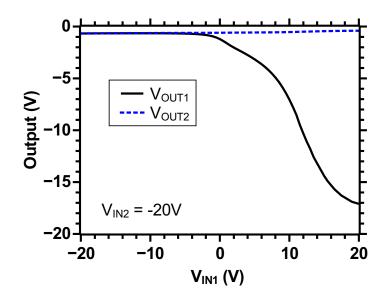

|               |                                                                                                                                 | 5.5.1 Differential Amplifier using a Positive Feedback Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 82                                                                                      |

|               |                                                                                                                                 | 5.5.2 Differential Amplifier using a Cascaded Zero-V <sub>GS</sub> Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 84                                                                                      |

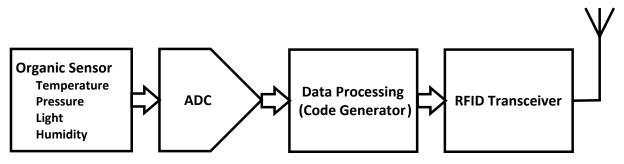

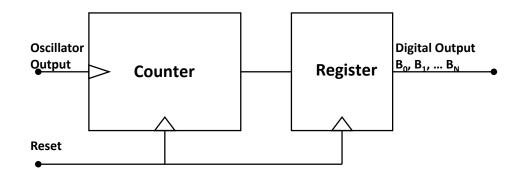

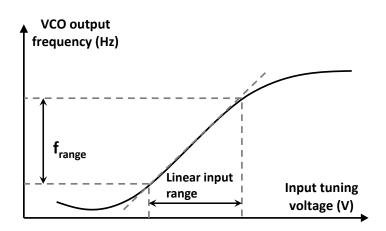

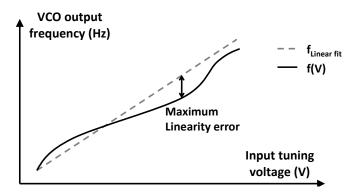

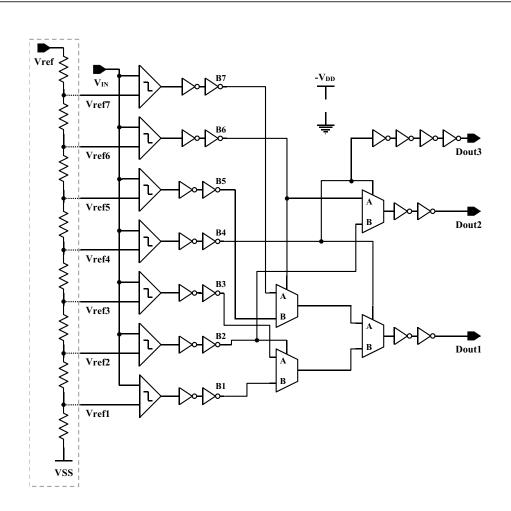

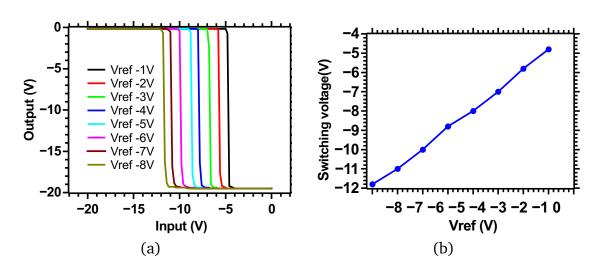

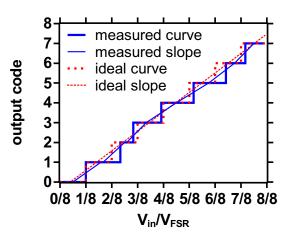

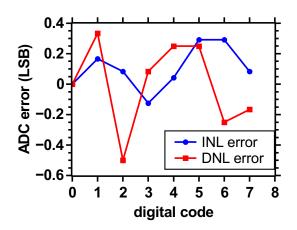

|               | 5.6                                                                                                                             | Organic Analog-to-Digital Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |

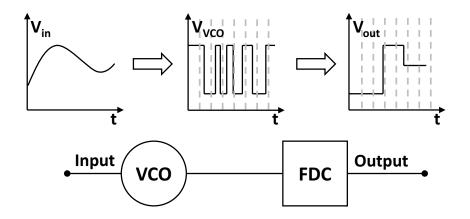

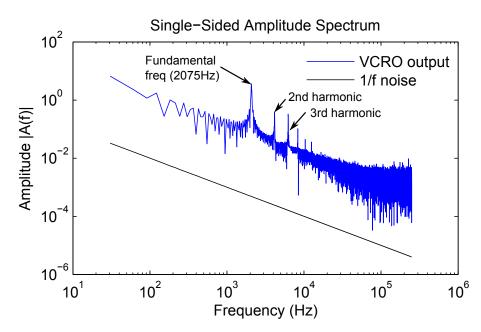

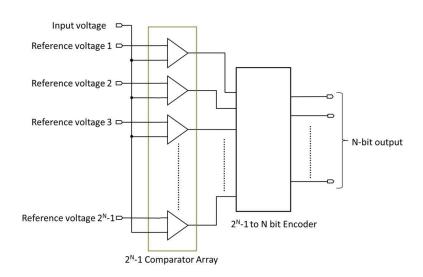

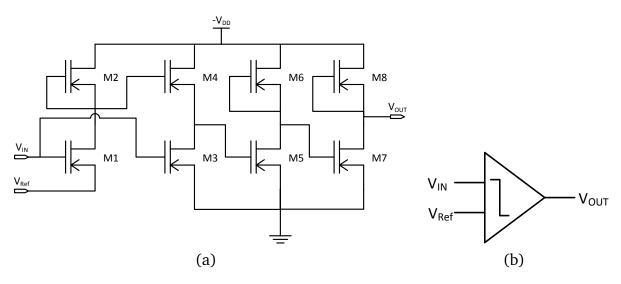

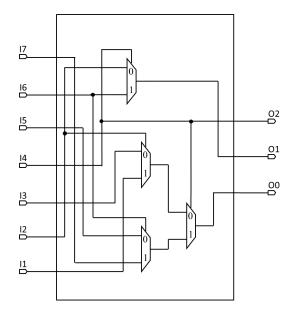

|               | 5.7                                                                                                                             | Digital Analog-to-Digital Converter Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 86                                                                                      |