## Analysis of Current Conveyor based Switched Capacitor Circuits for Application in $\Delta\Sigma$ Modulators

Dem Fachbereich Elektrotechnik und Informationstechnik der Technischen Universität Darmstadt zur Erlangung des akademischen Grades eines Doktor-Ingenieurs (Dr.-Ing.) genehmigte Dissertation

von **Harish Balasubramaniam, M.Sc.** Geboren am 16.08.1984 in Nagapattinam, Indien

Referent:

Korreferent:

Prof. Dr.-Ing. Klaus Hofmann Technische Universität Darmstadt Prof. Dr.-Ing. Roland Thewes Technische Universität Berlin

Tag der Einreichung: Tag der mündlichen Prüfung: 15.09.2014 15.12.2014

D17 Darmstadt 2015

### Erklärung laut §9 PromO

Ich versichere hiermit, dass ich die vorliegende Dissertation allein und nur unter Verwendung der angegebenen Literatur verfasst habe. Die Arbeit hat bisher noch nicht zu Prüfungszwecken gedient.

Plochingen, 16.02.2015

## Acknowledgements

This thesis is a consequence of the work done as a teaching and research assistant at the Integrated Electronic Systems Lab of the Technische Universität Darmstadt. I would like to express my sincere gratitude to my Doktorvater, mentor and advisor Prof. Dr.-Ing. Klaus Hofmann for his continuous support, patience and motivation throughout my years of Ph.D study. I thank him for having confidence in my capabilities and giving me this wonderful opportunity of pursuing research under his guidance.

I would like to express my gratitude to Prof. Dr.-Ing. Roland Thewes for agreeing to become the Co-Referee for my thesis. His comments and observations were valuable and instrumental in improving the quality of the work. Besides my advisor and co-referee, I would like to thank the rest of my thesis committee for their thoughtful comments and advice, which helped improve the quality of my thesis.

My Ph.D would not have been enjoyable without the friendly atmosphere and camaraderie displayed by my colleagues. For this I would like to thank all my colleagues with whom I had the pleasure of carrying out interesting conversations regarding research, projects, conferences and administrative issues.

Last but not least I would like to thank my entire family, particularly my parents for their support and encouragement throughout my career. Without their best wishes and backing, I would not be in the position I am in today. A very special thanks to my wife Kamala for her love, understanding and assistance in proofreading this thesis!

## Abstract

The reduction in supply voltage, loss of dynamic range and increased noise prevent the analog circuits from taking advantage of advanced technologies. Therefore the trend is to move all signal processing tasks to digital domain where advantages of technology scaling can be used. Due to this, there exists a need for data converters with large signal bandwidths, higher speeds and greater dynamic range to act as an interface between real world analog and digital signals.

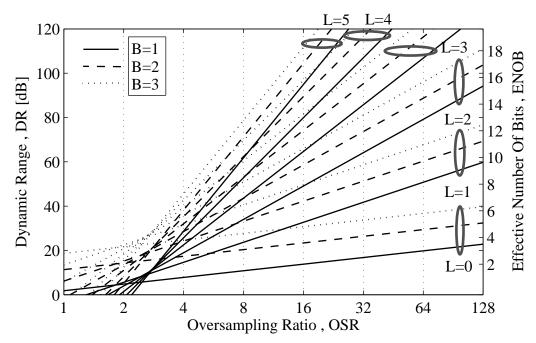

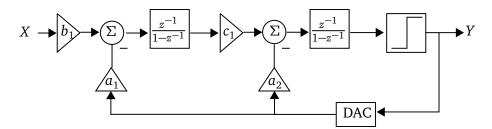

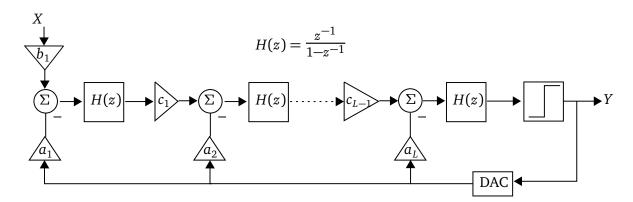

The Delta Sigma ( $\Delta\Sigma$ ) modulator is a data converter that makes use of large sampling rates and noise shaping techniques to achieve high resolution in the band of interest. The modulator consists of analog integrators and comparators which create a modulated digital bit stream whose average represents the input value. Due to their simplicity, they are popular in narrow band receivers, medical and sensor applications.

However Operational Amplifiers (Op-Amps) or Operational Transconductance Amplifiers (OTAs), which are commonly used in data converters, present a bottleneck. Due to low supply voltages, designers rely on folded cascode, multistage cascade and bulk driven topologies for their designs. Although the two stage or multistage cascade topologies offer good gain and bandwidth, they suffer from stability problems due to multiple stages and feedback requiring large compensation capacitors. Therefore other low voltage Switched-Capacitor (SC) circuit techniques were developed to overcome these problems, based on inverters, comparators and unity gain buffers.

In this thesis we present an alternative approach to design of  $\Delta\Sigma$  modulators using Second Generation Current Conveyors (CCIIs). The important feature of these modulators is the replacement of the traditional Op-Amp based SC integrators with CCII based SC integrators. The main design issues such as the effect of the non-idealities in the CCIIs are considered in the operation of SC circuits and solutions are proposed to cancel them. Design tradeoffs and guide-lines for various components of the circuit are presented through analysis of existing and the proposed SC circuits. A two step adaptive calibration technique is presented which uses few additional components to measure the integrator input output characteristic and linearize it for providing optimum performance over a wide range of sampling frequencies while maintaining low power and area.

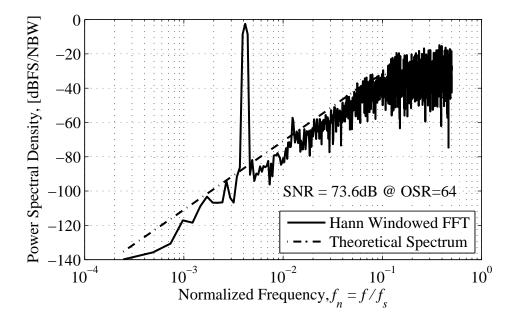

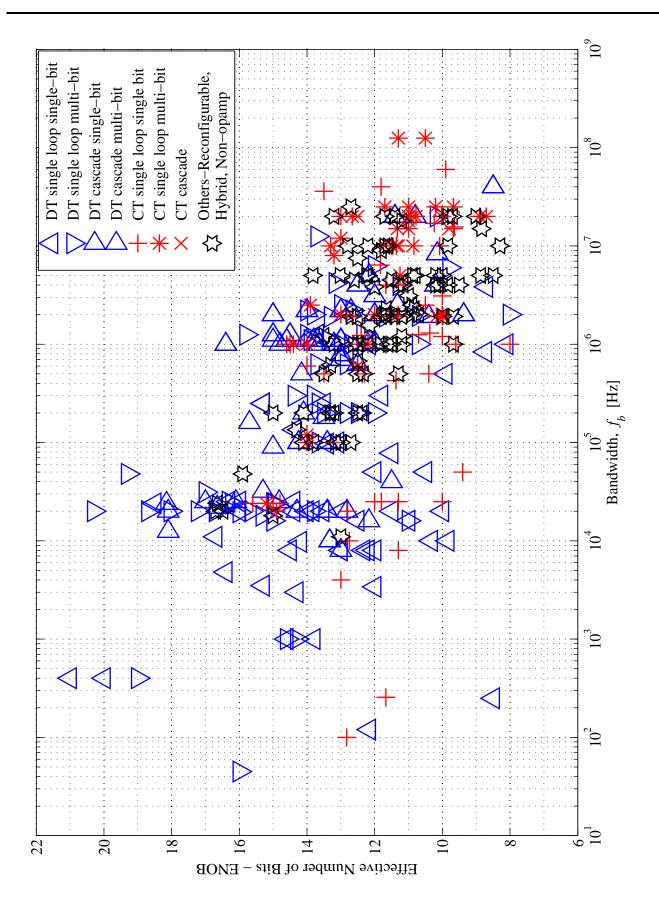

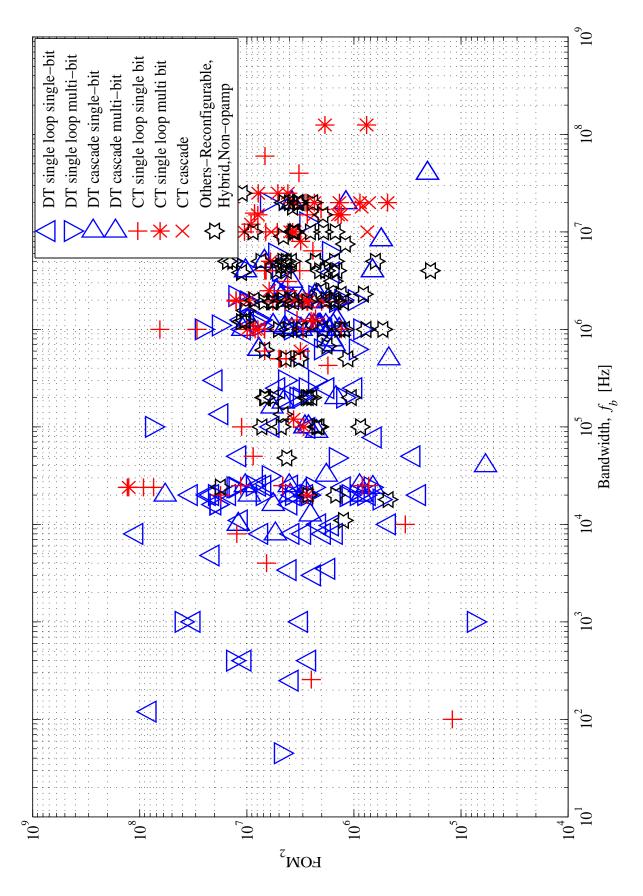

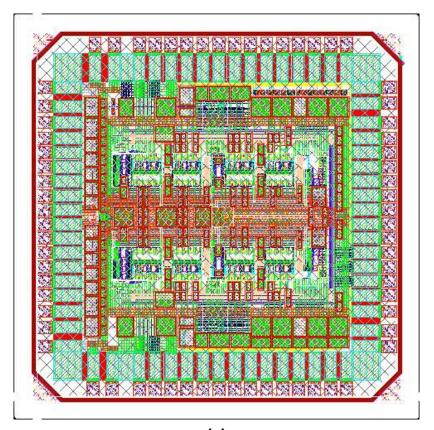

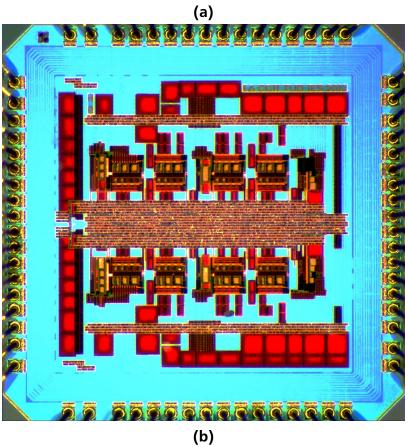

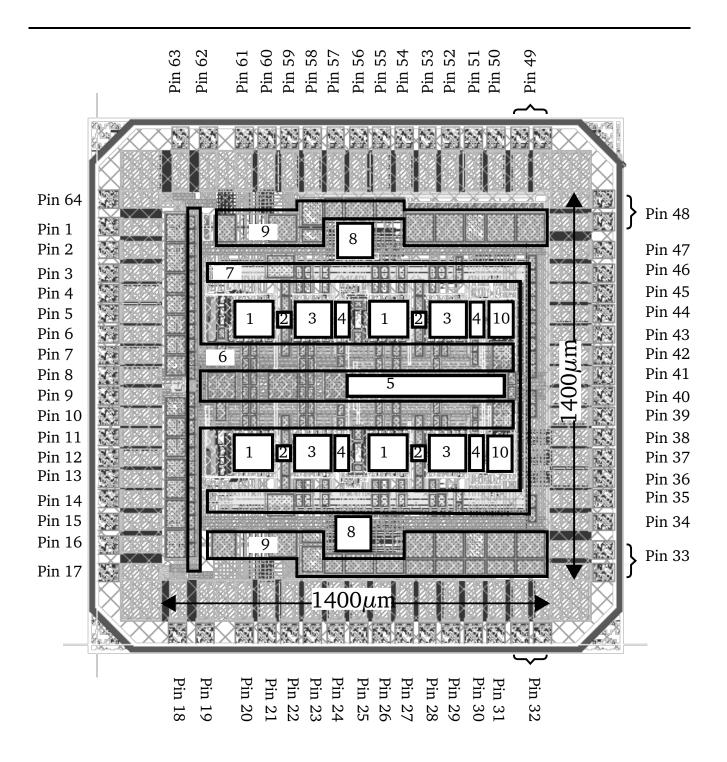

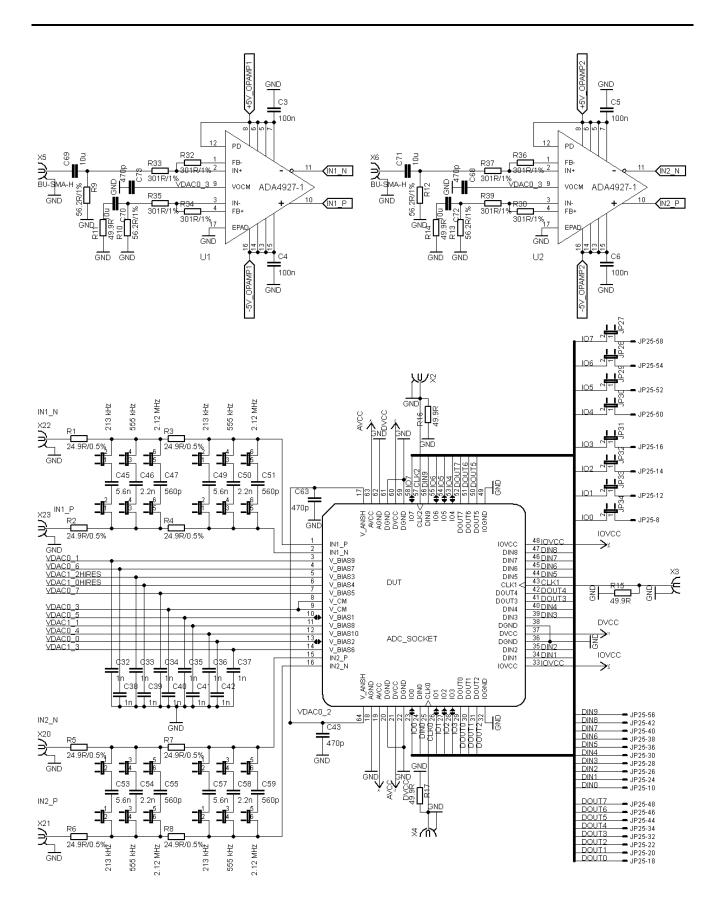

The presented CCII integrator and calibration circuit are used in the design of a 4th order (2-2 cascade)  $\Delta\Sigma$  modulator which has been fabricated in UMC 90nm/1V technology through Europractice. Experimental values for Signal to Noise+Distortion Ratio (SNDR), Dynamic Range (DR) and Figure Of Merit (FOM) show that the modulator can compete with state of art reconfigurable Discrete-Time (DT) architectures while using lower gain stages and less design complexity.

## Kurzfassung

Analoge Schaltungen profitieren im Vergleich zu digitalen Schaltungen nur wenig von den Vorteilen moderner Technologien, da die abnehmenden Versorgungsspannungen deren Dynamikbereich reduzieren und gleichzeitig mehr Leistung zur Rauschminimierung benötigen. Es war und ist daher nur konsequent möglichst viele Signalverarbeitungsaufgaben in die digitale Domäne zu verlagern, in der die Vorteile moderner Technologien mit kleinsten Strukturgrößen zum Tragen kommen. Als weitere Konsequenz hieraus stieg der Bedarf nach schnellen Datenkonvertern mit großer Bandbreite und großem Dynamikbereich als Schnittstelle zwischen der analogen und digitalen Domäne rasch an.

Der Delta Sigma ( $\Delta\Sigma$ ) Modulator ist eine der gebräuchlichsten Datenkonverterrealisierung mit hoher Abtastrate, ermöglicht eine hohe Auflösung im zu betrachtenden Spannungsbereich und bietet gleichzeitig die Möglichkeit einer effektiven Rauschunterdrückung. Der Modulator erzeugt einen pulsweitenmodulierten digitalen Datenstrom, ist darüber hinaus einfach aufgebaut und besteht im Wesentlichen aus analogen Integratoren und Komparatoren.  $\Delta\Sigma$ Modulatoren werden häufig für schmalbandige Empfänger, Medizin- und Sensoranwendungen eingesetzt. Herkömmliche Operationsverstärker (Op-Amps oder OTAs) als eine Hauptkomponente dieser Datenkonverter limitieren jedoch zunehmend deren Leistungsfähigkeit. Aufgrund der niedrigen Versorgungsspannungen sind Entwickler zunehmend gehalten Folded-Cascode-, Multistage-Kaskaden- und Bulk-Driven-Topologien in ihren Schaltungsentwürfen einzusetzen. Die bei Multistage-Kaskaden sehr hohe Verstärkung und Bandbreite wird meist mit Stabilitätsproblemen aufgrund der hohen Anzahl von verstärkenden Stufen bzw. Rückkopplungen mit großen Kompensationskapazitäten erkauft. Es war daher nur konsequent, leistungseffiziente Switched-Capacitor (SC) Schaltungstechniken auf der Basis von Invertern, Komparatoren und Spannungsfolgern zu favorisieren.

In dieser Arbeit wird ein alternativer Ansatz zum Entwurf von  $\Delta\Sigma$  Modulatoren unter Verwendung von Current Conveyor (CCII) der zweiten Generation untersucht. Bei diesen Modulatoren werden die herkömmlichen, auf Operationsverstärkern basierenden SC-Integratoren durch solche mit CCIIs ersetzt. Die auftretenden Entwurfsprobleme, wie beispielsweise die Nichtidealitäten der CCIIs werden in der Anwendung der SC-Integratoren diskutiert und Lösungen aufgezeigt. Weiterhin werden Entwurfsraumexplorationen zwischen verschiedenen Komponenten durch Analyse herkömmlicher und verbesserter SC-Schaltungen durchgeführt. Ferner wird ein adaptives Kalibrierungsverfahren mit nur wenigen zusätzlichen Komponenten beschrieben, das den Einsatz des Modulators über einen weiten Bereich von Abtastfrequenzen bei gleichzeitig optimaler Performanz, kleinem Silizium-Flächenbedarf und niedriger Leistungsaufnahme ermöglicht.

Die behandelten CCII Integratoren sind in einem Entwurfsbeispiel eines  $\Delta\Sigma$  Modulators 4. Ordnung (2-2 Kaskade) in 90nm/1V UMC Technologie exemplarisch unter Verwendung des Europractice Services gefertigt worden. Messungen zeigen ein gegenüber herkömmlichen zeitdiskreten Architekturen vergleichbares Rausch/Störverhältnis (Signal to Noise+Distortion Ratio (SNDR)) sowie einen vergleichbaren Dynamikbereich (Dynamic Range (DR)), bei jedoch deutlich reduzierter Schaltungskomplexität und geringerer Anzahl der Verstärkerstufen.

## Contents

| A  | knowledgements                                                                                                                                                                                                                                                                                            |                                       | Ш                                                    |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------|

| Al | ostract                                                                                                                                                                                                                                                                                                   |                                       | v                                                    |

| Κι | ırzfassung                                                                                                                                                                                                                                                                                                |                                       | VII                                                  |

| Li | at of Figures                                                                                                                                                                                                                                                                                             |                                       | XIII                                                 |

| Li | at of Tables                                                                                                                                                                                                                                                                                              |                                       | XVII                                                 |

| Li | t of Abbreviations                                                                                                                                                                                                                                                                                        |                                       | хіх                                                  |

| 1  | Introduction1.1Motivation and Research Scope1.2Thesis Outline                                                                                                                                                                                                                                             |                                       |                                                      |

| 2  | Fundamentals and State of the Art in Low Voltage $\Delta\Sigma$ ADCs2.1Nyquist ADCs                                                                                                                                                                                                                       | <br><br>                              | . 8<br>. 8<br>. 12<br>. 15                           |

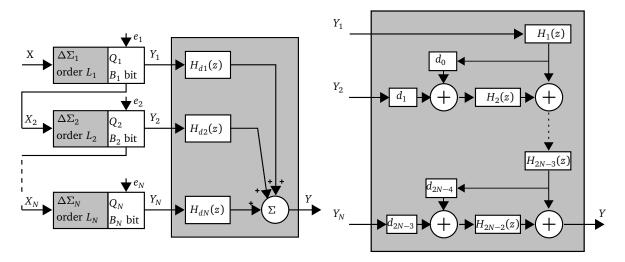

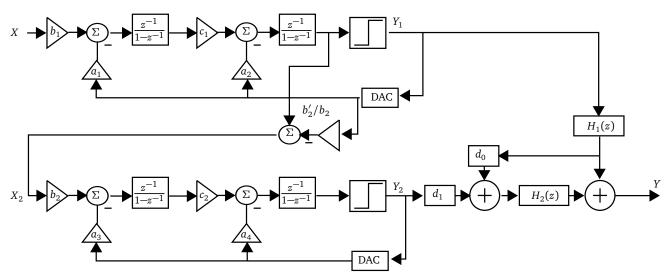

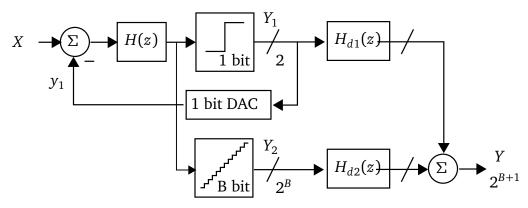

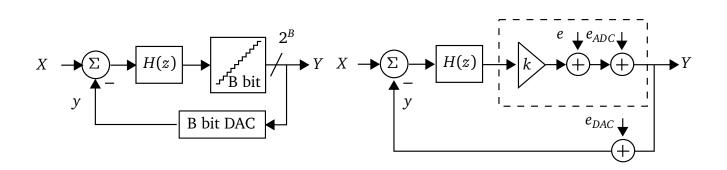

|    | 2.5Types of $\Delta\Sigma$ Topologies2.5.1Single Loop $\Delta\Sigma$ Topology2.5.2Cascade Topology2.5.3Multi-Bit Topology                                                                                                                                                                                 | · · · · ·                             | . 18<br>. 19<br>. 21<br>. 26                         |

|    | 2.6Low Voltage/Low Power Design Techniques for $\Delta\Sigma$ Modulators2.6.1Dynamic Amplifiers2.6.2Inverters2.6.3Comparators2.6.4Switched Current Techniques2.6.5Digital Techniques2.6.6Comparison of the Low Voltage Design Techniques2.7Survey of State of the Art $\Delta\Sigma$ Converters2.8Summary | · · · · · · · · · · · · · · · · · · · | . 29<br>. 31<br>. 32<br>. 33<br>. 34<br>. 34<br>. 35 |

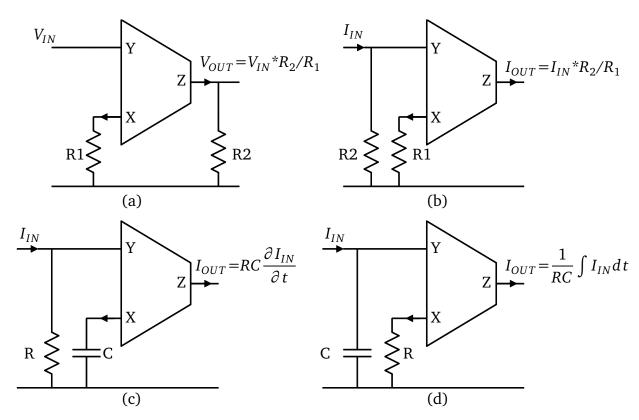

| 3  | Analysis and Design of Current Conveyor based Switched Capacitor Circuit3.1Introduction to Current Conveyors3.1.1First Generation Current Conveyor-CCI                                                                                                                                                    |                                       |                                                      |

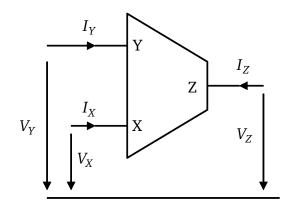

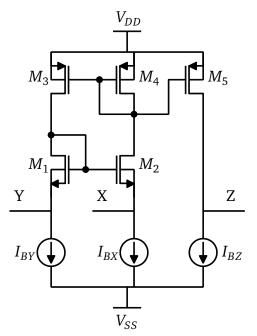

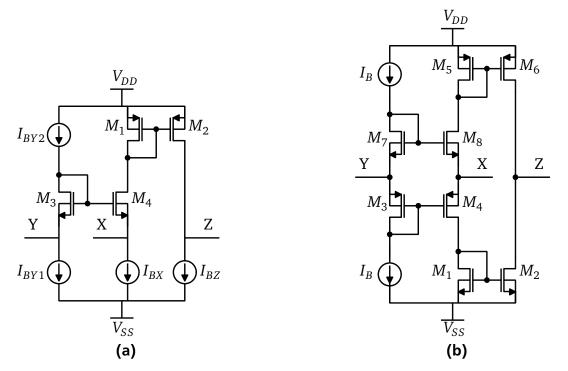

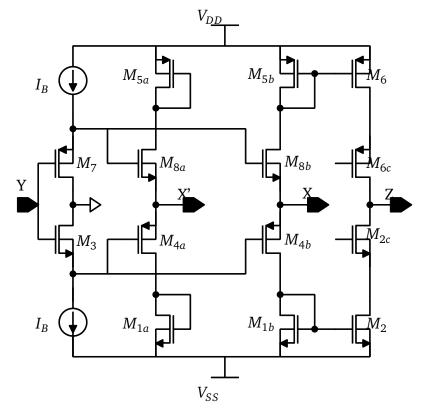

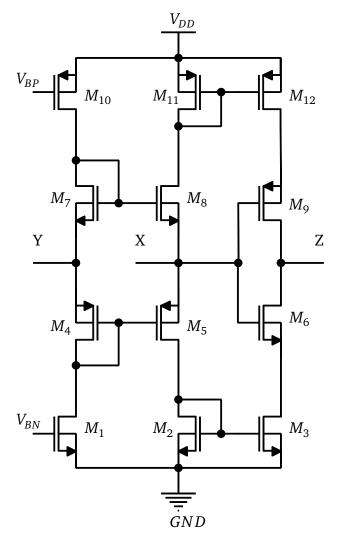

|   |                                                                                                                               | 3.1.2 Second Generation Current Conveyor-CCII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 46                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

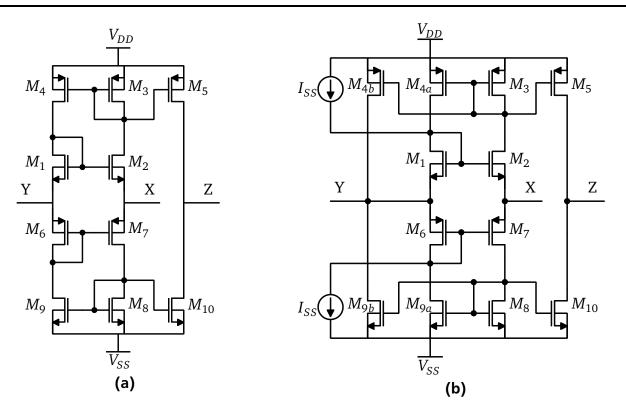

|   |                                                                                                                               | 3.1.3 Other Current Conveyors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 50                                                                                                                                                                                                                                                                                                                                                                                                                            |

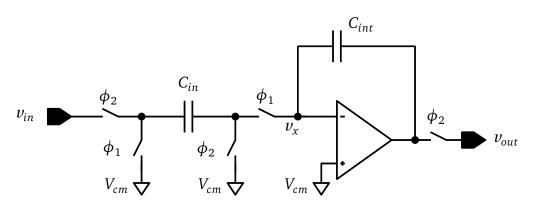

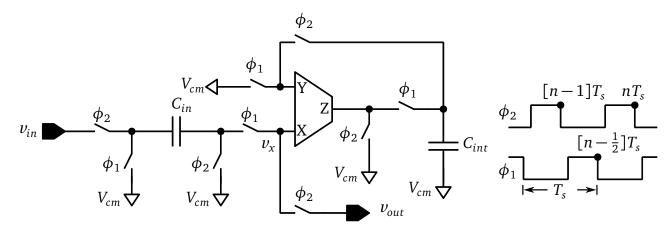

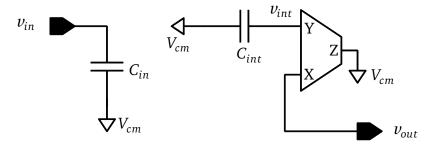

|   | 3.2                                                                                                                           | Basic Principle of Switched Capacitor Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 50                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                                                                               | 3.2.1 Ideal Op-Amp Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 50                                                                                                                                                                                                                                                                                                                                                                                                                            |

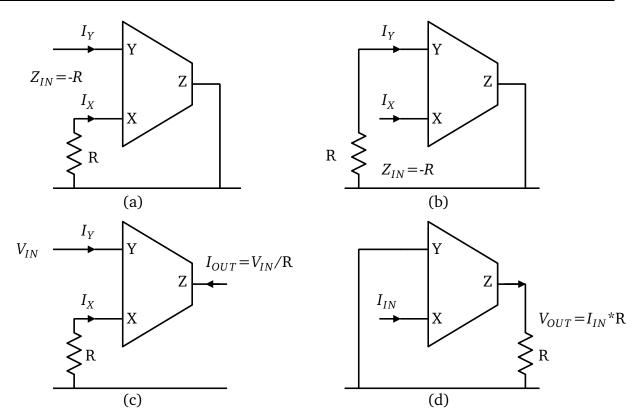

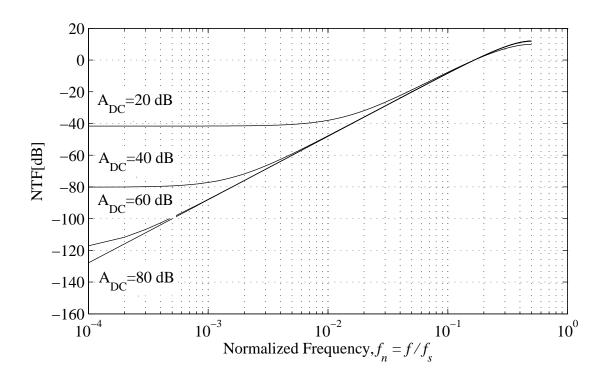

|   |                                                                                                                               | 3.2.2 Ideal CCII Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 51                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 3.3                                                                                                                           | Non-Ideal Effects in Switched Capacitor Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 54                                                                                                                                                                                                                                                                                                                                                                                                                            |

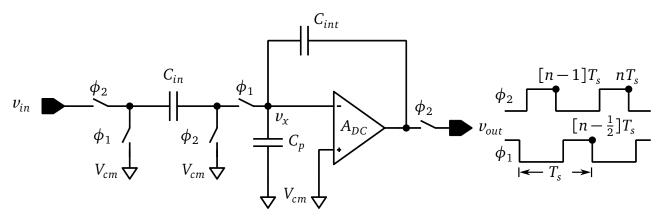

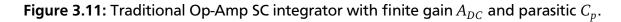

|   |                                                                                                                               | 3.3.1 Op-Amp Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 54                                                                                                                                                                                                                                                                                                                                                                                                                            |

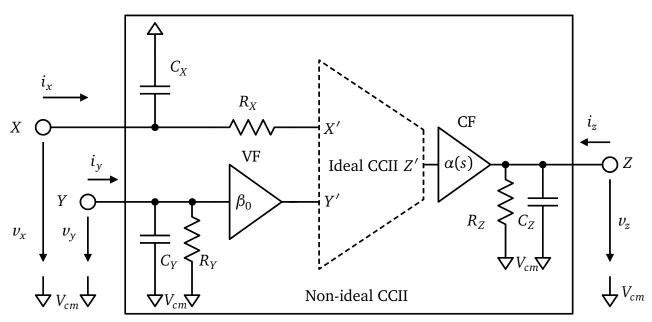

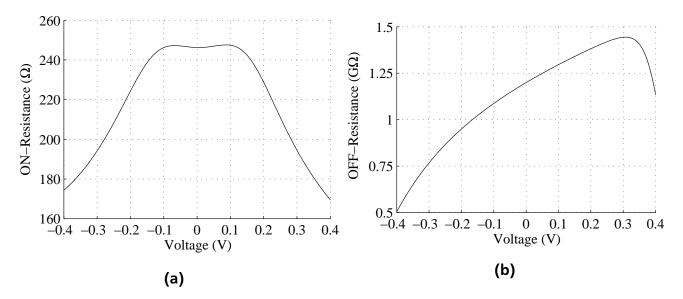

|   |                                                                                                                               | 3.3.2 CCII Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 56                                                                                                                                                                                                                                                                                                                                                                                                                            |

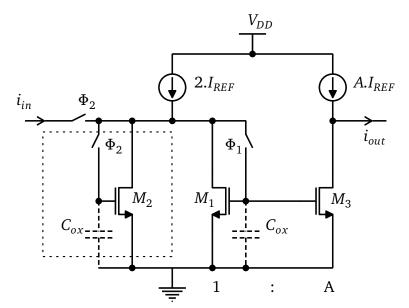

|   | 3.4                                                                                                                           | Proposed Fully Integrable CCII Integrators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 75                                                                                                                                                                                                                                                                                                                                                                                                                            |

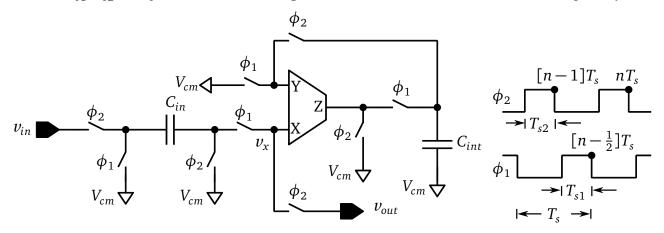

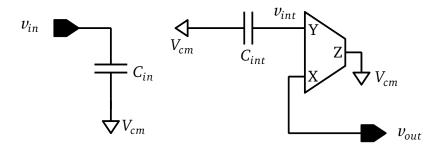

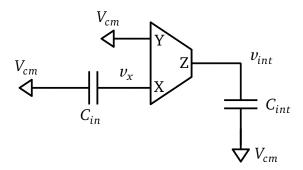

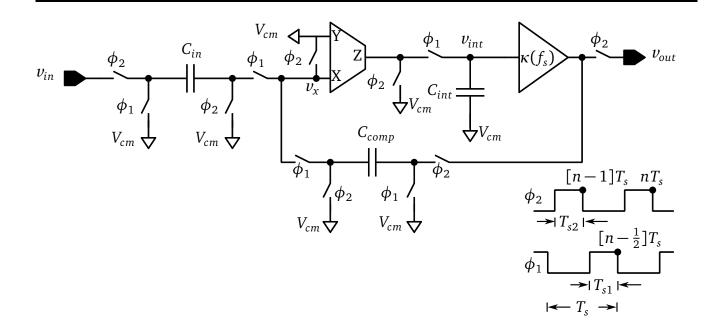

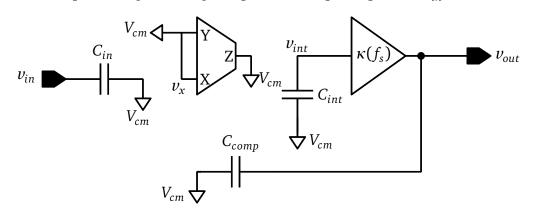

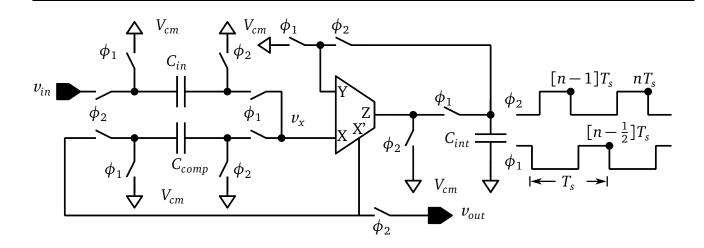

|   |                                                                                                                               | 3.4.1 Wideband Single Ended CCII Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 76                                                                                                                                                                                                                                                                                                                                                                                                                            |

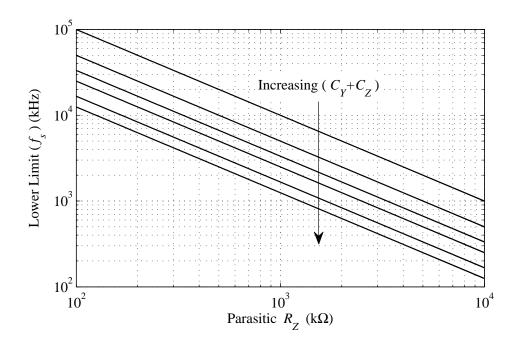

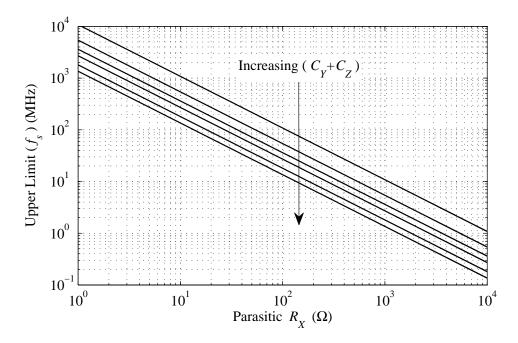

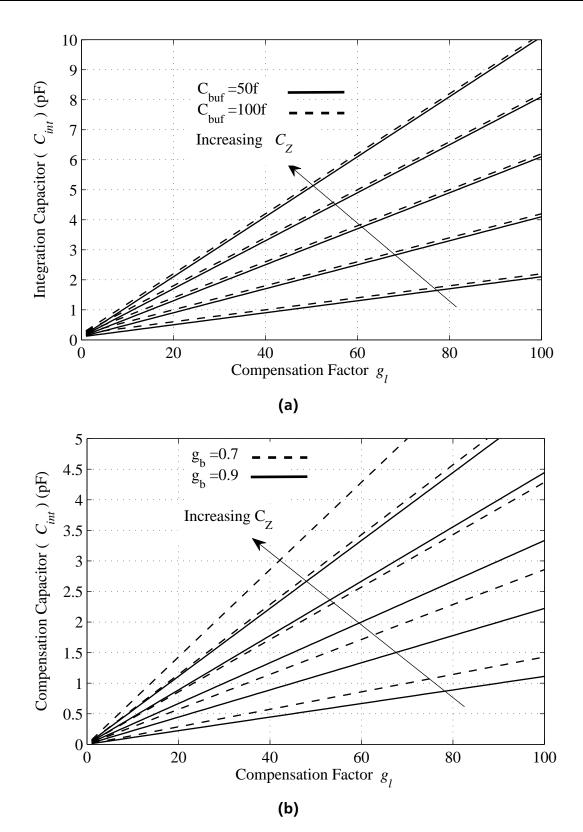

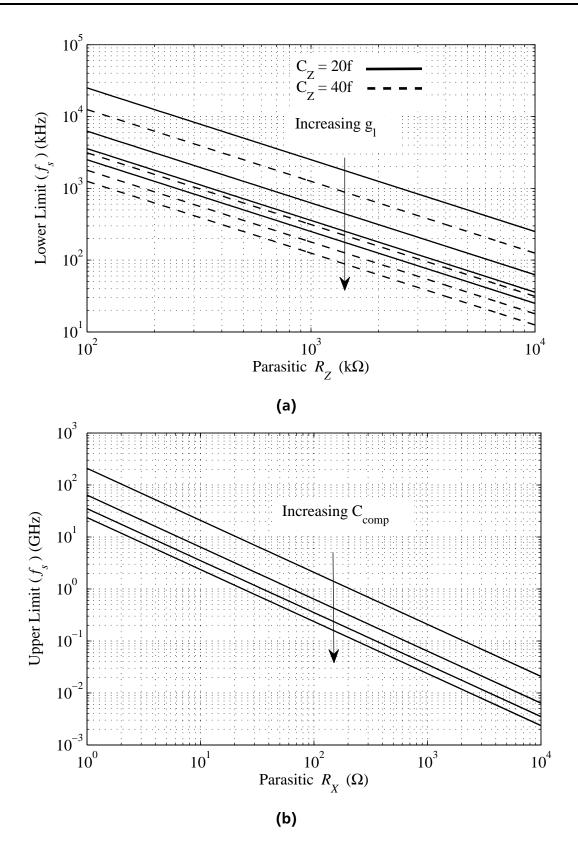

|   |                                                                                                                               | 3.4.2 Design Conditions for Wideband Single Ended CCII Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 84                                                                                                                                                                                                                                                                                                                                                                                                                            |

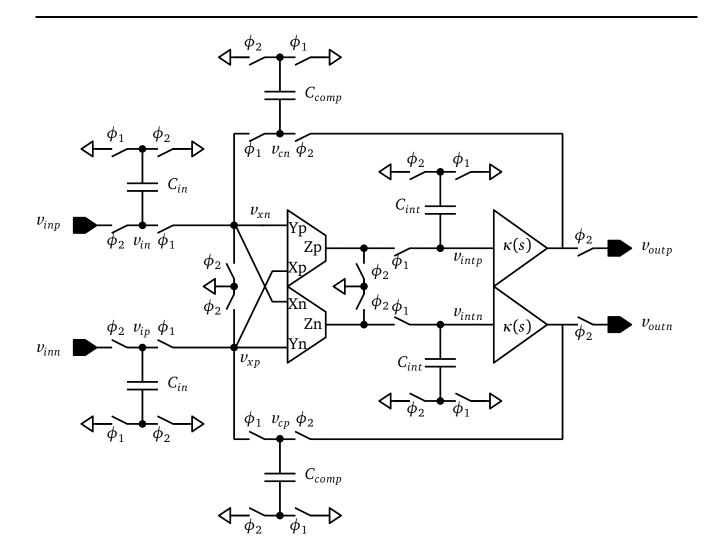

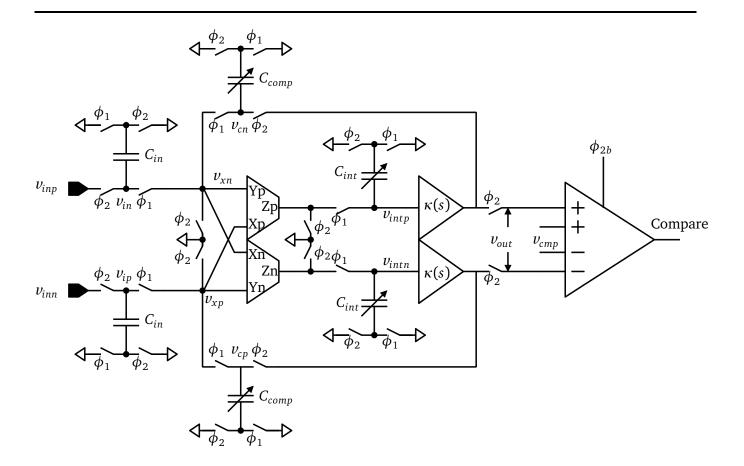

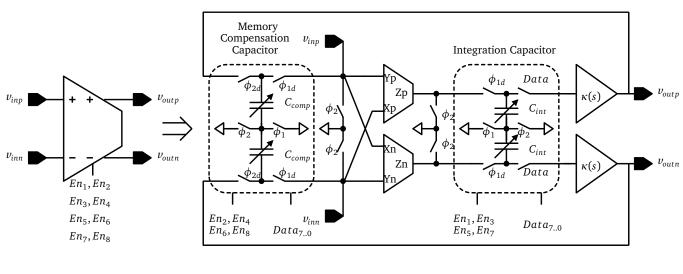

|   |                                                                                                                               | 3.4.3 Wideband Fully Differential CCII Integrator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 87                                                                                                                                                                                                                                                                                                                                                                                                                            |

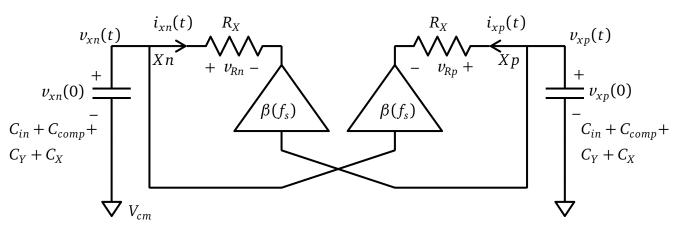

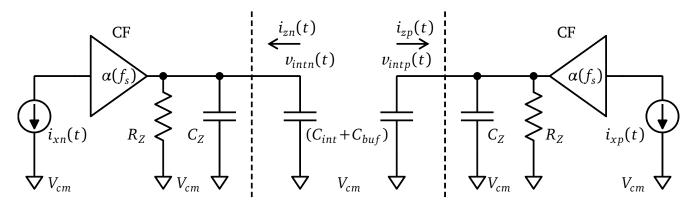

|   |                                                                                                                               | 3.4.4 Design Conditions for Wideband Fully Differential CCII Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 93                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                                                                               | 3.4.5 Low Bandwidth Single Ended CCII Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 94                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                                                                               | 3.4.6 Design Conditions for Low Bandwidth Single Ended CCII Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 96                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                                                                               | 3.4.7 Comparison of the Proposed and Existing CCII Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 97                                                                                                                                                                                                                                                                                                                                                                                                                            |

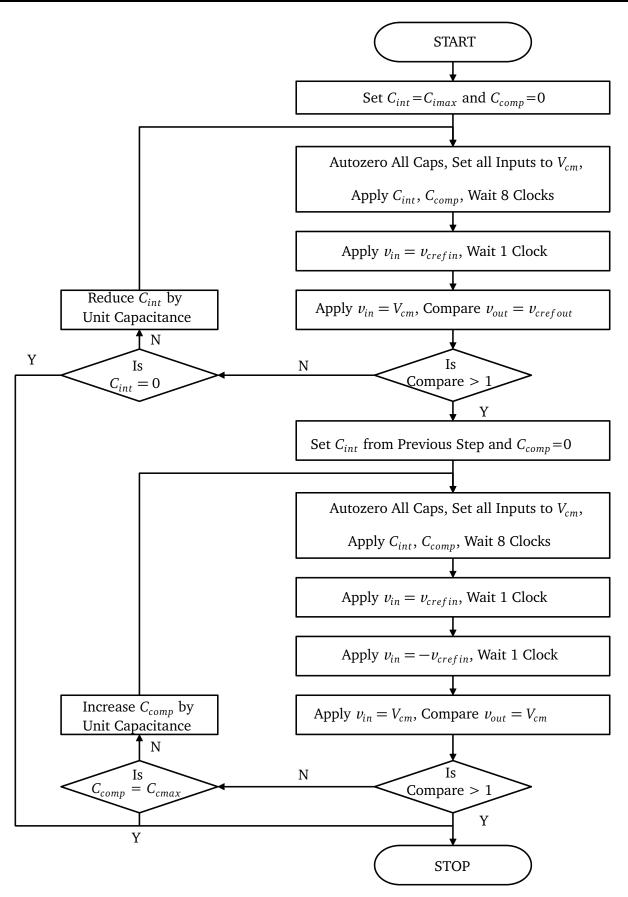

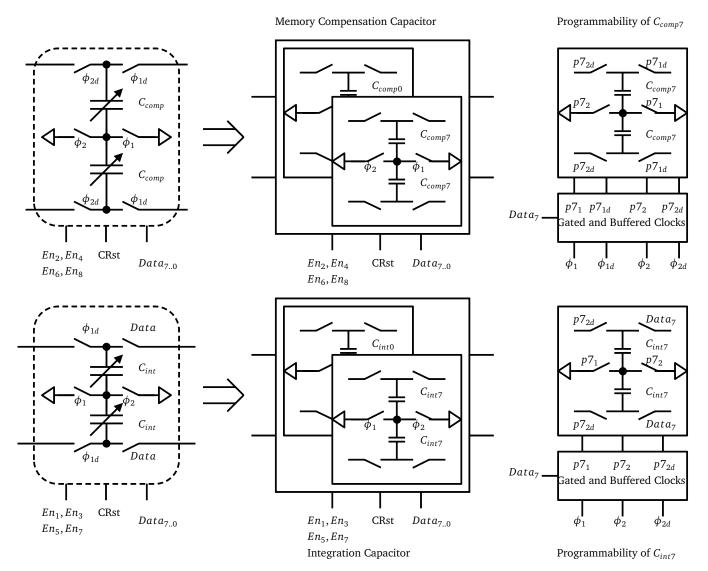

|   | 3.5                                                                                                                           | Wide Sampling Frequency Coverage Using Adaptive Calibration Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 105                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                                                                                                                               | 3.5.1 Choice of Programmable Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                                                               | 3.5.2 Calibration Architecture and Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 107                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 3.6                                                                                                                           | Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 113                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 3.7                                                                                                                           | Benefits and Drawback of the Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 119                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 5.7                                                                                                                           | II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 3.8                                                                                                                           | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

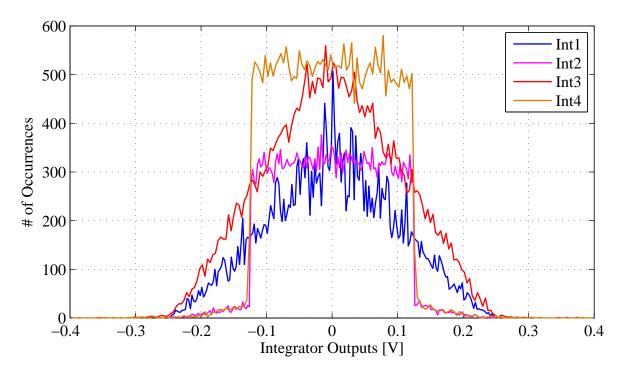

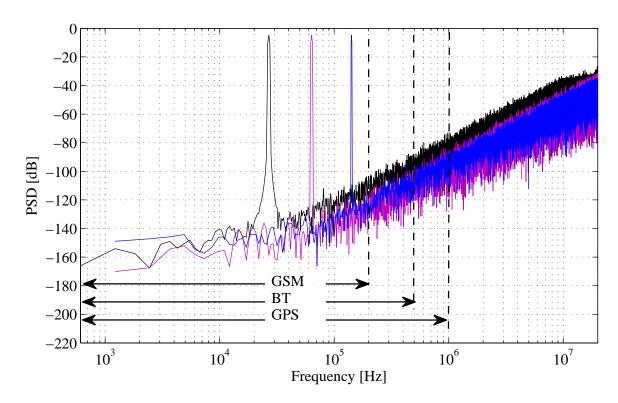

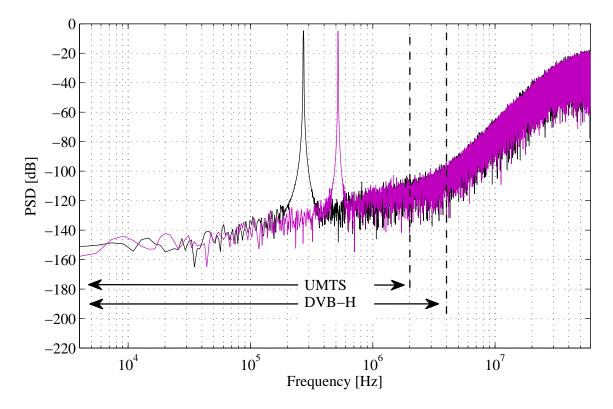

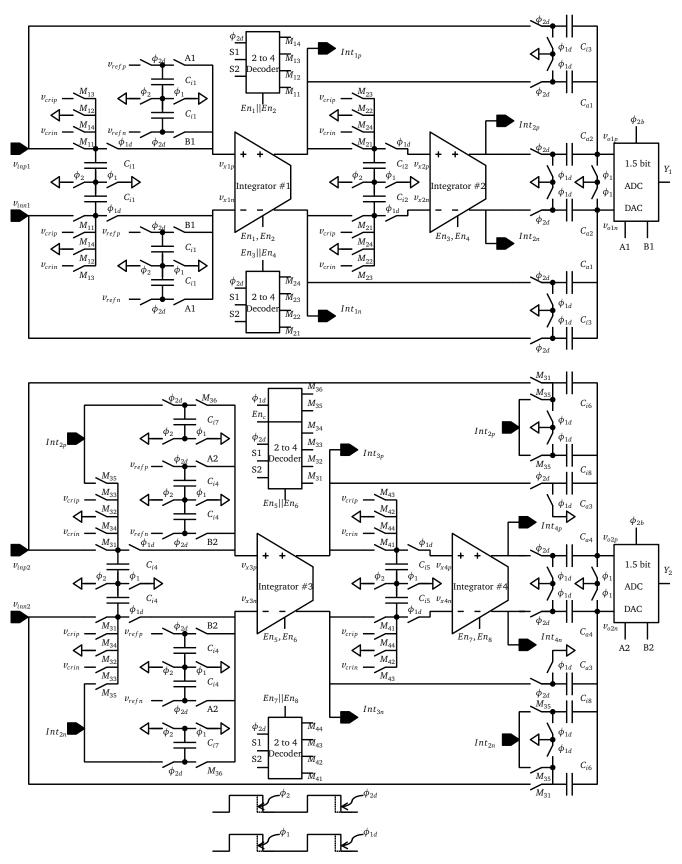

| _ | 3.8                                                                                                                           | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 119                                                                                                                                                                                                                                                                                                                                                                                                                           |