## Alma Mater Studiorum – Università di Bologna

## DOTTORATO DI RICERCA IN

## Ingegneria Elettrotecnica

CICLO XXVIII

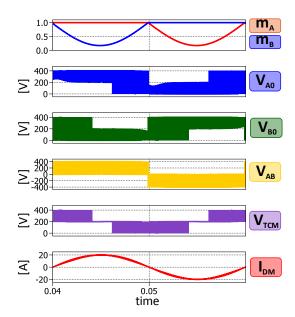

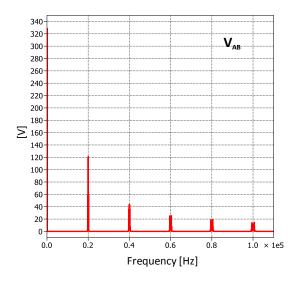

Settore Concorsuale di afferenza: 09/E2

Settore Scientifico disciplinare: ING-IND/32

## DEVELOPMENT OF DC/AC POWER CONVERTERS FOR APPLICATIONS REQUIRING HIGH EFFICIENCY

Presentata da: Ing. Gabriele Rizzoli

**Coordinatore Dottorato**

Relatore

Chiar.mo Prof. Domenico Casadei Chiar.mo Prof. Luca Zarri

Esame finale anno 2016

This page was intentionally left blank.

# Table of contents

| Preface1  |       |                                                           |    |  |

|-----------|-------|-----------------------------------------------------------|----|--|

| Chapter 1 |       | Trends in Power Transistors Technology                    |    |  |

| 1.1       | Sta   | te of the art of silicon transistors                      | 3  |  |

| 1.1.A     |       | Power MOSFETs                                             | 5  |  |

| 1.1.B     |       | Power IGBTs                                               | 9  |  |

| 1.2       | Wi    | de bandgap materials – Silicon Carbide                    | 10 |  |

| Chapte    | r 2   | Power Loss Mechanism in Power Transistors                 | 15 |  |

| 2.1       | Int   | oduction                                                  | 15 |  |

| 2.2       | Los   | sses in AC to DC power converters                         | 16 |  |

| Chapte    | r 3   | Soft Switching in DC to AC Converters                     | 23 |  |

| 3.1       | Int   | oduction                                                  | 23 |  |

| 3.2       | Ov    | erview of DC to AC soft switching inverters               | 25 |  |

| 3.3       | Zei   | o Voltage Transition Converter with two Coupled Inductors |    |  |

| 3.3       | 8.A   | Topology description                                      |    |  |

| 3.3       | 8.B   | Operating principle of the converter                      |    |  |

| ]         | Phase | e 0 - [ <b>t0</b> , <b>t1</b> ]                           |    |  |

| ]         | Phase | e 1 - [ <b>t1</b> , <b>t2</b> ]                           |    |  |

| ]         | Phase | e 2 - [ <b>t2</b> , <b>t3</b> ]                           |    |  |

| ]         | Phase | e 3 - [ <b>t3</b> , <b>t4</b> ]                           | 42 |  |

| ]         | Phase | e 4 - [ <b>t4</b> , <b>t5</b> ]                           | 45 |  |

| ]         | Phase | e 5 - [ <b>t5</b> , <b>t6</b> ]                           | 46 |  |

| ]         | Phase | e 6 - [ <b>t6</b> , <b>t7</b> ]                           | 48 |  |

| ]         | Phase | e 7 - [ <b>t7</b> , <b>t8</b> ]                           | 48 |  |

| ]         | Phase | e 8 - [ <b>t8</b> , <b>t9</b> ]                           | 49 |  |

| 3.3       | 8.C   | Converter design                                          | 51 |  |

| ]         | Desig | gn specifics                                              | 51 |  |

|       | Main transistor selection |                                                                       | 51   |

|-------|---------------------------|-----------------------------------------------------------------------|------|

|       | Reso                      | nant capacitor selection                                              | 56   |

|       | Auto                      | transformer turn ratio section                                        | 60   |

|       | Reso                      | nant inductance selection                                             | 62   |

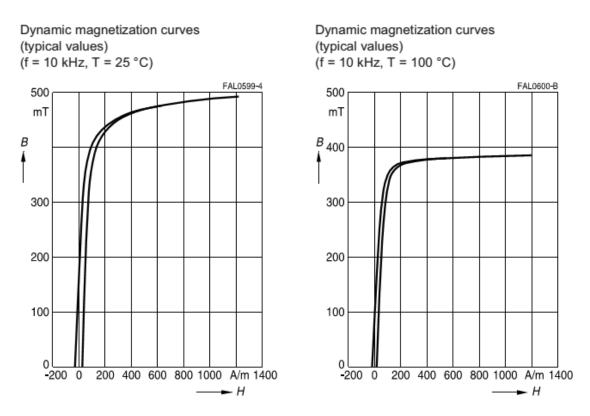

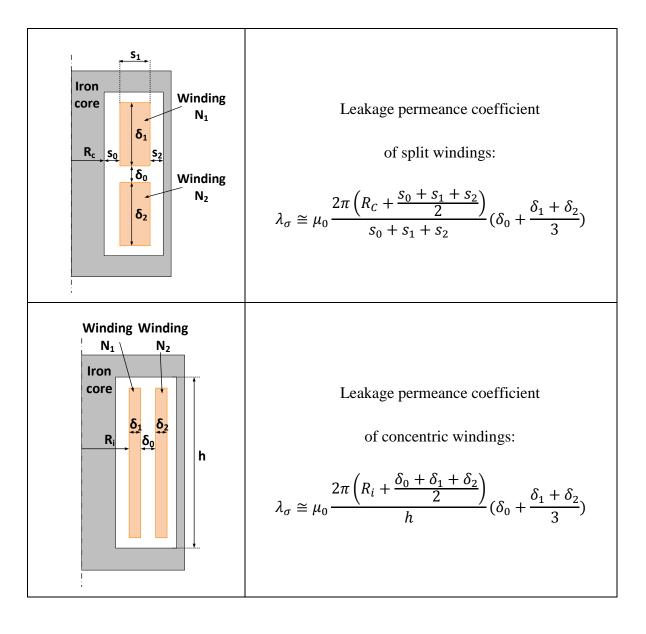

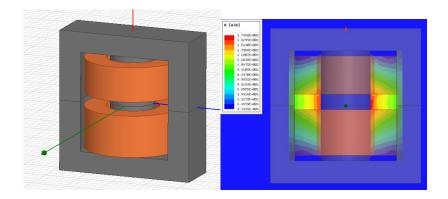

|       | Auto                      | transformer design and FEM simulation                                 | 63   |

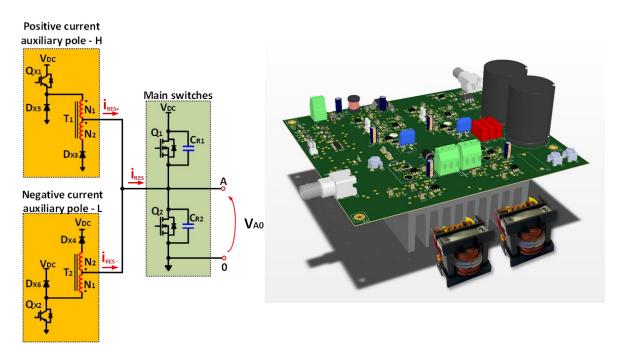

|       | Auxi                      | liary switches and selection of diodes                                | 69   |

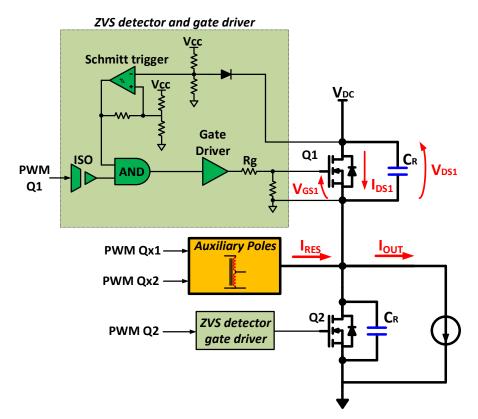

|       | Activ                     | ve ZVS gate driver design                                             | 69   |

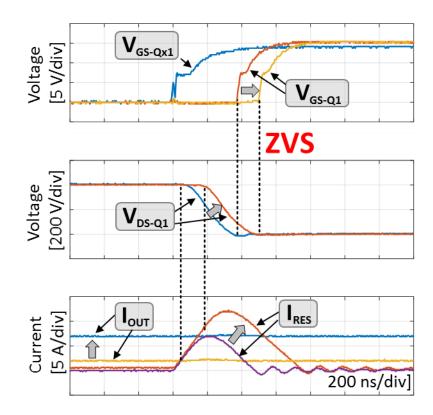

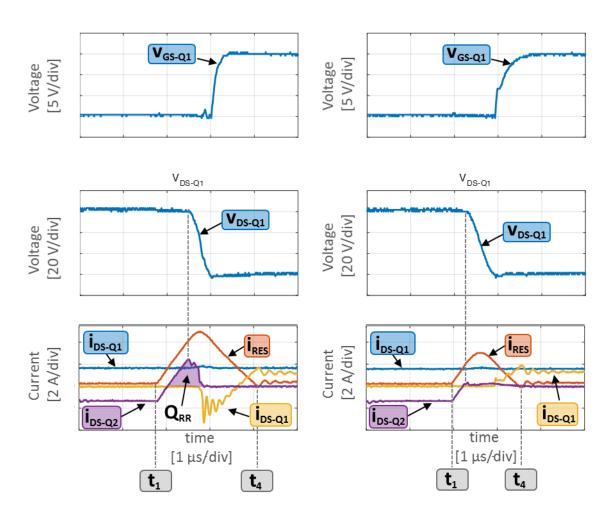

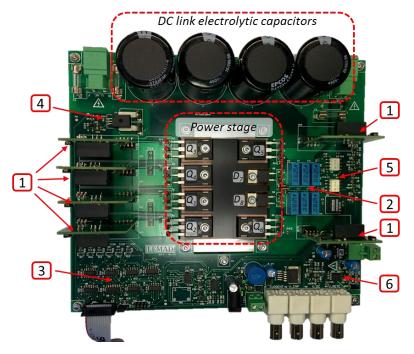

| 3     | .3.D                      | Experimental results                                                  | 71   |

|       | Func                      | tional tests of the converter                                         | 71   |

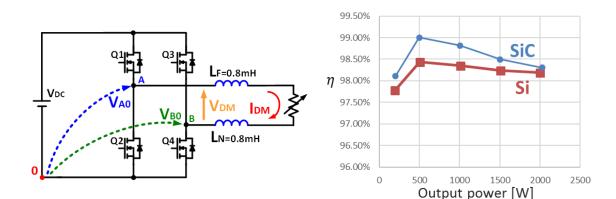

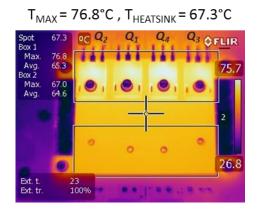

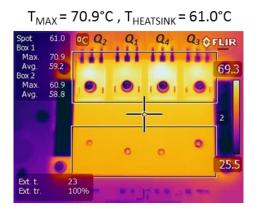

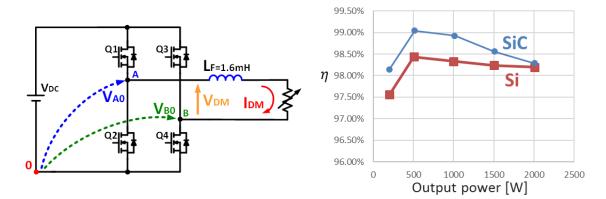

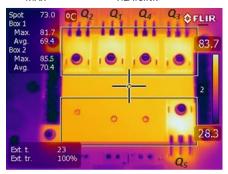

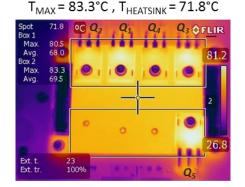

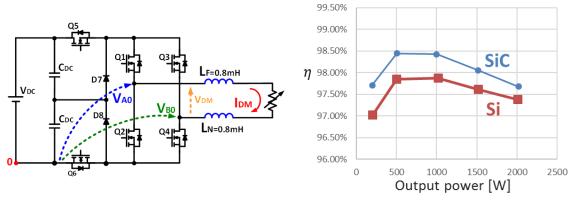

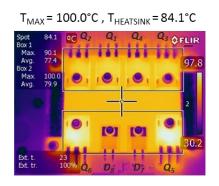

|       | Effic                     | iency comparison of ZVT2CI inverter and HS inverters                  | 77   |

|       |                           |                                                                       |      |

| Chapt | ter 4                     | Single Phase Inverters for Transformerless PV Applications            | 83   |

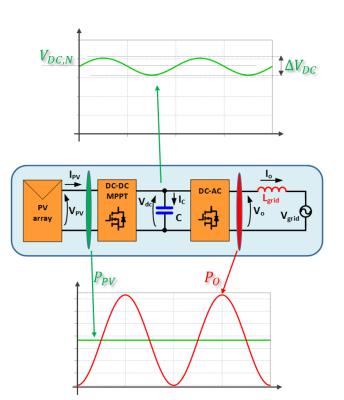

| 4.1   | Sh                        | ort introduction on solar energy conversion                           | 83   |

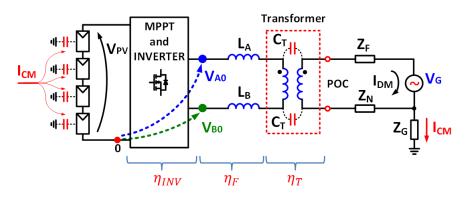

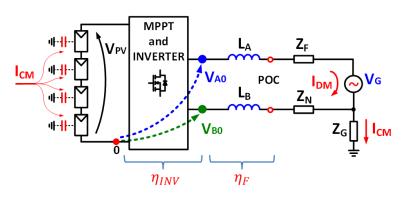

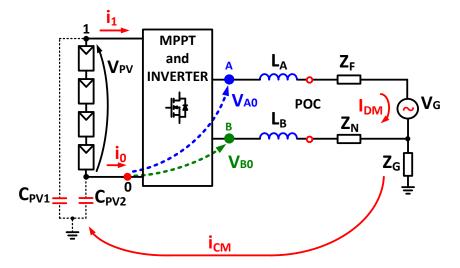

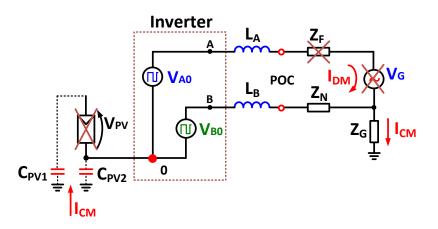

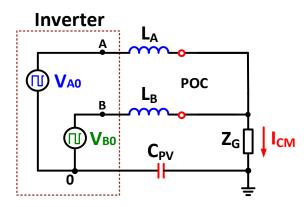

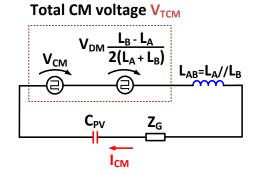

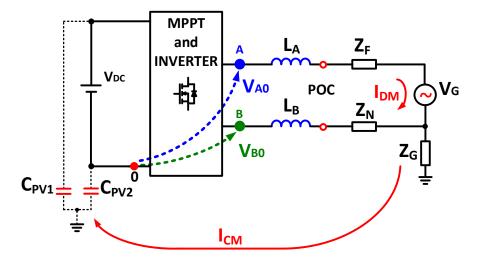

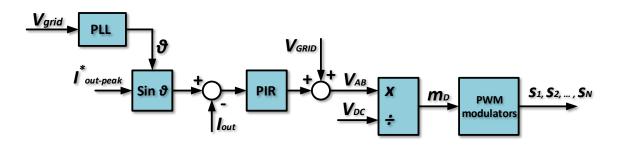

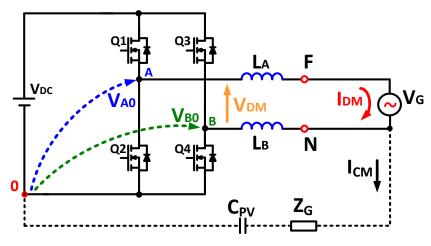

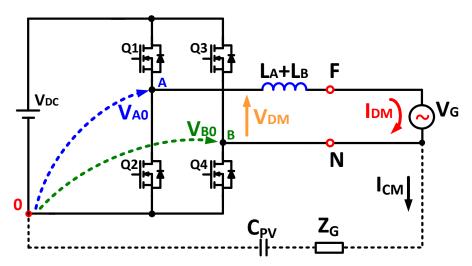

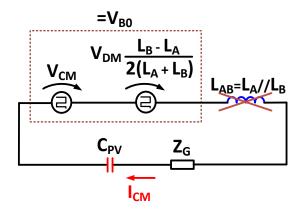

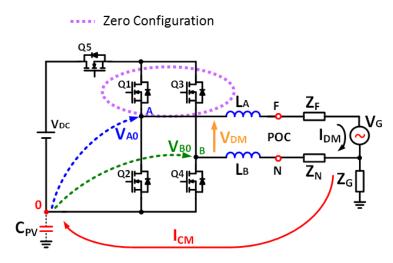

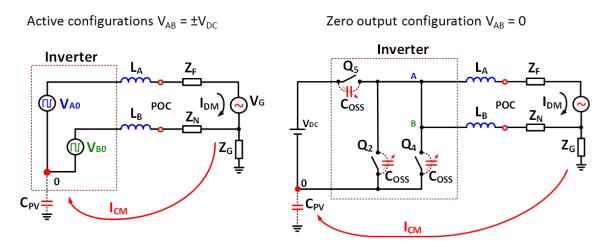

| 4.2   | Co                        | mmon mode model of single-phase transformerless inverters             | 87   |

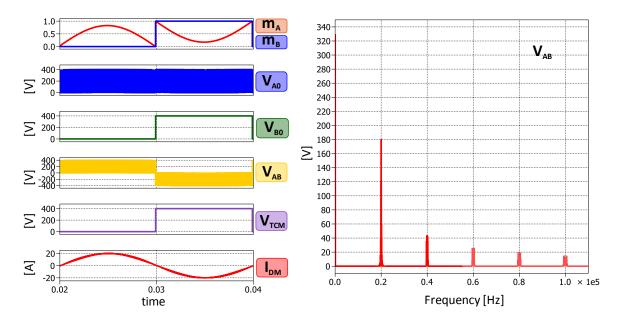

| 4.3   | Sir                       | ngle phase transformerless inverters derived from full cridge convert | er91 |

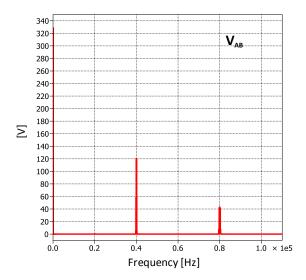

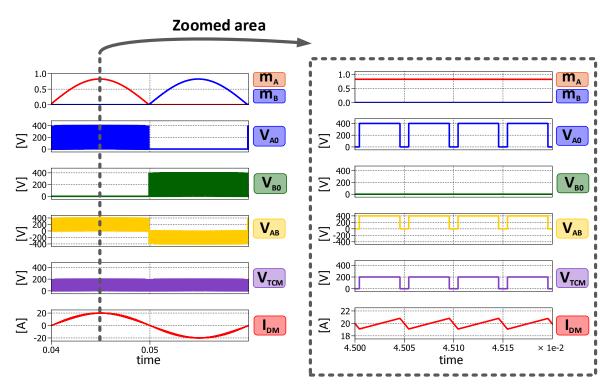

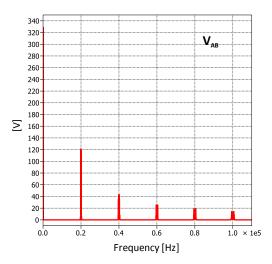

| 4     | .3.A                      | Full bridge converter (H4)                                            | 94   |

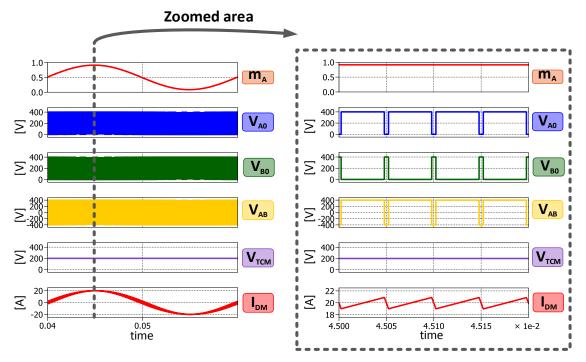

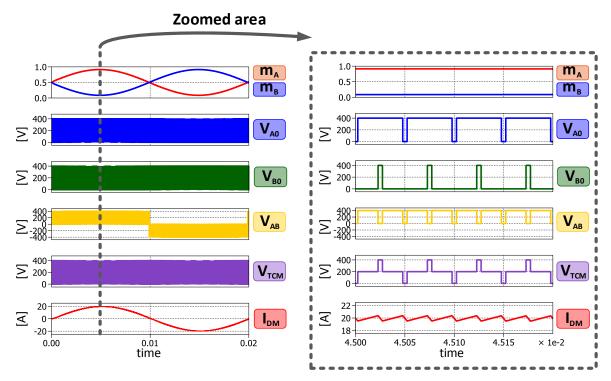

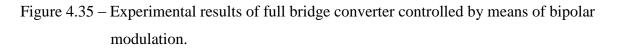

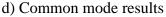

|       | Bipo                      | lar modulation                                                        | 95   |

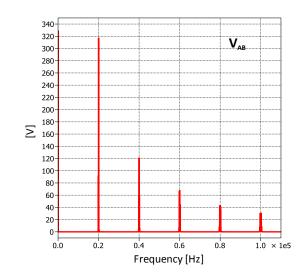

|       | Unip                      | olar modulation                                                       | 98   |

|       | Disco                     | ontinuous modulation                                                  | 101  |

|       | Hybr                      | id modulation                                                         | 104  |

| 4     | .3.B                      | H5 converter                                                          | 107  |

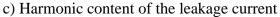

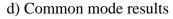

| 4     | .3.C                      | H6 converter                                                          | 110  |

| 4     | .3.D                      | H6 converter – unipolar modulation                                    | 114  |

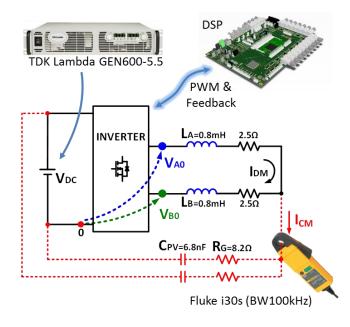

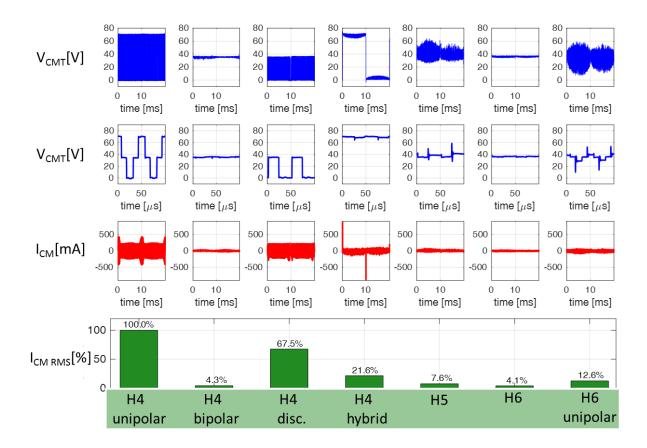

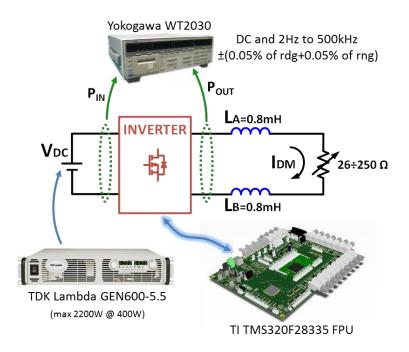

| 4.4   | Ex                        | perimental results                                                    | 116  |

| 4     | .4.A                      | Design of a H6 converter                                              | 116  |

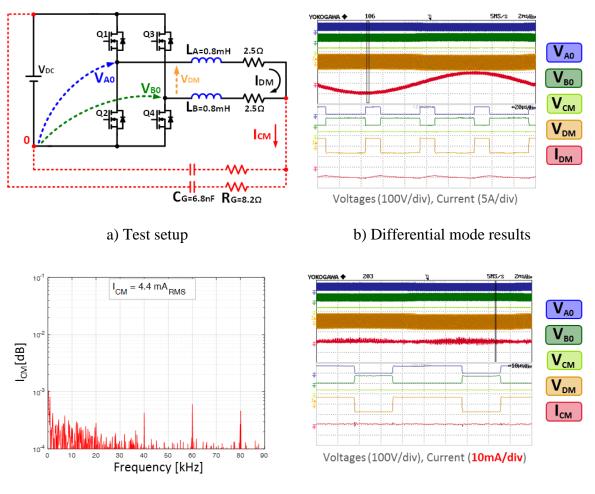

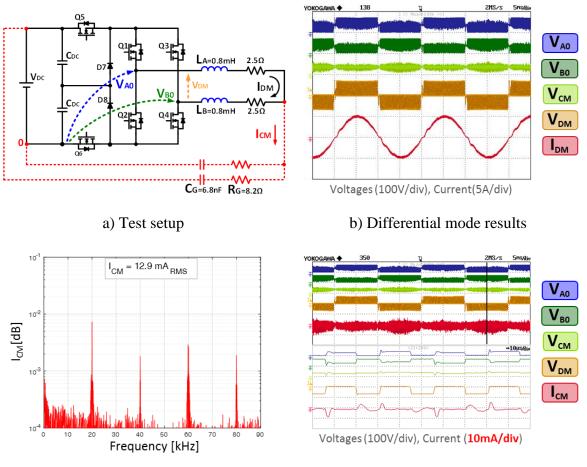

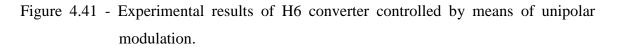

| 4     | .4.B                      | Leakage current test                                                  | 118  |

|       | H4 c                      | onverter with bipolar modulation                                      | 120  |

|       | H4 c                      | onverter with unipolar modulation                                     | 121  |

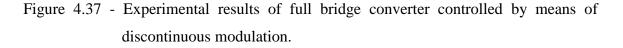

|       | H4 c                      | onverter with discontinuous modulation                                | 122  |

|       | H4 c                      | onverter with hybrid modulation                                       | 123  |

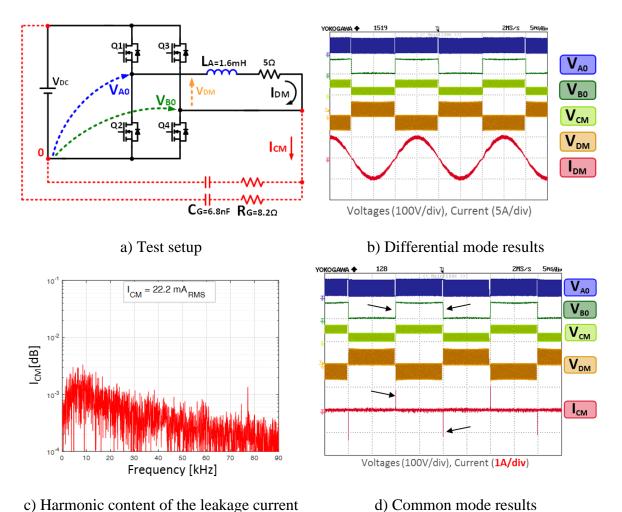

|       | H5 c                      | onverter                                                              | 124  |

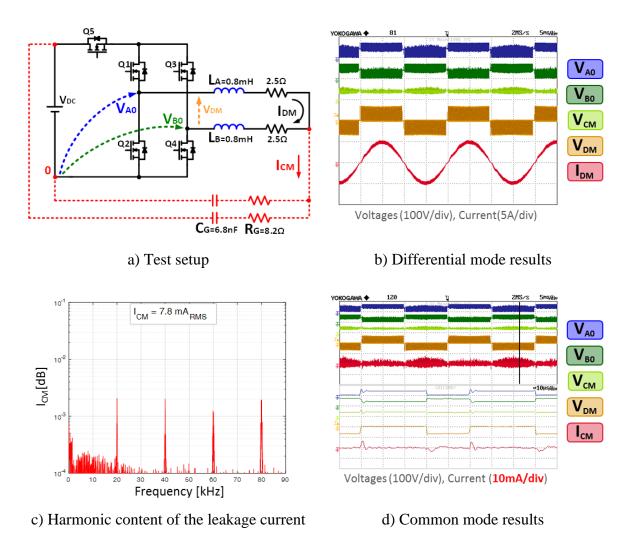

|       | H6 c                      | onverter                                                              | 125  |

| H6 converter with unipolar modulation      |     |

|--------------------------------------------|-----|

| Leakage current comparison                 |     |

| 4.4.C Efficiency tests                     |     |

| H4 converter with unipolar modulation      |     |

| H4 converter with discontinuous modulation |     |

| H4 converter with hybrid modulation        |     |

| H5 converter                               |     |

| H6 converter                               | 136 |

| H6 converter with unipolar modulation      |     |

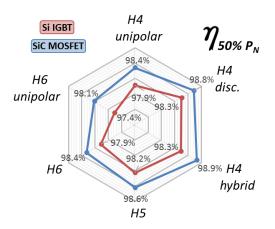

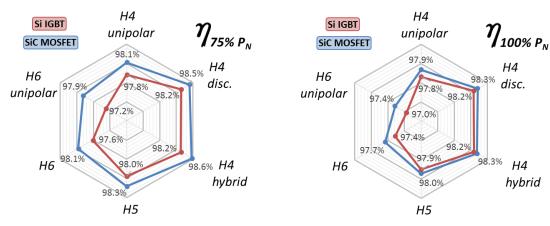

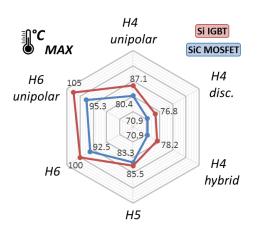

| Efficiency comparison                      |     |

| Conclusions                                | 141 |

| References                                 |     |

This page was intentionally left blank.

# Preface

DC to AC converters are widely used in industrial applications, such as motor drives, harmonic compensators, active filters and inverters for renewable energy systems.

Efficiency of motor drives is often sacrificed in order to lower the price of the converters and to increase the power density of the systems. The development of power converters for renewable energy generation, instead, is mainly driven by efficiency requirements. Higher cost of the converters is in fact paid back by energy efficiency policies, and by larger energy production over the long term.

Silicon-based power devices have dominated power electronics applications over the last decades. Research and development in microelectronics have pushed the performance of power devices to face some fundamental limitations of silicon material. Wide bandgap semiconductors, such as silicon carbide, offer a solution to the pressing performance requirements of power electronic systems. Silicon carbide power devices can operate at higher temperatures, higher frequencies, and generate less power losses as compared to traditional silicon-based technologies. In the last few years, several silicon carbide devices have become commercially available on the market at reasonable cost, thereby offering great benefits for efficiency demanding applications.

The use of wide bandgap transistors, however, is not the only way to increase the efficiency of the converters. Special DC to AC topologies, named soft switching converters, can be adopted as well in order to reduce the switching losses of transistors. Several soft switching inverters and control strategies have been proposed in literature. The price that has to be paid to increase the efficiency, is a greater hardware and control complexity the converter.

The aim of this thesis is the development of DC to AC power converters for applications requiring high efficiency. Silicon and silicon carbide based inverters, as well as soft switching inverters, have been analyzed and fabricated for performance comparison.

The dissertation is organized as follows.

Chapter 1 presents the state of art on silicon and silicon carbide power devices.

Chapter 2 explores the power loss generation in power switches.

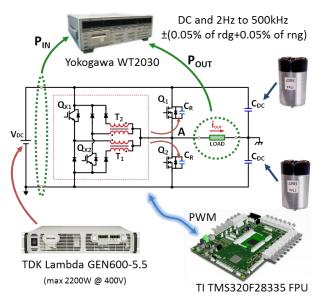

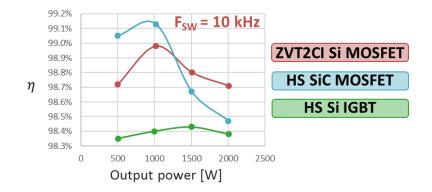

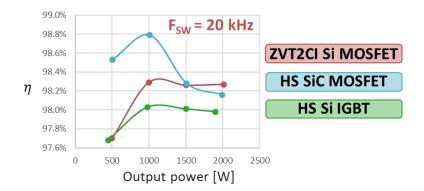

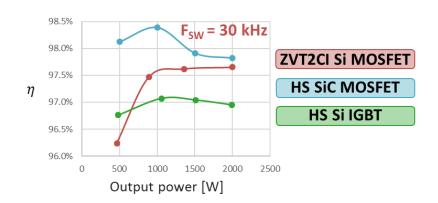

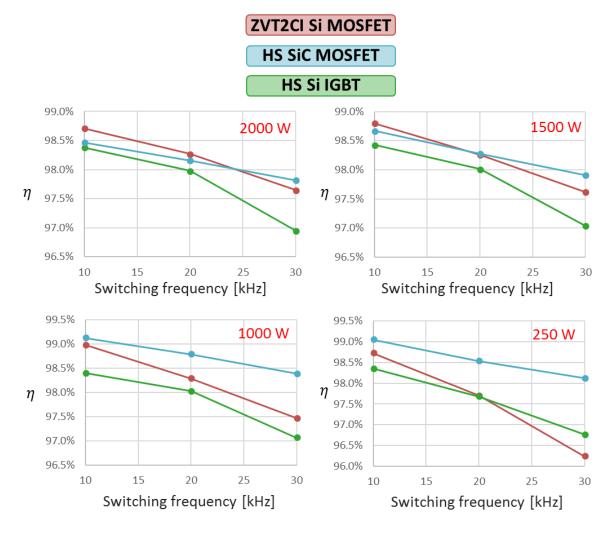

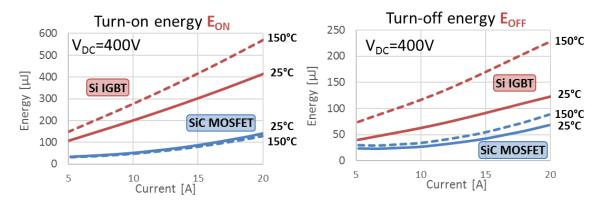

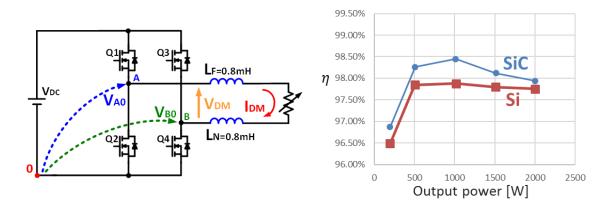

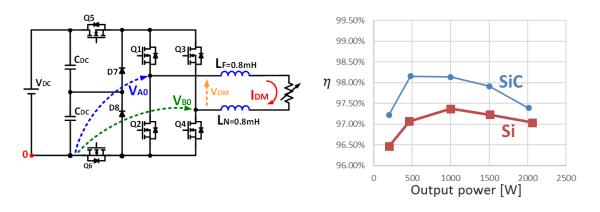

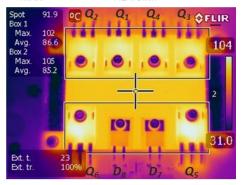

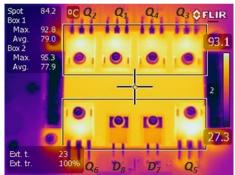

Chapter 3 presents a topology review of DC/AC soft switching converters. Particular attention is given to the operating principle and to the design guide lines of the Zero Voltage Transition converter with Two Coupled Inductors (ZVT2CI). The performances of a ZVT2CI prototype are compared to that of hard switching converters, based on latest silicon and silicon carbide technologies.

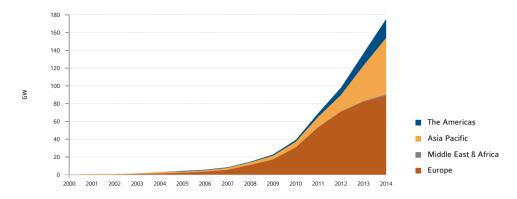

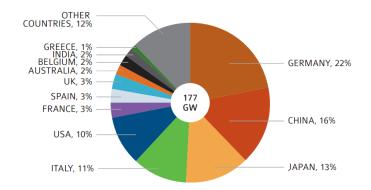

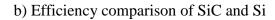

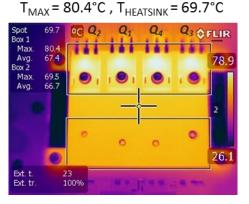

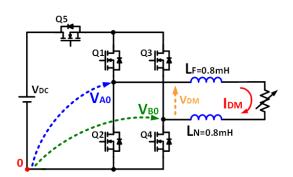

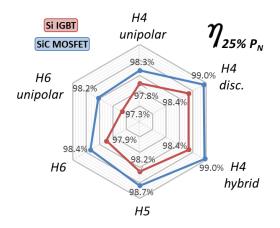

Chapter 4 explores inverter topologies for low power, single phase photovoltaic (PV) systems. In the first part of the chapter is presented the diffusion of photovoltaic systems in Italy and a review on the requirements for grid connected distributed generators. Particular attention is then given to the leakage current issue in transformerless PV system and to inverter topologies that can mitigate the problem. Eventually, the experimental performances of two single-phase transformerless inverters are presented, one built using high performance silicon switches, and one using high switching speed silicon carbide devices.

The last chapter presents a summary of the results obtained during the Ph.D. research activity.

# Chapter 1

# Trends in Power Transistors Technology

## 1.1 State of the art of silicon transistors

Efficiency of power electronic systems is strongly related to advances in power semiconductor technologies since large portion of the losses are dissipated by power transistors and diodes. Semiconductor power device technologies have evolved over the last decades improving the efficiency and lowering the cost of power converters [1].

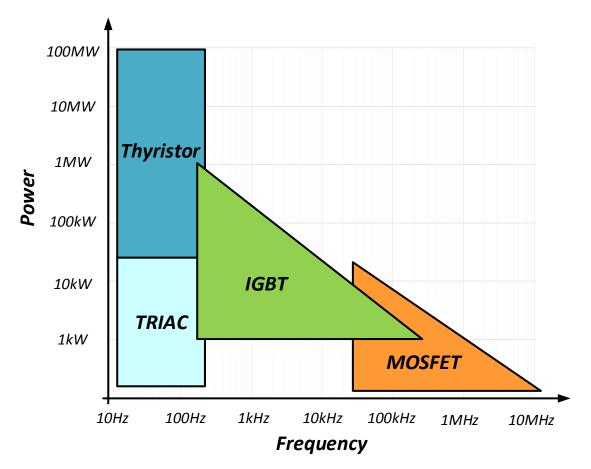

Figure 1.1 - Application of discrete power semiconductors.

Nowadays, power converters are mainly based on the mature and reliable silicon technology [2]. Power devices can be classified in two categories: controlled power switches and rectifiers. The controlled device family can be further divided in bipolar-based devices,

FET-based devices and devices, such as the IGBT, that combine a bipolar and a FET transistor.

Bipolar devices such as BJTs (Bipolar Junction Transistor), MCTs (Metal-Oxide Controlled Thyristor), GTOs (Gate Turn-off Thyristor) and IGCTs (Insulated Gate Controlled Thyristor) were the only power switches available before 80s [3]. The earlier power converter topologies of the silicon transistor era, e.g., bridge controlled rectifiers and cycloconverters, were developed around the characteristics of thyristors. The first real fully controllable power switch was the BJT. However, its slow turn-off characteristics (tail current) and the complexity required for the base driver circuitry, limited the diffusion of BJTs to low power and low frequency applications. Nowadays only IGCTs are still used, since they are the only feasible option for high voltage, for high power applications such as HVDC power stations and static synchronous compensators (STATCOMs) [4].

The commercial availability of power MOSFETs in the 70s, and IGBTs in the 80s represented an important breakthrough in power semiconductor device technology [5]. These new devices replaced bipolar transistors and thyristors for industrial applications, allowing the development of efficient power electronic systems.

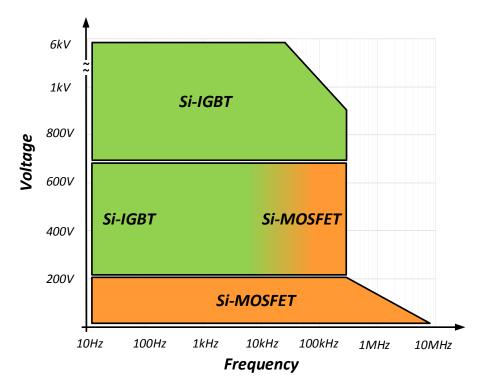

The aim of this thesis is the development of DC to AC power converters for applications requiring high efficiency, such as photovoltaic inverters, motor drives, active filters and harmonic compensators. For these applications, the typical DC voltage level is in the range from 400Vdc to 800Vdc. As can be seen in Figure 1.2, IGBTs are the only feasible choice for applications above 1000V, while MOSFETs are the best devices for applications below 200V. In between 200V to 1000V the choice between IGBT and MOSFET is application dependent [6]. Requirements on cost, size, speed, reliability and efficiency contribute to select of the most suitable device.

Figure 1.2 - Typical MOSFETs and IGBTs selection as a function of blocking voltage and switching frequency.

## 1.1.A Power MOSFETs

More than 30 years of research and development in microelectronics have led to silicon power switches with outstanding electrical performances, several classes of devices were developed following the requirements demanded by different kind of converter topologies.

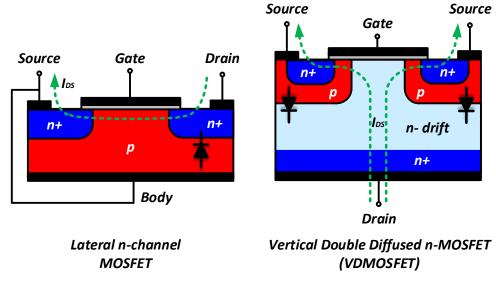

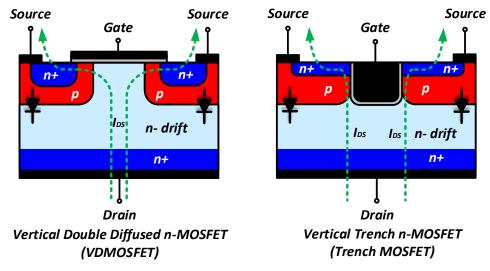

Figure 1.3 – Lateral and vertical MOSFET structures.

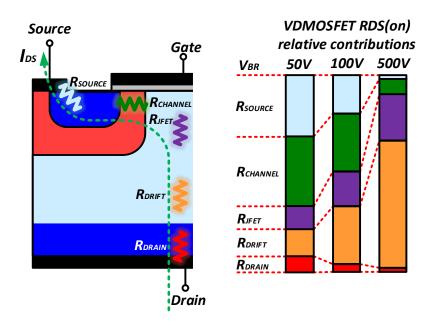

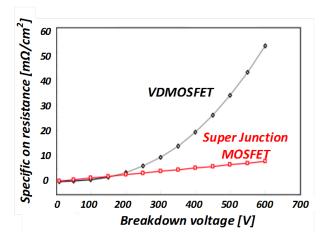

The earlier power MOSFET developed was a lateral device since, as depicted in Figure 1.3, the current flows along the plane of the device from the drain to the source. Lateral MOSFET have low on-resistance since the current flows in highly doped silicon region, however, the length of the channel increases with the increase of blocking voltage capability of the device, requiring larger silicon area [7]. For economic and power density reasons, the lateral MOSFET structure was replaced by the Vertical Double Diffused MOSFET (VDMOSFET). In this device, as can be observed in Figure 1.3, the current flows vertically from the top to the bottom through the silicon wafer [8]. The VDMOSFET structure includes an intrinsic body diode, therefore the operation in the first and in third quadrants of the V-I characteristic is allowed without the need of an external freewheeling diode. The drift region is a low-doping region of the MOSFET, which is required to support the block voltage when the device is off. Its thickness increases as the break down voltage  $(V_{BD})$  rating of the device increases. As can be seen in Figure 1.4, for high voltage VDMOSFET the main contribution to the on state resistance is due to the drift region, therefore, the only way to reduce the overall on-resistance is to use larger silicon area, increasing the cost of the device. The minimum contribution of the drift region to the specific on-resistance per surface unit  $(R_{ON-SP})$  is proportional to  $V_{BD}^{2.5}$ , which is known as 1D-Silicon limit of power MOSFETs [9]:

$$R_{ON-SP} = 6 \cdot 10^9 \, V_{BD}^{2.5} \, [\Omega/_{mm^2}]. \tag{1.1}$$

Another weakness of power MOSFETs is the fact that, as the voltage rating increase, the reverse recovery characteristics of the parasitic body diode deteriorates causing the increase of switching losses [10]. For the technical and economic reasons above, power MOSFETs are hardly ever selected for applications above 200V.

VDMOSFET layout is still used today, power transistor companies have invested resources to improve the dynamic behavior of the device and to increase its power density. At the same pace of the improvement in VDMOSFET technology, other device structures were born in response to the demand of devices specifically optimized for low voltage and high voltage applications.

Figure 1.4 - Contribution to the on state resistance of a VDMOSFET as function of the blocking voltage

The trench gate MOSFET was introduced in order to reduce the conduction losses of the transistor in low voltage applications. As depicted in Figure 1.5, the gate of the trench MOSFET does not lay on the surface of the chip like in VDMOSFET, but it expands vertically inside the wafer. For this device, the induced channel in the P well region in the on-state is arranged vertically, so that the overall distance covered by the electrons is shorter than in the case of VDMOSFET. This solution reduces significantly the  $R_{DS(on)}$  of the transistor [11].

Figure 1.5 – VDMOSFET and trench MOSFET structures.

Regarding high voltage MOSFETs, a breakthrough in the technology was the introduction in the late 90's of a device structure that broke the 1D-limit of power MOSFETs [12]. The concept was based on the charge compensation effect, known as super-junction principle [13], a special structure that allows a significant reduction of the drift region resistance. Super-junction power devices were commercially introduced in 1998 by Infineon (CoolMOS) [14], and are now available from 500V to 900V. The theoretical  $R_{ON-SP}$  limit of VDMOSFETs and SJ MOSFETs are depicted in Figure 1.6. It can be seen that the super junction technology can potentially achieve higher power density than VDMOSFET. However, super junction MOSFETs, for physical reasons, are more prone to have a low performance body diode. In DC to AC inverter topology i.e. half bridge, full bridge and three phase inverter, the presence of the freewheeling diode in parallel to the transistor is essential for the proper operation of the converter. Several applications reported the failure of the transistors under hard turn off of the diode due to its reverse recovery characteristic [15] [16] [17]. As reported in the section 2.2, for half bridge-based converters under inductive load, the reverse recovery current of the diodes increases the turn-on losses of the power transistor and is seen as a temporary shoot-trough of the DC source.

Figure 1.6 – 1D-Silicon limits of VDMOSFETs and SJ MOSFETs

Although SJ MOSFETs are hardly ever selected for DC to AC inverters, they are widely used in DC to DC power conversion. In topologies such as buck, boost, PFC and Flyback the body diode never conducts, so all the benefits of the power MOSFETs can be exploited.

#### 1.1.B Power IGBTs

The technological evolution of the power transistors has affected also IGBTs family. During the last two decades significant advances were achieved in the fabrication of IGBTs.

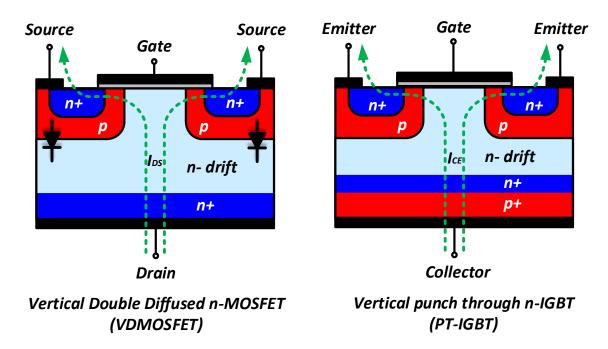

Figure 1.7 – Comparison of the structure of a VDMOSFET and of a PT IGBT.

The basic layouts of a power MOSFET and of a IGBT look very similar. The cross section of the firstly commercialized Punch Through (PT) IGBT and the one of the VDMOSFET are depicted in Figure 1.7. It can be notice that an IGBT is a power MOSFET with the addition of a P layer under the N substrate. However, in spite of the similarity, the physical operation of the IGBTs is closer to that of bipolar transistors rather than that of power MOSFETs. During the on-state, the P layer injects holes into the highly resistive n- drift layer increasing its conductivity. The overall effect is the reduction of the on-state voltage drop of the device. For this reason, IGBT is sometimes called conductivity modulated metal oxide field effect transistor [18]. For the reasons above, the IGBT merges the high current handling capability of a bipolar transistor with the ease of control of a MOSFET.

Another important characteristic of IGBTs is the absence of a parasitic body diode typical of MOSFETs. This feature gives the freedom and the flexibility to choose an external fast recovery diode to match the target application [19].

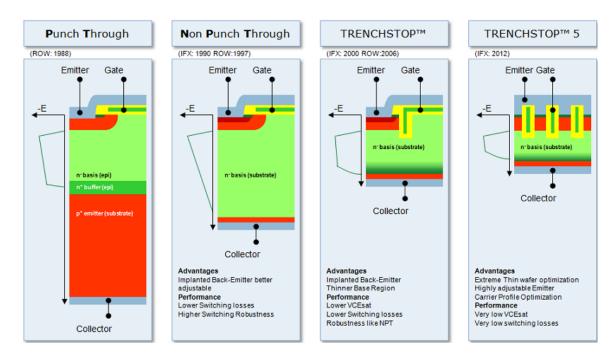

Figure 1.8 - Evolution of Infineon IGBTs, from Punch Trough to TRENCHSTOP™ 5 technology

Early versions of IGBTs suffered severe limitations. First of all, they could potentially loose ability to be turned-off (latch up) in some dynamic conditions [20], furthermore, the negative temperature coefficient of IGBTs made the parallel operation of devices hard to achieve [21]. The problems above are no longer present for the latest generations of IGBTs, moreover, improvement in the switching performances have narrowed the gap between IGBTs and MOSFETs. Figure 1.8 compares the cross sections of different IGBT technologies, namely planar Punch Through (PT), planar Non Punch Through (NPT), Trench Field Stop, and their historical introduction on the market [22].

### 1.2 Wide bandgap materials – Silicon Carbide

The development of power semiconductor devices has always been a driving force for power electronics systems. For a long time, silicon-based power devices have dominated the power electronics applications [23]. As the needs and requirements for electric energy continuously grow nowadays, silicon devices are coming to face some fundamental limits in performance due to the inherent limitations of silicon material properties. Wide bandgap materials, such as Silicon Carbide (SiC) offer a long term solution to the pressing requirements on dynamic performance and efficiency requirements of power electronic systems [2] [24] [25] [26] [27].

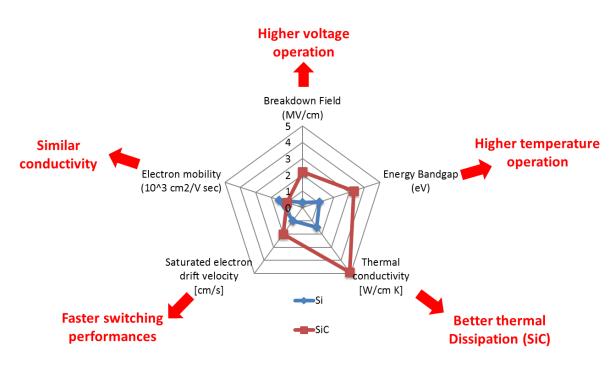

In a solid material, electrons exist at energy levels that combine to form energy bands [28]. The top level band is called the conduction band and the lower is called valence band. The region between the valence band and the conduction band is a forbidden state where ideally no electron exists. If the electrons in the valence band are excited externally, they can jump to the conduction band. For a conductor, like copper, the forbidden band does not exist and the energy bands overlap completely. For an insulator, on the other hand, this band is so wide that the electrons need large amount of energy to move from the valence band to the conduction band. For the semiconductors conversely, the forbidden gap exists and is smaller than that of an insulator. At a certain temperature, electrons have enough energy to move spontaneously to the conduction band, this generate an uncontrolled conduction mode that must be avoided. In silicon transistors, the temperature at which the devices start to behave like a conductor is around 170°C. Wide bandgap semiconductors have the advantage of high temperature operation as the thermal energy required to promote electrons in the valence band is higher than the one of silicon materials (1.12 eV). The energy bandgap level is not the only propriety that make SiC superior material for power electronics devices. The main physical property of Si and SiC semiconductors are reported and compared in Table 1.1.

Table 1.1 - Material properties of silicon and silicon carbide.

| Property                                                 | Si  | SiC |

|----------------------------------------------------------|-----|-----|

| Breakdown Field (MV/cm)                                  | 0.3 | 2.2 |

| Energy Bandgap (eV)                                      | 1.1 | 3.3 |

| Thermal conductivity [W/cm K]                            | 1.5 | 4.9 |

| Saturated electron drift velocity<br>[cm/s]              | 1   | 2   |

| Electron mobility $(10^{3} \text{ cm}^{2}/\text{V sec})$ | 1.5 | 1   |

Figure 1.9 - Material properties of silicon and silicon carbide.

As can be seen in Figure 1.9, SiC presents greater thermal conductivity, higher critical electric field, higher saturated electron drift velocity, and slightly lower electron mobility than Si [29].

SiC offers a critical electric field that is more than seven times higher than Si. This property increases the voltage blocking capability of power devices and allows the reduction of the drift layer thickness of power MOSFETs, reducing significantly the on-state resistance. Furthermore, the higher thermal conductivity of SiC makes it superior to Si in terms of heat dissipation, while the wider bandgap energy (3.3 eV) allows high-temperature operation above 300 °C. The superior electron drift velocity also makes SiC devices capable of extremely fast commutation.

Infineon Technologies and Cree Inc. introduced the first commercial SiC power devices in 2001 and 2002, which were 600V SiC Schottky diodes [30], [31]. Schottky diodes are majority carrier devices, therefore they do not exhibit the reverse recovery phenomena, a very favorable characteristic for high-voltage applications [32]. SiC technology extended the breakdown voltage of Schottky diodes above 1000 V, which was previously limited below 200 V for Si technology. Another important characteristic of the SiC Schottky diodes is their positive thermal coefficient, which allows a stable parallel connection of diodes in order to handle high currents. The success of the SiC Schottky diodes pushed the development and commercialization of the first junction field-effect transistor (JFET) by SemiSouth Laboratories in 2008 [33]. In 2011, three years after the release of the SiC JFET, Cree commercialized the first SiC Vertical Double Diffused MOSFET (SiC VDMOSFET) [31].

Figure 1.10 - History of the commercialization of SiC devices.

Today, several manufacturers produce SiC MOSFETs, including General Electric (GE), ROHM Semiconductor, Mitsubishi Electric, Microsemi, GeneSiC, and United Silicon Carbide. In 2012 the first SiC bipolar junction transistor (BJT) was presented by Fairchild [34].

SiC PN diodes [35], IGBTs [36] and thyristors [37] are still under development, and are targeted at high voltage systems (> 10 kV).

# Chapter 2

# Power Loss Mechanism in Power Transistors

### 2.1 Introduction

Understanding the power loss mechanism of power transistor is essential for the development of efficient power converters.

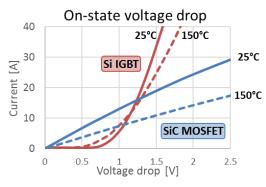

Device losses can be divided in two main contributes, the conduction losses and the switching losses [10]. Conduction losses are defined as the energy dissipated by a transistor or diode is in the conduction state (on-state). This loss contribution is related to the static characteristic of power switches, i.e., unipolar and bipolar devices but is independent to the switching frequency of the converter. As described in the previous chapter, many generations of MOSFETs and IGBTs have been developed during the last 30 years with the aim of the reduction of the forward voltage drop.

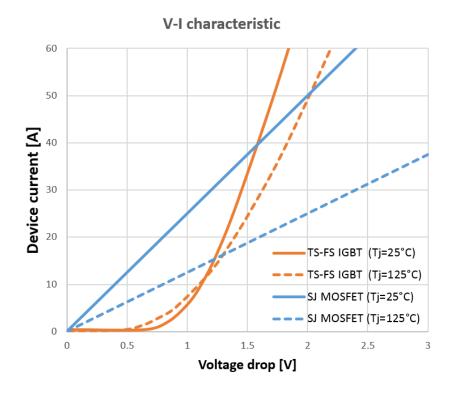

Figure 2.1 – V-I characteristic two typical 650 V IGBT and SJ MOSFET rated for the same current

Chapter 2

Generally, power MOSFETs have a linear forward voltage drop whereas IGBTs, being bipolar devices, show a diode like exponential characteristic. For example, the forward characteristics of two best in class devices are reported in Figure 2.1; the first is a 650V, 40A trench-field stop IGBT (TS-FS IGBT) and the second is a 650 V, 40A, 40 m $\Omega$  Super Junction MOSFET (SJ MOSFET). It can be seen that the two 25°C characteristics match at 40A. Below the nominal current, the voltage drop of the MOSFET is lower than the voltage drop of the IGBT, making the device more efficient during low load conditions. On the other hand, the forward characteristic of the MOSFET deteriorates more than the one of the IGBT when the junction temperature is 125 °C, making the IGBT more suitable for overload and high temperature operations.

The choice of the best device suited for the target application cannot be done only on the basis of the conduction behavior, switching losses must be considered as well. Switching losses are defined as the energy dissipated by the device during the transition from the on-state to the off-state, and vice versa, due to the overlap of the applied voltage and the conducted current.

In first analysis, switching losses depend on the dynamic performance of the devices, on the voltage applied in the block state, on the switching frequency and on the converter topology. Several families of MOSFETs and IGBTs have been developed with the aim of reducing the conduction losses, switching losses or a tradeoff of them.

### 2.2 Losses in AC to DC power converters

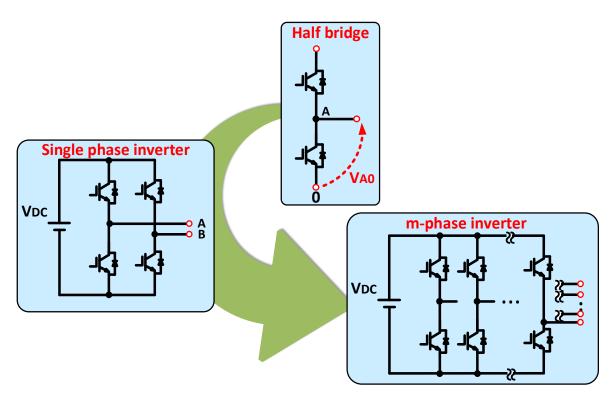

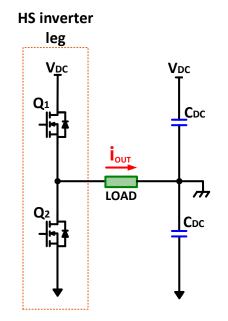

The world most diffused architectures of DC to AC power conversions are based on the half bridge two levels converter, also known as inverter leg, which consists of two power transistors in a totem pole configuration [10]. Single phase, three phase and, more in general *m*-phase DC to AC two level converters can be obtained connecting together *m* inverter legs, as illustrated in Figure 2.2.

Figure 2.2 – multi phase DC/AC converters based on the half bridge leg.

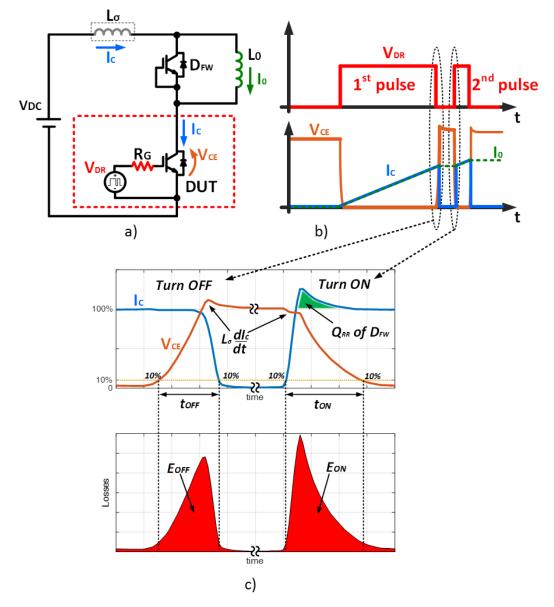

The half bridge topology, controlled by pulse width modulation (PWM), is widely adopted in industrial applications, especially with an ohmic-inductive load connected to the output. In this configuration, during the switching transient, the output inductance maintains nearly constant the load current, which commutates from a transistor to the complementary freewheeling diode and vice versa. Since this commutation mechanism is the most diffused operation mode in power electronics converters, manufactures provide the turn on and turn off losses of their transistors using a simplified operation of the half bridge under inductive mode operation, called double pulse tester (DPT) [38]. Basically the double-pulse tester is an inductive load buck converter, containing one device under test (DUT), one freewheeling diode (usually the same diode endowed in the DUT) and a load inductor (See Figure 2.3).

A two pulse train is sent to the gate of the DUT, the widths of both pulses and the interval in between them is adjustable.

During the first pulse,  $V_{DC}$  is applied to the inductor  $L_0$  and current  $I_0$  rises linearly:

$$\frac{dI_0}{dt} = \frac{dI_C}{dt} = \frac{V_{DC}}{L_0}.$$

(2.1)

Since in this condition the load current flows through the DUT, the duration of the fist gate pulse  $T_1$  is adjusted in a way to obtain the desired value for the current  $I_{CTEST}$ :

$$T_1 = \frac{L_0 \ I_{C \ TEST}}{V_{DC}}.$$

(2.2)

The falling edge of the first pulse corresponds to the turn off of the device, then the turn off switching energy  $E_{OFF}$  at the current  $I_{C TEST}$  and voltage  $V_{DC}$  can be evaluated.

Figure 2.3 – Switching characterization test power switches. a) double pulse tester. b) gateemitter voltage, collector-emitter voltage and collector current of the DUT. c) switching waveforms during turn-on and turn-off.

Between the fist and the second gate pulse, the load current flows through the top freewheeling diode  $D_{FW}$  and remains nearly unchanged at the value  $I_{C TEST}$ . The rising edge of the second pulse corresponds to the turn on of the device at current  $I_{C TEST}$  and voltage  $V_{DC}$ , then turn on switching energy  $E_{ON}$  can be evaluated.

The typical voltage and current switching waveforms of a power switch in the DPT are depicted in Figure 2.3. The turn-on time  $t_{ON}$  is defined as the time between the moment at which the conducted current ( $I_C$ ) rises to 10% of the  $I_{C TEST}$  current to the moment at which the applied voltage ( $V_{CE}$ ) falls to 10% of the steady state blocking voltage  $V_{DC}$ . The turn-off time  $t_{OFF}$  is defined as the time from the moment at which the applied voltage ( $V_{CE}$ ) rises to 10% of the steady state blocking voltage ( $V_{CE}$ ) rises to 10% of the steady state blocking voltage ( $V_{CE}$ ) rises to 10% of the steady state blocking voltage ( $V_{CE}$ ) rises to 10% of the steady state blocking voltage  $V_{DC}$  to the moment at which the conducted current ( $I_C$ ) falls to 10% of the test current  $I_{C TEST}$ . The turn-on switching energy  $E_{ON}$  and the turn-off switching energy  $E_{OFF}$  are defined as the integrals of the product of  $V_{CE}$  and  $I_C$  over  $t_{ON}$  and  $t_{OFF}$  respectively.

The switching speed of the transistor, i.e.,  $\frac{dI_C}{dt}$  and  $\frac{V_{CE}}{dt}$ , can be varied, within the safe operation limits of the device, changing the value of the gate resistance  $R_G$ . Faster switching speed reduces the overlap time of  $V_{CE}$  and  $I_C$ , hence, reducing the switching losses.

The junction temperature  $T_j$  of the DUT influences the switching energy as well. The DUT junction temperature during the test can be regulated by using a temperature controlled heatsink.

It's important to mention that the reverse recovery charge  $Q_{RR}$  of the freewheeling diode takes part to the switching loss generation increasing the carried current of the DUT during the turn on. Silicon Fast Recovery Diodes (FREDs) are usually chosen as a freewheeling diode of IGBTs due to their low reverse recovery charge. In the case of Si-MOSFET, the freewheeling diode coincides with the intrinsic parasitic body diode. However, the reverse recover performance of the body diode of MOSFETs degrades as the voltage rating increases. For high voltage MOSFETs ( $V_{BD} > 250V$ ), the reverse recover characteristics of the body diode is usually so poor that the transistor can easily fail due to the excessive heat generation. The introduction in 2001 of the first 600V zero reverse recovery charge SiC Schottky diode made possible the fabrication of hybrid Si-IGBT + SiC-Schottky devices for efficiency demanding applications. Differently from silicon SJ MOSFETs, silicon carbide MOSFETs counterpart are suited for the operation in totem pole configuration since the parasitic body diode has dynamic behavior similar to a FRED diode.

Another important parameter that affects the switching losses of the DUT is the parasitic inductance in the power loop of the double pulse tester. The DUT current  $I_c$  flows also through the stray inductance  $L_{\sigma}$ , increasing the transient blocking voltage on the DUT at the turn on  $(L_{\sigma} \frac{dI_D}{dt} > 0)$  and reducing the applied voltage at the turn off  $(L_{\sigma} \frac{dI_D}{dt} < 0)$ , therefore increasing  $E_{OFF}$  and reducing  $E_{ON}$ .

In fist approximation, switching losses of a transistor operating in a half bridge configuration are function of:

$$E_{sw} = f(V_{DC}, I_C, R_G, T_j, L_{\sigma}, Q_{RR}).$$

(2.3)

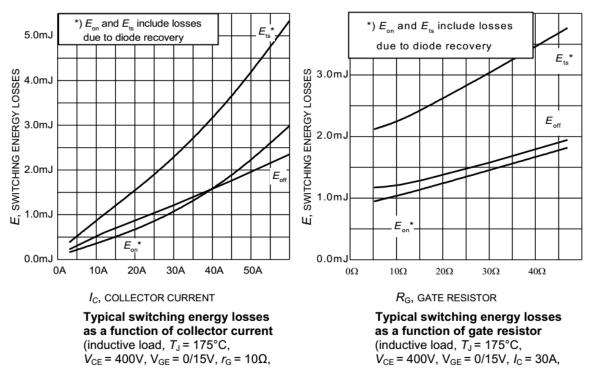

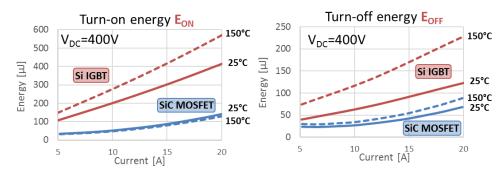

Device manufacturers provide in the datasheet of their devices the switching energies obtained in the DPT, varying the key parameters that influence the switching losses i.e.,  $V_{DC}$ ,  $I_C$ ,  $R_G$  and  $T_j$ . The switching losses obtained in the DPT of a commercial IGBT (Infineon IKW30N60T) are depicted in Figure 2.4 and Figure 2.5.

Figure 2.4 – Switching energies of the IGBT Infineon IKW30N60T as function of collector current (left figure) and of gate resistance (right figure)

Figure 2.5 - Switching energies of the IGBT Infineon IKW30N60T as function of the junction temperature (left figure) and of collector-emitter voltage (right figure)

In half bridge based converters, given the switching frequency and the modulation technique, the only way to reduce the switching losses is to select fast transistors, low reverse recovery diodes and minimize the parasitic inductance of the power loops.

Topologies in which power losses are generated during the turn on and off of the transistors are called hard switching converters, all the DC to AC converters based on the 2L half bridge topology are part of the hard switching family.

A different way to improve the overall efficiency of AC to DC power converters is to use topologies that reduce the switching losses, avoiding the simultaneous presence of high voltage and high current during the commutation of the transistors. Such kind of topologies are called soft switching converters [10].

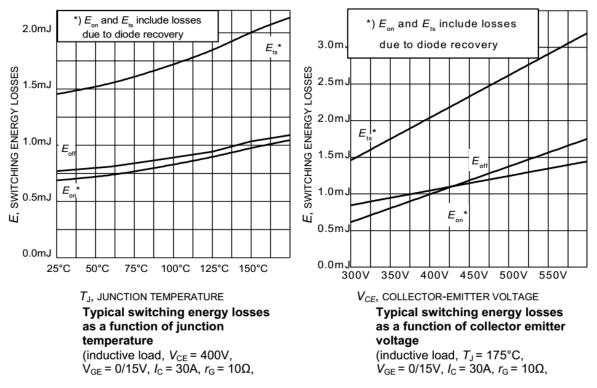

Switching trajectory is a graphical way to see the switching behavior of a transistor by superimposing the voltage  $V_{CE}$  and the current  $I_C$  in a X-Y plot. The switching trajectories of the DUT previously presented in Figure 1.1, are depicted on the left side of Figure 2.6. It can be clearly seen that hard switching commutations appear as rectangular square trajectories. The soft switching locus in the  $V_{CE}$ - $I_C$  plane instead, appear completely different. As can be

seen in the right side of Figure 2.6, the transition from the on state to the off state and vice versa moves along the axes of the graph, avoiding then the overlap of high voltage and high currents i.e. reducing the switching losses.

Figure 2.6 – Comparison of hard and soft switching trajectories.

Inevitably, to archive the soft switching operation, the complexity of the converter is increased when compared to a standard hard switched inverter.

Power electronic designers are called to choose the converter topology and select power devices that can satisfy the constraints on cost, efficiency, performance and power density of the converter. For applications requiring high efficiency, the higher complexity and cost of a soft switching converter can be justified only if the overall efficiency is higher than the efficiency obtainable with a simpler structure, e.g., half bridge based converter, using the best power transistors available on the market.

Further details about soft switching converters are presented in chapter Chapter 3.

# Chapter 3

# Soft Switching in DC to AC Converters

### 3.1 Introduction

Developments in power electronics of the last two decades involved not only power switches, but also circuit topologies and control strategies. Since the 70s, the most diffused control technique for power converters is the Pulse Width Modulation (PWM). Ideally, power switches are operated only in two low-loss conditions, the interdiction state (fully off) and the saturated state (fully on). When a switch is in the off state and high voltage is applied to the device, practically no current is allowed to flow. Instead when the switch is on, the current can flow through the device with a very low internal voltage drop (<2 V). Power losses, being the product of voltage and current, are thus in both cases extremely low. However, during the commutation between the on-state and the off-state, transistors could be subjected to the simultaneous presence of high voltage and high current, which lead to high levels of power losses.

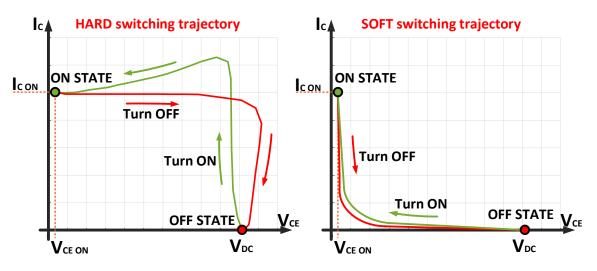

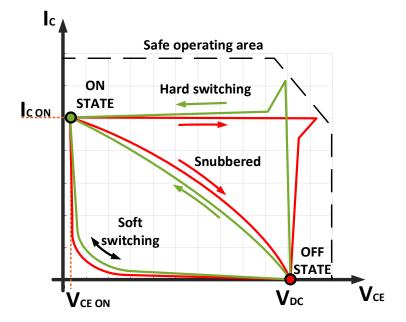

Converter topologies in which power losses are generated during the commutations are called *hard switching* converters.

Figure 3.1 – Comparison of typical hard, snubbered and soft switching trajectories of an IGBT or BJT.

A typical trajectory in ( $V_{CE}$ ,  $I_C$ ) plane of a switch, operated in hard switching conditions is shown in Figure 3.1 for an IGBT ( $V_{CE}$  is the collector-emitter voltage,  $I_C$  is the collector current). It is important to mention that the switching trajectory must be inside the Safe Operating Area (SOA) prescribed by the manufacturer for the device, operation outside this limit leads to the failure of the device. A possible solution to relieve the stresses of the component is the addition a snubber circuit (suppressor), which reduces the overlap of high values of current and voltage and consequentially the power dissipated by the device. However most snubber circuits divert the part of energy that would be dissipated by the transistor to an external dissipative circuit, e.g., RC snubber and RCD snubber, hence it is clear that the global efficiency of the system is not increased.

In the 80's, considerable research efforts were directed toward the use of resonant topologies to increase efficiency of converters [39]. The basic idea was to include reactive elements in converters, in order to induce sinusoidal oscillations that create the conditions for a zero-voltage (ZVS) or zero current (ZCS) switching of the transistors. This behavior corresponds, in the ( $V_{CE}$ ,  $I_C$ ) plane, to a switching trajectory that avoids the simultaneous presence of high voltage and high current. Such kind of topologies were firstly called *soft switching* converters. The drastic reduction of the switching losses and the technological improvement of the devices made possible to achieve switching frequencies of hundreds of kHz (typically 100-200 kHz). However, resonant converters had several drawbacks in comparison to conventional PWM converters, e.g., higher peak current and higher voltage and current rating. Furthermore, resonant converters where controlled by means of frequency modulations techniques (FM) rather than PWM, making this new class of converters more suited for DC to DC applications rather than for DC to AC inverters.

In the late 80s and during the 90s, new generations of soft-switching converters that combined the advantages of conventional PWM converters with those of resonant converters were proposed. Unlike full resonant converters, the resonance phase is used in a controlled way, during the on and off transition of the switches, creating the conditions for zero voltage and zero current switching. Apart from the resonant transition, these converters behaved like traditional PWM converters.

### 3.2 Overview of DC to AC soft switching inverters

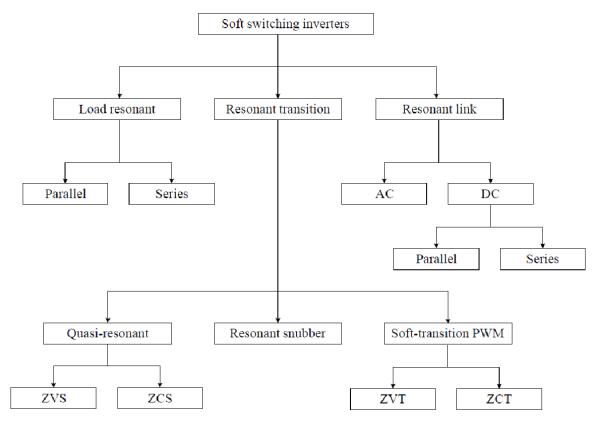

Soft-switching techniques offer a substantial reduction of the losses, allow high frequency operation and avoid the use of the dissipative snubbers. Many soft switching inverters and control strategies have been proposed, a general classification of soft switching inverter proposed in [40] is shown in Figure 3.2.

Figure 3.2 - Classification of soft switching DC/AC converters

Since in soft switching converters commutations have to happen when the voltage or the current of the switches are zero, measurement circuits are required to detect the ZV and ZC conditions and to trigger the gate driver of transistors; high bandwidth measurement circuits are hence required. Voltage measurement is quite easy to implement, whereas high bandwidth current measurement is more complicated. The simplest method for current measurement is the use of a shunt resistors, which acts as a linear current to voltage transducer, although power losses are introduced by the resistor as well as stray inductance in the power loop. For the reasons above, zero voltage switching operation is generally preferred to zero current switching.

Regarding zero voltage switching converters, it is possible to follow two different approaches to achieve soft switching.

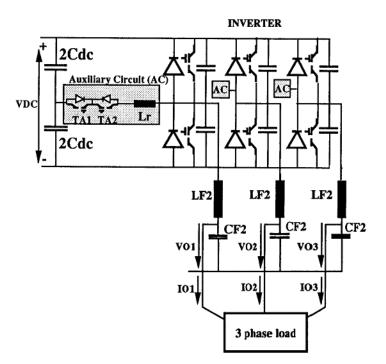

Resonant DC-Link family:

- Resonant DC-link inverter [41];

- Actively-clamped resonant DC-Link inverter [42];

- Resonant inverter with minimum voltage stress [39];

Resonant Pole family:

- Auxiliary resonant pole inverter [43];

- Auxiliary resonant commutated pole inverter [43];

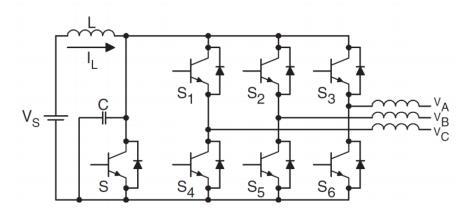

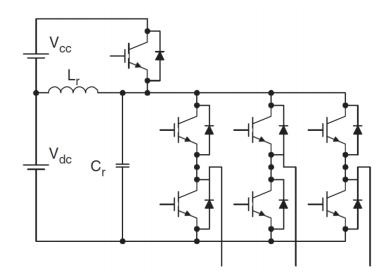

The Resonant DC-link inverter, depicted in Figure 3.3, was proposed by Deepakraj M. Divan in 1989 [41]. The basic idea is to introduce a resonance on the DC link of the inverter so that the voltage at the input of the inverter periodically drops to zero, therefore the configuration of the inverter can be changed under ZVS conditions. However, to control this type of converters, it is required an Integral Pulse Density Modulation (PMID) strategy since the switching can occur only at the instants at zero voltage, which are determined by the resonant frequency of the DC link [44]. Despite the potential advantages of this family of converters, too many drawbacks prevented its diffusion. In [45] [46] [47] is concluded that resonant DC link inverters, compared to traditional hard switched inverters, have a significantly higher harmonic distortion caused by the IPDM modulation. In addition, the peak voltage of the DC link is two times higher than the voltage of the DC link of a conventional inverter. Although auxiliary circuits can be used to reduce the peak voltage to 1.3-1.5 time the input voltage, the blocking capability of the transistor of the inverter (topologies in Figure 3.4 and Figure 3.5) is increased in comparison to a traditional hard switched converter. Furthermore, the power entirely passes through the resonant inductor of the DC link, thus reducing the efficiency and limiting the use of these converters only for low power applications.

Figure 3.3 - Resonant DC-Link Inverter.

Figure 3.4 - Active-Clamped Resonant DC-Link Inverter.

Figure 3.5 - Resonant Inverter with Minimum Voltage Stress.

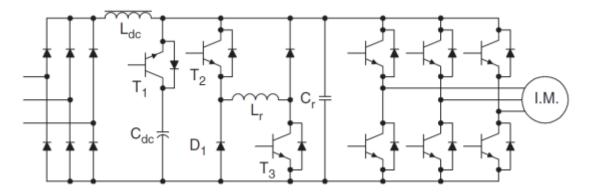

The resonant pole family was proposed by Rik W. De Doncker in 1990 to overcome the limitations of the DC link converters [43]. The basic configuration, depicted in Figure 3.6, uses auxiliary resonant circuits on the load side of each inverter branch to force to zero the voltage whenever it is required to switch a transistor. The auxiliary branches are constituted of a bidirectional switch connected in series with an inductor, which ensures the zero current switching operation of the bidirectional switch and the zero voltage switching of the transistor of the main branch.

Differently from DC link inverters, this approach does not cause over voltage spikes higher than the DC link voltage, therefore the blocking voltage of the power switches equal to that of hard switched DC/AC converters. Furthermore, the full power of the system does not flow through the auxiliary circuits, making this converter suitable for high power applications.

Figure 3.6 - ARCP DC to AC converter.

The control of the auxiliary branches, however, is very complicated since it depends on the amplitude and sign of the load current [43]. Several auxiliary circuit variations have been proposed to improve the efficiency of the first version of ARCP converter, to make the control easier and to reduce the current rating of the devices. Among them it is worth mentioning: - Zero Current Transition converter (ZCT) [45];

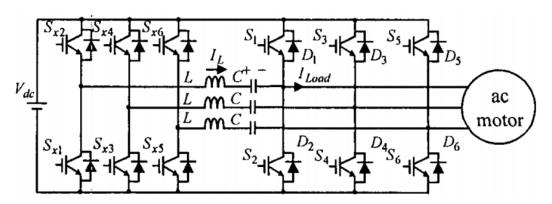

Figure 3.7 – Schematic of a three phase ZCT.

- Zero Voltage Transition with a Single Switch converter (ZVTSS) [45];

Figure 3.8 - Schematic of a three phase ZVTSS.

- Zero Voltage Transition with a Single Inductor converter (ZVTSI) [45];

Figure 3.9 - Schematic of a three phase ZVTSI.

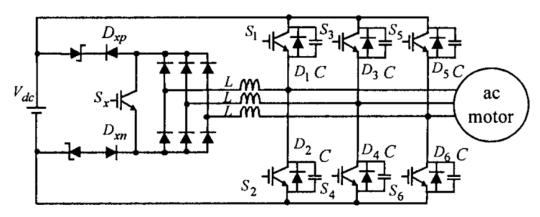

- Zero Voltage Transition with a Coupled Inductor converter (ZVTCI) [48];

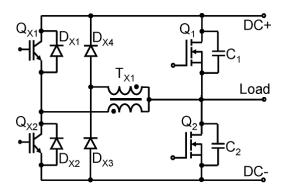

Figure 3.10 - Schematic of a ZVTCI inverter leg.

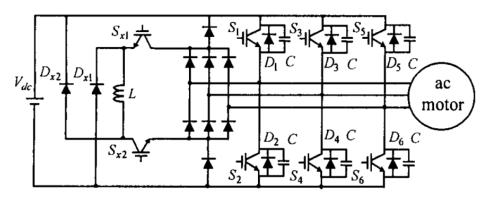

- Zero Voltage Transition with two Coupled Inductor converter (ZVT2CI) [49];

Figure 3.11 - Schematic of a ZVT2CI inverter leg.

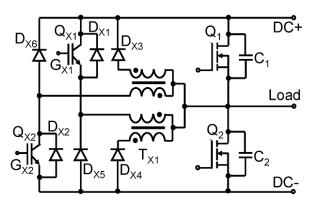

The Zero Voltage Transition with two Coupled Inductor (ZVT2CI) is the latest evolution of the Resonant Pole family [49]. The detailed analytical model of this topology is presented in section 3.3.B whereas the design procedures of a 2 kW, 400 Vdc single phase converter are presented in section 3.3.C. An efficiency comparison between the soft switching converter and a hard switched counterpart using the latest transistor technology is presented in section 3.3.D.

# 3.3 Zero Voltage Transition Converter with two Coupled Inductors

Among the soft-switching inverter presented in section 3.2, in this thesis attention has been given to the auxiliary pole family due to the higher efficiency [45] and relatively simple control. The converter selected for a performance comparison with hard switched converters is the zero voltage transition converter with two coupled inductors in one resonant pole [49]. This topology solves the main drawbacks of the transformed-based ZVS converters, i.e., the saturation of the core of the inductors [48], by resetting the magnetizing current each switching cycle.

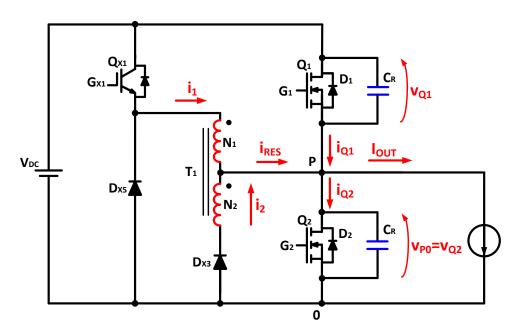

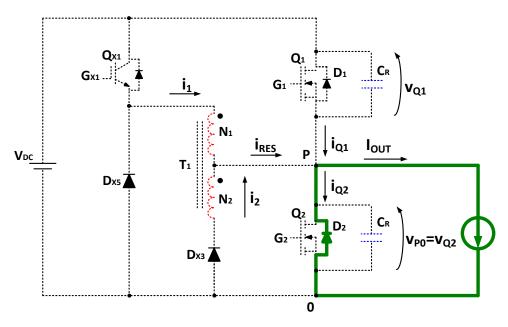

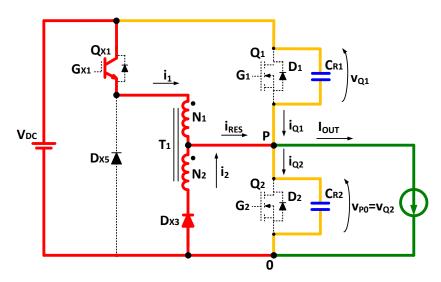

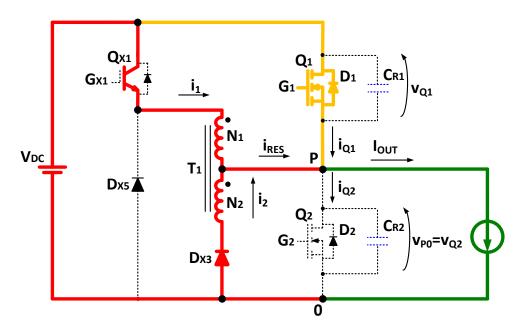

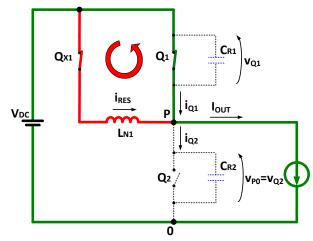

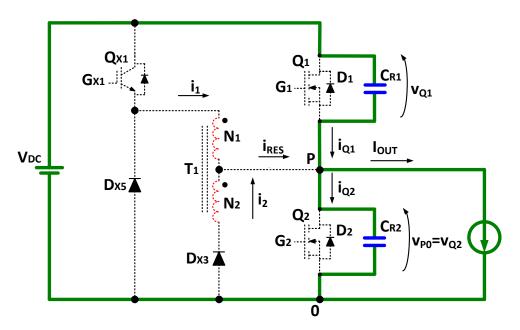

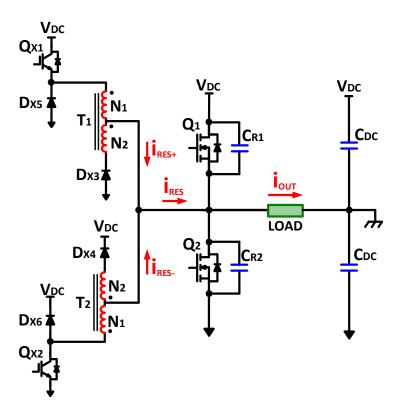

Figure 3.12 - Schematic of a ZVT2CI inverter leg feeding an highly inductive load, approximated by a current source.

# 3.3.A Topology description

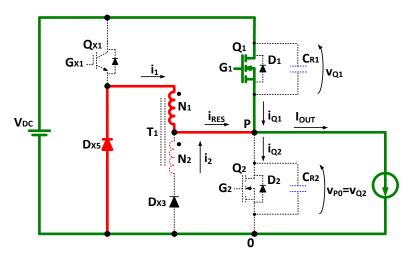

A branch of a zero voltage transition converter with two couple inductor in one resonant pole is shown in Figure 3.12. As in a conventional inverter, two switches ( $Q_1$  and  $Q_2$ ) with freewheeling diodes ( $D_1$  and  $D_2$ ) form the main leg of the converter. Connected in parallel to the two main switches there are the resonance capacitors  $C_{R1}$  and  $C_{R2}$ , which play a key role to archive the zero-voltage turn-on of  $Q_1$  and  $Q_2$  and to reduce the turn-off losses. Two auxiliary branches are connected to the central point of the main leg. Each one consists of an autotransformer ATR, an auxiliary switch ( $Q_{X1,2}$ ) and two auxiliary diodes ( $D_{X3,4}$ ) and ( $D_{X5,6}$ ). The auxiliary resonant current can be established by turning on the auxiliary switch, which conducts the resonant current through the respective coupled magnetics. The upper auxiliary branch takes part to the commutation only if the load current is positive while the second one operates only in case of commutation under negative load current. The switches of the main branch switch under zero voltage (ZVS) conditions, while the switches of the auxiliary branches under zero current (ZCS) conditions.

#### 3.3.B Operating principle of the converter

In order to simplify the analysis and obtain an analytical description of the converter, the following assumptions have been made:

- power switches and diodes have zero forward voltage drop in the on-state and are open circuits in the off-state;

- the output capacitance of the transistors is negligible;

- diodes have no reverse recovery charge;

- the switching time of the power switches is zero, i.e., commutations are instantaneous;

- autotransformers and capacitors have zero losses;

- the load is highly inductive, then the load current can be considered constant over a switching cycle. Therefore, the load can be modelled as a DC current source.

The control adopted for the converter, originally proposed in [49], requires four independent PWM signals  $G_{X1}$ ,  $G_{X2}$ ,  $G_1$  and  $G_2$  to control the switches  $Q_{X1}$ ,  $Q_{X2}$ ,  $Q_1$  and  $Q_2$  respectively.

$G_{X1}$  and  $G_{X2}$  are complementary signals with a dead time in between them, exactly as they were the gate signals of a half bridge converter.

The turn-on rising edge of the main switch gate signal  $G_1$  is controlled adaptively by a zero voltage detector logic, which checks the drain-source voltage of  $Q_1$  and ensures soft switching turn-on under any load current and any source voltage condition. Instead, the turn-off falling edge of  $G_1$  is controlled by a fixed time delay from the falling edge of the PWM command  $G_{X1}$ , the delay time ensures the complete reset of the magnetizing current of the transformer  $T_1$  every switching period.

In the same way, the turn ON rising edge of the main switch gate signal  $G_2$  is controlled adaptively by a zero voltage detector logic, which checks the drain-source voltage of  $Q_2$  and ensures soft switching turn ON. The turn OFF falling edge of  $G_2$  is controlled by a fixed time delay from the falling edge of the PWM command  $G_{X2}$ , the delay time ensures the complete reset of the magnetizing current of the transformer  $T_2$  every switching cycle.

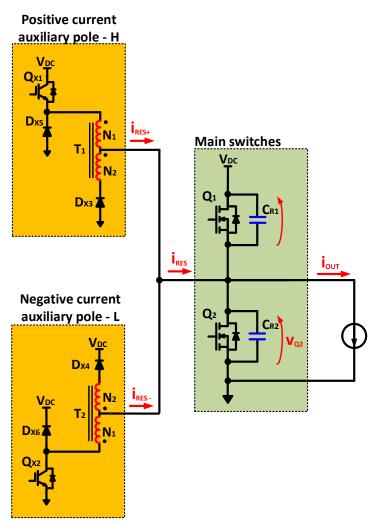

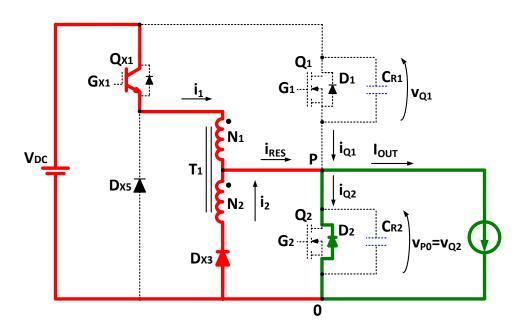

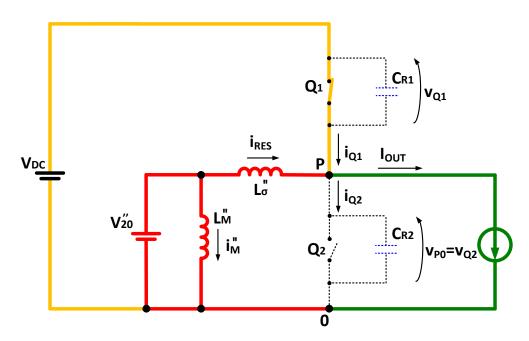

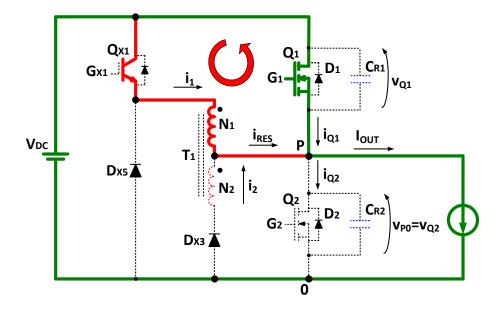

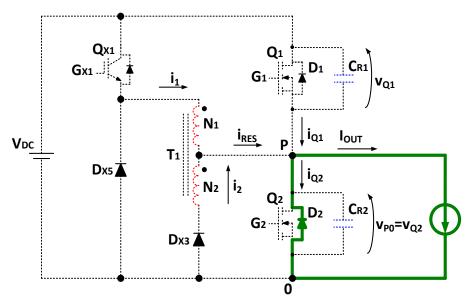

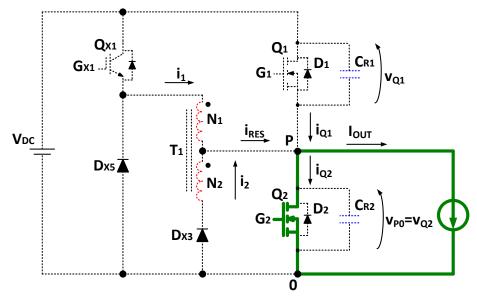

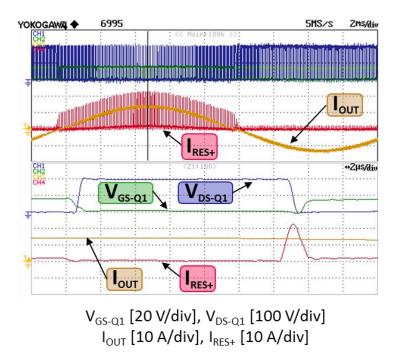

In the analysis of a period, it is assumed that the load current is positive. Therefore, in the following description the auxiliary pole L, which operates only in case of negative output current, is not considered. The circuit considered in the next analysis is re-drawn in Figure 3.13.

Figure 3.13 - Schematic of the ZVT2CI converter, considering only the main bridge and the positive current auxiliary pole.

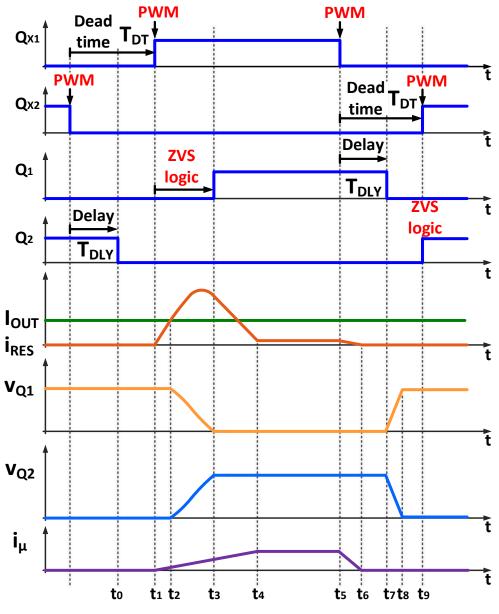

One operating cycle of the converter can be subdivided in nine phases as shown in Figure 3.14, each phase can be analyzed using an equivalent circuit of the converter. The duration of each phase has been increased for the sake of clarity. The sign convention for voltages and currents follows the notation of Figure 3.13.

The stating point of the analysis is the end of the interval  $[t_0-t_1]$ , which corresponds to the freewheeling circulation of the output current through the diode  $D_2$ .

Figure 3.14 - Timing diagram of the ZVT2CI inverter.

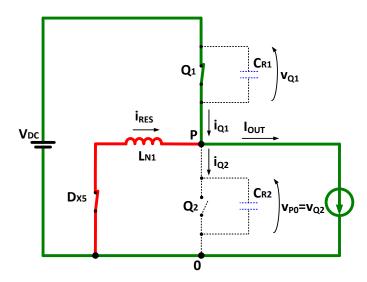

# *Phase* $0 - [t_0, t_1]$

At  $t = t_0$ , the main switch  $Q_2$  is turned off under ZVS conditions, the current  $I_{OUT}$  that was flowing through the channel of the MOSFET (third quadrant operation) is diverted to the body diode  $D_2$ . Therefore:

$$i_{Q2} = -I_{OUT}.$$

(3.1)

The turn-off action does not change the output voltage and current waveforms. All the gate signals are low and the resonant current  $i_{RES}$  is zero.

The resonant capacitors across  $Q_1$  and  $Q_2$  respectively are fully charged and discharged:

$$v_{Q1} = V_{DC} \tag{3.2}$$

$$v_{Q2} = 0. (3.3)$$

Figure 3.15 – Detail of the ZVT2CI converter during time [t<sub>0</sub>, t<sub>1</sub>].

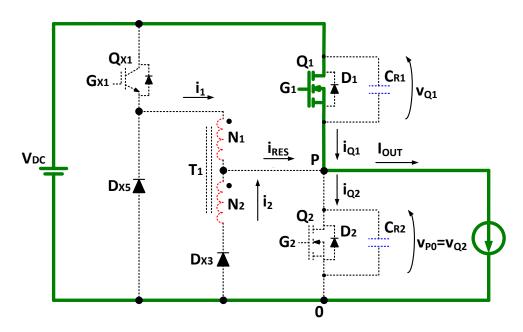

#### *Phase 1 -* $[t_1, t_2]$

At  $t = t_1$ , the auxiliary switch  $Q_{X1}$  is turned-on by the PWM signal  $G_{X1}$ . The input voltage  $V_{DC}$  is applied to the primary side of the autotransformer and then the diode  $D_{X3}$  is forced in conduction mode, the components that take part to this phase are highlighted in Figure 3.16.

Figure 3.16 - Detail of the ZVT2CI converter during time  $[t_1, t_2]$ .

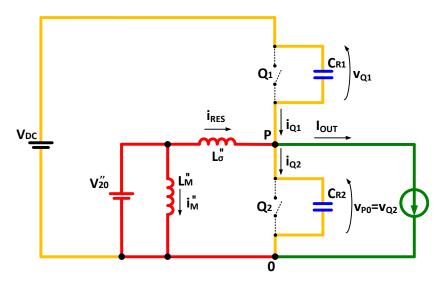

Figure 3.17 - Equivalent circuit of the ZVT2CI converter during time [t<sub>1</sub>, t<sub>2</sub>].

To simplify the analysis, the equivalent circuit of the auto transformer depicted in Figure 3.17 is introduced. The equivalent electrical parameters of the autotransformer, i.e., the no-load voltage  $V_{20}^{\prime\prime}$ , the magnetizing inductance  $L_M^{\prime\prime}$  and leakage inductance  $L_{\sigma}^{\prime\prime}$ , are referred to the secondary side. The autotransformer behaves then like a DC voltage source of amplitude

$$V_{20}'' = \frac{N_2}{N_1 + N_2} V_{DC} = k V_{DC}.$$

(3.4)

Initially, the load current  $I_{OUT}$  is freewheeling through  $D_2$ , keeping the pole voltage  $v_{P0}$  to zero. The secondary side of the autotransformer is then short circuited and voltage  $kV_{DC}$  is completely applied to the leakage inductance  $L''_{\sigma}$  and to the magnetizing inductance  $L''_{M}$ .

Let us define  $t' = t - t_1$ . The resonant current  $i_R$  rises linearly as follow:

$$i_R = \frac{kV_{DC}}{L''_{\sigma}}t'.$$

(3.5)

Simultaneously, a magnetizing current  $i''_M$  is established:

$$i''_{M} = \frac{kV_{DC}}{L''_{M}}t'.$$

(3.6)

Phase 1 ends at  $t = t_2$ , when the resonant current  $i_R$  reaches the value of the output current  $I_{OUT}$  and the diode  $D_2$  is forced to turn-off. Therefore, phase 1 lasts:

$$T_{12} = t_2 - t_1 = \frac{L_{\sigma}'' I_{OUT}}{k V_{DC}}.$$

(3.7)

The real currents in the windings of the autotransformer can be calculated as follow:

$$i_1 = k(i_{RES} + i_M'')$$

(3.8)

$$i_2 = i_{RES} - i_1 = (1 - k)i_{RES} - ki''_M.$$

(3.9)

It can be seen from equations (3.10) and (3.11) that the resonant current  $i_{RES}$  is shared between the transistor  $Q_{X1}$  and the diode  $D_{X3}$ .

#### *Phase 2 -* $[t_2, t_3]$

At  $t = t_2$ , the resonant current  $i_{RES}$  exceeds the load current: the diode  $D_2$  is forced in blocking mode and the resonant transition that leads to the ZV turn-on of  $Q_1$  begins. The excess of current  $i_{RES} - I_{OUT}$  charges and discharges the resonant capacitors  $C_{R2}$  and  $C_{R1}$  and the pole voltage  $V_{P0}$  start rising.

The Figure 3.18 illustrates the topological configuration of the circuit of phase 2, while Figure 3.19 shows the equivalent circuit.

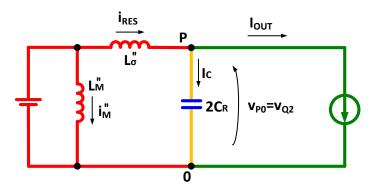

If we assume that the resonant capacitor  $C_{R1}$  and  $C_{R2}$  have the same capacity  $C_R$ , then the circuit of Figure 3.19 can be further simplified as in Figure 3.20.

Figure 3.18 - Detail of the ZVT2CI converter during time [t<sub>2</sub>, t<sub>3</sub>].

Figure 3.19 - Equivalent circuit of the ZVT2CI converter during time [t<sub>2</sub>, t<sub>3</sub>].

Figure 3.20 - Equivalent circuit of the ZVT2CI converter during time  $[t_2, t_3]$ .

Let us define  $t' = t - t_2$ . The following differential equations can be written:

$$\frac{di_{RES}}{dt'} = \frac{d(i_c + I_{OUT})}{dt} = \frac{di_c}{dt'}$$

(3.10)

$$kV_{DC} - L''_{\sigma} \frac{di_c}{dt} - v_{P0} = 0$$

(3.11)

$$i_c = 2C_R \frac{dv_{P0}}{dt'}.$$

(3.12)

Equations (3.10), (3.11) and (3.12) can be combined to obtain a second order differential equation:

$$\frac{d^2 v_{P0}}{dt'^2} + \frac{1}{2C_R} v_{P0} = \frac{1}{2C_R L'_{\sigma}} k V_{DC} \,. \tag{3.13}$$

The solution of (3.13) for the given initial conditions

$$v_{P0}|_{t'=0} = 0 \tag{3.14}$$

$$\frac{dv_{P0}}{dt'}\Big|_{t'=0} = \frac{i_c}{2C_R}\Big|_{t'=0} = \frac{i_{RES} - I_{OUT}}{2C_R}\Big|_{t'=0} = 0$$

(3.15)

is

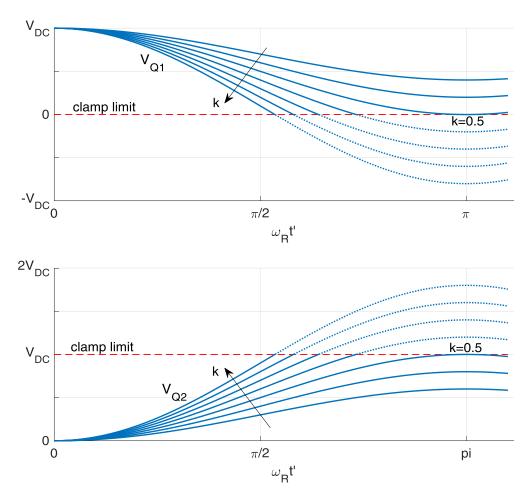

$$v_{P0} = k V_{DC} [1 - \cos(\omega_R t')]$$

(3.16)

where

$$\omega_R = \frac{1}{\sqrt{2C_R L''_\sigma}} \tag{3.17}$$

is the natural resonant frequency of the L-C series circuit. The equation (3.16) states that the pole voltage rises following a cosine shape evolution, whose peak voltage is:

$$V_{P0_{MAX}} = 2kV_{DC} . (3.18)$$

The voltages across  $Q_1$  and  $Q_2$  are obtained from  $v_{P0}$  as follows:

$$v_{Q_1} = V_{DC} - v_{P0} = V_{DC} - kV_{DC}[1 - \cos(\omega_R t')]$$

(3.19)

$$v_{Q_2} = v_{P0} = k V_{DC} [1 - \cos(\omega_R t')].$$

(3.20)

The time evolution of  $v_{Q_1}$  and  $v_{Q_2}$  for several values of k are depicted in Figure 3.21. If the turn ratio k of the autotransformer is greater than 0.5, the voltage  $v_{Q_2} = v_{P0}$  could rise above  $V_{DC}$ . Actually, the freewheeling diode  $D_1$  of the to switch  $Q_1$  prevents the pole voltage to be greater than the input voltage, therefore  $v_{P0}$  is clamped to  $V_{DC}$ . In this condition the ZV logic of the upper main switch turns  $Q_1$  on, since  $V_{Q1}$  is zero, archiving a zero switching losses commutation.

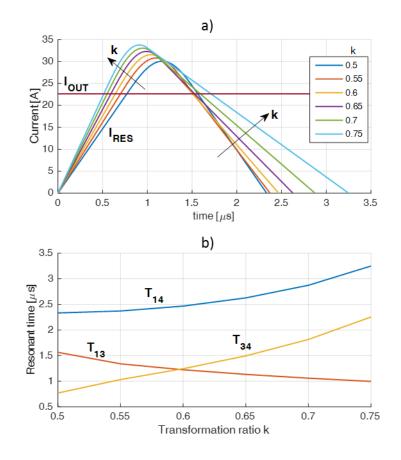

The autotransformer turn ratio k must be strictly greater than 0.5 to obtain a ZVS transition. Practically, k is selected between 0.55 and 0.6 in order to ensure a safe operation margin, since the real peak of  $V_{P0}$  during the resonant transition is reduced by the equivalent series resistance in the resonant loop, which includes the resistance of the transformer and the forward voltage drop on transistors and diodes.

Figure 3.21 – Resonant transition of voltages  $V_{Q1}$  and  $V_{Q2}$  during time [t<sub>2</sub>, t<sub>3</sub>].

Assuming that k > 0.5, phase 2 ends when at  $t = t_3$ , when  $v_{PO}$  reaches  $V_{DC}$ . The duration of phase 2 can be obtained by assuming  $v_{PO} = V_{DC}$  in (3.16):

$$T_{23} = t_3 - t_2 = \frac{1}{\omega_R} \cos^{-1}\left(\frac{k-1}{k}\right).$$

(3.21)

Thus, the turn-on delay time between the main switch  $Q_1$  and the auxiliary  $Q_{X1}$  switch can be obtained as follows:

$$t_3 - t_1 = \frac{L_{\sigma}'' I_{OUT}}{k V_{DC}} + \frac{1}{\omega_R} \cos^{-1}\left(\frac{k-1}{k}\right).$$

(3.22)

This expression indicates that the delay time is variable and dependent on the load current. Therefore, a ZV detector is required to automatically adapt the turn-on of  $Q_1$  to different load and source conditions [50].

The resonant current  $i_{RES}$  can be expressed as follows:

$$i_{RES} = i_C + I_{OUT} = 2C_R \frac{dv_{P0}}{dt'} + I_{OUT} = \frac{kV_{DC}}{Z_R} \sin(\omega_R t') + I_{OUT}$$

(3.23)

where  $Z_R$  is the resonant impedance:

$$Z_R = \sqrt{\frac{L''_{\sigma}}{2C_R}}.$$

(3.24)

The peak of the resonant current happens when  $v_{P0}$  is equal to  $kV_{DC}$ , because:

$$\frac{di_{RES}}{dt} = \frac{kV_{DC} - v_{P0}}{L''_{\sigma}}.$$

(3.25)

Assuming  $\frac{di_{RES}}{dt} = 0$  the peak value of  $i_R$  can be obtained:

$$I_{RES_{MAX}} = I_{OUT} + \frac{kV_{DC}}{Z_R}.$$

(3.26)

It can be seen that  $I_{RES_{MAX}}$  is greater than  $I_{OUT}$ , but the resonant contribution that takes part to the charge and discharge of  $C_{R1}$  and  $C_{R2}$  is constant for any load current. At the end of phase 2, the resonant current reaches the following value:

$$I_{RES-t_3} = I_{OUT} + \frac{kV_{DC}}{Z_R} \sin(\omega_R T_{23}).$$

(3.27)

During the entire phase 2 the voltage  $kV_{DC}$  is applied to  $L''_M$ , so the magnetizing current increases linearly and in  $t_3$  it reaches the value:

$$I_{M-t_3}^{\prime\prime} = \frac{kV_{DC}}{L_M^{\prime\prime}} (T_{12} + T_{23}).$$

(3.28)

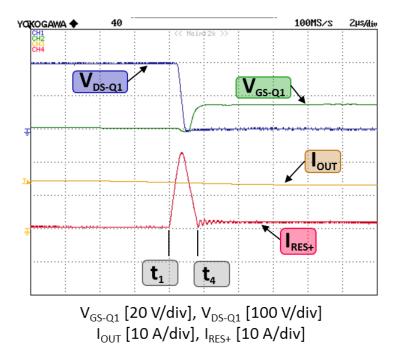

#### *Phase 3 -* $[t_3, t_4]$

At  $t = t_3$ , the capacitor  $C_{R1}$  is fully discharged, while the capacitor  $C_{R2}$  is charged at the voltage  $V_{DC}$ . Diode  $D_1$  prevents the pole voltage  $V_{P0}$  from rising above  $V_{DC}$  and conducts the excess current  $i_R - I_{OUT}$  back to the source. As long as the resonant current is greater than the output current,  $D_1$  is forward biased and  $V_{Q1}$  is clamped to zero. Therefore, switch  $Q_1$  can be turned-on under ZV conditions. The configuration of the converter during phase 3 is depicted in Figure 3.22, while Figure 3.23 shows the equivalent circuit.

Let us define  $t' = t - t_3$ . The resonant current decreases linearly subjected to the voltage  $(1 - k)V_{DC}$ :

$$i_{RES} = I_{RES-t_3} - \frac{(1-k)V_{DC}}{L'_{\sigma}}t'.$$

(3.29)

The ZV logic circuitry must detect the ZV condition and turn  $Q_1$  on before  $i_{RES}$  falls below the load current, otherwise the ZV switching condition is lost. The time window for the ZV turn-on can be evaluated introducing (3.26) into (3.29) and solving t' for  $i_{RES} = I_{OUT}$ :

$$\Delta T_{ZVS} = \frac{1}{\omega_R} \frac{k}{1-k} \sin(\omega_R T_{23}) = \frac{1}{\omega_R} \sqrt{\frac{2k-1}{(1-k)^2}}.$$

(3.30)

The equation (3.30) states that the ZV time window is an intrinsic property of the converter, which depends only on the transformer turn ratio, on the transformer leakage inductance and on the resonant capacitors.

When switch  $Q_1$  is turned on, the current  $i_{Q1}$  that was flowing in the diode  $D_1$  is diverted to the channel of  $Q_1$ . After the time  $\Delta T_{ZVS}$ , the current of  $Q_1$  becomes positive and continues to increase linearly, diverting the load current from the auxiliary circuit to the main switch:

$$i_{Q1} = i_{RES} - I_{OUT} \,. \tag{3.31}$$

The magnetizing current keeps rising since  $kV_{DC}$  is still applied to  $L''_{M}$ :

$$i''_{M} = I''_{M-t_{3}} + \frac{kV_{DC}}{L''_{M}}t'.$$

(3.32)

Figure 3.22 – Detail of the ZVT2CI converter during time [t<sub>3</sub>, t<sub>4</sub>].

Figure 3.23 - Equivalent circuit of the ZVT2CI converter during time [t<sub>3</sub>, t<sub>4</sub>].

Phase 3 ends when the current  $i_2$  that flows through  $D_{X3}$  falls back to zero, forcing the turn-off of the diode. By using (3.8), (3.29) and (3.32) the current  $i_2$  can be written as:

$$i_{2} = (1-k) \left( I_{RES-t_{3}} - \frac{(1-k)V_{DC}}{L_{\sigma}''} t' \right) - k \left( I_{M-t_{3}}'' + \frac{kV_{DC}}{L_{M}''} t' \right).$$

(3.33)

The duration of phase 3 can be obtained imposing  $i_2 = 0$  and solving for  $t' = T_{34}$ :

$$T_{34} = t_4 - t_3 = \frac{(1-k)I_{RES-t_3} - kI''_{M-t_3}}{V_{DC}\left(\frac{k^2}{L''_M} + \frac{(1-k)^2}{L''_\sigma}\right)}.$$

(3.34)

Since in a transformer the magnetizing inductance is much larger than the leakage inductance, (3.34) can be approximated as follows:

$$T_{34} \cong \frac{L_{\sigma}''}{(1-k)V_{DC}} I_{RES-t_3}$$

(3.35)

From time  $t_1$  to  $t_4$  the transformer is supplied. Therefore, the magnetizing current  $i''_M$  rises linearly and its final value in  $t_4$  can be calculated as:

$$I_{M-t_4}^{\prime\prime} = \frac{kV_{DC}}{L_M^{\prime\prime}} \left(T_{12} + T_{23} + T_{34}\right).$$

(3.36)

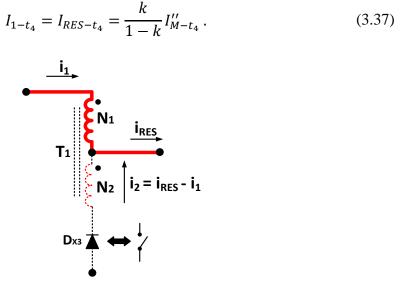

It has been shown that at the end of phase 3 the current  $i_2$  has dropped to zero. Figure 3.24 helps to understand the relations between the currents of the transformer in  $t_4$ . By using (3.8), (3.9) and (3.33),the resonant current  $I_{RES-t_4}$  and the primary current of the autotransformer  $I_{1-t_4}$  can be calculated as:

Figure 3.24 – Relation between the resonant current and the currents in the windings of the autotransformer.

# *Phase* $4 - [t_4, t_5]$

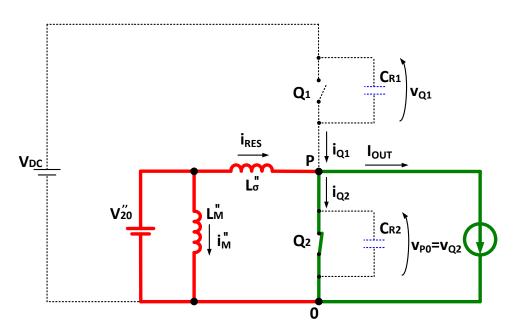

Phase 4 starts in  $t = t_4$  when the current  $i_2$  of the transformer falls to zero and the diode  $D_{X3}$  is forced to turn-off therefore, the secondary winding becomes an open circuit. Therefore, the autotransformer behaves just like an inductor, which is formed by  $N_1$  primary turns wounded around the core of the transformer. The equivalent inductance  $L_{N1}$  can be calculated as follows:

$$L_{N1} = L_M'' \left(\frac{N_1}{N_2}\right)^2 = L_M'' \left(\frac{1-k}{k}\right)^2.$$

(3.38)

It can be seen in Figure 3.25 and in the equivalent circuit of Figure 3.26 that a low resistance loop is formed by  $Q_{X1}$  (which is still on),  $Q_1$  and the primary winding  $N_1$ . Therefore the current  $I_{1-t_4} = I_{RES-t_4}$  calculated in (3.37) can freewheel without attenuation, since the voltage applied to  $L_{N1}$  is zero. The current carried by  $Q_1$  is:

$$i_{Q1} = I_{OUT} - I_{RES-t_4} \cong I_{OUT} \,. \tag{3.39}$$

Phase 4 lasts as long as the PWM signal of  $G_{X1}$  is high.

Figure 3.25 - Detail of the ZVT2CI converter during time [t<sub>4</sub>, t<sub>5</sub>].

Figure 3.26 - Equivalent circuit of the ZVT2CI converter during time [t<sub>4</sub>, t<sub>5</sub>].

# *Phase* $5 - [t_5, t_6]$

At  $t = t_5$ , the PWM signal  $G_{X1}$  goes to zero and turns-off the switch  $Q_{X1}$ . At the same time the current  $i_1$ , since is flowing through the inductor  $L_{N1}$ , forces the turn on of the diode  $D_{X5}$ .

Therefore, it begins the resetting phase of the current  $i_{RES}$ .

Let us define  $t' = t - t_5$ :

$$i_{RES} = I_{RES-t_4} - \frac{V_{DC}}{L_{N1}}t'.$$

(3.40)

Figure 3.27 illustrates the topological configuration of the circuit, while Figure 3.28 shows the equivalent circuit.

Figure 3.27 - Detail of the ZVT2CI converter during time [t<sub>5</sub>, t<sub>6</sub>].

Figure 3.28 - Equivalent circuit of the ZVT2CI converter during time [t<sub>5</sub>, t<sub>6</sub>].

During the resetting of  $i_2$ , the diode  $D_{X3}$  is reverse biased by the voltage induced in  $N_2$ :

$$v_{DX3} = V_{DC} + \frac{N_2}{N_1} V_{DC} = \frac{1}{1-k} V_{DC} .$$

(3.41)

For values of turn ratio greater than 0.5, it appears that  $D_{X3}$  has to withstand a voltage greater than  $2V_{DC}$ . This phenomenon must be taken seriously into account during the design of the converter.

Phase 5 ends at  $t = t_6$ , when the resonant current  $i_R$  falls to zero and the diode  $D_{X5}$  is forced to turn-off. Therefore, the duration of phase is:

$$T_{56} = t_6 - t_5 = \frac{L_{N1}I_{RES-t_4}}{V_{DC}}.$$

(3.42)

The delay time  $T_{DLY}$  introduced between the falling edges of the PWM signals  $G_{X1}$  and  $G_1$  (see Figure 3.14) must guarantee the complete reset of the resonant current each switching cycle. An incomplete reset leads to the bias of  $i_{RES}$ , which increases cycle by cycle, leading to the saturation of the autotransformer and to the possible failure of the converter. Therefore, the delay time must greater than  $T_{56}$  calculated at the maximum output current of the converter:

$$T_{DLY} > T_{56}|_{I_{OUT\,MAX}} . (3.43)$$

### *Phase 6 -* $[t_6, t_7]$

Phase 6 starts at  $t = t_6$  when the resonant current has been fully reset and the output current flows only through switch  $Q_1$ .

Figure 3.29 illustrates the topological configuration of the circuit.

Figure 3.29 - Detail of the ZVT2CI converter during time [t<sub>6</sub>, t<sub>7</sub>].

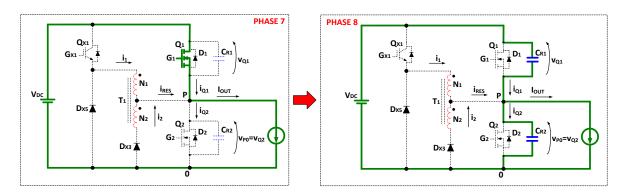

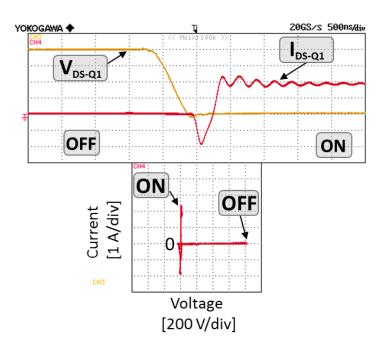

#### *Phase* 7 - [t<sub>7</sub>, t<sub>8</sub>]

At  $t = t_7$ , the main switch  $Q_1$  is turned-off by the PWM signal  $G_1$ . Ideally,  $Q_1$  interrupts instantly  $I_{OUT}$ , which continues to flow through the capacitor  $C_{R1}$ . Therefore,  $C_{R1}$  is being charged by  $I_{OUT}$  while  $C_{R2}$  is being discharged. Figure 3.30 illustrates the configuration of the circuit during phase 7.

Let us define  $t' = t - t_5$ , the pole voltage can be expressed as:

$$v_{P0} = V_{DC} - \frac{I_{OUT}}{2C_R} t'.$$

(3.44)

The pole voltage decreases linearly to zero, with a slope proportional to the load current, phase 7 ends when  $v_{P0}$  reaches zero.

$$T_{78} = t_8 - t_7 = \frac{2C_R V_{DC}}{I_{OUT}}.$$

(3.45)

Figure 3.30 - Detail of the ZVT2CI converter during time [t<sub>7</sub>, t<sub>8</sub>].

# *Phase* 8 - [t<sub>8</sub>, t<sub>9</sub>]

At  $t = t_8$  the pole voltage  $v_{P0}$  reaches zero, diode  $D_2$  is forced to turn-on and the load current  $I_{OUT}$  freewheels through  $D_2$  (see Figure 3.31).

Figure 3.31 - Detail of the ZVT2CI converter during time [t<sub>8</sub>, t<sub>9</sub>].

In this condition, since  $D_2$  keeps the voltage  $v_{Q2}$  to zero, the ZV logic can turn-on  $Q_2$  without the generation of switching losses. Then, the current  $I_{OUT}$  that was flowing through diode  $D_2$  is diverted to the channel of  $Q_2$ , resulting in a third quadrant operation as depicted in Figure 3.32.

Figure 3.32 - Detail of the ZVT2CI converter during time [t<sub>8</sub>, t<sub>9</sub>].

Phase 8 is the last mode of operation, and it continues until the beginning of the next switching cycle, which is described in phase 0.

The operation of the converter in the case of a negative output current involves the negative current auxiliary pole L and is similar to the analysis presented so far, therefore it will be not considered.

#### 3.3.C Converter design

# Design specifics

The design procedures of one leg of ZVT2CI inverter are presented in the following subsections. The specifications of the converter are as follows:

Table 3.1 – Design specifications of the ZVT2CI inverter.

| Design Specifics                | Value               |

|---------------------------------|---------------------|

| DC link voltage V <sub>DC</sub> | 400 V               |

| Phase current $I_{OUT-MAX}$     | 16 A <sub>RMS</sub> |

| Switching frequency $F_{SW}$    | Up to 20 kHz        |

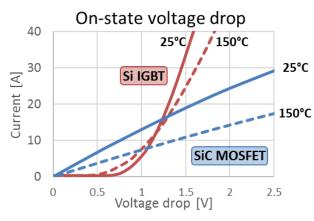

#### Main transistor selection

As discussed in section 1.1, IGBTs are usually selected for applications above 200  $V_{DC}$  in hard switched DC to AC inverters. The use MOSFETs could potentially increase the efficiency of converters due to the fact that the majority carrier devices can switch much faster than bipolar transistors. However, power MOSFETs present an inherent parasitic diode whose dynamic performance and di/dt ruggedness deteriorates dramatically with the increase of the blocking voltage, generating switching losses and leading to potential failure of the device. Typical di/dt ruggedness for the largest part of 600V SJ MOSFET body diodes is below 100A/µs, while the di/dt during the hard turn off of diode in DC to AC converters can easily reach 1500A/µs, far above the inherent limit of SJ MOSFETs.

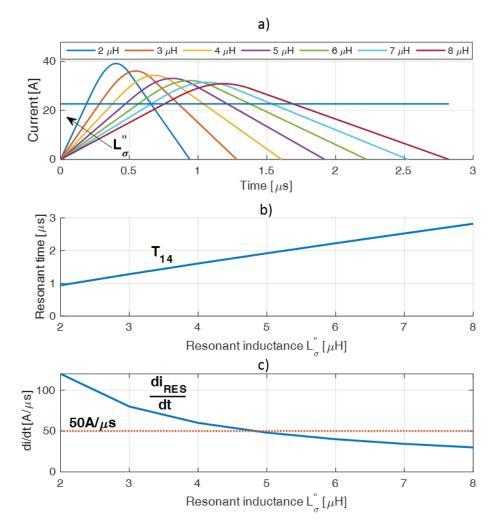

For the ZVS2CI Inverter described in 3.3.A, instead, the di/dt of the current during the turn off of the diode  $D_2$  (phase 1) is controlled by the leakage inductance and the turn ratio of the auxiliary autotransformer, accordingly to the equation:

$$\frac{di_Q}{dt} = \frac{di_R}{dt} = \frac{kV_{DC}}{L'_{\sigma}}.$$

(3.46)

Therefore, the leakage inductance of the auxiliary autotransformer can be designed to limit the di/dt to less than 50 A/ $\mu$ s, making the use of SJ MOSFETs possible and safe for the main switches  $Q_1$  and  $Q_2$  of the inverter. However, even if di/dt is limited below the physical limit

of the SJ MOSFETs, the reverse recovery charge of the body diode of MOSFETs could affect the ideal operation of the converter during the resonant transition.

A short introduction to reverse recover phenomena is required for best understanding of the power switches selection criteria.

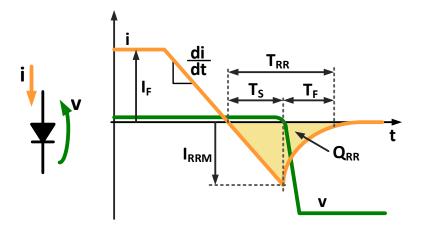

It is well known that when a diode is switched from the conducting state to the blocking state, the stored charge in the PN junction must be recombined before that the diode can recover the ability to block the reverse voltage. The recombination takes a finite amount of time, known as Reverse Recovery Time, or  $t_{rr}$ .

The reverse recovery time can be divided into two parts, corresponding to the duration of two distinct consecutive steps:

- 1. the storage time  $t_S$ , which is defined as the time between the instant when the current crosses the zero, and the instant when the current reaches the peak of reverse recovery  $I_{RRM}$ ;

- 2. the fall time  $t_f$ , which is defined as the time necessary for the current to fall from  $I_{RRM}$  to 10%  $I_{RRM}$ .

During the storage phase, the current decreases linearly, whereas during the second phase the current drops back to zero following an exponential law.

In general,  $t_s$ ,  $t_f$  and  $I_{RRM}$  are functions of the current  $I_F$  at the turn off, of the fall rate  $\frac{di_F}{dt}$  during  $t_s$ , of the reverse blocking voltage and of the junction temperature of the diode.

Figure 3.33 - Reverse recovery waveforms and definitions.

Regarding the ZVS2CI inverter, the reverse recovery charge of  $D_1$  and  $D_2$  can cause an increase in the resonant current during the resonant phases.

The switching cycle of the converter, described in section 3.3.B, begins when the load current flows through the freewheeling diode  $D_2$ . The aim of the auxiliary pole is to bring the pole voltage  $v_{P0}$  to  $V_{DC}$  allowing the ZV turn-on of the upper switch  $Q_1$ . In doing so, a current pulse  $i_{RES}$  higher than  $I_{OUT}$  is injected in the point P of the converter. The first part of the pulse has the aim of turning off the freewheeling diode  $D_2$ , while the second part charges and discharges the resonant capacitors across the transistor  $Q_1$  and  $Q_2$ , therefore increasing the pole voltage.

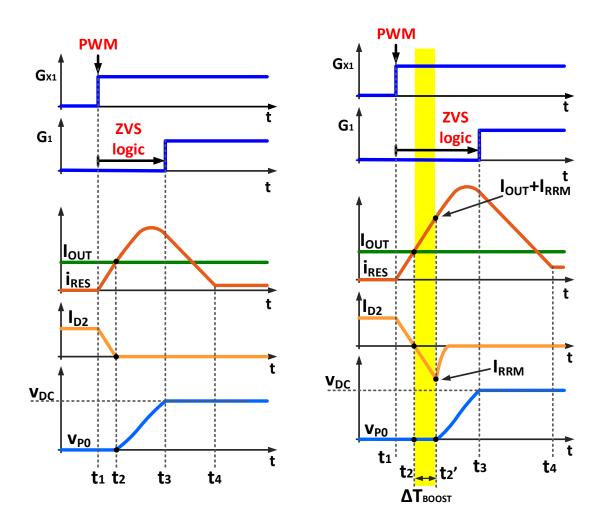

Assuming an ideal behavior of diodes, the pole voltage starts rising exactly when the resonant current reaches the load current, forcing the diode  $D_2$  in block mode. This case is analytically described in section 3.3.B and is reported in Figure 3.34 for the sake of clarity.

Figure 3.34 - Resonant transition of the converter if ideal diodes are considered.

Figure 3.35 - Resonant transition of the converter if real diodes are considered.

However, real diodes, can recover the blocking capability only when the charges stored in the PN junction have been completely recombined, therefore higher resonant current than in the ideal case is required to turn-off  $D_2$ . The resonant transition of the converter in the case of real diodes is depicted in Figure 3.34. It can be seen that the pole voltage is kept to zero until  $t_{2'}$ , when the resonant current is equal to:

$$I_{RES-t2'} = I_{OUT} + I_{RRM} . (3.47)$$

Therefore, the total time required to fully turn off the diode  $D_2$  is larger than in the ideal case and lasts:

$$T_{12'} = (t_2 - t_1) + (t_{2'} - t_2) = T_{12} + \Delta T_{BOOST} = \frac{L_{\sigma}'' I_{OUT}}{k V_{DC}} + \frac{L_{\sigma}'' I_{RRM}}{k V_{DC}}.$$

(3.48)

The time delay introduced by the reverse recovery characteristic of the diode is called boost time  $\Delta T_{BOOST}$ , since the resonant current  $i_{RES}$  is boosted above the load current  $I_{OUT}$ .

The presence of the boost phase has negative effects on the operation of the converter, including:

- increase in the peak value of the resonant current;

- longer duration of the resonant transition;

- increase in the conduction losses of the auxiliary circuits due to the larger RMS value of the resonant current;

- increase in the magnetizing current and therefore longer reset time is required.

Then the main switches  $Q_1$  and  $Q_2$  should be selected in such a way that the freewheeling diodes  $D_1$  and  $D_2$  are endowed with a low recovery current. IGBTs are usually co-packed with fast recovery diodes, therefore they are potentially suitable to operate as main switches in the ZVS2CI inverter. Instead not all power MOSFETs are suited for this application; only MOSFETs with a fast body diode should be selected for the use in the ZVS2CI inverter.

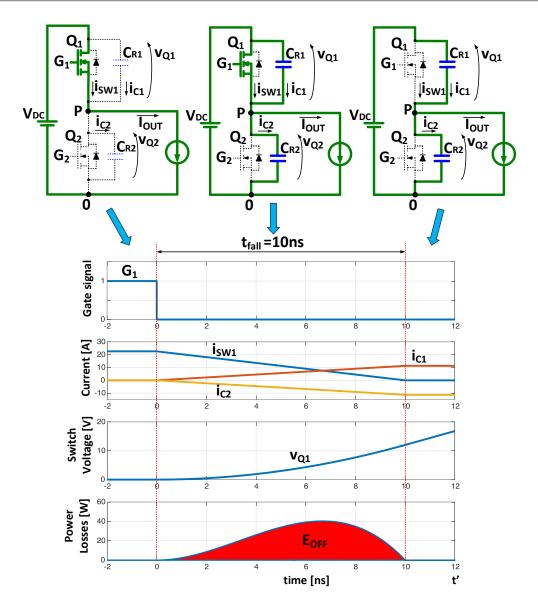

Given the above, both MOSFETs and IGBTs could be selected as main switches of the converter as long as theirs freewheeling diodes have proper dynamic performance. A second requirement that make a difference in the performance of the converter, is the turn-off characteristic of bipolar and majority carrier devices. Although the turn-on losses of  $Q_1$  and  $Q_2$  are negligible due to the zero-voltage switching, the turn-off loss can be only reduced, but

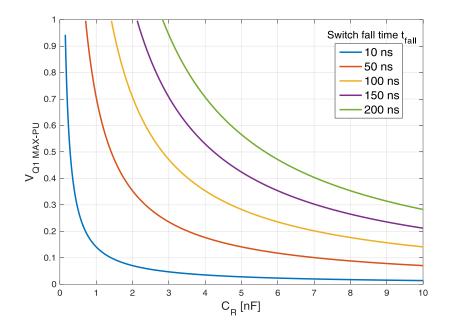

not fully eliminated, by the resonant capacitors  $C_{R1}$  and  $C_{R2}$ , acting as voltages snubbers. The shorter is the current fall time of the switch, the lower are the turn off losses. A detailed analysis of the resonant capacitor selection criteria is reported in the next section.

For the reasons above, and giving that the converters efficiency is the main focus of this thesis, power MOSFETs have been chosen due to the fast switching characteristics of majority carrier devices i.e., current fall time and absence of tail current.

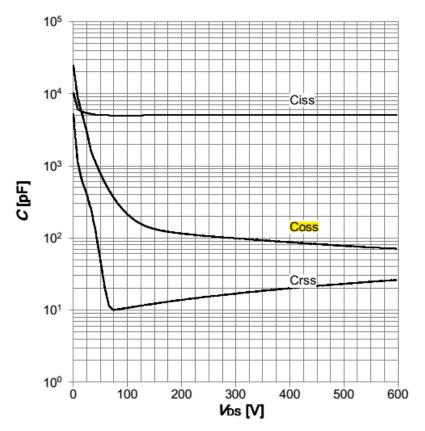

An Infineon IPW65R080CFD super junction MOSFET with fast body diode, designed specifically for resonant converter topologies, was selected for the switches  $Q_1$  and  $Q_2$ . Its main static and dynamic parameters are listed in Table 3.2.

| Parameter                      | Value                                    |

|--------------------------------|------------------------------------------|

| Continuous drain current       | 43.3 A @ 25 °C                           |

|                                | 27.4 A @ 100°C                           |

| Switching rise time            | 18 ns @ (400 V, 26.3 A)                  |

| Switching fall time            | 6 ns @ (400 V, 26.3 A)                   |

| $R_{TH}$ (junction-case)       | 0.32 K/W                                 |