**Publicly Accessible Penn Dissertations**

1-1-2014

# GROK-FPGA: Generating Real on-Chip Knowledge for FPGA Fine-Grain Delays Using Timing Extraction

Benjamin Gojman University of Pennsylvania, bgojman@gmail.com

Follow this and additional works at: http://repository.upenn.edu/edissertations

Part of the <u>Computer Engineering Commons</u>, <u>Computer Sciences Commons</u>, and the <u>Electrical</u> and Electronics Commons

#### Recommended Citation

Gojman, Benjamin, "GROK-FPGA: Generating Real on-Chip Knowledge for FPGA Fine-Grain Delays Using Timing Extraction" (2014). *Publicly Accessible Penn Dissertations*. 1287.

http://repository.upenn.edu/edissertations/1287

# GROK-FPGA: Generating Real on-Chip Knowledge for FPGA Fine-Grain Delays Using Timing Extraction

#### **Abstract**

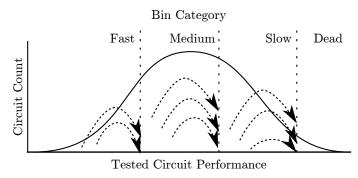

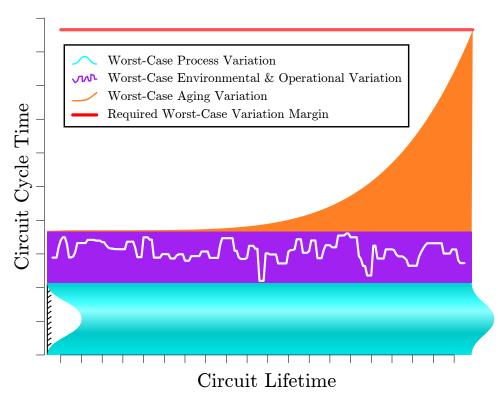

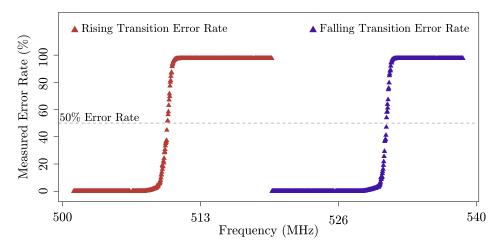

Circuit variation is one of the biggest problems to overcome if Moore's Law is to continue. It is no longer possible to maintain an abstraction of identical devices without huge yield losses, performance penalties, and energy costs. Current techniques such as margining and grade binning are used to deal with this problem. However, they tend to be conservative, offering limited solutions that will not scale as variation increases. Conventional circuits use limited tests and statistical models to determine the margining and binning required to counteract variation. If the limited tests fail, the whole chip is discarded. On the other hand, reconfigurable circuits, such as FPGAs, can use more fine-grained, aggressive techniques that carefully choose which resources to use in order to mitigate variation. Knowing which resources to use and avoid, however, requires measurement of underlying variation.

We present Timing Extraction, a methodology that allows measurement of process variation without expensive testers nor highly invasive techniques, rather, relying only on resources already available on conventional FPGAs. It takes advantage of the fact that we can measure the delay of logic paths between any two registers. Measuring enough paths, provides the information necessary to decompose the delay of each path into individual components-essentially, forming a system of linear equations. Determining which paths to measure requires simple graph transformation algorithms applied to a representation of the FPGA circuit. Ultimately, this process decomposes the FPGA into individual components and identifies which paths to measure for computing the delay of individual components.

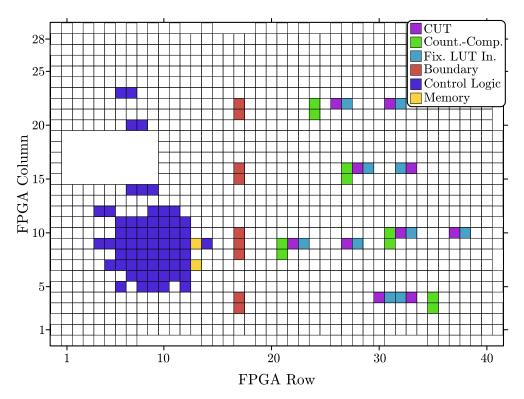

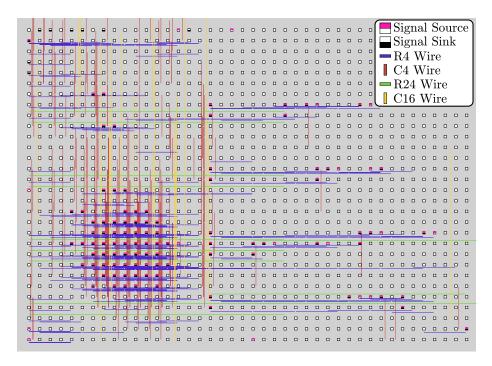

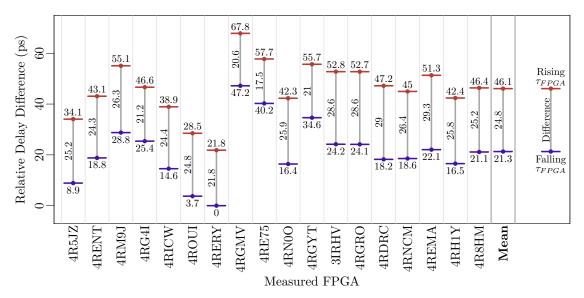

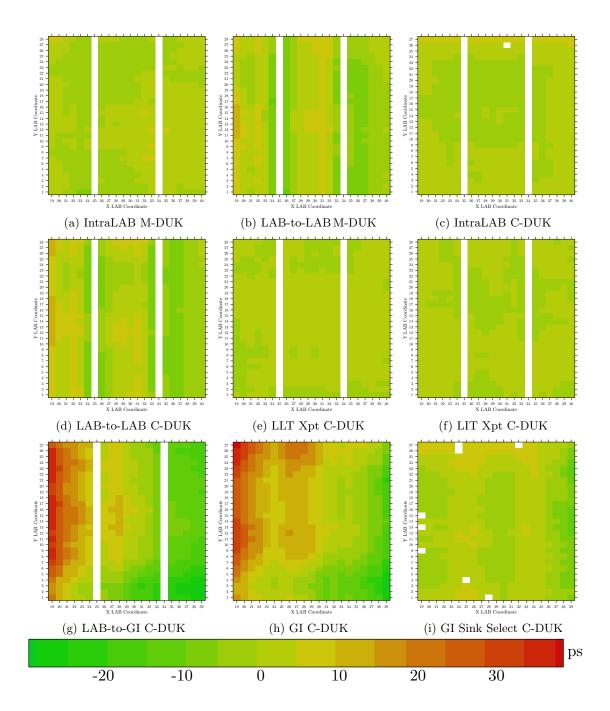

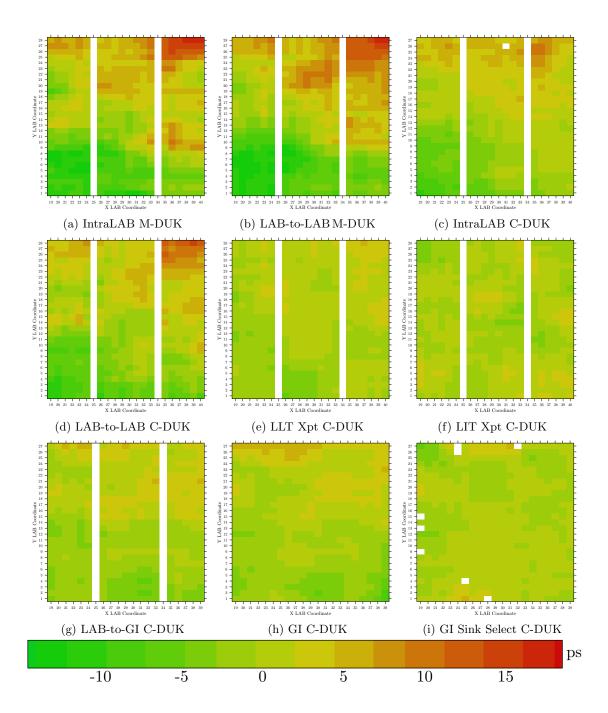

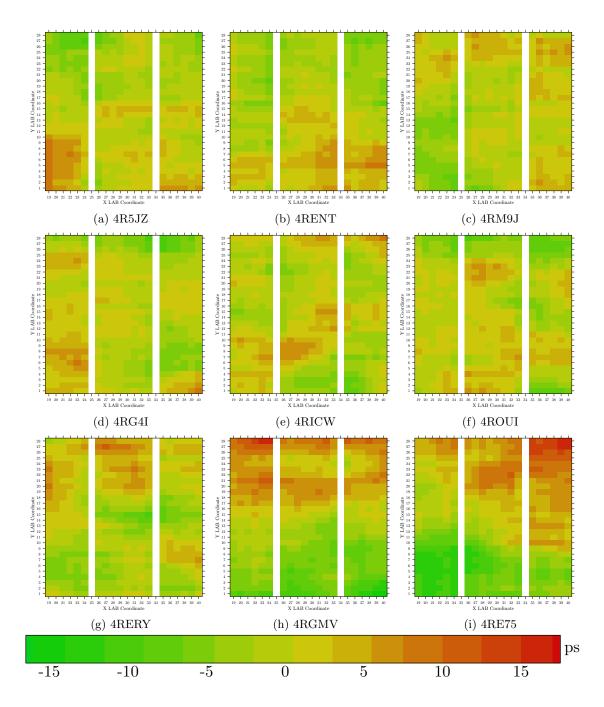

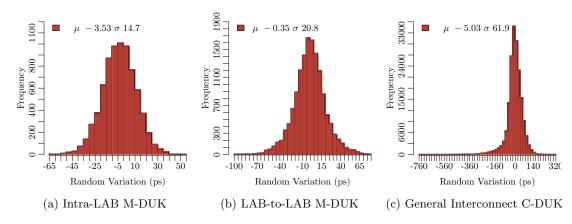

We apply Timing Extraction to 18 commercially available Altera Cyclone III (65 nm) FPGAs. We measure  $22\times28$  logic clusters and the interconnect within and between cluster. Timing Extraction decomposes this region into 1,356,182 components, classified into 10 categories, requiring 2,736,556 path measurements. With an accuracy of  $\pm3.2$  ps, our measurements reveal regional variation on the order of 50 ps, systematic variation from 30 ps to 70 ps, and random variation in the clusters with  $\sigma$ =15 ps and in the interconnect with  $\sigma$ =62 ps.

#### Degree Type

Dissertation

#### Degree Name

Doctor of Philosophy (PhD)

#### **Graduate Group**

Computer and Information Science

#### First Advisor

Andre M. DeHon

#### Keywords

FPGA, Measurement, Process Variation, Reconfigurable Circuits, Testing, Timing Extraction

| Subject Categories  Computer Engineering   Computer Sciences   Electrical and Electronics |  |  |  |  |

|-------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                           |  |  |  |  |

|                                                                                           |  |  |  |  |

|                                                                                           |  |  |  |  |

|                                                                                           |  |  |  |  |

|                                                                                           |  |  |  |  |

|                                                                                           |  |  |  |  |

|                                                                                           |  |  |  |  |

|                                                                                           |  |  |  |  |

|                                                                                           |  |  |  |  |

|                                                                                           |  |  |  |  |

|                                                                                           |  |  |  |  |

# GROK-FPGA: GENERATING REAL ON-CHIP KNOWLEDGE FOR FPGA FINE-GRAIN DELAYS USING TIMING EXTRACTION

Benjamin Gojman

#### A DISSERTATION

in

Computer and Information Science

Presented to the Faculties of the University of Pennsylvania

in

Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

2014

| Supervisor of Dissertation                        | Graduate Group Chairperson                    |

|---------------------------------------------------|-----------------------------------------------|

| André DeHon                                       | Lyle Ungar                                    |

| Professor of Electrical and Systems Engineering   | Professor of Computer and Information Science |

| Dissertation Committee:                           |                                               |

| Daniel E. Koditschek, Professor of Electrical and | Systems Engineering                           |

| Ali Jadbabaie, Professor of Electrical and System | s Engineering                                 |

| Insup Lee, Professor of Computer and Information  | on Science                                    |

| Mike Hutton, Altera                               |                                               |

# GROK-FPGA: GENERATING REAL ON-CHIP KNOWLEDGE FOR FPGA FINE-GRAIN DELAYS USING TIMING EXTRACTION

COPYRIGHT

2014

Benjamin Gojman

### Acknowledgements

First and foremost I have to thank my advisor, André DeHon. His support and motivation, infinite patience and guidance made this work possible. I have been extremely fortunate to have him as an advisor and friend. Thank you.

I also want to thank my committee members for their advice and feedback: Daniel Koditschek, Ali Jadbabaie, Insup Lee, and Mike Hutton.

The members of the IC Lab helped shape this work through discussions and feedback. In particular I want to thank Raphael Rubin, Nikil Mehta, Sirisha Nalmela, and Nicholas Howarth. Sirisha was instrumental in the developments of the Verilog used for this work. Without the work of Nick H. the experiments varying supply voltage would not have been possible. Nick M. developed the infrastructure to run millions of measurements, however, of most value was the insightful discussions we had developing the ideas presented here. Finally, Rafi's support, both technical and intellectual, was invaluable to me. Thank you all.

I want to thank my family Marcos and Karen, Mauricio, Tanya and Gabriel, and Monica Gojman for their love and encouragement, and Dita for knowing, with a pointed finger, that this work would come to a successful end.

Finally, I want to thank Emily Traver. Emily has been with me through this whole process, delighting in the ups and never failing to be there when things got rough. It has been a long road, and I am ever grateful you were with me through every step. Your boundless love and support made finishing this work possible.

### ABSTRACT

# GROK-FPGA: GENERATING REAL ON-CHIP KNOWLEDGE FOR FPGA FINE-GRAIN DELAYS USING TIMING EXTRACTION

Benjamin Gojman

#### André DeHon

Circuit variation is one of the biggest problems to overcome if Moore's Law is to continue. It is no longer possible to maintain an abstraction of identical devices without huge yield losses, performance penalties, and energy costs. Current techniques such as margining and grade binning are used to deal with this problem. However, they tend to be conservative, offering limited solutions that will not scale as variation increases. Conventional circuits use limited tests and statistical models to determine the margining and binning required to counteract variation. If the limited tests fail, the whole chip is discarded. On the other hand, reconfigurable circuits, such as FPGAs, can use more fine-grained, aggressive techniques that carefully choose which resources to use in order to mitigate variation. Knowing which resources to use and avoid, however, requires measurement of underlying variation.

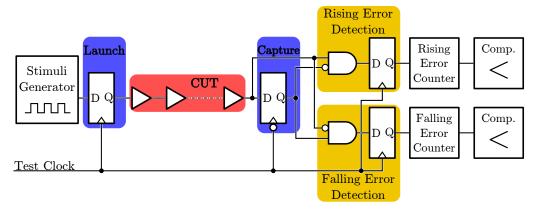

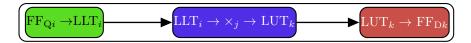

We present Timing Extraction, a methodology that allows measurement of process variation without expensive testers nor highly invasive techniques, rather, relying only on resources already available on conventional FPGAs. It takes advantage of the fact that we can measure the delay of logic paths between any two registers. Measuring enough paths, provides the information necessary to decompose the delay of each path into individual components—essentially, forming a system of linear equations. Determining which paths to measure requires simple graph transformation algorithms applied to a representation of the FPGA circuit. Ultimately, this process decomposes the FPGA into individual components and identifies which paths to measure for computing the delay of individual components.

We apply Timing Extraction to 18 commercially available Altera Cyclone III (65 nm) FPGAs. We measure  $22 \times 28$  logic clusters and the interconnect within and between cluster. Timing Extraction decomposes this region into 1,356,182 components, classified into 10 categories, requiring 2,736,556 path measurements. With an accuracy of  $\pm 3.2$  ps, our measurements reveal regional variation on the order of 50 ps, systematic variation from 30 ps to 70 ps, and random variation in the clusters with  $\sigma = 15$  ps and in the interconnect with  $\sigma = 62$  ps.

# Contents

| A            | ckno  | owledgements                                      | iii |

|--------------|-------|---------------------------------------------------|-----|

| A            | bstra | act                                               | iv  |

| $\mathbf{G}$ | lossa | ary                                               | xvi |

| 1            | Inti  | roduction                                         | 1   |

|              | 1.1   | Thesis                                            | 1   |

|              | 1.2   | Motivation                                        | 1   |

|              | 1.3   | Timing Extraction                                 | 2   |

|              | 1.4   | Overview                                          | 3   |

| 2            | Bac   | ckground                                          | 5   |

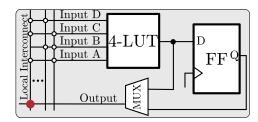

|              | 2.1   | Reconfigurable Circuits                           | 5   |

|              |       | 2.1.1 Ideal Model                                 | 6   |

|              |       | 2.1.2 Modern FPGAs                                | 7   |

|              | 2.2   | Transistor Properties                             | 8   |

|              |       | 2.2.1 Delay and Energy                            | 8   |

|              |       | 2.2.2 Current-Voltage Characteristics             | 10  |

|              | 2.3   | Variation Sources                                 | 11  |

|              |       | 2.3.1 Process Variation                           | 11  |

|              |       | 2.3.1.1 Manufacturing Process                     | 12  |

|              |       | 2.3.1.2 Variation Sources and Physical Effects    | 14  |

|              |       | 2.3.1.3 Physical Variation and Electrical Effects | 16  |

|              | 2.4   | Failure Model                                     | 17  |

|              | 2.5   | Managing Variation                                | 18  |

|              |       | 2.5.1 Testing                                     | 18  |

|              |       | 2.5.2 Margining                                   | 20  |

| Tin        | iming Extraction                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>23</b>                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

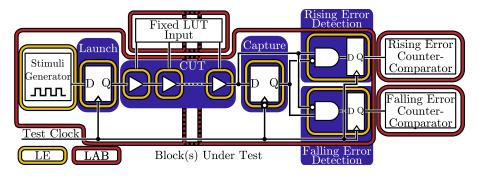

| 3.1        | 1 Path-Delay Measurement                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24                                                                                                                                                                                                                                                                                                                                                                                                                                            |

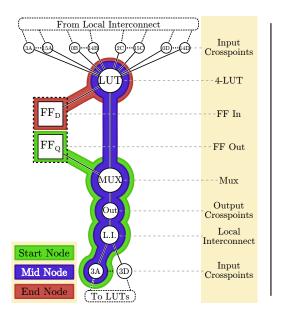

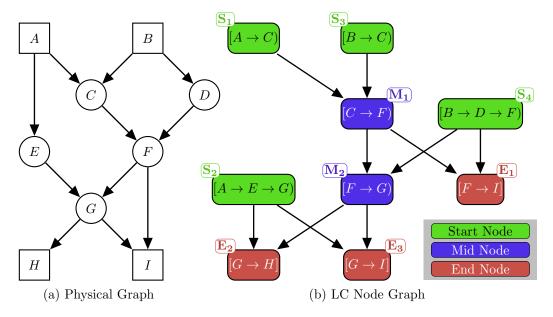

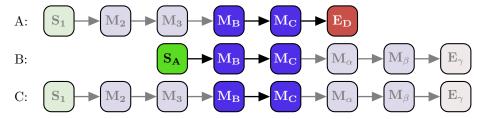

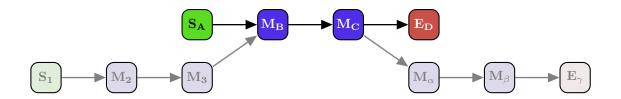

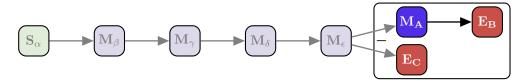

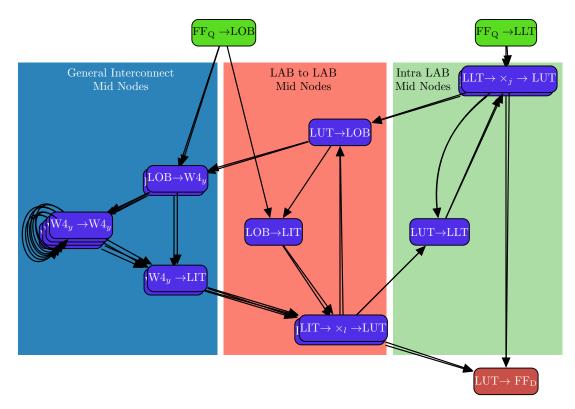

| 3.2        | 2 Logical Component Decomposition               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            | 3.2.1 LC Nodes as Components                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3        | 3 Alternate Basis                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                                                                                                                                                                                                                                                                                                                                                                                                            |

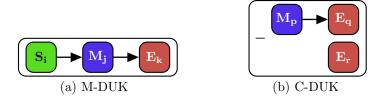

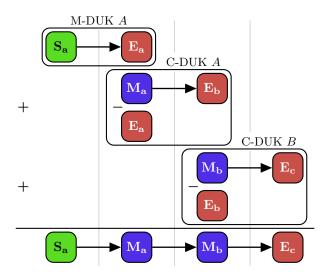

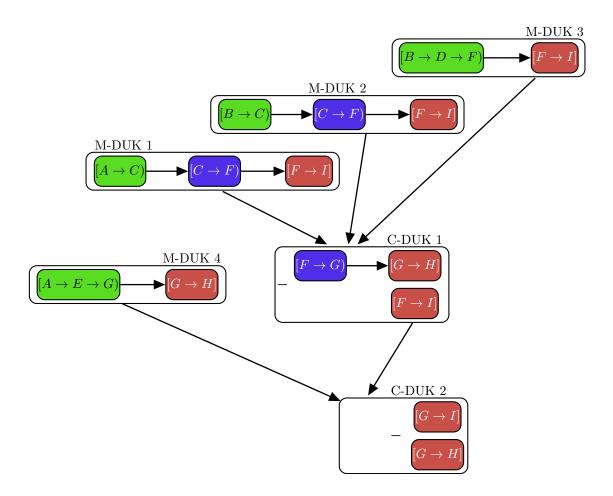

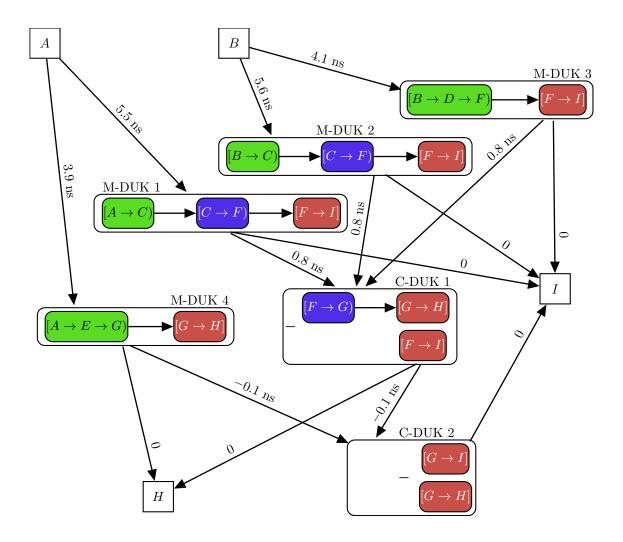

| 3.4        | 4 Discrete Units of Knowledge                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            | 3.4.1 DUK Types                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34                                                                                                                                                                                                                                                                                                                                                                                                                                            |

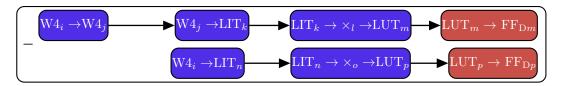

|            | 3.4.2 Incremental Path Computation              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34                                                                                                                                                                                                                                                                                                                                                                                                                                            |

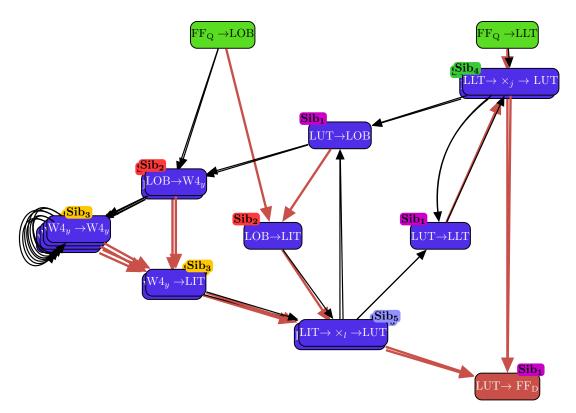

|            | 3.4.3 DUK Decomposition                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            | $3.4.3.1  {\rm LC\ Node\ Graph\ Annotation}  .$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                            |

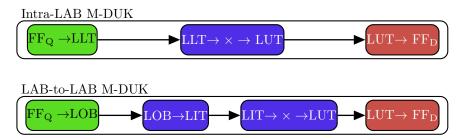

|            | 3.4.3.2 M-DUK Extraction                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36                                                                                                                                                                                                                                                                                                                                                                                                                                            |

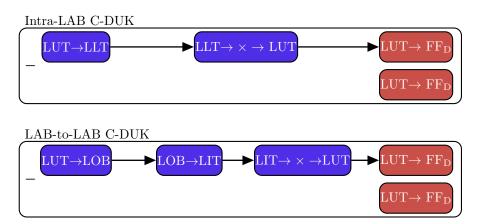

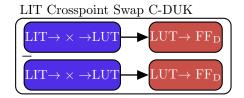

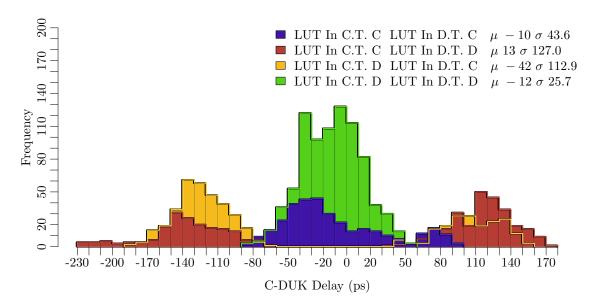

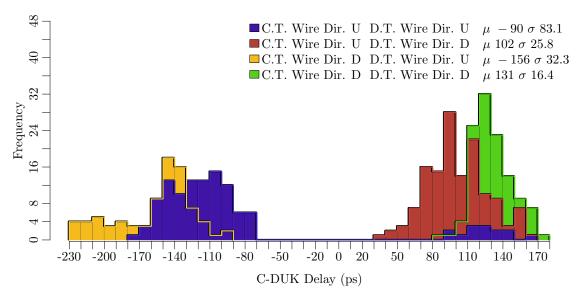

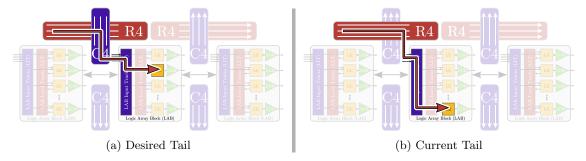

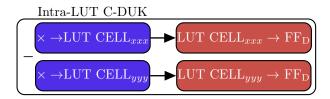

|            | 3.4.3.3 C-DUK Extraction                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38                                                                                                                                                                                                                                                                                                                                                                                                                                            |

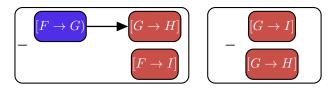

|            | 3.4.4 DUK Computation                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            | 3.4.5 DUK Accounting                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 41                                                                                                                                                                                                                                                                                                                                                                                                                                            |

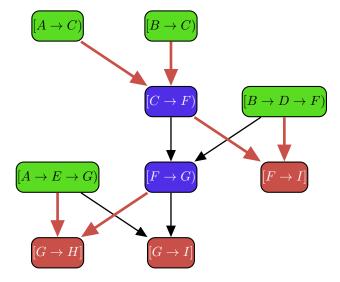

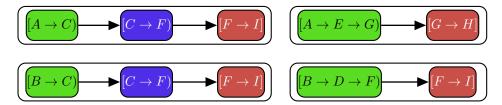

|            | 3.4.6 DUK Graph                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            | 3.4.7 Routing on the DUK Graph                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42                                                                                                                                                                                                                                                                                                                                                                                                                                            |

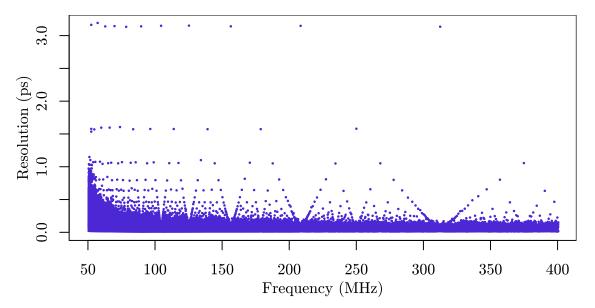

| 3.5        | 5 Measurement Precision                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                                                                                                                                                                                                                                                                                                                                                                                                                                            |

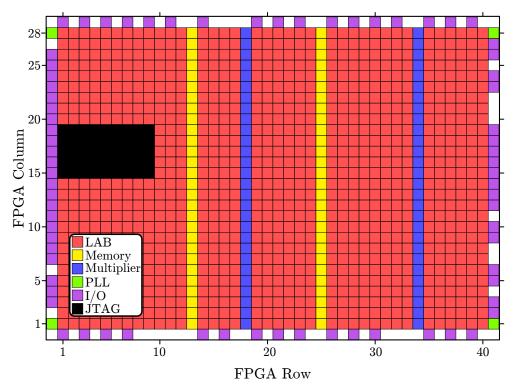

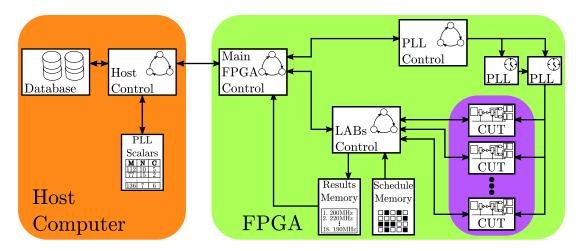

| Tin        | iming Extraction on Commercial FPGAs            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 47                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 47                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.1        | e yelone in omiceetare                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

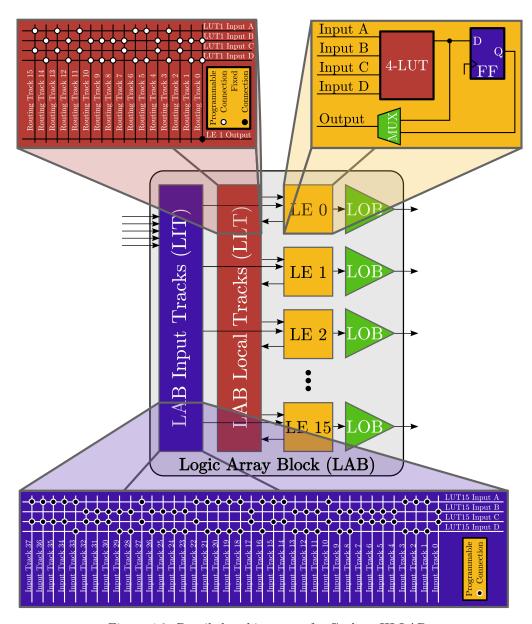

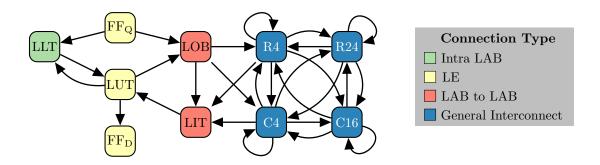

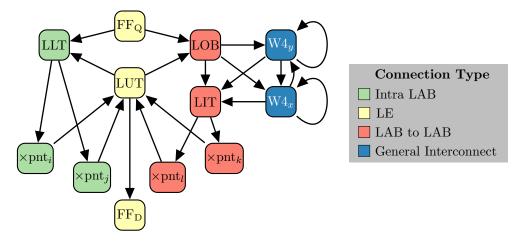

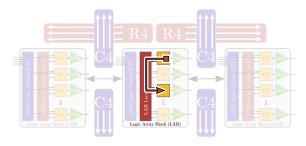

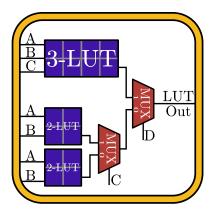

|            | 4 1 1 LAB Architecture                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48                                                                                                                                                                                                                                                                                                                                                                                                                                            |

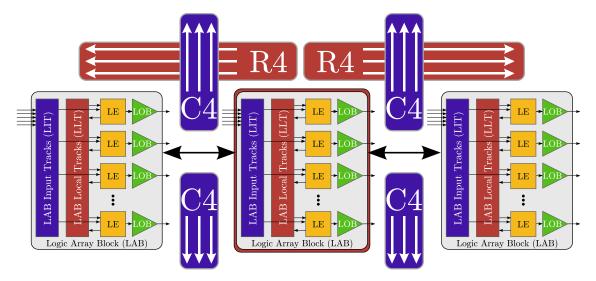

|            | 4.1.1 LAB Architecture                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48<br>49                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.2        | 4.1.2 Interconnect Architecture                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.2        | 4.1.2 Interconnect Architecture                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>52                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.3        | 4.1.2 Interconnect Architecture                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>52<br>53                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | 4.1.2 Interconnect Architecture                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>52<br>53<br>58                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.3        | 4.1.2 Interconnect Architecture                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>52<br>53<br>58<br>59                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.3        | 4.1.2 Interconnect Architecture                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>52<br>53<br>58<br>59<br>60                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.3        | 4.1.2 Interconnect Architecture                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>52<br>53<br>58<br>59<br>60<br>62                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.3        | 4.1.2 Interconnect Architecture                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>52<br>53<br>58<br>59<br>60<br>62<br>62                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.3        | 4.1.2 Interconnect Architecture                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>52<br>53<br>58<br>59<br>60<br>62<br>62<br>63                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.3        | 4.1.2 Interconnect Architecture                 | ement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49 52 53 58 59 60 62 62 63 64                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.3 4.4    | 4.1.2 Interconnect Architecture                 | ement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49<br>52<br>53<br>58<br>59<br>60<br>62<br>62<br>63<br>64<br>64                                                                                                                                                                                                                                                                                                                                                                                |

| 4.3<br>4.4 | 4.1.2 Interconnect Architecture                 | ement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49 52 53 58 59 60 62 62 63 64                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | 3.5<br>3.5<br>3.7                               | 3.2       Logical Component Decomposition         3.2.1       LC Nodes as Components         3.3       Alternate Basis         3.4       Discrete Units of Knowledge         3.4.1       DUK Types         3.4.2       Incremental Path Computation         3.4.3       DUK Decomposition         3.4.3.1       LC Node Graph Annotation         3.4.3.2       M-DUK Extraction         3.4.3.3       C-DUK Extraction         3.4.4       DUK Computation         3.4.5       DUK Accounting         3.4.6       DUK Graph         3.4.7       Routing on the DUK Graph         3.5       Measurement Precision         Timing Extraction on Commercial FPGAs         4.1       Cyclone Architecture | 3.2 Logical Component Decomposition 3.2.1 LC Nodes as Components 3.3 Alternate Basis 3.4 Discrete Units of Knowledge 3.4.1 DUK Types 3.4.2 Incremental Path Computation 3.4.3 DUK Decomposition 3.4.3.1 LC Node Graph Annotation 3.4.3.2 M-DUK Extraction 3.4.3.3 C-DUK Extraction 3.4.4 DUK Computation 3.4.5 DUK Accounting 3.4.6 DUK Graph 3.4.7 Routing on the DUK Graph 3.5 Measurement Precision  Timing Extraction on Commercial FPGAs |

| $\mathbf{A}_{\mathbf{J}}$ | ppen | dices                                         | 122 |

|---------------------------|------|-----------------------------------------------|-----|

| 7                         | Con  | clusions                                      | 120 |

|                           | 6.4  | Improved Variation Analysis                   | 119 |

|                           | 6.3  | Beyond the Cyclone III and Cyclone IV FPGAs   | 118 |

|                           | 6.2  | Beyond Logic Blocks and General Interconnect  | 117 |

|                           | 6.1  | Measurement Control and Runtime               | 116 |

| 6                         | Futu | ure Work                                      | 116 |

|                           | 5.5  | Random Variation                              | 114 |

|                           |      | 5.4.1 Systematic Delay Contributions          |     |

|                           | 5.4  | Systematic Variation                          |     |

|                           |      | 5.3.2 Random Regional Variation               |     |

|                           |      | 5.3.1 Systematic Regional Variation           |     |

|                           | 5.3  | Regional Variation                            |     |

|                           | 5.2  | Computing $\tau_0$ and $\tau_{FPGA}$          |     |

|                           | 5.1  | Variation Model                               | 100 |

| 5                         | Vari | iation Analysis                               | 99  |

|                           | 4.14 | Chapter Summary                               | 97  |

|                           |      | Scaling                                       | 96  |

|                           |      | Measurement Consistency                       | 94  |

|                           |      | Measurement Runtime                           | 91  |

|                           |      | CAD Vs. Measured Delays                       | 89  |

|                           | 4.9  | Effects of $V_{DD}$ on Variation              | 86  |

|                           |      | 4.8.1 Results                                 | 86  |

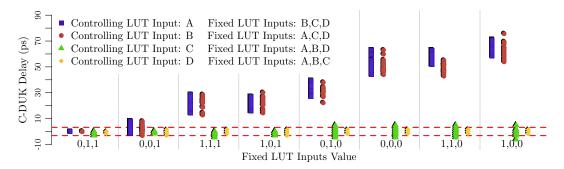

|                           | 4.8  | Intra-LUT C-DUK                               | 85  |

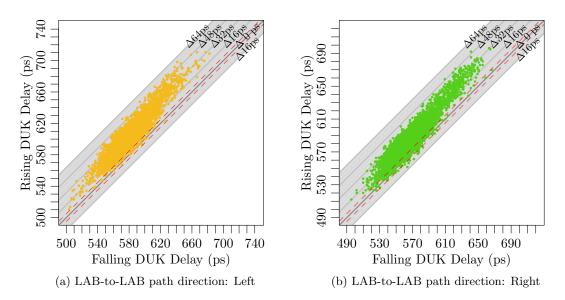

|                           | 4.7  | Falling Vs. Rising Transitions                | 82  |

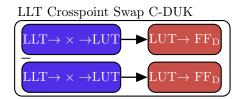

|                           |      | 4.6.9 LLT and LIT Crosspoint Swap C-DUKs      | 77  |

|                           |      | 4.6.8 General Interconnect Sink Select C-DUKs | 77  |

|                           |      | 4.6.7 General Interconnect C-DUKs             | 76  |

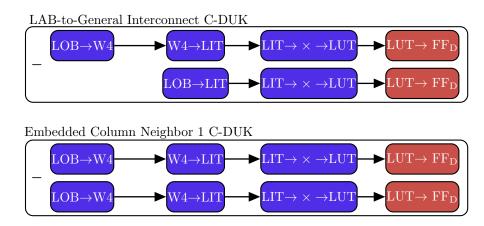

|                           |      | 4.6.6 Embedded Column Neighbor C-DUKs         | 73  |

|                           |      | 4.6.5 LAB-to-General Interconnect C-DUKs      | 71  |

|                           |      | 4.6.4 LAB-to-LAB C-DUKs                       | 68  |

|                           |      | 4.6.3 Intra-LAB C-DUKs                        | 68  |

| A  | Ope   | eration | al, Environmental, and Aging Effects                                                                                 | 123 |

|----|-------|---------|----------------------------------------------------------------------------------------------------------------------|-----|

|    | A.1   | Opera   | tional and Environmental Variation                                                                                   | 123 |

|    |       | A.1.1   | Temperature                                                                                                          | 123 |

|    |       | A.1.2   | Power Supply                                                                                                         | 125 |

|    |       | A.1.3   | Crosstalk                                                                                                            | 125 |

|    | A.2   | Aging   | Effects                                                                                                              | 126 |

|    |       | A.2.1   | Electromigration                                                                                                     | 126 |

|    |       | A.2.2   | Hot carrier injection                                                                                                | 127 |

|    |       | A.2.3   | $\label{thm:continuous} \mbox{Time-Dependant Dielectric Breakdown} \; . \; . \; . \; . \; . \; . \; . \; . \; . \; $ | 127 |

|    |       | A.2.4   | Negative Bias Temperature Instability                                                                                | 128 |

| Bi | bliog | graphy  |                                                                                                                      | 130 |

# List of Tables

| 4.1 | Device parameters for the Cyclone III EP3C16F256C8N on the BeMicro board $[8]$ .      | 48 |

|-----|---------------------------------------------------------------------------------------|----|

| 4.2 | Number of DUKs extracted from the region spanned from LAB $(19,1)$ to LAB $(40,28)$ . | 65 |

| 4.3 | Average delay and frequency count breakdown over all bitstreams and measured          |    |

|     | FPGAs                                                                                 | 93 |

| 5.1 | $\tau_0$ for each of the 10 DUK types                                                 | 01 |

# List of Figures

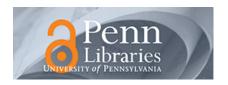

| 2.1 | Diagram of a simple FPGA showing the logic block (LB), switch box (SBox), con-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | nection box (CBox), and external IO. Small circles in the SBox and CBox represent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|     | programmable switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6  |