Publicly Accessible Penn Dissertations

1-1-2015

# Safety-Assured Model-Based Development of Real-Time Embedded Software for the Gpca Infusion Pump

Baekgyu Kim University of Pennsylvania, bgkim0110@gmail.com

Follow this and additional works at: http://repository.upenn.edu/edissertations

Part of the Computer Sciences Commons

#### Recommended Citation

Kim, Baekgyu, "Safety-Assured Model-Based Development of Real-Time Embedded Software for the Gpca Infusion Pump" (2015). Publicly Accessible Penn Dissertations. 1809.

http://repository.upenn.edu/edissertations/1809

This paper is posted at Scholarly Commons. http://repository.upenn.edu/edissertations/1809 For more information, please contact libraryrepository@pobox.upenn.edu.

### Safety-Assured Model-Based Development of Real-Time Embedded Software for the Gpca Infusion Pump

#### **Abstract**

Many safety-critical embedded systems must meet safety requirements associated with timing constraints. Not only shall a system read/write correct input or output values, but also those operations shall be performed with the right timing. Failing to meet those timing constraints results in serious safety issues (e.g., medical device malfunctions may harm patients). It is difficult to develop complex embedded software in a correct way without rigorous and systematic handling of various sources that affect the timed behavior of a system.

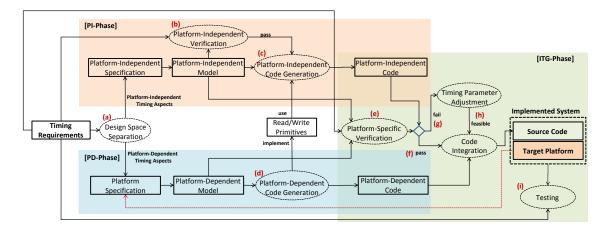

We propose the model-based development framework that enables timing aspects of a system to be formally modeled, verified, and further implemented in a systematic way.

The fundamental idea is to separate the timing concerns of the platform-independent and the platform-dependent aspects of a system. In the platform-independent development phase, input and output timed interactions between a system and its environment is modeled and verified using state-transition formalism (e.g., UPPAAL) by hiding platform-dependent timing details. In the platform-dependent development phase, such platform-dependent timing details are modeled using architectural modeling languages (e.g., AADL) that are necessary to execute the platform-independent code on a particular platform, such as internal interactions among software components (e.g., threads) and hardware components (e.g., sensors and actuators). The platform-independent code and the platform-dependent code are independently developed from the different levels of timing abstractions, and composed together in the integration phase. In this phase, we propose a way to systematically extend the platform-independent model into different platform-specific models, which formally characterize the implementation-level timed behavior that can be verified for timing requirement conformance. In case this verification step fails, we propose a way to adjust the timing parameters of the platform-independent code by compensating for the platform-dependent processing delays in such a way that the resulting implementation meets the timing requirements verified in the platform-independent model.

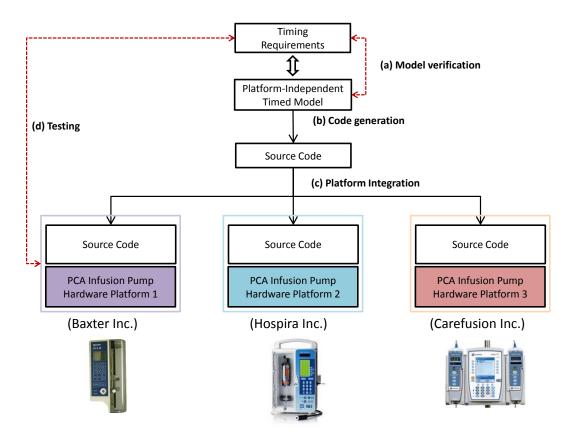

Applicability of this development approach was demonstrated by developing software running on several Patient-Controlled Analgesia (PCA) infusion pump systems. We hope that this approach is also applicable to other safety-critical domains where generic software needs to be developed independently of a particular platform, and integrated with many different platforms in a way that conforms to timing requirements.

#### Degree Type

Dissertation

#### Degree Name

Doctor of Philosophy (PhD)

#### **Graduate Group**

Computer and Information Science

# First Advisor Insup Lee Second Advisor Oleg Sokolsky **Subject Categories** Computer Sciences

## SAFETY-ASSURED MODEL-BASED DEVELOPMENT OF REAL-TIME EMBEDDED SOFTWARE FOR THE GPCA INFUSION PUMP

#### BaekGyu Kim

#### A DISSERTATION

in

Computer and Information Science

Presented to the Faculties of the University of Pennsylvania

in

Partial Fulfillment of the Requirements for the

Degree of Doctor of Philosophy

2015

Supervisor of Dissertation

Co-Supervisor of Dissertation

Insup Lee

Oleg Sokolsky

Professor of

Research Associate Professor of

Computer and Information Science

Graduate Group Chairperson

Lyle Ungar, Professor of Computer and Information Science

Dissertation Committee

Linh T.X. Phan, Research Assistant Professor of Computer and Information Science Rahul Mangharam, Associate Professor of Electrical and Systems Engineering Joseph Devietti, Assistant Professor of Computer and Information Science Mats Heimdahl, Professor of Computer Science (University of Minnesota) Paul Jones, Senior Systems/Software Engineer (U.S. Food and Drug Administration)

# SAFETY-ASSURED MODEL-BASED DEVELOPMENT OF REAL-TIME EMBEDDED SOFTWARE FOR THE GPCA INFUSION PUMP © COPYRIGHT 2015 BaekGyu Kim This work is licensed under the Creative Commons Attribution NonCommercial-ShareAlike 3.0 License To view a copy of this license, visit

http://creativecommons.org/licenses/by-nc-sa/3.0/

#### ACKNOWLEDGEMENTS

This dissertation could be completed based on the advice, feedback and support from the University of Pennsylvania (UPenn) faculty and students, external collaborators and my family.

First and foremost, I would like to express my deep appreciation to my advisor Prof. Insup Lee, who gave me the chance to study here at UPenn. Without this opportunity, this dissertation would not even have been possible. Throughout my Ph.D research, not only did he provide me with valuable advice in a way to keep my research on the right track, but he also patiently waited for me in spite of my slow progress for a long time. I believe that the way he has helped, guided me and taught me largely influence me in tackling more difficult problems that I will encounter in the future.

I am also grateful to my co-advisor Prof. Oleg Sokolsky, who guided me to complete my dissertation. He was willing to give me specific feedback on what I proposed, and guided me to approach the solution step by step. He was able to pinpoint exactly what was right or wrong in my research topic approach, so that I could adjust my research direction accordingly. Without his help, I believe the completion of this dissertation would have been further delayed.

The final dissertation was able to be greatly improved through the labor of my dissertation committee members, Linh, Rahul, Joseph, Mats and Paul. They guided me to identify the missing parts and highlighted the major contribution of this work in a better way. I feel that the final version became much closer to what I originally intended, compared to its initial version. This was possible through reflecting on the valuable feedback of my committee members, which I truly appreciated.

I would like to thank everyone else at UPenn who gave me valuable feedback on my work. Especially, I appreciate all the Ph.D students who provided me with feedback during our weekly meetings so that I could look at my research from different angles that I could not think of myself. In addition, through the contribution of each Ph.D. student who presented their work on a regular basis, I could accumulate and expand my knowledge of relevant issues in the medical devices domain. I also want to thank Linh who was always willing to provide detailed feedback on my ideas and guided me to write papers in a more precise and unambiguous way. Anaheed and Lu, to whom I want to express my appreciation, are the two postdoctoral researchers who collaborated with me to develop several research ideas through valuable discussions. Thanks to David Arney who helped me to accumulate background knowledge of the infusion pump safety issues in my early Ph.D studies. I also appreciate several masters' students who added their implementation efforts to build the research prototype platform to demonstrate the research ideas presented in this dissertation.

I also appreciate several external researchers who worked hard to collaborate with me for a long time. The interaction with the researchers at the University of Minnesota including Mats, Sanjay, Anitha, John and Dongjiang helped me to expand the way to approach the same problem from many different perspectives. I also had the chance to collaborate with the researchers at DGIST. I especially appreciate the Master's student, Hyeon I Hwang, at DGIST who spent hard time to complete this collaborative work. I also appreciate his co-advisors, Prof. Sang H. Son and Prof. Taejoon Park, for their patience that allowed me to continue working with Hyeon I.

I would like to express my special appreciation to the researchers at the U.S. Food and Drug Administration (FDA), especially to Paul Jones and Yi Zhang in the Center for Devices and Radiological Health (CDRH). Not only did I interact with Paul and Yi through email and conference calls, but also traveled to CDRH four times (Oct. 2010, Feb., July., Dec. 2011), and stayed several days for each visit for in-depth discussion about infusion pump safety issues through the support of the NSF/FDA Scholar in Residence at FDA program (NSF/FDA SIR). This series of interactions enabled me to understand the safety issues of medical devices from the perspectives of the industry and government regulators.

In addition, Paul and Yi were very supportive in explaining the research conducted in their software research lab, and provided necessary information that helped me to apply my academic research to the infusion pump domain. The GPCA safety model and safety requirements provided by their research lab were a good starting point for me to accumulate the domain knowledge of infusion pumps and its safety issues from a technical point of view. The technical knowledge that I obtained from them has played an important role not only in applying the model-based development approach to the infusion pump domain to enhance software safety throughout my Ph.D studies, but also in continuing my future career in broader safety-critical domains.

I also want to show my deep appreciation to my former advisor Prof. SoonJu Kang at Kyungpook National University, who advised me to complete my master's degree. The hands-on implementation experience for embedded systems that I learned during this period greatly helped me to build the research prototype system in my Ph.D studies as well. In addition, he encouraged me to continue my research studying abroad, which eventually enabled me to study at UPenn.

Finally, all my Ph.D research could not have been completed without the support from my family. I truly appreciate my family's endeavors which allowed me to fully focus on my research throughout my Ph.D studies.

This research was supported in part by the NSF CNS-1035715, NSF FDA Scholar In Residence 1042829, and the DGIST Research and Development Program of the Ministry of Science, ICT and Future Planning of Korea (CPS Global Center).

#### ABSTRACT

## SAFETY-ASSURED MODEL-BASED DEVELOPMENT OF REAL-TIME EMBEDDED SOFTWARE FOR THE GPCA INFUSION PUMP

BaekGyu Kim

Insup Lee

#### Oleg Sokolsky

Many safety-critical embedded systems must meet safety requirements associated with timing constraints. Not only shall a system read/write correct input or output values, but also those operations shall be performed with the right timing. Failing to meet those timing constraints results in serious safety issues (e.g., medical device malfunctions may harm patients). It is difficult to develop complex embedded software in a correct way without rigorous and systematic handling of various sources that affect the timed behavior of a system.

We propose the model-based development framework that enables timing aspects of a system to be formally modeled, verified, and further implemented in a systematic way. The fundamental idea is to separate the timing concerns of the platform-independent and the platform-dependent aspects of a system. In the platform-independent development phase, input and output timed interactions between a system and its environment is modeled and verified using state-transition formalism (e.g., UPPAAL) by hiding platform-dependent timing details. In the platform-dependent development phase, such platform-dependent timing details are modeled using architectural modeling languages (e.g., AADL) that are necessary to execute the platform-independent code on a particular platform, such as internal interactions among software components (e.g., threads) and hardware components (e.g., sensors and actuators). The platform-independent code and the platform-dependent code are independently developed from the different levels of timing abstractions, and com-

posed together in the integration phase. In this phase, we propose a way to systematically extend the platform-independent model into different platform-specific models, which formally characterize the implementation-level timed behavior that can be verified for timing requirement conformance. In case this verification step fails, we propose a way to adjust the timing parameters of the platform-independent code by compensating for the platform-dependent processing delays in such a way that the resulting implementation meets the timing requirements verified in the platform-independent model.

Applicability of this development approach was demonstrated by developing software running on several Patient-Controlled Analgesia (PCA) infusion pump systems. We hope that this approach is also applicable to other safety-critical domains where generic software needs to be developed independently of a particular platform, and integrated with many different platforms in a way that conforms to timing requirements.

#### TABLE OF CONTENTS

| ACKN(  | OWLEDGEMENT                                                 | iii |

|--------|-------------------------------------------------------------|-----|

| ABSTR  | ACT                                                         | vi  |

| LIST O | F TABLES                                                    | xi  |

| LIST O | F ILLUSTRATIONS                                             | xiv |

| СНАРТ  | TER 1: Introduction                                         | 1   |

| 1.1    | Motivation                                                  | 1   |

| 1.2    | Background: Infusion Pumps Safety and GIP Project           | 2   |

| 1.3    | The Research Goal and Challenges                            | 5   |

| 1.4    | The Approach Overview                                       | 8   |

| 1.5    | Contribution                                                | 13  |

| 1.6    | Dissertation Outline                                        | 14  |

| СНАРТ  | ΓER 2: Related Work                                         | 16  |

| 2.1    | The software development processes                          | 16  |

| 2.2    | Formal verification techniques for the platform integration | 18  |

| 2.3    | The code generation techniques                              | 21  |

| 2.4    | The testing techniques                                      | 25  |

| СНАРТ  | ΓER 3: Background                                           | 28  |

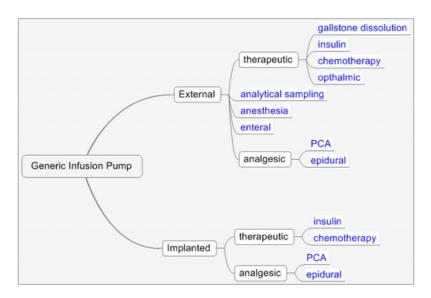

| 3.1    | Infusion Pump Preliminary                                   | 28  |

| 3.2    | Generic PCA Pump Safety Resources                           | 32  |

| СНАРТ  | ΓER 4: Platform-Independent Development Phase               | 36  |

| 11     | The Problem Statements and Challenges                       | 36  |

|    | 4.2  | The Approach Overview of the PI-Phase                  | 38  |

|----|------|--------------------------------------------------------|-----|

|    | 4.3  | Platform-Independent Modeling Process                  | 40  |

|    | 4.4  | Platform-Independent Verification Process              | 48  |

|    | 4.5  | Platform-Independent Code Generation Process           | 53  |

|    | 4.6  | Summary of the PI-Phase                                | 67  |

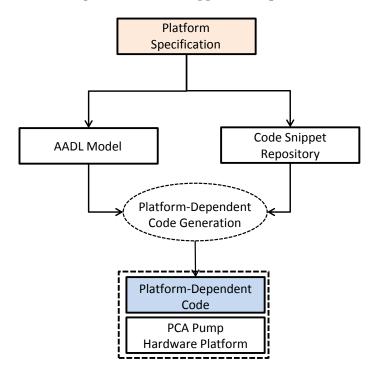

| СН | APT  | ER 5: Platform-Dependent Development Phase             | 69  |

|    | 5.1  | The Problem Statements and Challenges                  | 69  |

|    | 5.2  | The Approach Overview of the PD-Phase                  | 71  |

|    | 5.3  | Platform-Dependent Software Aspects                    | 73  |

|    | 5.4  | Platform-Dependent Modeling using AADL                 | 75  |

|    | 5.5  | Platform-Dependent Code Snippet Repositories           | 79  |

|    | 5.6  | Platform-Dependent Code Generation Process             | 90  |

|    | 5.7  | Summary of the PD-Phase                                | 95  |

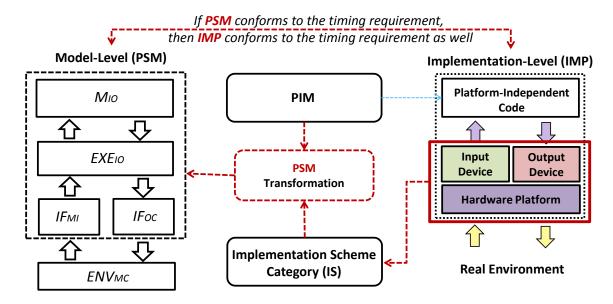

| СН | APT  | ER 6: Integration Phase (Part 1)                       | 97  |

|    | 6.1  | The Problem Statements and Challenges of the ITG-Phase | 97  |

|    | 6.2  | The Approach Overview of the ITG-Phase                 | 98  |

|    | 6.3  | The Problem Statement ( $PSM$ Verification)            | 100 |

|    | 6.4  | The Approach Overview ( $PSM$ Verification)            | 105 |

|    | 6.5  | Implementation Schemes                                 | 106 |

|    | 6.6  | Modular Transformation from $PIM$ to $PSM$             | 114 |

|    | 6.7  | The Property of the $PSM$                              | 129 |

|    | 6.8  | Case Study of the <i>PSM</i> Verification              | 133 |

|    | 6.9  | Summary of the <i>PSM</i> Verification                 | 135 |

|    | 6.10 | The Problem Statement (Timing Testing)                 | 135 |

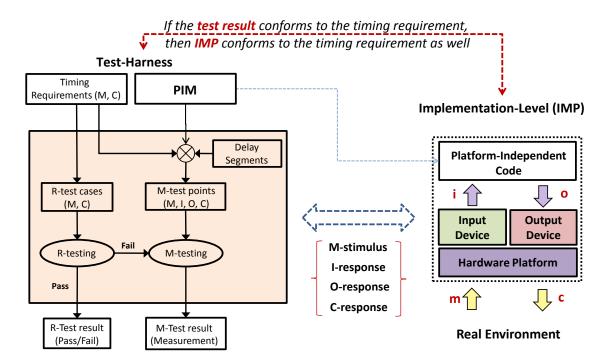

|    | 6.11 | The Approach Overview (Timing Testing)                 | 137 |

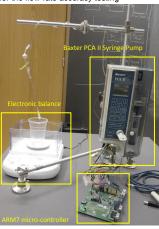

|    | 6.12 | Case Study of the Timing Testing                       | 143 |

|    | 6.13 | Summary of the Timing Testing                          | 145 |

| СНАРТ                  | TER 7: Integration Phase (Part 2)                                         | 147 |

|------------------------|---------------------------------------------------------------------------|-----|

| 7.1                    | The Problem Statements and Challenges                                     | 147 |

| 7.2                    | The Approach Overview                                                     | 149 |

| 7.3                    | Problem Formulation                                                       | 150 |

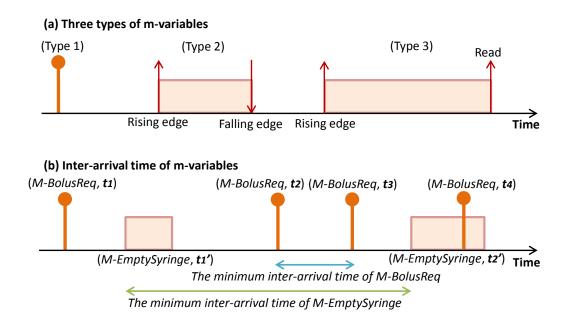

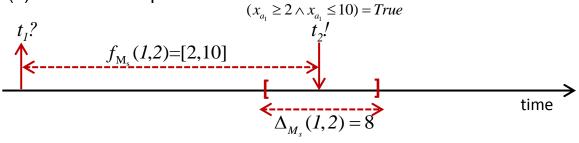

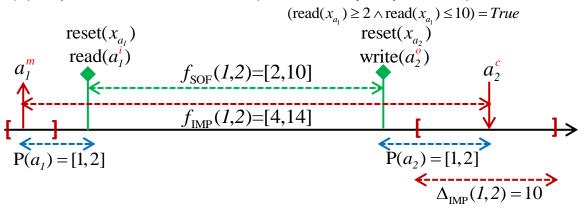

| 7.4                    | Computing $f_{M_s}$ and $f_{IMP}$                                         | 154 |

| 7.5                    | Delay-Bound Adjustment using Integer Linear Programming                   | 163 |

| 7.6                    | Case Study: Infusion Pump Systems                                         | 173 |

| 7.7                    | Summary of the Platform-Specific Code Generation                          | 179 |

| CHAPTER 8: Conclusions |                                                                           |     |

| СНАРТ                  | TER A:                                                                    | 185 |

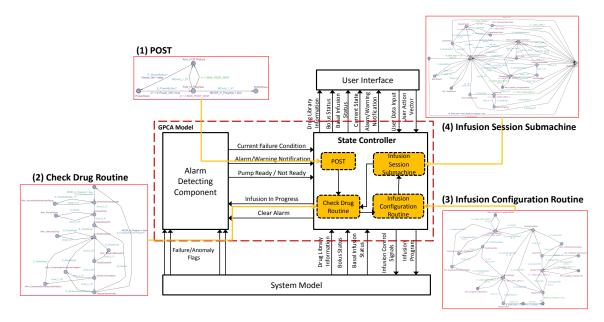

| A.1                    | The GPCA UPPAAL model                                                     | 185 |

| A.2                    | Appendix: Code Generation with Timing                                     | 185 |

| A.3                    | The Experimental Platforms for the GPCA Reference Implementations $$ . $$ | 186 |

|                        |                                                                           |     |

#### LIST OF TABLES

| TABLE 1:  | Example Hazards from GPCA Hazard Analysis                                                               | 32  |

|-----------|---------------------------------------------------------------------------------------------------------|-----|

| TABLE 2:  | Example GPCA Safety Requirements                                                                        | 34  |

| TABLE 3:  | Categorization of GPCA Safety Requirements                                                              | 50  |

| TABLE 4:  | Mapping between Safety Requirements and UPPAAL queries                                                  | 53  |

| TABLE 5 : | Categorization of code snippets                                                                         | 80  |

| TABLE 6:  | Information extracted from the AADL model                                                               | 91  |

| TABLE 7:  | $\label{thm:eq:cheme} \mbox{Implementation Scheme for Environment-to-Platform Interaction } (\emph{m},$ |     |

|           | c)                                                                                                      | 108 |

| TABLE 8:  | Implementation Scheme for Platform-to-Code Interaction $(i,\ o)$                                        | 112 |

| TABLE 9:  | The experiment result                                                                                   | 134 |

| TABLE 10: | Testing Results: Measured time-delays for the bolus request scenario                                    |     |

|           | in REQ1                                                                                                 | 145 |

| TABLE 11: | The measured platform processing delay of the Baxter II syringe                                         |     |

|           | pump platform                                                                                           | 176 |

| TABLE 12: | The parameter assignment ( $T_{\sf s}$ ) of ${\sf M}_{\sf s}$ and the parameter assignment              |     |

|           | $(T_{c})$ of $M_{c}$                                                                                    | 176 |

| TABLE 13: | The validation result of the delay-bound inclusion constraint of the                                    |     |

|           | GPCA reference implementation                                                                           | 177 |

| TABLE 14: | Notations used in Chapter 7                                                                             | 192 |

| TABLE 15: | The Linear Constraints for Model 4 (Figure 39 in Chapter 7) $$                                          | 193 |

| TABLE 16: | The comparison of three commercial PCA infusion pump hardware                                           |     |

|           | platforms                                                                                               | 193 |

#### LIST OF ILLUSTRATIONS

| FIGURE 1:  | The overview of the GPCA reference implementation project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6   |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

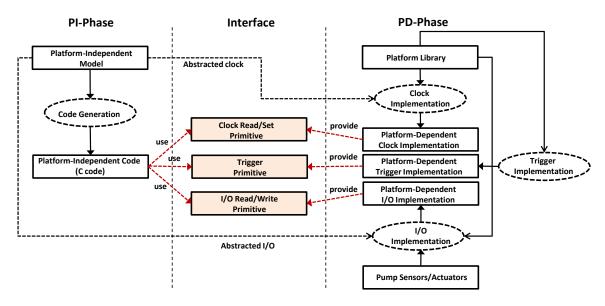

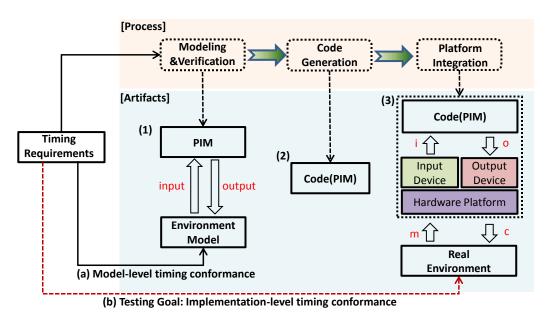

| FIGURE 2:  | The approach overview of the safety-assured model-based imple-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|            | mentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9   |

| FIGURE 3:  | Generic Infusion Pump (GIP) Class Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28  |

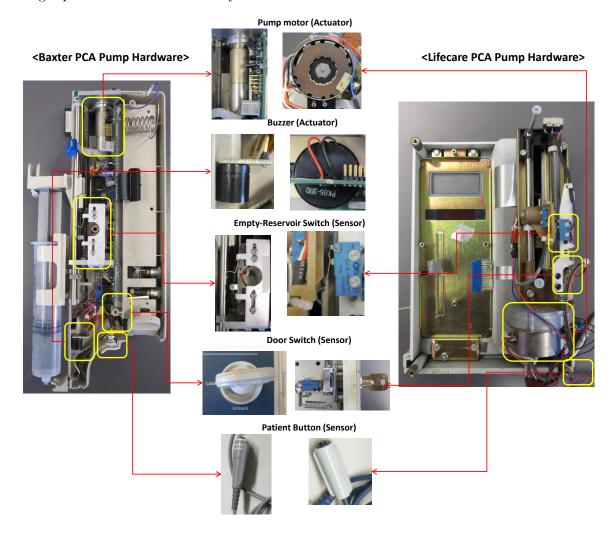

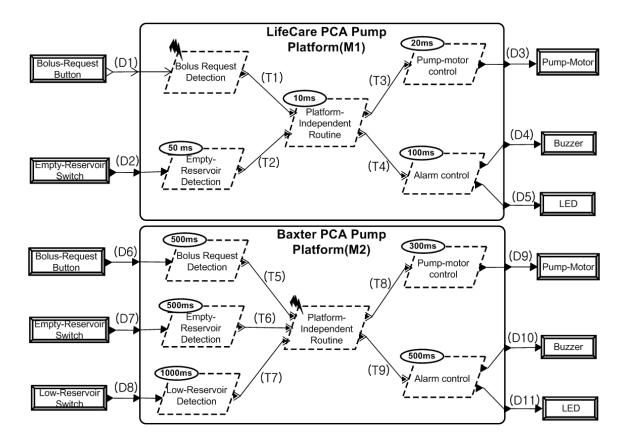

| FIGURE 4:  | PCA Infusion Pump Hardware Platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30  |

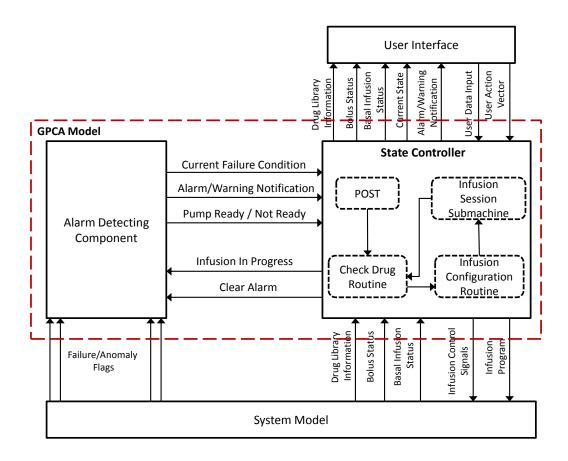

| FIGURE 5:  | System Architecture of the FDA's GPCA Pump Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35  |

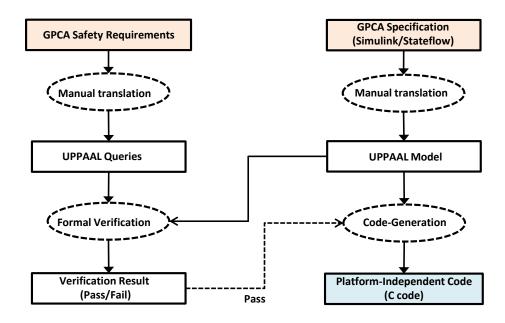

| FIGURE 6:  | The platform-independent phase of the safety-assured model-based                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|            | implementation  .  .  .  .  .  .  .  .  .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40  |

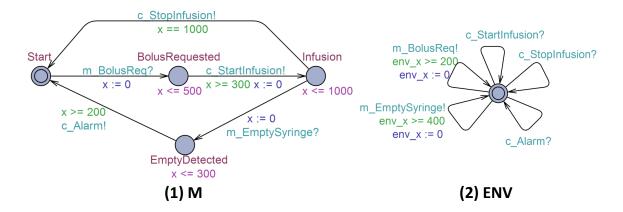

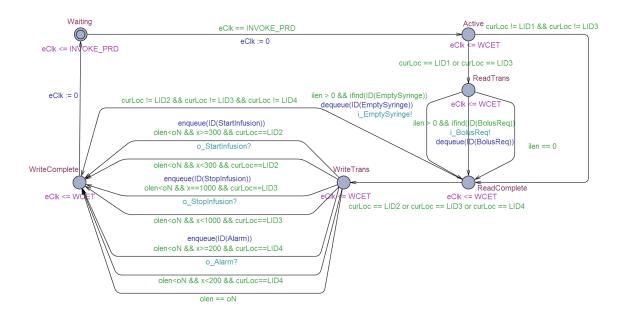

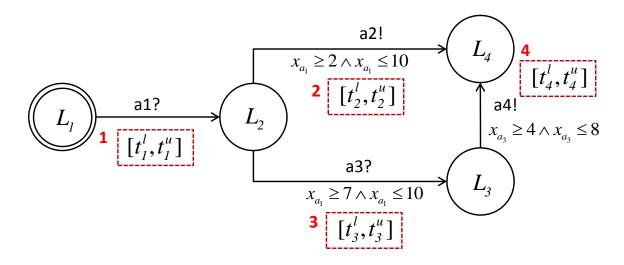

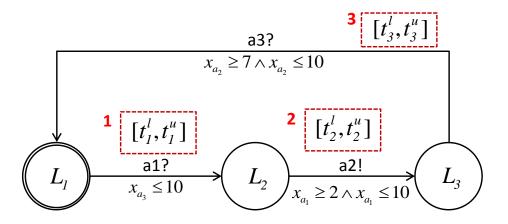

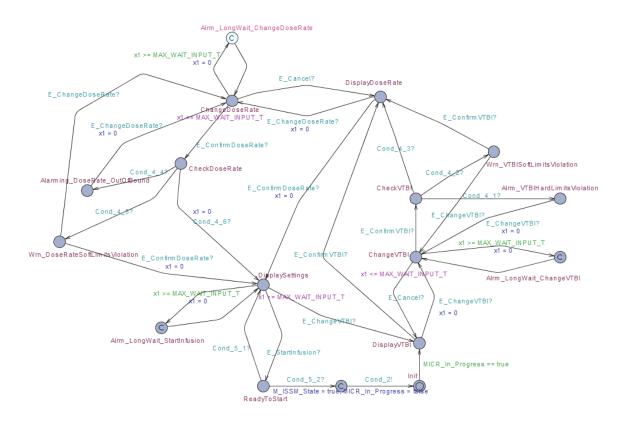

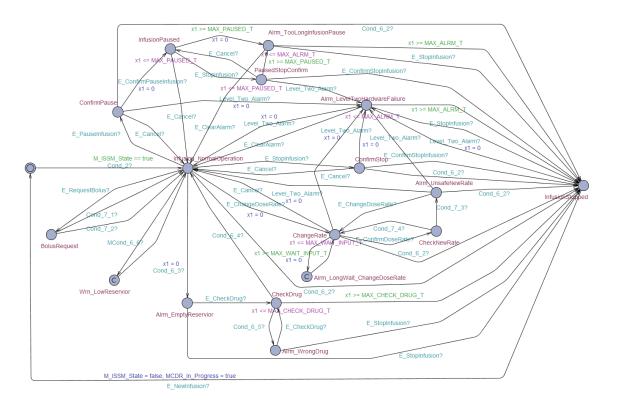

| FIGURE 7 : | The mapping between the GPCA model and the UPPAAL model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 44  |

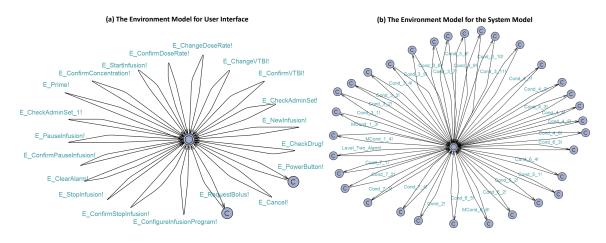

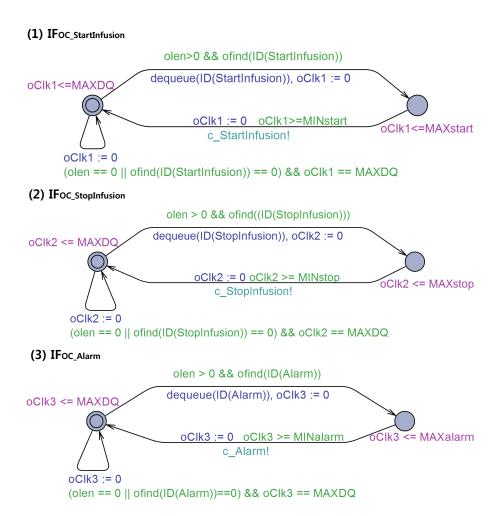

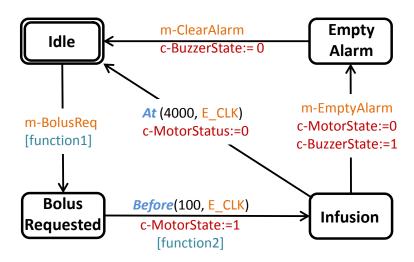

| FIGURE 8:  | The Environment Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48  |

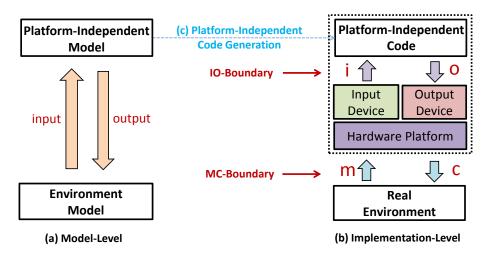

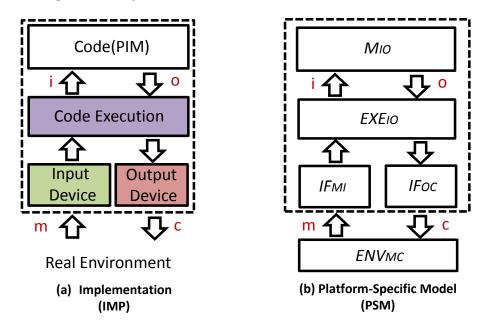

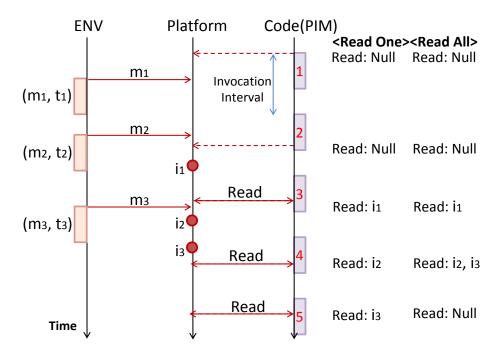

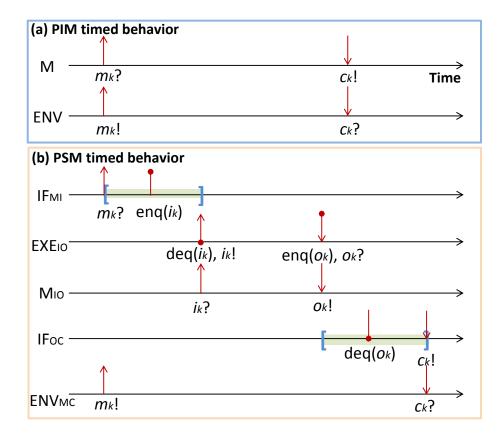

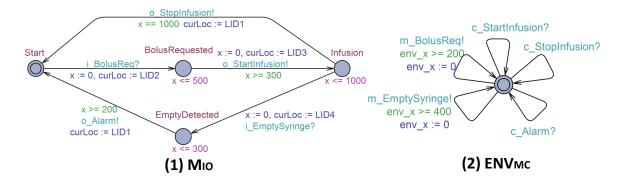

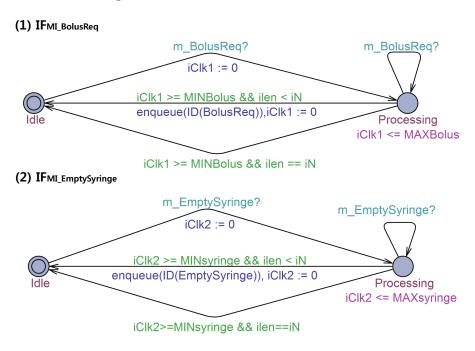

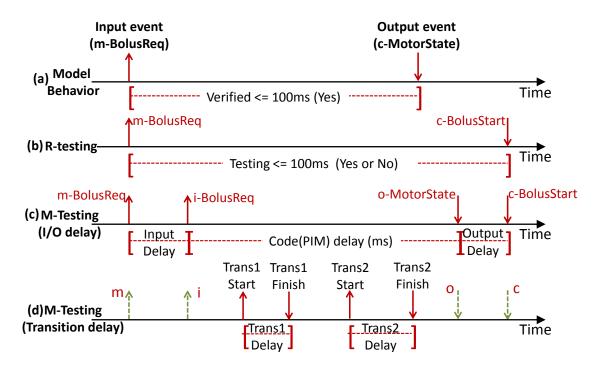

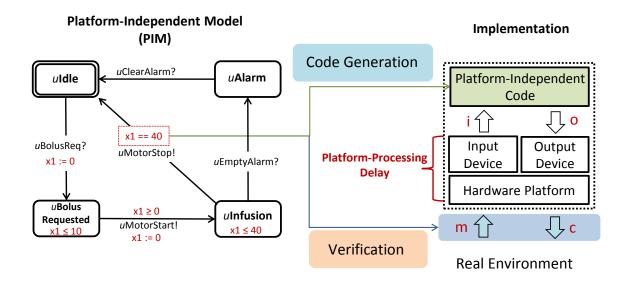

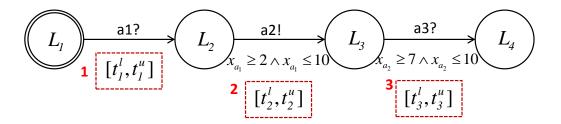

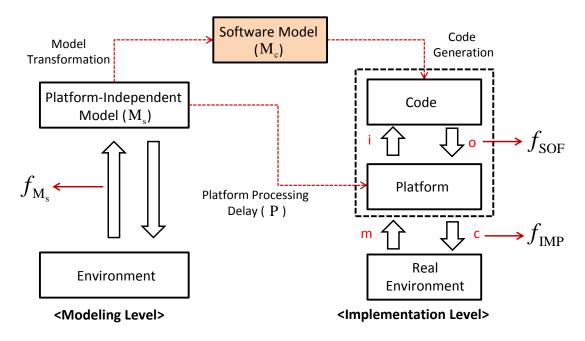

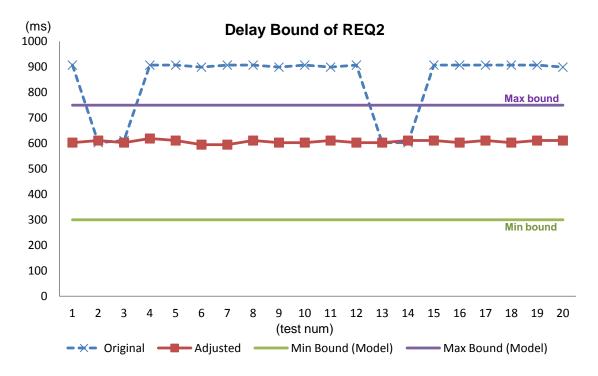

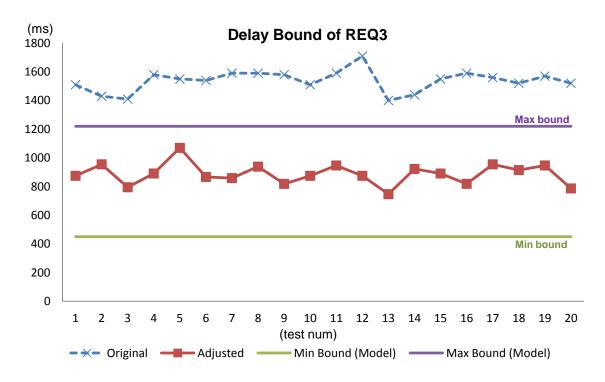

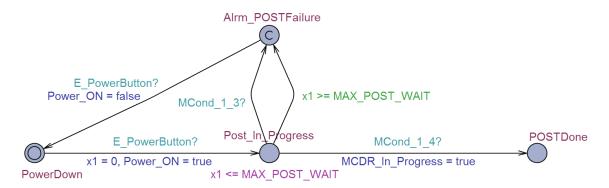

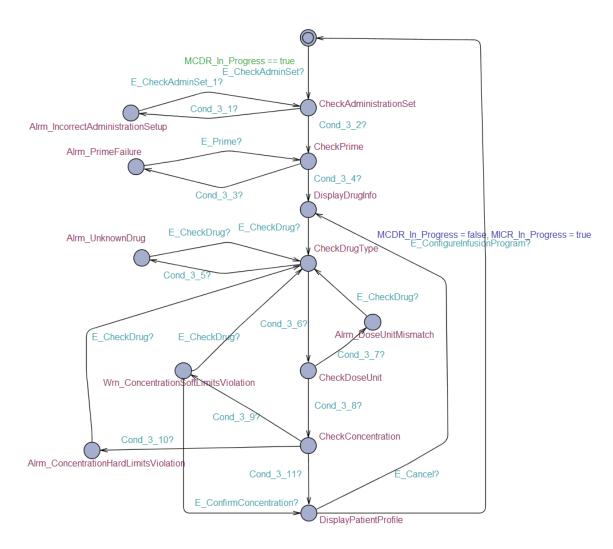

| FIGURE 9 : | The mapping between the model and the implementation using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |