University of Pennsylvania **ScholarlyCommons**

Publicly Accessible Penn Dissertations

1-1-2016

# Synthesis Of Distributed Protocols From Scenarios And Specifications

Abhishek Udupa University of Pennsylvania, audupa@seas.upenn.edu

Follow this and additional works at: http://repository.upenn.edu/edissertations

Part of the Computer Sciences Commons

### Recommended Citation

Udupa, Abhishek, "Synthesis Of Distributed Protocols From Scenarios And Specifications" (2016). Publicly Accessible Penn Dissertations. Paper 2067.

This paper is posted at Scholarly Commons. http://repository.upenn.edu/edissertations/2067 For more information, please contact repository@pobox.upenn.edu.

# Synthesis Of Distributed Protocols From Scenarios And Specifications

#### **Abstract**

Distributed protocols, typically expressed as stateful agents communicating asynchronously over buffered communication channels, are difficult to design correctly. This difficulty has spurred decades of research in the area of automated model-checking algorithms. In turn, practical implementations of model-checking algorithms have enabled protocol developers to prove the correctness of such distributed protocols. However, model-checking techniques are only marginally useful during the actual development of such protocols; typically as a debugging aid once a reasonably complete version of the protocol has already been developed. The actual development process itself is often tedious and requires the designer to reason about complex interactions arising out of concurrency and asynchrony inherent to such protocols. In this dissertation we describe program synthesis techniques which can be applied as an enabling technology to ease the task of developing such protocols. Specifically, the programmer provides a natural, but incomplete description of the protocol in an intuitive representation — such as scenarios or an incomplete protocol. This description specifies the behavior of the protocol in the common cases. The programmer also specifies a set of high-level formal requirements that a correct protocol is expected to satisfy. These requirements can include safety requirements as well as liveness requirements in the

form of Linear Temporal Logic (LTL) formulas. We describe techniques to synthesize a correct protocol which is consistent with the common-case behavior specified by the programmer and also satisfies the high-level safety and liveness requirements set forth by the programmer. We also describe techniques for program synthesis in general, which serve to enable the solutions to distributed protocol synthesis that this dissertation explores.

### Degree Type

Dissertation

#### **Degree Name**

Doctor of Philosophy (PhD)

### **Graduate Group**

Computer and Information Science

#### First Advisor

Rajeev Alur

### **Keywords**

Distributed Protocols, Program Synthesis

### **Subject Categories**

Computer Sciences

# SYNTHESIS OF DISTRIBUTED PROTOCOLS FROM SCENARIOS AND SPECIFICATIONS

Abhishek Udupa

A DISSERTATION

in

Computer and Information Science

Presented to the Faculties of the University of Pennsylvania in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

2016

Rajeev Alur, Zisman Family Professor of Computer and Information Science Supervisor of Dissertation

> Lyle Ungar, Professor of Computer and Information Science Graduate Group Chairperson

### **Dissertation Committee:**

Chaired by Steve Zdancewic, Professor of Computer and Information Science Joseph Devietti, Assistant Professor of Computer and Information Science Oleg Sokolsky, Research Associate Professor of Computer and Information Science Stavros Tripakis, Associate Professor, Aalto University, Finland

# SYNTHESIS OF DISTRIBUTED PROTOCOLS FROM SCENARIOS AND SPECIFICATIONS

COPYRIGHT

2016

Abhishek Udupa

Licensed under a Creative Commons Attribution 4.0 License.

To view a copy of this license, visit:

http://creativecommons.org/licenses/by/4.0/

To my parents

# Acknowledgments

I would like to thank my advisors Rajeev and Milo for their continual support and mentoring over the past five years. Rajeev provided me with a great deal of freedom to build tools and pursue my own ideas, while also gently nudging me in the right direction whenever I drifted too far off course. His problem solving techniques have shaped my own research abilities, and will continue to shape the way I approach problems in the years to come. Milo was always available to provide me with solid advice, whether it be on research, or other professional and personal matters. It is no understatement when I say that this dissertation would not have been possible without their mentoring.

I thank my dissertation committee chaired by Steve Zdancewic, and with Oleg Sokolsky, Joseph Devietti and Stavros Tripakis as members, for their comments and feedback that have served to improve the overall quality of this dissertation. I am also grateful to them for being extremely flexible with respect to the scheduling of the dissertation proposal and defense.

I am grateful to my parents, who encouraged my "scientific" curiosity at an early age, even if meant that I would take apart things and need a lot of assistance in putting them back together, assuming that I had not destroyed it. On a more serious note, they have provided me with every opportunity that paved the path to this dissertation, and tolerated all my off-kilter views on a variety of topics, and I thank them for that, and for not asking how long until I graduate too many times.

The work described in this dissertation was completed in collaboration with a great set of collaborators. Arun Raghavan, Santosh Nagarakatte and Jyotirmoy Deshmukh helped me find my feet in my early graduate school days. Stavros Tripakis, Christos Stergiou, Arjun Radhakrishna and Mukund Raghothaman have been a pleasure to work with. I thank them for being such awesome collaborators.

I thank Sudipto Guha, Rajeev Alur, Milo Martin, Ben Taskar, Val Tannen and Benjamin Pierce for being great instructors and putting the effort into teaching the courses at Penn that I have benefitted immensely from.

My stay at Penn was enriched by the company of great friends like Mukund Raghothaman, Christos Stergiou, Arjun Radhakrishna, Arun Raghavan, Jyotirmoy Deshmukh, Salar Moarref, Christian Delozier, Arjun Narayan and Katherine Gibson. I hope that these friendships will continue to grow, even after I graduate.

Outside of Penn, my friends from college, Aaron, Dianne, Aswin, Raksha, Chengappa, Nishi and Alden have proved to be gracious hosts on my various visits to and vacations in their respective cities, as well as objective, non-judgmental sounding boards in getting my thoughts straight at various points.

I would also like to thank my Master's thesis advisors, R. Govindarajan and Matthew J. Thazhuthaveetil, at the Indian Institute of Science, Bangalore, who encouraged, supported and mentored my very first research projects. Thanks are also due to Sriram Rajamani, Aditya Nori, Bill Thies and Kaushik Rajan, who have all mentored me during my various stints at Microsoft Research India, as well as Murali Talupur, who was my mentor during an internship at Intel Corporation. The mentoring I received from all of these people played a large role in my decision to pursue, and continue with a doctoral degree.

The research described in this dissertation was partially supported by NSF award CCF 0905464 and the NSF Expeditions in Computing grant CCF 1138996.

#### Abstract

Distributed protocols, typically expressed as stateful agents communicating asynchronously over buffered communication channels, are difficult to design correctly. This difficulty has spurred decades of research in the area of automated model-checking algorithms. In turn, practical implementations of model-checking algorithms have enabled protocol developers to prove the correctness of such distributed protocols. However, model-checking techniques are only marginally useful during the actual development of such protocols; typically as a debugging aid once a reasonably complete version of the protocol has already been developed. The actual development process itself is often tedious and requires the designer to reason about complex interactions arising out of concurrency and asynchrony inherent to such protocols. In this dissertation we describe program synthesis techniques which can be applied as an enabling technology to ease the task of developing such protocols. Specifically, the programmer provides a natural, but incomplete description of the protocol in an intuitive representation — such as scenarios or an incomplete protocol. This description specifies the behavior of the protocol in the common cases. The programmer also specifies a set of high-level formal requirements that a correct protocol is expected to satisfy. These requirements can include safety requirements as well as liveness requirements in the form of Linear Temporal Logic (LTL) formulas. We describe techniques to synthesize a correct protocol which is consistent with the common-case behavior specified by the programmer and also satisfies the high-level safety and liveness requirements set forth by the programmer. We also describe techniques for program synthesis in general, which serve to enable the solutions to distributed protocol synthesis that this dissertation explores.

# Contents

| Ac | knov    | vledgm        | ents                                                 | v    |

|----|---------|---------------|------------------------------------------------------|------|

| Αl | ostrac  | et            |                                                      | vi   |

| Li | st of T | <b>Tables</b> |                                                      | xi   |

| Li | st of l | Figures       | ;                                                    | xiii |

| Li | st of   | Algorit       | hms                                                  | xiv  |

| 1  | Intr    | oductio       | on                                                   | 1    |

|    | 1.1     | The T         | raditional Design Methodology                        | 3    |

|    |         | 1.1.1         | The VI Cache Coherence Protocol                      | 4    |

|    |         | 1.1.2         | Designing Distributed Protocols: The Easy Parts      | 8    |

|    |         | 1.1.3         | Designing Distributed Protocols: The Difficult Parts | 9    |

|    | 1.2     | An Alt        | ternative Approach to Protocol Design                | 11   |

|    |         | 1.2.1         | Automating the Difficult Parts of Protocol Design    | 11   |

|    |         | 1.2.2         | Feasibility and Effectiveness of Protocol Completion | 14   |

|    |         | 1.2.3         | Protocol Completion as Synthesis of Interpretations  | 16   |

|    | 1.3     | A Fran        | mework for Function Synthesis                        | 19   |

|    | 1.4     | Contri        | ibutions of this Dissertation                        | 20   |

| 2  | The     | Protoc        | col Completion Problem                               | 22   |

|    | 2.1     | Object        | tive                                                 | 22   |

|    | 2.2     | Forma         | llization and Notation                               | 22   |

|    |         | 2.2.1         | Types                                                | 23   |

|    |         | 2.2.2         | Function Symbols                                     | 23   |

|   |      | 2.2.3  | Messages                                                    | 23 |

|---|------|--------|-------------------------------------------------------------|----|

|   |      | 2.2.4  | Extended State Machines                                     | 24 |

|   |      | 2.2.5  | Executions                                                  | 25 |

|   |      | 2.2.6  | Composition of ESMs and ESM-SKS                             | 27 |

|   |      | 2.2.7  | Symmetry and Symmetric Types                                | 29 |

|   |      | 2.2.8  | Requirements and Specifications                             | 31 |

|   | 2.3  | Proble | em Statement                                                | 34 |

| 3 | A Sy | mbolio | Strategy via Parametrized Transitions                       | 35 |

|   | 3.1  | A Sim  | plified, Finite Version of the Problem                      | 36 |

|   | 3.2  | The Pa | arameterized Symbolic Transition System                     | 36 |

|   | 3.3  | Consti | ruction of the LTL Tester                                   | 38 |

|   | 3.4  | The Sy | ymbolic Synthesis Algorithm                                 | 40 |

|   |      | 3.4.1  | Correctness                                                 | 41 |

|   | 3.5  | Evalua | ating the Symbolic Algorithm                                | 42 |

|   |      | 3.5.1  | Applying the Symbolic Algorithm to Complete the VI Protocol | 43 |

|   |      | 3.5.2  | Insights from Experimenting with the Symbolic Algorithm     | 46 |

|   | 3.6  | Road-  | map for the Rest of the Dissertation                        | 47 |

| 4 | TRA  | NSIT:  | Specifying Protocols with Concolic Snippets                 | 51 |

|   | 4.1  | Overv  | iew of TRANSIT                                              | 51 |

|   | 4.2  | Conco  | lic Snippets and Programming with TRANSIT                   | 54 |

|   |      | 4.2.1  | Using Snippets in Transit                                   | 55 |

|   | 4.3  | Expres | ssion Inference                                             | 57 |

|   |      | 4.3.1  | Correctness of SynthForPoints                               | 62 |

|   |      | 4.3.2  | Constraints for Update Expressions                          | 64 |

|   |      | 4.3.3  | Constraints for Guard Expressions                           | 64 |

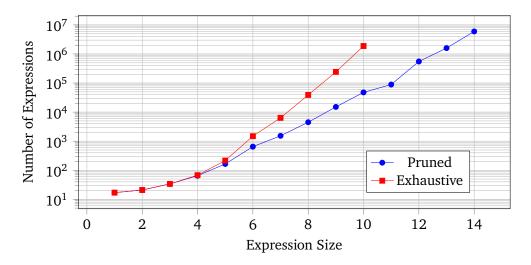

|   |      | 4.3.4  | Evaluation of the Expression Inference Algorithms           | 65 |

|   | 4.4  | Experi | imental Evaluation of TRANSIT                               | 66 |

|   |      | 4.4.1  | Case Study A: Non-blocking MSI                              | 67 |

|   |      | 4.4.2  | Case Study B: From MSI to MESI                              | 68 |

|   |      | 4.4.3  | Case Study C: The SGI-Origin Protocol                       | 68 |

|   |      | 4.4.4  | Discussion and Limitations                                  | 70 |

| 5 | SyG                                      | uS                   |                                                             | 71  |  |  |

|---|------------------------------------------|----------------------|-------------------------------------------------------------|-----|--|--|

|   | 5.1                                      | Correc               | ctness Specification                                        | 72  |  |  |

|   | 5.2                                      | Set of               | Candidate Expressions                                       | 72  |  |  |

|   | 5.3                                      | The Pi               | roblem Definition                                           | 73  |  |  |

|   | 5.4                                      | Compa                | arison with other Meta-synthesis Frameworks                 | 74  |  |  |

|   |                                          | 5.4.1                | SKETCH and Rosette                                          | 74  |  |  |

|   |                                          | 5.4.2                | FlashMeta                                                   | 75  |  |  |

| 6 | Enumerative Strategies for SyGuS Solvers |                      |                                                             |     |  |  |

|   | 6.1                                      | ESOLV                | VER: An Enumerative SyGuS Solver                            | 77  |  |  |

|   | 6.2                                      | Capab                | ilities and Limitations of ESOLVER                          | 78  |  |  |

|   |                                          | 6.2.1                | Separable Specifications                                    | 78  |  |  |

|   |                                          | 6.2.2                | Black Box and White Box Algorithms                          | 82  |  |  |

|   |                                          | 6.2.3                | A Comparison of White Box and Black Box Algorithms          | 85  |  |  |

|   | 6.3                                      | Combi                | ining Enumeration with Unification                          | 87  |  |  |

|   |                                          | 6.3.1                | Decision Trees                                              | 89  |  |  |

|   |                                          | 6.3.2                | Program Synthesis using Decision Trees                      | 90  |  |  |

|   |                                          | 6.3.3                | Putting it all Together                                     | 95  |  |  |

|   |                                          | 6.3.4                | Evaluation of EUSOLVER                                      | 102 |  |  |

| 7 | Synt                                     | thesis o             | of Finite-state Protocols from Scenarios and Specifications | 107 |  |  |

|   | 7.1                                      | Overv                | iew of Finite-state Protocol Synthesis                      | 107 |  |  |

|   | 7.2                                      | Scenarios to FSM-SKs |                                                             |     |  |  |

|   | 7.3                                      | Comp                 | letion of FSM-SKs                                           | 112 |  |  |

|   |                                          | 7.3.1                | State Coverage                                              | 113 |  |  |

|   |                                          | 7.3.2                | Analysis of Counterexample Traces                           | 113 |  |  |

|   |                                          | 7.3.3                | Complexity of the FSM-SK Completion Problem                 | 115 |  |  |

|   | 7.4                                      | Experi               | imental Evaluation                                          | 115 |  |  |

|   |                                          | 7.4.1                | Alternating-bit Protocol                                    | 116 |  |  |

|   |                                          | 7.4.2                | The VI Cache Coherence Protocol                             | 117 |  |  |

|   |                                          | 7.4.3                | The Consensus Protocol                                      | 117 |  |  |

|   |                                          | 7.4.4                | Discussion                                                  | 118 |  |  |

| 8  | Com  | pletion | of Distributed Protocols with Symmetry                   | 121 |

|----|------|---------|----------------------------------------------------------|-----|

|    | 8.1  | Overvi  | ew of Symmetric Protocol Completion                      | 121 |

|    | 8.2  | Solving | g the Symmetric Protocol Completion Problem              | 122 |

|    |      | 8.2.1   | Initial Constraints                                      | 123 |

|    |      | 8.2.2   | Analyzing Counterexample Traces                          | 124 |

|    |      | 8.2.3   | Heuristics and Optimizations                             | 127 |

|    | 8.3  | Model   | Checking                                                 | 129 |

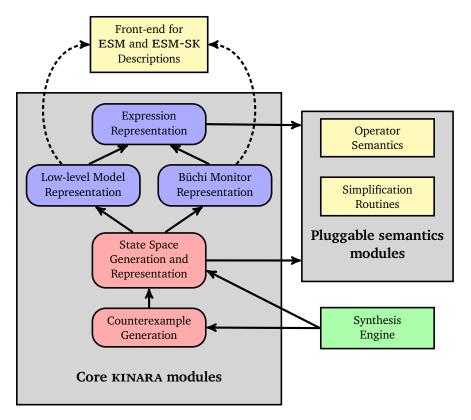

|    |      | 8.3.1   | Architecture of KINARA                                   | 130 |

|    |      | 8.3.2   | Construction of the Annotated Quotient Structure         | 133 |

|    |      | 8.3.3   | Construction of the Annotated Product Structure          | 135 |

|    |      | 8.3.4   | Checking for a Fair, Accepting Cycle                     | 136 |

|    | 8.4  | Experi  | mental Evaluation                                        | 137 |

|    |      | 8.4.1   | Peterson's Mutual Exclusion Algorithm                    | 138 |

|    |      | 8.4.2   | Self Stabilizing Systems                                 | 138 |

|    |      | 8.4.3   | Cache Coherence Protocol                                 | 138 |

|    | 8.5  | Summ    | ary of Experimental Results                              | 145 |

|    |      | 8.5.1   | Discussion                                               | 146 |

| 9  | Rela | ted Wo  | ork                                                      | 148 |

|    | 9.1  | Classic | al Reactive Synthesis Techniques                         | 148 |

|    | 9.2  | Synthe  | esis from Partial or Incomplete Descriptions             | 150 |

|    | 9.3  | Synthe  | esis from Sequence Charts                                | 150 |

|    | 9.4  | Straigl | nt-line and Recursive Program Synthesis                  | 151 |

| 10 | Con  | clusion | s                                                        | 153 |

|    | 10.1 | Summ    | ary of the Dissertation                                  | 153 |

|    | 10.2 | Theme   | es Explored in this Dissertation                         | 154 |

|    |      | 10.2.1  | Interplay between Programmer Involvement and Scalability | 154 |

|    |      | 10.2.2  | Use of Alternative Techniques to Specify Intent          | 155 |

|    | 10.3 | Avenue  | es for Future Work                                       | 156 |

|    | 10.4 | Reflect | ions on Verification and Program Synthesis               | 157 |

# List of Tables

| 4.1 | Expression Vocabulary used in Coherence Protocols                            | 59  |

|-----|------------------------------------------------------------------------------|-----|

| 4.2 | Illustration of the working of the expression inference algorithm            | 62  |

| 4.3 | Benchmarks and evaluation of the expression inference algorithms             | 67  |

| 4.4 | Performance of Snippet-based Protocol Design                                 | 67  |

| 4.5 | Effectiveness Metrics for Snippet-based Protocol Design                      | 69  |

| 5.1 | Comparison of various meta-synthesis frameworks                              | 75  |

| 6.1 | A multi-labelled sample set over which a decision tree is to be learned      | 93  |

| 6.2 | Entropies that result by splitting using the predicate $x < y \ldots \ldots$ | 94  |

| 6.3 | Entropies that result by splitting using the predicate $x=0$                 | 94  |

| 6.4 | Experimental Results for EUSOLVER on the ICFP benchmarks                     | 104 |

| 6.5 | Experimental Results for EUSOLVER on the MAX benchmarks                      | 105 |

| 7.1 | Experimental Results for Finite-state Protocol Synthesis from Scenarios      | 116 |

| 8.1 | Experimental Results for Automatic Completion of Symmetric Protocols         | 146 |

# **List of Figures**

| 1.1         | The traditional methodology for designing distributed protocols                      | 3   |

|-------------|--------------------------------------------------------------------------------------|-----|

| 1.2         | Communication Architecture of the VI Cache Coherence Protocol                        | 5   |

| 1.3         | The scenarios for the VI protocol                                                    | 6   |

| 1.4         | The incomplete state machine for the cache(s) in the VI protocol $\ \ldots \ \ldots$ | 8   |

| 1.5         | The incomplete state machine for the directory in the VI protocol                    | 8   |

| 1.6         | A scenario implied by the common-case scenarios in the VI protocol                   | 9   |

| 1.7         | Unhandled behavior in the cache state machine for the VI protocol                    | 10  |

| 1.8         | Unhandled behavior in the directory state machine for the VI protocol                | 10  |

| 1.9         | An alternative methodology for distributed protocol design                           | 12  |

| 1.10        | A possible completion of the implied scenario in the VI protocol                     | 13  |

| 1.11        | The completed state machine for the cache in the VI protocol $\ldots \ldots$         | 14  |

| 1.12        | The completed state machine for the directory in the VI protocol $\ \ldots \ \ldots$ | 14  |

| 1.13        | Peterson's Mutual Exclusion Protocol                                                 | 17  |

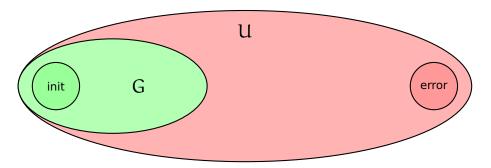

| 3.1         | Depiction of the space of all possible completions                                   | 45  |

| 3.2         | Common Algorithmic Scheme of Solution Strategies                                     | 47  |

| J. <u>Z</u> | Common Augorithmic benefite of bolution bridingles                                   | 77  |

| 4.1         | Overview of Developing a Protocol with TRANSIT                                       | 52  |

| 4.2         | Example of a Concolic Snippet                                                        | 54  |

| 4.3         | Example of an Erroneous Execution Presented to the Programmer                        | 55  |

| 4.4         | Impact of signature-based pruning in the expression inference algorithm              | 66  |

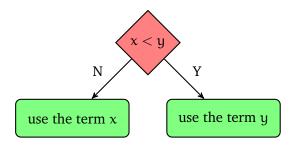

| 5.1         | An example of a learned decision tree                                                | 95  |

| 5.2         | Anatomy of an ICFP Benchmark                                                         | 102 |

| J.∠         | Anatomy of all for penchinary                                                        | 102 |

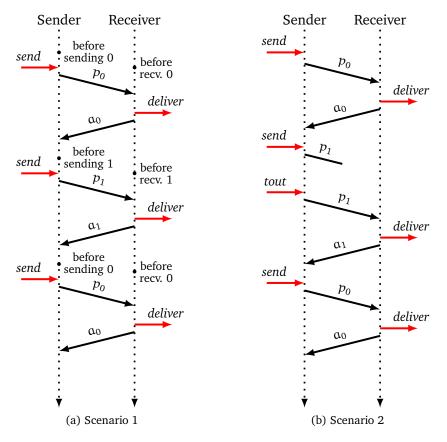

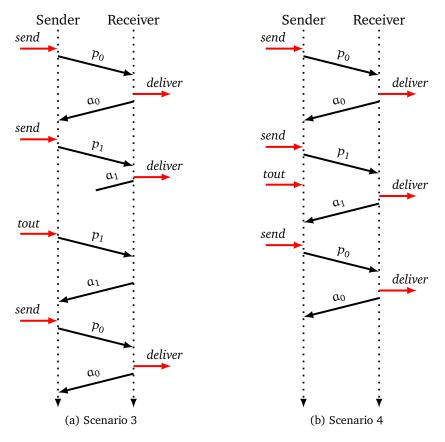

| 7.1         | Algorithm for Synthesizing Finite-state Protocols from Scenarios                     | 108 |

| 7.2 | Scenarios for the Alternating-bit Protocol (1)                  | 109 |

|-----|-----------------------------------------------------------------|-----|

| 7.3 | Scenarios for the Alternating-bit Protocol (2)                  | 110 |

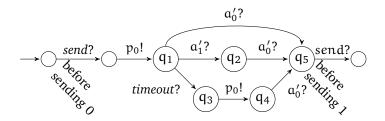

| 7.4 | FSM-SK for the ABP Sender Inferred from the Scenarios           | 112 |

| 7.5 | Scenario for the consensus protocol                             | 117 |

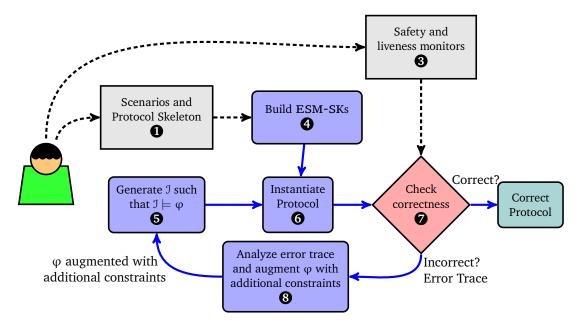

| 8.1 | Overview of the Algorithm for Completion of Symmetric Protocols | 122 |

| 8.2 | Architecture of the KINARA framework                            | 131 |

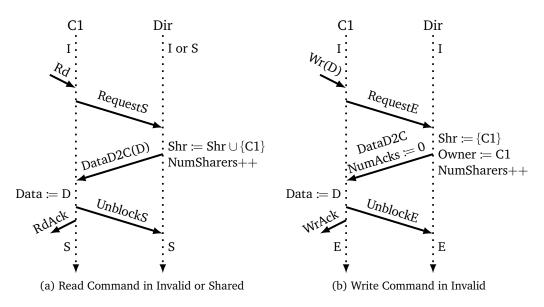

| 8.3 | Simple Cases for Read and Write Commands                        | 139 |

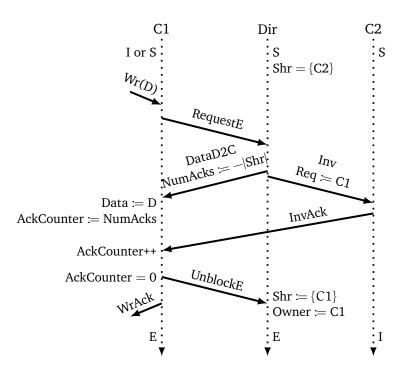

| 8.4 | Write Command in Shared State                                   | 140 |

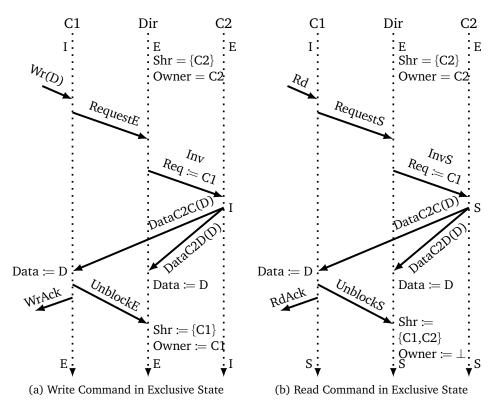

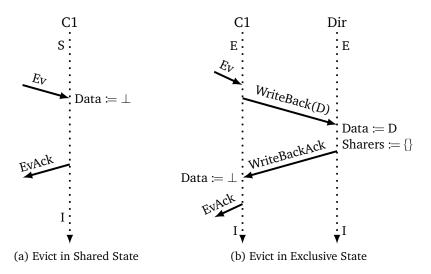

| 8.5 | Commands in Exclusive State in the German/MSI Protocol          | 142 |

| 8.6 | Evict Commands in the German/MSI protocol                       | 143 |

| 8.7 | A Racy Scenario in the MSI/German Cache Coherence Protocol      | 144 |

| 8.8 | A Corner-case in the German/MSI Protocol                        | 145 |

# List of Algorithms

| 3.1 | GETSYMBOLICINTERPS: Synthesize all correct FSM-SK completions              | 42  |

|-----|----------------------------------------------------------------------------|-----|

| 4.1 | SynthForPoints: Synthesize an expression consistent with a set of inputs . | 60  |

| 4.2 | SynthForAll: Synthesize an expression that is consistent for all inputs    | 61  |

| 6.1 | Learn-DT: An algorithm to learn a decision tree                            | 89  |

| 6.2 | ExpandTermSet: Expand the set of terms for synthesis                       | 95  |

| 6.3 | TERMSOLVE: Find partial expressions for a given set of points              | 96  |

| 6.4 | UnifyTerms: Attempt to combine sub-expressions                             | 97  |

| 6.5 | EUSOLVE: Solve for a SyGuS specification $\psi_{can}$                      | 98  |

| 8.1 | Algorithm to find a fair, green strongly connected subgraph                | 137 |

1

### Introduction

Protocols for coordination among concurrent processes are an essential component of modern multiprocessor and distributed systems. The multitude of behaviors arising due to asynchrony and concurrency makes the design of such protocols difficult. Consequently, analyzing such protocols has been a central theme of research in formal verification for decades. Now that verification tools have matured to a point where they can be applied to find bugs in real-world protocols, a promising research direction is to develop and leverage *program synthesis* techniques as an enabling technology to simplify the design process of such protocols via more intuitive programming abstractions for specifying the desired behavior.

Traditionally, a distributed protocol has been modeled as a set of communicating processes, where each process is described as an extended state machine which has a finite number of *control states* or *locations*, along with a finite number of typed *state variables*. The correctness of a protocol is specified by both safety and liveness requirements. Model-checking techniques are then used to check that the protocol satisfies the safety and liveness requirements. In many cases, the model-checking algorithms are completely automatic. It is thus natural to ask if we can derive a correct protocol implementation starting from a set of safety and liveness requirements. And indeed, in *reactive synthesis* [RW89, PR89, BJP<sup>+</sup>12], the goal is to automatically derive a non-distributed protocol, or a single reactive module, from its correctness requirements specified in temporal logic. However, if we require the implementation to be distributed, then reactive synthesis is undecidable [PR90, LT00, Tri04, FS05]. Furthermore, it is not clear that precisely codifying the behavior of the entire protocol using an intricate and complex formula in some temporal logic of choice is necessarily an easier or simpler task than specifying an operational description or an executable model of the protocol.

This dissertation proposes an alternative, and potentially more feasible approach inspired by program sketching [SLRBE05]. Our approach asks the programmer to specify the common case behavior of the protocol as a set of *incomplete* communicating processes, which may include some unknown functions. These unknown functions could be used in the guards for transitions — which describe the condition under which the transition in question can be executed and the update functions to state variables on transitions — which describe how the state variables of the state machine evolve upon execution of the transition. The programmer could also provide some information on the missing behavior. This information might be in the form of input-output examples describing the behavior of the unknown functions, or could be information about exactly what behavior is left unspecified, for example, information about what kinds of messages need to be handled at a given point. The programmer would also have to state the high-level correctness requirements for the protocol in a temporal logic of choice.<sup>1</sup> The role of the synthesizer is to *complete* the incomplete protocol provided by the programmer, such that the completed protocol (a) satisfies the high-level correctness requirements set forth by the programmer, and (b) is consistent with the information provided by the programmer about the unspecified behavior. This methodology for protocol specification can be viewed as a fruitful collaboration between the designer and the synthesis tool: the programmer has to describe the structure of the desired protocol, but some details that the programmer is unsure about, for instance, regarding corner cases and handling of unexpected messages, are filled in automatically by the tool.

In our formalization of the synthesis problem, processes communicate using input/output channels that carry typed messages. Each process is described by a state machine with a set of typed state variables. Transitions consist of guards — that test some condition over the state variables — and updates to state variables and fields of messages to be sent. Such guards and updates can involve *unknown* (typed) functions to be filled in by the synthesizer. In many distributed protocols, such as cache coherence protocols, processes are expected to behave in a symmetric manner. Thus, we allow variables to have *symmetric types* that restrict the read/write accesses to obey symmetry constraints. To specify safety and liveness requirements, we allow the use of safety and liveness (or Büchi) monitors respectively. Finally, fairness assumptions are utilized to restrict incorrect executions to those that are *fair*. It is worth noting that in

<sup>&</sup>lt;sup>1</sup>Note that these correctness requirements are typically much less detailed and simpler than the temporal logic formulae expected as input to typical reactive synthesis algorithms which attempt to synthesize a protocol purely from a specification in temporal logic.

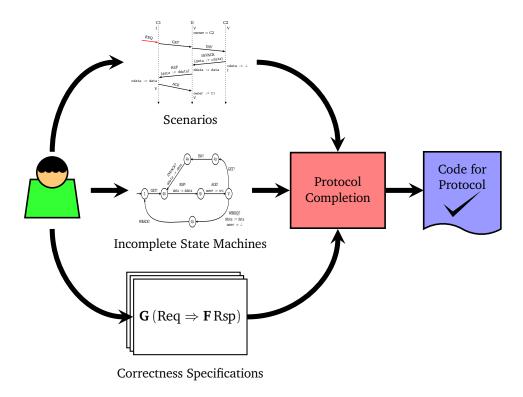

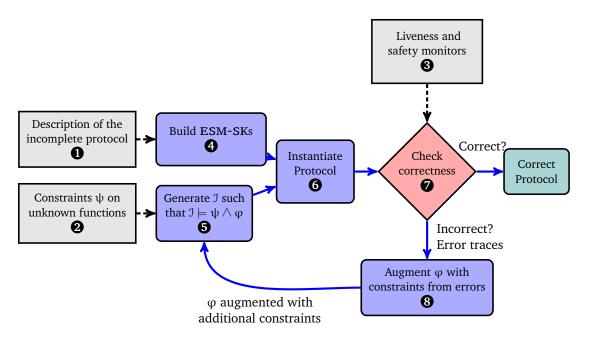

Figure 1.1: The traditional methodology for designing distributed protocols

verification one can get useful analysis results by focusing solely on safety requirements. In synthesis, however, ignoring liveness requirements and fairness assumptions, typically results in trivial solutions. The protocol completion problem, then, is, given a set of extended state machines with unknown guards and update functions, to find expressions for the unknown functions so that the composition of the resulting machines does not have an accepting fair execution.

In the rest of this chapter, we describe the design methodology we propose as part of this dissertation, as well as compare and contrast it with the traditional design methodology, by means of illustrative examples.

# 1.1 The Traditional Design Methodology

Figure 1.1 describes how distributed protocols are typically constructed. The programmer starts off with a variety of artifacts which describe the desired protocol. These can be in the form of *scenarios*, which describe the behavior of the protocol under specific use-cases, or as incomplete state machines which describe the *common-case* behavior of the protocol. In

addition, the programmer usually also has in mind some *high-level* correctness requirements that the protocol is expected to satisfy. These requirements could include *safety* requirements — which ensure that the protocol *never* does something "bad" — as well as *liveness* requirements — which ensure that the protocol *eventually* does something "good". The programmer then manually constructs an executable model (or implementation) of the protocol. This executable model can be described in various languages and formalisms, such as the Promela modeling language [Hol97], or the Mur $\varphi$  modeling language [ID96, Dil96], for example.

The resulting implementation is then checked for correctness using some combination of verification and testing techniques. For example, testing techniques could be used to check for correct behavior with respect to different scenarios specified by the programmer, whereas verification techniques could check that the candidate protocol satisfies the high-level safety and liveness specifications set forth by the programmer. In the event that an error is found during this check for correctness, the verification or testing framework provides the programmer with a concrete execution of the candidate protocol that demonstrates the error. The programmer then uses this information to *refine* or *correct* the behavior of the candidate protocol in the context of the specific counterexample currently under consideration. This process often requires the programmer to reason *globally* about the protocol to avoid introducing new errors as in the corrected version of the protocol. This tedious process of discovering bugs and correcting the protocol is iterated until a correct protocol is constructed. We now illustrate this process with a concrete example of how a simple cache coherence protocol might be constructed using this methodology.

### 1.1.1 The VI Cache Coherence Protocol

A cache coherence protocol ensures that all the processors in a multiprocessor system see a consistent view of data, despite the possibility that data values might be cached — and modified — by other processors in their local caches. Any coherence protocol essentially needs to ensure that the coherence property holds: The value *read* by any processor from a memory location must be the *most recent* value *written* to that memory location by any other processor in the system. Directory-based coherence protocols ensure that this property is maintained by using a centralized directory which is responsible for granting permissions to processors to read and write to memory locations. The processors and the directory then coordinate by exchanging messages with each other to acquire read and write permissions for memory locations in a

Figure 1.2: Communication Architecture of the VI Cache Coherence Protocol

manner that does not violate the coherence property. For the purpose of illustrating how the traditional design methodology might be applied, we consider a simple cache coherence protocol called the Valid-Invalid (VI) protocol.

Figure 1.2 depicts the communication architecture of a variant of the VI cache coherence protocol, shown here with two cache state machines for clarity. The same architecture generalizes to an arbitrary number of cache state machines. The protocol consists of a state machine called the "Directory", which maintains the knowledge of which cache currently holds a cached copy of each data address. The caches communicate requests for access to a data block through the reliable, but unordered buffer named "DirBuffer". All communication in the protocol is buffered and asynchronous. The only exception is that communication between the caches and their respective environments occurs synchronously. The buffers have a finite size, but are sized to be large enough to ensure that no state machine ever blocks on a full buffer. The directory processes requests in the "DirBuffer" in an arbitrary order, and communicates commands to the caches by the buffers "C1Buffer" and "C2Buffer". The caches on their part, again process commands in an arbitrary order. Finally, we note that a state machine need not necessarily respond to all commands and requests at all points in time. In other words, a state machine is allowed to *defer* the processing of some command or request, which is in a buffer, until some condition has been enabled.

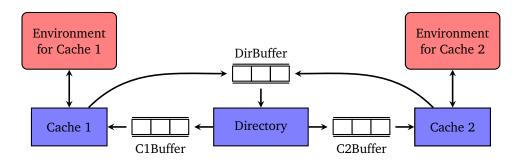

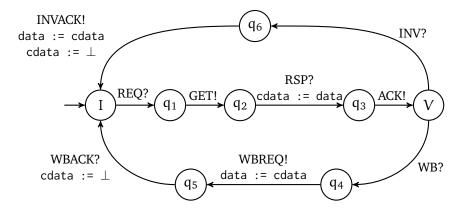

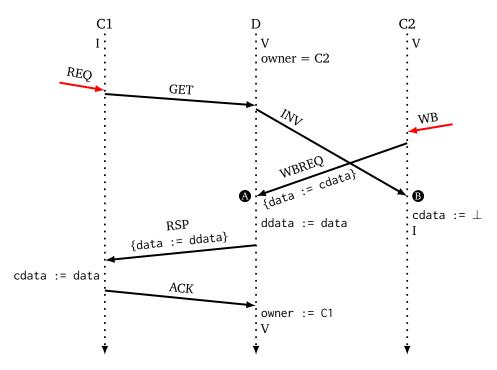

The working of the VI coherence protocol is perhaps best explained using the scenarios shown in Figure 1.3. The protocol consists of two classes of state machines: The cache controller state machines, whose behaviors are symmetric, denoted by C1, C2,..., Cn in Figure 1.3, and a singular directory state machine, denoted by D in Figure 1.3. Each cache machine has a state variable named cdata which contains the cached value of data at any point, and can be undefined if the cache does not have an up-do-date cached copy of the data. The directory

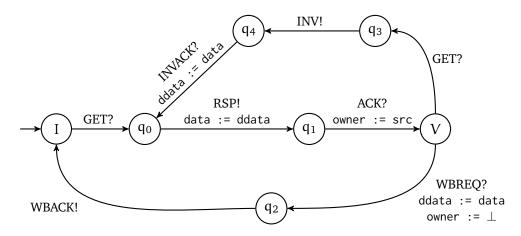

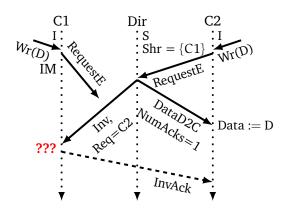

Figure 1.3: The scenarios for the VI protocol

machine has two state variables: one named ddata which represents the most up-to-date value of the data when no cache in the system has a valid cached copy of the data; the other variable named owner denotes which cache (if any) currently contains the most up-to-date value of the data. The description of the VI coherence protocol is presented here in a slightly abstracted fashion for ease of understanding. In an actual implementation, the directory state machine would need a few more state variables to track the cache whose request is currently being

serviced. Note that the inputs from the environments for the caches are denoted by red arrows in Figure 1.3.

The first scenario shown in Figure 1.3(a) describes the how the protocol behaves when a cache requests ownership, *i.e.*, read and write permissions, and no other cache currently has ownership of the data block in question. In this situation, all the caches as well as the directory are in the *Invalid* state, denoted by I. In this situation, the directory itself is assumed to possess the most up-to-date copy of the data value. The cache requests the directory for access by sending the directory a GET message and the directory responds immediately, with a response message RSP, which contains the most up-to-date value of the data block, granting ownership to the cache. Following this the cache *unblocks* the directory by sending an acknowledgment message ACK. Upon receipt of the ACK message, the directory notes that the cache C1 is now the *owner* of the block and transitions to the *Valid* state, denoted by V.

The second scenario shown in Figure 1.3(b) describes how a cache can *relinquish* ownership on a given data block. In this situation, the cache under question must own the data block, and thus it, along with the directory, must be in the *Valid* state denoted by V. The cache sends a WBREQ message containing the most up-to-date value of the data block to the directory. The directory updates its data block with the value received from the cache, and also notes that no cache currently owns the data block in question, by setting its owner state variable to be undefined. Following this, it responds with a WBACK message to the cache and transitions to the *Invalid* state, denoted by I. The cache, upon receipt of the WBACK message invalidates its local copy of the data, and also transitions to the *Invalid* state, denoted by I.

The third scenario, shown in Figure 1.3(c) describes how the protocol works when a cache requests ownership of a data block, but another cache already has ownership of the block. This situation is represented by the cache C1 being in the *Invalid* state, and the directory as well as the cache C2 being in the *Valid* state. From the perspective of cache C1, this scenario is the same as the one shown in Figure 1.3(a). However, the directory, upon receipt of the GET message sends an invalidation message INV to the cache C2 which currently owns the data block. Upon receipt of the INV message, cache C2 responds by sending an acknowledgment of invalidation, INVACK, which also contains the most up-to-date value of the data block, to the directory and transitions to the *Invalid* state. Its permissions have now been stripped by the directory. Upon receipt of the INVACK message from C2, the directory updates its local copy of the data. From this point on, the scenario proceeds in a manner similar to the scenario shown in Figure 1.3(a).

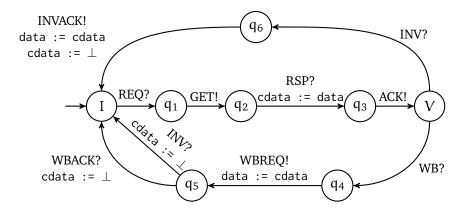

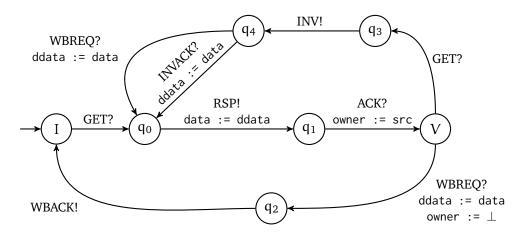

Figure 1.4: The incomplete state machine for the cache(s) in the VI protocol

Figure 1.5: The incomplete state machine for the directory in the VI protocol

In addition to the coherence property — which all cache coherence protocols ought to satisfy — it is desirable that each cache coherence protocol satisfies a set of *liveness* requirements, to ensure progress. In the case of the VI cache coherence protocol, the intuitive liveness requirement is that a GET request from every cache eventually results in the receipt of an RSP message with the most up-to-date value of the data by the cache that has issued a GET request. Additionally, a similar liveness requirement is also desirable with respect to the WBREQ request, which must eventually result in the receipt of a message that results in the cache transitioning to the *Invalid* or I state.

### 1.1.2 Designing Distributed Protocols: The Easy Parts

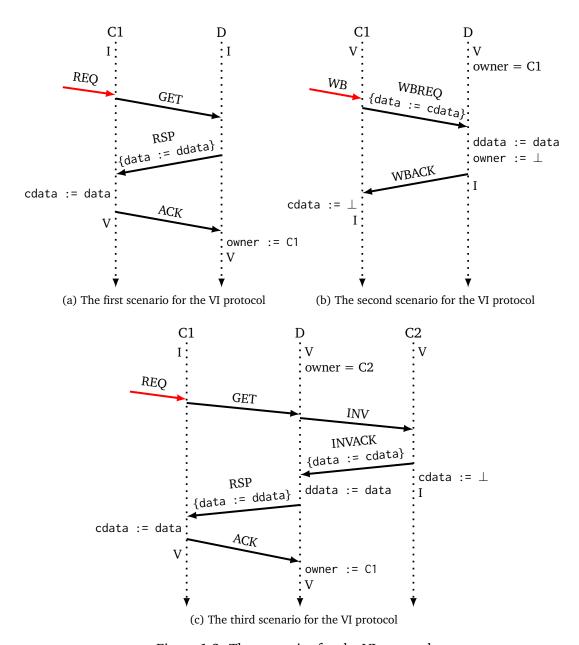

Based on the three common-case scenarios shown in Figure 1.3, the programmer constructs the state machines for the caches and the directory as shown in Figures 1.4 and 1.5 respectively.

Figure 1.6: A scenario implied by the scenarios shown in Figure 1.3 in the VI protocol

This translation is rather straight-forward and can even be automated in some cases, as we shall discuss in Chapter 7. Upon attempting to verify the correctness of the protocol described by the state machines in Figures 1.4 and 1.5, a verification tool presents the execution shown in Figure 1.6 as a counterexample which results in a deadlock.

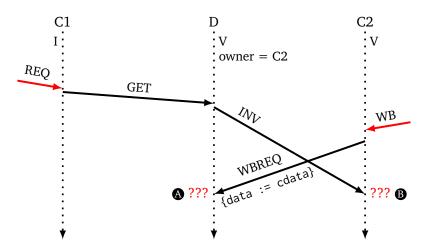

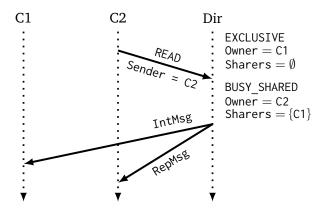

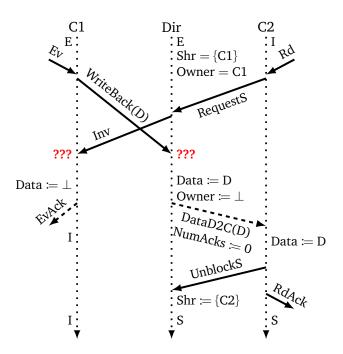

The execution shown in Figure 1.6 occurs as a result of the interleaving of the scenarios shown in Figure 1.3(b) and Figure 1.3(c). Specifically, the state machines C1 and the directory are proceeding according to the scenario shown in Figure 1.3(c). The cache C2 does not have any knowledge about the state of other state machines in the system and proceeds according to the scenario shown in Figure 1.3(b) upon receiving a WB command from its environment. This results in a deadlock. the directory state machine is expecting an INVACK message, but instead receives a WBREQ message. The state machine for the cache C2 is expecting a WBACK message, but instead receives an INV message. Neither the cache nor the directory state machines have a transition which describes what needs to happen in this circumstance, thus resulting in a deadlocked protocol. Note that it is impossible to avoid this situation, owing to the distributed nature of the protocol. This naturally leads us to a discussion about the difficult parts of designing a protocol using the traditional methodology.

# 1.1.3 Designing Distributed Protocols: The Difficult Parts

To specify the correct behavior in the specific scenario shown in Figure 1.6, the programmer needs to handle the behaviors in the state machines shown using dashed transitions to an unknown target state in Figures 1.7 and 1.8. Note that the locations labeled (A) and (B) in

Figure 1.7: Unhandled behavior in the cache state machine for the VI protocol

Figure 1.8: Unhandled behavior in the directory state machine for the VI protocol

Figure 1.6 correspond to the state  $q_4$  in the directory state machine and the state labeled  $q_5$  in the cache state machine respectively. The transitions represented by the dashed arrows thus represent the new transitions that must be added to eliminate the deadlock in the execution shown in Figure 1.6.

To eliminate the deadlocking execution, the programmer now needs to answer the following correlated questions:

1. Which state must the cache state machine transition to upon receipt of an INV message in the state  $q_5$ ?

- 2. How must the cdata state variable of the cache state machine be updated along this transition?

- 3. Which state must the directory state machine transition to upon receipt of a WBREQ message in the state  $q_4$ , given the choice made earlier for the transition of the cache machine upon receipt of the INV message in state  $q_5$ ?

- 4. How must the ddata and owner state variables of the directory state machine be updated along this transition, again taking into consideration all the choices made so far in the process of correcting the protocol.

Clearly, the right answers to these questions are correlated. Thus the programmer is forced to perform some form of global reasoning about the protocol to describe the correct behavior. Further, the programmer may need to perform this kind of reasoning multiple times as additional erroneous executions are discovered. We argue that this process is rather tedious and contributes significantly to the difficulty of designing correct implementations of distributed protocols. We now present an alternative methodology which makes use of program synthesis techniques to make the process of designing distributed protocols easier.

# 1.2 An Alternative Approach to Protocol Design

Given the undecidability of the problem of synthesizing distributed protocols purely from temporal logic specifications, we view the synthesis problem as one of *completion* in this dissertation. This section provides an intuitive description of how this view can help in making the difficult parts of protocol design easier.

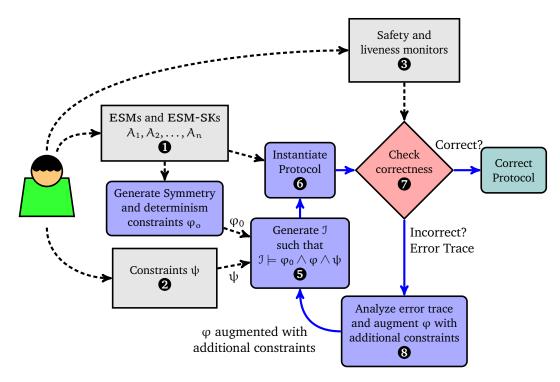

## 1.2.1 Automating the Difficult Parts of Protocol Design

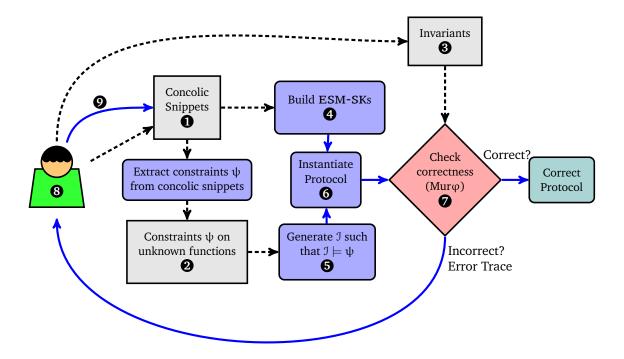

Figure 1.9 provides a high-level overview of the approach we propose in this dissertation. The programmer specifies the behavior of the protocol using a combination of common-case scenarios (which can be easily translated to incomplete state machines, either automatically, or manually) and incomplete state machines constructed from the well-understood common-case behavior of the protocol in question. Our approach also requires that the programmer formally specifies the high-level safety and liveness requirements that the protocol is expected to satisfy. We then leverage synthesis techniques to *complete* this incomplete protocol, or add behaviors to this incomplete protocol provided by the programmer to obtain an implementation which is *correct by construction*, *i.e.*, the completed protocol admits *at least* all the behaviors admitted

Figure 1.9: The methodology proposed in this dissertation for designing distributed protocols

by the incomplete protocol specified by the programmer, and satisfies all the high-level safety and liveness requirements.

This view of synthesis as a completion problem yields two advantages. First, the programmer is freed from the tedium and complexity of the iterative debugging process, and has only to specify an incomplete protocol, which is relatively easy. Second, we side-step the undecidability of distributed protocol synthesis. The completion problem is itself decidable, provided that the domains of all the state variables are finite. The decidability results from the fact that the completion process does not attempt to add new control states or variables. Obviously, this decidability comes at a cost: to be useful, the programmer needs to provide a "reasonably complete" version of the protocol, *i.e.*, it must be possible to obtain a correct protocol from the incomplete protocol provided by the programmer, without the addition of new control locations or state variables to the state machines in the protocol.

The upshot is that viewing the problem as one of *completion*, rather than synthesis, allows us to leverage the fact that the easy bits of distributed protocol design can be done by the programmer, to develop effective and useful algorithms that alleviate the difficulty of designing

Figure 1.10: A possible completion of the implied scenario in the VI protocol

distributed protocols. This trade-off between programmer involvement and effectiveness of automated algorithms for completion is a theme that we will explore throughout the subsequent chapters in this dissertation.

Turning our attention back to the example of the VI cache coherence protocol, Figure 1.10 shows one possible way in which the implied scenario shown in Figure 1.6 can be extended, such that all the correctness properties are satisfied. Essentially, the directory, treats the WBREQ message in the same manner as it would treat an INVACK message from the cache, and updates its local copy of the data with the value contained in the WBREQ message. The rest of the scenario plays out between the directory and cache C1 as shown in Figure 1.3(c). The cache C2, on its part, treats the INV message in the same manner as a WBACK message, invalidating its local copy of the data and transitioning to the *Invalid* or I state.

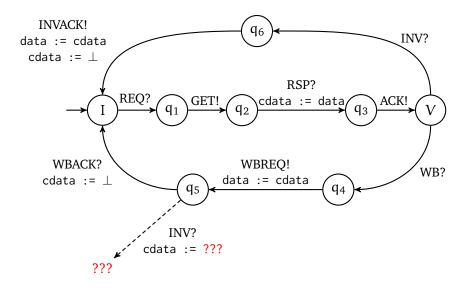

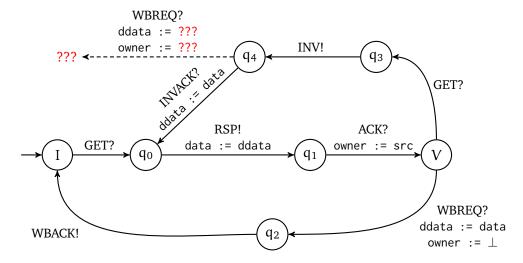

Figures 1.11 and 1.12 show the cache and directory state machines, respectively, completed according Figure 1.10. Viewed as a completion problem, the algorithms described in subsequent chapters of this dissertation are able to synthesize the state machines shown in Figures 1.11 and 1.12, starting from the incomplete state machines shown in Figures 1.4 and 1.5, along with a set of high-level safety and liveness requirements.

Figure 1.11: The completed state machine for the cache in the VI protocol

Figure 1.12: The completed state machine for the directory in the VI protocol

Note that although the state machines for the VI protocol did not have any *guards* in their transitions, this may not be the case in general. Some protocols might consist of state machines which require transitions to be executed *conditionally*, based on some predicate on the state variables of the machine in question. In the case of the VI protocol, these predicates can be viewed as being universally true. In general, a completion algorithm would need to determine these predicates, in addition to determining the target state and the updates to state variables along a transition.

### 1.2.2 Feasibility and Effectiveness of Protocol Completion

The utility of the design methodology for distributed protocols that we have just introduced, depends heavily on whether it is feasible to build tools that support the methodology and on the effectiveness of such tools. Objectively, the proposed design methodology for distributed

protocols can be considered useful, provided that the answers to the following two questions can be proven to be in the affirmative:

- Is it possible to develop effective algorithms to solve the distributed protocol completion problem? A related question is whether these algorithms can be useful in assisting a protocol designer in developing correct versions of real world protocols which are beyond the capabilities of traditional approaches to reactive synthesis.

- Is it easier for a protocol designer to specify the behavior of the protocol using a combination of scenarios and incomplete state machines, along with a set of high-level formal requirements in temporal logic?

Detailed experimental evaluations in the subsequent chapters of dissertation demonstrate that the answer to the first question is indeed in the affirmative. The second question, on the other hand, is rather subjective. While a large scale user study is beyond the scope of this dissertation, we hope that the examples provided in this chapter, as well as in subsequent chapters, serve to convince the reader that it is indeed easier to specify distributed protocols using the approach that we propose.

To demonstrate affirmative answers to the questions just raised, we built and evaluated several prototype tools. We now present a brief summary of the capabilities of each tool. A more thorough exposition will be provided in subsequent chapters.

The first tool we built, dubbed TRANSIT, required the protocol designer or programmer to be a part of the synthesis loop. The programmer was expected to provide *local* remedies to specific, concrete erroneous executions uncovered during the verification process. Our case studies demonstrate that this was useful in reducing the tedium of the debugging phase of protocol design. In each case, the programmer was able to obtain a correct protocol, with only a few rounds of interaction with the completion tool. The approach was found to be very scalable, and was successfully used to specify the industrial SGI Origin cache coherence protocol [LL97]. This is a large, scalable, real life protocol, with millions of reachable states, and has been deployed in high-end systems from SGI.

Encouraged by the success of TRANSIT, we now sought to automate the process, and free the programmer from being part of the synthesis loop. The second tool which we developed only handles protocols where the state machines do not have any state variables. In this specific setting, the completion problem can be viewed as a minimal Boolean satisfiability problem, which in turn can be solved effectively by Integer Linear Program (ILP) solvers. Another feature of this tool was it accepted inputs in the form of scenarios, which are as shown in Figure 1.3, rather than as incomplete state machines. This tool was able to automatically complete several text-book protocols, such as the alternating-bit protocol, protocols for consensus and even a simple cache coherence protocol.

The limitation of this scenario based completion tool was not scalability: it synthesized everything we threw at it with ease. However, it was rather difficult to specify larger protocols with the restriction that state machines not have any variables. The third tool which we built addresses this limitation, and also allows the programmer to specify symmetry constraints that a completed protocol ought to satisfy. Using this tool, we were able to automatically synthesize protocols for mutual exclusion, a moderately sized self-stabilization protocol, as well as the modestly complex German/MSI cache coherence protocol.

While the automated algorithms are not as scalable as the algorithms which require the programmer to be a part of the synthesis loop, they can still be useful in developing protocols of moderate complexity. The experimental evaluations in subsequent chapters of this dissertation will explore this trade-off between programmer involvement and scalability in greater depth.

### 1.2.3 Protocol Completion as Synthesis of Interpretations

Throughout this dissertation, we will take the view that the protocol completion is tantamount to the problem of synthesizing *interpretations* for multiple, possibly correlated, unknown functions. To make this view apparent, observe that the *guard* for each new transition to be added can be viewed as a Boolean valued function over the state variables of the state machine in question. Similarly, the *updates* to each state variable along a transition to be added can be viewed as a function of the appropriate type over the state variables. Lastly, the target control state to transition to can also be viewed as an update to a distinguished state variable — say a variable named "location" — of a suitable enumerated type.

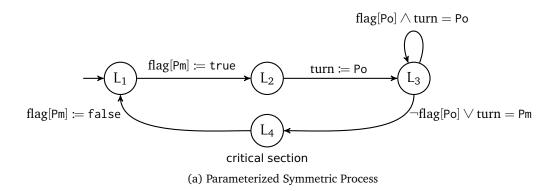

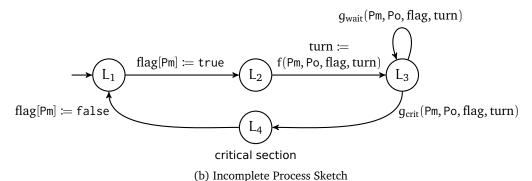

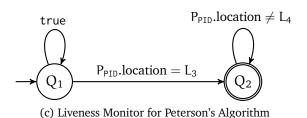

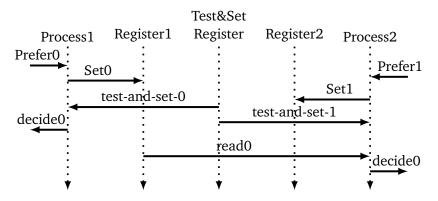

To illustrate this view, as well as to describe the subtleties of symmetry and fairness in some detail, we consider another example: the Peterson's mutual exclusion protocol. Figure 1.13(a), describes this protocol, which manages two symmetric processes contending for access to a critical section, labeled as the state L<sub>4</sub> in Figure 1.13. Each process is parameterized by two parameter variables Pm and Po (for "my" process id and "other" process id respectively), such that Pm  $\neq$  Po. Both the parameters Pm and Po are of type processid, which is a *symmetric type*, and they are allowed to take on values P0 and P1. We therefore have two instances of the

Figure 1.13: Peterson's Mutual Exclusion Protocol

symmetric process shown in Figure 1.13(a):  $P_0$ , where (Pm = P0, Po = P1), and  $P_1$ , where (Pm = P1, Po = P0).  $P_0$  and  $P_1$  communicate through the shared variables turn and flag. The variable turn has type processid. The flag variable is an array of Boolean values, indexed by values of the type processid. The main objective of the protocol is to control access to the critical section, represented by location  $L_4$ , and ensure that both of the processes  $P_0$  and  $P_1$  are never simultaneously in the critical section, i.e., it is a safety violation for both  $P_0$  and  $P_1$  to be in state  $L_4$  at the same time. For clarity, the assignments to flag and turn are shown as simple assignments in Figure 1.13, but in a faithful model of the Peterson's algorithm, these would be involve exchange of messages, with the shared variables flag and turn represented as state machines for atomic registers.

The liveness monitor shown in Figure 1.13(c) captures the requirement that a process not wait indefinitely to enter the critical section. The liveness monitor is itself parameterized by the parameters Pm and Po in a manner similar to the processes, with each instance encoding the liveness requirement for the appropriate process. The monitor accepts all undesirable runs where a process has requested access to the critical section (i.e., the process in question is in state L<sub>3</sub>), but never reaches state L<sub>4</sub> — which corresponds to entering the critical section after reaching state L<sub>3</sub>. In other words, the monitor accepts an infinite execution where one of the processes P<sub>0</sub> or P<sub>1</sub> is stuck in state L<sub>3</sub> forever. Note that a run accepted by the monitor may be unfair with respect to some processes. For instance, if process Po is in state L3 and could possibly transition to state L<sub>4</sub>, but the scheduler never schedules process P<sub>0</sub>, and process P<sub>0</sub> therefore never enters state L<sub>4</sub>, then this execution is unfair with respect to process P<sub>0</sub>. Enforcing weak process fairness on  $P_0$  and  $P_1$ , — i.e., if a process is enabled at every point in an infinite execution, then it must be executed at some point in that execution — is sufficient to rule out unfair executions, but not necessary. Enforcing weak fairness on the single transition between (L<sub>3</sub>, L<sub>4</sub>) suffices to rule out all unfair executions which could possibly be accepted by the monitor shown in Figure 1.13(c).

Now, to view the protocol completion problem as one of synthesizing interpretations, consider the *incomplete* version of Peterson's mutual exclusion protocol as shown in Figure 1.13(b). Here, the condition under which a process is allowed to enter the critical section, the condition under which a process must wait in location  $L_3$ , and the update to the *turn* variable along the edge from  $L_2$  to  $L_3$  have been replaced by the unknown functions  $g_{wait}$ ,  $g_{crit}$  and f respectively. The target control locations along these transitions could also be unknown, but are retained here for clarity.<sup>2</sup>

The functions  $g_{wait}$  and  $g_{crit}$  represent unknown Boolean valued functions over the state variables and the parameters of the process under consideration. The function f represents the unknown update to the *turn* variable. Including the parameter variables Pm and Po as part of the domain of  $g_{wait}$ ,  $g_{crit}$  and f is necessary to ensure that the completions synthesized by a tool for processes  $P_0$  and  $P_1$  are symmetric. We defer a formal definition of what it means for protocols and interpretations to be symmetric until Chapter 2. Now, given a set of fairness assumptions, the protocol completion problem reduces to automatically discovering interpretations for these unknown functions, such that the completed protocol satisfies the necessary mutual exclusion

<sup>&</sup>lt;sup>2</sup>It would be rather confusing to see transition arrows all shooting up into nowhere.

property, and that every *fair* execution of the completed protocol is not an accepting run of the liveness monitor shown in Figure 1.13(c).

Thus the protocol completion problem can indeed be viewed as a problem of synthesizing interpretations for a set of correlated unknown functions. This provides an excellent segue for the next section in this chapter, which motivates the development of a general framework for describing such problems, independent of distributed protocols.

# 1.3 A Framework for Function Synthesis

Although synthesis of distributed protocols is the primary focus of this dissertation, during course of research on this topic, we also had to develop scalable program synthesis techniques to enable the synthesis of distributed protocols. As we have just explained, synthesizing *guard* and *update* functions that constitute the descriptions of state machines in a distributed protocol is tantamount to the synthesis of multiple unknown functions, the constraints on the behavior of which can possibly be correlated. We observed that a lot of recent work on program synthesis for different domains were essentially solving this very same problem — *i.e.*, that of synthesizing an unknown function (or a set of unknown functions) such that the synthesized function satisfies some constraints — with a variety of independently developed (and possibly domain-specific) algorithms. Unfortunately, there was no uniform way to compare the strengths and weaknesses of each of these algorithms due to subtle differences in the way each of them required the constraints over the unknown functions to be expressed, as well as the search space for the interpretations or bodies of these unknown functions.

This led us to formulate the Syntax-Guided Synthesis (SyGuS) problem, which is intended to be a general framework — along with a specification language — for expressing program synthesis problems. The motivation for this was two-fold:

- Provide a common input language for specifying the constraints on, and the search space

for candidate interpretations or bodies of unknown functions to be synthesized. This format,

called SyGuS-IF, can then serve as a common input language for describing benchmarks to

evaluate tools implementing different program synthesis techniques.

- Spur research in program synthesis by organizing annual SyGuS competitions, in the same manner that the SMTLIB and SMTCOMP initiatives have helped encourage research in satisfiability modulo theory (SMT) solvers and theorem provers.

The intention is for SyGuS to be to program synthesis, what SMTLIB is to program verification.

This dissertation includes a description of the SyGuS problem as well as a description and evaluation of two SyGuS solvers which implement algorithms based on enumerative strategies — *i.e.*, algorithms which systematically, and intelligently, enumerate function interpretations or bodies from the search space until a solution is found — to solve instances of the SyGuS problem. The SyGuS solvers may be considered as technologies which enable the construction of higher-level and domain specific synthesis algorithms — such as algorithms for distributed protocol completion and synthesis.

## 1.4 Contributions of this Dissertation

Having introduced the specific problems that the research to be described in this dissertation was intended to tackle, we now provide a short summary of contributions made by this dissertation:

- We demonstrate that although the problem of full distributed reactive synthesis from temporal logic specifications is hard, useful assistance can still be provided to the designer/developer of such protocols by viewing the synthesis problem as one of *completion*. In this world-view, the developer assists the synthesis algorithm by providing the information which is natural and easy for a developer to provide. The tool in turn provides as much automation as possible to the developer in automatically discovering the parts of the protocol which the developer finds difficult to reason about.

- We describe and evaluate three tools which we have developed, which aim to make the

process of developing distributed protocols easier. Each of these tools differ in the level

of automation provided and thus in their performance and scalability and in the

restrictions they impose on the kinds of protocols they can handle.

- In evaluating and comparing the abilities of these tools, we explore the three-way trade-off between the level of automation provided by the tools versus the amount of developer involvement in the process of developing these protocols versus the scalability of the tools.

- We describe the SyGuS framework for specifying program synthesis problems in a general

manner, which is intended to be an enabling technology for higher-level synthesis techniques

to build upon. We also describe and evaluate algorithmic strategies based on systematic and

intelligent enumerative search to solve instances of the SyGuS problem.

The subsequent chapters of this dissertation are organized as follows. Chapter 2 introduces some notation and definitions and provides a formal definition of the protocol completion

problem. Chapter 3 describes an elegant symbolic solution strategy for the protocol completion problem, and explains why the strategy is not effective in a practical setting. Chapter 3 also describes the insights gained from implementing and experimenting with the symbolic algorithm, which motivated the choices made with respect to the rest of the work described in this dissertation. Chapters 4, 7 and 8 describe the solution approaches to the protocol completion problem that we have implemented and evaluated. Chapter 5 describes a general-purpose framework for program synthesis, called SyGuS, that arose from the work described in Chapter 4, and Chapter 6 discusses some enumerative strategies for solving instances of the SyGuS problem. Chapter 9 provides an overview of related work in the area and discusses how the work described in this manuscript differs from earlier work. Chapter 10 summarizes the contributions of this dissertation and discusses the avenues along which the work may be extended in the future, and concludes with some reflections on the problems addressed in this dissertation.

# The Protocol Completion Problem

Having informally described and motivated the protocol completion problem in the previous chapter, we now present a rigorous definition of the problem and set up the prerequisite definitions and notation which will be used in the rest of this dissertation.

## 2.1 Objective

Our primary objective is to ease the task of developing correct distributed protocols. To accomplish this, we leverage the fact that it is often easy to specify the behavior of a distributed protocol in the common cases. We allow the developer to specify a *skeleton* or *sketch* of the protocol that defines (i) the set of communicating processes that make up the protocol (ii) the *state variables* of each communicating process that is part of the protocol, (iii) the *communication architecture* of the protocol, which defines which processes can communicate, and along which direction, as well as describes the properties of communication links between processes, (iv) the behavior of the protocol in the common case scenarios, (v) the correctness properties, in the form of *invariants* and *liveness monitors*, and (vi) a set of *fairness* requirements under which the liveness properties ought to hold. Collectively, these artifacts describe an *incomplete* protocol. We will assume that the incomplete protocol, by itself, does not satisfy the desired correctness properties. The goal then, is to complete this incomplete protocol, by adding transitions where required, such that the completion satisfies the desired correctness properties.

#### 2.2 Formalization and Notation

We now formally define our notion of a state machine, executions of state machines, composition of state machines and other related notions in this section. Our formalism draws on the notion of

input-output automata (I/O automata) described in the text-book by Lynch [Lyn96]. However, we do not assume that the state machines (or I/O automata) are *input-complete*, *i.e.*, are required to handle *any* input at *any* point in their execution.

#### **2.2.1** Types

Let  $\mathcal{B}$  be a set of *base types*, where each type  $T \in \mathcal{B}$  has finite cardinality, and is either (1) the Boolean type, (2) an enumerated type, (3) a fixed range integer type, or (4) a *symmetric* type. Symmetric types are similar to enumerated types, but the behavior of the system is considered to be invariant under permutations of the symmetric type. The notion of a symmetric type will be described in more detail in Section 2.2.7. Given a type  $T_1 \in \mathcal{B}$ , and a type  $T_2$ , the composite type array $(T_1, T_2)$  contains all mappings from values of type  $T_1$  to values of type  $T_2$ . Given types  $T_1, T_2, \ldots, T_n$ , the composite type record $(T_1, T_2, \ldots, T_n)$  denotes a type whose values range over  $T_1 \times T_2 \times \cdots \times T_n$ . Given a fixed set of base types  $\mathcal{B}$ , we define  $\mathcal{T}_{\mathcal{B}}$  to be the smallest set of types such that  $(1) \mathcal{T}_{\mathcal{B}} \supseteq \mathcal{B}$  and,  $(2) \mathcal{T}_{\mathcal{B}}$  is closed under composition using the array and record operators, *i.e.*, if  $T_1 \in \mathcal{B}$ , and  $T_2 \in \mathcal{T}_{\mathcal{B}}$ , then array $(T_1, T_2) \in \mathcal{T}_{\mathcal{B}}$ , and if  $T_1, T_2, \ldots, T_n \in \mathcal{T}_{\mathcal{B}}$ , then record $(T_1, T_2, \ldots, T_n) \in \mathcal{T}_{\mathcal{B}}$ . We drop the subscript and use  $\mathcal{T}$  to refer to  $\mathcal{T}_{\mathcal{B}}$  whenever the context is clear. Note that every type  $T \in \mathcal{T}_{\mathcal{B}}$  has finite cardinality.

#### 2.2.2 Function Symbols

Given a set of types  $\mathfrak{T}$ , we fix a set of function symbols  $\mathfrak{F}$ . Each function symbol  $f \in \mathfrak{F}$  has a signature denoted  $d_1 \times d_2 \times \cdots d_n \to r$ , where  $d_1, d_2, \ldots, d_n \in \mathfrak{T}$  represent the domain of the function and  $r \in \mathfrak{T}$  represents the range of the function. A function symbol may have a fixed interpretation, e.g., the symbol '+' might denote integer addition, or the interpretation may be unknown. We denote by  $\mathfrak{U} \subseteq \mathfrak{F}$ , the subset of the function symbols in  $\mathfrak{F}$  whose interpretations are unknown. We define an *expression* to be a well-typed composition of function symbols applied to values or variables of the appropriate types. Further, we assume that *exactly one* state machine uses any given unknown function in its description. Thus for each unknown function  $f_{\mathfrak{U}} \in \mathfrak{U}$ , we can speak about *the* state machine that uses  $f_{\mathfrak{U}}$  in its description.

## 2.2.3 Messages

We define  $\Sigma$  to be a message alphabet and mtype :  $\Sigma \to \mathfrak{T}$  to be a function that maps each message  $\mathfrak{m} \in \Sigma$  to the type of its *payload*. Further, we define  $\Sigma_P$  to be a set of *parame*-

terized messages. A parameterized message has the form  $m \langle p_1 : T_1, p_2 : T_2, \ldots, p_n : T_n \rangle$ , where  $T_1, T_2, \ldots, T_n \in \mathfrak{I}$  are symmetric types, and  $p_1, p_2, \ldots, p_n$  are parameter variables whose values can range over  $T_1, T_2, \ldots, T_n$  respectively. For every parameterized message m of the form  $m \langle p_1 : T_1, p_2 : T_2, \ldots, p_n : T_n \rangle \in \Sigma_P$ , the corresponding *instances* of the message m are in  $\Sigma$ . *i.e.*,  $m \langle p_1 \mapsto \nu_1, p_2 \mapsto \nu_2, \ldots, p_n \mapsto \nu_n \rangle \in \Sigma$ , for all values  $\nu_1, \nu_2, \ldots, \nu_n$ , where  $\nu_1 \in T_1, \nu_2 \in T_2, \ldots, \nu_n \in T_n$ . Further, any two instances of a parametric message have the same payload type. Specifically, if m is a parameterized message as described above, then, we have that  $mtype(m \langle p_1 \mapsto u_1, p_2 \mapsto u_2, \ldots, p_n \mapsto u_n \rangle) \equiv mtype(m \langle p_1 \mapsto \nu_1, p_2 \mapsto \nu_2, \ldots, p_n \mapsto \nu_n \rangle)$  for all  $\{u_i\}$  and  $\{\nu_i\}$ . Parameterized messages themselves cannot be used as inputs to, or outputs of state machines, but instances of parameterized messages have restrictions on being inputs and outputs of state machines as we will describe shortly.

#### 2.2.4 Extended State Machines

An extended state machine (ESM) A is a tuple  $A \triangleq \langle L, l_0, I, O, V, \sigma_0, R, \mathcal{F}_s, \mathcal{F}_w \rangle$ , where:

- L is a finite set of locations.

- $l_0$  is the *initial* location at which every execution of the ESM begins.

- $I \subseteq \Sigma$  is a set of *input* messages.

- $O \subseteq \Sigma$  is a set of *output* messages, such that  $I \cap O = \emptyset$ .

- V is a finite set of typed state variables. For notational convenience, we define the typing function typeof: V → T which maps each variable to its type.

- $\sigma_0$  is an *initialization* function that maps each variable  $v \in V$  to an initial value  $s \in \mathsf{typeof}(v)$ .

- $R \triangleq R_i \cup R_o \cup R_\varepsilon$  is a set of transitions, partitioned into a set of *input* transitions  $R_i$ , a set of *output* transitions  $R_o$  and a set of *internal* transitions  $R_\varepsilon$ . Each transition  $r \in R$  is of the form  $r \triangleq \langle l, m, \text{guard}, \text{updates}, l' \rangle$ , where  $l, l' \in L$  are the initial and final locations for the transition;  $m \in I$  for input transitions,  $m \in O$  for output transitions, and  $m = \varepsilon$  for internal transitions; guard is a Boolean valued expression over the state variables V, and updates maps each lvalue under consideration to an update expression of the appropriate type. If  $r \in R_i$ , then updates maps each lvalue  $v \in V$  to an update expression which may only refer to the variables in  $V \cup \{m_p\}$ , where  $m_p \notin V$  refers to the payload of the incoming message m. If  $r \in R_o$ , then updates maps each lvalue  $v \in V \cup \{m_p\}$  to an update expression, where  $m_p \notin V$  is the payload of the outgoing message, and the update expressions may refer only

to variables in V. Finally, if  $r \in R_{\varepsilon}$ , then updates maps each lvalue  $v \in V$ , to an update expression which may only refer to variables in V.

•  $\mathcal{F}_s$ ,  $\mathcal{F}_w \subseteq 2^{R_o \cup R_\varepsilon}$  are sets of subsets of the transitions which characterize strongly and weakly *fair executions* of the state machine A respectively.

Note that the guard and update expressions in the description of an ESM might involve functions whose interpretations are unknown. If the description of an ESM contains at least one occurrence of a function symbol  $f_u \in \mathfrak{U}$  in any of its guards or in any of its update functions, then we call such a description an ESM sketch (ESM-SK).

#### 2.2.5 Executions