## University of Pennsylvania **ScholarlyCommons**

Departmental Papers (ESE)

Department of Electrical & Systems Engineering

11-1-2007

# Linear Current-Mode Active Pixel Sensor

Ralf M. Philipp Johns Hopkins University

David Orr Johns Hopkins University

Viktor Gruev University of Pennsylvania, vgruev@seas.upenn.edu

Jan Van der Spiegel University of Pennsylvania, jan@seas.upenn.edu

Ralph Etienne-Cummings Johns Hopkins University

Follow this and additional works at: http://repository.upenn.edu/ese\_papers

Part of the Electrical and Computer Engineering Commons

#### Recommended Citation

Ralf M. Philipp, David Orr, Viktor Gruev, Jan Van der Spiegel, and Ralph Etienne-Cummings, "Linear Current-Mode Active Pixel Sensor", . November 2007.

Copyright 2007 IEEE. Reprinted from IEEE Journal on Solid State Circuits, Volume 42, Issue 11, November 2007, pages 2482-2491.

This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of the University of Pennsylvania's products or services. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org. By choosing to view this document, you agree to all provisions of the copyright laws protecting it.

This paper is posted at Scholarly Commons. http://repository.upenn.edu/ese\_papers/312 For more information, please contact repository@pobox.upenn.edu.

### Linear Current-Mode Active Pixel Sensor

#### **Abstract**

A current mode CMOS active pixel sensor (APS) providing linear light-to-current conversion with inherently low fixed pattern noise (FPN) is presented. The pixel features adjustable-gain current output using a pMOS readout transistor in the linear region of operation. This paper discusses the pixel's design and operation, and presents an analysis of the pixel's temporal noise and FPN. Results for zero and first-order pixel mismatch are presented. The pixel was implemented in a both a 3.3 V 0.35  $\mu$ m and a 1.8 V 0.18  $\mu$ m CMOS process. The 0.35  $\mu$ m process pixel had an uncorrected FPN of 1.4%/0.7% with/without column readout mismatch. The 0.18  $\mu$ m process pixel had 0.4% FPN after delta-reset sampling (DRS). The pixel size in both processes was 10 X 10  $\mu$ m², with fill factors of 26% and 66%, respectively.

#### Keywords

CMOS analog integrated circuits, image sensors

#### **Disciplines**

**Electrical and Computer Engineering**

#### **Comments**

Copyright 2007 IEEE. Reprinted from *IEEE Journal on Solid State Circuits*, Volume 42, Issue 11, November 2007, pages 2482-2491.

This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of the University of Pennsylvania's products or services. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org. By choosing to view this document, you agree to all provisions of the copyright laws protecting it.

## Linear Current-Mode Active Pixel Sensor

Ralf M. Philipp, Student Member, IEEE, David Orr, Student Member, IEEE, Viktor Gruev, Member, IEEE, Jan Van der Spiegel, Fellow, IEEE, and Ralph Etienne-Cummings, Member, IEEE

Abstract—A current mode CMOS active pixel sensor (APS) providing linear light-to-current conversion with inherently low fixed pattern noise (FPN) is presented. The pixel features adjustable-gain current output using a pMOS readout transistor in the linear region of operation. This paper discusses the pixel's design and operation, and presents an analysis of the pixel's temporal noise and FPN. Results for zero and first-order pixel mismatch are presented. The pixel was implemented in a both a 3.3 V 0.35  $\mu m$  and a 1.8 V 0.18  $\mu m$  CMOS process. The 0.35  $\mu m$  process pixel had an uncorrected FPN of 1.4%/0.7% with/without column readout mismatch. The 0.18  $\mu m$  process pixel had 0.4% FPN after delta-reset sampling (DRS). The pixel size in both processes was  $10\times 10~\mu m^2$ , with fill factors of 26% and 66%, respectively.

Index Terms—CMOS analog integrated circuits, image sensors.

#### I. INTRODUCTION

THE NEED FOR compact, low power devices provides an increasing impetus for sensors integrating imagers and processing circuits on a single die. Current mode active pixel sensors (APS) provide an attractive alternative to the traditional voltage mode APS for focal-plane image processing. The use of current output pixels has two main advantages over the use of their voltage-mode counterparts. First, they simplify many on-chip computation tasks; large scale computations can be performed on the focal plane using current mode computation-on-readout [1]-[3]. Second, many current mode pixels, including the proposed pixel, have fixed output voltages, eliminating the requirement to charge and discharge the column capacitances during readout, yielding the potential for significantly higher scan-out rates. Many proposed current mode active pixel sensors have suffered from high fixed pattern noise (FPN) [4] and have nonlinear transfer characteristics [5], [6]. These nonlinearities reduce the effectiveness of the typical offset-removal circuits used to improve FPN figures [7]. Other current mode pixels have had inverted light-to-output current relationships (producing the maximum output current at minimum light) [6]. The referenced current mode imagers have FPN figures between about 1% [6] and 4% [4]. Their nonlinear conversion characteristics make it difficult to further reduce this FPN using offset correction. First-order FPN cancellation techniques assume linearity; increasing pixel linearity increases

Manuscript received September 11, 2006; revised June 6, 2007. This work was supported in part by the National Science Foundation, the Office of Naval Research and the U.S. Air Force Office of Scientific Research. Chip fabrication was provided by MOSIS.

R. M. Philipp, D. Orr, and R. Etienne-Cummings are with the Department of Electrical and Computer Engineering, The Johns Hopkins University, Baltimore, MD 21218 USA (e-mail: ralfphilipp@ieee.org; retienne@jhu.edu).

V. Gruev and J. Van der Spiegel are with the Department of Electrical and Systems Engineering, University of Pennsylvania, Philadelphia, PA 19104 USA (e-mail: vgruev@seas.upenn.edu; jan@seas.upenn.edu).

Digital Object Identifier 10.1109/JSSC.2007.907168

the efficacy of those techniques. Ref. [8] proposes a technique to lower the power consumption of the technique proposed in [6], thereby allowing operation at higher bias current levels, which increases that pixel's linearity. Numbers for FPN were not provided. The current mode imagers in [6] and [8] require significant output currents in order to achieve linear operation; currents on the order of hundreds of microamps are required, values that are impractical when designing focal plane computation circuits to simultaneously read out multiple pixels.

Voltage mode CMOS image sensors have shown superiority in FPN figures, achieving better than 0.01% matching, or 12 bit image quality after offset correction [9]. A voltage mode technique of note is the active column sensor (ACS) [10], where the pixel's output transistor acts as half of a unity-gain amplifier. This technique retains the benefits of a standard APS design, but reduces the gain errors seen in the APS source-follower.

In this paper, we describe a current-mode imager with inherently low fixed-pattern noise.  $10 \times 10~\mu\text{m}^2$  pixels were implemented in standard 3.3 V 0.35  $\mu\text{m}$  and 1.8 V 0.18  $\mu\text{m}$  CMOS processes. The pixel described in this paper has an uncorrected FPN of 0.7% without and 1.4% with column-parallel readout circuits (0.35  $\mu\text{m}$  process) and 0.4% after offset correction (0.18  $\mu\text{m}$  process).

The 0.35  $\mu$ m process implementation included two 128 × 128 pixel image sensors, with 10 × 10  $\mu$ m<sup>2</sup> pixels, that were used as part of a focal-plane image processing circuit. The description of the imager's application can be found elsewhere [1]; this paper describes the analysis of the imagers themselves. The 0.18  $\mu$ m process implementation included a single 256 × 256 array of 10 × 10  $\mu$ m<sup>2</sup> pixels. The authors have implemented the proposed pixel in two additional processes: 0.5  $\mu$ m 5 V CMOS [11] and 0.18  $\mu$ m 3-D integrated silicon-on-insulator [12].

In Section II of this paper, we describe the proposed pixel's design, operation, and light-to-output current transfer function. In Section III, we describe the generalized readout scheme for the pixel, as well as the readout scheme used in the 0.18  $\mu$ m process imager. An analysis of temporal and fixed pattern noise is presented in Section IV. Results are given in Section V.

#### II. THE PIXEL

#### A. Pixel Operation

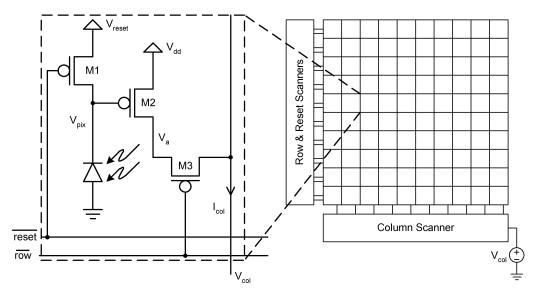

The pixel, shown in Fig. 1, along with its readout architecture, is operated as follows. Switch M1 resets the pixel's integrating node  $V_{\rm pix}$  to a fixed voltage  $V_{\rm reset}$ . After the reset signal is raised, turning M1 off, the photocurrent is integrated for a fixed period, producing a voltage directly proportional to the incident light intensity.  $V_{\rm reset}$  is set so that it is slightly more than one P-threshold  $|V_{tP}|$  below the positive supply  $V_{dd}$

Fig. 1. Active pixel sensor and generalized imager schematic. Voltage source  $V_{\rm col}$  is external to the pixel. All bulk terminals tied to  $V_{dd}$ .

(1) to ensure that the readout transistor M2 is always above threshold:

$$V_{\text{reset}} < V_{dd} - |V_{tP}|. \tag{1}$$

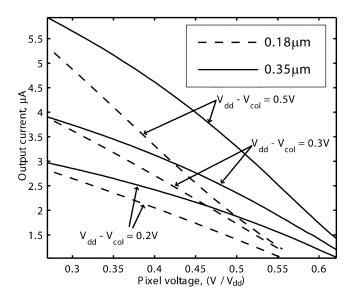

The integrated voltage  $V_{\rm pix}$  is converted to an output column current  $I_{\rm col}$  by transistor M2, acting as a transconductance amplifier, as shown in (2). Under the assumption that  $V_{\rm col}$  is constant and equal to  $V_a$  (4), the transconductance  $G_{\rm pix}$ , given by (5), is approximately linear.  $G_{\rm pix}$  can be controlled by varying  $V_{\rm col}$ . An image sensor incorporating this pixel could vary  $G_{\rm pix}$  to increase readout speed, lower power consumption, or to implement a scaling term in a spatial or temporal filter.

$$I_{\text{col}} = \beta_2 \left[ (V_{dd} - V_{\text{pix}} - |V_{tP}|) V_{sd2} - \frac{V_{sd2}^2}{2} \right]$$

(2)

$$\beta_2 = \frac{\mu_{\text{eff2}} C_{OX} W_2}{L_2} \tag{3}$$

$$V_a = V_{\text{col}} + V_{sd3} \approx V_{\text{col}} \tag{4}$$

$$G_{\rm pix} = \frac{\partial I_{\rm col}}{\partial V_{\rm pix}} \approx -\beta_2 \left( V_{dd} - V_{\rm col} \right). \tag{5}$$

The conversion gain from photo-generated electrons  $e^-$  to  $I_{\rm col}$  is given by

$$\frac{\Delta I_{\rm col}}{e^{-}} \approx \beta_2 \frac{q}{C_{\rm pix}} (V_{dd} - V_{\rm col}) \tag{6}$$

where  $C_{\text{pix}}$  is the capacitance at the integrating node.

Switch M3 connects the pixel to the output bus, typically a column or row line of the image. Ideally, M3 has zero on-resistance  $r_{\rm on3}$ , meaning that the voltage drop across M3 ( $V_a - V_{\rm col}$ ) is 0 V. This approximation, given by (4), becomes less valid at low supply voltages, owing to lower gate source voltages. The finite on resistance of M3 produces nonlinear effects that increase as the supply voltage is reduced. These effects can be ignored in a first-order analysis of the pixel's behavior, but provide a limit to the pixel's scalability. The analytical solution for the complete pixel transfer characteristic, including the effects of M3 on resistance, is provided in the Appendix. If the entire imager shares a single readout circuit, as shown in Fig. 1, the

series resistance of any switches in the column scanner/decoder can be included in M3's series resistance.

The pixel's integration range at  $V_{\text{pix}}$  is from  $V_{\text{reset}}$  down to 0 V. Unlike a standard three–transistor (3T) voltage mode APS, the proposed pixel's lower integration limit is set by the photodiode, not the readout structure. The proposed pixel is capable of integrating to slightly below 0 V, to the point where the photodiode's forward current equals the photocurrent. The full integration range of the pixel is one pMOS threshold less than the power supply. For the 0.35  $\mu$ m process used,  $V_{dd} = 3.3 \text{ V}$ ,  $V_{tP} = -0.78 \text{ V}$ , and the integration range was 2.5 V, while for the 0.18  $\mu$ m process used,  $V_{dd}=1.8$  V,  $V_{tP}=-0.45$  V, and the integration range was 1.2 V. This compares favorably to a 3T APS, which loses two nMOS thresholds (including substantial body effect) and an nMOS  $V_{\mathrm{DSsat}}$ , which would provide an integration range of less than 2 V and 0.7 V for the same processes, respectively. A 3T APS employing a pMOS reset transistor, as seen in many modern APS pixels, loses an nMOS threshold and an nMOS  $V_{DSsat}$ , providing a similar integration range to the proposed pixel.

#### B. Wells

The use of pMOS devices requires the use of an in-pixel n-well. Since the photodiode itself cannot reside in the n-well, the pixel's minimum size is constrained by n-well spacing requirements. The test imagers used  $10 \times 10 \, \mu \text{m}^2$  pixels with 26% and 66% fill factors in standard 0.35  $\mu$ m and 0.18  $\mu$ m processes, respectively. The 0.18  $\mu$ m process pixel's  $10 \times 10 \, \mu \text{m}^2$  size was dictated by external system requirements unrelated to this work. The additional area was used solely for the photodiode; readout transistors were scaled with the process feature size. In a standard submicron process [13], the minimum pitch for a regular pixel layout is  $32\lambda$ , where  $\lambda$  is approximately 1/2 the minimum gate length ( $\lambda = 0.2 \, \mu$ m, 0.1  $\mu$ m and  $32\lambda = 6.4 \, \mu$ m, 3.2  $\mu$ m for the 0.35  $\mu$ m and 0.18  $\mu$ m processes used, respectively).

Modifying the pixel to use nMOS devices would not eliminate the well requirement, as the photodiode would have to reside in an n-well (p+ diffusion to n-well). Well spacing requirements could be avoided by using an n+ to p-substrate diode with

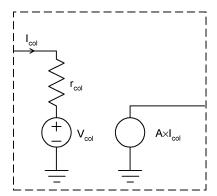

Fig. 2. Generalized image readout circuit. Note that A is in units of output unit per amp.  $r_{\rm col}$  is the input impedance of the device.

nMOS devices. The pixel's layout would then be nearly identical to a standard 3T APS, as the reset could be to  $V_{dd}$  (no separate  $V_{\rm reset}$  would be required). While this would significantly increase the pixel's fill factor or decrease its size, such a design would have several undesirable properties, including having the largest output current (highest noise) at the lowest light level, and reducing the available integration range by one threshold voltage.

#### III. IMAGE READOUT

#### A. Generalized Readout Circuit

Image readout from the pixel is accomplished using any circuit that applies a voltage  $V_{\rm col}$  to the drain of M3 while providing a way to measure the pixel's output current (called  $I_{\rm col}$ , assuming a column parallel readout scan). The input impedance  $r_{\rm col}$ , ideally zero, should be less than the series resistance of the pixel's select transistors. The readout circuit's gain A is in units of readout unit per amp, where the readout unit would typically be amps or volts (meaning the circuit would be called a current conveyor or transimpedance amplifier, respectively). The general form of this readout circuit is shown in Fig. 2.

Linear pixel operation is achieved when  $V_{\rm col}$  is close to, but below,  $V_{dd}$ , keeping M2 in the triode (linear) region of operation. The pixel operates with a nonlinear (quadratic) transfer characteristic when  $V_{\rm col}$  is brought further away from  $V_{dd}$ , such that M2 is in the saturation region. The use of the pixel in this manner will not be discussed in this work.

It should be noted that many readout structures, such as the current conveyor discussed below, will require some steady-state input bias current to guarantee reliable operation (i.e., speed, stability). This can be achieved either by adding a bias current source, or by simply lowering  $V_{\rm reset}$  so as to provide a sufficient current when  $V_{\rm pix} = V_{\rm reset}$ . This has the benefit of slightly increasing pixel linearity, as the pixel's behavior is least linear when M2 is just above threshold.

No double-sampling/offset correction of any kind was performed on the image outputs in the 0.35  $\mu$ m design; the 0.18  $\mu$ m design used a current memory unit to implement double-sampling offset removal. Methods of performing offset correction on currents are discussed in [5], and function much like voltage-domain offset correction.

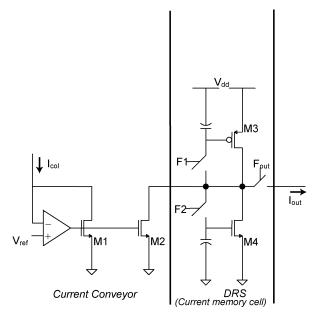

Fig. 3. Readout circuit used in 0.18  $\mu m$  process. Current conveyor and delta-reset sampling.

#### B. Current Conveyor Readout

The proposed pixel implemented in the 0.35  $\mu m$  process used column-parallel first-generation current conveyors (CCI+) to fix the pixel output voltage and provide a copy of the pixel output current. The input impedance of these circuits was simulated to be  $100-200~\Omega$  in the region of expected pixel output currents. This was significantly less than the 2.4 k $\Omega$  on-resistance of the pixel row select switch. The input impedance of the CCI+ "virtual ground" was therefore neglected; the virtual ground was considered perfect. The circuits used are described in [11]; however, the proposed imager's implementation was column parallel (one per column instead of one per chip) and did not include a double-sampling circuit.

The readout scheme for the 0.18  $\mu m$  design is presented in Fig. 3. The readout scheme is composed of two parts. The first part employs a second-generation current conveyor circuit (CCII+) [12]. This circuit is composed of a two-stage operational amplifier with a Miller compensation capacitor operated in a negative feedback mode via transistor M1. The amplifier had a gain bandwidth product of 50 MHz and a DC gain  $A_0$  of 80 dB. The negative feedback configuration pinned the inverting input terminal of the opamp to  $V_{\rm col} \approx V_{\rm ref}$ . The low-frequency input resistance of the current conveyor is given by

$$r_{\rm col} = \frac{1}{g_{m1} A_0} \tag{7}$$

in which  $g_{m1}$  is the transconductance of M1.

The minimum output current from the pixel in the 0.18  $\mu m$  process was 1  $\mu A$  during the reset interval and the measured input resistance of the current conveyor was 10  $\Omega$ . The input capacitance of the current conveyor consists of 256 drain capacitances (from M3 in the pixel) plus the line capacitance of the 2.5 mm long metal bus. With a total input capacitance of 300 fF, the time constant of the current conveyor circuit is 1 ns, giving

an operational bandwidth of 0.3 Grad/s or 53 MHz. The variations of the input terminal of the current conveyor over 10  $\mu$ A input range have been measured to be less than 1  $\mu$ V. The high readout bandwidth is desirable when analog processing units are implemented as part of the readout circuitry.

The second part of the 0.18  $\mu$ m process readout circuitry is the delta-reset sampling (DRS) offset suppression circuitry, which is a modified version of the current memory cell described in [15]. A single offset suppression circuit is used for the entire image array, alleviating column FPN. The DRS cell is composed of coarse and fine sub-memory cells. During the memorization stage of the coarse memory cell, charge injection errors dependent on the input current level are introduced. These signal-dependent charge injections are memorized in the fine memory cell and subtracted from the coarse memory cell.

The DRS of the pixel is performed in two steps. Initially, the output current, after integration, is memorized in the memory cell. The pixel is then reset and the reset-phase output current is subtracted from the previously memorized uncorrected output current. The final current output is independent of the voltage threshold variations of the readout transistor M2 in Fig. 1.

#### IV. Noise

#### A. Pixel Temporal Noise

The pixel circuit uses a pMOS transistor to provide hard reset to a fixed voltage  $V_{\rm reset}$ . This has the advantage of eliminating image lag and guaranteeing reset to a precise voltage, but at the cost of increased reset noise versus a conventional soft reset. Pixels with hard reset exhibit kT/C noise, given by (8), whereas pixels with soft reset have reset noise as low as kT/2C [16]. It should be noted that the DRS circuit used in the 0.18  $\mu m$ process imager doubles the effect of kT/C noise, since noise power from two uncorrelated reset phases is added.

$$\overline{V_{n,\text{reset}}^2} = \frac{kT}{C_{\text{Dix}}}.$$

(8)

During integration, the dark current  $i_{dark}$  and the photo-generated current  $i_{\rm ph}$  contribute shot noise:

$$\overline{V_{n,\text{shot}}^2} = \frac{q\left(i_{\text{ph}} + i_{\text{dark}}\right)}{C_{\text{pix}}^2} t_{\text{int}}.$$

(9)

Note that this assumes that the dark current, coming from the photodiode and the reset device, flows in the same direction as the  $i_{\rm ph}$ . The leakage at the drain of the reset device and the reset device's subthreshold off-current each contribute dark current opposite in direction to the photocurrent, thus increasing the magnitude of pixel shot noise. The use of a reset switch that is two threshold voltages away from "on" ensures that a minimum of subthreshold current flows through the reset device in the  $0.35 \mu m$  process pixel.

The case where the all dark current components flow in the same direction as the photocurrent (or if there is no dark current), a "best case" situation, provides a lower limit (10) for the total shot noise power for a given integrated voltage:

$$\frac{\overline{V_{n,\text{shot}}^2}}{\overline{V_{n,\text{shot}}^2}} \ge \frac{q\left(V_{\text{reset}} - V_{\text{pix}}\right)}{C_{\text{pix}}}.$$

(10)

TABLE I INPUT-REFERRED RANDOM AND FIXED PATTERN NOISE

| Technology                                                | 0.35μm                 | 0.18µm                  |

|-----------------------------------------------------------|------------------------|-------------------------|

| Pixel Capacitance, $C_{pix}$                              | 41 fF                  | 80 fF                   |

| Saturation Charge                                         | 615,000 e <sup>-</sup> | 600,000 e <sup>-</sup>  |

| Dark Current                                              | 4fA (100mV/sec)        | -80fA (-1V/sec)         |

| Reset Noise                                               | $320~\mu V$ $^*$       | $230\mu V$ #            |

| Shot noise @ full scale †                                 | $3.1 \text{ mV}^*$     | 1.6mV #                 |

| Readout noise <sup>†</sup>                                | $4.8~\mathrm{mV}$ *    | 8.0 mV <sup>#</sup>     |

| Total random noise (ignoring 1/f) †                       | 5.7 mV *               | 8.2 mV <sup>#</sup>     |

| Dynamic Range                                             | $64 dB^{\dagger}$      | 53dB <sup>†</sup>       |

| M3 on-resistance $r_{ds3}$                                | $2.4k\Omega$           | $\sim \! \! 10 k\Omega$ |

| Output capacitance $C_{col}$                              | 900fF                  | 300fF                   |

| Fixed-Pattern-Noise* (per-pixel, full-scale)              | 0.7% (17mV)            | 0.4%,                   |

|                                                           | (no correction)        | no correction: 1.6%     |

| Fixed-Pattern-Noise * (with readout mismatch, full-scale) | 1.4% (34mV)            | N/A                     |

For a temperature of 300 K, the power in the photon and dark current shot noise is greater than the reset noise power when the integrated voltage is above 26 mV (11), or about 1% and 2% of full-scale integration voltage in the 0.35  $\mu m$  and 0.18  $\mu m$ process pixels, respectively. This demonstrates that the reset noise is of importance only at low integration (i.e., brightness) levels. Reset noise provides a lower limit on the resolvable pixel integration voltage (most important at short integration times), while dark current provides a lower bound on the resolvable light level (most important at long integration times).

$$\forall V_{\text{pix}} > \frac{kT}{q} \to \overline{V_{n,\text{shot}}^2} > \overline{V_{n,\text{reset}}^2}.$$

(11)

The minimum detectable signal is determined by the power of the reset kT/C noise and dark current shot noise. The pixel's readout thermal noise is proportional to signal power and does not limit the dynamic range. Dark current shot noise power is proportional to integration time, as is the signal power; therefore the dynamic range (DR) remains constant regardless of integration time, as long as the reset noise dominates the dark current shot noise. This happens when the integration time  $t_{\rm int}$  is less

$$t_{\rm int} < \frac{C_{\rm pix}kT}{qi_{\rm dark}}.$$

(12)

The dark current was measured by resetting the pixels once and then reading multiple images in zero light. This measurement was repeated multiple times and the results were averaged. Calculated and measured noise values are summarized in Table I.

#### B. Readout Temporal Noise

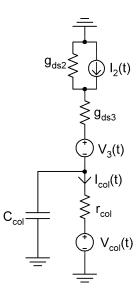

The small-signal circuit in Fig. 4 was used to compute the readout noise from thermal sources. Readout noise was referred

<sup>\*:</sup> at  $V_{col} = 2.9 \text{V}$ ,  $V_{reset} = 2.4 \text{V}$ \*: at  $V_{col} = 1.7 \text{V}$ ,  $V_{reset} = 1.2 \text{V}$

Fig. 4. Readout temporal noise sources, including generalized readout circuit. Noise is measured at  $I_{\rm col}$ .  $C_{\rm col}$  is the column (pixel output) capacitance.

to the circuit's output  $I_{\rm col}$ . The output (typically column or row)  $-3~{\rm dB}$  bandwidth is given by (13). This bandwidth was sufficient in both imagers to assume steady-state conditions for readout noise analysis.

$$f_{-3\text{dB}} \approx \frac{1}{2\pi r_{\text{col}} C_{\text{col}}}.$$

(13)

The output  $(I_{col})$  referred noise due to transconductor M2 and row select switch M3 are given by

$$\overline{I_{n,\text{M2,col}}^{2}} = \frac{2kT}{C_{\text{col}}} \frac{g_{ds2}g_{ds3}^{2}}{r_{\text{col}}(g_{ds2} + g_{ds3})(g_{ds2} + g_{ds3} + g_{ds2}g_{ds3}r_{\text{col}})}$$

(14)

$$\overline{I_{n,\text{M3,col}}^{2}} = \frac{2kT}{C_{\text{col}}} \frac{g_{ds2}^{2}g_{ds3}}{r_{\text{col}}\left(g_{ds2} + g_{ds3}\right)\left(g_{ds2} + g_{ds3} + g_{ds2}g_{ds3}r_{\text{col}}\right)}.$$

(15)

By definition, the total power of the output-referred thermal noise due to the readout circuit (excluding M2 and M3) is not band-limited; the noise power is limited only by temperature. The circuit's input impedance is inherently low (on the order of tens to hundreds of ohms), and a wide variety of possible circuit architectures exist. The contribution of the output noise source itself is therefore ignored.

The readout temporal noise amplitude produced in M2 (16) is proportional to the square-root of its drain-source conductance, which is proportional to the integrated pixel voltage (17).

$$\overline{I_{n,M2}^{2}(t)} = \gamma 4kT\Delta f \ g_{ds2}|_{V_{a}=V_{dd}} \qquad 1 > \gamma > \frac{2}{3} \quad (16)$$

$$g_{ds2} = \beta_{2} \left[ (V_{dd} - V_{\text{pix}} - |V_{tP}|) - 2(V_{dd} - V_{a}) \right]. \quad (17)$$

The maximum output temporal noise occurs at a full-scale integration voltage of 2.4 V and 1.2 V ( $V_{\rm pix}=0$  V) in the 0.35  $\mu{\rm m}$  and 0.18  $\mu{\rm m}$  process pixels, respectively. The calculated output temporal noise for the 0.35  $\mu{\rm m}$  process pixel at full scale (with  $V_{\rm col}=2.9$  V) is 56 nA $_{\rm rms}$ . Referred back to the pixel, this is approximately 5.7 mV $_{\rm rms}$ , or 1500 e $^-$ . Since the output current is

linearly proportional to the integrated voltage, the output noise power is roughly proportional to the light level. At 10% full-scale, the input-referred output noise is about 2.2 mV $_{\rm rms}$ . The 0.18  $\mu$ m process pixel was calculated to have 8.2 mV $_{\rm rms}$  of total (excluding 1/f) input-referred temporal noise at full-scale (with  $V_{\rm col}=1.7$  V). The resulting calculated full-scale signal-to-noise ratios (SNR) are 42 dB and 39 dB for the 0.35  $\mu$ m and 0.18  $\mu$ m process imagers, respectively.

Lowering the pixel output voltage, and thus increasing the pixel transconductance, decreases the input-referred readout noise and increases the SNR. For a given pixel voltage, the rms readout noise grows only slightly with increasing transconductance, but the noise level, when referred back to the pixel, is divided by a larger number.  $V_{\rm col}=2.8~{\rm V}$  was calculated to have 4 mV of input referred noise at full-scale. This comes at the price of increased power consumption and a smaller linear integration range.

#### C. Fixed Pattern Noise

The pixel, operating without FPN, is considered to follow the model:

$$I_{\text{col,ideal}} = G_{\text{ideal}} V_{\text{pix}} + I_{\text{DC,ideal}}.$$

(18)

where the integrated light level  $V_{\rm pix}$  is converted to a current  $I_{\rm col,ideal}$  by the ideal linear transconductance  $G_{\rm ideal}$ . An offset current  $I_{\rm DC,ideal}$ , uniform across the pixel array and independent of light level, is considered part of the ideal transfer characteristic. This analysis considers pixel FPN to consist of additive offset ( $I_{\rm DC,fpn}$ ) and multiplicative gain ( $G_{\rm fpn}$ ) errors, both normalized:

$$I_{\text{col}} = G_{\text{ideal}} V_{\text{pix}} \left( 1 + G_{\text{fpn}} \right) + I_{\text{DC,ideal}} \left( 1 + I_{\text{DC,fpn}} \right). \tag{19}$$

The proposed APS utilizes a hard reset to a fixed voltage; therefore reset transistor threshold mismatch does not contribute significantly to pixel FPN. However, readout transconductor M2 threshold mismatch contributes directly to the pixel output current mismatch. This mismatch is part of the additive  $I_{\rm DC,fpn}$  term, meaning that  $V_{\rm pix}$  does not appear in (20), and can be removed using double-sampling techniques.

$$\frac{\partial I_{\text{col}}}{\partial V_{tp2}} = \beta_2 \left( V_{dd} - V_{\text{col}} \right). \tag{20}$$

Unlike the standard 3T APS, the proposed pixel's transfer function includes a significant nonunity gain term (5) that is set by the transistors in the pixel. Mismatch in this gain term contributes directly to observed fixed pattern noise at nonzero output. This gain term is proportional to  $\beta_2$ , which includes the size ratio of M2 (3). This multiplicative mismatch is not removed by standard mismatch-correction (offset-removal) circuits; a minimum 2-point correction is required to remove this error. The use of a separate reset voltage enables such a 2-point correction by allowing all pixels'  $V_{\rm pix}$  to be set to the same fixed voltage, thereby extracting slope information. This technique would also permit *in situ* acquisition of the data necessary for readout gain correction without the need for uniform illumination or complex spatiotemporal processing schemes [18], and

Fig. 5. Pixel transfer characteristics: integrated voltage to output current.  $V_{dd}=3.3~{\rm V}$  for 0.35  $\mu{\rm m}$  pixel,  $V_{dd}=1.8~{\rm V}$  for 0.18  $\mu{\rm m}$  pixel.

was used below to characterize the pixels' transfer function, but was not implemented for image readout.

$$\frac{\partial I_{\rm col}}{\partial \beta_2} = V_{sd2} \left( V_{dd} - V_{tp} - V_{\rm pix} \right) - \frac{V_{sd2}^2}{2} \propto -V_{\rm pix} V_{sd2}. \tag{21}$$

Due to the sensitivity to transistor characteristics described by (20) and (21), the test imagers' readout transconductors M2 were made significantly larger than minimum size: a square device of roughly triple the minimum width in the 0.35  $\mu$ m process and a rectangular device of W/L = 0.3 for the 0.18  $\mu$ m process.

The  $0.35~\mu m$  process test imager contained a column-parallel readout structure, which introduced significant inter-column mismatch. To remove the effects of this mismatch, which would not be present if a global readout circuit were used, FPN calculations were performed along the column. The individual column FPN values were then combined (root-mean-square) to compute the FPN. This method makes the assumption that the pixel itself does not have any inherent column-to-column bias in its mismatch; the mismatch is assumed to be random over the imager [19]. The measured pixel FPN was 0.7% at full scale. The FPN, when including the effects of the column circuit mismatch, was 1.4% at full scale.

The FPN in the gain term was also evaluated by forcing each pixel to a range of reset voltages and reading the output current. The relationship between  $V_{\rm pix}$  and  $I_{\rm col}$  for various output voltages  $V_{\rm col}$  is plotted in Fig. 5. Note that direct manipulation of  $V_{\rm pix}$  takes into account neither variations in the pixels' quantum efficiency nor the variations in pixel capacitance. Neither of these two considerations is unique to this pixel, which uses a standard n+ diffusion to p-substrate diode.

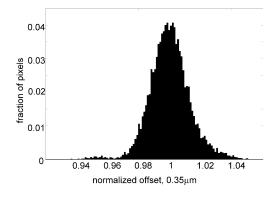

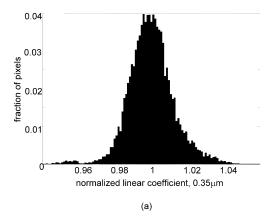

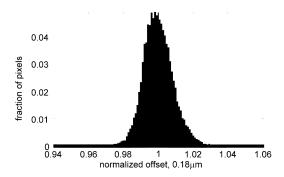

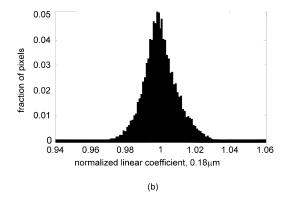

Linear curve fits were performed on measured transfer curves between  $V_{\rm pix}$  and  $I_{\rm col}$  to acquire  $G_{\rm fpn}$  and  $I_{\rm DC,fpn}$  (multiplicative and offset FPN values). The deviation of each pixel's first-order fit from the global first-order fit was obtained. The distribution of these deviations  $(1+I_{\rm DC,fpn}$  and  $1+G_{\rm fpn})$  is shown in Fig. 6(a) and (b) for the 0.35  $\mu$ m and 0.18  $\mu$ m process imagers,

respectively. It can be seen that the pixel mismatch sees similar amounts of offset FPN and gain FPN. Note that these data, taken at  $V_{\rm pix}$  values from 0 to 50% saturation, exhibit higher mismatch levels than the imager operating at full scale (down to 0 V); the use of a pMOS reset transistor did not permit directly controlling  $V_{\rm pix}$  below 1.1 V and 0.5 V for the 0.35  $\mu$ m and 0.18  $\mu$ m process imagers, respectively.

The calculated and measured results for temporal and fixed pattern noise in the 0.35  $\mu m$  and 0.18  $\mu m$  process pixels are summarized in Table I.

#### V. RESULTS

#### A. 0.35 µm Process

The 0.35  $\mu$ m process pixel was implemented in a 3.3 V n-well 0.35  $\mu$ m CMOS process with four metal and two polysilicon interconnect layers. The pixel was  $10 \times 10~\mu\text{m}^2$  in size and had a 26% fill factor. The test chip included two  $128 \times 128$  pixel imagers with column parallel readout and on-chip analog current-mode computation circuitry. Offset correction circuits such as correlated double-sampling (CDS) or delta-reset sampling (DRS) were not used on the chip.

The measured rms dark current was 4 fA (100 mV/s), or 4.2% of full-scale per second. The resulting dynamic range, including the effects of calculated reset noise and measured dark current shot noise, as well as readout thermal noise on the integrated dark current, is 64 dB at  $t_{\rm int}=33$  ms. The tested pixel's dynamic range is constant at 67 dB up to approximately 25 ms of integration time, at which point it begins to decrease because of dark current shot noise.

The imager's power consumption is determined primarily by the pixel output current and the readout circuit, which was not individually measurable in the test chip. By design, the image readout power consumption is proportional to output current, and therefore proportional to light intensity. The test chip used column-parallel readout circuitry to read an entire row of 128 pixels simultaneously for use in analog current-mode computation circuits. The simulated power consumption, with all 128 columns active pixels illuminated at 50% of saturation brightness, was 4 mW. Scanning one pixel requires approximately six times the pixel output current, or approximately 60  $\mu W$  (assuming 50% saturation) plus the power consumption of the digital scanning circuits.

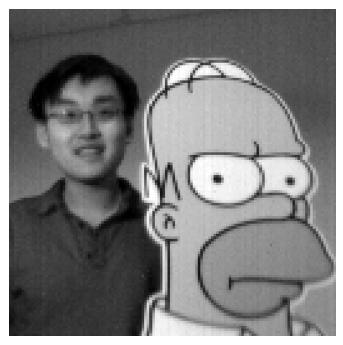

A sample image is shown in Fig. 7. The imager's characteristics are summarized in Table II.

#### B. 0.18 µm Process

The 0.18  $\mu$ m process pixel was implemented in a 1.8 V n-well 0.18  $\mu$ m CMOS process with six metal and one polysilicon interconnect layers. The pixel was  $10 \times 10 \ \mu\text{m}^2$  in size and had a 66% fill factor. The test chip included a 256  $\times$ 256 pixel imager with global readout and offset correction circuits.

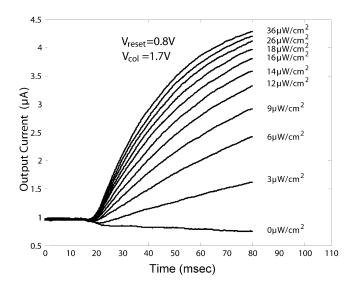

The 0.18  $\mu$ m image sensor was tested for linearity, FPN, and memory unit (DRS unit) accuracy. The image sensor was composed of  $256 \times 256$  photo elements, with pixel size of  $10 \times 10 \ \mu\text{m}^2$  and a fill factor of 66%. The transfer characteristics of the photo pixels were measured and presented in Fig. 8. The horizontal axis presents the output current as a function

Fig. 6. (a) Offset and gain error distributions (0.35  $\mu$ m process pixel). (b) Offset and gain error distributions (0.18  $\mu$ m process pixel, after double-sampling).

of integration time. The set of curves was recorded at different light intensities from  $0 \mu W/cm^2$  to  $36 \mu W/cm^2$ . The power supply voltage  $(V_{dd})$  was 1.8 V, column voltage  $(V_{col})$  was 1.7 V, and reset voltage ( $V_{\rm reset}$ ) was 0.8 V. The photo pixels

Fig. 7. Sample image.  $0.35 \,\mu$ m process:  $128 \times 128$  pixels. No offset correction. Note that the majority of the FPN is the form of readout column mismatch.

TABLE II IMAGE SENSOR CHARACTERISTICS

| Technology                        | 0.35μm, 4m2p                                      | 0.18µm, 6m1p                           |

|-----------------------------------|---------------------------------------------------|----------------------------------------|

| Supply voltage                    | 3.3V                                              | 1.8V                                   |

| $ V_{tP} $                        | $\sim 0.78V$                                      | ~0.45V                                 |

| Pixel array size                  | 128 × 128                                         | 256 × 256                              |

| Pixel size                        | $10\times10\mu\text{m}^2$                         | $10\times10\mu\text{m}^2$              |

| Fill factor                       | 26%                                               | 66%                                    |

| Maximum frame rate                | > 30 frames/s                                     | > 30frames/s                           |

| Total input-referred random noise | $5.7~\text{mV}_{\text{rms}}^{}*\dagger}$          | $8.2~mV_{rms}^{~\#\uparrow}$           |

| Fixed-pattern-noise               | $0.7\%  \left(17 \text{mV}_{\text{rms}}\right)^*$ | 0.4% (2 mV <sub>rms</sub> ) *          |

| (per-pixel)                       | (no correction)                                   | (after CDS)                            |

| Signal to Noise Ratio             | 42dB * †                                          | 39dB #†                                |

| (full-scale, no 1/f noise)        |                                                   |                                        |

| Dynamic Range                     | 64dB *†                                           | $53 dB^{\# \dagger} (t_{int} = 33 ms)$ |

<sup>\*:</sup> at  $V_{col} = 2.9$ V,  $V_{reset} = 2.4$ V,  $t_{int} = 33$ ms. \*: at  $V_{col} = 1.7$ V,  $V_{reset} = 0.8$ V,  $t_{int} = 60$ ms.

were held in reset mode from 0 s to 20 ms, at which point the reset transistor was turned off, allowing the pixel to begin integrating the photocurrent for an integration time  $t_{\rm int} = 60$  ms. Given the bias voltages ( $V_{\text{reset}}$  and  $V_{\text{col}}$ ), the pixel output current remained linear within 99% for light intensities up to 9  $\mu$ W/cm<sup>2</sup>. For this light intensity, the measured FPN after DRS was 0.4%.

For the higher light intensity of 36  $\mu$ W/cm<sup>2</sup>, the linearity of the output current was reduced to 88%. This nonlinearity is due to several factors. First, the pixel integration voltage was below 0 V, near its lowest possible value. Additionally, the high output current creates a large voltage drop across the switch transistor M3; the approximation given by (4) becomes less valid. Hence,

<sup>†:</sup> Calculated, (ignoring 1/f noise)

Fig. 8. Output current as a function of time and light intensity for 0.18  $\mu m$  process imager (reset at 20 ms).

readout transistor M2 sees substantially different drain voltages, and thus transconductances, during the reset and readout phases. This voltage difference causes nonlinear current output, which reduces the effectiveness of the DRS circuit.

The third contribution to the nonlinear output is the mobility degradation due to the high  $V_{sg}$  of transistor M2, which is more pronounced in technologies with smaller feature sizes. The FPN figure for this light level increases to 0.85%. For high intensities, the image sensor can be biased with a reset voltage closer to  $V_{dd}$ , or a higher column voltage, which will decrease the output current. Hence, the pixel's linearity can be increased, which in turn will decrease the FPN, at the cost of decreased SNR.

A large dark current  $i_{\rm dark}$  can also be observed in Fig. 8; the output current under zero illumination decreases with time. This indicates that the dark current, coming from the reset transistor, flows in the reverse direction of the photocurrent. An average of  $i_{\rm dark} = -80$  fA (1 V/sec) dark current was measured, with a standard deviation of 30 fA. In addition, less than 0.5% of the total number of pixels exhibited very large dark current ( $|i_{\rm dark}| > 800$  fA). These "dead" pixels were excluded from the FPN measurement. The large negative dark current, from transistor off-current and gate leakage, was attributed to the use of a standard 0.18  $\mu$ m CMOS process.

Comparing Figs. 5–8, it can be seen that the 0.18  $\mu m$  process pixel is least linear at high levels of integration and high output currents. The effects for high light levels reflect pixel saturation, which are not unique to this imager. The behavior at lower light levels (12  $\mu W/cm^2$  and lower) is far more linear, and reflects the transfer characteristics shown in Fig. 5.

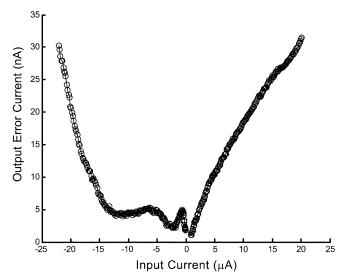

Offset correction was performed using a current memory unit. The memory unit was tested for various input currents at a sampling rate of 10 MHz; the results are presented in Fig. 9. For a current range of  $\pm 20~\mu\text{A}$ , the maximum measured error current was less than 20 nA. This indicates that the memory unit can replicate/memorize a current over a  $\pm 20~\mu\text{A}$  range with 10 bit accuracy at a 10 MHz sampling rate. The bidirectional input current can be memorized in the memory cell due to a constant bias

Fig. 9. A memory unit is used to implement a DRS unit. The output error current is measured as a function of the input current.

current flowing through the memory transistors. As long as the input current is smaller than the bias current, the memory cell can memorize the current. In the measurements shown in Fig. 9, the bias current was set to  $22~\mu\text{A}$ , allowing for successful memorization of an input current of  $\sim 21.5~\mu\text{A}$ . The bidirectional current memory cell can be easily used as a part of a processing unit, where the input current can be scaled with both positive and negative coefficients. The offset currents can be cancelled out by memorizing a scaled version of an input current and subtracting it from a scaled version of a reference current.

The total power consumption of the 0.18  $\mu$ m process imager was simulated to be 0.6 mW, including the double-sampling unit. The tested chip included three double sampling units, which, together with the 256 × 256 pixel imager, consumed 2.5 mW, excluding digital scanning circuits.

#### C. Comparison

The 0.35  $\mu$ m and 0.18  $\mu$ m process imagers exhibited linear transfer characteristics shown in Fig. 5. Both were within 6% of linear (worst case) for integrated values up to 50% of full-scale integration. Both imagers' linearity worsened at the extremes of integration (Figs. 5 and 8); by lowering the reset voltage, linearity could be increased at the cost of reduced dynamic range. The 0.18  $\mu$ m process imager exhibited worse uncorrected FPN than the 0.35  $\mu$ m process imager (1.4% versus 0.7%), but was equipped with double-sampling circuits that reduced FPN to 0.4%.

Using standard CMOS rules, directly scaling the 0.35  $\mu$ m process pixel's layout to the 0.18  $\mu$ m process would result in a 5 × 5  $\mu$ m<sup>2</sup> pixel size. This would quadruple the imager spatial resolution, but the reduced well capacity would decrease the dynamic range and SNR.

The high subthreshold leakage in the 0.18  $\mu$ m process pixel's reset transistor created a large dark current, which was about 20 times larger than  $i_{\rm dark}$  in the 0.35  $\mu$ m process pixel. This issue could be addressed in future work through the use of a 3.3 V thick-oxide nMOS reset transistor [20].

$$I_{\text{col}} = \frac{\beta_{2}\beta_{3}}{2\left(\beta_{2} + \beta_{3}\right)^{2}} \cdot \begin{pmatrix} \beta_{3}\left(V_{dd}^{2} - V_{\text{out}}^{2} + 2V_{\text{col}}V_{tP} + 2V_{\text{pix}}V_{tP} - 2V_{dd}\left(V_{\text{pix}} + V_{tP}\right)\right) \\ +\beta_{2}\left(V_{dd}^{2} - V_{\text{col}}^{2} + 2V_{\text{col}}V_{tP} + 2V_{\text{pix}}\left(V_{\text{pix}} + V_{tP}\right)\right) \\ -2V_{dd}\left(V_{\text{pix}} + V_{tP}\right) \end{pmatrix} \\ +2V_{\text{pix}}\left(\begin{cases} \beta_{3}^{2}\left(V_{\text{col}} - V_{tP}\right)^{2} + \beta_{2}^{2}\left(V_{\text{pix}} - V_{dd} + V_{tP}\right)^{2} \\ +\beta_{2}\beta_{3}\left(V_{\text{col}}^{2} + V_{dd}^{2}\right) \\ -2\left(V_{\text{col}}V_{tP} + V_{dd}\left(V_{\text{pix}} + V_{tP}\right) - V_{tP}\left(V_{\text{pix}} + V_{tP}\right)\right) \\ -V_{tP}\left(V_{\text{pix}} + V_{tP}\right) \end{pmatrix}\right) \right)$$

#### VI. CONCLUSION

A current mode active pixel sensor with low fixed pattern noise, implemented in both 0.35  $\mu$ m and 0.18  $\mu$ m standard CMOS processes, has been presented. The image sensors' characteristics are summarized in Table II. The underlying pixels in the 0.35  $\mu$ m process imager exhibited only 0.7% FPN, a result that was achieved without on-chip correction of any kind. The  $0.18 \mu m$  process imager attained 0.4% FPN after delta-reset sampling. The imagers' light-to-output current transfer characteristics were within 6% of linear. The current output pixels are suitable for use in focal plane computation-on-readout image processing tasks.

#### APPENDIX

The analytical solution for the pixel transfer characteristic (from integrated voltage  $V_{\text{pix}}$  to output current  $I_{\text{col}}$ ) is shown in the equation at the top of the page.

Using linear triode transistor models, ignoring the quadratic drain-source dependence, yields the following simplification, which is valid for small drain-source voltages:

$$\begin{split} I_{\rm col} &= \frac{\beta_2}{2} \left( V_{\rm pix} - V_{dd} + V_{tP} \right) \\ &\times \begin{pmatrix} \left( V_{\rm col} - 2V_{dd} + V_{tP} \right) + \frac{\beta_2}{\beta_3} \left( V_{\rm pix} - V_{dd} + V_{tP} \right) + \\ & - \left( \frac{\left( \frac{\beta_2}{\beta_3} \right)^2 \left( V_{\rm pix} - V_{dd} + V_{tP} \right)^2}{+ 2 \frac{\beta_2}{\beta_3} \left( V_{\rm pix} - V_{dd} + V_{tP} \right) \left( V_{\rm col} - 2V_{dd} + V_{tP} \right)} + \left( V_{\rm col} - V_{tP} \right)^2 \end{pmatrix} \,. \end{split}$$

#### REFERENCES

- [1] R. M. Philipp and R. Etienne-Cummings, "A 128x128 33mW 30frames/s single-chip stereo imager," in 2006 IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, San Francisco, CA, Feb. 2006, pp. 2050-2059

- [2] R. Etienne-Cummings, S. Mehta, R. Philipp, and V. Gruev, "Neuromorphic vision systems for mobile applications," in *Proc.* 2006 IEEE Custom Integrated Circuits Conf. (CICC), San Jose, CA, Sep. 2006, pp. 531-534.

- [3] V. Gruev, J. Van der Spiegel, and N. Engheta, "Image sensor with focal plane extraction of polarimetric information," in Proc. IEEE ISCAS, May 2006, p. 4.

- [4] R. M. Philipp and R. Etienne-Cummings, "Single-chip stereo imager," Analog Integrat. Circuits Signal Process., vol. 39, pp. 237-250, Jun.

- [5] J. Nakamura, B. Pain, T. Nomoto, T. Nakamura, and E. R. Fossum, "On-focal-plane signal processing for current-mode active pixel sensors," IEEE Trans. Electron Devices, vol. 44, no. 10, pp. 1747–1758, Oct. 1997.

- [6] L. G. McIlrath, V. S. Clark, P. K. Duane, R. D. McGrath, and W. D. Waskurak, "Design and analysis of a 512x768 current-mediated active pixel array image sensor," IEEE Trans. Electron Devices, vol. 44, no. 10, pp. 1706–1715, Oct. 1997.

- [7] A. El Gamal, "High dynamic range image sensors," presented at the IEEE Int. Solid-State Circuits Conf.-Tutorial, San Francisco, CA,

- F. Boussaid, A. Bermak, and A. Bouzerdoum, "An ultra-low power operating technique for mega-pixels current-mediated CMOS imagers,' IEEE Trans. Consum. Electron., vol. 50, no. 1, pp. 46-53, Feb. 2004.

- J. Yang, K. Fife, L. Brooks, C. Sodini, A. Betts, P. Mudunuru, and H. Lee, "A 3 megapixel, low-noise flexible architecture CMOS image sensor," in IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, San Francisco, CA, 2006, pp. 496-497.

- [10] T. L. Vogelsong, J. Zarnowski, M. Pace, and T. Zarnowski, "Scientific/ industrial camera-on-a-chip using active column sensor CMOS imager core," in Proc. SPIE, May 2000, vol. 3965, pp. 102-113.

- [11] V. Gruev, R. Etienne-Cummings, and T. Horiuchi, "Linear current mode imager with low fix pattern noise," in Proc. IEEE ISCAS, May 2004, vol. 4, pp. 860–863.

- [12] V. Gruev, R. M. Philipp, J. van der Spiegel, and R. Etienne-Cummings, "Image sensor with general spatial processing in a 3D integrated circuit technology," in Proc. IEEE ISCAS, May 2006, p. 4.

- [13] Design Rules: MOSIS Scalable CMOS Edition 8, [Online]. Available: http://www.mosis.org/Technical/Designrules/scmos/scmos-main.html

- A. M. Ismail and A. M. Soliman, "Wideband CMOS current conveyor," Electron. Lett., vol. 34, no. 25, pp. 2368–2369, Dec. 1998. [15] J. Hughes and K. Moulding, "S<sup>3</sup>I: The seamless S<sup>2</sup>I switched-current

- cell," in *Proc. IEEE ISCAS*, Hong Kong, Jun. 1997, vol. 1, pp. 113–116.

- [16] H. Tian, B. Fowler, and A. El Gamal, "Analysis of temporal noise in CMOS photodiode active pixel sensor," *IEEE J. Solid-State Circuits*, vol. 36, no. 1, pp. 92–101, Jan. 2001.

- [17] B. Wang, J. R. Hellums, and C. Sodini, "MOSFET thermal noise modeling for analog integrated circuits," IEEE J. Solid-State Circuits, vol. 29, no. 7, pp. 833-835, Jul. 1994.

- [18] S. Lim and A. El Gamal, "Gain fixed pattern noise correction via optical flow," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 51, no. 4, pp. 779-786, Apr. 2004.

- [19] A. El Gamal, B. Fowler, H. Min, and X. Liu, "Modeling and estimation of FPN components in CMOS image sensors," in Proc. SPIE, San Jose, CA, Jan. 1998, vol. 3301, pp. 168-177.

- S. Kleinfelder, S. Lim, X. Liu, and A. El Gamal, "A 10,000 frames/s CMOS digital pixel sensor," IEEE J. Solid-State Circuits, vol. 36, no. 12, pp. 2049–2059, Dec. 2001.

Ralf M. Philipp (S'98) received the B.S. degree in electrical engineering from The Cooper Union, New York, NY, in 2000, and the M.S.E. degree in electrical and computer engineering from The Johns Hopkins University, Baltimore, MD, in 2002. He is currently pursuing the Ph.D. degree at The Johns Hopkins University. His research interests include mixed-signal VLSI, CMOS imagers, and sensors.

**David M. Orr** (S'03) is pursuing the B.S. degree in computer engineering at The Johns Hopkins University, Baltimore, MD, and expects to graduate in 2007.

Dr. Van der Spiegel is the recipient of the IEEE Third Millennium Medal, the UPS Foundation Distinguished Education Chair and the Bicentennial Class of 1940 Term Chair. He received the Christian and Mary Lindback Foundation, and the S. Reid Warren Award for Distinguished Teaching. He has served on several IEEE program committees and is currently the program chair of the 2007 International Solid-State Circuit Conference (ISSCC). He has also served on the Technology Directions and the Executive Committees of the ISSCC. He has been the chapters Chairs coordinator of the IEEE Solid-State Circuits Society (SSCS) for the past eight years.

**Viktor Gruev** (M'06) received the B.S. degree in electrical engineering with distinction from Southern Illinois University, Carbondale, IL, in 1997. He received the M.S. and Ph.D. degrees in electrical engineering from The Johns Hopkins University, Baltimore, MD, in 2000 and 2004, respectively.

Currently, he is a Post Doctoral Researcher at the University of Pennsylvania, Philadelphia. His research interests include mixed-signal VLSI systems, polarization image sensors, 3-D image sensors, VLSI systems for adaptive optics and computer vision.

**Jan Van der Spiegel** (S'73–M'79–SM'90–F'02) received the Masters and Ph.D. degrees in electrical engineering from the University of Leuven, Belgium, in 1974 and 1979, respectively.

He joined the University of Pennsylvania, Philadelphia, in 1981 where he is currently a Professor in the Department of Electrical and Systems Engineering and the Director of the Center for Sensor Technologies. His research interests are in mixed-mode VLSI design, biologically based sensors and sensory information processing systems,

micro-sensor technology, and analog-to-digital converters.

Ralph Etienne-Cummings (M'98) received the B.Sc. degree in physics from Lincoln University of Pennsylvania in 1988, and the M.S.E.E. and Ph.D. degrees in electrical engineering from the University of Pennsylvania, Philadelphia, in 1991 and 1994, respectively.

Currently, he is an Associate Professor of computer engineering at The Johns Hopkins University (JHU), Baltimore, MD. He is the Director of Computer Engineering at JHU and the Institute of Neuromorphic Engineering. He is also the Associate

Director for Education and Outreach of the National Science Foundation (NSF) sponsored Engineering Research Centers on Computer Integrated Surgical Systems and Technology at JHU. His research interests include mixed-signal VLSI systems, computational sensors, computer vision, neuromorphic engineering, smart structures, mobile robotics and legged locomotion.

Dr. Etienne-Cummings has served as Chairman of the IEEE Circuits and Systems (CAS) Technical Committee on Sensory Systems and on Neural Systems and Application, and was re-elected as a member of CAS Board of Governors in 2006. He is the recipient of the NSF's Career and Office of Naval Research Young Investigator Program Awards. He recently was named a Visiting African Fellow and a Fulbright Fellowship Grantee for his current sabbatical at the University of Cape Town, South Africa.