#### University of Pennsylvania **ScholarlyCommons**

Department of Physics Papers

Department of Physics

4-14-2011

# Optimized Photolithographic Fabrication Process for Carbon Nanotube Devices

Samuel M. Khamis

University of Pennsylvania, smk@physics.upenn.edu

R. A. Jones

University of Pennsylvania

A. T. Charlie Johnson

University of Pennsylvania, cjohnson@physics.upenn.edu

Follow this and additional works at: http://repository.upenn.edu/physics\_papers

Part of the Physics Commons

#### Recommended Citation

Khamis, S. M., Jones, R. A., & Johnson, A. C. (2011). Optimized Photolithographic Fabrication Process for Carbon Nanotube Devices. Retrieved from http://repository.upenn.edu/physics\_papers/162

Suggested Citation:

S.M. Khamis, R.A. Jones and A.T. Charlie Johnson. (2011). "Optimized photolithographic fabrication process for carbon nanotube devices." AIP Advances 1, 022106.

AIP Advances is published by the American Institute of Physics. Copyright © 2011, owned by the Authors.

This paper is posted at Scholarly Commons. http://repository.upenn.edu/physics\_papers/162 For more information, please contact repository@pobox.upenn.edu.

## Optimized Photolithographic Fabrication Process for Carbon Nanotube Devices

#### **Abstract**

We have developed a photolithographic process for the fabrication of large arrays of single walled carbon nanotube transistors with high quality electronic properties that rival those of transistors fabricated by electron beam lithography. Abuffer layer is used to prevent direct contact between the nanotube and the novolac-based photoresist, and a cleaning bake at 300C effectively removes residues that bind to the nanotube sidewall during processing. In situ electrical measurement of a nanotube transistor during a temperature ramp reveals sharp decreases in the ON-state resistance that we associate with the vaporization of components of the photoresist. Data from nearly 2000 measured nanotube transistors show an average ON-state resistance of  $250 \pm 100 \,\mathrm{k}\Omega$ . This new process represents significant progress towards the goal of highyield production of large arrays of nanotube transistors for applications including chemical sensors and transducers, as well as integrated circuit components.

#### **Disciplines**

Physical Sciences and Mathematics | Physics

#### Comments

Suggested Citation:

S.M. Khamis, R.A. Jones and A.T. Charlie Johnson. (2011). "Optimized photolithographic fabrication process for carbon nanotube devices." *AIP Advances* **1**, 022106.

AIP Advances is published by the American Institute of Physics. Copyright © 2011, owned by the Authors.

### Optimized photolithographic fabrication process for carbon nanotube devices

S. M. Khamis, a,b R. A. Jones, and A. T. Charlie Johnson Department of Physics and Astronomy, University of Pennsylvania, Philadelphia, PA USA (Received 17 January 2011; accepted 25 March 2011; published online 14 April 2011)

We have developed a photolithographic process for the fabrication of large arrays of single walled carbon nanotube transistors with high quality electronic properties that rival those of transistors fabricated by electron beam lithography. A buffer layer is used to prevent direct contact between the nanotube and the novolac-based photoresist, and a cleaning bake at 300C effectively removes residues that bind to the nanotube sidewall during processing. In situ electrical measurement of a nanotube transistor during a temperature ramp reveals sharp decreases in the ON-state resistance that we associate with the vaporization of components of the photoresist. Data from nearly 2000 measured nanotube transistors show an average ON-state resistance of 250  $\pm$  100 k $\Omega$ . This new process represents significant progress towards the goal of high-yield production of large arrays of nanotube transistors for applications including chemical sensors and transducers, as well as integrated circuit components. © 2011 Author(s). This article is distributed under a Creative Commons Attribution Non-Commercial Share Alike 3.0 Unported License. [doi:10.1063/1.3582820]

Since the discovery of single walled carbon nanotubes (SWNTs) twenty years ago, <sup>1</sup> there has been great interest in their use as electronic circuit elements, such as field effect transistors (FETs), <sup>2,3</sup> chemical sensors, <sup>4,5</sup> and transducers. <sup>6</sup> Electron beam lithography (EBL) has been the most commonly used fabrication method for SWNT circuits to date, <sup>2,3</sup> but EBL is a serial process, so the production of large arrays of devices or complex circuits is time-consuming and costly. A major goal for the field is thus the development of a fabrication method based on photolithography, a well established technique that enables parallel, wafer-scale patterning of circuits in a matter of seconds. <sup>7</sup>

Past investigations of photolithographically defined SWNT circuits all reported an undesirable scum layer that remains after processing.<sup>8,9</sup> One method to avoid the ill effects of this scum is to define and metalize the electrical leads before nanotube growth.<sup>10</sup> However, this geometry, with the nanotube on top of the leads, has been shown to result in less desirable device characteristics than when the leads are deposited on top of the nanotube.<sup>11</sup>

We report here on a photolithographic process for fabricating large arrays of SWNT field effect transistors (FETs) based on a resist bilayer of Shipley 1813 positive-tone photoresist on top of Microchem SF2S, a polymethyl glutarimide (PMGI) based resist. PMGI is designed for use in photolithographic processing as a sacrificial layer and as the under-layer in bi-layer lift-off metallization processing, and its effectiveness in EUV lithography has been demonstrated. <sup>12</sup> In the field of SWNT devices, PMGI has been shown to have excellent properties as a carrier material for iron catalyst particles for SWNT growth. <sup>13</sup> To our knowledge, however, there have been no reports of its use in an improved photolithographic process for fabricating contacts to high quality SWNT devices. After contact patterning by photolithography based on a PMGI-Shipley 1813 bilayer, we see no evidence of an undesirable scum layer. Device properties are further improved by a cleaning

<sup>&</sup>lt;sup>b</sup>Corresponding authors: smkhamis@gmail.com and cjohnson@physics.upenn.edu

<sup>&</sup>lt;sup>a</sup>Present address: Adamant Technologies, 953 S. van Ness Ave #2, San Francisco CA 94110

bake at 300C after contact metallization. We have measured the electronic characteristics of more than 1000 FETs fabricated using this process and find an "ON" state resistance of  $250k\Omega \pm 100k\Omega$ , indicating that the device quality is equal to that of FETs produced in our lab using electron beam lithography.

SWNTs were grown via catalytic chemical vapor deposition at 900C with a methane feedstock, on degenerately doped silicon wafers coated with 400nm of  $SiO_2$ . <sup>14</sup> SWNT-bearing wafers were spin coated with PMGI resist at 4000 rpm for 45 seconds, and then baked at 150C for five minutes. The samples were then spin coated with Shipley S1813 positive resist for 45 seconds at 5000 rpm, and baked at 130C for 3 minutes. Contacts to nanotube devices were patterned on a Karl Suss MA4 mask aligner, and the resist developed in a 2.2% tetramethylamonium hydroxide (TMAH) solution <sup>15</sup> that also isotropically etches the PMGI underlayer at a rate of  $\sim$ 1nm/sec. Cr/Au contacts were deposited by thermal evaporation, followed by a two-step liftoff process. Samples were soaked in acetone at 65C for 10 minutes to dissolve the S1813 layer, and then transferred to a 2.4% TMAH solution for 15 minutes to dissolve the PMGI layer. The nanotube devices were then treated with a cleaning bake step in air at 300C for 1 hour. For comparison, additional devices were fabricated using a single layer of Shipley S1813 (i.e., no PMGI buffer layer), followed by the same cleaning bake step.

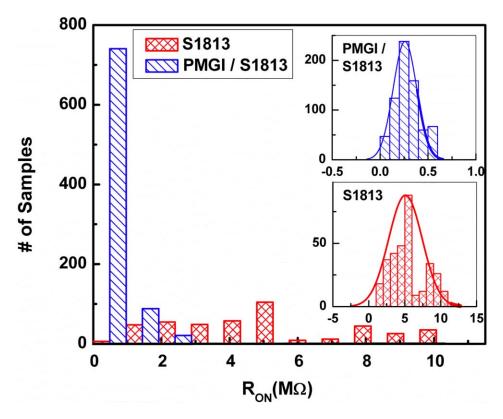

SWNT devices were characterized electrically using the degenerately doped silicon wafer as a gate electrode. Circuits consisting of a single semiconducting SWNT were selected based on their I(V<sub>G</sub>) characteristic. Figure 1 shows a histogram of the "ON" state resistance of 1000 semiconducting SWNT devices fabricated using the PMGI/S1813 bilayer resist, and 700 fabricated with S1813 alone. We find that devices fabricated using the PMGI/S1813 bilayer show an ON-state resistance of 250 k $\Omega \pm 100$  k $\Omega$ , a range that is essentially identical to the best results that we and other groups have obtained using EBL. 16-18 In contrast, samples made using S1813 alone had a much larger ON-state resistance with considerably larger fluctuations (5.0 M $\Omega \pm 3.0$  M $\Omega$ ). This striking difference in contact resistance is attributed to the presence of scum from the S1813 photoresist on the SWNT sidewall and on the substrate surface when the PMGI buffer layer is omitted. Others have reported, and we have verified, that standard photolithographic processing with S1813 alone results in residual nodules of photoresist (~ 2-10 nm diameter) that decorate the sample surface and preferentially accumulate on the SWNT sidewall. This molecular contamination layer is expected to act as an additional tunneling barrier, in series with the Schottky barrier known to form at the nanotube metal junction <sup>19,20</sup> and in this way lead to sharply increased device resistance. No such contamination is observed on samples fabricated with the bilayer process.

We attribute the formation of this undesirable photoresist scum to the presence of  $\pi$ -conjugated aromatic components in the photoresist, e.g., the novolac resin that forms the base of the resist, the diazonapthoquinone (DNQ) photosensitizer, and trace amounts of cresol that arise during the production of the resin. Aromatic molecules bind strongly to the nanotube sidewall due to the attractive  $\pi$ - $\pi$  interaction. While this effect can be exploited to non-covalently attach aromatic molecules to carbon nanotubes, excessive photoresist contamination is very harmful to devices. The PMGI layer in our optimized process is free of  $\pi$ -conjugated species, similar to the electron beam resist PMMA, which can be used to fabricate high quality SWNT transistors. It thus interacts only weakly with the SWNT, and serves as a buffer layer that prevents deposition of photoresist scum after development. We find, however, that some surface contamination remains on the SWNT devices after lift-off, and that this contamination is effectively removed by a cleaning process described below. We attribute this surface contamination to dissolved species that redeposit onto the SWNT sidewall during liftoff.

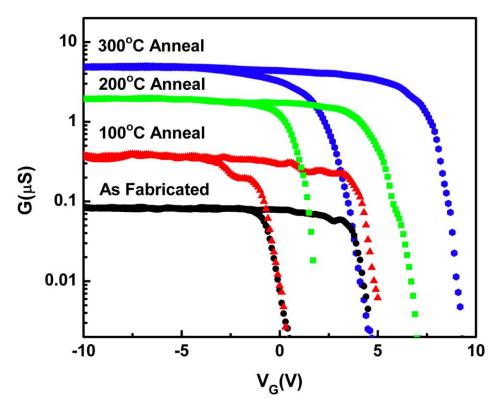

In order to determine the ideal temperature for post process cleaning of the samples, as-fabricated devices were baked for 1 hour each at 100C, 200C, and 300C sequentially, and the current-gate voltage (I-V<sub>G</sub>) characteristic was measured after each bake (Fig. 2). Typically this process resulted in a decrease in ON-state resistance of 2-3 orders of magnitude. We attribute this increase in conductance to both desorption of molecular species adsorbed along the FET channel,  $^{25}$  and annealing of the contacts.  $^{26}$  We also observed a progressive shift of the threshold voltage towards positive voltage, which is characteristic of decreased positive charge near the nanotube. This shift is also attributed to a reduction in molecules adsorbed onto the SWNT sidewall and the nearby  $SiO_2$  surface due to the cleaning bake.

FIG. 1. Histogram of ON-state resistance of FETs fabricated with the PMGI/S1813 bilayer process and a process using a single layer of S1813. FETs fabricated with the bilayer procedure have an  $R_{ON}$  value strongly peaked at  $250 k\Omega \pm 100 k\Omega$ , while  $R_{ON}$  values for devices fabricated with S1813 alone are peaked at  $5M\Omega \pm 3M\Omega$ . Insets: Histogram of 80% of the devices fabricated by each method and a Gaussian fit used to extract the average  $R_{ON}$  values.

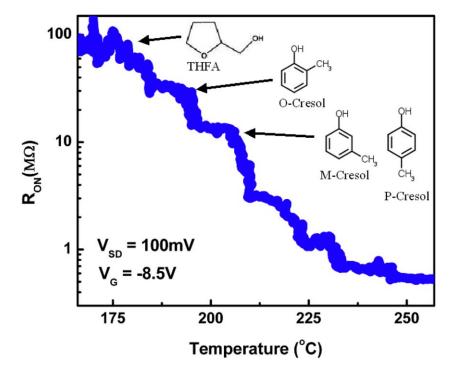

The observed decrease in ON-state resistance likely reflects desorption of multiple species of contaminants. To probe the dynamics of this process, the ON-state current of a device was monitored in situ as the temperature of the device was increased from room temperature to 300C, at a ramp rate of 0.5C/min (see Fig. 3). The bias voltage was 100mV, and the gate voltage was set at -8.5V, to assure that the device was in the ON-state at all times during the measurement. The ON-state resistance of the as-fabricated device was approximately  $100M\Omega$ , and it decreased to roughly  $500k\Omega$  after the procedure. Strikingly, we observe that the ON-state resistance decreases sharply at particular temperatures: 185C, 193C, 205C, 220C, 230C and 245C. We associate the first three temperature values with vaporization temperatures of component compounds of the Shipley 1813 photoresist and PMGI buffer layer. Specifically, tetrahydrofurfuryl alcohol (THFA), a solvent used in the production of PMGI resist, boils at 185C. The PMGI undergoes a glass transition at 190C, which may also contribute to this resistance decrease. The next two resistance drops (193C, 205C) correspond to the boiling points of different species of cresol ( $C_7H_8O$ ), a  $\pi$ -conjugated aromatic compound used in the production of novolac resin resists, including \$1813. The observation of such sharp decreases in ONstate resistance at the vaporization temperatures of known components of Shipley 1813 and PMGI demonstrates that residual contamination from the lithographic processing can be removed through baking at modest temperatures that have no ill effects on SWNT devices. The higher temperature jumps are attributed to either unidentified components of Shipley 1813 or PMGI, or annealing of the Cr/Au contacts.

In conclusion, we have developed a method for the reproducible production of large arrays of SWNT FET's. By enabling the use of photolithographic processing of SWNT circuits, parallel processing at the wafer scale is a reality. A buffer layer is used to prevent direct contact between the SWNT and the novolac-based photoresist, and a cleaning bake step at 300C is effective at removing

FIG. 2. FET conductance as function of gate voltage after successive bakes at 100, 200, and 300°C. The ON-state conductance grows with each bake, with a total increase of a factor of 50. The bias voltage is 100m°V.

FIG. 3. ON-state Resistance of a SWNT FET decreases as the bake temperature is ramped at a rate of 0.5C/min. Sharp decreases in resistance are observed at temperatures assigned to desorption of specific contaminants that are components of the S1813 and PMGI resists.

residual compounds that bind to the SWNT sidewall during processing. This enables the production of SWNT transistors with an average ON-state resistance identical to the best quality devices fabricated by electron beam lithography. We selected an optimum temperature for the cleaning bake by treating a single sample multiple times at successively higher temperatures, and measuring the device electrical properties after each cleaning step. In situ electrical measurements revealed sharp decreases in the ON-state resistance of a device during a temperature ramp, which we associate with the vaporization of known components of PMGI and Shipley S1813 photoresist. This type of process should allow the integration of carbon nanotube devices into standard CMOS architectures given recent advances in low temperature growth of SWNTs<sup>27</sup> and the fact that our post process annealing temperature is compatible with CMOS devices.

#### **ACKNOWLEDGMENT**

This work was supported by the JSTO DTRA and the Army Research Office Grant # W911NF-06-1-0462 and by NSF grant DMR-0805136. Support by NCMR and NSF/DIA Grant # IIS-07-15024 is also acknowledged (RAJ). The authors wish to thank the staff of Penn's Wolf Nanofabrication Facility.

```

<sup>1</sup> S. Iijima, Nature 354, 56 (1991).

<sup>2</sup> S. J. Tans, M. H. Devoret, R. J. A. Groeneveld, et al., Nature 394, 761 (1998).

<sup>3</sup> M. Radosavljevic, M. Freitag, K. V. Thadani, et al., Nano Letters 2, 761 (2002).

<sup>4</sup> J. Kong, N. R. Franklin, C. W. Zhou, et al., Science 287, 622 (2000).

<sup>5</sup>C. Staii, M. Chen, A. Gelperin, et al., Nano Letters 5, 1774 (2005).

<sup>6</sup>S. Ghosh, A. K. Sood, S. Ramaswamy, et al., Science 299, 1042 (2003).

<sup>7</sup>I. Brodie and J. Murray, The Physics of Micro/Nano-Fabrication (Plenum Press, New York, 1992).

<sup>8</sup> A. Tselev, K. Hatton, M. S. Fuhrer, et al., Nanotechnology 15, 1475 (2004).

<sup>9</sup> P. Qi, O. Vermesh, M. Grecu, et al., Nano Letters 3, 347 (2003).

<sup>10</sup> N. R. Franklin, Y. M. Li, R. J. Chen, et al., Applied Physics Letters 79, 4571 (2001).

<sup>11</sup> F. Leonard and J. Tersoff, Physical Review Letters 84, 4693 (2000).

<sup>12</sup> A. A. Talin, G. F. Cardinale, T. I. Wallow, et al., Journal of Vacuum Science & Technology B 22, 781 (2004).

<sup>13</sup> J. Q. Lu, N. Moll, Q. Fu, et al., Chemical Materials 17, 2237 (2005).

<sup>14</sup> A. M. Cassell, J. A. Raymakers, J. Kong, et al., Journal of Physical Chemistry B 103, 6484 (1999).

15 www.microchem.com

<sup>16</sup> A. Javey, Q. Wang, W. Kim, et al., IEEE Electron Device Meeting (IEDM) Technical Digest, 31.2.1 (2003).

<sup>17</sup> J. Appenzeller, J. Knoch, V. Derycke, et al., Physical Review Letters 89 (2002).

<sup>18</sup> A. T. Johnson, C. Staii, M. Chen, et al., Semiconductor Science and Technology 21, S17 (2006).

<sup>19</sup> A. Javey, J. Guo, Q. Wang, et al., Nature 424, 654 (2003).

<sup>20</sup> S. Heinze, J. Tersoff, R. Martel, et al., Physical Review Letters 89 (2002).

<sup>21</sup> R. R. Johnson, A. T. C. Johnson, and M. L. Klein, Nano Letters 8, 69 (2008).

<sup>22</sup>M. P. Waller, A. Robertazzi, J. A. Platts, et al., Journal of Computational Chemistry 4, 491 (2005).

<sup>23</sup> F. Tournus and J. C. Charlier, Physical Review B 71, 165421 (2005).

<sup>24</sup> F. Tournus, S. Latil, M. I. Heggie, et al., Physical Review B 72, 075431 (2005).

<sup>25</sup> S. Datta, Electronic transport in mesoscopic systems (Cambridge University Press, New York, 1995).

<sup>26</sup> T. D. Yuzvinsky, W. Mickelson, S. Aloni, et al., Applied Physics Letters 87, 083103 (2005).

<sup>27</sup> M. Cantoro, S. Hofmann, S. Pisana, et al., Nano Letters 6, 1107 (2006).

```