### University of Pennsylvania ScholarlyCommons

Departmental Papers (MSE)

Department of Materials Science & Engineering

6-4-2010

## Extremely Low Drift of Resistance and Threshold Voltage in Amorphous Phase Change Nanowire Devices

Mukut Mitra University of Pennsylvania

Yeonwoong Jung University of Pennsylvania, yjung@seas.upenn.edu

Daniel S. Gianola University of Pennsylvania, gianola@seas.upenn.edu

Ritesh Agarwal University of Pennsylvania, riteshag@seas.upenn.edu

Follow this and additional works at: http://repository.upenn.edu/mse\_papers Part of the <u>Materials Science and Engineering Commons</u>

#### **Recommended** Citation

Mitra, M., Jung, Y., Gianola, D. S., & Agarwal, R. (2010). Extremely Low Drift of Resistance and Threshold Voltage in Amorphous Phase Change Nanowire Devices. Retrieved from http://repository.upenn.edu/mse\_papers/181

Suggested Citation:

Mitra, M., Y. Jung, D.S. Gianola, R. Agarwal. (2010). "Extremely low drift of resistance and threshold voltage in amorphous phase change nanowire devices." *Applied Physics Letters*. Vol. 96, 222111.

© 2010 American Institute of Physics. This article may be downloaded for personal use only. Any other use requires prior permission of the author and the American Institute of Physics.

The following article appeared in Applied Physics Letters and may be found at http://dx.doi.org/10.1063/1.3447941.

## Extremely Low Drift of Resistance and Threshold Voltage in Amorphous Phase Change Nanowire Devices

#### Abstract

Time-dependent drift of resistance and threshold voltage in phase change memory (PCM) devices is of concern as it leads to data loss. Electrical drift in amorphous chalcogenides has been argued to be either due to electronic or stress relaxation mechanisms. Here we show that drift in amorphized Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> nanowires with exposed surfaces is extremely low in comparison to thin-film devices. However, drift in stressed nanowires embedded under dielectric films is comparable to thin-films. Our results shows that drift in PCM is due to stress relaxation and will help in understanding and controlling drift in PCM devices.

#### Disciplines

Engineering | Materials Science and Engineering

#### Comments

Suggested Citation: Mitra, M., Y. Jung, D.S. Gianola, R. Agarwal. (2010). "Extremely low drift of resistance and threshold voltage in amorphous phase change nanowire devices." *Applied Physics Letters*. Vol. 96, 222111.

© 2010 American Institute of Physics. This article may be downloaded for personal use only. Any other use requires prior permission of the author and the American Institute of Physics.

The following article appeared in *Applied Physics Letters* and may be found at http://dx.doi.org/10.1063/ 1.3447941.

# Extremely low drift of resistance and threshold voltage in amorphous phase change nanowire devices

Mukut Mitra, Yeonwoong Jung, Daniel S. Gianola, and Ritesh Agarwal<sup>a)</sup> Department of Materials Science and Engineering, University of Pennsylvania, 3231 Walnut Street, Philadelphia, Pennsylvania 19104-6272, USA

(Received 15 April 2010; accepted 15 May 2010; published online 4 June 2010)

Time-dependent drift of resistance and threshold voltage in phase change memory (PCM) devices is of concern as it leads to data loss. Electrical drift in amorphous chalcogenides has been argued to be either due to electronic or stress relaxation mechanisms. Here we show that drift in amorphized  $Ge_2Sb_2Te_5$  nanowires with exposed surfaces is extremely low in comparison to thin-film devices. However, drift in stressed nanowires embedded under dielectric films is comparable to thin-films. Our results shows that drift in PCM is due to stress relaxation and will help in understanding and controlling drift in PCM devices. © 2010 American Institute of Physics. [doi:10.1063/1.3447941]

Electric-field induced structural phase transformations in chalcogenides have attracted significant interest due to their potential use in nonvolatile phase change memory (PCM) devices.<sup>1</sup> Chalcogenides (e.g., Ge–Sb–Te alloys) are particularly important for PCM owing to their fast and reversible crystalline to amorphous phase change properties via Joule heating to produce electrically distinct states. However, various challenges including understanding their structural, electronic, thermal, and mechanical properties especially in the amorphous state, the effect of field on electrical switching, and device scalability needs to be addressed before PCM can become a viable alternative to flash technology.

Chalcogenide glasses are affected by relaxation processes that occur on a large distribution of timescales resulting in time-dependent electrical,<sup>2–5</sup> optical,<sup>6</sup> mechanical,<sup>7</sup> and thermal<sup>8</sup> behavior. For PCM device operation, the amorphous state resistance and the field strength at which it switches to a higher conducting state (threshold voltage,  $V_{th}$ ) are fundamental parameters that determine device reliability. Any phenomenon that affects these critical parameters leading to temporal drift in PCM is an important issue that needs to be investigated<sup>2-4</sup> as they lead to changes in the measurable device characteristics used for recording and reading the information. This issue becomes particularly important for multilevel memory devices, as drifts in resistance would lead to states being overwritten causing serious errors.9,10 Therefore, it becomes important to understand the physical origin of phenomena that cause drift in material properties to eventually minimize such effects.

The drift of amorphous phase resistance in PCM has been described by a power law,

$$R(t) = R(t_0)(t/t_0)^{\alpha},$$

(1)

where  $\alpha$  lies in the range of 0.03 to 0.1 depending on the device type and initial amorphous state resistance.<sup>2–4</sup> However, the drift in V<sub>th</sub> has been fitted either to a power law,<sup>2,3</sup> or a logarithmic dependence,<sup>4</sup>

$$\frac{\Delta V_{\rm th}(t)}{V_{\rm th}(t_0)} = \frac{V_{\rm th}(t) - V_{\rm th}(t_0)}{V_{\rm th}(t_0)} = \nu \ln \frac{t}{t_0},\tag{2}$$

where v has been reported in the range of 0.02–0.04.<sup>4</sup>

The fundamental understanding and the origin of amorphous phase drift in PCM are being actively debated and have been explained by a variety of effects including stress relaxation,<sup>2,4</sup> relaxation processes which anneal the electronic defects,<sup>2,3</sup> and the formation of valence alternation pairs (VAP),<sup>11–13</sup> all of which can increase the mobility gap causing an increase in material's resistivity and V<sub>th</sub>. Within the electronic structural relaxation model, the annealing of traps occurs due to atomic motions that results in an increase in the intertrap distance. The stress relaxation model is based on the built-in internal hydrostatic pressure in the embedded amorphous dome due to the melt-quench process owing to the large difference between the densities of the crystalline and amorphous phase (5%-7%). The slow relaxation of internal stress (volume dilation), consistent with the stress relaxation data,<sup>14</sup> is due to atomic motions within the embedded amorphous dome which increases the Fermi level from the valence band edge causing time-dependent increase in resistance and V<sub>th</sub>.

One way to distinguish between these proposed mechanisms is to design experiments on unembedded nanoscale systems in which the stress upon amorphization can relax efficiently. The stress relaxation efficiency can also be engineered by changing the surface-to-volume ratio or by embedding the nanodevice without altering the material's electronic properties. If the stress relaxation mechanism dominates the drift dynamics, then any change in the system's ability for efficient stress relaxation should significantly influence its drift characteristics.

Phase change nanowires (NWs) are important materials as they can be reliably connected into devices, their sizes can be controlled down to 10 nm to tune the surface-to-volume ratio, and unlike thin films, NW devices can be configured with their surfaces exposed or completely embedded. Experiments on phase change NWs have shown efficient electrical switching due to material confinement, scalability,<sup>15</sup> multibit operation,<sup>16</sup> and evidence of strong heterogeneous nucleation from its surfaces.<sup>17</sup> Here, we utilize the unique geometry of NWs to understand the mechanism of resistance and V<sub>th</sub> drift in PCM. It is shown that NW devices have extremely small values of drift coefficients in comparison to thin films. By systematically varying the stress relaxation parameters such as the surface-to-volume ratio of the NWs and comparing unembedded and embedded devices, it is demonstrated that

0003-6951/2010/96(22)/222111/3/\$30.00

#### 96, 222111-1

#### © 2010 American Institute of Physics

Downloaded 13 Oct 2010 to 130.91.117.41. Redistribution subject to AIP license or copyright; see http://apl.aip.org/about/rights\_and\_permissions

<sup>&</sup>lt;sup>a)</sup>Electronic mail: riteshag@seas.upenn.edu.

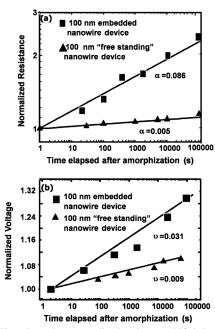

FIG. 1. (a) Time-dependent normalized resistance drift behavior of a 100 nm thick unembedded  $Ge_2Sb_2Te_5$  NW device (triangles), and the same device embedded under a 300 nm thick  $SiO_2$  film (squares), amorphized to a resistance of 2.1 M $\Omega$ . The solid lines are fit to Eq. (1) and the corresponding drift coefficients are given. (b) Drift of normalized V<sub>th</sub> for an unembedded (triangles) and the embedded NW device (squares). Solid lines are fit to Eq. (2). The embedded device shows higher drift coefficients in comparison to unembedded devices.

the release of built-in stress upon amorphization is primarily responsible for drift in PCM.

Phase change  $Ge_2Sb_2Te_5$  NWs were synthesized using the bottom-up approach of catalyst mediated vapor–liquid– solid process.<sup>15</sup> NW devices were fabricated with Pt electrodes<sup>15</sup> and their resistances were measured at 0.2V (dc). The NW devices were amorphized by 200 ns electrical pulses to resistance values of 1–4 M $\Omega$ , and then were allowed to relax over five decades of time during which the resistance was measured at different intervals. For V<sub>th</sub> drift measurements, dc *I-V* sweeps were measured beyond the V<sub>th</sub> and the devices were amorphized back to the original resistance for time-dependent measurements.

The time evolution of amorphous state resistance (normalized at t=1 s, first measurement) of a 100 nm thick NW device from the initial value of 2.1 M $\Omega$  [Fig. 1(a)] clearly shows that the resistance drift is very small with the resistance increasing to just 2.3 M $\Omega$  over five decades in time. The data are fit to a power law [Eq. (1)] with the power exponent,  $\alpha$  of 0.005, which is very small in comparison to thin-film devices where  $\alpha$  typically ranges from 0.03–0.1.<sup>4</sup> The corresponding data for drift in V<sub>th</sub> (normalized at 2 s, first measurement) can be fit to Eq. (2) [Fig. 1(b)], which also reveals a lower drift exponent (v=0.009) in comparison to typical values ranging from 0.01–0.04 in thin films.<sup>4</sup> These experiments demonstrate that drift coefficients are lower in NW devices in comparison to thin-films.

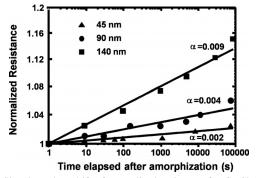

In order to study the correlation of drift coefficients with NW size, we measured the resistance drift on three different NW thicknesses, 140, 90, and 45 nm, all amorphized to resistance values that were  $\sim 100$  times more than their crystalline state resistance. The NW devices show a systematic size-dependent drift of amorphous state resistance (Fig. 2); the drift coefficients increase with increasing NW thickness.

FIG. 2. Size-dependent drift of normalized resistance for  $Ge_2Sb_2Te_5$  NW devices. Smaller diameter devices show less drift compared to larger diameter devices. Solid lines are fit to Eq. (1).

The thinnest NW (45 nm) with the highest surface-to-volume ratio shows the lowest drift ( $\alpha$ =0.002), while the thickest NW device (140 nm) with the lowest surface-to-volume ratio shows higher drift coefficient ( $\alpha$ =0.009) but much smaller than thin-film devices The V<sub>th</sub> drift coefficients did not reveal any clear size-dependence, mostly because the V<sub>th</sub> changes typically from ~1.5 V (t=2 s) to ~1.7 V (t=10<sup>5</sup> s) for NW devices, a small increase to reliably extract their size-dependence.

The above described data suggests that the unique geometry of NW devices with exposed surfaces may be responsible for the observed low but size-dependent drift coefficients. In order to explore the effect of exposed surfaces on drift in NWs, we performed measurements on the same NW devices by depositing thick ( $\sim$ 300 nm) dielectric films such as  $SiO_2$  or  $Si_3N_4$  on them. The devices were imaged with scanning electron microscopy (SEM) to ensure that they were completely embedded. The same 100 nm NW device as discussed in Fig. 1 but embedded under SiO<sub>2</sub> film was amorphized again to a resistance value of 2.1 M $\Omega$  and its resistance drift was measured. The NW device now showed a much higher resistance ( $\alpha$ =0.086, compared to 0.005 for unembedded), and  $V_{th}$  drift coefficients (v=0.031, compared to 0.009 for unembedded), which are similar to values reported for embedded thin-film PCM devices (Fig. 1). Similar values of increase in drift coefficients for NWs embedded under  $Si_3N_4$  film in comparison to unembedded devices were obtained (data not shown). These data suggest that the drift characteristics of the devices can be engineered by altering their surface-to-volume ratio and exposing/embedding the surfaces.

Our measurements on NW devices clearly demonstrate the difference in drift behavior as a function of surface-tovolume ratio and exposed surfaces. These observations suggest that the efficient relaxation of the built-in stress upon amorphization is primarily responsible for drift in PCM devices in comparison to annealing of electronic defects or VAP generation mechanisms. In a conventional thin-film PCM device, a polycrystalline film is sandwiched between two electrodes; upon amorphization, a completely embedded amorphous dome results, which is compressed under large stresses from the surrounding materials. In the course of time, the metastable amorphous region relaxes with a large distribution of timescales, which has been mapped with stress relaxation experiments,<sup>14</sup> resulting in a time-dependent increase in resistance and V<sub>th</sub> due to volume dilation. These relaxations have been extensively studied in glasses and have

Downloaded 13 Oct 2010 to 130.91.117.41. Redistribution subject to AIP license or copyright; see http://apl.aip.org/about/rights\_and\_permissions

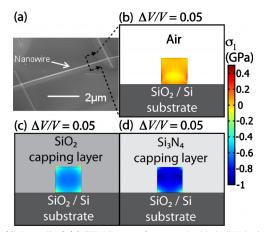

FIG. 3. (Color online) (a) SEM image of an unembedded NW device. [(b)–(d)] Finite element analysis of the elastic first principal stresses that develop in a Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> NW cross-section (100×100 nm<sup>2</sup>) upon amorphization. A volume change of  $\Delta V/V = tr(\varepsilon_{ij}) = 0.05$  ( $\varepsilon_{ij}$ , strain tensor), representing the decrease in density upon amorphization, Young's modulus of 35 GPa and Poisson's ratio of 0.3 were used for Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (Ref. 22). An unembedded NW (b) develops small stresses due to adhesion at the substrate interface but large compressive stresses develop in devices confined with SiO<sub>2</sub> (c) and Si<sub>3</sub>N<sub>4</sub> (d). These stresses are likely accommodated by relaxation mechanisms in the amorphous material, which influences the drift behavior (Ref. 14). Note that stresses in the substrate and capping layers are present but have been omitted for clarity.

been attributed to atomic relaxations, where unsaturated and distorted bonds in the metastable state relax to more stable states leading to time-dependent mechanical and electrical properties.

Unlike thin-film devices, NW devices do not have a completely embedded amorphized dome, which will enable them to relax their stress rapidly from the large available surface (Fig. 3), leading to very different drift behavior as observed. Typically, phase change NWs have a  $\sim 1-2$  nm coaxial surface oxide shell which can easily expand when the NW device is locally amorphized thereby releasing the stress. Smaller diameter NWs have large surface-to-volume ratio and can relax their stress more easily. It is known that NWs can be epitaxially grown on highly mismatched substrates and their heterostructures can be created to withstand large strains due to the free surfaces allowing for lateral strain relaxation.<sup>18,19</sup> Theoretical studies on nanostructures have also revealed that strain-relaxation become more efficient with increasing surface-to-volume ratio.<sup>20</sup> For NWs buried under dielectric-films, the situation becomes similar to convention thin-film PCM devices and the amorphous region cannot relax the built-in pressure and hence relaxes slowly on multiple timescales leading to higher drift. This is in agreement with crystallization-induced stress measurements in Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> thin-films where the stress was reported to be much higher for capped films.<sup>21</sup> It is unlikely that the deposition of the dielectric-film significantly alters the electronic properties of the NWs as the presence of the thin coaxial oxide layer minimizes their direct interaction. In addition, the drift properties of the embedded NW devices do not appear to be dependent on the dielectric composition, although the drift dependence on the film thickness and stiffness would require further investigation.

We have estimated the elastic stresses associated with the amorphization of the NW geometry for both the embedded and unembedded devices using finite element analysis to provide insight on the relationship between drift and struc-

tural confinement. Plane strain two-dimensional calculations were performed on a Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> NW cross-section (100  $\times 100 \text{ nm}^2$ ) on a SiO<sub>2</sub> substrate, where the bottom surface of the NW was constrained while the other surfaces were modeled as free [Fig. 3(b)]. The first principal stress  $\sigma_1$  for the unembedded NW [Fig. 3(b)], reveals that a very small but finite stress develops due to the constraint from the substrate. In contrast, large compressive stresses develop when  $SiO_2$ and  $Si_3N_4$  capping layers are applied [Figs. 3(c) and 3(d)] due to confinement effects upon amorphization, which are  $\sim 20$  times more than the unembedded case. The low and size-dependent drift coefficients are consistent with the notion of the high surface-to-volume ratio of the NW serving to effectively accommodate the stresses, although a detailed understanding of the atomic relaxation mechanisms in Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> NWs requires future investigation.

In conclusion, we have shown that stress relaxation mechanisms are primarily responsible for the observed drift behavior in PCM devices by using unembedded NWs as a model system. The NWs have extremely low values of drift coefficients due to efficient stress relaxation from the exposed free surfaces in comparison to thin-film devices. These results help understand the effect of mechanical stresses on electrical properties of phase change materials and will be useful for the development of improved device geometries that can minimize drift for multilevel memory applications.

This work was supported by ONR (Grant No. N000140910116), Materials Structures and Devices Center at MIT, NSF (Grant No. DMR-0706381), and Penn-MRSEC (Grant No. DMR05-20020).

- <sup>1</sup>S. Raoux, Annu. Rev. Mater. Res. **39**, 25 (2009).

- <sup>2</sup>A. Pirovano, A. L. Lacaita, F. Pellizzer, S. A. Kostylev, A. Benvenuti, and R. Bez, IEEE Trans. Electron Devices **51**, 714 (2004).

- <sup>3</sup>D. Ielmini, L. Lacaita, and D. Mantegazza, IEEE Trans. Electron Devices **54**, 308 (2007).

- <sup>4</sup>I. V. Karpov, M. Mitra, D. Kau, G. Spadini, Y. A. Kryukov, and V. G. Karpov, J. Appl. Phys. **102**, 124503 (2007).

- <sup>5</sup>R. T. Johnson and R. K. Quinn, J. Non-Cryst. Solids 28, 273 (1978).

- <sup>6</sup>V. G. Karpov and M. Grimsditch, Phys. Rev. B 48, 6941 (1993).

- <sup>7</sup>O. B. Tsiok, V. V. Brazhkin, A. G. Lyapin, and L. G. Khvostantsev, Phys. Rev. Lett. **80**, 999 (1998).

- <sup>8</sup>M. T. Loponen, R. C. Dynes, and V. Narayanamurti, Phys. Rev. B 25, 1161 (1982).

- <sup>9</sup>S. Braga, A. Cabrini, and G. Torelli, Appl. Phys. Lett. **94**, 092112 (2009).

- <sup>10</sup>D. H. Kang, J.-H. Lee, J. H. Kong, D. Ha, J. Yu, C.Y. Um, J. H. Park, F. Yeung, J. H. Kim, W. I. Park, Y. J. Jeon, M. K. Lee, Y. J. Song, J. H. Oh, G. T. Jeong, and H. S. Jeong, Dig. Tech. Pap. Symp. VLSI Technol. **2008**, 98.

- <sup>11</sup>R. A. Street and N. F. Mott, Phys. Rev. Lett. 35, 1293 (1975).

- <sup>12</sup>M. Kastner, D. Adler, and H. Fritzsche, Phys. Rev. Lett. **37**, 1504 (1976).

<sup>13</sup>M. Kastner and H. Fritzsche, Philos. Mag. B **37**, 199 (1978).

- <sup>14</sup>J. Kalb, F. Spaepen, T. P. L. Pedersen, and M. Wuttig, J. Appl. Phys. 94, 4908 (2003).

- <sup>15</sup>S. H. Lee, Y. Jung, and R. Agarwal, Nat. Nanotechnol. 2, 626 (2007).

- <sup>16</sup>Y. Jung, S. H. Lee, A. T. Jennings, and R. Agarwal, Nano Lett. 8, 2056 (2008).

- <sup>17</sup>S. H. Lee, Y. Jung, and R. Agarwal, Nano Lett. 8, 3303 (2008).

- <sup>18</sup>P. Caroff, J. B. Wagner, K. A. Dick, H. A. Nilsson, M. Jeppsson, K. Deppert, L. Samuelson, L. R. Wallenberg, and L. Wernersson, Small 4, 878 (2008).

- <sup>19</sup>T. Mårtensson, J. B. Wagner, E. Hilner, A. Mikkelson, C. Thelander, J. Stangl, B. J. Ohlsson, A. Gustafsson, E. Lundgren, L. Samuelson, and W. Seifert, Adv. Mater. **19**, 1801 (2007).

- <sup>20</sup>H. S. Park and P. A. Klein, Phys. Rev. B **75**, 085408 (2007).

- <sup>21</sup>Q. Guo, M. Li, Y. Li, L. Shi, T. C. Chong, J. A. Kalb, and C. V. Thompson, Appl. Phys. Lett. **93**, 221907 (2008).

- <sup>22</sup>T. P. Leervard Pederson, J. Kalb, W. K. Njoroge, D. Wamwangi, M. Wuttig, and F. Spaepen, Appl. Phys. Lett. **79**, 3597 (2001).

Downloaded 13 Oct 2010 to 130.91.117.41. Redistribution subject to AIP license or copyright; see http://apl.aip.org/about/rights\_and\_permissions