## Hopping Conduction and Metallic behavior in 2D Silicon Surface States induced by an Ionic Liquid

### A THESIS

# SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA

$\mathbf{B}\mathbf{Y}$

JJ Nelson

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor of Philosophy

A. M. Goldman

June, 2015

© JJ Nelson 2015 ALL RIGHTS RESERVED

# Acknowledgements

I would like to acknowledge and thank my family for all the assistance they provided over the past several years. Their help and support outside of the lab was essential to the completion of this work. This work was possible due to the facilities and funding provided by the University and Allen Goldman. Results from blue sky research can be said to follow a diffusive progression with time. There were several important side projects over the years that made the engineering of the silicon project possible. The support of Allen allowed me to pursue the research.

There have been many other people who have helped me over the years. Steve Snyder was very influential to my early lab work and collaborated with me on several side projects throughout the years. Tom Dunn was a helpful theorist and I would like to thank him for useful discussions over lunches and afternoon pints of beer. Our trips to the pub and scribbling equations on napkins had a huge impact on my life. It was during these trips that I met Mathew Ryden who introduced me to Barley Johns Brewpub.

I would like to thank the Barley John's crew for being an adopted family during my time here. Barley John's has been an important place to go relax, play games, and talk physics over a fire. In particular, I would like to thank Hultman Mckenna and Reed Eichele for their friendship and company at Barley John's. The pub is also the location that the wife and I had our first date, and shared many more. Thank you Mat for introducing me to Barley and for many games of cribbage. Lastly I would like to thank Adam Hupach, Scott Thaller, and Terence Bretz-Sullivan for all the relaxing trips out after some of the stressful days at work.

# Dedication

To the wife: For patiently awaiting the completion of this PhD.

#### Abstract

Ionic liquids (ILs) are essentially molten salts with a melting point below room temperature. When used as the gate dielectric of a transistor, carrier densities on the order of  $10^{15}$  cm<sup>-2</sup> can be achieved. These record high carrier densities are significantly higher than the maximum carrier density achievable with oxide dielectrics. The physical mechanism for inducing carriers to such a high carrier density is not well understood. Some groups have reported that the induced carriers are a result of electrostatic and electrochemical processes. Other groups have suggested that carriers induced with an IL may be entirely due to electrochemical reactions.

Here we report on IL gated Si at carrier densities from  $10^{11}$  cm<sup>-2</sup> to  $10^{13}$  cm<sup>-2</sup>. The experiment was designed to preferentially induce electrostatic carriers over electrochemical reactions. At low carrier densities, sample surface conductivity follows nearest neighbor hopping conduction. This form of conduction has also been observed in experiments where surface conductivity was induced by implanting Na<sup>+</sup> near the oxide surface interface.

A surprising result of this work was that in some samples a 2D metallic state could be created on the surface of Si. The transition to metallic behavior occurred just below  $10^{13}$  cm<sup>-2</sup>. High quality Si transistors with oxide dielectric materials observe critical carrier densities around  $10^{11}$  cm<sup>-2</sup>. The critical carrier density observed in IL gated Si is the highest density reported to date.

At carrier densities higher than  $10^{13}$  cm<sup>-2</sup> it was observed that the sample conductivity decreased with increasing carrier density. The behavior was unexpected and not fully understood. Both metallic and non metallic samples show a similar reduction in conductivity that is not thought to be due to sample degradation by the IL. The reduction in the sample conductivity at high carrier densities is thought to be due to surface roughness scattering. Similar behavior has been observed in other IL gated experiments on different materials.

# Contents

| Α             | Acknowledgements         |         |                                                        |    |  |  |

|---------------|--------------------------|---------|--------------------------------------------------------|----|--|--|

| D             | Dedication               |         |                                                        |    |  |  |

| A             | Abstract                 |         |                                                        |    |  |  |

| $\mathbf{Li}$ | ist of                   | f Figur | es                                                     | ix |  |  |

| 1             | 1 Introduction           |         |                                                        |    |  |  |

| 2             | Techniques and Materials |         |                                                        |    |  |  |

|               | 2.1                      | Intro   | production                                             |    |  |  |

|               | 2.2                      | Electi  | tric Double Layer Transistors                          |    |  |  |

|               |                          | 2.2.1   | High Carrier Density                                   | 9  |  |  |

|               |                          | 2.2.2   | Electrostatic or Electrochemical Changes               | 12 |  |  |

|               |                          | 2.2.3   | Calculating the Carrier Density                        | 14 |  |  |

|               | 2.3                      | Cryog   | Cryogenic Resistance Measurements with an Ionic Liquid |    |  |  |

|               |                          | 2.3.1   | Measurement Cryostat and Charging Procedure            | 15 |  |  |

|               |                          | 2.3.2   | Sheet Resistance Calculation                           | 16 |  |  |

|               |                          | 2.3.3   | Determination of the Hall Resistance                   | 18 |  |  |

|               | 2.4                      | Samp    | le Design and Cleanroom process                        | 19 |  |  |

|                          |     | 2.4.1 Silicon fabrication                            | 19 |  |

|--------------------------|-----|------------------------------------------------------|----|--|

|                          |     | 2.4.2 Sample design                                  | 21 |  |

|                          | 2.5 | Summary                                              | 22 |  |

| 3                        | 2D  | Silicon Surface State and Hopping Conduction         | 32 |  |

|                          | 3.1 | Introduction                                         | 32 |  |

|                          | 3.2 | Nearest Neighbor Hopping Theory                      | 35 |  |

|                          |     | 3.2.1 2D Surface State                               | 35 |  |

|                          |     | 3.2.2 Mechanism of Conduction                        | 36 |  |

|                          | 3.3 | Ionic Liquid Surface State in Silicon                | 36 |  |

|                          | 3.4 | Low Carrier Density and High Resistance Measurements | 40 |  |

|                          | 3.5 | Hopping Conduction Analysis                          | 45 |  |

|                          | 3.6 | Summary                                              | 48 |  |

| 4 Silicon Metallic State |     |                                                      |    |  |

|                          | 4.1 | Introduction                                         | 51 |  |

|                          | 4.2 | Metal Insulator Transition                           | 53 |  |

|                          | 4.3 | High Critical Carrier Density                        | 56 |  |

|                          | 4.4 | Critical Carrier Density and Sample Peak Mobility    | 60 |  |

|                          | 4.5 | Summary                                              | 64 |  |

| 5                        | Mo  | bility Peak                                          | 66 |  |

|                          | 5.1 | Introduction                                         | 66 |  |

|                          | 5.2 | Non-Metallic Samples                                 | 67 |  |

|                          | 5.3 | Mobility Peak                                        | 72 |  |

|                          | 5.4 | Repeatability                                        | 74 |  |

|                          | 5.5 | Reentrant Insulator Theory                           | 76 |  |

|                          | 5.6 | Summary                                              | 80 |  |

| 6 | 6 Conclusion |             |  |  | 81   |        |

|---|--------------|-------------|--|--|------|--------|

|   | 6.1          | Future Work |  |  | <br> | <br>83 |

| R | efere        | nces        |  |  |      | 87     |

# List of Figures

| 2.1 | Ionic Liquid Transistor                                                              | 24 |

|-----|--------------------------------------------------------------------------------------|----|

| 2.2 | Current as a function of time after increasing the gate voltage at $230{\rm K}$ .    | 25 |

| 2.3 | Integrated carrier density and Hall carrier density as a function of gate            |    |

|     | voltage                                                                              | 26 |

| 2.4 | Hall Resistance vs Magnetic Field at 2K                                              | 27 |

| 2.5 | Hall effect measurement of the bulk Si wafer                                         | 28 |

| 2.6 | Bulk Resistance vs Temperature for B Doped Si                                        | 29 |

| 2.7 | Cartoon of Ionic Liquid gated Silicon                                                | 30 |

| 2.8 | Microscope photograph of a second generation device                                  | 31 |

| 3.1 | Low Carrier Density Model                                                            | 34 |

| 3.2 | Bulk and Silicon Surface State Resistance                                            | 37 |

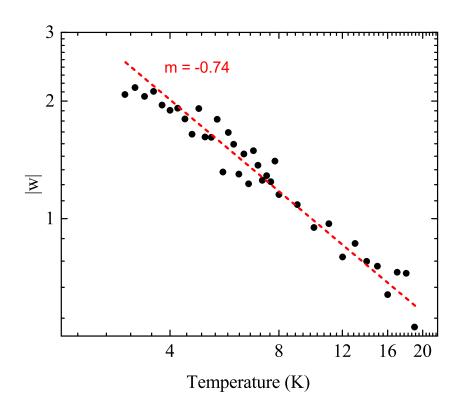

| 3.3 | Nearest Neighbor Hopping Zabrodskii plot                                             | 39 |

| 3.4 | Electrical schematic of the IL liquid measurement at high resistance $\ . \ .$       | 41 |

| 3.5 | Conductance at the Onset of Surface Conduction                                       | 42 |

| 3.6 | High Resistance Surface State at Low Carrier Densities                               | 44 |

| 3.7 | Arrhenius Plots of Resistance at Different Carrier Densities                         | 46 |

| 3.8 | $\epsilon_3$ at Low Carrier Densities for IL Gated Si and Na^+ implanted Si $~$      | 47 |

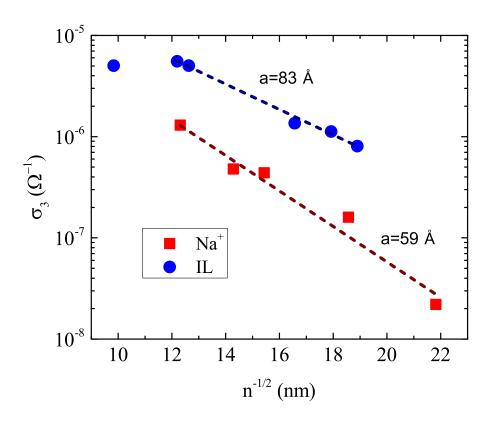

| 3.9 | $\sigma_3$ at low carrier densities for IL gated Si and Na <sup>+</sup> implanted Si | 49 |

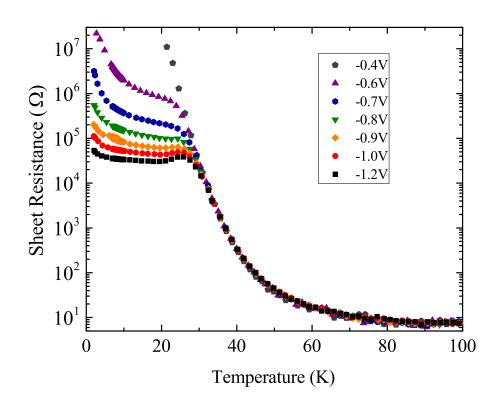

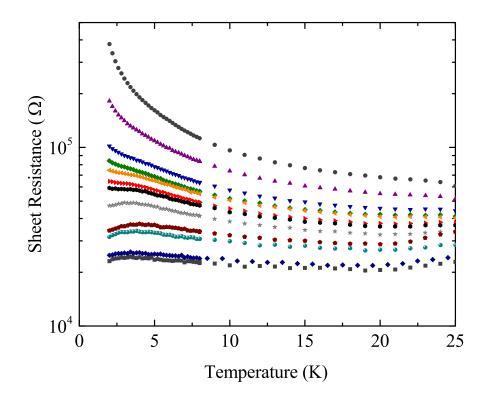

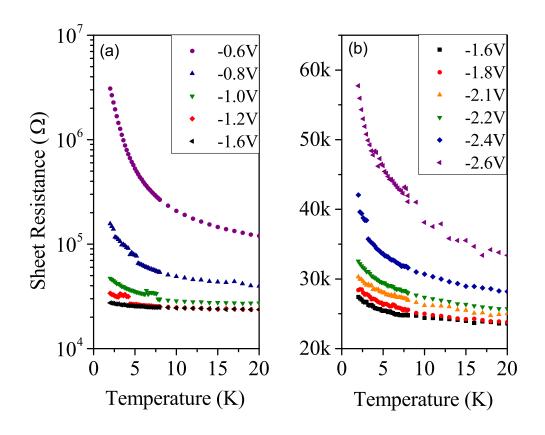

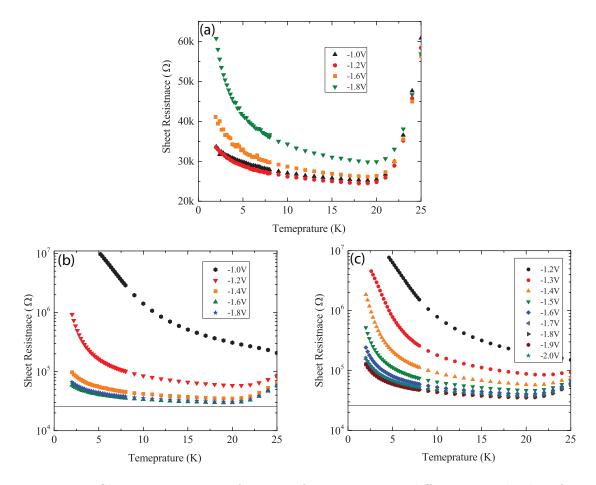

| 4.1 | Resistance vs Temperature beyond Nearest Neighbor Hopping                            | 52 |

| 4.2 | Zabrodskii Plot at Carrier Concentrations Beyond Nearest Neighbor Hop-                             |    |

|-----|----------------------------------------------------------------------------------------------------|----|

|     | ping                                                                                               | 54 |

| 4.3 | Metal Insulator Transition in IL Gated Si                                                          | 57 |

| 4.4 | Discharging the Metallic State, Returning to Insulating Behavior                                   | 59 |

| 4.5 | Metallic State Measured Using <sup>3</sup> He Insert $\ldots$                                      | 61 |

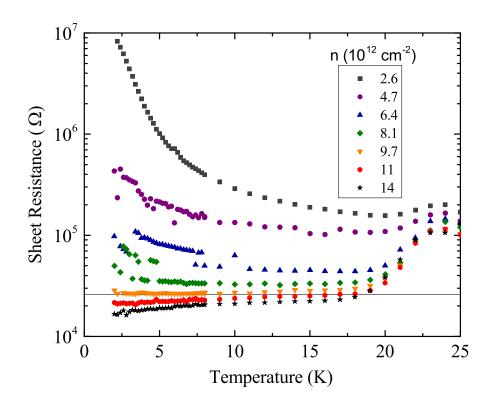

| 5.1 | Nonmetallic Resistance at <sup>3</sup> He Temperatures $\ldots \ldots \ldots \ldots \ldots \ldots$ | 69 |

| 5.2 | Resistance vs Temperature at Voltages where the Conductivity Decreases                             |    |

|     | with Increasing Gate Voltage                                                                       | 71 |

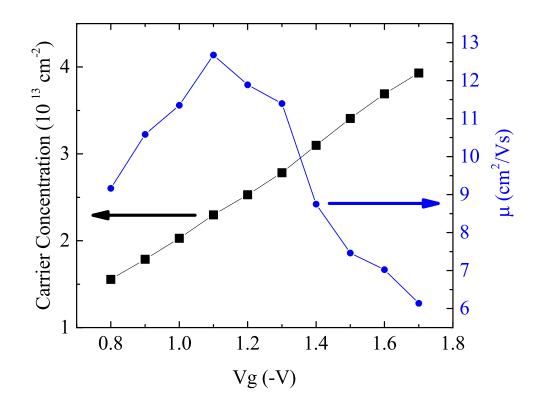

| 5.3 | Mobility and Carrier Density as a Function of Gate Voltage Showing a                               |    |

|     | Peak in Mobility                                                                                   | 73 |

| 5.4 | Reproducibility of the Mobility Peak                                                               | 77 |

| 6.1 | Method to measure the Seebeck and Nernst Coefficient of Metallic IL                                |    |

|     | Gated Si                                                                                           | 85 |

# Chapter 1

# Introduction

Superconductivity, which was discovered in 1911 by Kamerlingh Onnes, is a quantum state where electric properties of a material are quantized into units of two electrons.[1, 2] Superconducting materials have zero resistance and some are perfect diamagnets. In 1957 a theory by Bardeen, Cooper, and Schrieffer (BCS) was the first microscopic theory to describe existing superconducting properties.[3] In their theory, two electrons can overcome repulsive Coulomb interactions by a mutual attraction involving vibrations of positively charged nuclei in the atomic lattice, known as phonons. The energy scale for the electron phonon interaction made it unlikely that superconductors of this type could exist above 40 K. Thus the advantages one would gain from the superconducting properties of a material are hindered by the requirement of temperatures accessible only though the use of liquefied helium or helium based refrigerators.

The field was revolutionized in 1986 by the discovery of superconductors with transition temperatures above the boiling point of liquid nitrogen.[4] In these materials, superconducting planes composed of Cu and O intercalated with Group II, Group III, and f-block elements. In addition to doping with oxygen, the interstitial elements can alter the bonds and carrier densities of the CuO planes leading to superconductivity. Unlike BCS superconductors, the microscopic mechanism leading to the pairing of electrons could not be explained by the phonon mediated model. Since then, several other families of superconductors have also been discovered that fall outside of BCS theory. A special issue on superconductivity in preparation had identified 32 classes of superconducting materials where at least a third are thought to be non-BCS.[5] In addition to new forms of superconductivity, electron-electron interactions have given rise to other unpredicted behavior like the possibility of 2D metallic behavior at T = 0 and heavy fermion materials where the electron effective mass can be orders of magnitude above the free electron rest mass.[6] Heavy fermion materials have also been shown to be superconducting.[7] These are examples of the many unsolved problems that exist regarding electron interactions in solids.

The motivation for this thesis stems from the discovery of superconductivity in Group IV materials. Coined covalent superconductors, the discovery of superconductivity in heavily boron doped diamond attracted significant interest to the subject. It was found that when single crystals of carbon with the diamond crystal structure were doped with boron at concentrations of  $10^{21}$  cm<sup>-3</sup>, the materials were superconductors with a transition temperature,  $T_c$ , near 4 K.[8] It was later reported that crystals could be produced with  $T_c = 8$  K[9]. It is an open question as to whether or not superconductivity of Group IV materials can be described by the BCS theory. The two additional theories that have been proposed involve electron pairing by spin flip interactions and interactions associated with boron impurity bands.[10]

Shortly after the discovery of superconductivity in diamond, it was found that other Group IV elements were superconductors by doping with Group III acceptors at similar boron concentrations as that of diamond. A brief summary of the experiments shows that single crystal silicon could also be made into a superconductor with  $T_c = 350$ mK at sufficient boron concentrations[11]. The solubility limit of B in Si is lower than  $10^{21}$  cm<sup>-3</sup> so the crystals were created through gas immersion laser doping. The dopant depth was estimated to be within 100nm of the surface and it is thought that boron acceptors are substitutional and not interstitial. SiC crystals could be made into a superconductor with B or Al acceptors at the  $10^{21}$  cm<sup>-3</sup> level[12]. For the SiC films,  $T_c \sim 1$ K falls in between  $T_c$  for crystals of C and Si. Measurements of the specific heat indicate the existence of an energy gap and calculations based on the density of states agree with the gap being isotropic. While Si forms the diamond crystal structure, the equivalent structure for SiC is referred to as zincblende. In effect, SiC can be viewed at two inter-penetrating FCC crystals of Si and C as opposed to an FCC crystal with two atoms per site in the unit cell. The jump in the specific heat was small compared to the jump expected from BCS theory.

In an effort to constrain the theories for superconductivity in Group IV materials, we developed an experiment to electrostatically induce holes at carrier densities similar to the level required for superconductivity in Si and SiC with B. The experiment would require carrier densities beyond the limit of conventional solid dielectrics.[13] Recently, record high carrier densities have been realized though the use of an ionic conductor as a dielectric material in a transistor configuration.[14] The dielectric is a binary compound of charged organic molecules, which is liquid at room temperature, referred to as an Ionic Liquid (IL). Ionic liquid transistors are referred to as electric double layer transistors, as the ions in the dielectric will form electric double layers with both the sample and the gate electrode. The high carrier density achievable has been sufficient to observe superconductor-insulator transitions.[15, 16, 17] Metal-insulator transitions have also been observed when gating with an IL.[18, 19] A microscopic mechanism for the high carrier accumulation is currently being investigated.[20, 21] At high carrier densities the sample surface will be subject to large electric fields, which have been shown to cause reversible structural changes in some samples.[22]

Experimental details of the electric double layer transistor are covered in Chapter 2. A model for electrostatic carrier induction by an ionic liquid is discussed in Chapter 3. The purpose of the model is to understand the microscopic physics of carrier induction by an ionic liquid at low carrier densities. Once the low carrier density behavior is understood future experiments could extend the model to the record high carrier densities reported in IL gating experiments. Ionic liquids can induce carrier densities as high as  $10^{15}$  cm<sup>-2</sup> in surface layers only a few Å thick on the surface, suggesting that carrier densities of  $10^{21}$  cm<sup>-3</sup> required for superconductivity in diamond or silicon should be accessible.

A study of  $T_c$  as a function the volume carrier density,  $n_b$ , of boron dopants in Si observed that  $n_b d$  determined  $T_c$  by the phenomenological equation

$$\frac{T_c(n_b)}{T_{c0}} = 1 - \frac{A}{n_b d}$$

(1.1)

[23]. Here A is a constant found to be of the order of  $10^{15}$  cm<sup>-2</sup>, and d is the doping depth of the B layer. One hypothesis derived from the results is that this is an example of interface superconductivity where  $n_b d$  is an approximate 2D sheet carrier density. Superconductivity may be related to an interface between a layer of heavily boron doped Si and bulk Si or the crystal surface.

When monolayers of Pb or In deposited on top of cleaved Si  $\langle 111 \rangle$  surfaces, the interfaces were also observed to be superconducting. The monolayers of metal had a density of  $10^{15}$  atoms/cm<sup>2</sup>. This atomic density is similar to the sheet carrier densities observed in the boron doping experiments. The superconducting gap was measured by scanning tunneling spectroscopy. Angle resolved photoemmision spectroscopy measurements indicated that superconductivity was associated with covalent Pb-Si bonds and not due to the thin Pb film which was a single monolayer in thickness.[24] Thicker Pb film overlayers showed superconducting properties that are consistent with Pb. Interface

superconductivity has also been observed at interfaces of  $LaAlO_3$  with  $SrTiO_3$ .[25]

Our experiment involved inducing a conducting layer on  $\langle 100 \rangle$  Si wafers using an ionic liquid. Details regarding the sample design and the measurement are covered in chapter 2 This chapter also contains the details of calculating the induced carrier density in Si. Si has been referred to as the hydrogen atom of solid state physics. Isolated donors with the background of full valence shell of Si atoms have an electron binding energy with a hydrogen-like spectrum. The bound electrons have a hydrogen like wave functions. Overall, the physics of Si is well understood, which makes this system an ideal platform for the microscopic study of gating with an ionic liquid.

Chapter 3 contains a description of a model of electrostatic carrier induction using an ionic liquid. The chapter will cover the onset of conduction at the low carrier density of  $10^{11}$  cm<sup>-2</sup>, and the conduction mechanism of the induced carriers. The IL was found to induce surface acceptor states where conduction happens by tunneling of holes between localized states. The behavior of holes on the Si surface due to the charged ions in the ionic liquid were found to conduct in a manner similar to that of electron clouds formed by Na<sup>+</sup> ions implanted within a SiO<sub>2</sub> overlayer of a Si wafer.[26]

At high carrier densities the double layer is often viewed as a uniform sheet of charge. The similarities to the Na<sup>+</sup> experiment suggests that at low carrier densities one should consider the ions in the liquid as a series of discrete charges. Our experiment was also designed to suppress electrochemical reactions observed in other experiments.

Chapter 4 will focus on behavior at carrier densities between  $10^{12}$  cm<sup>-2</sup> and  $10^{13}$  cm<sup>-2</sup>. The carrier density range is still well below the high  $10^{15}$  cm<sup>-2</sup> density achievable with an IL liquid. The carrier densities studied in this Chapter are within densities achievable with conventional transistors using high dielectric constant gate insulators. A very interesting and unexpected result of this study was the discovery of 2D metallic behavior at carrier densities much higher than those at which metallic behavior was previously observed. Data on the high carrier density metal-insulator transition (MIT) is presented and discussed in the framework of existing MIT physics. Only a subset of samples showed metallic behavior and the reason for this is not yet understood.

At densities higher than  $10^{13}$  cm<sup>-2</sup> further increase of the carrier density lead to the samples becoming more insulating. In effect the sample mobility exhibits a peak as a function of carrier density. This was true for both metallic and nonmetallic Si samples. This peak behavior is not yet well understood but has been observed in experiments on other materials. The behavior has been explained by theories that can account for the behavior by calculating the effect of surface roughness scattering at high carrier densities. Covered in Chapter 5 is the observed mobility peak as a function of carrier density, the reproducability of the observed peak, and a theory that calculates the mobility as a function of carrier density.

We were unable to induce superconductivity into a surface layer which was the original goal of the experiment. The discovery a high carrier density metal-insulator transition is one of significant experimental interest. Si was also found to be a platform where an IL can be used to electrostatically induce carriers in a surface state. Further experiments may lead to a better understanding of the microscopics of carrier induction at high carrier densities. In addition, IL gating of Si could be used to study the transition from electrostatic to electrochemical processes and the interplay of the two mechanisms in EDLTs.

# Chapter 2

# **Techniques and Materials**

### 2.1 Introduction

This chapter will cover some of the basic experimental details of ionic liquid (IL) gated silicon. The chapter consists of three sections. Section 2.2 covers the basic details of the electric double layer transistor (EDLT) and the methods we used to determine sheet carrier densities. High carrier densities can be achieved with EDLTs using ionic liquids, but the microscopic physics is not yet understood. The current model is that of the formation of a Helmholtz layer as a uniform sheet of ions. Using ionic liquids in EDLTs involves both electrostatic and electrochemical processes and a review of electrochemical observations is discussed in section 2.2.2. Our experiments were designed to suppress electrochemical reactions and we have several observations that lead us to believe the carriers we discuss are electrostatically induced.

Section 2.3 covers the measurement system used and the considerations required to work at cryogenic temperatures when using ionic liquids. This section will also cover the procedure used to calculate sheet resistance using the van der Pauw method. Details involving sample fabrication can be found in section 2.4. Samples were prepared using equipment available at the University of Minnesota Nanofabricaiton center.

### 2.2 Electric Double Layer Transistors

This year marks the 50th year of Moore's Law which was an observation that onchip transistor density increased in a linear log relationship with time. The transistor is a three terminal device whose name is derived from transconconductance and resistance.[27] In its realization as a field effect device, it is a combination of a capacitor and resistor. Capacitors are devices that store charge with an applied voltage. Thus the charge density is altered on the capacitor electrodes. If one also adds an additional wire to one of the capacitor electrodes, the electrode conductivity can be measured. For a material where the conductivity varies exponentially with carrier density this configuration can be used as an electrical switch. The invention of the transistor and the use of silicon transistors in technology has lead some to refer to the past 50 years as the "Age of Silicon."

In the laboratory, transistor configurations can be a tool to measure material properties as a function of carrier density. Conventional solid dielectrics have several limitations that prevent their use at the high carrier densities involved in our experiments. High carrier densities can be achieved by using either large capacitance transistors or high gate voltages. In the later case one is limited by the breakdown voltage of the measurement lines or capacitor or gate dielectric. Increasing the capacitance of a transistor is another way to increase carrier densities at a fixed gate voltage; however one must either increase the dielectric constant of the insulator or decrease the thickness of the capacitor. Quantum mechanics allows for electrons to tunnel though sufficiently thin dielectric materials thus leading to a upper bound on carrier density achievable though the reduction of capacitor thickness. In EDLTs using ionic liquids as dielectrics will result in atomically thin capacitors without the added complication of electron tunneling, and densities of  $10^{15}$  cm<sup>-2</sup> are routinely achieved. Conventional dielectrics are unable to reach the  $10^{15}$  cm<sup>-2</sup> carrier density possible using ionic liquids.[28]

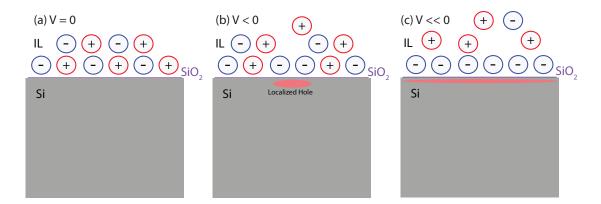

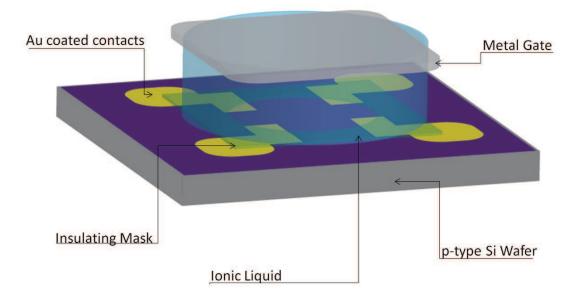

Figure 2.1 is a cartoon depicting the interaction between the IL and the sample surface. Without an applied  $V_g$  the cations and anions are randomly distributed throughout the liquid. There are equal numbers of cations and anions at the sample surface and there are no screening charges due to the collection of ions being neutral. When a negative voltage is applied to the gate, anions are repelled and pushed to the sample surface while cations will be attracted to the gate. This model of carrier induction is discussed in greater detail in Chapter 3. The excess anions will induce screening holes in the Si. At low gate voltages the number of excess anions at the surface are much smaller than the number of total ions at the sample surface. At higher gate voltages and high carrier densities, anions are considered to be a uniform sheet of charge with a second, less dense, layer of cations attracted to the sheet of anions. Voltages must remain within the electrochemical window of the IL. The electrochemical window is defined as the range of voltages over which oxidation and reduction of the ionic liquid does not take place.[29]

#### 2.2.1 High Carrier Density

Interest in ionic liquids dates back as far as the thermal battery. Thermal batteries contain an electrolyte that is solid and inert at room temperature. Energy can be released from the battery by warming it to a temperature where the electrolyte no longer remains solid. The batteries are single use but have a very high power output due to large ionic conductivities and high carrier densities. Significant focus has been on producing rechargeable batteries with high energy density and decreasing the operating temperature. The ionic liquids we use are molten salts with freezing temperatures below room temperature. The ions are composed of charged molecules and the increase in their sizes compared to those of single atoms reduces the Coulomb energy between a pair of ions by increasing their separation. It is this reduction in the Coulomb attractive energy that allows ionic liquids to be liquids at room temperature.

Thermal batteries are able to store large amounts of energy due to the ability to reach extremely high carrier densities a property shared by capacitors. This can be seen in the following equation expressing the relationship between stored energy and charge

$$U = \frac{1}{2}CV^2 \tag{2.1}$$

Here V is the voltage on a plate and the capacitance C is the ratio of the amount of stored charge for a given voltage given by

$$Q = CV \tag{2.2}$$

At a fixed voltage the energy density of a capacitor is entirely determined by its capacitance. It should be noted that while a battery chemically stores energy, in a capacitor the energy is stored as an electric field. In the simple case of the parallel plate capacitor the capacitance is determined by

$$\frac{C}{A} = \frac{\epsilon}{d} \tag{2.3}$$

Here d is the separation of the plates,  $\epsilon$  is the dielectric constant of the insulating material, and A is the area of the electrodes. The variable C/A is the capacitance per unit area used to determine the charge density at a fixed voltage. Higher carrier densities can be achieved by increasing the capacitance and that comes from using an insulator with a higher dielectric constant, or reducing the separation of the metal electrodes. The former case is limited by the physical materials that are available. Increasing the capacitance by reducing the thickness of the capacitor has recently approached a physical limit.

Quantum mechanics tells us that in the limit of very thin finite potential barrier there is a nonzero tunneling probability that increases with decreasing thickness. In the limit of an atomically thin capacitor electrons can pass through the insulator thereby reducing the total charge that one can accumulate in the capacitor. One solution to this problem is to construct a circuit where the charge carriers are not electrons. By using a dielectric material composed of conducting ions, the ions are able to move to the surface of the electrodes but must remain in the dielectric material. The electrons on either plate remain separated by distances where quantum tunneling is not an issue yet are within nanometers of the ions.

The model of the Helmholtz double layer involves the formation of an atomically thin capacitor between the ions in the liquid and the screening electrons in the electrode. When a voltage is applied, the ions will form a layer of cations at the negative electrode and anions at the positive electrode. A second layer of cations will form on the anion layer as well as a second layer of anions on the cation layer. The configurations at each electrode are referred to as double layers. Double layers are formed at both electrodes leaving the bulk liquid in a net neutral state. The combined double layer along and electrode is an individual capacitor with an effective nanometer level separation where the charges are composed of the ions and electrons. The ions have a much lower tunneling probability and so high carrier densities can be achieved. There will be two double layers in series and while capacitors in series store less charge for a given voltage the increase in the capacitance at each electrode more than makes up for this effect. In our experiments a thin layer of  $SiO_2$  roughly 10 - 15Å, as measured by ellipsometry, was on the Si surface separating the ions from the electron channel. In the 2D limit where the the screening electrons are assumed to be confined to the Si/SiO<sub>2</sub>interface, the expected capacitance per unit area of the thin  $SiO_2$  layer is  $4\mu F/cm^{-2}$ . The ions in the ionic liquid are typically cylindrical shaped molecules and the simple calculation assumed the charged portion of the ion is resting on the  $SiO_2$  surface.

### 2.2.2 Electrostatic or Electrochemical Changes

While ILs can achieve high carrier densities, the mechanism in some instances has been shown to be a combination of electrochemical and electrostatic processes. An electrochemical processes is a redox reaction between an electrode and an ionic conductor. Oxidation was also determined to be the source of carrier modulation in the experiment in which VO<sub>2</sub> was shown to undergo a MIT.[30]. Several observations were made that all support the oxygen vacancy scenario. XPS measurements were conducted and found that  $V^{4+}$  changed to  $V^{3+}$  as a function of gating. When  $O^{17}$  was introduced during the gating process, its concentration within the VO<sub>2</sub> film would be significantly above the atmospheric concentration. When the gate voltage was removed after VO<sub>2</sub> had been gated into the metallic state the material remained metallic, even hours after the removal of the ionic liquid. To restore insulating sample behavior a negative voltage as large as the largest positive voltage had to be applied. The applied voltages were lower than the energy required to form oxygen vacancies so the reduction process was thought to be related to migration of oxygen from the ionic liquid into VO<sub>2</sub> due to the high electric fields that were present.

There was evidence for oxidation even in the gating of Au. By using low angle X-rays, it was shown that IL gating of Au resulted in monolayers of  $Au_2O_3$ .[31] The removal of electrons due to the formation of the oxide greatly exceeded the number of electrostatic carriers and was determined to be the origin of the high carrier modulation. In the previous two experiments, the gate voltage was applied at room temperature.

It has been suggested that carrier modulation is entirely an electrochemical process but oxidation processes have been shown to be be suppressed with the use of a thin insulating barrier.[32] In our experiments the electrochemical effects were suppressed by modulating the carrier density below room temperature; however, carrier modulation must be performed when the ions are in a mobile state. In addition a thin oxide was used as a passivation layer to reduce trapping sites on the Si surface. Without the oxide, traps can number in excess of  $10^{16}$  cm<sup>-2</sup>, but the increased separation between the ions and the channel will reduce the capacitance of the transistor. It is therefore desirable to have a very thin oxide barrier.

When electrochemical processes are present, both the magnitude of the gate voltage and the amount of time spent with the IL in a liquid state are parameters that determine the change in resistance of the sample. There were no observed changes to the low temperature resistance unless the gate voltage was changed. Changing the gate voltage and waiting either for minutes or for an hour had the same effect. Warming to a temperature where the ionic liquid melts and not changing the gate voltage had no affect on the surface state resistance. Electrochemical processes will also lead to large leakage currents measured by the gate ammeter. For our measurements, the leakage currents were on the order of a nA or lower. The electrochemical window sets an upper limit to the voltage that, when exceeded, results in breakdown of the electrolyte. In our experiment we gated with voltages, < 2V, below the electrochemical window of 3V for DEME-TFSI. The value for the electrochemical window was determined at room temperature and should be larger at 230 K where the gate voltage was changed. Further evidence supporting electrostatic processes with IL gating of Si are presented in the following section in addition to Chapters 3 and 5. While more work needs to be done to better understand the role of oxygen when using an ionic liquid, in Chapter 3 a model for the electrostatic behavior when using an ionic liquid is presented.

A recent publication concluded that structural changes are also possible due to high electric fields from the sheet of ions.[22] The change was found to be a reversible process just like the electrochemical reactions. The carrier densities used in Chapter 3 and 4 of the IL gated Si experiment are similar to carrier densities used with conventional dielectrics and thus high electric field structural changes are thought not to occur; however Chapter 5 covers carrier densities that are high enough to consider the possibility.

### 2.2.3 Calculating the Carrier Density

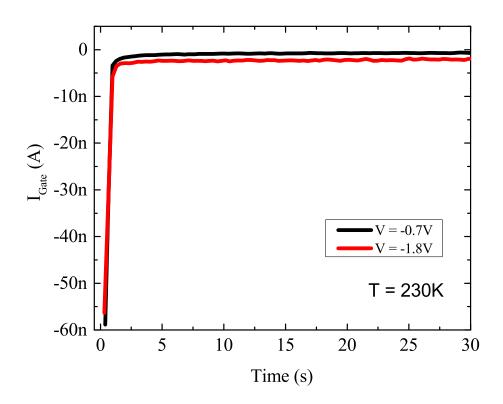

With an ammeter in series between the gate voltage source and the sample, one can monitor the current flowing to the electrodes as a function of time during the charging process. By Kirchhoff's law, this is a measure of the number of ions moving to the sample surface. Integrating the current as a function of time, one can then calculate the number of charges that have moved though the ammeter as the sample was charged. This process can be a measure of the number of ions that are now at the sample surface as long as there are no additional chemical reactions that would lead to an additional leakage current though the transistor. In an ideal capacitor, no current should flow once the capacitor voltage is charged to the source voltage. In Fig 2.2 a plot of two charging curves are presented. They are representative of all the charging curves measured for each sample presented in this work. During charging, we see what appears to be an exponential decay in the current as a function of time within the first 10 s of charging after which the current level is below the noise level of  $\sim 0.8$  nA at low voltages and around 2 nA near a gate voltage of 2V.

To determine the carrier density, the area under the curve of current vs time is measured relative to the background current. This subtraction of the leakage current leads to a shift in the amount of calculated charge by about 10. This method can be problematic in situations where the leakage current is much higher, as the subtracted area approached the order of the integrated area.

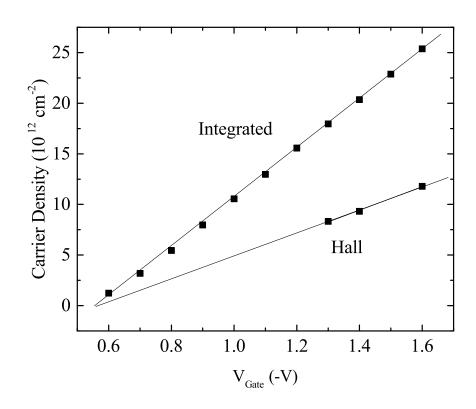

Situations where the leakage current is high involve higher temperatures and higher gate voltages. Below 200 K, the ammeter displays a value consistent with the ammeter reading a broken connection and we interpret the disappearance of any ionic conductivity with the solidification of the ionic liquid. Above 200 K, there is a finite leakage current that increases with temperature, and at temperatures near room temperature the leakage current is constant on the order of 1 - 10 nA. At higher gate voltages the leakage current is much higher and is no longer found to exponentially decay but decays with a  $\sqrt{t}$  time dependence. In these situations, the integrated density will differ from measurements of the carrier density using the Hall effect by a couple orders of magnitude. In our samples the Hall carrier density is a factor of 2 below the integrated carrier density. One example of this is shown in Fig 2.3. The reason for this dependency is not known at this time but both methods have complications that are discussed in Chapters 3 and 4.

# 2.3 Cryogenic Resistance Measurements with an Ionic Liquid

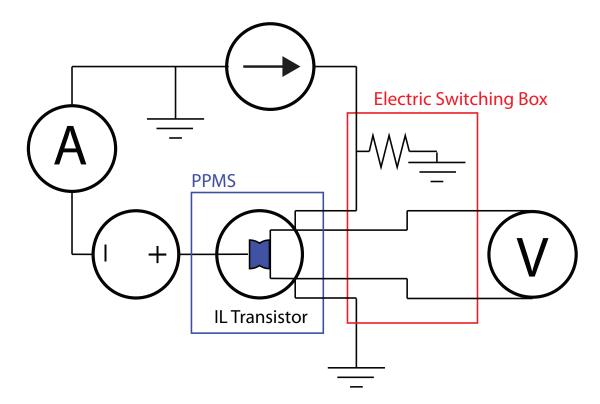

#### 2.3.1 Measurement Cryostat and Charging Procedure

Samples were measured in a Quantum Design Physical Properties Measurement System (PPMS) with a 2K base temperature. An optional <sup>3</sup>He refrigerator insert could be used to lower the base temperature to 450mK. The PPMS system was chosen because of the need to temperature cycle the sample above the melting point of the IL. This procedure allows the ions to be mobile and the carrier density to be altered. While the optional <sup>3</sup>He insert lowers the base temperature of the system, this comes at the cost of thermal cycling time as the additional mass must be heated and cooled with each cycle to 230K. Most samples were screened without the insert to minimize measurement time. If a lower temperature was determined to be needed the sample would be installed on the refrigerator insert, but this required removing the sample from the system and thus discharging the conducting surface state. Once the sample was mounted to the insert and installed the measurement procedure would begin again.

The samples were loaded at room temperature with all the sample contacts grounded. The samples were then cooled to 180 K before beginning the measurement procedure. When the ionic liquid was in a liquid state (above 200 K) all the sample leads were grounded. Measuring the sample resistances when the conductivity of the ionic liquid is comparable to the sample can lead to measurement artifacts. This happens when the sample conductivity is low or at high gate voltages when the ionic liquid conductivity is high. While the conductivity of the bulk Si wafer is significantly higher than the ionic liquid conductivity, all the sample leads were grounded when the ions were mobile so as to not skew the carrier density with stray electric fields.

At 180 K the sample leads with the exception of  $I^-$  were ungrounded and permuted with a Keithley 7001 electric switch. Even though the IL is solid,  $V^-$  of the gate source remained connected to  $I^-$  of the current source and the sample, throughout the measurements. Resistance measurements were made in a 4-terminal configuration and the sheet resistance was calculated by the van der Pauw method. Resistance was measured as a function of time as the sample was slowly cooled. Upon reaching base temperature, current-voltage sweeps were made to determine if the contacts were ohmic and the range of currents were within the linear regime. Then, a constant current within the linear regime was be used to measure the sample resistance as it was incrementally warmed. To nullify any DC offset the resistance was calculated from the following formula

$$R_i = \frac{V(+I) - V(-I)}{2I}$$

(2.4)

where  $R_i$  is the resistance for a given permutation of the contacts.

#### 2.3.2 Sheet Resistance Calculation

The Van der Pauw method allows one to calculation of the sheet resistance of an object with an unknown geometry.[33] Four contacts are placed on the perimeter of the

sample, ideally at the center of mass. By rotating the contacts and making multiple resistance measurements, two orthogonal measurements can be combined to check the sheet resistance. If the sample is known to have a large amount disorder, the Van der Pauw method is not advised. Specifically, if a permutation of the contacts by 180 leads to resistance measurements than 10% apart then the sample is too disordered to use the van der Pauw method. A key advantage of the van der Pauw method is that two measurements made with a 90 permutation of the measurement leads can be combined to determine the sheet resistance independent of the sample geometry.

The sheet resistance is determined from the following formula

$$\exp(-\pi R_H/R_S) + \exp(-\pi R_V/R_S) = 1$$

(2.5)

where  $R_S$  is the sheet resistance and  $R_H$  and  $R_V$  are two orthogonal resistance measurements of the sample. If the ratio  $r = R_H/R_V$  is close to 1, then the sheet resistance can be determined from the following simplification

$$R_S = \frac{R_H + R_V}{2} \frac{\pi}{\ln(2)} * f$$

(2.6)

When  $r \neq 1$ , f must be determined analytically. Using the dimensionless variable

$$u = \frac{r-1}{r+1}$$

(2.7)

f can be determined from the following equation

$$\exp(u/f_1) - \exp(-u/f_1) - \exp(1/f_1) = 0 \tag{2.8}$$

where  $f = f_1 ln(2)$ . For most of our sample patterns r fell within the range of 1.4 - 4 but in some geometries the ratio was as high as 15. We also used a Hall bar geometry to measure the sheet resistance and found that the results agreed with the values produced by the van der Pauw method.

### 2.3.3 Determination of the Hall Resistance

The Hall coefficient is an off-diagonal term of the conductivity matrix and must be odd with respect to the sign of magnetic field. To remove components of the sample magnetoresistance when determining the Hall coefficient, the following calculation was made.

$$2R_{ODD} = R(B) - R(-B)$$

(2.9)

The variable  $R_{ODD}$  should be the contribution that is odd in field. We define the Hall coefficient as

$$R_{Hall} = \frac{dR_{ODD}}{dB}$$

. The density of holes is related to the Hall coefficient by

$$R_{Hall} = \frac{1}{en_h} \left( \frac{1 - ab^2}{(1 + ab)^2} \right)$$

(2.10)

where  $a = n_e/n_h$  and  $b = \mu_e/\mu_h$ .[35]  $n_i$  and  $\mu_i$  are the carrier density and mobility respectively, with the index *i* indicating either electrons or holes. In semiconductors, the product of  $n_h$  and  $n_e$  is referred to as the law of mass action is independent of the doping level following

$$n_e n_h = N_e N_h \exp\left(-\frac{E_g}{T}\right) \tag{2.11}$$

where  $N_i$  are the density of states for electron and holes. At temperatures where the Hall effect was measured, the intrinsic carrier density is suppressed enough that the densities of holes from the Hall coefficient were determined using  $n_h = (eR_{Hall})^{-1}$ .

### 2.4 Sample Design and Cleanroom process

#### 2.4.1 Silicon fabrication

There is a large market established for silicon wafers. Silicon can be purchased undoped or doped at a variety of concentrations with both n and p-type dopants. A very common transistor is one based on the p-n junction of a Si MOSFET where n type contact are placed in p-type silicon.

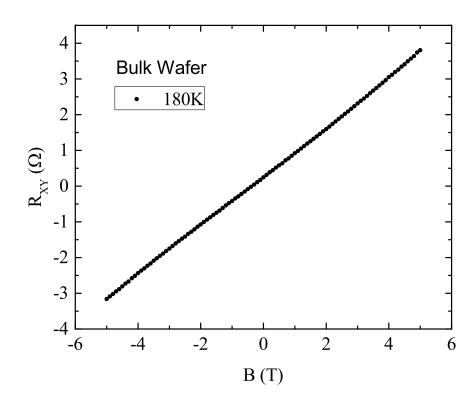

The wafers used in this study were supplied by Silicon Quest International. They were single side polished, boron, doped  $\langle 100 \rangle$  wafers, 100 mm in diameter. The quoted total thickness variation (TTV) was 15 $\mu$ m. The wafers were test grade with  $\rho = 1 - 5 \Omega$ cm corresponding to boron dopants on the order of  $10^{16} \text{ cm}^{-3}$ . The density was confirmed by measuring the Hall effect at 180 K and is shown in Fig 2.5. A commercial wafer saw was used to dice the wafer into 6 mm square substrates that were then further processed for the study. Shipley's 1800 series photoresist was used to protect the wafer surface during the cutting procedure. The photoresist was kept on the samples during storage and only removed prior to metal deposition.

A silicon surface without a passivation layer has trap density on the order of  $10^{16}$  cm<sup>-2</sup>[36]. The trapping sites are due to dangling silicon bonds. Trapping sites can be reduced by bonding the surface silicon atoms to another element like hydrogen or oxygen. Dilute hydrofluoric acid can be used to remove a surface oxide of silicon and terminate the surface with hydrogen atoms.[37] The hydrogen terminated surface is metastable and the surface will oxidize in the presence of dry oxygen or water. The growth of SiO<sub>2</sub> on Si is a self-limiting process that occurs over a 10 minute time period.[38] The presence of an oxide can lower the trap density down to  $10^{11}$ cm<sup>-2</sup> after annealing in a forming gas solution. A forming gas is typically a mixture of an inert gas or N<sub>2</sub> with H<sub>2</sub>. The presence of H<sub>2</sub> increases the number of hydrogenated bonds on the silicon atoms not

bonded to the oxide.

No surface state could be formed on devices that had the oxide removed prior to the application of the ionic liquid. Attempts were made to decrease the roughness of the silicon surface by annealing but this procedure also did not produce a functional device. Silicon surface states could be formed on devices where the oxide was regrown at room temperature with the use of ozone. These devices were not as conducting as devices that were made using the native oxide that was formed on the wafer at the factory. Most publications on transistor fabrication focus on very thick oxides that would reduce the capacitance of the IL transistor. Further study is needed to produce good quality thin oxides with low oxide charge, uniform coverage, and low surface roughness. Available cleanroom tools were considered to follow Volmer–Weber growth mode of cluster nucleation as opposed to layer by layer or Stranski–Krastanov growth.[39] Atomic layer deposition (ALD) tools have promise for the formation of thin uniform oxides.[40] In addition, SiN has been found to be an effective passivation layer.[41, 42]

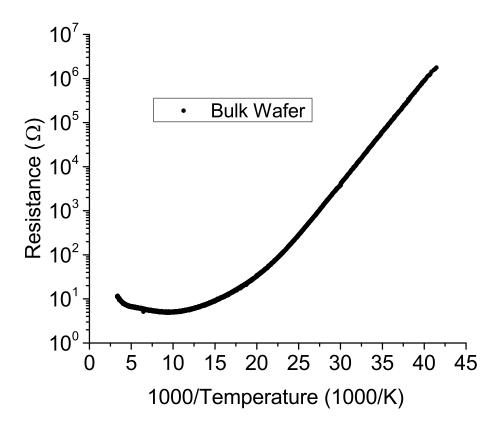

All the devices presented in this dissertation used the native oxide as a passivation layer and ellipsometry measurements indicated the oxide was roughly 15 - 20 Å thick. The sample contacts were made of a metal stack of Al, Ti and Au. Al makes ohmic contact to p-type silicon and also has the potential to create an enhanced hole doped region under the contact. Aluminum has the added benefit of making ohmic contact to the underlying silicon by dissolving the surface oxide.[43] The Al<sub>2</sub>O<sub>3</sub> that forms will diffuse into the bulk Al. The layer of Au on top of the metal stack was to reduce any electrochemical effects the Al contacts may encounter from electrostatic gating. Titanium was used as a diffusion barrier during subsequent annealing as Au atoms in silicon devices are recombination centers. All 3 metals were deposited in the same sputtering chamber without breaking vacuum and were patterned with a shadow mask. The metal stack was annealed at 350°C in a forming gas solution for 5 minutes. The annealing temperature was chosen to be well under the Au/Si eutectic temperature of 380°C.[44] There was some interdiffusion of the three metals which occurred in the annealing process. The first few samples were made in a modified process where Al was deposited and annealed before the deposition of Ti and Au. In the latter, case one must remove the samples from the sputtering chamber for the annealing step and the devices were the same as those produced using the aforementioned procedure. Figure 2.6 is a typical resistance vs temperature measurement of the bulk wafer.

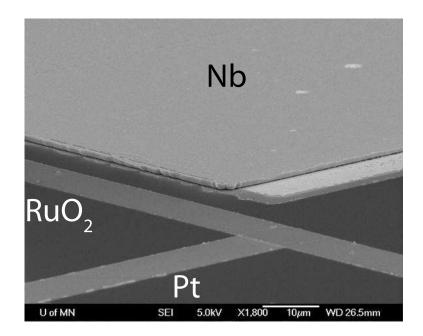

#### 2.4.2 Sample design

In some samples, a SiN layer was deposited to define the channel exposed to the IL. In those cases the SiN layer was grown by Plasma Enhanced Chemical Vapor deposition and pattered with UV lithography using a single layer of Shipley's 1813. Both Hall bar geometries and square patterns were made with SiN. Hall bar patterns were made using positive UV lithography and an image reversal process. [45] The photo masks were designed for material deposition into Hall bar patterns. Positive lithography was chosen as the resist sidewalls will have a negative slope after the image reversal process. [45] With positive lithography exposure to UV light increased the solubility of the resist to a developing solution. The image reversal process involves an additional chemical reaction within the photoresist before development. Exposure to  $NH_3$  will cause the portions of the resist that are more soluble due to UV exposure to harden and become nonreactive to the developing solution. After the image reversal process, the wafers were flood exposed to UV light to chemically activate the previously unexposed regions after which were developed away. Square pattern geometries were also formed using positive photoresist lithography but in this case the pattern on the photo mask did not require the use of the image reversal process. The relatively large 0.5mm square contact pads were covered in Kapton tape so as to not coat them with SiN during the deposition.

A glass cylinder was used to contain the IL on the Si surface. Some cylinders had an inner diameter that was slightly larger than the area of the square SiN pattern. In some samples the smaller diameter cylinder was used to define the sample area and the insulating SiN layer was not deposited. In this case the the cylinder was positioned with the assistance of an optical microscope to ensure that the 4 metal electrodes would be exposed to the liquid. Any unexposed Si would be an insulator, isolating an electrode from the surface state at low temperatures. The cylinders were attached with Epoxy 220 and allowed to cure for the manufacturer's allotted time. In some cases the IL was found to have escaped confinement after several thermal cycles. While possible that the IL acts as solvent for the epoxy, several samples were observed to be very robust. A few samples were each used in up to four different gating experiments, being removed and cleaned in propanol between each experiment, with no signs of liquid loss after each measurement.

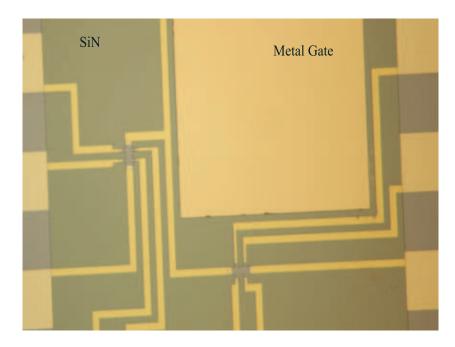

Second generation devices made use of a planer side gate, a configuration that does not require the attachment of a glass cylinder to the sample surface. Figure 2.8 is an example of a second generation pattern but with a planer gate. The gate must be sufficiently insulated from the wafer as as to not short the EDLT. The conductivity between the gate and the wafer at 230 K for the sample in the figure was too high for a proper gating experiment. Although work is being done to improve second generation devices, all data presented in the following Chapters were taken using the first generation devices.

### 2.5 Summary

To induce an IL liquid surface state in Si, ohmic contact was made to p-type Si wafers. A glass cylinder was epoxied to the Si surface with a with Pt. metal coil inserted as a gate

electrode. The cylinder was filled with the IL, DEME-TFSI before each measurement. If the sample was removed from the cryostat, the liquid would be removed and new IL used before another experiment. A PPMS was used for the measurements as modulation of the carrier density must be done with the IL in a liquid state. DEME-TFSI freezes at 200 K. The gate voltage was adjusted at 230 K with all the sample contacts grounded. At 180 K the contacts were ungrounded and resistance measurements were made using the van der Pauw method.

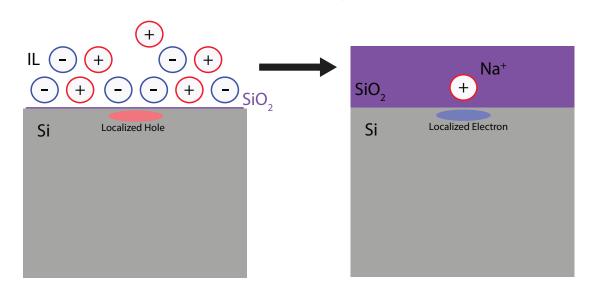

Figure 2.1: Cartoons of an EDLT transistor at different values of  $V_g$ . The gate electrode is not shown. In each case the cations on the gate are assumed to exhibit the same behavior as the ions at the IL to sample interface. (a) IL to sample interface at  $V_g = 0$ . (b) At low carrier densities and with  $V_g < 0$  excess anions will repel electrons from the sample surface. Here the anions are treated as dilute descrete quantities on the sample surface. This model is discussed in greateer detail in Chapter 3 (c) EDLT cartoon when  $V_g \ll 0$ . The anions are viewed as a uniform sheet of charge in the high density limit.

Figure 2.2: Current measured by an ammeter in series with the sample and the gate during charging. The charging curves were recorded for each increment of the gate voltage. Plotted are an example of two of the curves. From the graph one can see that the current decays to the background level within the first few seconds and the background level increases with gate voltage. To determine charge transferred to the sample surface the gate, current was integrated as a function of time up to 10s subtracting off the average current level taken from the 20s to 30s time interval.

Figure 2.3: Carrier densities as a function of gate voltage calculated using the integration method and determined from the Hall coefficient at 2 K. Both methods produce a linear carrier density as a function of gate voltage. For multiple samples the Hall slope is typically half of the slope found by the integration method. Extrapolation of the Hall carrier density to the origin predicts that the onset of conduction should occur near V = -0.6 V which was the case for this sample. The integrated carrier density was determined by counting only charges transferred to the surface after  $V_T$ , determined by the onset of conduction, was reached.

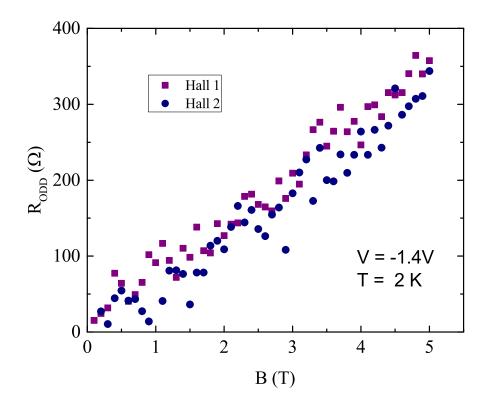

Figure 2.4: Example of Hall effect data taken at V = -1.4 V for both Hall orientations. The data was taken from -5 T to 5 T and  $R_{ODD}$  was calculated using Eq. 2.9. The two curves represent orthogonal measurement in of the van der Pauw geometry for Hall effect measurement.[34] Both slopes agree with each other and the scattering of the points leads to  $\Delta n$  of 2%. The voltmeter was connected in an orientation where holes would produce a positive slope with field.

Figure 2.5: Transverse resistance,  $R_{XY}$ , vs magnetic field at 180 K. The Si wafers were 500  $\mu$ m thick. The volume carrier density determined from the wafer thickness and the slope of the graph was calculated to be  $1.6 \times 10^{16}$  cm<sup>-3</sup>. The voltmeter was connected in a manner where holes produced a positive Hall resistance. 180 K is well above the freezeout range for such a high doping. The measured carrier density was determined to be an accurate measurement of the extrinsic carrier density.

Figure 2.6: Resistance vs temperature for boron doped Si after annealing. The x-axis was scaled to match standard industry plots of semiconductor resistance vs temperature. After annealing to make ohmic contact to the bulk Si wafer several samples were screened though the PPMS to make sure the contacts to the wafer remained ohmic. The figure is a standard curve for a sample determined to be good.

Figure 2.7: Cartoon of the device used to measure silicon surface states induced by an ionic liquid. The contacts were an annealed stack of Al, Ti, and Au. A layer of SiN used in some samples as an insulating mask to define the gated channel. Not shown is a glass cylinder epoxied to the surface that was used as a containment vessel for the IL. The metal gate was a Pt. coil submerged in the IL and is depicted as a planer gate for clarity in the figure.

Figure 2.8: Photograph taken with a microscope camera of a completed second generation device. Second generation devices employed a planar side gate that does not require the use of a metal coil submerged within the liquid and as well as a glass containment vessel. The use of epoxied cylinders was sometimes a point of failure for the experiment. Instead a drop of IL would be applied directly to the wafer covering both the sample area and the wafer. A cover glass in addition to the liquid surface tension was sufficient to hold the liquid in place. Because of the high conductivity of the bulk wafer, side gates must be sufficiently insulated from the wafer at gating temperatures to prevent shorting the transistor. In the pictured device, the conductivity between the gate and the wafer was too large at 230 K for a proper gating experiment.

### Chapter 3

# 2D Silicon Surface State and Hopping Conduction

#### 3.1 Introduction

This chapter will focus on gating with an ionic liquid (IL) at carrier densities below  $10^{12} \text{ cm}^{-2}$  along with a model for the process. When the IL is in contact with the Si wafer, there are both cations and anions on the SiO<sub>2</sub> surface. The ions have cylindrical geometries that when approximated as a sphere, the radius of the anion TFSI is roughly 4.4 Å.[46] whereas the cation DEME is slightly larger. Based on the size of the ions there are roughly  $10^{15}$  ions cm<sup>-2</sup> at the sample surface. Being equal in number and opposite in charge has the result that there will be no net charge over the whole sample surface. When the gate is negatively biased excess, anions will be driven towards the Si surface leaving it with a net negative charge. The result is that electrons in semiconducting Si are repelled by the charged surface leaving behind a screening cloud of holes. The screening holes will form a 2D conducting layer just below the Si surface at non zero temperatures.

The configuration is similar to that of Fowler were 2D electron surface states where created by implanting Na<sup>+</sup> into the SiO<sub>2</sub> layer and diffusing them to the interface. In these experiments, the Na<sup>+</sup> ion produced a screening electron cloud at the Si/SiO<sub>2</sub> interface. The conductivity of the surface layer as a function of temperature was shown to follow a two parameter function of the form

$$\sigma_{2D} = \sigma_1 \exp(-\epsilon_1/T) + \sigma_3 \exp(-\epsilon_3/T) \tag{3.1}$$

where  $\epsilon_i$  is an activation energy and  $\sigma_i$  a conductivity prefactor.[26] The first term represents activation to the mobility edge with energy  $\epsilon_1$  which is observed at high temperatures. The second term represents nearest neighbor hopping of electrons between the surface states. Section 3.2 covers the theory of nearest neighbor hopping in greater detail. We would like to understand the physics of ionic liquid gating at low carrier densities similar to those employed in the Na<sup>+</sup> experiments, which were 10<sup>11</sup> cm<sup>-2</sup>.

At densities of  $10^{11}$  cm<sup>-2</sup>, the number of anions leading to the formation of the screening layer is much less than the total number of anions on the oxide surface. This is thought to be due to the large number of cations that will also be on the sample surface. In our model, equal numbers of cations and anions can be treated as a neutral background. Treated this way, the excess anions are the equivalent of isolated charges. If this model is accurate, the physics of the screening hole layer should follow the same physics as screening electrons induced by isolated Na<sup>+</sup> ions. An example of this mapping is shown in Fig. 3.1. To test the validity of treating the ions as a series of discrete isolated charges,  $\epsilon_3$  and  $\sigma_3$  were measured at densities similar to those measured in the Na<sup>+</sup> experiments. A comparison between the two experiments is made in Section 3.5. Other sections of this thesis will cover the physics of surface state conduction in Si for carrier densities between  $10^{11}$  cm<sup>-2</sup> and  $10^{12}$  cm<sup>-2</sup>. Data for  $n \ge 10^{12}$  cm<sup>-2</sup> is discussed in Chapters 4 and 5. The following section summarizes some of the relevant theory for the case of bound charges due to Na<sup>+</sup> atoms embedded in the oxide[26, 36]

Figure 3.1: Illustration of ionic liquid carrier induction in the low density limit. Here we will compare the IL induced Si surface state to the one formed by  $Na^+$  implanted in the oxide at the SiO<sub>2</sub> interface. The remarkable agreement between the two suggests excess quantities of one type of ion can be treated as isolated charges with a neutral background.

#### 3.2 Nearest Neighbor Hopping Theory

When Group V elements are substituted for Si in the lattice, the extra electron is found to be bound to the donor with a hydrogen-like energy spectrum. Electrons bound to positive charges in the oxide are also found to have a hydrogen-like binding energy. Initially at low carrier densities the Na<sup>+</sup>will act like donors and form electron bound states in the silicon layer. The electron and Na<sup>+</sup> are attracted by the Coulomb potential

$$V = \frac{e^2}{\kappa r} \tag{3.2}$$

where  $\kappa$  is the average of the dielectric constants of Si and SiO<sub>2</sub>. The screening electrons have hydrogen-like wave functions that decay as  $\exp(-r/a)$ .[26]

#### 3.2.1 2D Surface State

In the 2D limit of the screening layer, the electrons are considered to be confined to the interface. In actual devices, there is a thickness to the screening electron layer. An approximation of the thickness of the layer can be made by

$$g(z) = \frac{b^3}{2} z^2 \exp(-bz)$$

(3.3)

where z is the distance in Si from the interface and b is a parameter calculated to minimize the total energy per electron in the screening layer. [26] The potential barrier at the interface is large enough that the electron wave function must go to zero at z = 0and be entirely confined to the Si layer. The parameter b is a measure of the average depth,  $z_0$ , of the charge layer in Si given by

$$z_0 b = 3 \tag{3.4}$$

At  $n \sim 10^{12} \text{ cm}^{-2}$ , the charge density as a function of thickness was calculated for accumulation and inversion devices and the calculation produced a peak in the density roughly 30 Å from the interface. [47]

#### 3.2.2 Mechanism of Conduction

As the number of Na<sup>+</sup> ions increases, distance between two neighboring bound states will decrease and the wave functions will begin to overlap. Once the wave functions overlap, electrons will be able to tunnel between neighboring bound states. The process is referred to as nearest neighbor hopping and expressed as the second term of Eq. 3.1 with the hopping activation energy  $\epsilon_3$  that is lower than  $\epsilon_1$ .[26] At higher densities the states form an impurity band.[48] At even lower temperatures and very high resistance, it is proposed that variable range hopping can occur thus requiring a third term to be added to Eq. 3.1. The temperatures and resistance required to observe variable range hopping are not within the accessible parameters of the low carrier density IL experiment.

#### 3.3 Ionic Liquid Surface State in Silicon

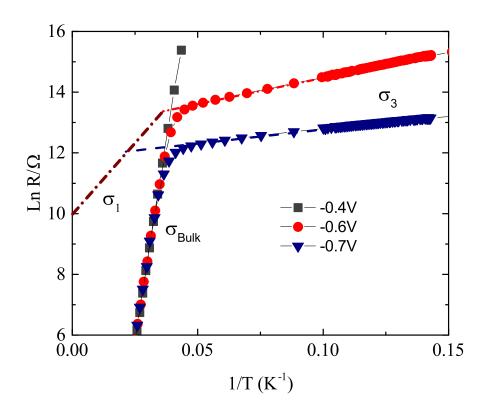

In our experiment, ohmic contact was made to a boron doped Si wafer. In addition to the surface conductivity induced by the ionic liquid, the wafer has conductivity due to bulk conduction. Figure 3.2 shows the natural logarithm of the sheet resistance as a function of temperature for an ionic liquid gated Si sample. At temperatures below 50 K, the resistance was initially independent of the applied gate voltage and followed

$$R_S = \frac{1}{\sigma_{Bulk}} \exp(T_A/T) \tag{3.5}$$

where  $T_A = 43$  meV. Boron acceptors in silicon have an activation energy  $T_A = 45$  meV so we attribute the measured resistance to the conduction of the bulk wafer.[36] Influence on the conduction due to the ionic liquid induced surface state is seen only at temperatures below 20 K, but at low gate voltages a surface state is not observed.

Figure 3.2: Natural logarithm of sheet resistance plotted as a function of inverse temperatures. At high temperatures, the resistance is independent of gate voltage where at lower temperature a conduction surface state is observed. The dotted lines are guides to the eye showing that conducting due to  $\sigma_1$  is completely shorted by bulk conduction.

Semiconductor surfaces can exhibit either p or n type surfaces with silicon typically forming an n-type surface.[36] It is believed that the observed effect is do to trapped positive charge within the oxide. If the trapped charge is in p-type Si, and is large enough, a natural inversion layer is formed on the surface. Although rare, the behavior was observed in some samples.

In all samples we observed a threshold voltage,  $V_T$ , for surface conduction. Interface charge and trapped positive oxide charges are thought to exist at the Si/SiO<sub>2</sub> interface. This results in a downward bending of the energy bands.[36] A different  $V_T$  was observed in almost every sample and we interpret this as a different amount of band bending for each sample. This is also supported by the observation of electron surface states in some ungated samples. In the latter case, application of a negative  $V_g$  will first dissipate the electron surface state before a hole conducting state is formed.

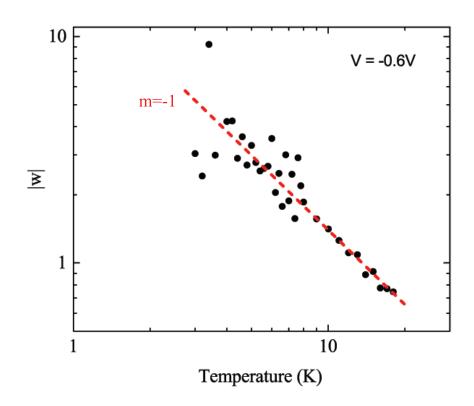

The resistance in hopping conduction has an exponential temperature dependence. Other forms of conduction such as 2D Mott or Efros-Shklovskii variable range hopping have a stretched exponential temperature dependence with x = 1/3 and x = 1/2respectively, where x is the temperature exponent of

$$R = R_0 \exp(T_0/T)^x$$

(3.6)

One method of determining x is by measuring the slope of w vs T on a log-log scale where

$$w = \frac{d(lnR)}{d(lnT)} \tag{3.7}$$

[49]. This is shown in Fig 3.3 where a red dashed line with a slope m = -1 corresponds to the value -x in Eq. 3.6. This shows that the IL surface state in Si has a temperature dependence consistent with the nearest neighbor hopping model. To test the hypothesis that the surface state was due to nearest neighbor hopping we measured  $\epsilon_3$  and  $\sigma_3$  as a function of carrier density n in the low density limit was performed. The results of the

Figure 3.3: Log-log plot of w vs T. The data is plotted for one of the curves in Fig 3.2 below 20 K. The dashed line is a guide to the eye, but is the expected slope for Arrhenius behavior. At 2 Kthe resistance was nearly 10% of the input impedance of the measurement system. Data from 2 K to 5 K were not in the calculation used to produce the Zabrodskii plot.

experiment are discussed in the following sections.

The surface states in Fowler's work had two Arrhenius conduction regimes as seen in Eq. 3.1. Accounting for the fact that the IL ions will be at the SiO<sub>2</sub> surface, the binding energy of a hole to the anion results in  $\epsilon_1 = 8$  meV. At high temperatures, the first term will be shorted by bulk conduction as  $\sigma_{Bulk} \gg \sigma_1$ . The experiments performed by Fowler were on inversion mode devices where the bulk was isolated by the depletion layer. Estimates for the two conduction terms are drawn as dashed lines in Fig 3.2 and the transition from conduction associated with  $\epsilon_1$  to that given by  $\epsilon_3$  is also thought to be shorted by the bulk; therefore only surface conduction due to nearest neighbor hopping is measurable in this experiment.

## 3.4 Low Carrier Density and High Resistance Measurements

The low carrier density limit was studied by first increasing  $V_g$  until a surface state was formed. Carriers were then removed from the surface by decreasing  $V_g$  in small steps. The low temperature activation energy and prefactor were measured at each step. This was done to minimize the measurement time as  $V_T$  will depend on several unknown microscopic parameters.

Below  $V_T$ , no surface state can be seen this is thought to be due to the trapped positive charge in the oxide, as mentioned above. The negative ions that move to the surface are first attracted to the fixed positive charge. The effect is to dissipate a screening electron attached to the oxide charge. Once all the oxide charge is saturated, the additional negative ions will then form a screening hole gas in the sample. Based on the capacitance of the ionic liquid transistor and  $V_T$  the trapped charge could be as numerous as  $10^{12}$  cm<sup>-2</sup>. While this number is larger than the number of anions

Figure 3.4: Electrical schematic of IL gated Si. The high resistance short is thought to be in the Keithley electrical switching card used to permute the contacts. The data sheet for a Keithley 7012 suggests the isolation to ground > 1 G $\Omega$ . The input impedance of the voltmeter is > 10 G $\Omega$ . Removing the electrical switch only lead to a marginal increase in measurable resistance suggesting that there is an additional impedance to ground preventing higher resistance measurements. The additional limiting impedance is thought to be in the PPMS and could be overcome with the use of external user run wires. In addition resistance measurements > 10 G $\Omega$  will require the use of an electrometer to measure the voltage drop across the sample. Electrometers can have an input impedance of > 200 T $\Omega$ .

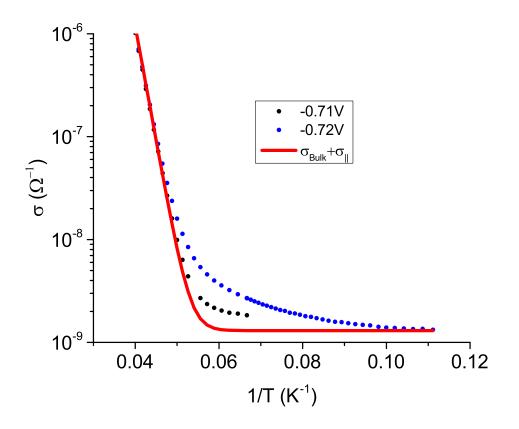

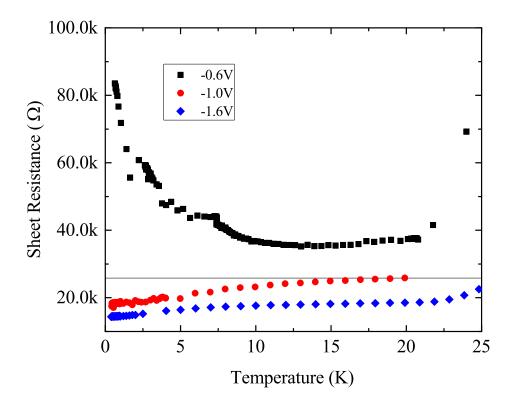

Figure 3.5: Conductance vs inverse temperature for the two lowest gate voltages. The red line is a calculation of the net conductance thought to be due to the bulk wafer and a parallel conduction channel of the level of G $\Omega$  within the measurement electronics.  $V_T$  was determined to be between -0.71 V and -0.72 V with an error of  $\pm 5$ mV. The surface state at -0.72 V was not analyzed as carrier density and error would be of similar size.

contributing to the surface conducting state, the inferred number of trapped charge is much smaller than the number the positive ions,  $\sim 10^{15}$  cm<sup>-2</sup>, that are within the ionic liquid.

The highest resistance measurable in the experiment was limited by the input impedance of an electrical switch used to permute the sample leads for van der Pauw measurements. Each line in the switching card had an impedance on the order of 1 G $\Omega$ to ground. We modeled the sheet conductance, depicted in Fig 3.4, as

$$\sigma = \sigma_{Bulk} + \sigma_3(n) + \sigma_{||} \tag{3.8}$$

where  $\sigma_{\parallel}$  was the conductivity due to parallel current paths to ground. The data for  $\sigma_{Bulk}$  was determined from the change in resistance between 50 K and 20 K for measurements where  $V_g < V_T$  during the initial charging process. In Fig. 3.5 we plot the conductance as a function of temperature for the two lowest measured gate voltages after forming the surface state. The red line is a calculation of the conductance expected from the bulk wafer,  $\sigma_{Bulk}$ , in parallel with a 1.3 G $\Omega$  resistor. The input impedance of our electrical switch box has an input impedance of > 1 G $\Omega$ . The value of the resistor was chosen so that the calculated value matched the lowest temperature conductance measured at V = -0.72 V. From results presented in Fig. 3.5, it was determined that  $-0.71 V \leq V_T < -0.72 V$ . Based on the voltage step size, the error in the accuracy of zero charge is  $\Delta n \pm 6 \times 10^{10}$  cm<sup>-2</sup>. The conductance vs temperature for V = -0.72 V indicates there is excess conductance not accounted for by the bulk. We attribute the excess conduction to the presence of a surface state. While parameters for the surface state could by extracted by subtracting off the calculated curve, this was not done as the calculated carrier density would be of similar magnitude to the carrier density error.

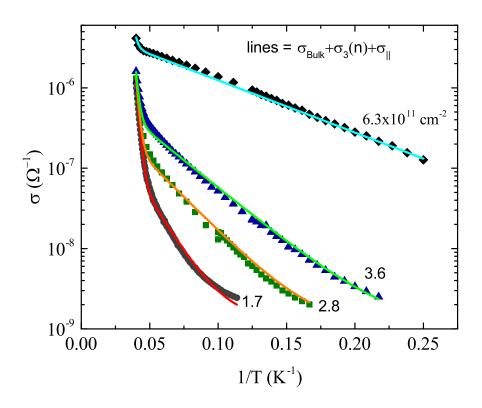

Carrier densities were calculated by the integration method starting from  $V_T$ . Figure 3.6 shows the conductance as a function of temperature and carrier density for the

Figure 3.6: Conductance of silicon surface states plotted vs inverse temperature. Data for four surface states is plotted over the full measurement range. The lines are fits to the conductance assuming three contributions. The bulk conduction parameters were extracted from the linear regime at high temperatures with no surface state. The parallel conduction channel was determined by the low temperature limit of the -0.72 Vcurve in Fig. 3.5. The parameters for the  $\sigma_3$  term were determined from the visible straight line portions of the data. The fits show good agreement with the data and that above 100 M $\Omega$  the source current is not confined to the sample; therefore data for  $R_S \geq$ 200 M $\Omega$  was masked for the nearest neighbor hopping analysis.

next four measured gate voltages. For the low carrier density measurements, the conductivity due to the input impedance of the electrical switch was noticeable when the sample resistance is larger than 100 MΩ. The lines on the figure are calculations of the conductivity from Eq. 3.8. The linear region in resistance was used to determine the parameters of nearest neighbor hopping conduction. The data is in good agreement with Eq. 3.8. Because of artifacts in the sample resistance measurement (caused by $\sigma_{||}$ ) data above 200 MΩ was masked and not considered in the determination of  $\epsilon_3$  and  $\sigma_3$ .

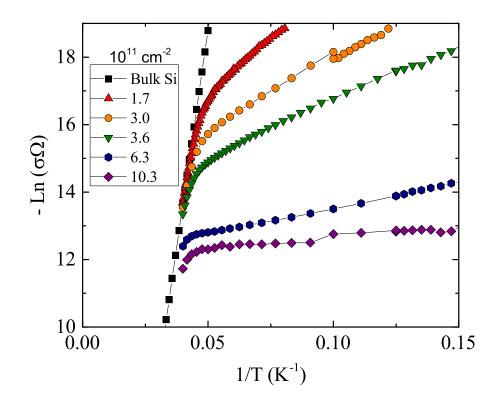

#### 3.5 Hopping Conduction Analysis

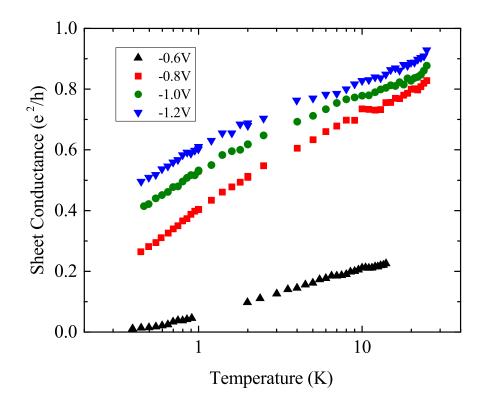

Figure 3.7 shows the natural log of the sheet resistance as a function of inverse temperature. From this we can extract  $\epsilon_3$  and  $\sigma_3$  from linear fits below 15 K. A mask to high resistance data was only applied to the three lowest carrier densities. The two highest carrier density measurements were measured down to 2 K but the data was not plotted to greater emphasize the low carrier density curves. In addition, two curves were omitted for clarity, as the data would overlap with that plotted in the figure.

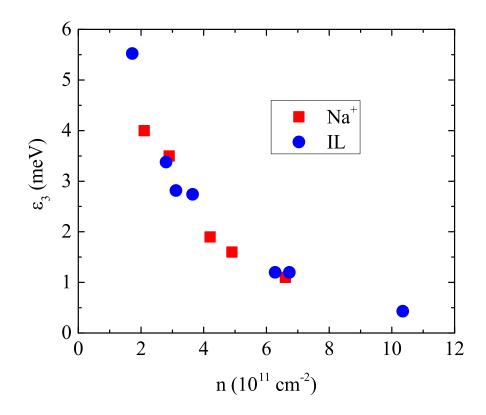

Figure 3.8a is a plot of the activation energy as a function of carrier density for the curves shown in the inset. In addition the results for Si, the activation energy taken from Table III in the review by Ando *et al.* for Na<sup>+</sup> surface states were added for comparison.[26] In the experiments by Fowler, the carrier density was determined as the number of Na<sup>+</sup>at the Si/SiO<sub>2</sub> interface. In the IL experiment, the carrier density was determined by integrating the leakage current which is a measure of the number of ions that moved to the SiO<sub>2</sub> surface. The activation energies as a function of carrier density overlap between the two experiments.

Plotted in Fig 3.9 is prefactor  $\sigma_3$  as a function of the inverse root of the carrier density. The prefactor was determined form the intercept of the linear fits to the data