### QUADRATURE FREQUENCY SYNTHESIS FOR WIDEBAND WIRELESS TRANSCEIVERS

### A DISSERTATION

### SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA

$\mathbf{B}\mathbf{Y}$

MOHAMMAD A. ELBADRY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor of Philosophy

PROF. RAMESH HARJANI

May, 2014

© MOHAMMAD A. ELBADRY 2014 ALL RIGHTS RESERVED

### Acknowledgements

This work is the culmination of more than nine years of work and study in the Analog/RF integrated circuits field, during which I was priveleged to work with, and learn from, many brilliant engineers and exceptional professors.

I am deeply indebted to my professors in the IC Lab, Ain Shams University, who introduced me to the fascinating world of integrated circuit design: Prof. Khaled Sharaf who laid down the basics of circuit design, frequency-response analysis, and PLL/ADC design basics, Prof. Emad Hegazi for introducing the basics of analog integrated circuits, and supervising my senior-year project, and Prof. Hani Ragai for his amazing course on integrated circuit fabrication, and his dedication to the IC Lab. I have also learnt a lot from my TAs: Essam Attalah, Ahmed Amer, Sameh Ibrahim, Mohamed Elnozahi, Michael Youssef, Mohyee Mikhemar, Amr Amin, Amr Elshazly and Karim Ragab.

During my few years of work in Si-Ware Systems, I had the honour of working under Dr. Ayman Elsayed, from whom I have learnt a lot about real-world analog design. I also thank him for overseeing my Master's thesis work, in spite of not having his name officially on it due to an administrative error. I also feel lucky to have had the chance to work under Ayman Ahmed, who was my first manager, and Dr. Amr Hafez. I am also very grateful to Dr. Hisham Haddara for providing me the chance to work in Si-Ware Systems, which has added a lot to me, on the technical as well as the personal levels. I was also blessed with the work relationship, and friendship, of many brilliant engineers at Si-Ware Systems: Botros Iskander, Nabil Sinoussi, Mohamed Mamdouh, Tarek Elesseily, Bassem Zaki, Ahmed Elshennawy, Ahmed Helmy, Ahmed Safwat, Hussein Ali, Ahmed Shaban, Mohamed Mohsen, Mohamed Samir, Ahmed Elkholy, Ahmed Mokhtar, Ayman Amin and Ahmed Ashry.

I am indebted to Prof. Harjani for his guidance in my PhD work. He was always supportive throughout my PhD, pushing me all the way to success, in spite of my faliures along the way. I am also grateful to Savita Harjani, for her kindness and hospitality. It was always a delight having dinner at the Harjani's, with their warm hospitality and meticulously prepared food.

I was blessed with lots of great lab-mates. I am grateful to my seniors: Narasimha Lanka for helping me through my first designs in the lab, Satwik Patnaik for all the help and support throughout my first tape-out, Bodhisatwa Sadhu for teaching me EM-simulation and helping me debug and correct my first chip, Martin Sturm for all the PCB and testing support and expertise, and Taehyoun Oh for graciously helping me out with my first tape-out. I am also indebted to Sudhir Kudva, a dear friend and a brilliant lab-mate, for all his help in the desperate times of tape-out deadlines and all the non-technical "tips & tricks".

I am equally grateful to my juniors: Sachin Kalia, to whom I owe most of my coauthored papers, for being a great friend and for the many hours of technical discussions, and Ashutosh Mehra for being a great friend and lab-mate. I also had the privelege of helping Mustafijur Rahman with some of his RF work, and of meeting Rakesh Palani who is one of the most passionate analog designers I have ever known.

I learnt a lot during my two internships at Broadcom and Texas Instruments. Thanks to Hui Pan and Derek Tam of Broadcom, I was exposed to the intricacies of Gigabit Ethernet transceivers. At Texas Instruments' Kilby lab, I had the chance to witness cutting-edge next-generation wireless technology. I am very grateful to my manager at Kilby, Bob Payne, for all his help, guidance, and giving me the chance to work on a couple of research ideas that developed into two patent applications. I am equally grateful to my mentor at Kilby, Gerd Schuppener, for giving me the chance to explore some of the interesting millimeter-wave designs at Kilby and for all his technical help. I was also lucky to meet, and learn from, some of the exceptional people at Kilby labs: Swaminathan Sankaran, Brad Kramer and Juan to name a few.

Finally, I am indebted to my parents for instilling the love of science and the passion for excellence into me. Their help and moral support was invaluable to the accomplishment of this feat. My brother and my sister-in-law have always been kind to me during my short visits back to Egypt. And finally, my sweet little nephew and niece - Omar and Judy - have always brought around joy and mischief during my stays in Egypt.

I sincerely thank you all!

To my dear parents... To Dalia

### Abstract

In this thesis, three different techniques pertinent to quadrature LO generation in high data rate and wideband RF transceivers are presented. Prototype designs are made to verify the performance of the proposed techniques, in three different technologies: IBM 130nm CMOS process, TSMC 65nm CMOS process and IBM 32nm SOI process. The three prototype designs also cover three different frequency bands, ranging from 5GHz to 74GHz.

First, an LO generation scheme for a 21 GHz center-frequency, 4-GHz instantaneous bandwidth channelized receiver is presented. A single 1.33 GHz reference source is used to simultaneously generate 20 GHz and 22 GHz LOs with quadrature outputs. Injection locking is used instead of conventional PLL techniques allowing low-power quadrature generation. A harmonic-rich signal, containing both *even and odd harmonics* of the input reference signal, is generated using a digital pulse slimmer. Two ILO chains are used to lock on to the 10<sup>th</sup> and 11<sup>th</sup> harmonics of the reference signal generating the 20 GHz and the 22 GHz quadrature LOs respectively. The prototype design is implemented in IBM's 130 nm CMOS process, draws 110 mA from a 1.2 V supply and occupies an active area of 1.8 mm<sup>2</sup>.

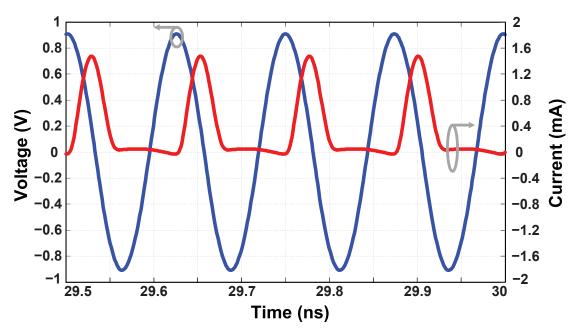

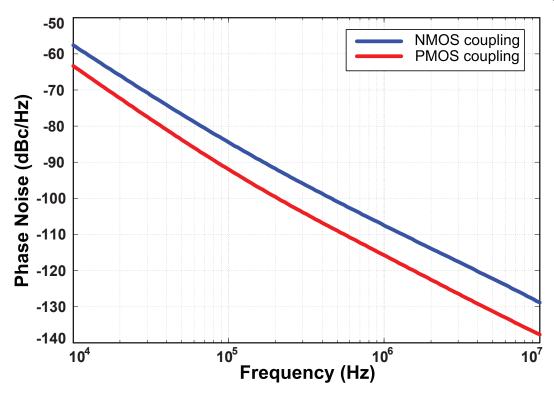

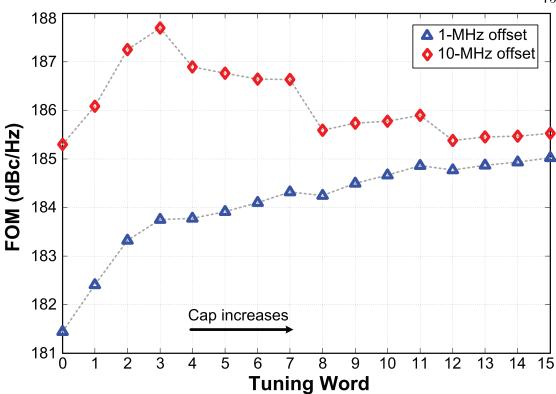

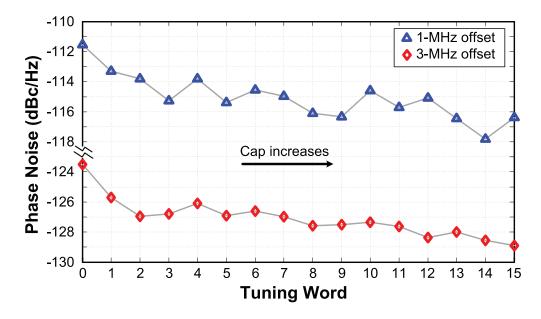

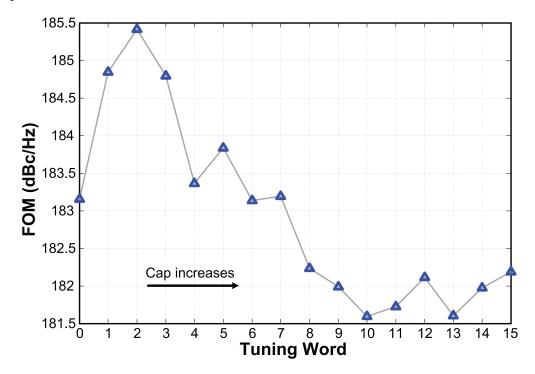

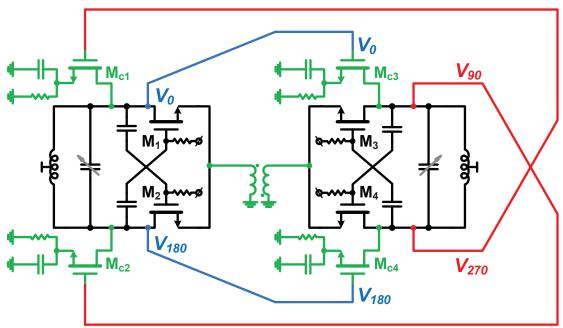

Next, a wide-tuning range QVCO with a novel complimentary-coupling technique is presented. By using PMOS transistors for coupling two VCOs with NMOS  $g_m$ -cells, it is shown that significant phase-noise improvement (7-9 dB) can be achieved over the traditional NMOS coupling. This breaks the trade-off between quadrature accuracy and phase-noise, allowing reasonable accuracy without a significant phase-noise hit. The proposed technique is frequency-insensitive, allowing robust coupling over a wide tuning range. A prototype design is done in TSMC 65nm process, with 4-bits of discrete tuning spanning the frequency range 4.6-7.8 GHz (52% FTR) while achieving a minimum FOM of 181.4dBc/Hz and a minimum FOMT of 196dBc/Hz.

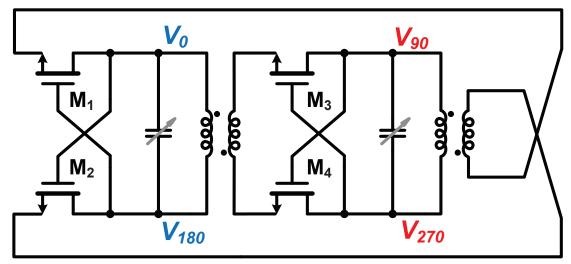

Finally, a wide tuning-range millimeter wave QVCO is presented that employs a modified transformer-based super-harmonic coupling technique. Using the proposed technique, together with custom-designed inductors and metal capacitors, a prototype is designed in IBM 32nm SOI technology with 6-bits of discrete tuning using switched capacitors. Full EM-extracted simulations show a tuning range of 53.84GHz to 73.59GHz, with an FOM of 173 dBc/Hz and an FOMT of 183 dBc/Hz. With 19.75GHz of tuning range around a 63.7GHz center frequency, the simulated FTR is 31%, surpassing all similar designs in the same band. A slight modification in the tank inductors would enable the QVCO to be employed in multiple mm-Wave bands (57-66 GHz communication band, 71-76 GHz E-band, and 76-77 GHz radar band).

# Contents

| A        | cknov     | wledge  | ements                             |  |  | i  |

|----------|-----------|---------|------------------------------------|--|--|----|

| A        | bstract v |         |                                    |  |  |    |

| Li       | st of     | Table   | S                                  |  |  | x  |

| Li       | st of     | Figur   | es                                 |  |  | xi |

| 1        | Intr      | oducti  | ion                                |  |  | 1  |

|          | 1.1       | Freque  | ency Channelization                |  |  | 3  |

|          | 1.2       | Softwa  | are Defined Radio                  |  |  | 6  |

|          | 1.3       | Organ   | nization                           |  |  | 7  |

| <b>2</b> | Cha       | anneliz | zed ILO                            |  |  | 8  |

|          | 2.1       | Introd  | luction                            |  |  | 8  |

|          | 2.2       | System  | m Overview                         |  |  | 11 |

|          |           | 2.2.1   | Pulse Slimmer                      |  |  | 11 |

|          |           | 2.2.2   | Bandpass Filter                    |  |  | 13 |

|          |           | 2.2.3   | Injection Locked Frequency Divider |  |  | 16 |

|          |           | 2.2.4   | Injection Locked Frequency Tripler |  |  | 16 |

|          | 2.3       | Circui  | its                                |  |  | 16 |

|   |                        | 2.3.1 Pulse Slimmer                                                                                                                                     | ĵ        |

|---|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|   |                        | 2.3.2 Bandpass Filter                                                                                                                                   | 3        |

|   |                        | 2.3.3 Injection Locked Frequency Divider                                                                                                                | 3        |

|   |                        | 2.3.4 Injection Locked Frequency Tripler                                                                                                                | 6        |

|   |                        | 2.3.5 Chip Floorplan                                                                                                                                    | 0        |

|   | 2.4                    | EM design methodology                                                                                                                                   | 3        |

|   | 2.5                    | PVT considerations                                                                                                                                      | 6        |

|   | 2.6                    | Measurements and Discussion                                                                                                                             | 7        |

|   | 2.7                    | Conclusions                                                                                                                                             | 7        |

| 3 | Wie                    | leband QVCO 49                                                                                                                                          | <b>)</b> |

|   | 3.1                    | Introduction                                                                                                                                            | 9        |

|   | 3.2                    | Prior art                                                                                                                                               | 3        |

|   |                        | 3.2.1 Phase-shift based                                                                                                                                 | 3        |

|   |                        | 3.2.2 Super-harmonic-coupling based                                                                                                                     | 7        |

|   |                        | 3.2.3 Alternative direct-coupling                                                                                                                       | 1        |

|   | 3.3                    | Proposed architecture                                                                                                                                   | 4        |

|   |                        | 3.3.1 Motivation $\ldots \ldots \ldots$ | 4        |

|   |                        | 3.3.2 Core VCO choice                                                                                                                                   | 5        |

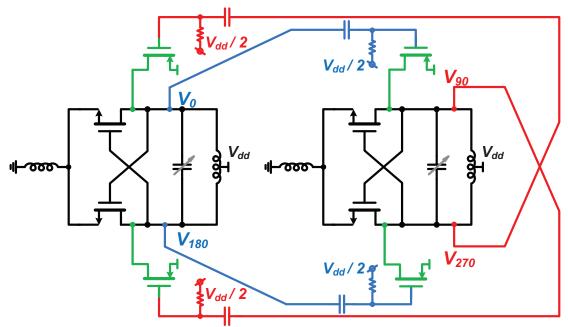

|   |                        | 3.3.3 Full QVCO                                                                                                                                         | 6        |

|   | 3.4                    | Prototype design                                                                                                                                        | 0        |

|   |                        | 3.4.1 Measurement results                                                                                                                               | 6        |

|   | 3.5                    | Conclusions                                                                                                                                             | 2        |

| 4 | $\mathbf{m}\mathbf{m}$ | -Wave QVCO 84                                                                                                                                           | 1        |

|   | 4.1                    | Introduction                                                                                                                                            | 4        |

|   | 4.2                    | Motivation                                                                                                                                              | 5        |

| R | References 103 |        |                             |   | 103 |

|---|----------------|--------|-----------------------------|---|-----|

|   | 5.1            | Future | e Work                      | • | 101 |

| 5 | $\mathbf{Res}$ | earch  | Contributions & Future Work |   | 100 |

|   |                | 4.3.2  | Measurements                | • | 98  |

|   |                | 4.3.1  | Prototype Design            | • | 90  |

|   | 4.3            | Propo  | sed QVCO                    |   | 88  |

# List of Tables

| 2.1 | Current consumed per block        | 38 |

|-----|-----------------------------------|----|

| 2.2 | Phase noise performance           | 41 |

| 3.1 | Measured QVCO performance summary | 82 |

| 3.2 | Comparison with literature        | 83 |

| 4.1 | Performance Comparison            | 97 |

# List of Figures

| 1.1  | Evolution of the cell-phone [1]                                                          | 2  |

|------|------------------------------------------------------------------------------------------|----|

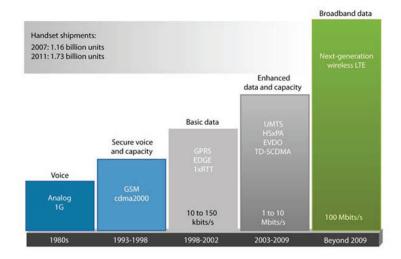

| 1.2  | Evolution of the cellular data rates [2]                                                 | 2  |

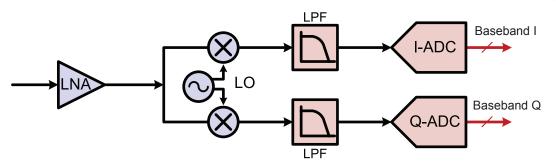

| 1.3  | A typical direct-conversion receiver                                                     | 3  |

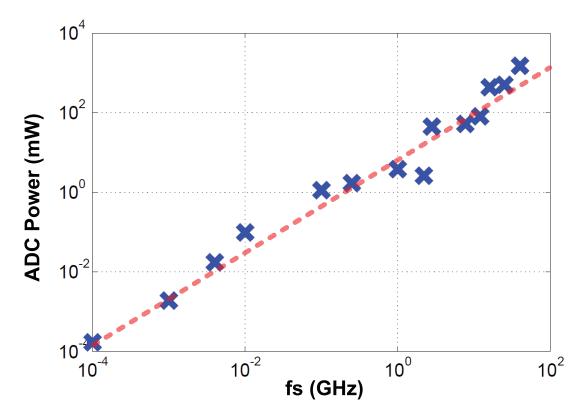

| 1.4  | ADC power consumption versus sampling rate $(f_s)$                                       | 4  |

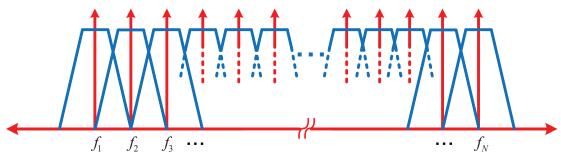

| 1.5  | Frequency channelization                                                                 | 5  |

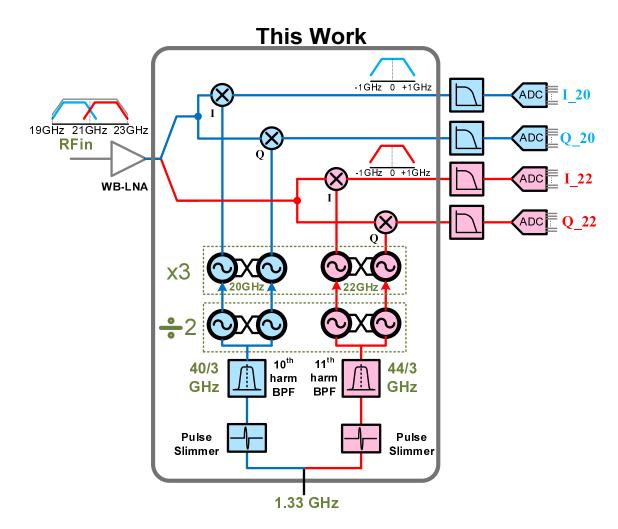

| 2.1  | Simultaneous dual channel 19GHz - 23GHz receiver                                         | 9  |

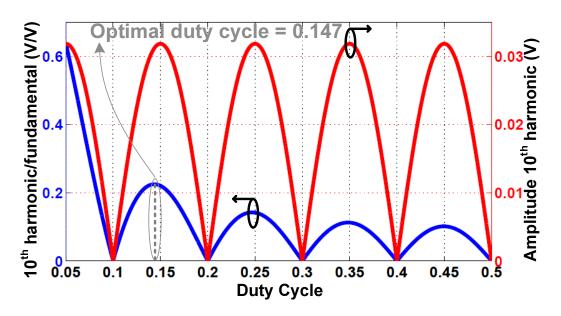

| 2.2  | Amplitude of $10^{th}$ harmonic and ratio of $10^{th}$ harmonic to fundamental           | 12 |

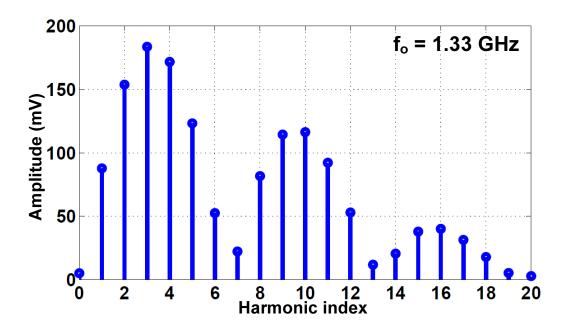

| 2.3  | Pulse slimmer output spectrum (SpectreRF <sup>®</sup> simulation) $\ldots \ldots \ldots$ | 13 |

| 2.4  | BPF output spectrum (SpectreRF <sup>®</sup> simulation) $\ldots \ldots \ldots \ldots$    | 14 |

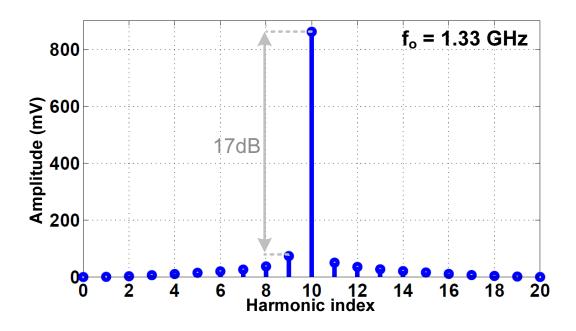

| 2.5  | Digital pulse slimmer (PSLIM) circuit diagram                                            | 15 |

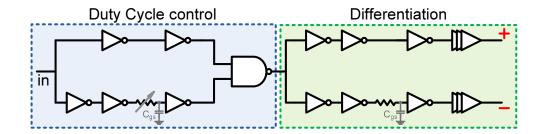

| 2.6  | Variable delay versus control voltage                                                    | 15 |

| 2.7  | Pulse-slimmer output                                                                     | 17 |

| 2.8  | Bandpass Filter (BPF) - bias details omitted                                             | 19 |

| 2.9  | Simulated gain of BPF (under equal power consumption) $\ldots \ldots \ldots$             | 20 |

| 2.10 | Simulated quality factor of conventional and ILO-based BPF $\ . \ . \ .$ .               | 21 |

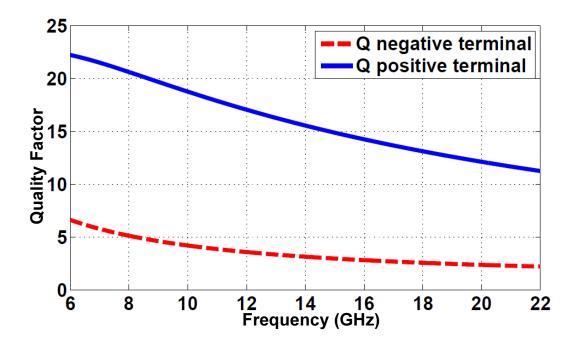

| 2.11 | Varactor quality factor at negative and positive terminals                               | 22 |

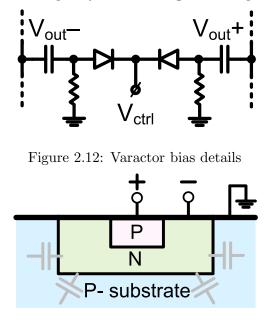

| 2.12 | Varactor bias details                                                                    | 22 |

| 2.13 | Structure of hyper-abrupt PN-junction varactor (parasitics highlighted)                  | 22 |

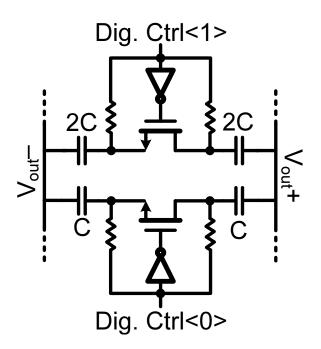

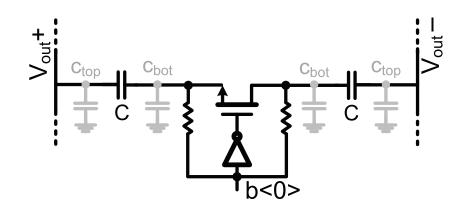

| 2.14 | Two-bit capacitor bank details                                                           | 23 |

| 2.15 | Injection Locked Frequency Divider (ILFD) - bias details omitted                                                                                                         | 25 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.16 | Injection switch bias details                                                                                                                                            | 26 |

| 2.17 | ILFD's lock range and output amplitude versus switch bias $\ldots \ldots$                                                                                                | 27 |

| 2.18 | ILFD phase and amplitude mismatch - Monte Carlo simulations $\ . \ . \ .$                                                                                                | 28 |

| 2.19 | Injection Locked Frequency Multiplier (ILFM) - bias details omitted $\ .$ .                                                                                              | 29 |

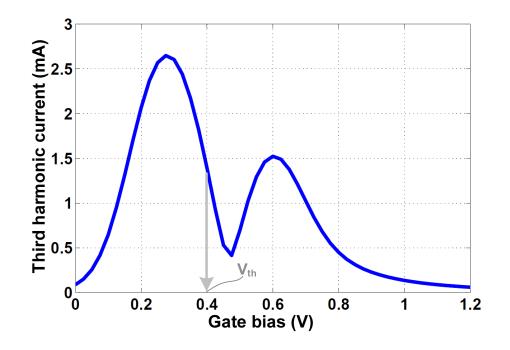

| 2.20 | $\operatorname{SpectreRF}^{\ensuremath{\mathbb{R}}}$ simulation of the third harmonic current in injection pair $% \operatorname{SpectreRF}^{\ensuremath{\mathbb{R}}}$ . | 30 |

| 2.21 | ILFM phase and amplitude mismatch - Monte Carlo simulations $\ . \ . \ .$                                                                                                | 31 |

| 2.22 | Chip floorplan                                                                                                                                                           | 32 |

| 2.23 | EM design methodology flow graph                                                                                                                                         | 35 |

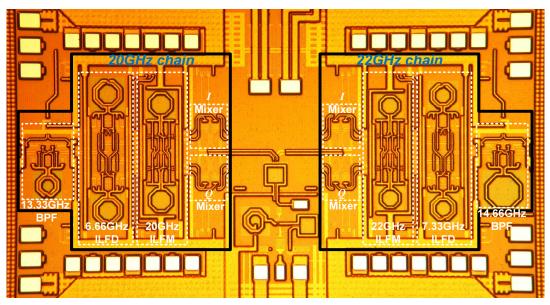

| 2.24 | Chip Micrograph                                                                                                                                                          | 38 |

| 2.25 | Test Setup                                                                                                                                                               | 39 |

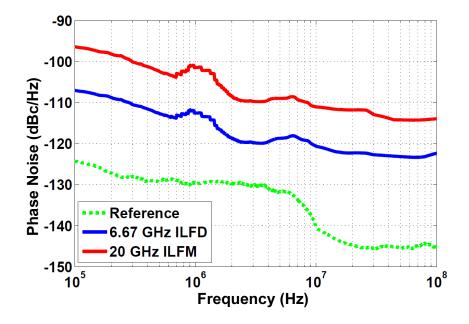

| 2.26 | Measured phase noise along the 20 GHz chain                                                                                                                              | 40 |

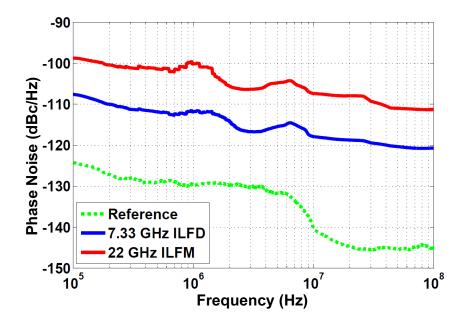

| 2.27 | Measured phase noise along the 22 GHz chain                                                                                                                              | 40 |

| 2.28 | Phase noise model                                                                                                                                                        | 41 |

| 2.29 | Simulated output-referred phase noise contributions at $6.67~\mathrm{GHz}$ ILFD .                                                                                        | 42 |

| 2.30 | Spurious performance of the 20 GHz LO chain                                                                                                                              | 43 |

| 2.31 | Spurious performance of the 22 GHz LO chain                                                                                                                              | 44 |

| 2.32 | Generation of $\pm 666$ MHz spurs in 22 GHz LO chain $\ldots \ldots \ldots \ldots$                                                                                       | 45 |

| 2.33 | Measured downconverted quadrature outputs of the 20 GHz LO $$                                                                                                            | 46 |

| 2.34 | Measured downconverted quadrature outputs of the 22 GHz LO $~$                                                                                                           | 47 |

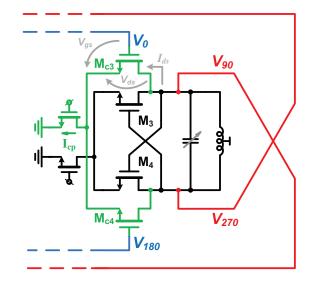

| 3.1  | Basic LC QVCO                                                                                                                                                            | 50 |

| 3.2  | One LC VCO from the QVCO structure with voltages and currents of                                                                                                         |    |

|      | injection transistors highlighted                                                                                                                                        | 51 |

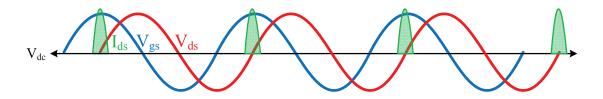

| 3.3  | Gate voltage, drain voltage and drain current of transistors $M_{c3}$ and $M_{c4}$                                                                                       | 52 |

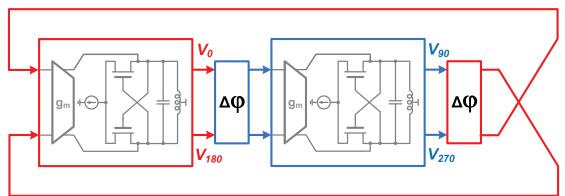

| 3.4  | Block diagram of phase-shift based LC QVCO                                                                                                                               | 53 |

| 3.5  | Phase-shift based QVCO using R-C degeneration                                                                                                                            | 54 |

| 3.6          | Phase-shift based QVCO using resistors in coupling path                                                            | 55       |

|--------------|--------------------------------------------------------------------------------------------------------------------|----------|

| 3.7          | Phase-shift QVCO techniques using (a) current addition and capacitive                                              |          |

|              | degeneration and (b) frequency-independent injection $\ldots \ldots \ldots$                                        | 56       |

| 3.8          | Generalized super-harmonic-coupling based LC QVCO                                                                  | 57       |

| 3.9          | Transformer based super-harmonic coupled QVCO                                                                      | 58       |

| 3.10         | Simplified schematic of frequency doubler based super-harmonic QVCO                                                | 59       |

| 3.11         | Simplified schematic of super-harmonic QVCO based on cross-coupled                                                 |          |

|              | tail transistors                                                                                                   | 60       |

| 3.12         | Top series-coupled LC QVCO                                                                                         | 61       |

| 3.13         | Back-gate coupled LC QVCO                                                                                          | 62       |

| 3.14         | Simplified schematic of transformer-coupled QVCO                                                                   | 63       |

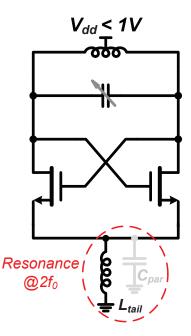

| 3.15         | Core VCO for the proposed architecture                                                                             | 64       |

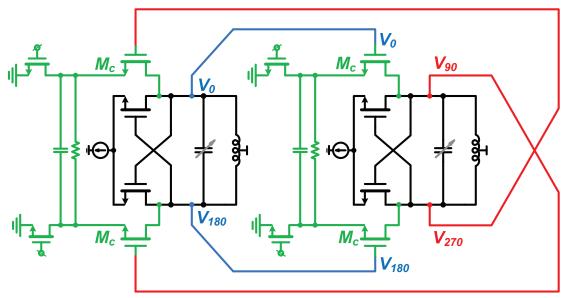

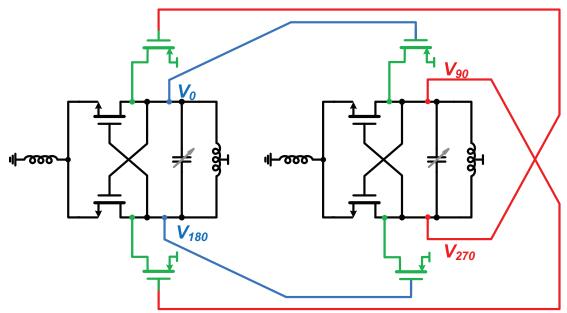

| 3.16         | Schematic of the proposed QVCO                                                                                     | 65       |

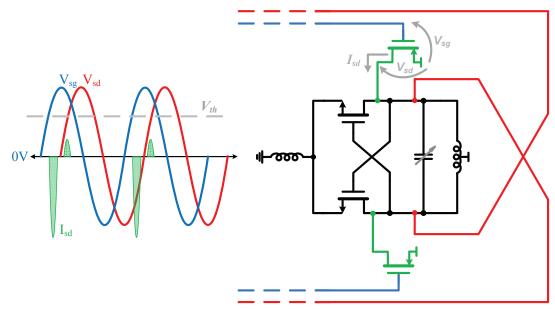

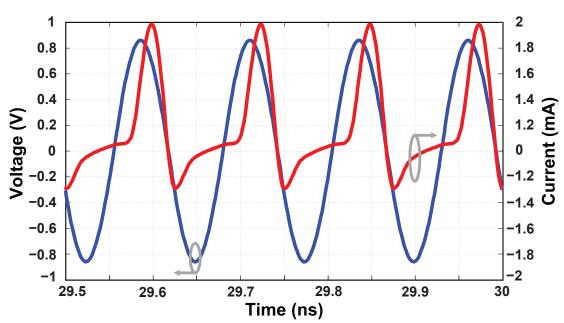

| 3.17         | Coupling transistor current and voltage waveforms for proposed architec-                                           |          |

|              | ture                                                                                                               | 66       |

| 3.18         | Simulated injection current and output voltage for PMOS coupling                                                   | 67       |

| 3.19         | Simulated injection current and output voltage for NMOS coupling                                                   | 68       |

| 3.20         | Phase-noise performance of PMOS and NMOS coupled QVCOs                                                             | 69       |

| 3.21         | Schematic of designed prototype with class-AB complimentary coupling                                               | 71       |

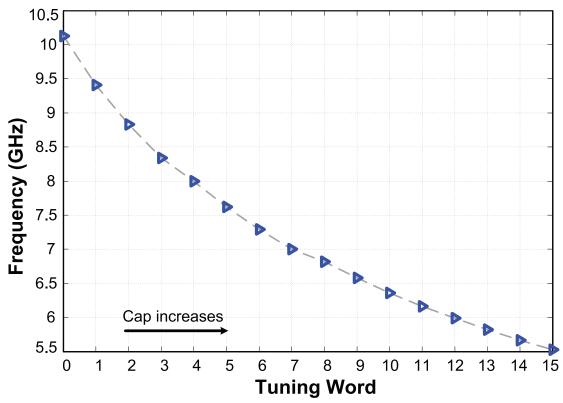

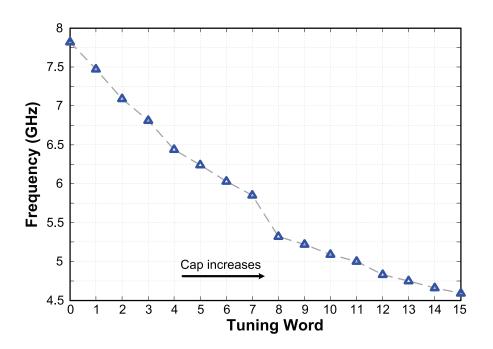

| 3.22         | Output frequency of the QVCO prototype versus tuning word                                                          | 72       |

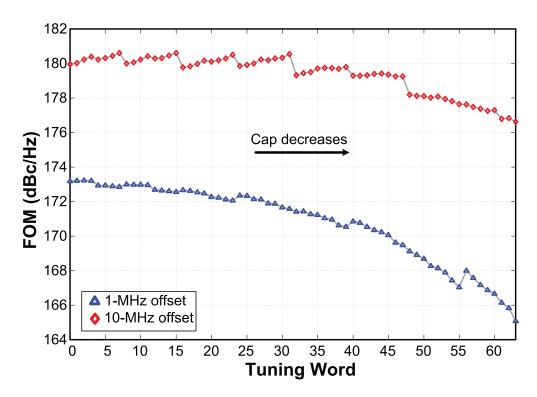

| 3.23         |                                                                                                                    |          |

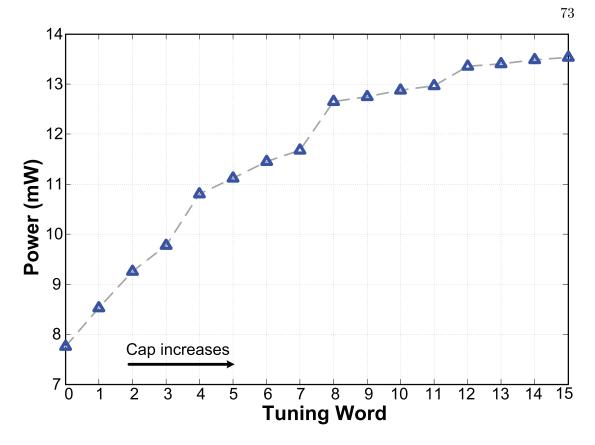

|              | Power consumption of the QVCO prototype versus tuning word                                                         | 73       |

| 3.24         | Power consumption of the QVCO prototype versus tuning word<br>Phase-noise of the QVCO prototype versus tuning word | 73<br>74 |

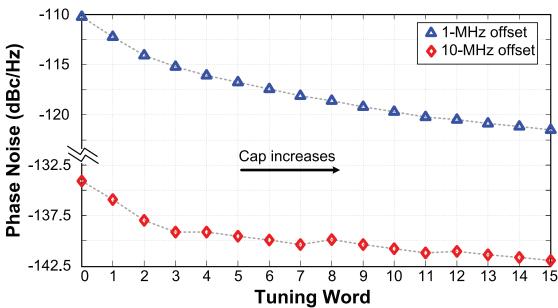

|              |                                                                                                                    |          |

| 3.25         | Phase-noise of the QVCO prototype versus tuning word                                                               | 74       |

| 3.25<br>3.26 | Phase-noise of the QVCO prototype versus tuning word                                                               | 74<br>75 |

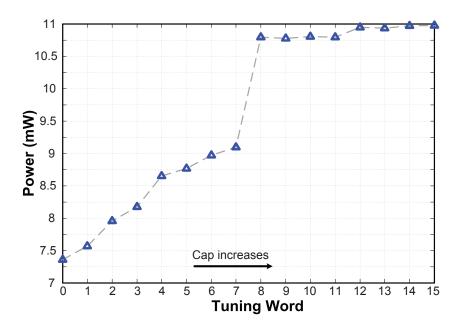

| 3.29 | Measured power consumption at the three tested supply voltages               | 79 |

|------|------------------------------------------------------------------------------|----|

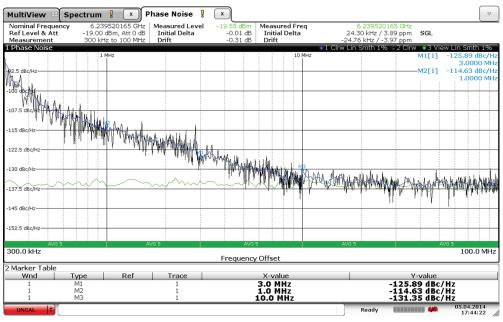

| 3.30 | Measured phase-noise at 0.5V supply, and tuning-word="5"                     | 80 |

| 3.31 | Measured phase-noise at 0.5V supply for 1MHz and 3MHz offsets                | 80 |

| 3.32 | Measured FOM at 0.5V supply for 3MHz offset                                  | 81 |

| 4.1  | Proposed millimeter-wave QVCO                                                | 87 |

| 4.2  | A single bit slice of the capacitor bank, and associated parasitics $\ldots$ | 89 |

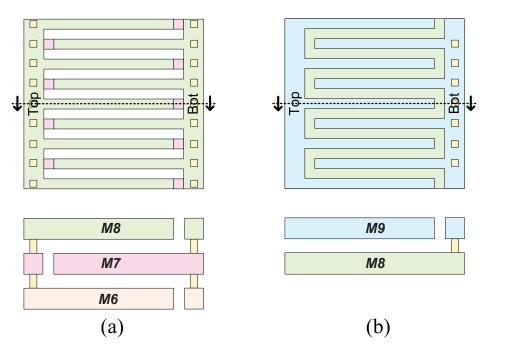

| 4.3  | Capacitor structures (a) MOM-capacitor and (b) Custom Capacitor $\ .$ .      | 91 |

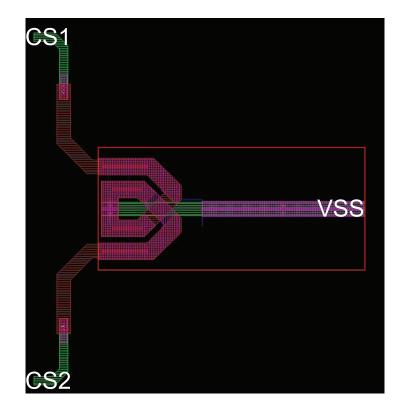

| 4.4  | Tail transformer layout                                                      | 92 |

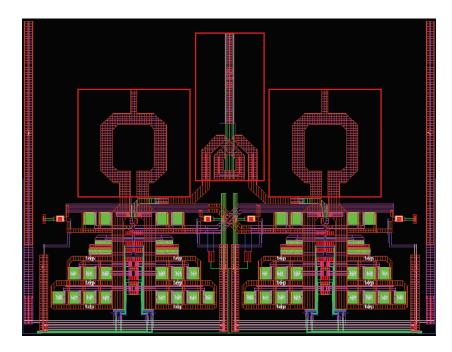

| 4.5  | Full layout of the proposed QVCO                                             | 93 |

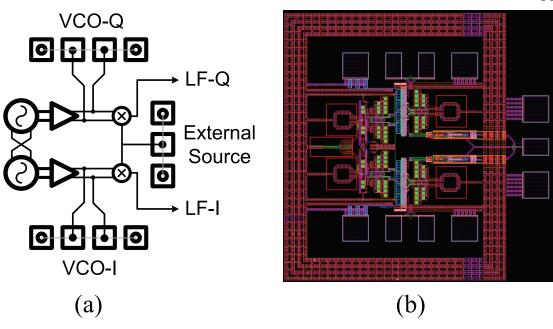

| 4.6  | Entire system (a) Block Diagram, and (b) Layout                              | 94 |

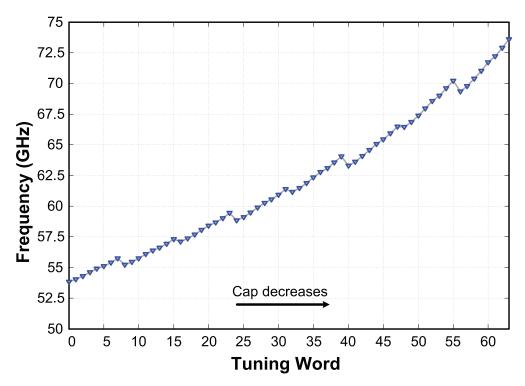

| 4.7  | Output frequency of the proposed QVCO versus tuning word $\ldots \ldots$     | 95 |

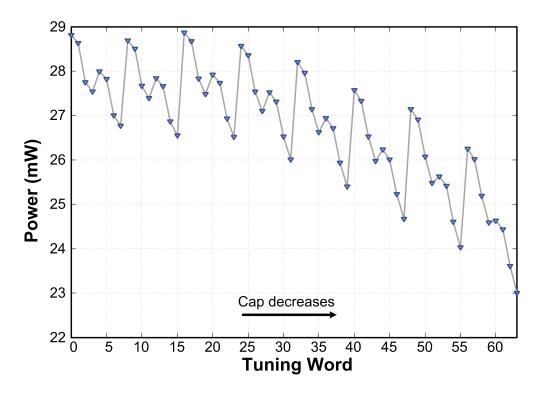

| 4.8  | Power consumption of the proposed QVCO versus tuning word $\ldots$ .         | 96 |

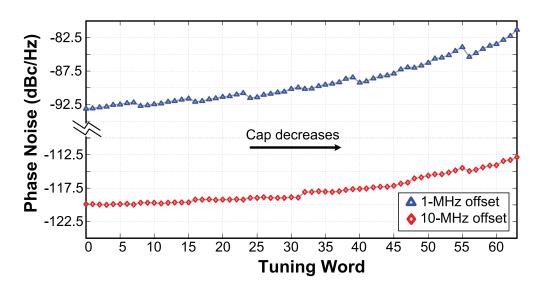

| 4.9  | Phase-noise of the proposed QVCO                                             | 96 |

| 4.10 | Figure of merit of the proposed QVCO                                         | 97 |

| 4.11 | Chip micrograph                                                              | 98 |

### Chapter 1

## Introduction

With the proliferation of wireless technology in the last two decades, a plethora of new devices and applications have revolutionized our everyday life. Portable devices with wireless connectivity have become ubiquitous, while continuously getting thinner and lighter (Fig. 1.1). Moreover, wireless data rates have increased rapidly from the slow rates of the earliest cellular networks of the late nineties to the dazzling speeds of the next generation 4G-LTE (Fig. 2). In addition to the increased speeds, the wireless capabilities have also increased. Modern smartphones and tablets have GPS (for navigation), Bluetooth (for wireless headsets and file transfer), WiFi (for wireless internet), GSM and CDMA (for phone calls and texting), and FM radio. And some even have wireless NFC (Near Field Communication) capabilities allowing us to pay for drinks and food on the go with cell phones.

These advances, however, do not come for free. Higher data rates come with the cost of higher power consumption, adversely affecting battery life of portable devices. This is further aggravated by the small form factors which don't allow large batteries. Additionally, the multiple radios needed require the use of a large number of integrated circuit chips. This, in turn, makes it more difficult to reduce form factors and power

Figure 1.1: Evolution of the cell-phone [1]

consumption. With the widespread use of high-definition multi-media, data rates are projected to increase and higher speed wireless standards (such as WirelessHD [3]) are expected to emerge.

Figure 1.2: Evolution of the cellular data rates [2]

In high data rate wireless receivers, a major power hog is the analog-to-digital converter (ADC) (which is responsible for converting radio signals at the antenna into digital ones-and-zeros that can be shown on the screen or heard via the speaker). One

Figure 1.3: A typical direct-conversion receiver

way to reduce the power consumption in such receivers is to split the incoming signal into a number of parallel streams (channelization), each with a smaller data rate. The aggregate data rate remains the same, but the overall energy is reduced [4]. On the other hand, the number of chips can be reduced by incorporating programmability into the radio design, allowing a single radio to be used with multiple wireless standards, i.e., by designing software defined radios (SDR). An important component of an SDR is wide tuning range quadrature oscillator, that enables quadrature LO generation for direct downconversion in different bands.

This work presents a quadrature LO generation scheme for a high data rate (4GHz instantaneous bandwidth) wireless receiver, as well as wide tuning range quadrature VCO design for SDR-type applications in both the lower GHz range (5-10GHz) and millimeter-wave range (50-70GHz).

### **1.1** Frequency Channelization

Fig. 1.3 shows a typical direct-conversion receiver. A low-noise amplifier amplifies the input signal, which is passed on to quadrature mixers for downconversion. Quadrature mixing is typically done by using quadrature LO, although quadrature signal generation can be done as well. A low-pass filter follows the mixer, to filter out the higher frequency

Figure 1.4: ADC power consumption versus sampling rate  $(f_s)$

component. Finally, an ADC converts the downconverted and filtered data into digital for demodulation and post-processing. A major burden of the receiver linearity lies on the ADC, since it is the last block in the receiver and subject to large signal amplitudes specially in the presence of in-band blocker signals (the filter attenuates out-of-band blockers) [5]. Due to this linearity constraint, the ADC block usually has significant power consumption.

Unlike the RF front-end, the ADC power consumption rises exponentially with increased bandwidth. To illustrate this point, consider [6] which presents a GSM receiver with bandwidth of 200kHz, and [7] which presents a 60GHz WirelessHD receiver with

Figure 1.5: Frequency channelization

1GHz of bandwidth. Although the bandwidth of the WirelessHD receiver in [7] is 50times higher than the bandwidth of the GSM receiver in [6], the power consumption of the RF front-end in [7] is only 1.6 times higher than that in [6] (454mW for WirelessHD versus 235mW for GSM).

Fig. 1.4, on the other hand, shows the power consumption of ADCs versus their sampling rate based on the data in [8]. At each sampling rate, the ADC with the lowest power consumption at that sampling rate is chosen for the plot. Power versus sampling frequency  $(f_s)$  is, then, plotted on a Log-Log scale. As evident from Fig. 1.4, the power consumption increases exponentially with sampling rate  $(f_s)$ , i.e. Power  $\propto (f_s)^n$ . Fitting shows that  $n \approx 2$ ; a large power saving can be achieved by reducing the ADC sampling rate.

To maintain the overall bandwidth, while reducing the ADC sampling rate, frequency channelization can be employed as shown in Fig. 1.5. The signal bandwidth (BW) is divided into N different chunks, each of bandwidth  $\frac{BW}{N}$ . Hence, N different streams need to be digitized, requiring N ADCs each with a sampling rate  $\frac{f_s}{N}$  ( $f_s$  being the sampling frequency of the unchannelized signal). Hence, the ratio of the power consumption of the channelized ADCs  $P_c$  to the power consumption of a single ADC  $P_s$  can be given by:

$$\frac{P_c}{P_s} \approx \frac{N \times \left(\frac{f_s}{N}\right)^2}{f_s^2} = \frac{1}{N}$$

(1.1)

This means that the ADC power consumption can be reduced roughly N times by using channelization. Actual power savings will depend on the extra power consumed for performing channelization, as well as additional amplification that might be needed post-channelization. Nevertheless, significant power savings can be achieved through channelization. Moreover, channelization improves the RF receiver performance by making the system more interference tolerant [9]. For instance, if an interferer falls onto one of the channels, that channel and the associated ADC can be shut-off, reducing the data rate but without compromising the overall performance. If a single ADC is used, on the other hand, a single large interferer can overwhelm leading to a total signal blockage. A major challenge for channelization is the generation of multiple, uniformly spaced, quadrature LOs for downconversion of the different channels.

### 1.2 Software Defined Radio

Software-defined radio receivers allow a single front-end to be used for multiple standards, through software programmability and reconfigurability. While the original "Mitola" [10] SDR has an ADC directly following the antenna, allowing all downconversion and post-processing to be performed in digital domain, this approach is not practical with current technology. A more practical approach is to use a generic direct-conversion receiver, similar to that shown in Fig. 1.3, with programmable filters as well as programmable LO to cover multiple bands [11].

For very wideband programmability in the LO path (close to a decade), banks of VCOs are needed [11]. Quadrature VCOs allow the direct generation of quadrature LOs without requiring the VCO to operate at twice the desired operating frequency. Moreover, a wide tuning range in the QVCO allows less number of QVCOs in the bank, thus reducing area requirements, complexity, and design time.

### **1.3** Organization

This thesis is focused on quadrature LO generation techniques for wideband applications. "Wideband" includes instantaneous wide bandwidth system, as well as systems with smaller instantaneous bandwidth but have a wide range of center (or carrier frequencies).

Chapter 2 explores the use of injection locking techniques to generate simultaneous LOs for a channelized receiver. Two injection-locking based chains are designed to generate two simultaneous carriers at 20 and 22-GHz with quadrature outputs. This enables the operation of 4-GHz bandwidth receiver while relaxing the constraints on the required ADCs (as discussed in section 1.5).

Chapter 3 presents a wide tuning range QVCO which can be tuned from 5.5–10.1 GHz. A new simple and robust quadrature coupling technique is introduced that allows the wide tuning range to be achieved without sacrificing the VCO's Figure-Of-Merit (FOM). The proposed technique is compatible with low supply voltages of current technologies, and is frequency insensitive, relaxing the classical design constraints/trade-offs found in other QVCOs.

Chapter 4 presents a wide tuning range mm-Wave QVCO. Through merging two different coupling techniques, and by the use of custom-designed passives, a 19.75GHz tuning-range is achieved around a  $\approx$ 64GHz center frequency for a 31% tuning range. With a slight modification, the presented design can cover three different mm-Wave bands, possiblt allowing a mm-Wave SDR.

Finally, chapter 5 some of the research contributions of the presented work, as well as possible future work.

### Chapter 2

# Channelized ILO

### 2.1 Introduction

Wireless technology continually demands higher data rates. Increasing the bandwidth is the most effective way to achieve higher data rates [12]. Higher bandwidths, however, imply a high ADC clocking speed as well as a high dynamic range making the ADC power-hungry and difficult to design, if at all feasible. Frequency channelization is an effective way to alleviate this problem. It reduces the clocking speed of the ADC and also increases the immunity to narrow-band interferers, hence reducing the ADC dynamic range requirements [4]. Channelization also reduces the number of independent in-band signals, hence, reducing the peak to average power ratio (PAPR) [13], leading to an overall reduction in power consumption.

A channelized receiver, capable of achieving 4-GHz of instantaneous bandwidth, around a 21 GHz center frequency, is shown in Fig. 2.1. An external wideband LNA amplifies the entire band. The wideband signal is then down-converted into two 2-GHz channels using two sets of quadrature mixers, operating at 20 GHz and 22 GHz. Two sets of lowpass filters complete the channelization. The desired wideband signal

Figure 2.1: Simultaneous dual channel 19GHz - 23GHz receiver

can then be reconstructed digitally by upsampling each digitized stream by two and the use of digital reconstruction filters to account for the filters' phase and amplitude responses [4]. For a faithful reconstruction of the original signal, the two channels need to be phase synchronous.

A major challenge for the receiver in Fig. 2.1 is the generation of two phase synchronous quadrature LOs at 20 GHz and 22 GHz. PLL-based solutions such as [9] are ineffcient at mm-wave frequencies due to the need of power-hungry high frequency dividers and SSB mixers. Besides, parasitics become prominent at these frequencies, limiting mixer linearity and resulting in a large number of spurious components.

Injection locking is an alternative approach for LO generation in mm-wave designs [14–17]. Most designs, however, are aimed at a single LO. The design in [14] implements simultaneous LOs but it has two drawbacks: it is not capable of quadrature signal generation and it can only generate integer multiples of the reference signal. Hence, a different approach needs to be used for a more generalized solution.

This work addresses the use of injection locking to simultaneously generate 20 GHz and 22 GHz phase synchronous quadrature LOs using a single 1.33 GHz reference [18]. Compared to [19] this paper provides additional details on the circuit design, supporting simulation results, an overview on the electromagnetic (EM) design methodology and new measurement results. Section 2.2 provides an overall system overview. Section 2.3 presents circuit design details and simulation results. Section 2.4 discusses the EM design methodology used to ensure proper operation of high frequency oscillators. Section 2.5 discusses PVT considerations. Section 2.6 provides measurement results. Finally, Section 2.7 outlines overall conclusions.

### 2.2 System Overview

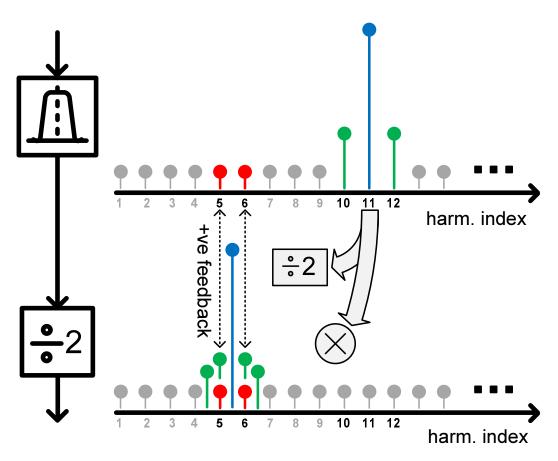

The LO system block diagram is shown in Fig. 2.1. For this specific design, only two channels are implemented. The system, however, can be extended to an arbitrary number of channels. The major limiting factor would be the diminishing amplitude of higher harmonics of the pulse-slimmer for a given process technology. Both even and odd harmonics of the input signal are used, unlike the designs in [20–22], making the system more flexible and allowing smaller channel spacing.

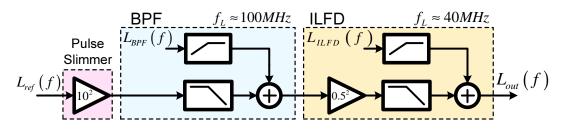

The  $n^{th}$  and  $(n+1)^{th}$  harmonics of the reference are generated using pulse-slimmers. The pulse-slimmers' outputs contains a large number of undesired harmonics as well. Hence, the pulse-slimmer in each chain is followed by a bandpass filter (BPF) to emphasize the harmonics of interest and suppress the undesired harmonics. Up to this point, only a single phase is present. To generate quadrature outputs, the BPF's output is then fed to an injection locked frequency divider (ILFD) which performs a divide-by-2 operation. The quadrature outputs are further multiplied using quadrature injection locked frequency multipliers (ILFM), generating  $\frac{3}{2}nf_{ref}$  and  $\frac{3}{2}(n+1)f_{ref}$  LOs. To generate 20 GHz and 22 GHz, n = 10 and  $f_{ref} = 1.33$  GHz are chosen. System aspects and architectural choices of each block are discussed further in the following subsections.

### 2.2.1 Pulse Slimmer

Each chain in Fig. 2.1 starts with a pulse-slimmer which generates all the harmonics of the input signal. The duty cycle of the pulse-slimmed signal is optimized in order to maximize the harmonics of interest. For a square wave with a duty cycle D and a unity peak-to-peak amplitude, the amplitude y of the  $n^{th}$  harmonic can be given by [23]:

$$y = D \frac{\sin(n\pi D)}{n\pi D} \tag{2.1}$$

For the  $n^{th}$  harmonic, there exists several values of D for which the amplitude is maximized. In fact, according to Eqn.(2.1) the absolute value of the amplitude of the  $n^{th}$  harmonic is periodic in D with a period  $D = \frac{1}{n}$ . Hence, an additional criterion is needed to select the optimum duty cycle. In this case, it is desirable to reduce the amplitude of the lower harmonics (which is naturally larger) as well. This reduces the amount of desensitization, caused by the undesired low-frequency (and high amplitude) harmonics, to the following stage (the BPF).

Based on these two criteria, a plot is made for the amplitude of the  $10^{th}$  harmonic and the ratio of the  $10^{th}$  harmonic to the fundamental versus D. As shown in Fig. 2.2, the maximum value of the  $10^{th}$  harmonic is periodic in D with a period of  $\frac{1}{10}$ . Nevertheless, the ratio of the  $10^{th}$  harmonic to the fundamental is higher for lower values of D. The absolute maximum of the ratio, which simultaneously corresponds to a maximum of the absolute value of the harmonic, occurs for  $D \approx \frac{1}{20}$ . This value of D is too small to be realized practically, hence the next higher value (highlighted in Fig. 2.2) is chosen. In a practical scenario, a value of D ranging from  $\frac{1}{8}$  to  $\frac{1}{6}$  can be used. This range of D is also usable for the other chain n = 11. This means that a single pulse slimmer can be used for both chains. However, in our design, chip floorplan considerations lead to the use of two pulse-slimmers (one for each chain) as discussed in Section 2.3.5.

In addition to duty cycle optimization, a differentiator is added after the pulse slimmer to further enhance higher harmonics and suppress lower ones. The circuit implementation details of the slimmer and the differentiator are discussed in Section 2.3.1.

Figure 2.3: Pulse slimmer output spectrum (SpectreRF<sup>®</sup> simulation)

### 2.2.2 Bandpass Filter

The techniques discussed in Section 2.2.1 help reduce the amplitude of the undesired harmonics. Nevertheless, the amplitude of lower harmonics remains higher than the desired harmonics. Fig. 2.3 shows the output harmonics of the pulse slimmer used in the 20 GHz chain as predicted by  $\text{SpectreRF}^{\text{(R)}}$  simulations. It can be clearly seen

Figure 2.4: BPF output spectrum (SpectreRF<sup>®</sup> simulation) that the harmonics close to the fundamental are 2-3 times higher than the desired  $10^{th}$ harmonic. In the absence of a BPF, this would have an adverse effect on the ILFD. The high-amplitude low-frequency harmonics would saturate the input  $g_m$  stage of the ILFD, desensitizing it with respect to the desired harmonic. This, in turn, results in a limited lock range and hence higher phase noise [24] and lower process tolerance. In the presence of the BPF, on the other hand, the low frequency harmonics are highly suppressed as shown in Fig. 2.4 (SpectreRF<sup>®</sup> simulations). Unlike the BPF in [20], an active injection-locking based BPF is used in this design. This has the advantage of higher gain at the frequency of interest, as well as higher Q for the filtering action with a lower power consumption (the  $10^{th}$  harmonic is amplified by a factor of 7 and the highest harmonic is 17dB below desired signal). The drawback, however, is the possibility for higher phase noise due to the intrinsic phase noise of the injection-locked oscillator (ILO). The output phase noise of a conventional BPF is approximately the same as the

input's phase noise. With an injection-locked BPF, however, additional phase noise is added by the oscillating core. Nevertheless, with proper design the additional phase noise can be made negligible while retaining the high gain and high Q advantages [24]. A more detailed comparison between conventional and injection-locked based BPF is provided in Section 2.3.2.

Figure 2.5: Digital pulse slimmer (PSLIM) circuit diagram

Figure 2.6: Variable delay versus control voltage

#### 2.2.3 Injection Locked Frequency Divider

Following the BPF, an injection-locked frequency divider similar to the one in [20] is used. The injection method, however, is different than the one in [20]. This is discussed in detail in Section 2.3.3.

An ILFD is used for quadrature generation to get good phase accuracy [20, 25, 26] without the use of multi-stage polyphase filters (which would result in signal attenuation [27]). It is to be noted that the ILFD in each chain operates at one third the final LO frequency. A similar divide-by-2 scheme for quadrature generation in a PLL would have required operation at *twice the final LO frequency*. The suggested scheme, hence, provides a more feasible solution with a lower power consumption.

### 2.2.4 Injection Locked Frequency Tripler

The final stage in each chain is an injection-locked frequency tripler. The tripler takes I and Q injection inputs and generates I and Q outputs at three times the input frequency [28]. Circuit design details of the multiplier are presented in Section 2.3.4.

### 2.3 Circuits

In this section, the circuit details of each of the synthesizer chain blocks are discussed and relevant simulation results are presented.

#### 2.3.1 Pulse Slimmer

One of the key features of the proposed synthesizer architecture is that it makes use of both the even and odd harmonics of the reference clock signal. As discussed in Section 2.2.1, the  $10^{th}$  and  $11^{th}$  harmonics have to be maximized while suppressing the other unwanted harmonics as much as possible. This is achieved by a two-stage,

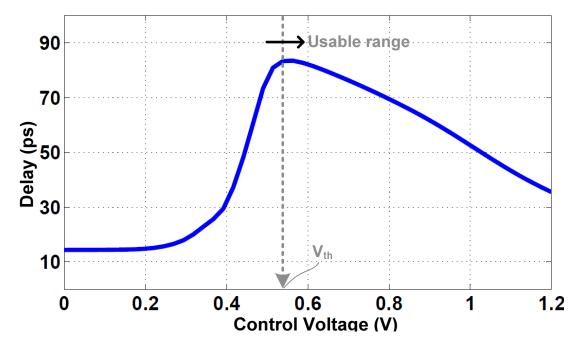

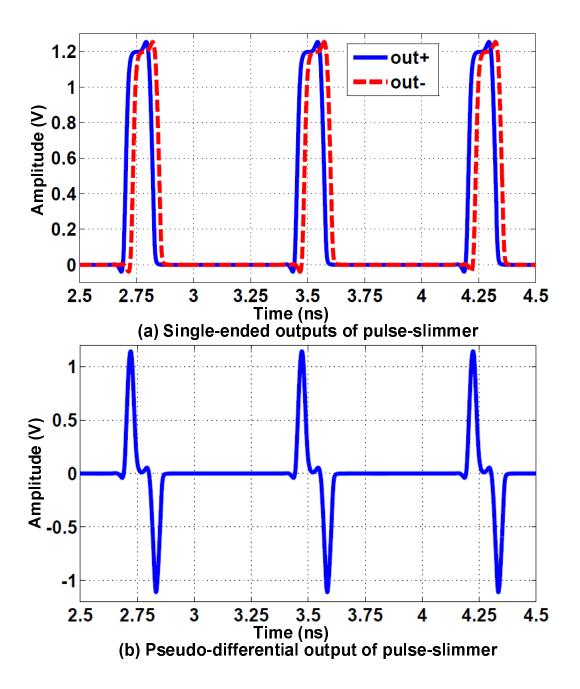

Figure 2.7: Pulse-slimmer output

semi-digital design as shown in Fig. 2.5.

The first stage is a duty cycle control stage; it converts the input 50% duty cycle clock to the optimal value discussed in Section 2.2.1 ( $\frac{1}{6}$  to  $\frac{1}{8}$ ). This is done by NAND'ing two paths with a one inverter delay difference. Since the required delay is slightly higher, additional fine delay is added by means of a MOS resistor. This delay can be controlled off-chip. In this process, one inverter delay amounts to around 26 ps; the variable delay can be changed from 35 ps to 83 ps as shown in Fig. 2.6.

The second stage performs two functions: it acts as a discrete-time differentiator, and it converts the single-ended signal to a pseudo-differential signal. This is done by splitting the signal into two paths with equal number of inverters. One of the two paths, however, has an additional small delay implemented by a fixed MOS resistor (the two output signals are shown in Fig. 2.7 (a)). Hence, the pseudo-differential output takes the form  $(1 - z^{-1}) s(t)$ , which is a differentiated version of the input signal s(t). Here the  $z^{-1}$  is the delay difference between the two paths. Combining this with the inherent low-pass nature of the chain results in an overall bandpass response as evident from Fig. 2.7(b).

#### 2.3.2 Bandpass Filter

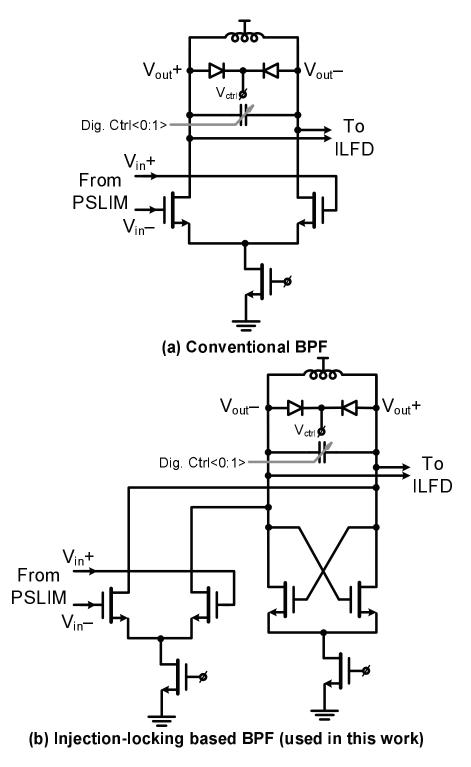

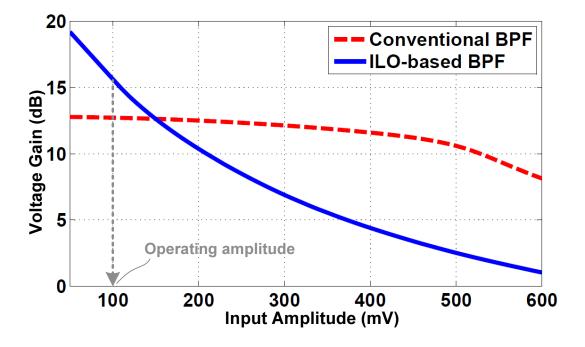

As discussed in Section 2.2.2, an active injection-locking based bandpass filter is used in this design. Fig. 2.8 shows the schematics of a conventional bandpass filter and the injection-locking based bandpass filter used in this work. Under free-running conditions, the ILO's amplitude ( $V_{osc}$ ) has a finite value. Once locked, the output amplitude remains the same creating an effective gain of  $V_{osc}/V_{inj}$ ,  $V_{inj}$  being the injected signal's amplitude. With a constant output amplitude, the filter's gain depends on  $V_{inj}$ with smaller  $V_{inj}$  resulting in larger gain as shown in Fig. 2.9. This nonlinear behavior, though undesirable for general filtering applications, doesn't pose a problem here as the

Figure 2.8: Bandpass Filter (BPF) - bias details omitted

19

desired signal is a single-tone sinusoid. As evident from Fig. 2.9, the conventional BPF has a flat gain versus input amplitude, whereas the ILO-based BPF's gain has a -6 dB/octave slope suggesting a  $\frac{1}{V_{inj}}$  gain dependance. At a 100mV input amplitude (the amplitude of the  $10^{th}$  harmonic from pulse-slimmer), the ILO-based BPF has a 3 dB higher gain than the conventional BPF. An additional benefit of the ILO based BPF is that the output amplitude saturates even for small inputs and remains relatively independent of the input signal amplitude, i.e., it behaves as an AGC providing constant amplitude to the next stage. The only tradeoff is that at lower amplitudes the phase noise increases [24] suggesting a moderate input level as a good compromise.

Figure 2.9: Simulated gain of BPF (under equal power consumption)

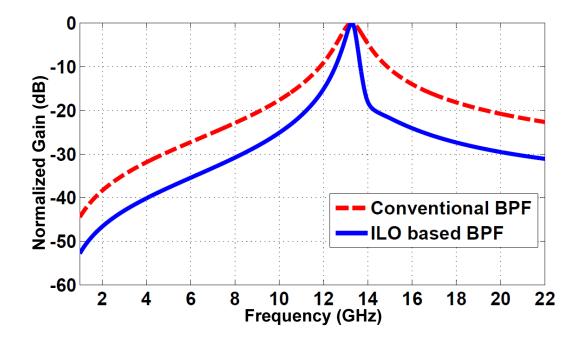

In addition to the higher gain, the injection-locking based bandpass filter also provides higher suppression of undesired harmonics. A spur at an offset  $f_m$  from the input signal is suppressed by  $f_m/f_L$  [21], where  $f_L$  is the single-sided lock range. As shown in fig. 2.10, the effective Q of the ILO-based BPF is almost twice that of the passive LC

20

tank ( $Q \approx 30$  for ILO-based filter versus  $Q \approx 13$  for conventional filter). Two ILO-based BPFs are designed for the 20 GHz and 22 GHz chains, with center frequencies of 13.33 GHz and 14.66 GHz respectively. Each ILO draws 4-mA from a 1.2 V supply.

Figure 2.10: Simulated quality factor of conventional and ILO-based BPF

#### Varactor

Bias details of the varactor are shown in Fig. 2.12. The same structure is also used in the ILFD and the ILFM. Hyper-abrupt PN junctions are used as varactors since their quality factor is higher than that of the conventional MOS varactors at the frequencies of interest. As shown in Fig. 2.13, a large parasitic capacitor is formed between the varactor's negative terminal and the substrate degrading the Q-factor. The positive terminal, on the other hand, is not prone to this parasitic capacitance. Hence, the positive terminal has a Q-factor which is 3-5 times higher than that of the negative terminal as shown in Fig. 2.11.

Figure 2.11: Varactor quality factor at negative and positive terminals

Figure 2.13: Structure of hyper-abrupt PN-junction varactor (parasitics highlighted)

#### Capacitor bank

The details of the two-bit capacitor bank are shown in Fig. 2.14 [29]. A similar capacitor bank structure is used in the ILFD and the ILFM. When the switch control is at  $V_{dd}$ , the resistor bias is at ground and vice-versa. Without this bias scheme, an off-switch might turn on if the output swing is high. This can happen when the output voltage is close to its trough. Parasitic switch capacitance would cause the switch source voltage to spike down, in effect producing a net positive  $V_{gs}$  and causing the switch to turn on for a fraction of the cycle. By forcing  $V_{dd}$  bias through a resistor, this undesired effect is avoided.

Figure 2.14: Two-bit capacitor bank details

#### 2.3.3 Injection Locked Frequency Divider

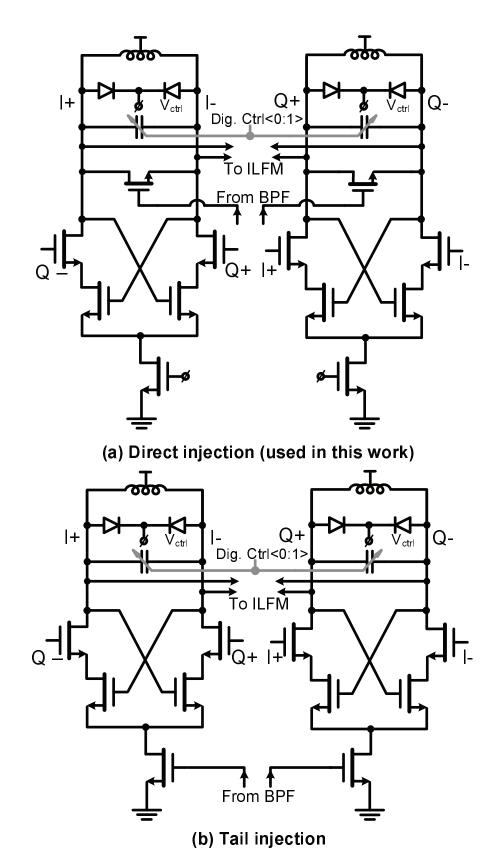

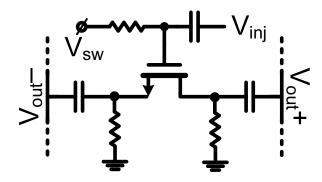

As discussed in Section 2.2.3, an injection locked frequency divider is used in this work to generate a quadrature signal from the single phase reference. The design is based on the work in [20]. This, in turn, is similar to the architecture proposed in [30] but with inter-oscillator injection added to form a quadrature oscillator as the core (the core quadrature oscillator is based on [31]). Unlike [20] and [30], however, injection is not performed at the tail current source as shown in Fig. 2.15. Since no buffer is used between the BPF and the ILFD, injection at the tail source presents a large load capacitance to the BPF increasing its power consumption considerably. To avoid this, direct injection is used as suggested in [32]. The injected signal is applied to an NMOS switch in parallel with the oscillator's LC tank. In this work, the input has a 50% duty cycle and hence the switch is on only once during a whole cycle of the injection signal. This, in effect, makes the output frequency half that of the input. The switch's input capacitance is roughly 25 times smaller than what would have been for the tail current transistor, simplifying the design of the preceding BPF. Two ILFDs are designed, a 6.66 GHz ILFD for the 20 GHz chain and a 7.33 GHz ILFD for the 22 GHz chain; each consumes 27 mA from a 1.2 V supply.

It is to be noted that the DC bias at the NMOS switch terminals in Fig. 2.15 is  $V_{dd}$ . Hence it is not possible to turn the switch on unless the bias point is adjusted, which necessitates the use of AC coupling. Towards this end, both the gate connection and the source and drain connections of the switch are AC coupled. This provides more flexibility in choosing the bias point. The bias details of the switch are shown in Fig. 2.16.

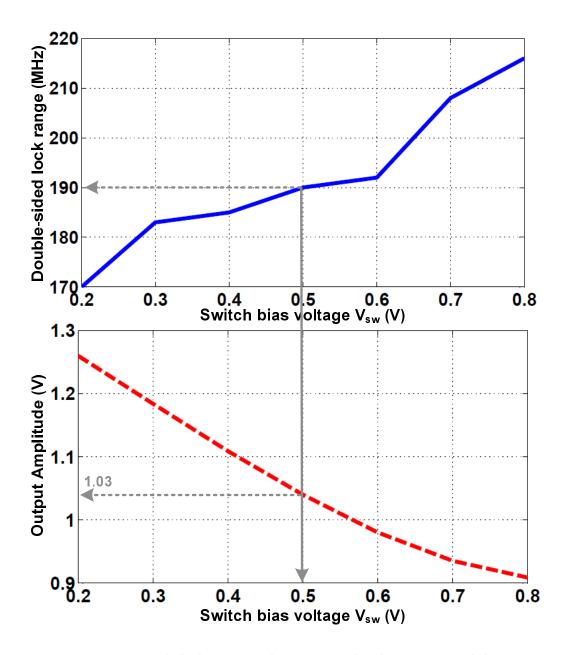

With the NMOS switch on, the quality factor of the tank is reduced. The timeaveraged quality factor of the tank will thus depend on the switch on-resistance as well as the switch on time. The time-averaged quality factor, in turn, determines two important aspects of the ILFD: lock range and output amplitude. A wider lock range is desirable to suppress the ILFD's intrinsic phase noise and to cope with process variations. A higher output amplitude is also desirable to widen the lock range of the following stage,

Figure 2.15: Injection Locked Frequency Divider (ILFD) - bias details omitted

Figure 2.16: Injection switch bias details

the ILFM. There is a clear trade-off between the two requirements which is controlled by the switch's bias point. A higher bias point leads to a lower time-averaged quality factor and hence a wider lock range and a lower output amplitude and vice-versa. Fig. 2.17 shows the lock range and the output amplitude of the ILFD versus the switch bias point  $V_{sw}$ . A reasonable trade-off is achieved for  $V_{sw} \approx 0.5$  V, resulting in a 190 MHz double-sided lock range and a 1.03 V output amplitude.

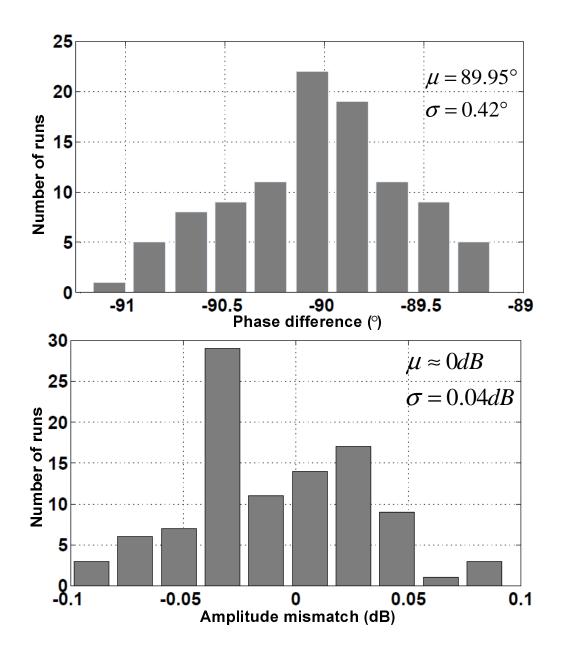

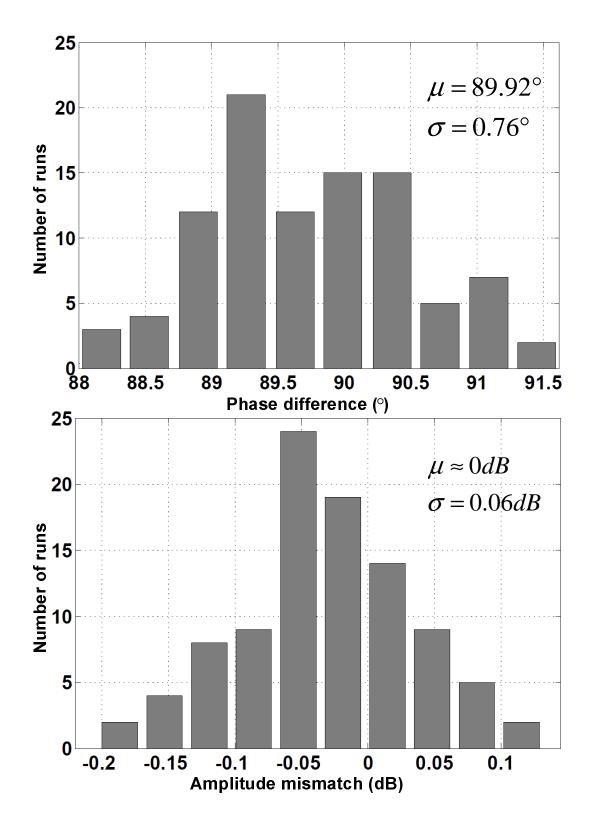

Monte-Carlo simulations are performed to determine the expected phase-error and amplitude mismatch in the ILFD's output. As shown in Fig. 2.18, the simulated  $3\sigma$ phase error amounts to  $\pm 1.27^{\circ}$  whereas the  $3\sigma$  amplitude mismatch amounts to 0.12 dB.

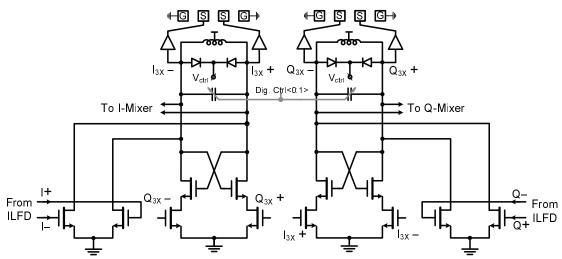

#### 2.3.4 Injection Locked Frequency Tripler

The injection locked frequency multiplier (ILFM), acting as a tripler, is shown in Fig. 2.19 [28]. At the core of the ILFM is a bottom-series-coupled quadrature VCO similar to [33]. The injection differential pair is biased in subthreshold, and is operated in class-B mode resulting in a strong third harmonic current component. As shown in Fig. 2.20, the third harmonic of the injection current has its peak below the threshold voltage  $V_{th}$ . An added advantage of subthreshold operation is the reduced power consumption in the injection pair. Two ILFMs are designed, with 20 GHz and 22 GHz

Figure 2.17: ILFD's lock range and output amplitude versus switch bias

Figure 2.18: ILFD phase and amplitude mismatch - Monte Carlo simulations

Figure 2.19: Injection Locked Frequency Multiplier (ILFM) - bias details omitted

center frequencies. Each consumes 21 mA from a 1.2 V supply.

Monte Carlo simulations are performed to estimate the phase and amplitude mismatch of the ILFM. The results, shown in Fig. 2.21, represent *the intrinsic* phase and amplitude mismatches of the ILFM. The intrinsic  $3\sigma$  phase error amounts to  $\pm 2.28^{\circ}$ whereas the  $3\sigma$  amplitude mismatch amounts to 0.18dB.

Since the final LO amplitude is large enough for full mixer switching, amplitude mismatch at the LO output is irrelevant. Phase mismatch, however, is crucial. The total phase mismatch at the LO output is affected by the intrinsic phase mismatch of the ILFM, as well as the phase mismatch of the ILFD (which drives the ILFM). For a given fixed phase error of the ILFD  $\Delta \phi_{in}$  and a fixed phase error of the ILFM  $\Delta \phi_{int}$ , a pessimistic estimate of the output LO phase error would be:

$$\Delta\phi_{LO} = \Delta\phi_{int} + 3 \times \Delta\phi_{in} \tag{2.2}$$

Hence, the standard deviation of the phase error at the output will be the r.m.s sum of the standard deviations of the two terms in Eqn.(2.2):

29

Figure 2.20: SpectreRF<sup>®</sup> simulation of the third harmonic current in injection pair

$$\sigma_{LO} = \sqrt{\sigma_{int}^2 + (3 \times \sigma_{in})^2} \tag{2.3}$$

Accordingly, the estimated  $3\sigma$  phase error at the output of the LO is  $\pm 4.4^{\circ}$ . This is a pessimistic estimate that represents an upper bound on the output phase error.

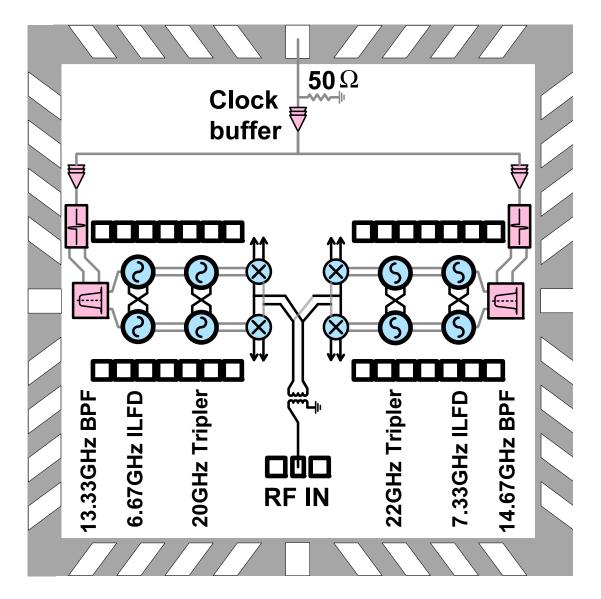

#### 2.3.5 Chip Floorplan

The chip floorplanning is an integral part of the design process that is critical for successful operation. The floorplan of the chip in this work is presented in Fig. 2.22. The input reference clock signal is terminated on-chip via a  $50\Omega$  resistor for matching. The clock is buffered and then two separate paths are routed to the pulse-slimmer of each chain. Since the reference clock has a relatively low frequency, it is easier to route it for a longer distance. Another set of inverter buffers is also introduced along each path for

Figure 2.21: ILFM phase and amplitude mismatch - Monte Carlo simulations

Figure 2.22: Chip floorplan

further signal enhancement. As noted in Section 2.2.1, a single pulse-slimmer could be used. However, this would require the output of the slimmer to be routed for a very long distance. This would, in turn, impose two problems: attenuation of the desired high frequency harmonic content of the output and undesired parasitic coupling to different points in the chain. Hence, two pulse-slimmers are used; one for each chain. The slimmer is placed as close as possible to the bandpass filter to minimize the routing distance and hence minimize signal loss and parasitic couplings. The associated area and power overhead are negligible. The output of the slimmer is not available for measurement and neither is the output of the bandpass filter. The injection locked divider and the injection locked multiplier follow in cascade. Care is taken to achieve maximum layout symmetry. The outputs of both the divider and the multiplier are buffered and fed to on-chip GSSG pads for probing. The final LO outputs are fed to active Gilbert-cell based double-balanced quadrature mixers for measurement purposes. The other input of the mixer is provided externally through probing via an on-chip GSG pad followed by an on-chip balun.

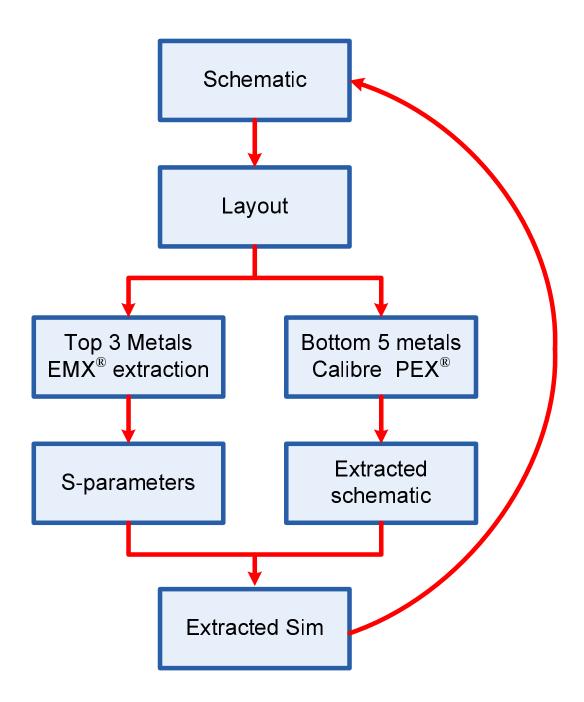

## 2.4 EM design methodology

In high frequency oscillators, interconnects play a critical role in the performance. Interconnects can no longer be treated as wires with a constant resistance (i.e. against frequency). Higher order effects kick-in, considerably altering the performance. The three major effects are: skin effect, substrate loss and current-crowding (or proximity effect) [34,35]. If not accounted for, the extra AC resistance added by these effects can cause a significant degradation in the oscillation amplitude or, in the extreme case, a total startup failure. Moreover, with low tank inductances (150 pH  $\sim$  750 pH) the interconnect inductance cannot be neglected and can cause considerable frequency shifts. Due to the complex nature of these effects, as well as the complex interconnect pattern typical of integrated circuits, EM simulations become crucial for successful design validation. EM simulation tools, however, are not suited for extraction of the transistor parasitics. Moreover, as the number of simulated metal layers increases simulation times increase significantly.

To both accommodate transistor parasitics and speed-up EM simulations, a divideand-conquer approach is used for extraction. Each oscillator layout is dissected vertically into two sections: a lower section (i.e. closer to substrate) which includes the transistors and the interconnects on the lower five metals and an upper section (i.e. farther away from substrate) including the inductors, capacitors and upper three metal interconnects. This choice is made because the high-frequency signals are routed on the top three metal layers (which are the thickest) to reduce DC resistance. Moreover since the thickness of the top three metals is larger than the skin depth, their resistance varies significantly at high-frequencies, as opposed to the thin lower metals whose resistance is dominated by the DC value. Conventional circuit extraction tools (in our case Calibre PEX<sup>®</sup>) are used on the lower section resulting in an extracted schematic with lumped resistor and capacitor parasitics. For the upper section, EM simulations are used to capture parasitic AC resistances and parasitic inductances and capacitances. Due to the large interconnect structures typical of quadrature VCOs, a fast and efficient EM simulation tool was needed. Towards this end, Integrand's EMX<sup>®</sup> EM-simulation tool [36] was used. The tool outputs an S-parameter data file, which is then combined with the extracted schematic from the lower section to perform a simulation of the whole structure. The circuit is then modified, if needed, and another simulation iteration is performed until the desired performance (frequency/output amplitude) is obtained. Fig. 2.23 summarizes the design methodology.

Figure 2.23: EM design methodology flow graph

# 2.5 PVT considerations

As discussed in Section 2.2.1, a duty cycle of  $\frac{1}{8}$  to  $\frac{1}{6}$  is required for maximum amplitude of the desired harmonics at the output of the pulse slimmer. To accomodate PVT variations, the gate voltage of the MOS resistor in the duty-cycle control section of Fig. 2.5 can be changed to control the variable delay, and change the duty-cycle accordingly. The variable delay is designed such that, at the worst PVT corner, the delay can be tuned to bring the duty cycle back to the acceptable range.

With three LC ILOs in each LO chain, it is instructive to investigate the effect of PVT variations. Typically LC oscillator frequency shifts due to PVT variations are in the order of 15% - 20%. Hence, tuning for each ILO has to be designed to accommodate the expected frequency shift.

Nevertheless, some amount of shift is usually allowed in the IF center frequency. This, in turn, translates to some amount of shift in the LO frequency. This can relax the tuning range requirements of the oscillators. For instance, let's assume that a 10% LO shift is acceptable. Hence, with a maximum PVT shift of 20%, the ILFM tuning range can be reduced to just 10%. A 10% shift in the ILFM frequency requires a similar 10% shift in the ILFD frequency. With a maximum PVT shift of 20%, the ILFD tuning range can be reduced to 10% as well. Similarly, the BPF tuning range can be reduced to 10% as well. Similarly, the BPF tuning range can be reduced to 10% as well. Similarly, the BPF tuning range can be reduced to 10% as well. Similarly, the BPF tuning range is a design guideline; actual design has to ensure that in the worst PVT corner, tuning can bring back the oscillator to an acceptable frequency.

Automatic center-frequency tuning can be done by exploiting injection-locking. An ILO's amplitude is highest when the injected signal is close to the free-running frequency and decreases as the injected signal frequency deviates [37]. A possible procedure for automatic tuning based on this observation can be done as follows:

- With the ILFD and ILFM turned off, the pulse slimmer and the BPF are turned on. The delay setting in the pulse-slimmer is set to its nominal value. The BPF frequency control is swept and its output amplitude is monitored using a peakdetector. When the peak-detector's reading reaches its maximum value, the sweep is stopped and the BPF frequency setting is stored.

- With the ILFD and ILFM still off and the BPF frequency set to the value stored in the previous step, the delay control of the pulse slimmer is swept until the BPF output is maximized. The delay setting is stored.

- The ILFM is kept off, and the ILFD is turned on (together with the pulse slimmer and the BPF). The ILFD's frequency control is swept and its output is monitored using a peak-detector till the output hits a maximum. The ILFD's frequency setting is then stored.

- Finally, the whole LO chain is turned on and the ILFM frequency control is swept while its output is monitored using a peak detector. When the output is maximized, the sweep is stopped and the frequency setting is stored.

The stored values then represent the best frequency settings that ensure that each ILO is tuned as close as possible to its injection input.

#### 2.6 Measurements and Discussion

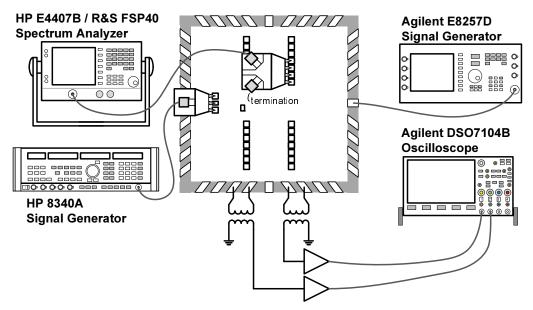

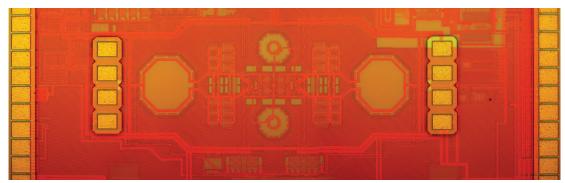

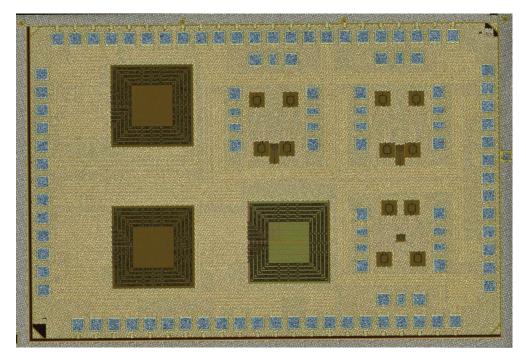

The chip was fabricated in IBM's 130 nm CMOS technology. The chip micrograph is shown in Fig. 2.24. The active area is  $1.8 \text{ mm}^2$ . The test setup is shown in Fig. 2.25. A reference 1.33 GHz signal is supplied using an Agilent E8257D signal generator. An on-chip 50 $\Omega$  resistor provides termination for the generator. The quadrature oscillator outputs are measured using GSSG probes and the output is displayed on an HP E4407B

Figure 2.24: Chip Micrograph

| Table 2.1: Current consumed per block        |              |  |

|----------------------------------------------|--------------|--|

| Block                                        | Current (mA) |  |

| Digital (buffering + pulse slimmer)          | 3            |  |

| Bandpass Filter (BPF)                        | 4            |  |

| Injection Locked Frequency Divider (ILFD)    | 27           |  |

| Injection Locked Frequency Multiplier (ILFM) | 21           |  |

spectrum analyzer where the spur levels are measured. A R&S FSP40 spectrum analyzer is used to measure the phase noise. The GSSG probes are driven by on-chip  $50\Omega$  buffers. The RF signal is supplied from an HP 8340A signal generator through GSG probes. The differential outputs of the quadrature downconversion mixers are connected to offchip baluns. The single-ended outputs are then amplified and displayed on an Agilent DSO7104B oscilloscope.

Each chain consumes around 55 mA from a 1.2 V supply, for a total current consumption of 110 mA. The current consumed by each block is detailed in Table 2.1.

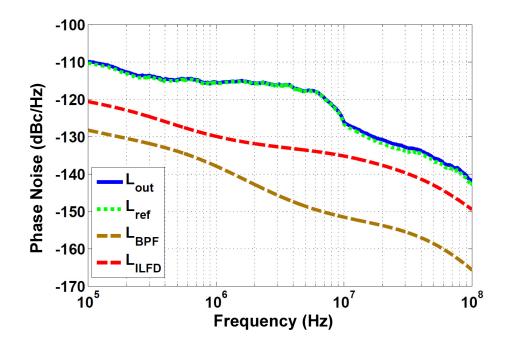

Fig. 2.26 shows the phase noise of the reference oscillator along with the phase noises of the 6.67 GHz ILFD and the corresponding 20 GHz ILFM, when the chain is locked

Figure 2.25: Test Setup

to the reference. The ILFD phase noise is measured at the output of the ILFD's  $50\Omega$  buffers using GSSG probes. Similarly, the ILFM phase noise is measured at the output of the ILFM's  $50\Omega$  buffers using GSSG probes as well. It is clear from Fig. 2.26 that the 20 GHz ILFM has negligible contribution to the output phase noise; the phase noise at the ILFM output is a faithful replica of the ILFD shifted by around +10dB (since the ILFM multiplies its input frequency by three, it adds  $20log(3)\approx9.5$  dB to the input phase noise). This can be attributed to the relatively large lock range of the ILFM (single-sided lock range> 350 MHz). In contrast, the loop bandwidth of a PLL is typically in the range of a few MHz leading to a large contribution from the PLL's VCO to the output phase noise. The 22 GHz chain performs in a similar manner to the 20 GHz chain as shown in Fig. 2.27. The spot phase noise values at 1-MHz and 10 MHz offsets along the two chains are summarized in Table 2.2.

It is instructive to find the contribution of the reference, BPF and ILFD to the output phase noise. Towards this end, the model in [24] is used. Each ILO acts as a first-order low-pass filter to its input phase noise, with the corner frequency determined

Figure 2.26: Measured phase noise along the 20 GHz chain

Figure 2.27: Measured phase noise along the 22 GHz chain

| Table 2.2: Phase noise performance    |        |        |

|---------------------------------------|--------|--------|

| Offset frequency (MHz)                | 1      | 10     |

| Measured $@6.67 \text{ GHz} (dBc/Hz)$ | -112.5 | -121   |

| Measured $@20 \text{ GHz} (dBc/Hz)$   | -101.5 | -111   |

| Measured $@7.33 \text{ GHz} (dBc/Hz)$ | -112   | -118   |

| Measured $@22 \text{ GHz} (dBc/Hz)$   | -100   | -107.5 |

by the single-sided lock range  $f_L$ . The intrinsic ILO phase noise is filtered by a first order high-pass filter of corner frequency  $f_L$  as well. Frequency division and multiplication scale the phase noise accordingly. The resultant model for the cascade of pulse-slimmer, BPF and ILFD is shown in Fig. 2.28.

Figure 2.28: Phase noise model

Using this model, the output-referred phase noise contributions at the 6.67 GHz ILFD are plotted in Fig. 2.29 based on the simulated phase noise of the BPF and ILFD, and the measured reference phase noise. As evident from the figure, the BPF phase noise contribution is negligible. Even with the slight increase in actual BPF phase noise (due to modeling inaccuracies and supply-noise), BPF phase noise contribution remains negligible<sup>1</sup>. The simulated ILFD phase noise contribution is small but increases at larger offsets. The discrepancy between the simulated phase noise at the output of the ILFD (shown in Fig. 2.29) and the actual measured phase noise at the ILFD output (shown in Fig. 2.26) can be attributed to two reasons: 1) the actual ILFD phase noise is higher than simulated (again due to modeling inaccuracies and supply-noise) and

$<sup>^1~</sup>$  The actual phase noise of BPF could not be measured because its output is not available for probing

Figure 2.29: Simulated output-referred phase noise contributions at 6.67 GHz ILFD 2) the measurement instrument intrinsic phase noise is considerable compared to the up-converted reference phase noise [38]. This results in a final phase noise profile that is different from the simulated curve.

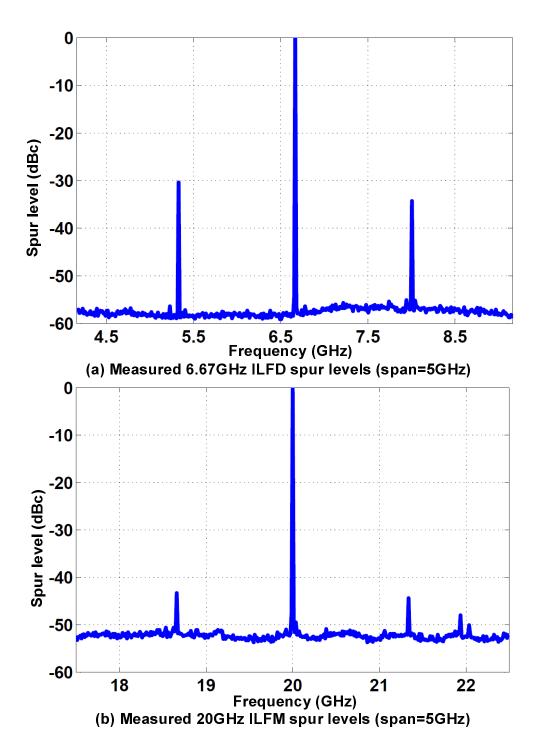

The spurious performance of the 20 GHz LO chain is shown Fig. 2.30. The spurs are at 1.33 GHz offset; the significant harmonics at the BPF's output are the  $9^{th}$ ,  $10^{th}$  and  $11^{th}$  harmonics. At the 6.67 GHz ILFD, the  $10^{th}$  harmonic is divided down generating the 6.67 GHz signal. The  $9^{th}$  and  $11^{th}$  harmonics, on the other hand, mix with the 6.67 GHz LO generating spurs at  $\pm 1.33$  GHz offset. These spurs are suppressed by virtue of the ILFD's filtering effect (in a manner similar to the effect of the BPF). At the 20 GHz ILFM, the spur levels are further attenuated. The maximum spur at the output of the 20 GHz ILFM falls at -43 dBc as compared to -30 dBc at the output of the 6.67 GHz ILFD. While the BPF measurements are not available, the simulations shown in Fig. 2.4 suggest that the spurs at the BPF's output fall at around -17 dBc. Hence the

Figure 2.30: Spurious performance of the 20 GHz LO chain

Figure 2.31: Spurious performance of the 22 GHz LO chain

Figure 2.32: Generation of  $\pm 666$  MHz spurs in 22 GHz LO chain

cascade of ILOs provide excellent spur suppression.

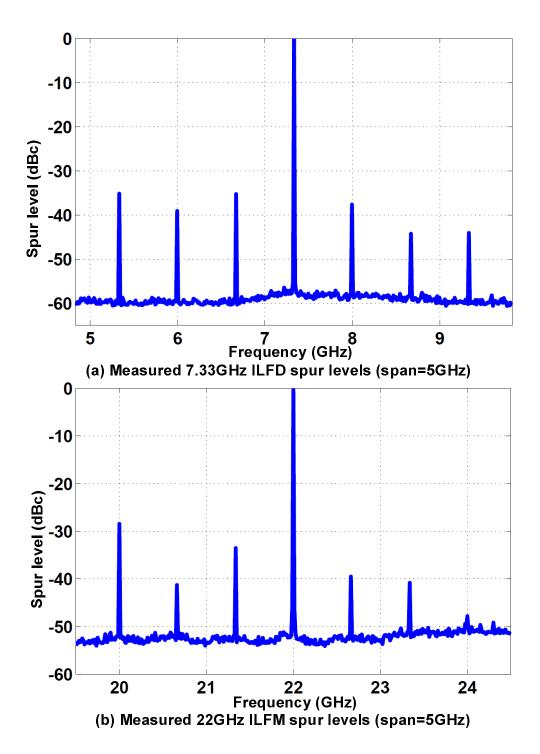

Fig. 2.31 shows the spurious performance of the 22 GHz LO chain. Similar trends can be observed for the  $\pm 1.33$  GHz spurs which are generated in a manner similar to the spurs in the 20 GHz chain. However, additional spurs appear at  $\pm 666$  MHz offset as well as at  $\pm 3 \times 666$  MHz offset. To explain the generation of the additional spurs, consider Fig. 2.32. The output of the BPF and ILFD is shown in terms of harmonics of the reference signal. When applied to the ILFD, the  $11^{th}$  harmonic is divided by two, generating a frequency corresponding to the 5.5<sup>th</sup> harmonic of the reference. The  $10^{th}$  and  $12^{th}$

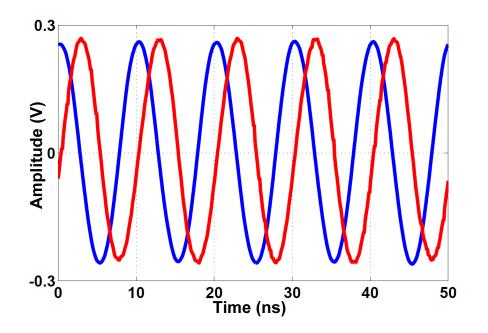

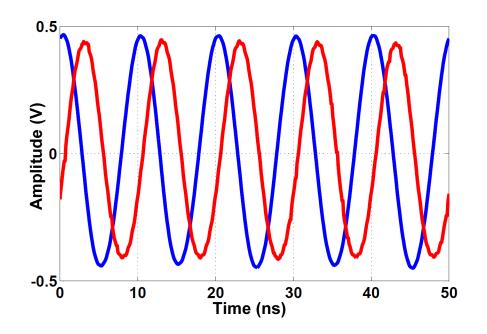

Figure 2.33: Measured downconverted quadrature outputs of the 20 GHz LO

harmonics are divided as well, generating very small components which fall onto the  $5^{th}$  and  $6^{th}$  harmonics of the reference. Due to the inevitable on-chip parasitic coupling (through electromagnetic radiation, substrate coupling, and capacitive coupling), the  $5^{th}$  and  $6^{th}$  harmonics at the output of the ILFD add to the similar components at the ILFD's input. A parasitic positive feedback loop is formed, enhancing these components which correspond to spurs at  $\pm 666$  MHz from the desired  $5.5^{th}$  harmonic. The spurs at  $\pm 3 \times 666$  MHz are formed through third-order intermodulation of the  $\pm 1.33$  GHz spurs and the  $\pm 666$  MHz spurs. At the ILFM's output, the spur at  $+3 \times 666$  MHz is filtered out. The component at  $-3 \times 666$  MHz, however, remains and its amplitude increases due to parasitic reinforcement from the 20 GHz LO chain. One possible way to get rid of the  $\pm 666$  MHz spur and the subsequent  $\pm 3 \times 666$  MHz spurs is to use a pulse slimmer that only generates odd harmonics in the 22 GHz LO chain. This further justifies the use of a separate pulse-slimmer for each chain as suggested in Section 2.3.5.

Figure 2.34: Measured downconverted quadrature outputs of the 22 GHz LO

The downconverted time domain I and Q outputs of the 20 GHz and 22 GHz LOs are shown in Fig. 2.33 and Fig. 2.34 respectively. Due to a limitation of the off-chip balun, the output frequency cannot be below 100 MHz. This, in turn, means that the mismatches between I and Q paths on board are not negligible and add considerably to the measured phase difference. Nevertheless, the measured average phase error under these conditions is  $10^{\circ}$  and  $2^{\circ}$  for the 20 GHz and the 22 GHz LOs respectively.

# 2.7 Conclusions

In this work an LO scheme for generating simultaneous phase synchronous quadrature LOs was presented for a 19 - 23 GHz channelized receiver. The architecture developed here can easily be extended to more than two channels, and can be implemented at different frequencies. This provides a viable mechanism to realize mm-wave channelized

receivers. A number of novel techniques are used in the design, including a differentiating pulse-slimmer that exploits even and odd harmonics, an injection-locking based bandpass filter and an injection-locked quadrature frequency divider with direct injection. Building upon [19], more thorough discussion of the system-level and circuit-level design issues is presented. Additional measurements are presented, allowing the assessment of the contribution of each of the building blocks to the output phase noise. Moreover, an anomaly in the spurious response of the 22 GHz channel is explained and a less spurious alternative is suggested.

# Chapter 3

# Wideband QVCO

# 3.1 Introduction

With the advent of CMOS technology, direct downconversion receivers are becoming more popular due to low cost and simplicity. Quadrature LO generation is crucial to the operation of downconversion receivers [5]. Two common techniques for quadrature generation are using divide-by-two frequency dividers, and using polyphase filters [31]. Divide-by-two dividers require the system's oscillator to work at double the desired frequency, resulting in an overall increase in power consumption. Polyphase filters allow quadrature generation without the need for doubling the frequency. The lossy nature of polyphase filters, however, results in increased power consumption (for buffering and amplifying signals). Moreover, polyphase quadrature accuracy is sensitive to absolute component values. Hence, multistage polyphase filters are often employed to combat process variations, resulting in increased losses [27]. Quadrature accuracy is also reduced if the polyphase filter input is not a pure sinusoid. Generating a pure sinusoid can be elusive in today's submicron technologies, resulting in yet another source of quadrature error.

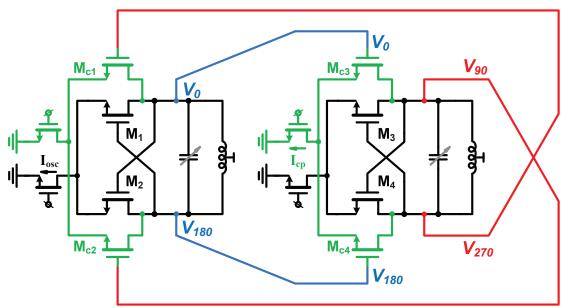

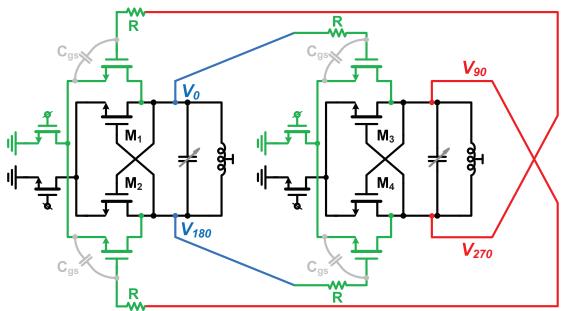

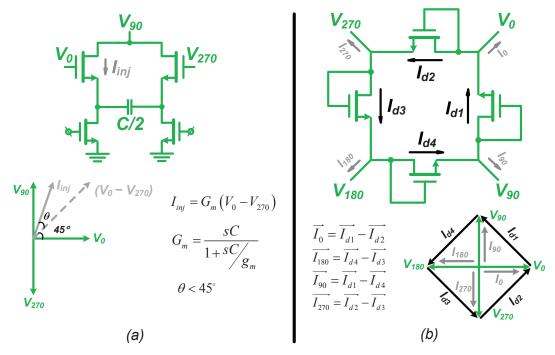

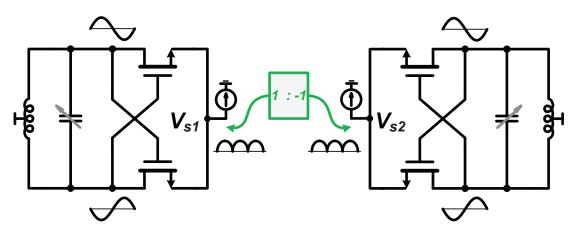

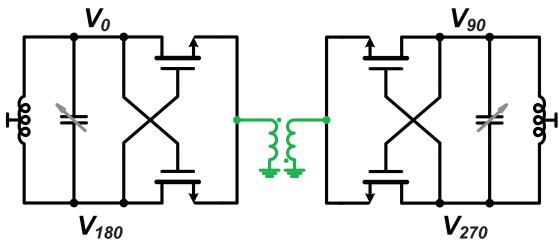

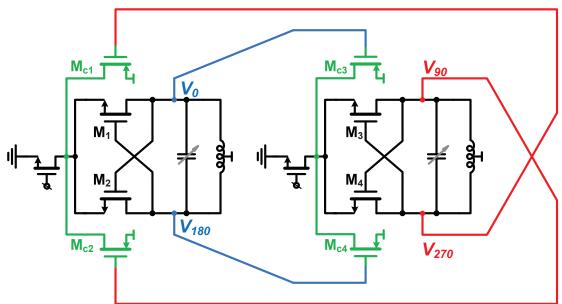

Figure 3.1: Basic LC QVCO

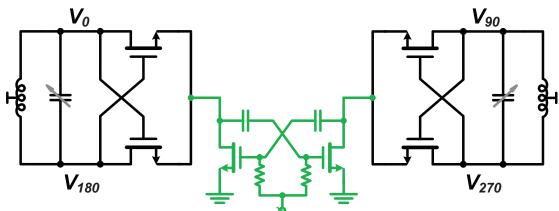

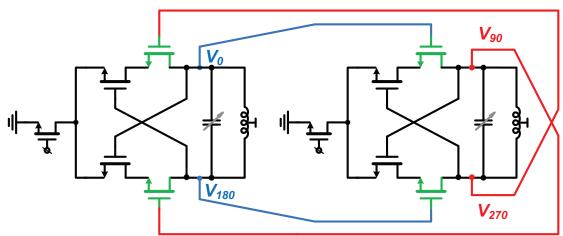

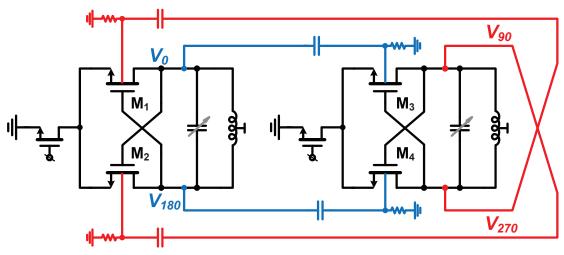

LC-based Quadrature Voltage Controlled Oscillators (QVCOs) allow the generation of quadrature LO signals without the need for doubling the frequency, and without the need for polyphase filtering. The basic structure of the LC-based QVCO is shown in Fig. 3.1 [39]. Two LC VCOs are coupled through both direct coupling (blue wires in Fig. 3.1), and cross coupling (red wires in Fig. 3.1). If both LC VCOs are matched, then owing to symmetry their differential outputs have to be in quadrature [40]. The QVCO can also be regarded as two inter-injection-locked VCOs [20].

The LC QVCO of Fig. 3.1 provides a simple and robust way for quadrature generation. However, it has an inherent trade-off between phase-noise and quadrature accuracy. If we denote the coupling strength as  $\alpha$ , then it can be defined as:

$$\alpha = \frac{I_{cp}}{I_{osc}} \tag{3.1}$$

where  $I_{cp}$  is the tail current of the coupling transistor pairs  $(M_{c1}-M_{c2} \text{ and } M_{c3}-M_{c4})$ , and  $I_{osc}$  is the tail current of the oscillator core transistor pairs  $(M_1-M_2 \text{ and } M_3-M_4)$ .

50