Design Techniques for Dense Embedded Memory in Advanced CMOS Technologies

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA BY

Ki Chul Chun

## IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Chris H. Kim, Adviser

February 2012

#### Acknowledgements

This dissertation has been accomplished with the advice of Professor Chris H. Kim, collaboration with colleagues, financial support from Samsung Electronics, and dedication of my family and wife.

First, I would like to thank my academic adviser, Professor Chris H. Kim, for guiding me with exploratory research items and providing me with friendly environments for doing research as well as enjoying life in MN. His endless enthusiasm for academic explorations has always inspired me; consequently, we achieved many outstanding research outcomes.

Next, I am grateful to my final defense committee; Professors Ramesh Harjani, Sachin Sapatnekar, and Antonia Zhai for reviewing this dissertation and providing valuable discussions during your busy schedules.

I owe a great deal of gratitude to Samsung Electronics for supporting my entire PhD study through the Samsung PhD scholarship. I started my career as a VLSI designer at Samsung Electronics in 2000. I am grateful to all the members of Samsung DRAM Design Team for making my understanding of memory circuit design strong.

The time that I have got together with all the members of VLSI Research Lab at the University of Minnesota would last for the last of my life. To previous members; I thank Jie Gu, Tony T. Kim, and John Keane for your many helps during my settlement. To current members; I am grateful for lots of insightful discussions with you. I have been happy with you; Dong Jiao, Wei Zhang, Pulkit Jain, Xiaofei Wang, Seunghwan Song,

Ayan Paul, Bongjin Kim, Jongyeon Kim, Wonho Choi, Weichao D. Xu, Renukprasad Hiremath, and Dan Liu.

My PhD study has never been lonely due to many good Korean friends. I thank Jaehyup Kim, Youngil Kim, Boram Lee, Jaesang Oh, Hweerin Sohn, and Sungmin Sohn for sharing your valuable times with me.

I would also like to thank my parents and my younger brother. They have always been supporting me and encouraging me with their best wishes.

Finally, I would like to thank my wife, Sun Young Hwang. She has dedicated herself astoundingly to support my PhD study. I also thank our daughter; Siyeon Chun to be such a lovely kid. Thank you for everything.

#### **Abstract**

On-die cache memory is a key component in advanced processors since it can boost micro-architectural level performance at a moderate power penalty. Demand for denser memories only going to increase as the number of cores in a microprocessor goes up with technology scaling. A commensurate increase in the amount of cache memory is needed to fully utilize the larger and more powerful processing units. 6T SRAMs have been the embedded memory of choice for modern microprocessors due to their logic compatibility, high speed, and refresh-free operation. However, the relatively large cell size and conflicting requirements for read and write make aggressive scaling of 6T SRAMs challenging in sub-22 nm.

In this dissertation, circuit techniques and simulation methodologies are presented to demonstrate the potential of alternative options such as gain cell eDRAMs and spin-torque-transfer magnetic RAMs (STT-MRAMs) for high density embedded memories.

Three unique test chip designs are presented to enhance the retention time and access speed of gain cell eDRAMs. Proposed bit-cells utilize preferential boostings, beneficial couplings, and aggregated cell leakages for expanding signal window between data '1' and '0'. The design space of power-delay product can be further enhanced with various assist schemes that harness the innate properties of gain cell eDRAMs. Experimental results from the test chips demonstrate that the proposed gain cell eDRAMs achieve

overall faster system performances and lower static power dissipations than SRAMs in a generic 65 nm low-power (LP) CMOS process.

A magnetic tunnel junction (MTJ) scaling scenario and an efficient HSPICE simulation methodology are proposed for exploring the scalability of STT-MRAMs under variation effects from 65 nm to 8 nm. A constant J<sub>C0</sub>•RA/VDD scaling method is adopted to achieve optimal read and write performances of STT-MRAMs and thermal stabilities for a 10 year retention are achieved by adjusting free layer thicknesses as well as projecting crystalline anisotropy improvements. Studies based on the proposed methodology show that in-plane STT-MRAM will outperform SRAM from 15 nm node, while its perpendicular counterpart requires further innovations in MTJ material properties in order to overcome the poor write performance from 22 nm node.

## **Table of Contents**

| List of Figures                                                    | viii         |

|--------------------------------------------------------------------|--------------|

| 1 Introduction                                                     | 1            |

| 1.1 Embedded Memories in Multi-Core Microprocessor                 | 2            |

| 1.2 Alternative Memory Technologies                                | 4            |

| 1.3 Summary of Dissertation Contributions                          | 6            |

| 2 A 3T Embedded DRAM Utilizing Preferential Boosting for Lo        | $\mathbf{w}$ |

| Voltage On-Die Caches                                              | 8            |

| 2.1 Basic Operation of a Conventional 3T EDRAM                     | 8            |

| 2.2 Boosted 3T EDRAM Design                                        | 10           |

| 2.2.1 Boosted 3T Gain Cell                                         | 11           |

| 2.2.2 Regulated Bit-Line Write Scheme                              | 15           |

| 2.2.3 PVT-Tracking Read Reference Bias                             | 16           |

| 2.2.4 Architecture and Operation of a 32 kb Sub-Array              | 17           |

| 2.3 Statistical Simulation Results for 6T SRAM and 3T EDRAM Arrays | 19           |

| 2.3.1 Read and Write Performance                                   | 20           |

| 2.3.2 Static Power Consumption                                     | 24           |

| 2.4 Test Chip Implementation and Measurements                      | 27           |

| 2.5 Canalysians                                                    | 32           |

| 3 | An Asymmetric 2T EDRAM for High Speed On-die Caches                | 34 |

|---|--------------------------------------------------------------------|----|

|   | 3.1 Retention Characteristics of Conventional Gain Cells           | 34 |

|   | 3.2 Asymmetric 2T EDRAM Design                                     | 36 |

|   | 3.2.1 Asymmetric 2T Gain Cell                                      | 36 |

|   | 3.2.2 Pseudo-PMOS Diode Based Current-Mode Sense Amplifier (C-S/A) | 38 |

|   | 3.2.3 Half Swing Write Bit-Line Scheme                             | 43 |

|   | 3.2.4 Stepped Write Word-Line Driver                               | 44 |

|   | 3.2.5 Sense Amplifier and Write-Back Circuit Design                | 46 |

|   | 3.3 Comparison Between SRAM and Gain Cell EDRAM                    | 48 |

|   | 3.3.1 Macro Layout Comparison                                      | 48 |

|   | 3.3.2 Macro Performance Comparison                                 | 50 |

|   | 3.4 Test Chip Implementation and Measurements                      | 52 |

|   | 3.5 Conclusions                                                    | 57 |

| 4 | A Logic-Compatible 2T1C EDRAM for Enhanced Reliability             | 59 |

|   | 4.1 Boosted Supply Level vs. EDRAM Performance                     | 59 |

|   | 4.2 2T1C EDRAM with No Boosted Supplies                            | 60 |

|   | 4.2.1 2T1C Gain Cell                                               | 60 |

|   | 4.2.2 Decoupled 7T SRAM Repair Cell with Shared Control            | 65 |

|   | 4.2.3 Cell Storage Monitor                                         | 69 |

|   | 4.3 2T1C EDRAM Test Chip Measurements                              | 71 |

|   | 4.4. Conclusions                                                   | 78 |

### **5** A Scalability Exploration of STT-MRAMs Considering Variation

| Effects                                            | 80  |

|----------------------------------------------------|-----|

| 5.1 Introduction to STT-MRAM                       | 80  |

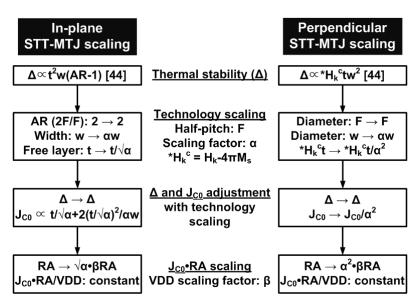

| 5.2 STT-MTJ Scaling Roadmap                        | 82  |

| 5.2.1 In-Plane STT-MTJ Scaling Scenario            | 84  |

| 5.2.2 Perpendicular STT-MTJ Scaling Scenario       | 85  |

| 5.2.3 STT-MTJ Scaling Trend                        | 86  |

| 5.3 STT-MRAM HSPICE Simulation Methodology         | 88  |

| 5.3.1 STT Switching and MTJ Macromodel             | 88  |

| 5.3.2 Transistor Scaling Trend                     | 90  |

| 5.3.3 Sub-Array Architecture and Variation Sources | 91  |

| 5.4 Comparison Between SRAM and STT-MRAM           | 94  |

| 5.4.1 Macro Performance                            | 94  |

| 5.4.2 In-Plane STT-MRAM vs. 6T SRAM                | 95  |

| 5.4.3 In-Plane STT-MRAM vs. Perpendicular STT-MRAM | 99  |

| 5.5 Conclusions                                    | 100 |

| 6 Conclusion                                       | 102 |

| Bibliography                                       | 106 |

## **List of Figures**

| Fig. 1.1: | High-end microprocessors with high density on-die L3 caches based on      |    |

|-----------|---------------------------------------------------------------------------|----|

|           | 6T SRAM and 1T1C eDRAM.                                                   | 2  |

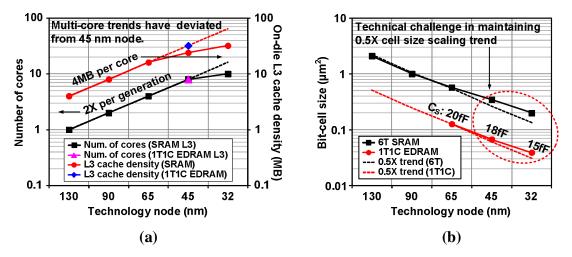

| Fig. 1.2: | (a) Trend of number of cores and corresponding on-die L3 cache densities  |    |

|           | in Intel's and IBM's high-end microprocessors. (b) Bit-cell size scaling  |    |

|           | trend of 6T SRAMs and 1T1C eDRAMs.                                        | 4  |

| Fig. 2.1: | (a) Conventional 3T PMOS eDRAM gain cell circuit diagram. (b) Signal      |    |

|           | voltages in each operating mode.                                          | 8  |

| Fig. 2.2: | Monte Carlo simulation results of storage node voltage during data hold   |    |

|           | mode                                                                      | 10 |

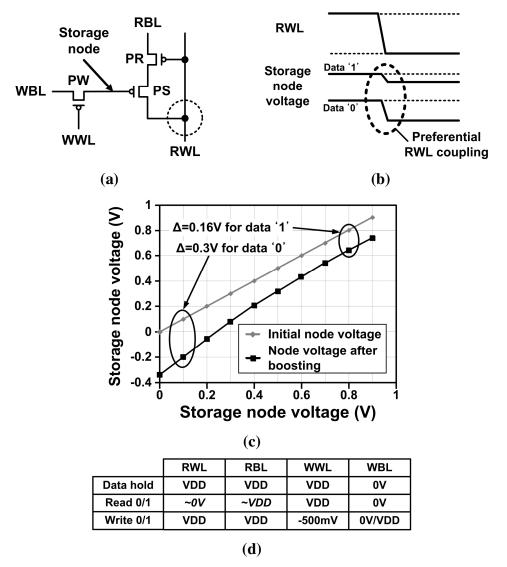

| Fig. 2.3: | (a) Proposed boosted 3T PMOS eDRAM gain cell. (b) Preferential RWL        |    |

|           | coupling effects of the proposed cell. (c) Simulation results of the      |    |

|           | storage node preferential boosting effects. (d) Signal voltage conditions |    |

|           | for each operating mode.                                                  | 12 |

| Fig. 2.4: | (a) Hybrid bit-line current/voltage sense amplifier (S/A) with read port, |    |

|           | write port, and write-back circuits. (b) Read and write-back timing       |    |

|           | diagram of the proposed S/A.                                              | 14 |

| Fig. 2.5: | (a) Storage node disturbance problem when writing data '1' to a cell      |    |

|           | sharing the same WBL. (b) Simulation results showing steady-state         |    |

|           | storage node voltage in case of no refresh. (c) Proposed regulated bit-   |    |

|           | line write bias generator based on replica cells                          | 15 |

| Fig. 2.6: I | PVT-tracking and die-to-die adjustable read reference bias (VDUM)                   |    |

|-------------|-------------------------------------------------------------------------------------|----|

|             | generator.                                                                          | 17 |

| Fig. 2.7: ( | (a) Simulation results of the proposed VDUM generator tracking                      |    |

|             | temperature and process variations. (b) Simulation results showing the              |    |

|             | dependency of VDUM on VDD.                                                          | 17 |

| Fig. 2.8: A | A 32 kb array structure of the proposed eDRAM including (a) boosted 3T              |    |

|             | gain cell, (b) hybrid current/voltage S/A, (c) regulated bit-line write             |    |

|             | scheme, and (d) PVT-tracking read reference scheme.                                 | 18 |

| Fig. 2.9: I | Read and write-back simulation waveform with a 2 ns random cycle time               | 19 |

| Fig. 2.10:  | Simulation setup for 1 M Monte Carlo simulations.                                   | 20 |

| Fig. 2.11:  | Read performance comparisons between 6T SRAM and 3T eDRAM                           |    |

|             | obtained from 2 <sup>20</sup> Monte-Carlo iterations. Results are equivalent to the |    |

|             | distribution of a 1 Mb macro array. 6T SRAM has the shortest bitline                |    |

|             | delay attributed to the differential swing nature and large drive current           |    |

|             | (361.7ps @ $6\sigma$ ) followed by the proposed 3T eDRAM (607.4ps @ $6\sigma$ )     |    |

|             | and the conventional 3T eDRAM (944.5ps @6σ).                                        | 21 |

| Fig. 2.12:  | Comparison of various logic-compatible embedded memory cell layouts                 |    |

|             | using a 65nm logic design rule (the authors did not have access to the              |    |

|             | dense bitcell design rule but for area comparison purposes, the logic               |    |

|             | design rule is generally acceptable). The outer box represents the cell             |    |

|             | boundary. Signal names, wire tracks, and device names are marked for                |    |

|             | the boosted 3T and conventional 3T cells                                            | 22 |

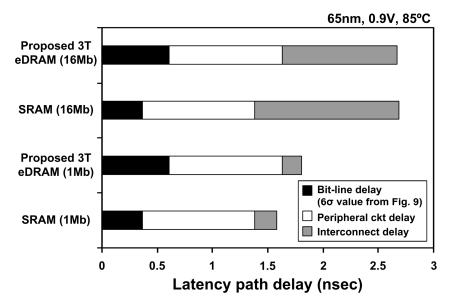

| Fig. 2.13: | Latency comparisons between SRAM and 3T eDRAM for 1 Mb and 16                 |

|------------|-------------------------------------------------------------------------------|

|            | Mb cache sizes. Gain cells have a shorter interconnect delay due to the       |

|            | smaller cell size making their performance favorable in larger arrays23       |

| Fig. 2.14: | Write delay distributions of 1Mb arrays using 6T SRAM and 3T                  |

|            | eDRAM                                                                         |

| Fig. 2.15: | Leakage components of a (a) 6T SRAM, a (b) conventional 3T eDRAM              |

|            | and the (c) proposed 3T eDRAM. (d) Bias conditions and normalized             |

|            | cell leakages of SRAM and 3T eDRAM in active and sleep modes25                |

| Fig. 2.16: | Static power comparisons between a 1 Mb SRAM and a 2 Mb 3T                    |

|            | eDRAM. Leakage power of the peripheral circuit is assumed to be               |

|            | negligible                                                                    |

| Fig. 2.17: | Comparison of logic-compatible embedded memories                              |

| Fig. 2.18: | Microphotograph of the 65 nm eDRAM test chip and feature summary28            |

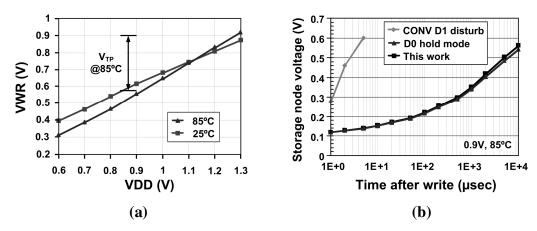

| Fig. 2.19: | (a) Measured regulated bit-line write bias (VWR) level. (b) Storage node      |

|            | voltage measurement results under data '1' disturbance conditions29           |

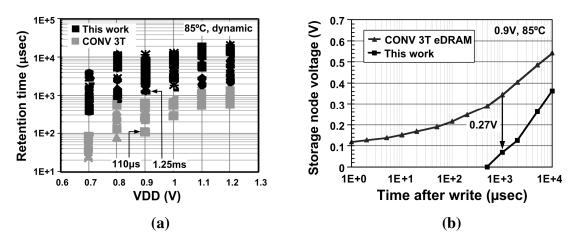

| Fig. 2.20: | (a) Measured retention time statistics. Due to limitations in the test setup, |

|            | only 32 cells were measured from each sub-array. The measured cells           |

|            | were located evenly across the memory array. (b) Measured storage             |

|            | node voltage in the proposed boosted 3T cell and the conventional 3T          |

|            | cell. The cell voltage was indirectly and noninvasively measured by           |

|            | sweeping the reference cell node voltage                                      |

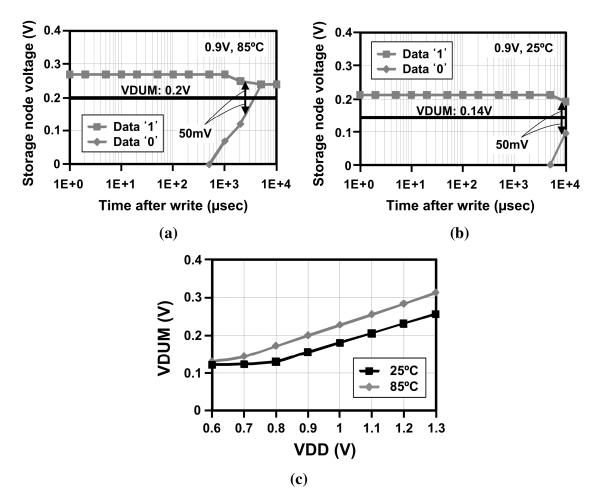

| Fig. 2.21: Measured storage node voltages at (a) 85°C and (b) 25°C. (c) Measured                       |

|--------------------------------------------------------------------------------------------------------|

| PVT-tracking read reference (VDUM) level at different supply voltages32                                |

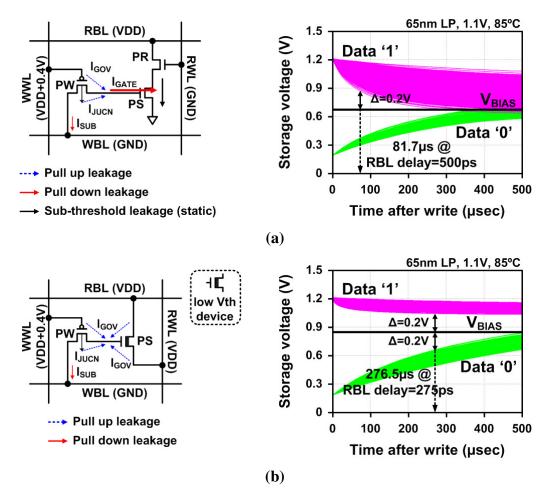

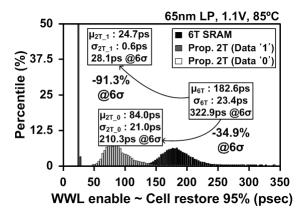

| Fig. 3.1: (a) Leakage components of a 3T NMOS gain cell during data hold mode.                         |

| (b) Monte-Carlo simulation results of storage node voltage during data                                 |

| hold mode showing 1 Mb macro retention characteristics35                                               |

| Fig. 3.2: Circuit diagrams and retention characteristics of (a) a previous                             |

| asymmetric 3T gain cell [16] and (b) the proposed asymmetric 2T gain                                   |

| cell                                                                                                   |

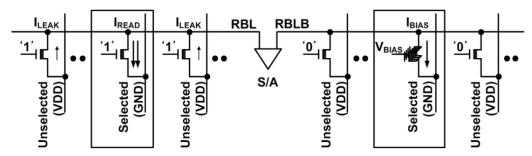

| Fig. 3.3: Illustration of limiting read margin by adjacent cells holding high state in                 |

| a 2T eDRAM                                                                                             |

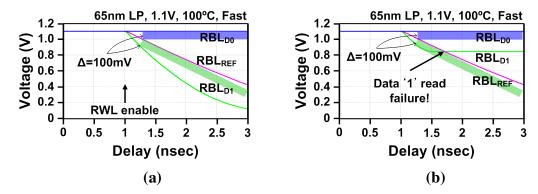

| Fig. 3.4: (a) Simulated RBL sensing waveform when all adjacent cells hold a data                       |

| '0'. (b) All adjacent cells hold a data '1' indicating a data '1' read failure.                        |

| The shaded regions denote the $\Delta V_{RBL}$ =100mV window between the                               |

| accessed RBL and the reference                                                                         |

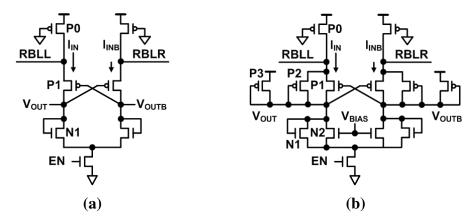

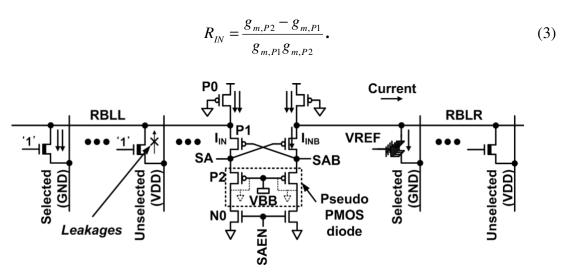

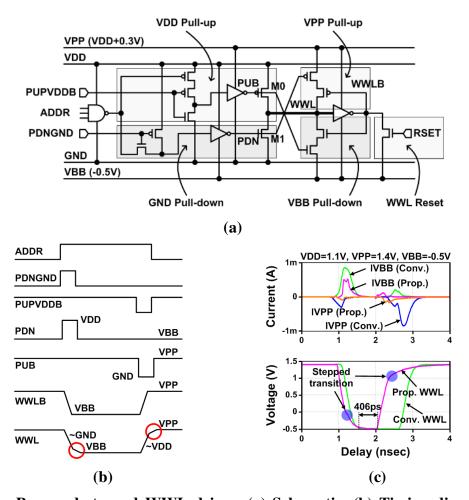

| Fig. 3.5: (a) NP series-stacked C-S/A [39]. (b) Hybrid C-S/A [40]41                                    |

| Fig. 3.6: Proposed pseudo-PMOS diode based C-S/A to overcome the issue of                              |

| limited RBL voltage swing in a 2T eDRAM with improved voltage                                          |

| headroom and better impedance matching                                                                 |

| Fig. 3.7: (a) Simulated input resistance ( $\Delta V_{RBL}/\Delta I_{IN}$ ) vs. VDD. (b) Comparison of |

| RBL sensing delay under PVT variations and mismatches in the C-S/A                                     |

| pairs43                                                                                                |

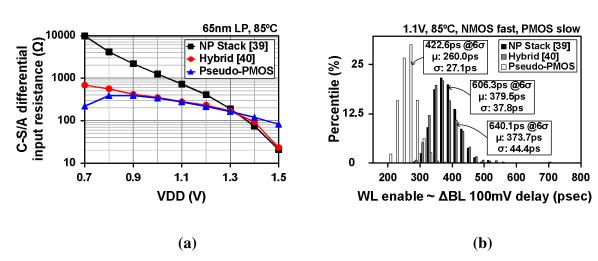

| Fig. 3.8:  | (a) Simulated waveforms of the WBL charging delay. (b) Simulated          |    |

|------------|---------------------------------------------------------------------------|----|

|            | storage voltage distributions of a conventional GND pre-discharge (full   |    |

|            | swing WBL) and the proposed half-VDD pre-charge (half swing WBL)          |    |

|            | schemes                                                                   | 44 |

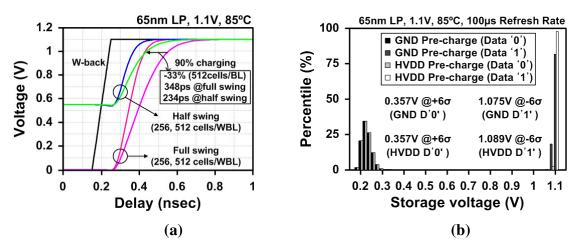

| Fig. 3.9:  | Proposed stepped WWL driver. (a) Schematic. (b) Timing diagram. (c)       |    |

|            | Simulated boosted current consumptions and WWL waveforms during           |    |

|            | transition.                                                               | 46 |

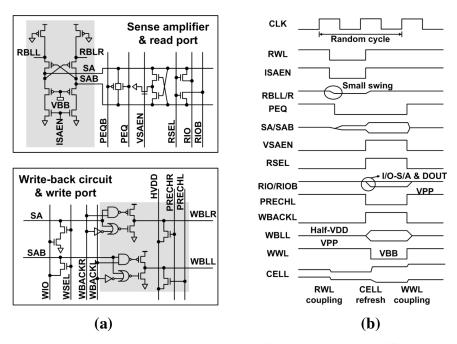

| Fig. 3.10: | (a) Circuit diagram of the proposed Sense Amplifier (S/A) with read port, |    |

|            | write port, and write-back circuits. (b) Two-stage read and write-back    |    |

|            | timing diagram.                                                           | 47 |

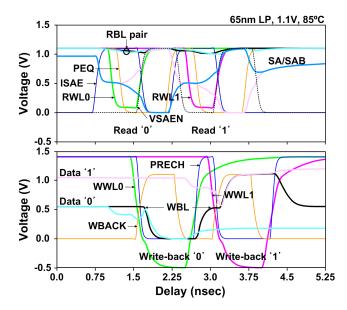

| Fig. 3.11: | Simulated waveforms of back-to-back read and write-back operations for    |    |

|            | a 1.5 ns cycle time.                                                      | 48 |

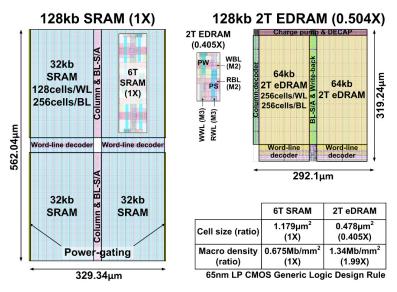

| Fig. 3.12: | Comparison of bit-cell and 128 kb sub-array layout between 6T SRAM        |    |

|            | and 2T eDRAM                                                              | 49 |

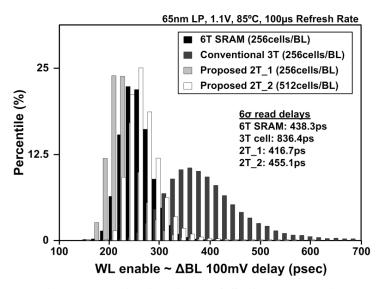

| Fig. 3.13: | RBL sensing delay distributions of SRAM and gain cell eDRAMs each         |    |

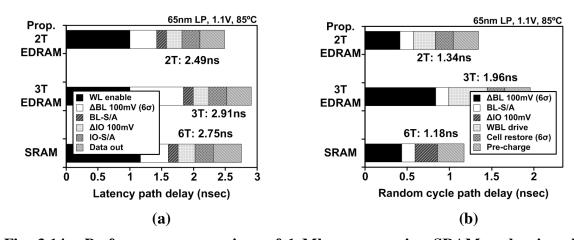

|            | with a 1 Mb macro density.                                                | 50 |

| Fig. 3.14: | Performance comparison of 1 Mb macros using SRAM and gain cell            |    |

|            | eDRAMs. (a) Latency. (b) Random cycle.                                    | 51 |

| Fig. 3.15: | Performance comparison of 1 Mb macros using SRAM and gain cell            |    |

|            | eDRAMs. (a) Latency. (b) Random cycle                                     | 52 |

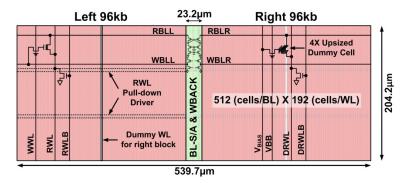

| Fig. 3.16: | A 192 kb test array architecture with 192 cells-per-WL and 512 cells-     |    |

|            | par PI                                                                    | 52 |

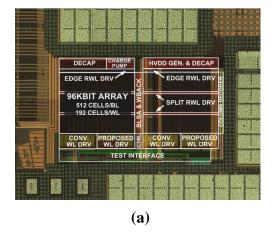

| Fig. 3.17:  | (a) Microphotograph of the 65nm eDRAM test chip. (b) Chip feature         |

|-------------|---------------------------------------------------------------------------|

|             | summary53                                                                 |

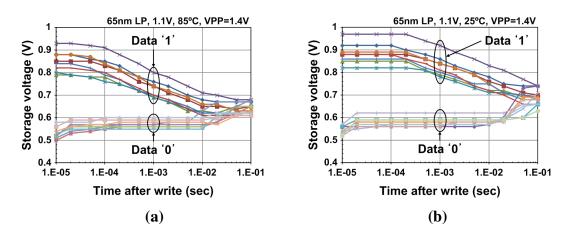

| Fig. 3.18:  | Measured storage node voltage at different retention times at (a) 85°C    |

|             | and (b) 25°C                                                              |

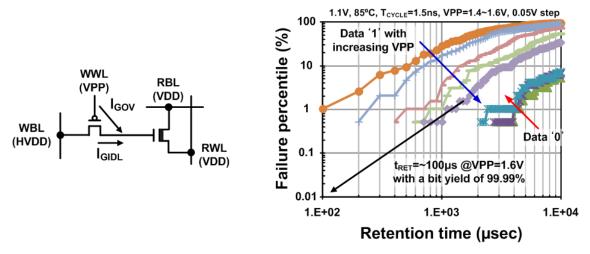

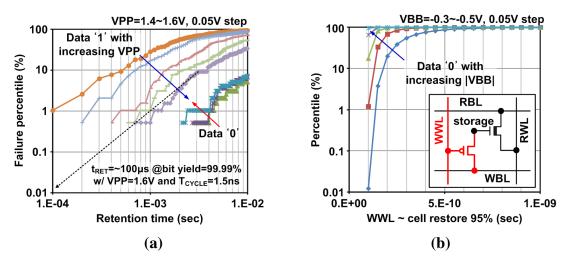

| Fig. 3.19:  | Measured retention time distribution vs. boosted high supply (VPP) level. |

|             | 55                                                                        |

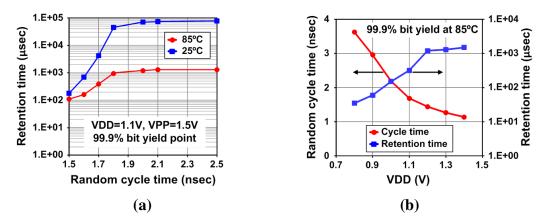

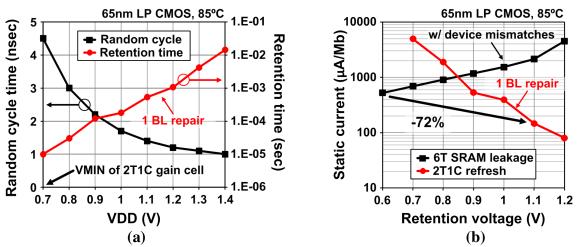

| Fig. 3.20:  | (a) Measured random cycle time vs. retention time. (b) Measured VDD       |

|             | shmoo of random cycle time and corresponding retention time56             |

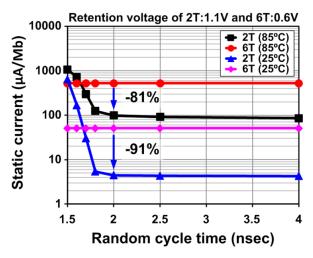

| Fig. 3.21:  | Static power comparison between 6T SRAM and the proposed 2T               |

|             | eDRAM with varying random cycle time at 85 °C and 25 °C57                 |

| Fig. 4.1:   | Impact of boosted supply level on 2T eDRAM performance [35]. (a)          |

|             | Boosted high supply (VPP) level vs. retention time (measured). (b)        |

|             | Boosted low supply (VBB) level vs. data '0' write time (simulated)60      |

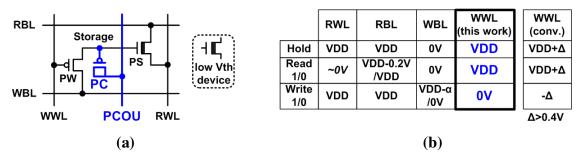

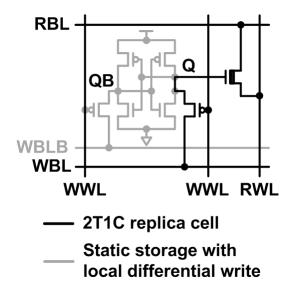

| Fig. 4.2: 1 | Proposed 2T1C gain cell based on thin oxide devices with no boosted       |

|             | supplies. (a) Schematic. (b) Signal conditions for each operating modes61 |

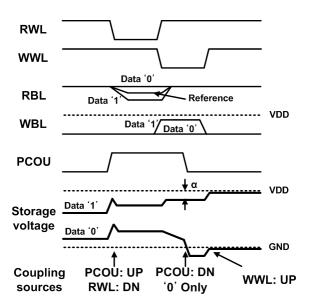

| Fig. 4.3:   | Timing diagram of the proposed 2T1C cell for read and write-back          |

|             | operations                                                                |

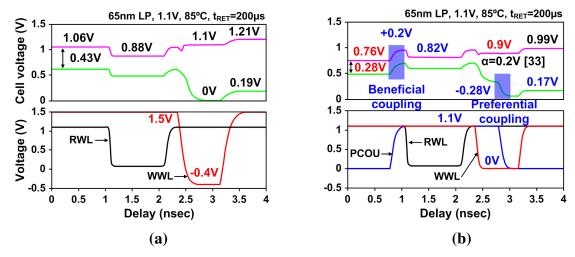

| Fig. 4.4: S | Simulated waveforms of read and write-back operations for (a) a           |

|             | conventional 2T eDRAM and (b) the proposed 2T1C eDRAM63                   |

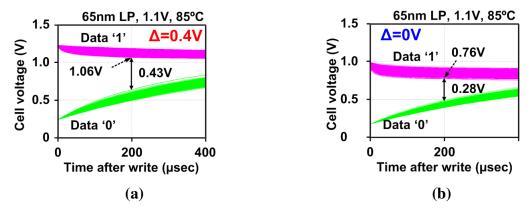

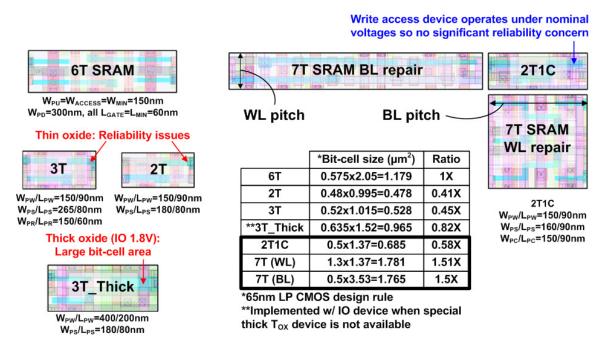

| Fig. 4.5: 0 | Comparison of retention characteristics between (a) a conventional 2T     |

|             | eDRAM with boosted supplies and (b) the proposed 2T1C eDRAM with          |

|             | no boosted supplies                                                       |

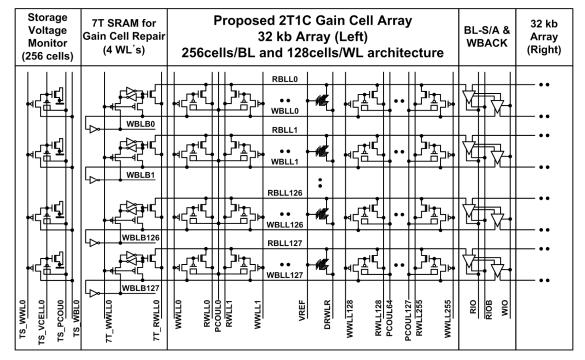

| Fig. 4.6: Sche | ematic diagram of a 64 kb 2T1C gain cell eDRAM macro with no          |    |

|----------------|-----------------------------------------------------------------------|----|

| boo            | osted supplies6                                                       | 54 |

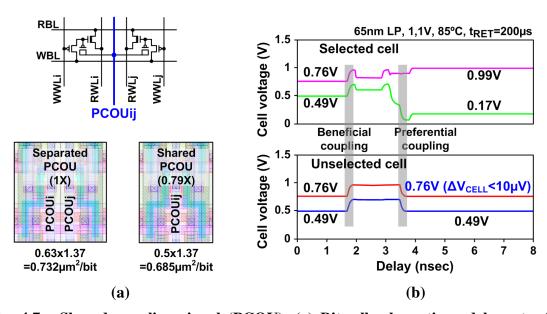

| Fig. 4.7: Shar | red coupling signal (PCOU). (a) Bit-cell schematic and layouts. (b)   |    |

| Sin            | mulated waveforms show negligible disturbance in an unselected cell6  | 55 |

| Fig. 4.8: Prop | posed decoupled 7T SRAM repair cell shares BL and WL signals with     |    |

| the            | e 2T1C cell6                                                          | 56 |

| Fig. 4.9: Sign | nal-to-noise margin (SNM) of a 6T SRAM and the proposed 7T            |    |

| SR             | RAM. (a) Read SNM. (b) Write SNM.                                     | 57 |

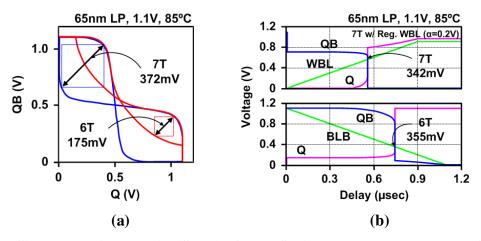

| Fig. 4.10: Bit | t-cell comparison(6T SRAM, 3T, 2T, 2T1C cells): All bit-cells were    |    |

| dra            | awn in a generic 65 nm LP process                                     | 58 |

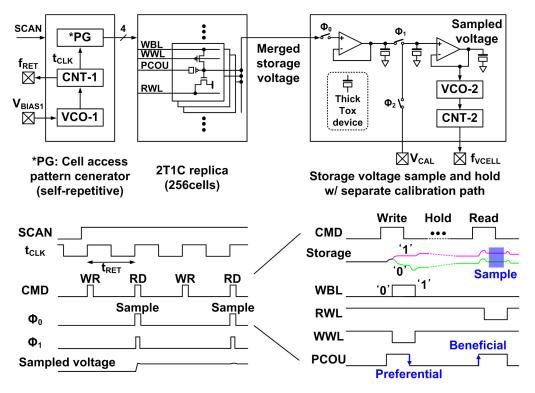

| Fig. 4.11: Pro | oposed storage voltage monitor for adaptive refresh control           | 70 |

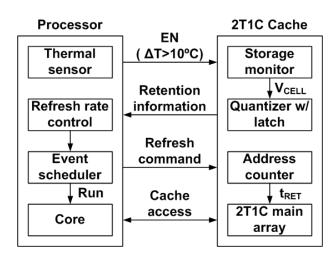

| Fig. 4.12: Blo | ock diagram of the adaptive refresh control.                          | 71 |

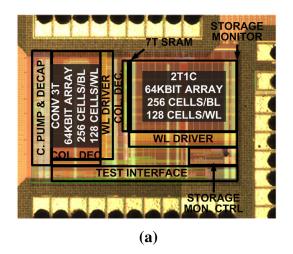

| Fig. 4.13: (a) | Microphotograph of the 65 nm eDRAM test chip. (b) Chip feature        |    |

| sur            | mmary                                                                 | 72 |

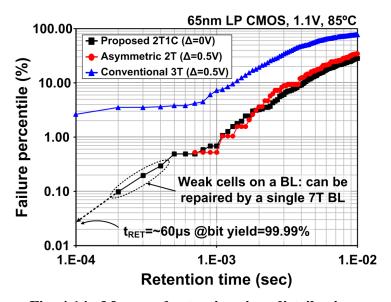

| Fig. 4.14: Me  | easured retention time distribution.                                  | 73 |

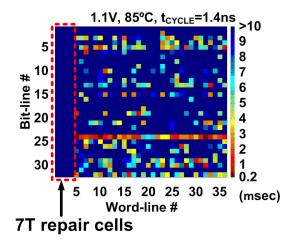

| Fig. 4.15: Me  | easured retention bit-map of 2T1C and decoupled 7T arrays             | 74 |

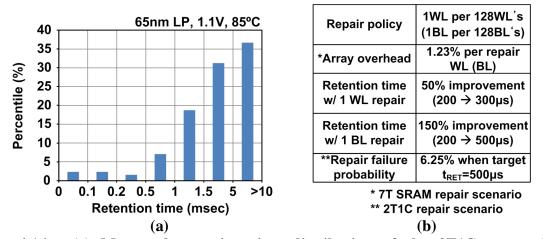

| Fig. 4.16: (a) | Measured retention time distribution of the 2T1C array. (b)           |    |

| Eff            | fectiveness of various repair schemes                                 | 74 |

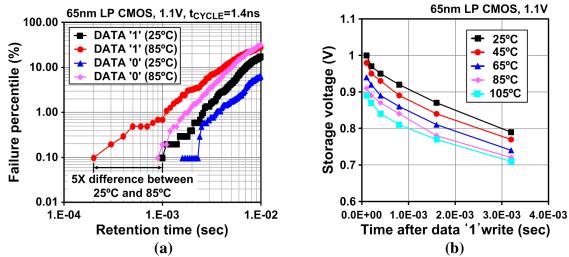

| Fig. 4.17: (a) | Measured retention time distribution of data '1' and '0' at 25 °C and |    |

| 85             | °C. (b) Measurement storage voltage with varying temperature and      |    |

| rate           | cantion time                                                          | 75 |

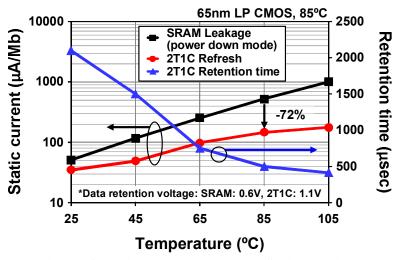

| Fig. 4.18: | Comparison of static current between SRAM (with power-gating) and             |

|------------|-------------------------------------------------------------------------------|

|            | 2T1C eDRAM (with adaptive refresh control)                                    |

| Fig. 4.19: | Measured VDD shmoo. (a) Random cycle time and retention time of the           |

|            | 2T1C eDRAM. (b) Static power dissipations of a 6T SRAM and the                |

|            | 2T1C eDRAM                                                                    |

| Fig. 4.20: | Comparison between our design and several embedded memory options77           |

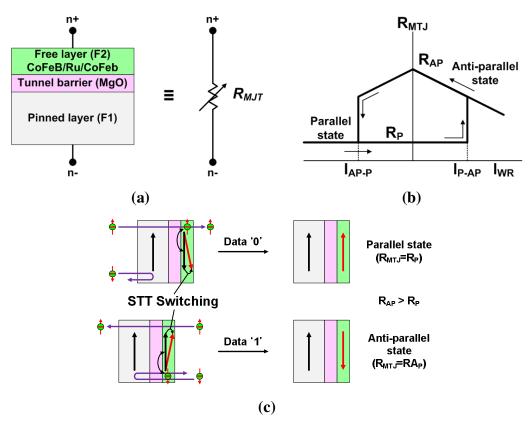

| Fig. 5.1:  | (a) Magnetic tunnel junction (MTJ) stack and its corresponding circuit        |

|            | schematic as a two-terminal device with varying resistance. (b)               |

|            | Resistance vs. write current (R-I) hysteresis curve. (c) Illustration of spin |

|            | torque transfer (STT) switching's                                             |

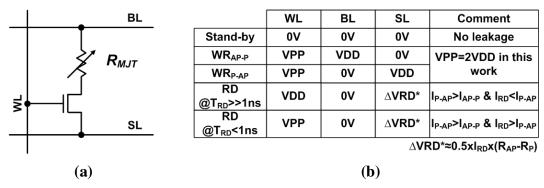

| Fig. 5.2:  | (a) STT-MRAM bit-cell schematic. (b) Signal voltages for each operating       |

|            | mode82                                                                        |

| Fig. 5.3:  | STT-MTJ scaling scenario based on dimensional adjustment and/or               |

|            | material innovation in order to maintain non-volatility and achieve           |

|            | optimal RD and WR operations.                                                 |

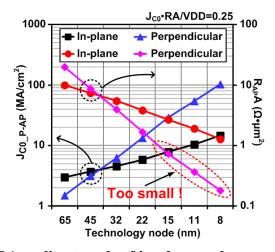

| Fig. 5.4:  | In-plane and perpendicular STT-MTJ scaling trends based on Fig. 5.386         |

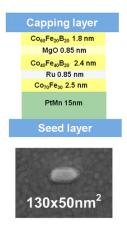

| Fig. 5.5:  | Vertical structure and SEM image of fabricated STT-MTJ (left) and             |

|            | summary of measured MTJ parameters (right)87                                  |

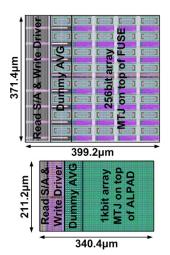

| Fig. 5.6:  | STT-MTJ characterization array layout and test chip feature summary88         |

| Fig. 5.7:  | MTJ macromodel fitting results using MTJ data from our characterization       |

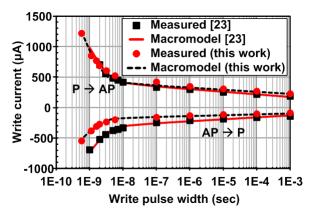

|            | array and [23]89                                                              |

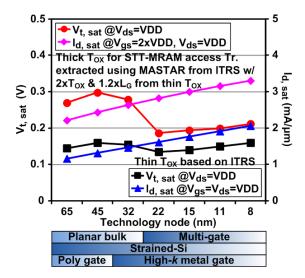

| Fig. 5.8:  | High performance (HP) transistor scaling trend based on ITRS91                |

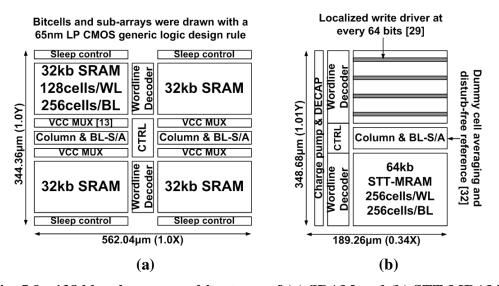

| Fig. 5.9:  | 128 kb sub-array architectures of (a) SRAM and (b) STT-MRAM            | 92  |

|------------|------------------------------------------------------------------------|-----|

| Fig. 5.10: | Simulation set-up for evaluating SRAM and STT-MRAM variability         | 93  |

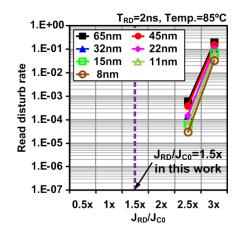

| Fig. 5.11: | Simulated read disturb rate with varying $J_{\text{RD}}/J_{\text{C0}}$ | 93  |

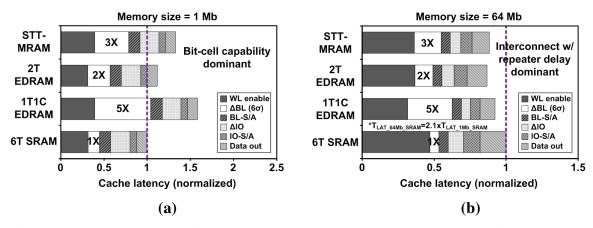

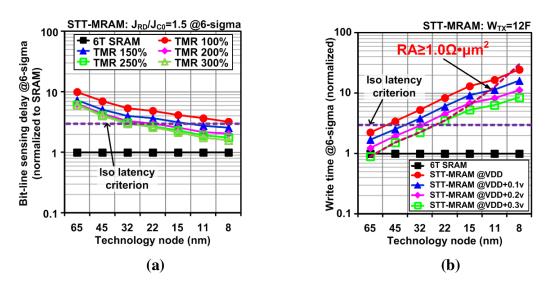

| Fig. 5.12: | Latency comparison between several embedded memory options with (a)    |     |

|            | 1 Mb and (b) 64 Mb densities.                                          | 95  |

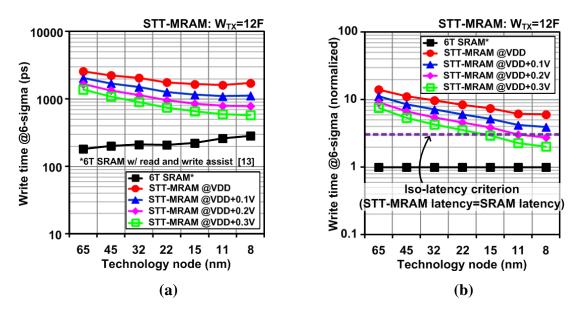

| Fig. 5.13: | In-plane STT-MRAM scaling trends: Write time. (a) Absolute values.     |     |

|            | (b) Normalized to SRAM.                                                | 96  |

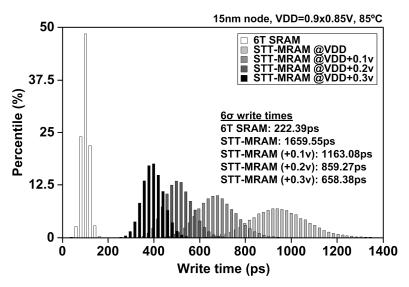

| Fig. 5.14: | Write time distributions of SRAM and in-plane STT-MRAM (P-AP) for      |     |

|            | a 1 Mb macro density at 15 nm node.                                    | 97  |

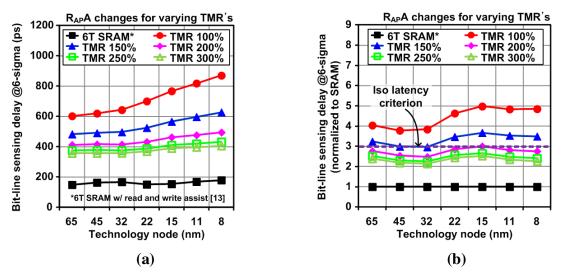

| Fig. 5.15: | In-plane STT-MRAM scaling trends: Read sensing delay. (a) Absolute     |     |

|            | values. (b) Normalized to SRAM                                         | 98  |

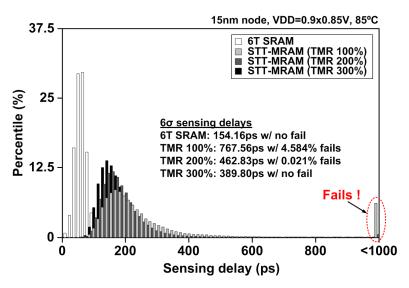

| Fig. 5.16: | Read sensing delay distributions of SRAM and in-plane STT-MRAM for     |     |

|            | a 1 Mb macro density at 15 nm node.                                    | 98  |

| Fig. 5.17: | $J_{C0}$ and RA scaling trends of in-plane and perpendicular STT-MTJs  | 99  |

| Fig. 5.18: | Perpendicular STT-MRAM scaling trends. (a) Sensing delay comparison    |     |

|            | with SRAM. (b) Write time comparison with SRAM                         | 100 |

## **Chapter 1**

#### Introduction

Multi-core processors exploit microarchitecture-level parallelism to deliver higher computing performance while curbing chip power dissipation. The number of cores per socket has increased at a pace of two per year for high end enterprise processors [1]. There needs to be a commensurate increase in the amount of on-die embedded memory in order to utilize the multi-core architecture fully with a larger appetite for data [1]-[3]. As a result, in the past decade, the die area devoted to cache memory has grown to approximately 50% in state-of-the-art processors (Fig. 1.1). For example, Intel's 8-core enterprise Xeon<sup>TM</sup> processor has a 24 MB Last Level Cache (LLC) [1] based on SRAM cells while IBM's POWER7<sup>TM</sup> processor has a 32 MB L3 cache built in an embedded DRAM (eDRAM) technology [4], [5]. The need for robust high-density embedded memories is projected to grow as designers continue to seek power-conscious ways to improve multi-core chip performance.

However, delivering dense embedded memories with higher performance for computing systems have faced with a unique scaling challenge compared to logic circuits. With technology scaling, transistor parameters and parasitic loadings are innovated in

such a way that enhances the performance of the core that is the most important building block in microprocessors. On the other side of the technology scaling, embedded memories, which are the other essential component in computing systems, have suffered from the reduced signal-to-noise margin due to the scaled power supply level for device reliability and power constraint. Furthermore, memory bit-cells implemented using minimally sized devices are susceptible to device mismatches, various noise couplings, and sense amplifier offsets resulting in the difficulty of maintaining the traditional scaling trend in advanced CMOS technologies such as sub-22 nm node.

| High-end microprocessor @ 45nm node |                              |                            |  |  |  |

|-------------------------------------|------------------------------|----------------------------|--|--|--|

|                                     | Enterprise Xeon <sup>™</sup> | POWER7 <sup>™</sup>        |  |  |  |

|                                     | 6T SRAM<br>L3 (24MB)         | 1TIC eDRAM<br>L3 (32MB)    |  |  |  |

|                                     | S. Rusu <i>et al</i> [1]     | J. Barth e <i>t al</i> [5] |  |  |  |

| Cores                               | 8                            | 8                          |  |  |  |

| L3 cache                            | 24MB (6T SRAM)               | 32MB (1T1C EDRAM)          |  |  |  |

| Transistor count                    | 2.3B                         | 1.2B                       |  |  |  |

| Cache bitcell size                  | 0.346µm² (1X)                | 0.0672μm² (0.194X)         |  |  |  |

| Chip size                           | 684mm² (1X)                  | 567mm² (0.829X)            |  |  |  |

| L3 portion over<br>chip             | ~45% @24MB<br>~55% @32MB     | ~33% @32MB                 |  |  |  |

Fig. 1.1: High-end microprocessors with high density on-die L3 caches based on 6T SRAM and 1T1C eDRAM.

#### 1.1 Embedded Memories in Multi-Core Microprocessor

6T SRAMs and 1T1C eDRAMs have been the embedded memory of choice. The logic compatible bit-cell, fast differential read, and refresh-free operation make 6T

SRAMs the most viable option for on-die cache memories. 1T1C eDRAMs have features such as small cell size, low cell leakage, and non-ratioed circuit operation. The smaller footprints of 1T1C eDRAMs reduce global interconnect delay and enable faster overall system performance in high density cache memories [4]-[9]. Fig. 1.2 shows the trend of Intel's and IBM's high-end microprocessors based on 6T SRAM cells [10]-[15] and 1T1C DRAM cells [5], [6], respectively. The number of cores per socket has doubled at every process generations with commensurate increases of cache densities, namely 4 MB L3 caches have been added for every additional core (Fig. 1.2(a)). However, the aforementioned trend has deviated from 45 nm due to the difficulty of achieving practical parallel computing performance as the chip design and programming become more complicated with the increased core count. Delivering a dense and stable embedded memory is another constraint limiting the continuance of the traditional way to achieve higher computing performance while curbing chip power dissipation. The relatively large cell size and conflicting requirements for read and write at low operating voltages make aggressive scaling of 6T SRAMs challenging in scaled CMOS technologies. The bit-cell scaling trend of the 6T SRAMs has deviated from 45 nm due to the abovementioned technological difficulties, while the 1T1C eDRAMs have followed the 0.5X bit-cell scaling trend up to 45 nm (Fig. 1.2(b)). However, the noise margin of 1T1C eDRAMs is reduced substantially at low voltages as the read operation is based on the charge sharing principle, and difficulties in scaling the trench capacitor and the additional process steps involved in manufacturing the thick oxide (T<sub>OX</sub>) access devices are currently limiting the wide spread adoption of 1T1C technology. As a matter of fact,

only a limited company has been able to deliver stable 1T1C eDRAMs for high density on-die caches [4]-[6].

Fig. 1.2: (a) Trend of number of cores and corresponding on-die L3 cache densities in Intel's and IBM's high-end microprocessors. (b) Bit-cell size scaling trend of 6T SRAMs and 1T1C eDRAMs.

#### 1.2 Alternative Memory Technologies

Gain cell eDRAMs and spin-torque-transfer magnetic RAMs (STT-MRAMs) are gaining popularity in the research community due to their compact bit-cells and excellent scalabilities. Gain cells are implemented using logic devices allowing them to be built in a standard CMOS process with minimal adjustments. The cell can be implemented using three transistors, or even two transistors when used with delicate read control circuits, achieving a roughly 2X higher bit-cell density than SRAM as recently demonstrated by several industrial designs [16]-[19]. Furthermore, gain cells can have smaller cell leakage current than SRAMs in sleep mode due to the fewer number of devices and the negative-Vgs biasing condition. Therefore, the static power dissipation of gain cell

eDRAM including both leakage and refresh components can be smaller than that of SRAMs and similar to that of 1T1C eDRAMs. The cell write margin is better than SRAMs since there is no contention between the access device and the cross-coupled latch in a gain cell. Despite these favorable attributes, conventional gain cells suffer from short retention times due to the small storage capacitor and leakage currents that vary exponentially under Process-Voltage-Temperature (PVT) variations [16]-[19]. A shorter retention time leads to higher refresh power dissipation and/or smaller read current. The former is a result of the frequent refresh operation while the latter is due to the fast loss of cell voltage. Frequent refresh operation also reduces memory availability resulting in degradation in overall system performance. Therefore, attaining practical retention time and improving random access speed remain as key challenges in gain cell eDRAM designs. In this dissertation, three unique test chip designs are presented to enhance the retention time and random access speed of gain cell eDRAMs for achieving overall faster system performances and lower power dissipations than SRAMs and 1T1C eDRAMs.

As the second part of this dissertation, STT-MRAMs are investigated to evaluate their potential as an alternative for high density on-die caches. An STT-MRAM bit-cell consists of an access transistor and a magnetic tunnel junction (MTJ). The simple structure makes the bit-cell size of STT-MRAM comparable to that of an eDRAM in a memory specific process. The MTJ device has a free magnetic layer and a pinned magnetic layer which are separated by a thin insulator layer. Depending on the direction of the write (WR) current, magnetization of the two layers can be set to a parallel state (P: low resistance, data '0') or an anti-parallel state (AP: high resistance, data'1') using spin

polarized current. Read (RD) operation is accomplished by sensing the resistance difference between the two states using voltage or current Sense Amplifier (S/A).

The state reversal happens only to the selected bit-cell when the current flowing into the MTJ is larger than its threshold current (write threshold current; I<sub>C0</sub>). The STT switching originates from the exchange of angular momentum between a spin-polarized current and the magnetization of the free layer. The localized spin-injection within a bitcell enables the excellent write selectivity with no high oxide field involved nor high temperature required during the process, which are the most critical scaling challenges in currently popular non-volatile memories such as FLASHs and phase-change RAMs (PCRAMs or PRAMs). Most interestingly, the I<sub>C0</sub> decreases exponentially with technology scaling as the critical current density ( $J_{C0}$ ) remains constant due to the STT switching phenomenon when there is no thermal stability constraint. Therefore, the slow write time (T<sub>WR</sub>) which is several nanoseconds or even larger, is projected to be relieved with technology scaling [20]-[22]. Despite the recent advances in STT-MRAM fabrication and circuit techniques [23]-[32], it is still unclear whether this emerging memory technology can achieve higher overall performance than conventional SRAMs or eDRAMs in future technology nodes in the presence of variation effects. In this dissertation, I explore the scalability and variability of STT-MRAM by comparing its performance with 6T SRAM from 65 nm to 8 nm process nodes.

#### 1.3 Summary of Dissertation Contributions

The remainder of this dissertation will explore the benefits of various circuit techniques and HSPICE simulation methodologies that we have proposed to demonstrate the potential of gain cell eDRAMs and STT-MRAMs as alternative options for high density embedded memories. Three unique test chip designs will be presented to enhance the retention time and read speed of gain cell eDRAMs, enabling faster overall system performances and lower static power dissipations than SRAMs and eDRAMs [33]-[37]. An MTJ scaling scenario, an efficient HSPICE simulation methodology, and a characterization macro are described for exploring the scalability of STT-MRAMs under variation effects from 65 nm to 8 nm, demonstrating that the alternative option can outperform SRAMs and eDRAMs in advanced CMOS technologies [38].

## Chapter 2

## A 3T Embedded DRAM Utilizing Preferential Boosting for Low Voltage On-Die Caches

#### 2.1 Basic Operation of a Conventional 3T EDRAM

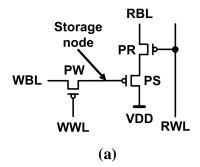

To aid the understanding of our proposed techniques, in this section, the basic operation of a conventional 3T gain cell eDRAM is described. Fig. 2.1(a) shows the cell schematic and Fig. 2.1(b) summarizes the signal conditions for each operating mode.

|     | Data hold | Read 0/1 | Write 0/1 |  |

|-----|-----------|----------|-----------|--|

| RWL | VDD       | 0V       | VDD       |  |

| RBL | 0V        | 200mV/0V | 0V        |  |

| WWL | VDD       | VDD      | -500mV    |  |

| WBL | 0V        | 0V       | 0V/VDD    |  |

| (b) |           |          |           |  |

Fig. 2.1: (a) Conventional 3T PMOS eDRAM gain cell circuit diagram. (b) Signal voltages in each operating mode.

PMOS devices are chosen over NMOS devices because they have significantly less gate tunneling leakage current, which extends the data retention time [19]. This

preference may not hold in the future where high-*k* gate dielectrics become prevalent. The operating principle of an NMOS cell is identical to that of a PMOS cell with the only difference being the signal polarities. In the 3T PMOS cell, PW denotes the write access device, PS denotes the cell storage device, and PR denotes the read access device. In write (or write-back) mode, the Write Bit-Line (WBL) data is written into the storage node through PW. Similar to a 1T1C eDRAM cell, the Write World-Line (WWL) is negatively over-driven so that a 0 V can be written into the cell without the threshold voltage loss. In read mode, the pre-discharged Read Bit-Line (RBL) voltage is pulled up only when the voltage stored in the gate of PS is low. In case the storage voltage is high, PS is off so RBL remains at the pre-discharged level. Cell data can be determined by comparing the RBL voltage with a reference RBL, whose level is between the data '1' and data '0' RBL levels, using a sense amplifier.

During hold mode, PW and PR are turned off and the storage node is left floating. The sub-threshold, gate, and junction leakages in the surrounding devices make the floating voltage change with time as shown in Fig. 2.2. Since the storage node is surrounded by high voltages in the PMOS cell, the retention time of data '0' is much shorter than data '1'. Similarly, the retention time of data '1' becomes critical in an NMOS cell where the surrounding signal voltages are 0 V during hold mode. The data retention time is directly related to the aggregated leakage currents flowing into the storage node. In the presence of process variation, each cell in a memory array will have different retention characteristics so the cell with the shortest retention time (after

applying any redundancy schemes to remove bad cells) will determine the refresh rate of the entire eDRAM array.

Fig. 2.2: Monte Carlo simulation results of storage node voltage during data hold mode.

Fig. 2.2 shows the simulation results of cell retention time variation. This plot was obtained by running Monte-Carlo simulations in HSPICE with 1024 iterations, which gives a cell-to-cell variation equivalent to a 1 kb array. Results indicate that the time it takes for the data '0' voltage to rise to a specific voltage (0.3 V in this simulation to guarantee a 0.3V gate over-drive voltage in the storage transistor which has a  $V_{TP}$  of 0.3 V) ranges from 58  $\mu$ s to 345  $\mu$ s at a 0.9 V supply voltage and 85 °C temperature. Poor retention characteristics of tail cells result in a large refresh current and decreased read performance. Therefore, increasing the cell retention time is the foremost challenge in low voltage gain cell eDRAMs.

#### 2.2 Boosted 3T EDRAM Design

In this section, three circuit techniques are presented for improving the eDRAM data retention time and ensuring robust circuit operation under PVT variations.

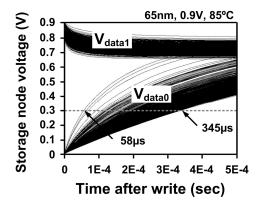

#### 2.2.1 Boosted 3T Gain Cell

The retention time and read speed of eDRAMs are highly dependent upon the storage node voltage at the time when the cell is accessed. Even a small signal loss can cause severe speed degradation at low operating voltages. Fig. 2.3(a) shows the proposed 3T PMOS gain cell which can preferentially boost the storage voltage via capacitive coupling. Unlike the conventional design in Fig. 2.1(a), the drain of the storage device PS is connected to the RWL signal instead of the supply voltage. For read operation, RBL is first precharged to VDD and then the RWL switches from VDD to 0V. The resultant bitline signal is detected by a sense amplifier. The central idea of the proposed cell is to preferentially boost the storage node voltage using the RWL signal for improving the cell's data retention capability. For example, consider the case when the storage node voltage is low (e.g. 0V). This will make the gate-to-RWL coupling capacitance larger compared to when the storage node voltage is high (e.g. VDD). PS in inversion mode makes the entire oxide capacitance act as the coupling capacitance whereas PS in weak-inversion mode, the significantly smaller depletion capacitance acts as the coupling capacitance. Since a lower storage voltage has a larger coupling capacitance, it is coupled down more than a higher storage voltage when the RWL switches from high to low as illustrated in Fig. 2.3(b). This preferential boosting action amplifies the signal difference during read which allows the storage node voltage to decay further before it needs to be refreshed. This translates into a longer effective data retention time. A similar concept was proposed by Luk et al., where a 3T1D cell was used to boost the cell voltage [18]. However, this cell structure requires an additional

diode device which increases the cell area as well as the gate tunneling leakage. It also has a limited signal amplification effect since the storage device acts as a parasitic capacitor limiting the amount of coupling that can be achieved. The proposed boosted 3T gain cell can provide a stronger coupling effect with only three transistors, increasing data retention time, enhancing the RBL margin and improving read performance.

Fig. 2.3: (a) Proposed boosted 3T PMOS eDRAM gain cell. (b) Preferential RWL coupling effects of the proposed cell. (c) Simulation results of the storage node preferential boosting effects. (d) Signal voltage conditions for each operating mode.

Simulation results in Fig. 2.3(c) verify that the data '0' voltage is amplified by 0.3 V while the data '1' voltage is coupled down by only 0.16 V. In addition to the amplification effect, the proposed cell can provide a ~2X larger current than conventional 3T gain cells since the boosted voltage provides a higher gate overdrive for PS. Fig. 2.3(d) summarizes the signal conditions for each operating mode for the proposed gain cell. It should be pointed out that the higher drive current is only observed when the RBL level is high, as the read current quickly diminishes as the RBL voltage drops due to the V<sub>TP</sub> loss in the PMOS read device. To utilize the boosted read current of the proposed 3T cell, we employ a hybrid current/voltage sense amplification technique that keeps the RBL level close to VDD during the read operation [39], [40].

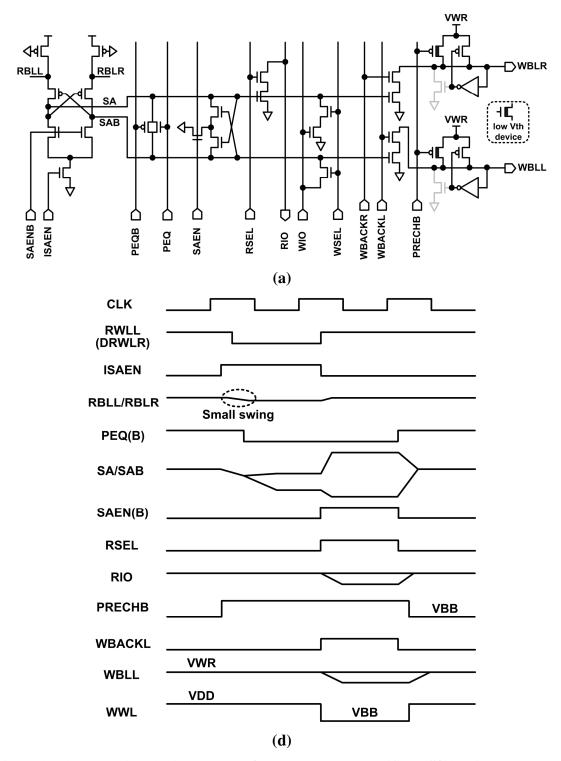

Fig. 2.4 shows the schematic and timing diagram of the bit-line Sense Amplifier (S/A) consisting of a hybrid current/voltage S/A, read port, write port and drivers for write-back. During read, the RBL signals to the current S/A are amplified and converted to voltage signals through a cross-coupled PMOS pair and a NMOS resistor pair while a load PMOS pair keeps the RBL swing small. After transferring the input differential current, the cross-coupled PMOS pair, in tandem with the cross-coupled NMOS pair, acts as a voltage S/A which generates a full CMOS swing signal. Dedicated timing control circuits are implemented for the equalizer to ensure stable current S/A operation as shown in Fig. 2.4(b). The write-back operation automatically follows the read cycle to refresh the cell data.

Fig. 2.4: (a) Hybrid bit-line current/voltage sense amplifier (S/A) with read port, write port, and write-back circuits. (b) Read and write-back timing diagram of the proposed S/A.

#### 2.2.2 Regulated Bit-Line Write Scheme

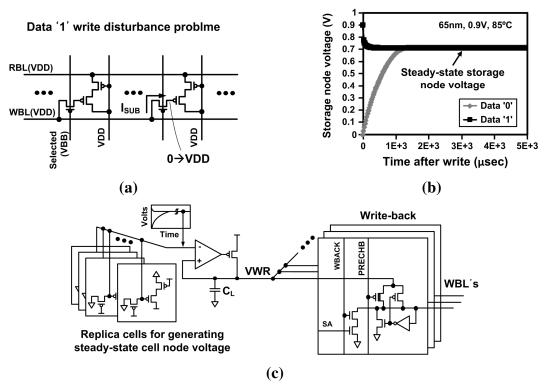

When the WBL is driven to data '1', the data '0' levels in the unselected cells on the same WBL are pulled up by the sub-threshold leakage through the write access PMOS devices as shown in Fig. 2.5(a). Most DRAM designs use a boosted supply for the WWL to prevent the signal loss in the unselected cells by asserting a negative Vgs in the write access devices. However, this method incurs area and power penalty due to the large charge pump capacitors and poor pumping efficiency at low voltages. In this work, we propose a regulated bit-line write scheme which can eliminate the data '1' disturbance issue without having to generate an additional boosted supply.

Fig. 2.5: (a) Storage node disturbance problem when writing data '1' to a cell sharing the same WBL. (b) Simulation results showing steady-state storage node voltage in case of no refresh. (c) Proposed regulated bit-line write bias generator based on replica cells.

Without a refresh, the storage node voltage eventually converges to a steady-state level close to VDD regardless of the initial cell voltage as shown in Fig. 2.5(b). In our design, we use this steady-state voltage level for writing data '1', as it will produce a negative Vgs in all the unselected cells without impacting the retention time of the selected cell. Note that the retention time is determined by the data '0' cell voltage rather than the data '1' voltage in a PMOS gain cell. A steady-state storage node voltage monitor shown in Fig. 2.5(c) is implemented with replica cells biased in hold mode, followed by a voltage down converter to drive the large WBL load. The speed loss due to the regulated bit-line write voltage (VWR) is prevented by pre-charging the WBL to VWR using the negative supply VBB as the gate signal, which is readily available on-chip for the WWL under-drive.

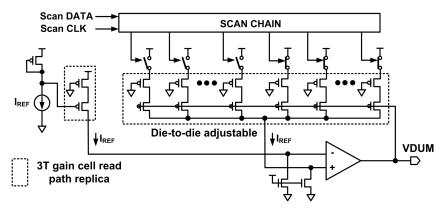

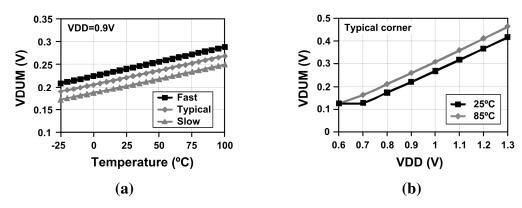

#### 2.2.3 PVT-Tracking Read Reference Bias

An optimal bias voltage (VDUM) is applied to the reference dummy cells to maximize the read operating margin. VDUM must be carefully chosen as it affects both the data retention time and the read speed; a higher VDUM level improves the data retention time at a read speed penalty. Fig. 2.6 shows the proposed PVT-tracking and die-to-die adjustable read reference bias generator to cope with PVT variations. The negative feedback circuit tracks the desired cell read reference current (I<sub>REF</sub> in the figure). Fig 2.7 shows simulation results of the proposed VDUM level under PVT variations. Unlike previous designs which use a fixed VDUM level or a simple averaging scheme [19], our circuit can achieve the target retention time without sacrificing read speed by adaptively lowering the VDUM level at low leakage PVT conditions as shown in Fig. 2.7.

For example, at lower temperatures or in slow corner dies, the excess retention time is traded off for faster read speed by lowering the VDUM level. Similarly, at low supply voltages, the VDUM level is shifted down since the reduced leakage make the storage node voltage lower compared to at high supply voltages for the same retention time. Binary weighted read path replica branches are implemented to precisely adjust the VDUM level according to the retention characteristics and read performance of each chip.

Fig. 2.6: PVT-tracking and die-to-die adjustable read reference bias (VDUM) generator.

Fig. 2.7: (a) Simulation results of the proposed VDUM generator tracking temperature and process variations. (b) Simulation results showing the dependency of VDUM on VDD.

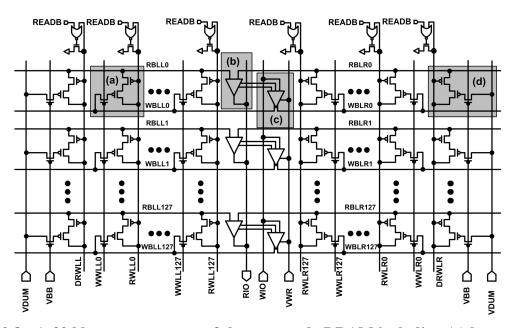

#### 2.2.4 Architecture and Operation of a 32 kb Sub-Array

A detailed circuit diagram of the 32 kb boosted 3T array is shown in Fig. 2.8. The array has 128 cells per WL and 128 cells per split BL, which share a common BL S/A located at the center of the array. The proposed VDUM bias is connected to the dummy cells placed at both edges of the array, and the VWR bias is connected to the write-back circuitry of the BL S/A. The RWL pull-down keepers are located at the top row of the array to keep the ground noise of the activated RWL as small as possible. HSPICE simulations indicate a 66 mV RWL ground noise at 0.9 V, 85 °C when all cells connected to the same RWL contain data '0' which corresponds to the worst case scenario.

Fig. 2.8: A 32 kb array structure of the proposed eDRAM including (a) boosted 3T gain cell, (b) hybrid current/voltage S/A, (c) regulated bit-line write scheme, and (d) PVT-tracking read reference scheme.

Fig. 2.9 shows simulation waveforms of read and write-back operations with a 2 ns random cycle time. A two-stage full pipeline structure was implemented to control read and write-back operations. At the first clock cycle, RWL is selected, and this amplifies

the cell node by preferential coupling. When the current S/A control signal (ISAEN) is enabled, the current S/A amplifies its input signals to analog voltage signals with RBL held close to VDD. After achieving a recognizable voltage difference, the voltage S/A control signal (SAEN) is enabled. At the second clock cycle, read-out and write-back operations are followed. After write-back, discharged WBLs are pre-charged using the negative supply VBB control signal (PRECHB).

Fig. 2.9: Read and write-back simulation waveform with a 2 ns random cycle time.

# 2.3 Statistical Simulation Results for 6T SRAM and 3T EDRAM Arrays

This section presents Monte-Carlo simulation results on megabit density SRAM and eDRAM arrays to estimate their speed and power in a practical scenario [41]. An operating voltage of 0.9 V was chosen (nominal operating voltage of the 65 nm process used is 1.2 V) so that cell failures exist in the small 32 kb unit test array. Fig. 2.10 summarizes the simulation setup for the Monte-Carlo iterations including assumptions on the mismatch and voltage variations.

|                                                                                    |                      | CONV 3T<br>eDRAM                                                                            | Proposed 3T eDRAM            | 6T SRAM |  |

|------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------|------------------------------|---------|--|

| 0.9V, 85°C, 1M Monte Carlo full array simulation<br>w/ 1.2V, 65nm, LP CMOS process |                      |                                                                                             |                              |         |  |

| Read<br>operation                                                                  | Cell node<br>voltage | @100µs with voltage<br>distribution under T <sub>OX</sub> and<br>V <sub>TH</sub> variations |                              | N/A     |  |

|                                                                                    | Reference<br>bias    | Adaptive VDUM with 10% variations                                                           |                              | N/A     |  |

|                                                                                    | Cell                 | Device mismatch                                                                             |                              | es      |  |

|                                                                                    | Dummy cell           | Dummy cell<br>averaging<br>scheme [19]                                                      | 4X upsized device mismatches | N/A     |  |

|                                                                                    | Current S/A          | N/A                                                                                         | S/A pair<br>mismatches       | N/A     |  |

| Write<br>operation                                                                 | Boosted supply       | -0.5V with 10% variations                                                                   |                              | N/A     |  |

|                                                                                    | Cell                 | Device mismatche                                                                            |                              | es      |  |

<sup>\*</sup>Mismatches (i.e. sigma of Vt) are based on process parameters provided in the design kit adjusted by individual device dimensions using the inverse square root relationship

Fig. 2.10: Simulation setup for 1 M Monte Carlo simulations.

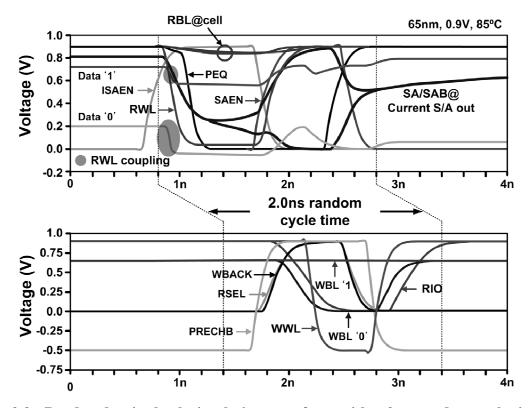

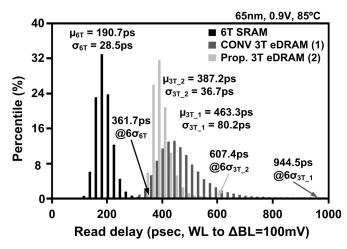

#### 2.3.1 Read and Write Performance

Fig. 2.11 shows read bitline delay distributions with average and 6-sigma point delays annotated for the following three memory arrays; a 1Mb SRAM, a 2 Mb conventional 3T, and a 2 Mb boosted 3T. Simulation results were obtained from 2<sup>20</sup> Monte-Carlo

iterations. The peripheral circuit delay, which is a function of the unit sub-array size, and the global interconnect delay, which is a function of the total cache area, are identical for the three simulated arrays since we selected an SRAM with half the number of cells as the eDRAMs. Recall that an SRAM bitcell is about twice the area of an eDRAM bitcell. The single-ended sensing nature and the gradual loss in the storage node voltage of the conventional 3T eDRAM result in a 6-sigma read bit-line delay that is 2.6 times longer than a 6T SRAM as shown in Fig. 2.11. The proposed 3T eDRAM with preferential amplification effect partially makes up for this performance shortfall, improving the bit-line sensing speed by 36% compared with the conventional 3T eDRAM. Although 6T SRAMs still have a 40% faster sensing delay than the proposed circuit, we will see later that their performance becomes worse than eDRAMs for large cache sizes due to the longer global interconnect delay.

Fig. 2.11: Read performance comparisons between 6T SRAM and 3T eDRAM obtained from  $2^{20}$  Monte-Carlo iterations. Results are equivalent to the distribution of a 1 Mb macro array. 6T SRAM has the shortest bitline delay attributed to the differential swing nature and large drive current (361.7ps @ 6 $\sigma$ ) followed by the proposed 3T eDRAM (607.4ps @6 $\sigma$ ) and the conventional 3T eDRAM (944.5ps @6 $\sigma$ ).

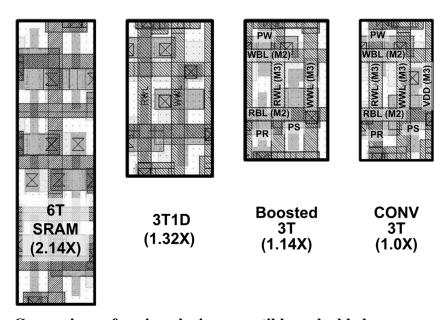

Fig. 2.12 shows detailed cell layouts of various logic-compatible embedded memory cells drawn using a standard 65nm logic design rule. The dense bitcell design rules were not available to the authors but for area comparison purposes, using a logic design rule is generally sufficient. The four signal wire lines and the three transistors of the conventional boosted 3T gain cells are marked in Fig. 2.12. The proposed boosted 3T gain cell is 47% smaller than a 6T SRAM cell.

Fig. 2.12: Comparison of various logic-compatible embedded memory cell layouts using a 65nm logic design rule (the authors did not have access to the dense bitcell design rule but for area comparison purposes, the logic design rule is generally acceptable). The outer box represents the cell boundary. Signal names, wire tracks, and device names are marked for the boosted 3T and conventional 3T cells.

Fig. 2.13 shows latency comparison results between a 6T SRAM array and the boosted 3T eDRAM array for two different cache sizes. The latency of a cache shown in Fig. 2.13 consists of the bit-line sensing time (6-sigma value from Fig. 2.11), the peripheral circuit delay, and the global interconnect delay. The boosted 3T eDRAM

achieves faster access times for cache sizes greater than 16 Mb (or 2 MB) owing the shorter interconnect delay made possible by the smaller bitcell.

Fig. 2.13: Latency comparisons between SRAM and 3T eDRAM for 1 Mb and 16 Mb cache sizes. Gain cells have a shorter interconnect delay due to the smaller cell size making their performance favorable in larger arrays.

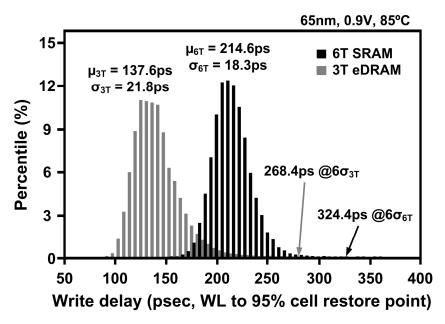

Fig. 2.14 shows the 1 Mb write delay distributions of a 6T SRAM array and the proposed 3T eDRAM array. Here, the write delay is defined as the WL signal to the time when the cell node reaches 95% of the full voltage swing. The write speed of the gain cell is faster than the 6T SRAM since the latter is based on a ratioed operation. Note that the WWL of the gain cell must be sufficiently negative in order for the PMOS write devices to pass a good data '0' level. For a WWL under-drive voltage of -0.5V, the 1Mb Monte-Carlo simulations show a write speedup of 17 % (6-sigma point) for the boosted 3T eDRAM.

Fig. 2.14: Write delay distributions of 1Mb arrays using 6T SRAM and 3T eDRAM.

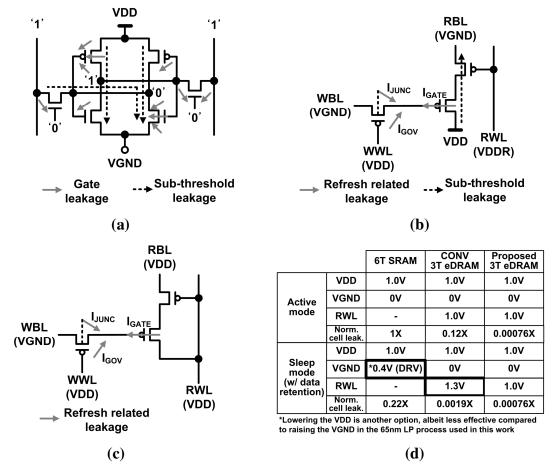

#### 2.3.2 Static Power Consumption

Static power consumption of an eDRAM system consists of two main components: (i) the leakage current of the cell itself and (ii) the refresh power to keep the data "alive". The refresh operation is a dummy read followed by a write-back cycle which simply reinforces the cell data. Hence, the refresh power is inversely proportional to refresh period. The data '0' storage node voltage should be kept sufficiently low so that the PMOS read device can provide enough drive current that meets the target read speed. This criterion determines the refresh period as pointed out in section 2.1. Fig. 2.15 (a), (b), and (c) illustrate the leakage components in the three memory cells. Due to the higher number of devices per cell, there are more leakage paths from the supply to the ground in a 6T SRAM cell than in the 3T eDRAM cells. Since the leakage current through the storage node has to be extremely small in an eDRAM cell for it to be viable (e.g., >100 µs retention time), the main cell leakage component is through the read access

device. In other words, the refresh related leakages shown in Fig. 15 (b) and (c) are much smaller than the leakage current through the read access device.

Fig. 2.15: Leakage components of a (a) 6T SRAM, a (b) conventional 3T eDRAM and the (c) proposed 3T eDRAM. (d) Bias conditions and normalized cell leakages of SRAM and 3T eDRAM in active and sleep modes.

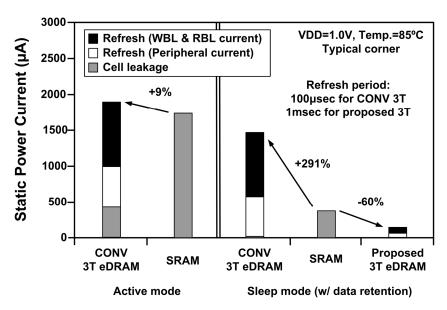

Fig. 2.16 compares the static power consumption of a 1 Mb 6T SRAM array and a 2 Mb 3T eDRAM array with a 100 µs refresh period. HSPICE simulations were performed using a 65 nm low-leakage CMOS process at 1.0 V, 85 °C. Again, the number of cells of the 3T eDRAM array was chosen to be twice that of the SRAM array to account for the ~50% smaller cell size. Note that the eDRAM's higher density makes up for its longer

latency improving the overall architectural performance [4], [5]. Simulation results show that the static power of a 2Mb conventional 3T eDRAM array is similar to that of a 1 Mb SRAM during active mode. The refresh current consists of the RBL and WBL switching currents for the dummy read and write-back operations, as well as the refresh control power in the peripheral circuits. The refresh power constitutes 75% of the total eDRAM static power for a 100 µs refresh period.

Fig. 2.16: Static power comparisons between a 1 Mb SRAM and a 2 Mb 3T eDRAM. Leakage power of the peripheral circuit is assumed to be negligible.

Most embedded memories are now equipped with sleep mode capability, so it is important to compare the sleep mode power between SRAM and the proposed eDRAM. When power gating and wordline overdrive techniques shown in Fig. 2.15(d) are applied, the cell leakage component is reduced in both the SRAM and the eDRAM arrays [12], [42]. Since refresh power is not affected by these sleep techniques, the eDRAM's total static power becomes 3X larger compared to the SRAM's even with an additional boosted high supply for the RWL to suppress the read path sub-threshold leakage as

shown in Fig. 2.15(b). Our proposed 3T eDRAM cell significantly reduces the refresh power component as it has a 10X longer retention time without any extra boosted supply. This makes the static power of the proposed eDRAM 53% less than that of a power gated SRAM, as shown in Fig. 2.16.

Fig. 2.17 summarizes simulation and layout results of various logic-compatible embedded memory cells.

|                               |                                   |                                           |                                    | 65nm, 0.9V, 85°C                             |

|-------------------------------|-----------------------------------|-------------------------------------------|------------------------------------|----------------------------------------------|

|                               | CONV 3T (2T [19])                 | 3T1D [18]                                 | Proposed 3T [33]                   | 6T SRAM [12]                                 |

| *Cell schematic               | WBL RWL                           | WBL RWL                                   | RBI - RWI                          | W. T. B. |

| Features                      | Small size                        | Partial storage node<br>amplification     | Full storage node<br>amplification | Fast                                         |

| Issues                        | Short retention time              | Additional device                         | RWL noise                          | Large size,<br>low noise margin              |

| **Cell size (ratio)           | 0.54x1.02=<br>0.551µm² (1.0X)     | 0.64x1.14 <del>=</del><br>0.73µm² (1.32X) | 0.615x1.02=<br>0.627µm² (1.14X)    | 0.575x2.05=<br>1.178µm² (2.14X)              |

| ***RWL-BL delay<br>(Δ=100mV)  | 945ps                             | 794ps                                     | 607ps                              | 362ps                                        |

| ***WWL-Cell 95% restore delay | -                                 | -                                         | 268ps                              | 324ps                                        |

| Latency<br>(simulated)        | -                                 | -                                         | 1.81ns @1Mb<br>2.67ns @16Mb        | 1.58ns @1Mb<br>2.69ns @16Mb                  |

| Retention time                | 110µs<br>(measured)               | 200µs<br>(simulated)                      | 1.25ms<br>(measured)               | -                                            |

| Static power                  | Large due to short retention time | Medium                                    | Small                              | Large due to<br>transistor leakage           |

<sup>\*</sup> PMOS cells for low  $I_{gate}$ , \*\* 65nm logic design rule, \*\*\* Monte-carlo  $6\sigma$  simulation results

Fig. 2.17: Comparison of logic-compatible embedded memories.

# **2.4** Test Chip Implementation and Measurements

A proof-of-concept 64 kb eDRAM test chip was built in a 1.2 V, 65 nm low-leakage logic CMOS process to demonstrate the proposed circuit techniques. In order to fully verify the proposed techniques against the existing ones, each sub-array has a different combination of cell structure (boosted 3T vs. conventional 3T), reference scheme

(proposed PVT-tracking vs. cell averaging [19]), and write scheme (conventional vs. regulated bit-line write). Fig. 2.18 shows the chip microphotograph and feature summary of the 64 kb eDRAM test chip fabricated in a 1.2 V, 65 nm low-leakage logic CMOS process.

| Process                          | 65nm LP CMOS (7-MET)                              |

|----------------------------------|---------------------------------------------------|

| Circuit dimension                | 250.7x129.9μm²                                    |

| Cell size                        | 53% of 6T SRAM                                    |

| Retention time                   | > 1.25ms @ 0.9V, 85°C                             |

| Operating voltage                | 1.2V - 0.7V                                       |

| Preferential<br>boosting @ 1.0ms | 0.27V for data '0'<br>0.14V for data '1'          |

| Cycle time                       | 2.0ns @ 0.9V (simulation)                         |

| Refresh power                    | 91.3µW per Mb @ 1V, 85°C,<br>1.0msec refresh rate |

Fig. 2.18: Microphotograph of the 65 nm eDRAM test chip and feature summary.

Fig. 2.19(a) shows the measured VWR levels at different supply voltages. The data '1' voltage (i.e., VWR) is high enough to keep the storage transistor off: the PMOS threshold voltage ( $V_{TP}$ ) of this process is 0.315 V at 85 °C and the measured VWR level is slightly lower than VDD- $V_{TP}$ . The unselected cells undergoing the data '1' disturbance situation are not affected since a sufficient amount of negative Vgs is applied to the write access transistor. The VWR level is determined by the balance between the subthreshold, gate, and junction leakage components. In most cases, sub-threshold leakage is the dominant factor in determining the VWR level. At high temperature and high VDD conditions however, the junction and gate leakage components have a stronger affect on the VWR level than the sub-threshold leakage component resulting in higher level over 1.1 V as shown in Fig. 2.19(a).

Fig. 2.19: (a) Measured regulated bit-line write bias (VWR) level. (b) Storage node voltage measurement results under data '1' disturbance conditions.

By externally adjusting the VDUM voltage, we can indirectly and noninvasively measure the storage node voltage at different data retention times. For example, read failure will happen for data '0' if the VDUM level is lower than the storage node voltage so the storage voltage can be measured by sweeping the VDUM voltage and measuring the failure point. It is worth mentioning that the storage node voltage measured using this method include effects such as process variation or transient noise (e.g. coupling noise or supply noise) providing us with an "effective" cell node voltage. Fig. 2.19(b) shows the measurement results of the storage node voltage of the proposed regulated write scheme compared with the conventional 3T gain cell under the data '1' disturbance condition. The data retention characteristics of the data '1' disturbance case and the data hold mode case are virtually identical when using the proposed regulated bit-line write scheme.

Fig. 2.20(a) shows the data retention characteristics of the conventional 3T and the proposed boosted 3T from the same test chip, including the cell-to-cell retention time variation. The retention time was for a read speed (i.e., RWL enable to voltage S/A

enable interval) of 1.0 ns at 0.9 V and 85 °C. This translates into a 2.0 ns cycle time. The proposed boosted 3T design achieves a data retention time of 1.25 ms at 0.9 V, 85 °C, which is a 10X improvement over the conventional 3T cell measured from the same silicon die. Note that due to limitation in the test setup, only 32 cells were measured from each sub-array. As a point of reference, the target retention time of a 2T gain cell eDRAM was 10 µs in [19] and the measured retention time of a 1T1C eDRAM was 40 µs in [6].

Fig. 2.20: (a) Measured retention time statistics. Due to limitations in the test setup, only 32 cells were measured from each sub-array. The measured cells were located evenly across the memory array. (b) Measured storage node voltage in the proposed boosted 3T cell and the conventional 3T cell. The cell voltage was indirectly and noninvasively measured by sweeping the reference cell node voltage.

Similar to Fig. 2.19(b), Fig. 2.20(b) shows the measured storage node voltage of the proposed boosted 3T and the conventional 3T gain cell. Due to threshold voltage variations between the read devices and the WWL coupling effect after the write-back, the data '0' voltage of the conventional 3T started at around 0.1 V. Read failures start to occur when the cell voltage is higher than around 0.2 V for the conventional 3T. The

amount of cell node boosting of the proposed cell was 0.27 V after a 1.0 ms of hold time. The preferential boosting effect can be clearly observed in the measured data as the difference between the two curves diminishes at longer hold times. Note that the VDUM level could not be lowered below 0V in the test chip, so although a large negative cell voltage is expected at short retention times, we were only able to measure the positive cell voltages as shown in Fig. 2.20(b). This is sufficient as we are more interested in measuring the positive storage node voltage region which is when the memory operation starts to fail.

Figs. 2.21(a) and (b) show the measured storage node voltage of data '1' and data '0' enabling a 2.0 ns random cycle time at 0.9 V, for high (85 °C) and room (25 °C) temperature corners, respectively. Optimal VDUM levels to achieve longer retention time with fixed read speed were 0.2 V for high temperature and 0.14 V for room temperature. Fig. 2.21(c) shows the measured VDUM level at high and room temperature corners for various supply voltages. VDUM level change across a temperature range of 25 °C to 85 °C and a supply voltage range of 0.8V to 1.3V was 50 mV. The 50 mV voltage difference is approximately the threshold voltage difference between the two temperature conditions.

Fig. 2.21: Measured storage node voltages at (a) 85°C and (b) 25°C. (c) Measured PVT-tracking read reference (VDUM) level at different supply voltages.

#### 2.5 Conclusions

Circuit techniques have been presented for increasing the data retention time and enhancing the performance of gain cell eDRAMs. The proposed boosted 3T eDRAM cell preferentially boosts the cell voltage to obtain high performance and low static power dissipation, with a layout penalty of only 14% compared to a conventional 3T cell. The proposed regulated bit-line write scheme can eliminate the data '1' write disturbance problem without introducing another boosted supply for WWL. The measurement results

show the 1.25 ms data retention time with 2 ns random cycle time at 0.9 V, 85 °C, which is a 10X improvement compared to a conventional 3T gain cell measured from the same silicon die. The measured static power dissipation from a 64 kb test chip with the proposed schemes was 91.3  $\mu$ W per Mb at 1.0 V, 85 °C, and 1.0 ms refresh period, which is about 50% smaller compared with a power gated SRAM with half the number of cells.

# **Chapter 3**

# An Asymmetric 2T EDRAM for High Speed On-die Caches

#### 3.1 Retention Characteristics of Conventional Gain Cells

In the second test chip, read paths implemented only with NMOS's are explored to achieve higher performance than PMOS based gain cells described in Chapter 2. To aid the understanding of our proposed techniques, I first describe the detailed retention characteristics of conventional gain cells having a NMOS read path.

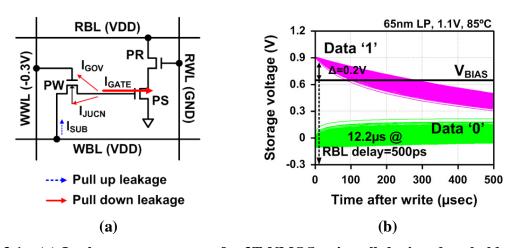

In the 3T NMOS cell shown in Fig. 3.1(a), PW denotes the write access device, PS the storage device, and PR the read access device. Unlike 6T SRAMs or 1T1C eDRAMs, gain cells have a decoupled read and write structure – Read Word-Line (RWL) and Read Bit-Line (RBL) are used for read access and Write Word-Line (WWL) and Write Bit-Line (WBL) are used for write access. This attribute leads to improved read and write margins and flexibility in the bit-cell design - for example, the read and write paths can be optimized separately allowing gain cells to scale favorably in future technology nodes. In data retention mode, PW and PR are turned off and the storage node is left floating.

The sub-threshold, gate, and junction leakages in the surrounding devices cause the floating voltage to change with time as shown in Fig. 3.1(b). Since the storage node is surrounded by many low supplies in an NMOS only cell, the retention time of data '1' is much shorter than that of data '0'. To make matters worse, the data '1' (not data '0') voltage level is critical for the read access speed as the read port also uses an NMOS. The data retention time depends on the aggregated leakage current flowing into the storage node. Fig. 3.1(b) shows the cell retention time variations obtained by running  $2^{20}$  Monte-Carlo simulations in HSPICE, which represents the cell-to-cell variation of a 1 Mb memory macro. In this analysis, we define retention time as the time it takes for the cell node voltage to reach a level corresponding to a target RBL delay of 500 ps.

Fig. 3.1: (a) Leakage components of a 3T NMOS gain cell during data hold mode. (b) Monte-Carlo simulation results of storage node voltage during data hold mode showing 1 Mb macro retention characteristics.

The read reference bias level is set as 0.65 V and the data '1' voltage should be higher than this reference voltage by at least 0.2 V to achieve the same read margins as the data '0' case. Results based on our criterion indicate that the retention time of data '1' varies

from 12.2 µs to 54.1 µs mainly due to the gate leakage through the inverted channel of the NMOS storage device, while the non-critical data '0' voltage shows a very stable retention characteristic. Note that the WWL coupling after write-back operation results in lower initial storage levels than VDD and GND in case of data '1' and data '0', respectively. This further degrades the retention time of data '1' when a gain cell is implemented only with NMOS devices. The central idea of this work is to maximize the retention time and performance by using a new bit cell that balances the retention characteristics of data '0' and '1'.

### 3.2 Asymmetric 2T EDRAM Design

#### 3.2.1 Asymmetric 2T Gain Cell