# **Aalborg Universitet**

## PSpice Modeling Platform for SiC Power MOSFET Modules with Extensive **Experimental Validation**

Ceccarelli, Lorenzo: Iannuzzo, Francesco: Nawaz, Muhammad

Published in:

Proceedings of 8th IEEE Energy Conversion Congress and Exposition, 2016: ECCE 2016

DOI (link to publication from Publisher): 10.1109/ECCE.2016.7855369

Publication date: 2016

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Ceccarelli, L., lannuzzo, F., & Nawaz, M. (2016). PSpice Modeling Platform for SiC Power MOSFET Modules with Extensive Experimental Validation. In *Proceedings of 8th IEEE Energy Conversion Congress and Exposition, 2016: ECCE 2016* IEEE Press. https://doi.org/10.1109/ECCE.2016.7855369

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research. ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# PSpice Modeling Platform for SiC Power MOSFET Modules with Extensive Experimental Validation

Lorenzo Ceccarelli, Francesco Iannuzzo

Department of Energy Technology

Aalborg University, Pontoppidanstraede 101

9220 Aalborg, Denmark

lce@et.aau.dk, fia@et.aau.dk

Muhammad Nawaz

ABB Corporate Research

Forskargränd 8

SE-721 78, Västerås, Sweden

muhammad.nawaz@se.abb.com

Abstract—The aim of this work is to present a PSpice implementation for a well-established and compact physics-based SiC MOSFET model, including a fast, experimental-based parameter extraction procedure in a MATLAB GUI environment. The model, originally meant for single-die devices, has been used to simulate the performance of high current rating (above 100 A), multi-chip SiC MOSFET modules both for static and switching behavior. Therefore, the simulation results have been validated experimentally in a wide range of operating conditions, including high temperatures, gate resistance and stray elements. The whole process has been repeated for three different modules with voltage rating of 1.2 kV and 1.7 kV, manufactured by three different companies. Lastly, a parallel connection of two modules of the same type has been performed order to observe the unbalancing and mismatches experimentally, and to verify the model effectiveness in such challenging topologies.

Keywords—SiC-MOSFETs, PSpice modeling, Parameter extraction, Wide bandgap devices

#### I. INTRODUCTION

Among wide bandgap semiconductor devices, silicon carbide (SiC) MOSFETs have been experiencing a rather fast technological development process during last few years due to their promising features such as high breakdown field strength, wide bandgap, saturation velocity and thermal conductivity. In SiC high-frequency power switches, it is possible to achieve a high breakdown voltage with relatively small on-state resistance, fast switching speed, and good thermal conductivity, which allows reliable operations in harsh condition environments [1] - [6]. Moreover, not presenting tail current due to their unipolar structure, they show higher switching speed and lower losses in comparison to Silicon IGBTs and BJTs. Nevertheless, the technology used nowadays in the manufacturing of SiC MOSFETs has just settled and reliable operations are only possible for devices with quite low current ratings. For high power applications, parallel connection of several chips is required in high power modules, which are already available in the commercial market rated 100 - 800 A and 1.2 - 1.7 kV. While the technological manufacturing of SiC MOSFETs is moving toward its maturity phase, modern challenges as the reliability evaluation, and high-voltage packages development are still

on their infancy stage, that hinders them to be used in the real field. On the other side, simple analytical device models are required to facilitate the power converter design, and hence to lower the development cost and effort. On this front, device modeling research is far lagging behind the technological development of SiC power MOSFETs.

Many models have been proposed in the literature to predict the static and switching characteristics of Si and SiC power MOSFETs [7] - [16], in order to support the development process of SiC-based converters and evaluate their performances and advantages. These models basically divide into two main categories: behavioral models and physicsbased models. In the first typology category a mathematical fitting of the device characteristics is performed, resulting in simple equations and fast simulation time, but hardly being able to describe the device behavior in all the operating conditions. On the other hand, the physics-based ones include the physical laws governing the device, and often more complex numeric methods relying on finite-element analysis of the model. A physics-based model can estimate in a satisfactory level of detail of the MOSFET's performances, if the parameters are correctly identified, without requiring advanced knowledge of the device manufacturing features and with rather fast convergence time. The physics-based model proposed in [14] has been chosen for the purposes of this work with a novel PSpice code implementation, described in the following section. However, the use of such model to evaluate a whole module, made up of several parallelized dies, is rather new in literature and thus, verifying its validity is one of the main aims of this work.

#### II. MODEL DESCRIPTION AND PSPICE IMPLEMENTATION

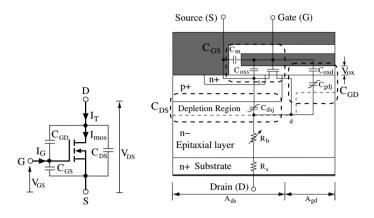

The model presented in [13], [14] is a well-established adaptation of an IGBT model [17] to a MOSFET structure. It describes analytically a quite unique feature of the semiconductor: the presence of a sub-threshold current  $I_{\rm mosl}$  originated at the corners of the MOSFET cells, whose effect is non-negligible at low gate voltage. This regions present lower gate threshold and transconductance respect to the main channel region.

Fig. 1. Power MOSFET schematics for the McNutt-Hefner model

The "soft-threshold" Vtl together with the main high-threshold Vth currents ( $I_{mosl}$  and  $I_{mosh}$ ) are taken into account in two different equations, both in linear and saturation region, and then summed up to form the main MOSFET current  $I_{MOS}$  (Eq. 1 to 5 [14]). In the above equations, Kfl, Kp and Kf are the low current transconductance factor, the saturation transconductance and the linear transconductance factor, respectively, Pvf is the pinch-off voltage factor,  $\theta$  is the transverse electric field parameter and y=Kf/(Kf-Pvf/2).

$$I_{mosl} = K_{fl} K_{p} K_{f} \frac{\left(V_{gs} - V_{tl}\right) V_{ds} - \frac{1}{y} \left[P_{vf}^{1-y} V_{ds}^{y} \left(V_{gs} - V_{tl}\right)^{2-y}\right]}{1 + \theta \left(V_{gs} - V_{tl}\right)}$$

$$when \ V_{ds} \leq \frac{V_{gs} - V_{tl}}{P_{vf}}$$

$$(1)$$

$$I_{mosl} = K_{fl} K_p \frac{\left(V_{gs} - V_{tl}\right)^2}{2\left[1 + \theta\left(V_{gs} - V_{tl}\right)\right]} \quad when \ V_{ds} > \frac{V_{gs} - V_{tl}}{P_{vf}}$$

(2)

$$I_{mosh} = \left(1 - K_{fl}\right) K_p K_f \frac{\left(V_{gs} - V_{th}\right) V_{ds} - \frac{1}{y} \left[P_{vf}^{1-y} V_{ds}^{y} \left(V_{gs} - V_{th}\right)^{2-y}\right]}{1 + \theta \left(V_{gs} - V_{tl}\right)}$$

$$when \ V_{ds} \le \frac{V_{gs} - V_{th}}{P_{vf}}$$

(3)

$$I_{mosl} = \left(1 - K_{fl}\right) K_p \frac{\left(V_{gs} - V_{th}\right)^2}{2\left[1 + \theta\left(V_{gs} - V_{th}\right)\right]} \quad when \quad V_{ds} > \frac{V_{gs} - V_{th}}{P_{vf}}$$

(4)

$$I_{MOS} = I_{mosl} + I_{mosh} \quad (5)$$

The MOSFET current equations have been represented in the PSpice code with two voltage-dependent current sources in parallel. Depending on the gate voltage and thresholds, an IF statement determines the operation of the device in linear or saturation region. The on-state resistance of the device is taken into account in the model as the series connection of the bulk (epitaxial layer) resistance, affected by the thickness of the drain-source depletion region and the carrier mobility, and a constant drain substrate resistance (Fig. 1). So the drain-source voltage Vdds is given by:

$$V_{dds} = V_{ds} + I_{MOS}(R_b + R_s)$$

(6)

In PSpice, a voltage-dependent voltage source has been connected in series with the MOSFET current to model the

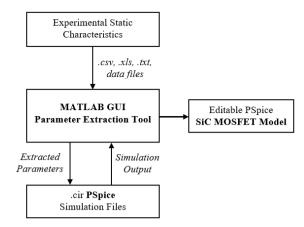

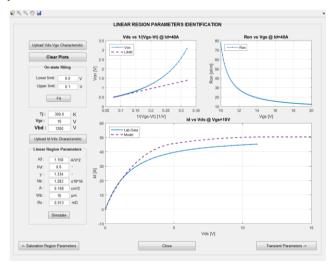

Fig. 2. Structure of the parameter extraction tool

on-state drop. The switching behavior of the MOSFET is determined by the three capacitances in Fig. 1. In good approximation the gate-source capacitance is assumed to be constant, while the gate-drain and drain-source ones are dependent on the change of the respective depletion regions with the drain voltage. In particular, the gate-drain capacitance is considered as the series of the variable junction capacitance Cgdj and the fixed oxide capacitance Coxd. The correct estimation of these parameters implies the knowledge of the device area and oxide thickness, as well as other fundamental properties of the material. All the parameters of the depletion

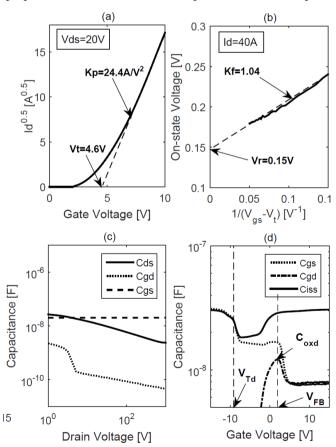

Fig. 3. Parameter extraction sequence: (a) saturation region; (b) linear region; (c)-(d) transient parameters

region (width, built-in voltage and carrier mobility) and the on-state resistance and capacitances values have been modeled in PSpice as stand-alone, voltage-dependent voltage sources. Both the drain capacitances are included in the code as voltage-dependent current generators. Moreover, the temperature dependency of threshold voltage Vt and saturation transconductance Kp is taken into account in the model through two simple behavioral equations (Eq. 7-8).

$$V_t = V_{t0} + V_{t1}(T_i - T_0) \tag{7}$$

$$K_{p} = K_{p0} \left(\frac{T_{0}}{T_{j}}\right)^{K_{p1}} \tag{8}$$

$$\mu_n = \frac{947}{1 + \left(\frac{N_b}{1.49 \cdot 10^{17}}\right)^{0.61}} \left(\frac{T_0}{T_j}\right)^{2.15} \tag{9}$$

Finally, the temperature dependency of the carrier mobility  $\mu_n$

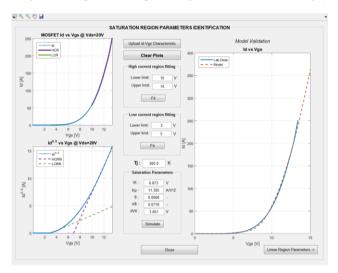

Fig. 4. MATLAB GUI panel for the identification of the saturation region parameters  $\,$

Fig. 5. MATLAB GUI panel for the identification of the linear region parameters

is also included, allowing the modeling of the on-state resistance Ron variation for high temperature (Eq. 9).

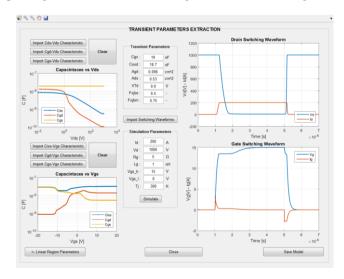

#### III. PARAMETER EXTRACTION PROCEDURE

The parameter extraction process proposed in [14] has been used for identifying the static parameters, while the method illustrated in [17] was adopted for the transient analysis. Other general-purpose equations related to semiconductor physical properties were also used [18], [19]. All the procedure has been embedded in a new "parameter-extraction tool" (see Fig. 2), developed in MATLAB through a GUI, consisting of three steps: saturation region, linear region and transient parameters identification [14]. Each of the steps has a dedicated panel in the GUI (Fig. 4 - 6), which allows the direct validation of the model, running the PSpice .cir simulation file and processing its output, together with the manual tuning of the extracted parameters. The main idea is to provide the user with a complete and rather simple tool to identify a given device/module and eventually create a PSpice model or library part without the need for advanced Spice programming effort. The saturation region parameter extraction basically consists of an analysis of the I - V static characteristic of the device (Fig. 3.a). The extraction of gate threshold Vt and peak transconductance Kp is performed by fitting the high current region of the Id - Vgs curve for root squared values of Id, approximated as follows [14][20]:

$$\sqrt{I_d} = \sqrt{\frac{K_p}{2}} \left( V_{gs} - V_t \right) \tag{10}$$

Rearranging and manipulating the model equation it is possible to calculate the remaining coefficients.

The characteristic Vds - Vgs for a forced constant value of Id can be used to observe the on-state behavior and thus extract the linear transconductance Klin (and the linear transconductance factor Kf=Klin/Kp) and the on-state resistance. A fitting is easier to achieve when linearizing, plotting Vds = Von versus 1/(Vgs - Vt) instead of Vgs. The

Fig. 6. MATLAB GUI panel for the identification of the transient parameters

TABLE I. EXTRACTED PARAMETERS

| Parameter                         |                                          | Unit             | Module 1 (Cree)        | Module 2 (Microsemi)   | Module 3 (Rohm)        |  |  |

|-----------------------------------|------------------------------------------|------------------|------------------------|------------------------|------------------------|--|--|

| Vbd                               | Module Rated Breakdown Voltage           | kV               | 1.7                    | 1.2                    | 1.2                    |  |  |

| Id                                | Module Rated Drain Current               | A                | 325                    | 357                    | 180                    |  |  |

| Vt                                | Gate Threshold Voltage                   | V                | 5.287                  | 4.960                  | 6.648                  |  |  |

| Kp                                | Saturation Transconductance              | A/V <sup>2</sup> | 28.04                  | 32.012                 | 10.392                 |  |  |

| Kfl                               | Low Current Transconductance Factor      | -                | 0.055                  | 0.067                  | 0.085                  |  |  |

| θ                                 | Transverse Electric Field Parameter      | -                | 0.001                  | 0.005                  | 0.006                  |  |  |

| dVtl                              | Low Threshold Voltage Difference         | V                | 2.129                  | 2.322                  | 3.943                  |  |  |

| Kf                                | Linear Transconductance Factor           | -                | 1.043                  | 1.205                  | 1.059                  |  |  |

| Rs                                | Drain Series Resistance                  | Ω                | 1.2                    | 1.7                    | 1.1                    |  |  |

| A                                 | Active Area                              | cm <sup>2</sup>  | 0.174                  | 0.123                  | 0.112                  |  |  |

| Nb                                | Bulk Doping Concentration                | cm <sup>-3</sup> | $0.906 \times 10^{16}$ | 1.283×10 <sup>16</sup> | 1.283×10 <sup>16</sup> |  |  |

| Wb                                | Bulk Thickness                           | μm               | 14                     | 10                     | 10                     |  |  |

| Pvf                               | Pinch-off Voltage Factor                 | -                | 0.65                   | 0.65                   | 0.45                   |  |  |

| Cgs                               | Gate-Source Capacitance                  | nF               | 20.05                  | 15.43                  | 20                     |  |  |

| Coxd                              | Oxide Capacitance                        | nF               | 12.14                  | 12.34                  | 12                     |  |  |

| Agd                               | Gate-Drain Depletion Area                | cm <sup>2</sup>  | 0.054                  | 0.091                  | 0.052                  |  |  |

| VTd                               | Gate-Drain Depletion Threshold           | V                | -9                     | -9                     | -11                    |  |  |

| Fxjbe                             | Depletion Charge Factor (edge)           | -                | 0.5                    | 0.5                    | 0.5                    |  |  |

| Fxjbm                             | Depletion Charge Factor (middle)         | -                | 0.75                   | 0.75                   | 0.75                   |  |  |

| TEMPERATURE DEPENDENCY PARAMETERS |                                          |                  |                        |                        |                        |  |  |

| Vt0                               | Gate Threshold Temperature Coeff.        | -                | 5.609                  | 5.017                  | 7.002                  |  |  |

| Vt1                               | Gate Threshold Temperature Coeff.        | -                | -0.0166                | -0.0137                | -0.0178                |  |  |

| Kp0                               | Saturation Transconductance Temp. Coeff. | -                | 28.04                  | 32.2                   | 10.392                 |  |  |

| Kp1                               | Saturation Transconductance Temp. Coeff. | -                | 2                      | 0.58                   | 1                      |  |  |

slope of this linear regression is inversely proportional to Klin (as expressed in Eq. 11). Through the value of the intercept Vr, rearranging Eq. 12, it is possible to find out Rb + Rs (Fig. 3.b).

$$V_{on} = V_r + \frac{I_d}{K_{lin}(V_{gs} - V_t)}$$

(11)

$$V_r = I_d(R_b + R_s) + \frac{I_d \theta}{K_{lin}}$$

(12)

The estimation of the depletion region parameters is carried out following some simple equations related to the breakdown voltage and the intrinsic properties of 4H-SiC material [18], including the identification of the device active area A. The identification of the device transient parameters is made

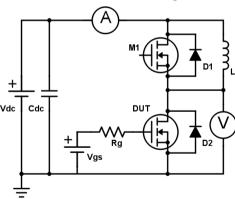

Fig. 7. Schematic of the double-pulse switching test setup.

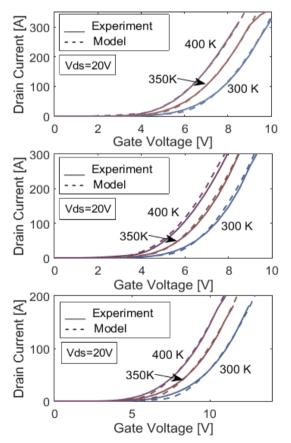

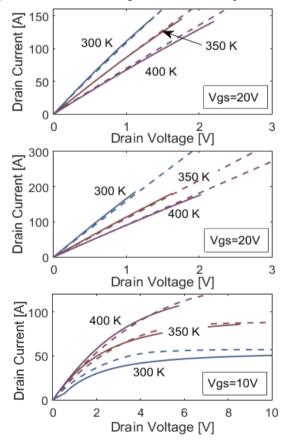

Figure 8. Id-Vgs validation with temperature spread for three modules: Cree (top), Microsemi (middle), Rohm (bottom).

through the study of the capacitance variation over drain voltage (carrying out measurements up to Vds=1.0 kV, with Vgs=0) and gate voltage sweep (from -20 V to 20 V, with Vds=0). In particular, from Cds-Vds and Cgd-Vds, it is possible to estimate the respective depletion overlap regions areas [17], while the mean value of Cgs-Vds gives the constant gate-source capacitance (Fig 2.c). Cgd-Vgs sweep allows instead to find out the value of Coxd, correspondent to the flat band voltage  $V_{FB}$  (depletion region is negligible and Vgs drops only on the SiO $_2$  insulator), and the depletion threshold  $V_{Td}$  (Fig 2.d) [17]. The proposed parameter identification strategy has only been applied to single-die devices in the literature so far, though the model validation shows its rather good suitability when applied to high-power multi-chip modules.

#### IV. EXPERIMENTAL RESULTS AND VALIDATION

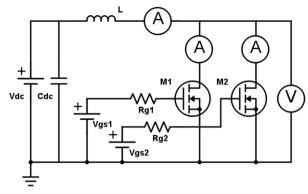

The whole experimental and theoretical work has been carried out at ABB Corporate Research Center in Västerås, Sweden. A power device curve tracer (i.e., B1505A from Keysight) was used to obtain the static characteristics and the capacitance measurements with a rather simple experimental setup. For the switching measurements, a double pulse test has been set up in a circuit with inductive load. Two devices of the same type have been used in the circuit: one as DUT and the other to provide freewheeling path for the current through its body diode, as shown in Fig. 7. A similar setup was used for

Figure 9. Id-Vds validation (solid: exp; dashed: model) with temperature spread for three modules: Cree (top), Microsemi (middle), Rohm (bottom).

TABLE III. SWITCHING TESTS RESULTS

| Parameter  | Unit | Module 1<br>(Cree) | Module 2<br>(Microsemi) | Module 3<br>(Rohm) |

|------------|------|--------------------|-------------------------|--------------------|

| T          | K    | 300                | 300                     | 300                |

| $V_{DC}$   | V    | 1000               | 800                     | 900                |

| $I_{load}$ | A    | 200                | 100                     | 200                |

| Lσ         | nΗ   | 30                 | 150                     | 50                 |

| Rg         | Ω    | 10                 | 15                      | 10                 |

| Vdds       | V    | 965                | 790                     | 879                |

| Vos%       | -%   | 11.8 (15)          | 27.1 (32.1)             | 20.6 (18.5)        |

| Ios%       | -%   | 33.5 (31)          | 40 (47)                 | 13 (15.3)          |

| Eon        | mJ   | 16.2 (20)          | 8.1 (7.6)               | 17 (18.9)          |

| Eoff       | mJ   | 25.9 (23.1)        | 9.3 (11)                | 22.7 (24.1)        |

| Etot       | mJ   | 42.1 (43.1)        | 17.4 (18.6)             | 39.7 (43)          |

the parallelization of two devices of the same type. A hot plate with temperature regulation was used to heat up the DUT up to 425 K and measure the static and dynamic parameters spread. Different load inductances values and DC bus voltage levels have been set when performing the measurements. The gate drive unit (GDU) provides option to vary the gate resistance as well. The room temperature parameters extracted by means of the presented procedure and the temperature dependency coefficients for Vt and Kp are listed in Table I for the three tested modules.

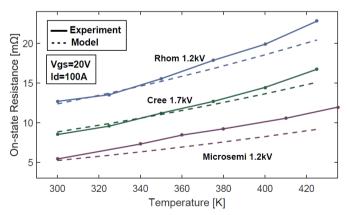

#### A. Static Validation

In Fig. 8-9, the results of the validation for the static I-V characteristic have been reported. The curves have been simulated and compared with experimental data at different temperature values. A satisfactory agreement is achieved over different bias conditions with relative error rarely exceeding 5%. In particular, the model succeeds in taking into account the degradation of carrier mobility for high gate voltages at high temperature, which is a rather important property in SiC devices, preventing thermal runaway during fault conditions and self-stabilizing the device. The coefficients used for the temperature dependency modeling of Vt and Kp result from behavioral fittings of the experimental curves. Moreover, the variation of on-state resistance Ron with temperature in the model has been experimentally validated for the three modules, resulting in a good matching, shown in Fig. 10.

Fig. 10. Ron variation with temperature for three modules with model validation

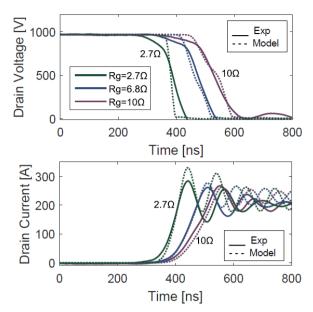

Figure 11. Validation of turn-on switching waveforms (Solid: exp, Dotted: model) for Cree module with Rg spread of 2.7, 6.8 and 10  $\Omega$ .

Figure 12. Validation of turn-off switching waveforms (Solid: exp, Dotted: model) for Cree module with Rg spread of 2.7, 6.8 and 10  $\Omega$ .

### B. Dynamic Validation

The results of a transient simulation, compared with switching measurements, are showcased in Fig. 11 - 12 for the Cree 1.7kV-325A module for three different gate drive resistances. Here, the model predicts fairly well the switching behavior of drain voltage and current during both turn-on and turn-off transients, though parasitic elements had to be included in the simulation to imitate the oscillation's amplitude and frequency given by the stray elements present in the module and in the setup itself. Table II reports the values of DC bus voltage  $V_{\rm DC}$ , load current  $I_{\rm load}$ , loop stray inductance L $\sigma$  (extracted from the measurements), and gate resistance Rg used during the tests as well as the drain voltage

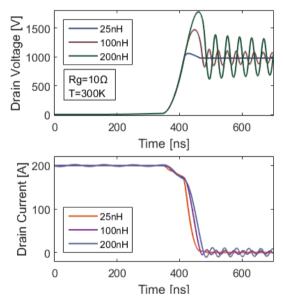

Fig. 13. Simulated turn-on switching waveforms for Cree module with L  $\sigma$  spread of 25, 100 and 200 nH.

Fig. 14. Simulated turn-off switching waveforms for Cree module with L  $\sigma$  spread of 25, 100 and 200 nH.

measured value (after the drop) Vdds, the turn-on overshoot for voltage and current and the switching energy losses compared with the model estimation (values in brackets).

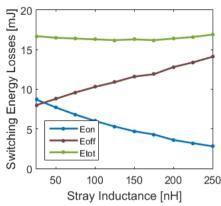

No significant variation of the switching behavior at high temperatures was noticed. Further analysis have been carried out for both circuit and intrinsic parameter spread in order to define a range of reliability for the model and its estimation capability of switching losses. L $\sigma$  was changed in the switching-mode simulations, showing the expected behavior. As shown in Fig. 13 and 14, an increase in the rise and fall time can be noticed for higher values of L $\sigma$ . On the other side, the transient frequency is reduced while the turn-off voltage overshoot and the oscillation amplitude becomes higher. The switching energy losses variation is plotted in Fig. 15 with L $\sigma$

Fig. 15. Simulated switching energy losses vs. stray inductance for Cree 1.7kV module

from 25 nH to 250 nH. Here, two opposite phenomena are occurring: during turn on the slower current and voltage transients provoke decreasing losses for higher  $L\sigma$ ; on the other hand, during turn off the increased overvoltage results in higher losses. The two effects cause the overall losses in the device to remain almost unchanged for higher stray inductance, as visible in Fig. 15.

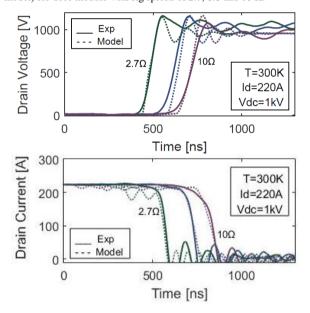

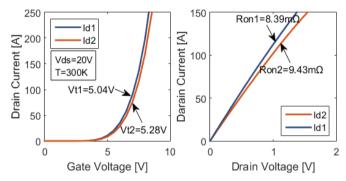

### C. Current Sharing Analysis

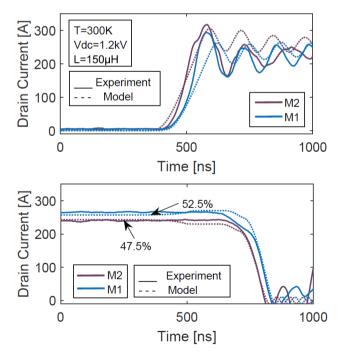

Accurate studies about parallel SiC MOSFETs have been carried out in [21] - [23] and an active current balancing has been proposed in [24]. The focus of these studies has been the observation of static and dynamic characteristics of the parallel modules or devices in order to figure out and quantify how the mismatches in the module's characteristics can influence the switching behavior. Fig. 16 shows one of the experimental results for the double-pulse test carried out on

Fig. 16. Current sharing for two paralleled 1.7kV Cree modules during turnon and turn-off with model validation

Fig. 17. Measurement setup for double-pulse test of two parallel connected modules

Fig. 18. Mismatch between the static characteristics for two Cree 1.7kV modules

two parallel 1.7 kV modules with the setup reported in Fig. 17. and the related modeling. The model parameters are different for the two devices and have been extracted carrying out separate static measurements on each module in order to properly identify the mismatch, which in this case is not particularly relevant, as visible in Fig. 18. Module M1 presents slightly bigger gate threshold and smaller on-state resistance than M2 and this affects the current sharing and the switching speed. In particular, it can be observed from Fig. 16 that M1, as expected, carries less current in comparison to M2; so does it happen in the simulation. The shift of the two waveforms during switching can be due to several phenomena, including gate resistance mismatch and gate pulse delay. The model, however, successfully represents with satisfactory precision the unbalances, though the influence of the stray elements has to be investigated further [21]. In the simulated circuit, the drain stray inductances were kept at the same value for both the modules. A mismatch in the gate resistances was introduced to simulate the delay of the waveforms. It can be observed that the current sharing is accurately modeled, while the transient dynamics still show some inaccuracy, especially in the turn-on transient, though the delay is correctly estimated.

#### V. CONCLUSIONS

This work presents a deep investigation on the modeling approach and parameter identification for SiC MOSFETs, through solid but simplified implementation strategy. The implemented model combined with the exposed identification method is capable of simulating in a wide range of operational

conditions the behavior of three different MOSFET multichip modules, as showed in the experimental validation. Moreover, the simulation time for one switching period of about 5us, solved by a variable step-size algorithm with 0.1 ns maximum step, took less than one minute to be worked out, which makes this implementation very suitable for simulating more complex topologies, with several connected modules. The model has been proven to be robust and convergent in all the analyzed operating conditions. Furthermore, an insight into the parallel connection of SiC power modules has been gained, enabling a good correlation between the different modules' characteristics and the switching unbalances. A dedicated and complete MATLAB GUI has been created in order to easily identify the model parameters and obtain a turn-key simulation file and/or an editable PSpice model. The implemented model is capable of properly simulating the forward biasing operation of the device, yet further improvements for this work are: 1) the reverse conduction region modeling; 2) the body diode modeling; 3), the breakdown behavior modeling; 4) the short circuit thermal modeling. An improved and complete model should therefore include these features, which is the objective of our future research. In addition, an improved thermal modeling can be introduced, whose output is the junction temperature based on the energy losses of the device.

#### REFERENCES

- P. Neudeck, R. Okojie, and L. Chen. High-temperature electronics: a role for wide bandgap semiconductors? Proceedings of the IEEE, 90(6):1065-1076, 2002.

- [2] J Millan, P Godignon, X Perpina, A Perez-Tomas, and J Rebollo. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Transactions on Power Electronics, 29(5):2155-2163, 2014.

- [3] Cyril Buttay, Dominique Planson, Bruno Allard, Dominique Bergogne, Pascal Bevilacqua, Charles Joubert, Mihai Lazar, Christian Martin, Hervé Morel, Dominique Tournier, and Christophe Raynaud. State of the art of High Temperature Power Electronics. pages 1-10, 2009.

- [4] Anant K. Agarwal. An overview of SiC power devices. 2010 International Conference on Power, Control and Embedded Systems, pages 1-4, 2010.

- [5] John W. Palmour. Silicon carbide power device development for industrial markets. pages 1.1.1-1.1.8, 2014.

- [6] Max N. Yoder. Wide Bandgap Semiconductor Materials and Devices. IEEE Transactions on Electron Devices, 43(10):1633-1636, 1996.

- [7] Jun Wang, Tiefu Zhao, Jun Li, Alex Q. Huang, Robert Callanan, Fatima Husna, and Anant Agarwal. Characterization, modeling, and application of 10-kV SiC MOSFET. IEEE Transactions on Electron Devices, 55(8):1798-1806, 2008.

- [8] M. Mudholkar, M. Saadeh, and H. Mantooth. A datasheet driven power MOSFET model and parameter extraction procedure for 1200V, 20A SiC MOSFETs. Proceedings of the 2011 14th European Conference on Power Electronics and Applications, pages 1-10, 2011.

- [9] I. Budihardjo and P.G. Lauritzen. The Lumped-Charge Power MOSFET Model, Including Parameter Extraction. IEEE Transactions on Power Electronics. 10(3):379-387, 1995.

- [10] Ganesh C Patil, Santosh C Wagaj, and Pravin M Ghate. A Simple Analytical Model of 4H-SiC MOSFET for High Temperature Circuit Simulations. 2014.

- [11] Georgios Kampitsis, Michail Antivachis, Sotirios Kokosis, Stavros Papathanassiou, and Stefanos Manias. An Accurate Matlab/Simulink Based SiC MOSFET Model for Power Converter Applications. pages 1058-1064. 2015.

- [12] Ruiyun Fu, Enrico Santi, and Yucheng Zhang. Power SiC MOSFET Model with Simplified Description of Linear and Saturation Operating Regions. pages 190-195, 2015.

- [13] Ty McNutt, Allen Hefner, Alan Mantooth, David Berning, and Ranbir Singh. Compact models for silicon carbide power devices. Solid-State Electronics, 48: 1757-1762, 2004.

- [14] T.R. McNutt, A.R. Hefner, H.A. Mantooth, D. Berning, and Sei-Hyung Ryu. Silicon carbide power mosfet model and parameter extraction sequence. Power Electronics, IEEE Transactions on, 22(2):353-363, March 2007.

- [15] Siddharth Potbhare, Neil Goldsman, Aivars Lelis, James M. McGarrity, F. Barry McLean, and Daniel Habersat. A physical model of high temperature 4H-SiC MOSFETs. IEEE Transactions on Electron Devices, 55(8):2029-2040, 2008.

- [16] N. Phankong, T. Funaki, and T. Hikihara. A static and dynamic model for a silicon carbide power MOSFET. In Power Electronics and Applications, 2009. EPE '09. 13th European Conference on, pages 1-10, Sept 2009.

- [17] Allen R. Hefner. Modeling buffer layer IGBTs for circuit simulation. Power Electronics, IEEE Transactions on, 10(2):111-123, Mar 1995.

- [18] B. Jayant Baliga. Fundamentals of Power Semiconductor Devices. Springer Publishing Company, Incorporated, 1st edition, 2008.

- [19] Ned Mohan, Tore M. Undeland, and William P. Robbins. Power Electronics Converters, Applications and Design. John Wiley and Sons, Inc, 3rd edition, 2003.

- [20] A. Ortiz-Conde, F.J. Garcia Sanchez, J.J. Liou, A. Cerdeira, M. Estrada, and Y. Yue. A review of recent MOSFET threshold voltage extraction methods. Microelectronics Reliability, 42(4-5):583-596, 2002.

- [21] Helong Li, S. Munk-Nielsen, Xiongfei Wang, R. Maheshwari, S. Beczkowski, C. Uhrenfeldt, and W.-T. Franke. Influences of device and circuit mismatches on paralleling silicon carbide mosfets. Power Electronics, IEEE Transactions on, 31(1):621-634, Jan 2016.

- [22] Gangyao Wang, J. Mookken, J. Rice, and M. Schupbach. Dynamic and static behavior of packaged silicon carbide mosfets in paralleled applications. In Applied Power Electronics Conference and Exposition (APEC), 2014 Twenty-Ninth Annual IEEE, pages 1478-1483, March 2014.

- [23] D.-P. Sadik, J. Colmenares, D. Peftitsis, Jang-Kwon Lim, J. Rabkowski, and H.-P. Nee. Experimental investigations of static and transient current sharing of parallel-connected silicon carbide mosfets. In Power Electronics and Applications (EPE), 2013 15th European Conference on, pages 1-10, Sept 2013.

- [24] Yang Xue, Junjie Lu, Zhiqiang Wang, L.M. Tolbert, B.J. Blalock, and F. Wang. Active current balancing for parallel-connected silicon carbide mosfets. In Energy Conversion Congress and Exposition (ECCE), 2013 IEEE, pages 1563-1569, Sept 2013.