### **Aalborg Universitet**

#### Novel screening techniques for wind turbine power converters

Jørgensen, Asger Bjørn; Sønderskov, Simon Dyhr; Christensen, Nicklas; Frederiksen, Kristian Linding; Iciragiye, Eddy; Maarbjerg, Anders Eggert; Munk-Nielsen, Stig; Rannestad, Bjørn

Published in:

Proceedings of 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe), 2016

DOI (link to publication from Publisher): 10.1109/EPE.2016.7695302

Publication date: 2016

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Jørgensen, A. B., Sønderskov, S. D., Christensen, N., Frederiksen, K. L., Iciragiye, E., Maarbjerg, A. E., Munk-Nielsen, S., & Rannestad, B. (2016). Novel screening techniques for wind turbine power converters. In Proceedings of 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe), 2016 IEEE Press. https://doi.org/10.1109/EPE.2016.7695302

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research. ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# "Novel Screening Techniques for Wind Turbine Power Converters"

by A. B. Jørgensen, S. D. Sønderskov, N. Christensen, K. L. Frederiksen, E. Iciragiye, A. E. Maarbjerg, S. Munk-Nielsen, B. Rannestad

This is a post-print of a paper published at 2016 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe). The final published version is available at the IEEE Xplore Digital Library: DOI: 10.1109/EPE.2016.7695302

Citation for published version:

A. B. Jørgensen, S. D. Sønderskov, N. Christensen, K. L. Frederiksen, E. Iciragiye, A. E. Maarbjerg, S. Munk-Nielsen and B. Rannestad, "Novel Screening Techniques for Wind Turbine Power Converters," 2016 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe), Karlsruhe, 2016, pp. 1-8.

© 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

The following PDF is intended for storage at university and authors websites only. It has been prepared in reviewed, revised and typeset form, but is not the published PDF as in compliance with IEEE Policy.

# **Novel Screening Techniques for Wind Turbine Power Converters**

A. B. Jørgensen<sup>(1)</sup>, S. D. Sønderskov<sup>(1)</sup>, N. Christensen<sup>(1)</sup>, Kristian L. Frederiksen<sup>(1)</sup> E. Iciragiye<sup>(1)</sup>, A. E. Maarbjerg<sup>(1)</sup>, S. Munk-Nielsen<sup>(1)</sup>, B. Rannestad<sup>(2)</sup>

(1) School of Engineering and Science Aalborg University 9100 Aalborg, Denmark Email: ajarge11@student.aau.dk URL: http://www.ses.aau.dk

Boegildvej 3 7430 Ikast, Denmark Email: bjran@kkwindsolutions.com URL: http://www.kkwindsolutions.com

(2)KK Wind Solutions

## Acknowledgments

Support has been received from the IEPE and CORPE projects funded by Innovation Fund Denmark and the MV platform project funded by the Obel Family Foundation.

## **Keywords**

«IGBT», «Power cycling», «Estimation technique», «Reliability»

### **Abstract**

Power converters represent one of the highest failure rates in the wind turbine. Therefore converter manufacturers perform burn-in tests to prevent shipping of faulty converters. Recent developments in junction temperature estimation, based on accurate online IGBT collector-emitter voltage measurements, allow for thermal stress estimation of the IGBT modules. This is utilized to detect infant mortalities in power converters, by comparing thermal responses of IGBTs for faulty and non-faulty converters. The method proves to be a time and cost efficient candidate to replace burn-in tests of power converters for wind turbines applications.

### Introduction

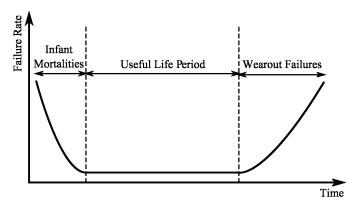

A key issue in modern wind turbines is the reliability. In [1], Spinato et al. investigate the reliability of wind turbine subassemblies. The highest failure rates are found in the electrical system, the rotor and the converter. Spinato et al. suggest that more thorough tests of the converter could eliminate early failures and thereby improve the overall reliability of the wind turbine. The reliability of power converters can be represented by the bathtub curve as shown in Fig. 1 [2].

To avoid infant mortalities, converter manufacturers perform burn-in tests. The purpose of the burn-in tests is to identify converters that are likely to fail early in their life period [3]. This is often done through accelerated operating conditions where the temperature in the converter is at its critical level. The high stress causes the revelation of faulty converters, which are potentially destroyed. In addition to the destruction of the faulty converters, the downside of the burn-in tests is that a vast amount of time and energy is needed to precipitate the infant mortalities. The burn-in tests therefore account for a substantial expense to the converter manufacturers.

The junction temperature is not known in conventional burn-in tests as it is impractical to measure directly. Recent developments in online measurement of temperature-sensitive electrical parameters (TSEP) has led to the possibility of accurately estimating the junction temperature during operation of an IGBT module [4], [5]. This paper aims to investigate if this method for estimating junction temperature can be utilized to detect converter failures which could potentially lead to infant mortality.

Fig. 1: Bathtub curve representing converter failure rate over time.

#### **Faults**

According to [6], possible causes of excessive increase in junction temperature and thereby potential infant mortality of the converter are: Too high losses caused by over load operation, bugs in gate driver circuit, and increased thermal impedance either internally in the power modules or in the interconnection between power module and heat sink.

To determine if a junction temperature estimation based on online measurement of TSEPs is usable for detecting increased switching loss and increased thermal impedance, four fault scenarios are examined: Partly or entirely missing thermal interface material (TIM) between module and heat sink, wrong torque applied to bolts when mounting on heat sink, wrong tightening sequence of bolts and increased switching loss by increasing the gate turn-on resistance.

The scenarios are tested on an Infineon IGBT FF1000R17IE4 power module consisting of two IGBTs and two diodes in a half bridge configuration. The module is rated to 1700 V and 1000 A nominal current.

# **Junction Temperature Estimation**

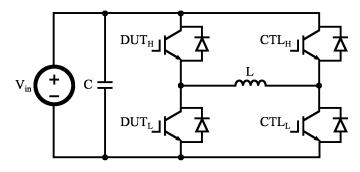

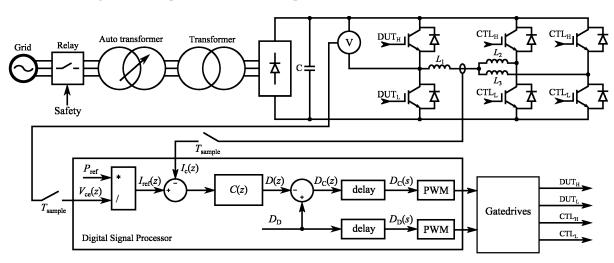

To obtain the TSEP- $T_j$  (junction temperature) characteristics, a calibration is done. The calibration setup is a two half bridge concept consisting of the device under test (DUT) and a control leg (CTL) connected through an inductive load, as shown in Fig. 2. The DUT is externally heated to a specified temperature, ranging from 25°C to 145°C with a 10°C increment. The heat source is a hot plate, mounted on the baseplate of the power module. For each of the temperatures, a calibration is done by ramping the load current to a desired level by having DUT<sub>H</sub> and CTL<sub>L</sub> conducting. Through appropriate switching, the current is conducted through the DUT<sub>H</sub> IGBT. After a specified time ( $t_{meas}$ ) the on-state voltage and the current are measured. A similar process is done for DUT<sub>H</sub> diode, DUT<sub>L</sub> IGBT and DUT<sub>L</sub> diode.  $t_{meas}$  should be sufficiently high, so that the  $V_{ce}$  on-state voltage has settled. Through experiment this time period was found to be 30  $\mu$ s.

Fig. 2: Circuit scheme of calibration setup.

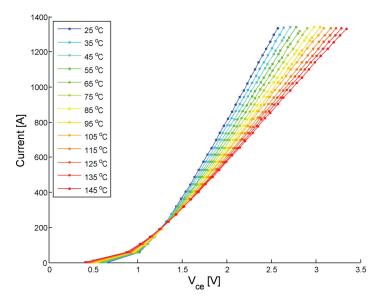

The calibration curves of the IGBT are shown in Fig. 3. The  $V_{ce}$ - $I_c$  characteristics have a positive temperature coefficient (PTC) at high currents and a negative temperature coefficient (NTC) at low currents. This paper will, however, only concern the PTC region, i.e. the region related to high power operation.

Fig. 3: IGBT I-V characteristics at different temperatures.

#### **Temperature calculation**

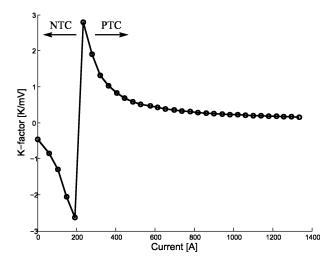

From the calibration curves the calibration factor (K) is obtained. The K-factor is the ratio of change in  $T_j$  to change in  $V_{ce}$  at a specific current level. Applying a linear fit to the  $T_j$ - $V_{ce}$  relation at every measured current of Fig. 3 yields the plot shown in Fig. 4. The plot shows the PTC and NTC regions.

Fig. 4: K-factor plot at different current levels.

Using the K-factor and a  $T_j$ - $V_{ce}$  reference point the junction temperature is calculated from (1).

$$T_{\rm i} = T_{\rm ref} + K(V_{\rm ce} - V_{\rm ref}) \tag{1}$$

$V_{\rm ce}$  is the measured on-state voltage and  $T_{\rm ref}$  is the defined reference temperature, in this case 25°C.  $V_{\rm ref}$  is the calibrated  $V_{\rm ce}$  corresponding to the measured current and the reference temperature. Similarly K is the K-factor value relating to the measured current.

## Thermal impedance

The thermal impedance from the semiconductor junction to the ambient surroundings (through the heat sink) is calculated as:

$$Z_{\rm th}(t) = \frac{T_{\rm j}(t) - T_{\rm a}}{P_{\rm loss}(t)} \tag{2}$$

Where  $T_a$  is the ambient temperature and  $P_{loss}$  is the power loss. If the power loss is kept constant in (2),  $Z_{th}$  will be directly proportional to the junction temperature. The power loss of the DUT<sub>H</sub> is a combination of switching and conduction losses.

$$P_{\rm loss} = P_{\rm cond} + P_{\rm sw} \tag{3}$$

The conduction loss is caused by the on-state voltage of the IGBT and diode when either is conducting. For the IGBT, the average conduction loss is given by

$$P_{\rm cond} = D_{\rm D} V_{\rm ce} I_{\rm c} \tag{4}$$

Where  $D_{\rm D}$  is the duty cycle of the DUT. Switching losses occur when the semiconductor goes from conducting to blocking and vice versa, and thus occurs as pulses of power. This causes issues in regard to keeping a constant power loss in the power module.

By giving a DUT duty cycle of unity i.e. always conducting through the DUT<sub>H</sub> IGBT, power losses consists only of the conduction loss. Thus the power loss can be obtained directly from the measurements of  $V_{ce}$  and  $I_c$ . Thereby, it is possible to calculate  $Z_{th}$  from (2) using the  $P_{cond}$  measurement and the junction temperature estimation.

#### Test bench

A test bench with conduction power loss control is constructed using a structure as shown in Fig. 5. Temperatures of devices in the CTL-leg are not monitored. Two CTL-legs are used in parallel to reduce the stress experienced by a single CTL leg. The two CTL power modules are cooled using Danfoss ShowerPower<sup>®</sup> whereas no active cooling is implemented on the DUT power module. By not having to apply liquid cooling to the DUT, it is easier to exchange the DUT in the setup which saves time and complexity in the test procedure. For safety reasons DC-link discharge and over/undercurrent protection circuits are designed and implemented in the setup.

Fig. 5: Principal schematic of the test bench

#### **Control**

The control is implemented on a F28M36x digital signal processor (DSP). The duty cycle of the DUT,  $D_D$ , follows a given reference by feed forward, while the CTL,  $D_C$ , is given by the controller.  $D_C$  is obtained through a conduction loss controller by feedback of load current  $I_L$  and  $V_{ce}$ .

The open loop transfer function from D to  $I_c$  is derived to be

$$G(s) = \frac{I_{c}(s)}{D(s)} = zoh(s) \cdot delay(s) \cdot G_{L}(s)$$

$$= (e^{-sT_{sample}} - e^{-2sT_{sample}}) \frac{V_{DC}}{s(Ls+R)}$$

(5)

where zoh is the zero order hold, delay is the delay caused by the time period between measurement and updating the control.  $G_L(s)$  is the transfer function of the load,  $T_{\text{sample}}$  is the sampling period, L is load inductance,  $V_{\text{DC}}$  is the DC-link voltage. R is a combination of the load resistance, the IGBT on-resistance and wire resistance. When discretizing (5) becomes

$$G(z) = \frac{I_{\rm c}(z)}{D(z)} = \frac{V_{\rm DC}}{R} \frac{1 - e^{-\frac{R}{L}T_{\rm sample}}}{z(z - e^{-\frac{R}{L}T_{\rm sample}})}$$

(6)

The PI controller has the discrete transfer function as shown in (7).

$$C(z) = K_0 \frac{z - z_0}{z - 1} \tag{7}$$

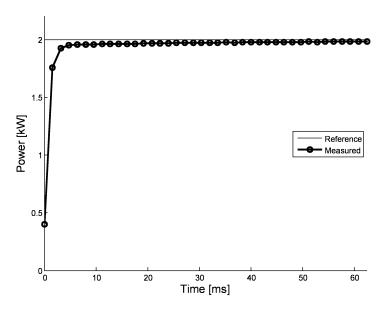

$K_0$  is the controller gain and  $z_0$  is the zero location.  $z_0$  is chosen so that it cancels the G(z) pole at  $e^{-\frac{R}{L}T_{\text{sample}}}$ .  $K_0$  is chosen from a root locus analysis so that no overshoot is present. The designed discrete PI-controller settles at specified conduction power loss levels within 3.2 ms, as shown in Fig. 6

Fig. 6: Power step calculated from measured on-state voltage and current.

## **Faulty Assembly**

Tests are performed with conduction losses at levels of 1 kW, 1.5 kW and 2 kW. In the PTC region,  $V_{ce}$  increases with rising temperature, thus the PI-controller adjusts the current accordingly to maintain constant power loss. The tests are run for 40 s, during which  $V_{ce}$  and  $I_c$  are measured. These measurements are used for junction temperature estimation and are finally translated into thermal impedance using (2).

The first test conducted has the purpose of being a reference for comparing with faulty assemblies. For the reference test the TIM is spread evenly and in the correct amount using a template and the mounting of the module on the heat sink is done according to the specified guidelines [7]. The TIM distribution after test is shown in Fig. 7.

Fig. 7: IGBT and cooling block with correct TIM (left), 2/3 applied TIM (middle), and no TIM (right).

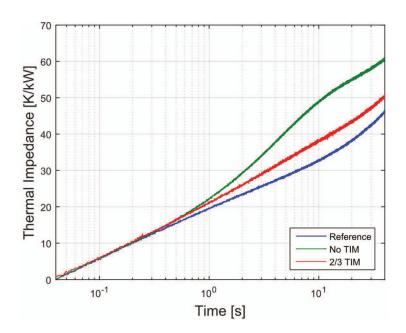

If no TIM is applied (Fig. 7 right) or only two thirds of the power module is covered with TIM (Fig. 7 middle) the heat path from semiconductor to heat sink is obstructed. This is shown in the response of the thermal impedance in Fig. 8. The three curves are equal from zero to around 400 ms. After this point the curves break apart revealing a significant difference in thermal impedance for the three different cases. This highlights that the test procedure is able to distinguish between cases of correctly or poorly distributed TIM.

Fig. 8: Thermal impedance without TIM and with 2/3 applied TIM compared to the reference at 1.5 kW conduction loss.

Tests of wrong mounting sequence and wrong mounting torque are performed. Instead of following mounting sequence given in the guideline [7], bolts are fastened in a counter-clockwise order. In the test of mounting torque, the correct sequence is followed but the applied torque is 2 Nm instead of the recommended 6 Nm. Results of wrong mounting sequence and wrong mounting torques are omitted, as results are indistinguishable from the reference tests. The results are regarded as inconclusive and requires further investigation.

#### **Gate-driver faults**

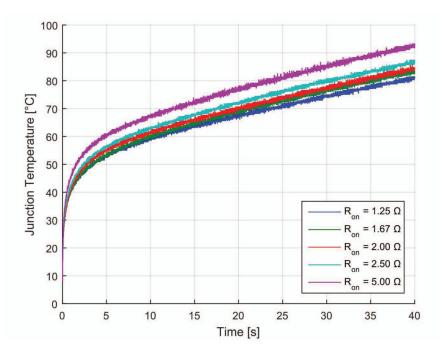

To test if faults in gate turn-on resistance can be detected, five tests are conducted. These tests are performed with switching losses. The first test is conducted using the rated gate resistance followed by four test where the resistance is gradually increased. The tests are done with a DC-link voltage of 600 V, a DUT duty cycle of 0.5 and a reference IGBT conduction loss of 500 W.

Fig. 9: Junction temperature as a function of time with various gate turn-on resistances.

The junction temperature is estimated using the calibrated data. The thermal impedance is not calculated using (2), because losses now include switching losses. The temperature curves for each of the five tests are shown in Fig. 9, calculated using (1). An increase in temperature is seen when increasing the resistance, which is caused by the increased switching loss. Thus the test enables identification of faults leading to increased switching losses.

#### **Discussion**

$Z_{th}$ -curves of Fig. 8 break apart at the same time constant. These results indicate that the fault can be diagnosed at a distance from the junction by evaluating the time constant from which the tested power module deviates from a reference curve. This requires further investigation to be verified.

Industry might still require burn-in tests to be performed, and do not regard proposed methods as being sufficient to ensure reliable power converters. However, the proposed method enables diagnosis of faults prior to the burn-in. This allows the identification of the fault, and thus potentially save valuable hours of burn-in testing before a faulty power converter fails.

#### **Conclusion**

The thermal impedance monitoring of cases where the thermal interface material was partly or entirely missing showed clear indications of faults, whereas the results of wrong mounting momentum and sequence were inconclusive. If the turn-on gate resistance value is modified, it is detectable by examining the differences in thermal responses. The novel temperature estimation method used throughout this paper has proved to be of great potential for power converter screening applications.

#### References

- [1] F. Spinato et al., "Reliability of wind turbine subassemblies," in IET Renewable Power Generation, vol. 3, pp. 1-15, Dec. 2009.

- [2] E. E. Lewis, "Load-capacity interference and the bathtub curve," in Reliability, IEEE Transactions on, vol. 43, pp. 470-475, Sep. 1994.

- [3] N. Sumikawa et al., "An Experiment of Burn-In Time Reduction Based On Parametric Test Analysis" in International Test Conference, pp. 1-10, 2012.

- [4] P. Ghimire et al., "Online monitoring of high-power IGBT modules," in IEEE Industrial Electronics Magazine, vol. 8, no. 3, pp. 40-50, Sep. 2014.

- zine, vol. 8, no. 3, pp. 40-50, Sep. 2014.

[5] P. Ghimire et al., "A real time measurement of junction temperature variation in high power IGBT modules for wind power converter application," Proc. of CIPS, Nuremberg, Germany, 2014.

- [6] A. Volke and M. Hornkamp, "Quality and reliability" in *IGBT Modules: Technologies, Driver and Application*, 2nd ed., Germany, Infineon Technologies AG, ch. 14, sec. 2, pp. 490.

[7] Infineon (2009, September), *Mounting Instructions for PrimePACK*<sup>TM</sup> modules Application Note (AN2009-

- [7] Infineon (2009, September), Mounting Instructions for PrimePACK<sup>TM</sup> modules Application Note (AN2009-08, V1.0) [Online]. Available: http://www.infineon.com/cms/en/product/promo pages/primepack/