High Order VCO Based Delta Sigma Modulator

Amir Babaie Fishani

Promotor: prof. dr. ir. P. Rombouts Proefschrift ingediend tot het behalen van de graad van Doctor in de ingenieurswetenschappen: elektrotechniek

Vakgroep Elektronica en Informatiesystemen Voorzitter: prof. dr. ir. R. Van de Walle Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2016 - 2017

ISBN 978-90-8578-970-3 NUR 959 Wettelijk depot: D/2017/10.500/5

# FACULTEIT INGENIEURSWETENSCHAPPEN EN ARCHITECTUUR

#### Universiteit Gent Faculteit Ingenieurswetenschappen en Architectuur Vakgroep Elektronica en Informatiesystemen

#### Promoter:

Prof. dr. ir. Pieter Rombouts

#### Examination board:

| Prof. dr. ir. Jan Van Campenhout (chairman) | Universiteit Gent                |

|---------------------------------------------|----------------------------------|

| Prof. dr. ir. Pieter Rombouts (promoter*)   | Universiteit Gent                |

| Prof. dr. ir. Jan Doutreloigne              | Universiteit Gent                |

| Prof. dr. ir. Georges Gielen                | Katholieke Universiteit Leuven   |

| Prof. dr. ir. Luis Hernandez                | Universidad Carlos III de Madrid |

| Prof. dr. ir. Marc Moeneclaey               | Universiteit Gent                |

| Prof. dr. ir. Guy Torfs                     | Universiteit Gent                |

<sup>\*</sup> The promoter is not a voting member of the board.

#### Universiteit Gent

Faculteit Ingenieurswetenschappen en Architectuur

Vakgroep Elektronica en Informatiesystemen Technologiepark-Zwijnaarde 15 iGent, 9052 Gent, Belgie.

Tel: +32-9-264-3366 Fax: +32-9-264-3594

This work was supported by FWO.

Dissertation submitted to obtain the degree of Doctor of Electrical Engineering Academic year 2016-2017

## Acknowledgment

First of all, I would like to express my deep appreciation to my advisor Professor Dr. Pieter Rombouts, you have been a tremendous mentor for me. I would like to thank you for encouraging my research and for allowing me to grow as a research scientist. Your advice on both research as well as on my career have been priceless.

I would also like to thank the members of the examination board. Your feedback and comments have been a great help to improve the quality of this work.

I am indebted to Prof. Gielen for all the challenging meetings that we've have had during these years and for his constructive feedbacks at every turn of my work.

My family, whom I immensely love and miss, have always been there for me during my years in Iran and their moral support never stopped afterwards.

I would like to thank the members of the Circuit And System research group (Pieter, Ludo, Maarten, Johan, and Dries) for being such great friends to me and for all the help and advice throughout these years.

The most special thanks to my wife for her unconditional support and love. Thanks for encouraging me to strive towards my goal.

Gent, December 2016 Amir Babaie-Fishani

## Contents

| 1 | Inti | roduction                                   | 1  |

|---|------|---------------------------------------------|----|

|   | 1.1  | Dissertation organization                   | 3  |

| 2 | Pre  | evious work on VCO-ADC                      | 5  |

|   | 2.1  | Basics of Analog to Digital Conversion      | 5  |

|   |      | 2.1.1 Nyquist rate ADC                      | 6  |

|   |      | 2.1.2 Over-sampling ADC                     | 7  |

|   |      | 2.1.3 Discrete Time Delta Sigma Modulator   | 8  |

|   |      | 2.1.4 Continuous Time Delta Sigma Modulator | 10 |

|   | 2.2  | First order VCO-ADC                         | 11 |

|   |      | 2.2.1 Circuit level considerations          | 13 |

|   | 2.3  | PWM pre-coding                              | 14 |

|   | 2.4  | Coarse-fine structure                       | 16 |

|   | 2.5  | Voltage-to-phase VCO-based ADC              | 17 |

|   | 2.6  | High order VCO-based ADC's                  | 19 |

|   |      | 2.6.1 Using conventional loop-filter        | 19 |

|   |      | 2.6.2 MASH VCO-ADC                          | 21 |

|   |      | 2.6.3 All-VCO CT-DSM                        | 22 |

| 3 | Hig  | gh order VCO-based CT-DSM                   | 25 |

|   | 3.1  | Modeling a first order VCO-ADC              | 25 |

|   |      | 3.1.1 Splitting the Sampling Quantizer      | 25 |

|   |      | 3.1.2 CT equivalence of a VCO ADC           | 27 |

|   | 3.2  | Using a VCO as the first Integrator         | 29 |

|   |      | 3.2.1 Introducing the Up-Down Counter       | 30 |

|   |      | 3.2.2 Proposed Scheme                       | 31 |

|   |      | 3.2.3 Simulation results                    | 33 |

|   |      | 3.2.4 Implementation considerations         | 35 |

**iv** Contents

|   | 3.3           | High o  | order All-VCO CT-DSM                            | 36        |

|---|---------------|---------|-------------------------------------------------|-----------|

|   |               | 3.3.1   | VCO based continuous-time integrator            | 36        |

|   |               | 3.3.2   | VCO based sampling quantizer                    | 38        |

|   |               | 3.3.3   | General All-VCO CT-DSM architecture             | 41        |

|   |               | 0.10.10 |                                                 |           |

| 4 | Lin           | ear vo  | ltage controlled ring oscillator                | 43        |

|   | 4.1           | Ring    | oscillator input circuit                        | 43        |

|   | 4.2           | Oscilla | ator core design                                | 45        |

|   | 4.3           | Measu   | arement Results                                 | 47        |

| 5 | The           | eory ar | nd design of a passive ADSM                     | 51        |

|   | 5.1           | Analy   | zing ADSMs without delay                        | 52        |

|   |               | 5.1.1   | Proposed Theory                                 | 54        |

|   |               | 5.1.2   | Simulation Results                              | 60        |

|   |               | 5.1.3   | Conclusion                                      | 63        |

|   | 5.2           | Analy   | zing ADSMs, with loop delay                     | 64        |

|   |               | 5.2.1   | Previous theory and its limitations             | 65        |

|   |               | 5.2.2   | Proposed approach                               | 67        |

|   |               | 5.2.3   | Implications and Results                        | 72        |

|   |               | 5.2.4   | Simulation results                              | 72        |

|   |               | 5.2.5   | Conclusion                                      | 75        |

|   | 5.3           | Imple   | mentation and measurement                       | 77        |

|   |               | 5.3.1   | Passive ADSM                                    | 77        |

|   |               | 5.3.2   | Circuit design                                  | 78        |

|   |               | 5.3.3   | Measurement Results                             | 80        |

|   |               | 5.3.4   | Conclusion                                      | 83        |

| 6 | Des           | sign an | nd implementation of a mostly digital VCO-based | ı         |

|   | $\mathbf{CT}$ | -DSM    | with 3rd order noise shaping                    | <b>85</b> |

|   | 6.1           | Simpl   | ified Implementation                            | 86        |

|   |               | 6.1.1   | Implementation for a Single phase VCO           | 86        |

|   |               | 6.1.2   | Multi phase implementation                      | 89        |

|   |               | 6.1.3   | Reduced degree of freedom in the system         | 91        |

|   | 6.2           | VCO     | and DCO's                                       | 93        |

|   | 6.3           | Exper   | rimental Results                                | 96        |

|   | 6.4           | Conal   | ugion                                           | 105       |

<u>Contents</u> <u>v</u>

| 7 | Imp           | plementation of a 3rd order VCO-based CT-DSM with | h   |  |

|---|---------------|---------------------------------------------------|-----|--|

|   | $\mathbf{PW}$ | M pre-coding                                      | 107 |  |

|   | 7.1           | Implementation details                            | 107 |  |

|   | 7.2           | Implementation and Measurement                    | 110 |  |

|   | 7.3           | Mismatch, aliasing, and inter-modulation          | 112 |  |

|   | 7.4           | Conclusion                                        | 115 |  |

| 8 | Cor           | nclusion                                          | 117 |  |

|   | 8.1           | Contributions                                     | 118 |  |

|   | 8.2           | Future work                                       | 119 |  |

vi Contents

# List of Figures

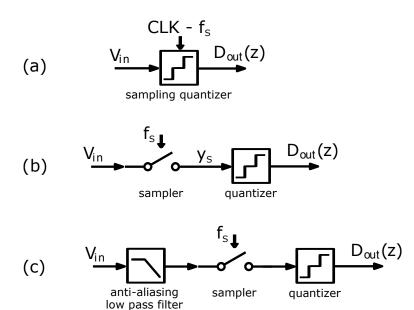

| 2.1 | (a) A sampling quantizer as a Nyquist rate ADC, (b) separating the sampling and quantizing functions, and (c) adding anti-aliasing low pass filter                                                      | 6  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

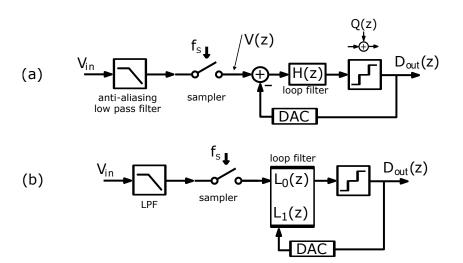

| 2.2 | (a) System level structure of a typical DT-DSM, without additional feed-forward or local feedback paths, and (b) a DT-DSM with a more general loop filter                                               | 9  |

| 2.3 | (a) System level structure of a typical CT-DSM, without additional feed-forward or local feedback paths, and (b) a CT-DSM of the $k$ th order                                                           | 11 |

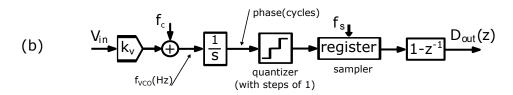

| 2.4 | <ul><li>(a) an open-loop first order VCO based ADC, and</li><li>(b) and (c) its equivalent model</li></ul>                                                                                              | 12 |

| 2.5 | <ul><li>(a) a typical structure for a voltage controlled Ring Oscillator</li><li>(b) a voltage controlled inverting delay stage, used in an RO.</li></ul>                                               | 13 |

| 2.6 | <ul><li>(a) a common implementation for a single phase reset-counter,</li><li>(b) its timing diagram</li></ul>                                                                                          | 15 |

| 2.7 | <ul><li>(a) the system level representation of the PWM pre-coding technique for VCO-ADC linearization.</li><li>(b) the effect of PWM pre-coding technique on the non-linearity curve of a VCO</li></ul> | 16 |

| 2.8 | System level representation of a Coarse-fine VCO-ADC structure, also know as 0-1 MASH VCO-ADC or residue canceling VCO-ADC                                                                              | 17 |

| 2.9 | <ul> <li>(a) a voltage-to-phase VCO based integrator,</li> <li>(b),(c) its system level equivalents,</li> <li>(d) a first order voltage-to-phase VCO based ADC</li> </ul>                               | 18 |

|     |                                                                                                                                                                                                         |    |

viii List of Figures

| 2.10 | <ul><li>(a) using a voltage-to-frequency VCO-ADC as a noise shaping quantizer in the loop of a CT-DSM,</li><li>(b) using a voltage-to-phase VCO-ADC as a noise shaping quantizer in the loop of a CT-DSM.</li></ul>                                                                                                                                                                    | 20 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.11 | The system level structure of a second order 1-1 MASH VCO-ADC                                                                                                                                                                                                                                                                                                                          | 21 |

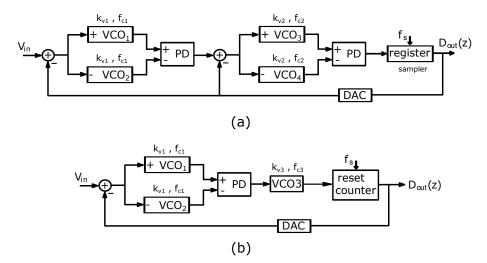

| 2.12 | Two high order VCO based ADC's using voltage-to-phase and voltage-to-frequency integrators and quantizers                                                                                                                                                                                                                                                                              | 22 |

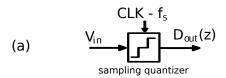

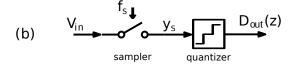

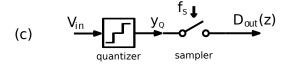

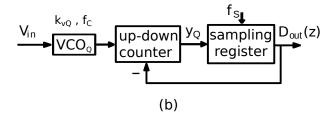

| 3.1  | (a) a sampling quantizer, (b),(c) and its equivalents                                                                                                                                                                                                                                                                                                                                  | 26 |

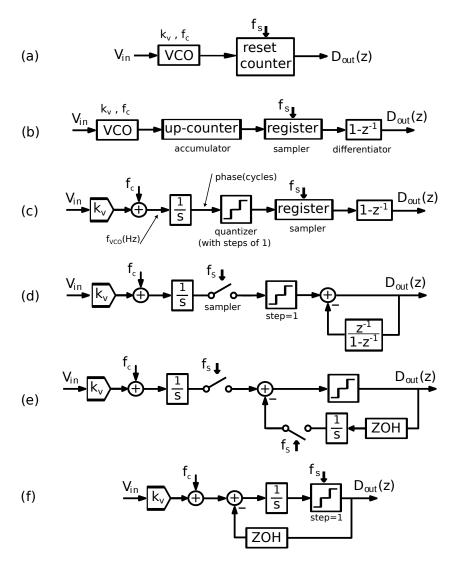

| 3.2  | (a) a first order VCO ADC, (b-f) and its system level equivalents                                                                                                                                                                                                                                                                                                                      | 28 |

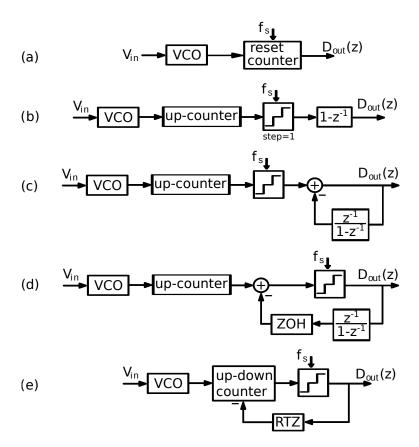

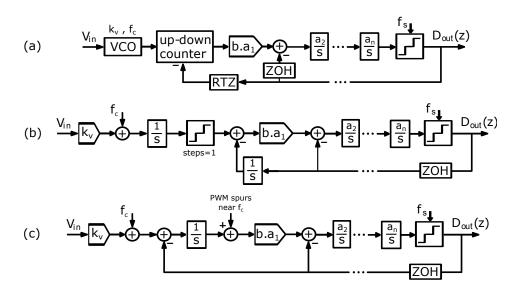

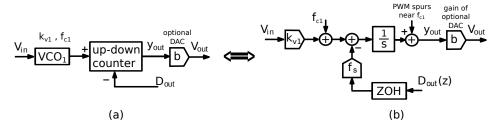

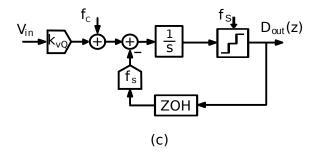

| 3.3  | Metamorphosis of an open-loop first order VCO-ADC to a closed-loop one.  (a) the basic structure of a VCO-ADC  (b) An equivalent system with up-counter and digital differentiator  (c) replacing the differentiator with an integrator in the feedback  (d) extending the loop from digital to analog domain  (e) replacing the up-counter and the integrator with an up-down counter | 31 |

| 3.4  | (a) The proposed system with a VCO as the first integrator, (b),(c) and its CT equivalents                                                                                                                                                                                                                                                                                             | 32 |

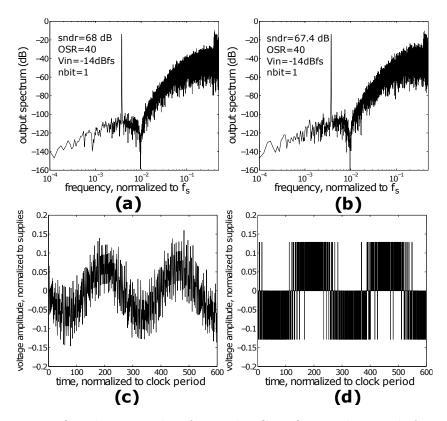

| 3.5  | Simulation results of two 1-bit CT-DSMs with a -14 dBfs input tone.  (a) output spectrum of a conventional 3rd order modulator (b) output spectrum of a VCO-based modulator with the same NTF  (c) output signal of the first integrator for the conventional modulator  (d) output signal of the first integrator for the VCO-based modulator                                         | 34 |

List of Figures ix

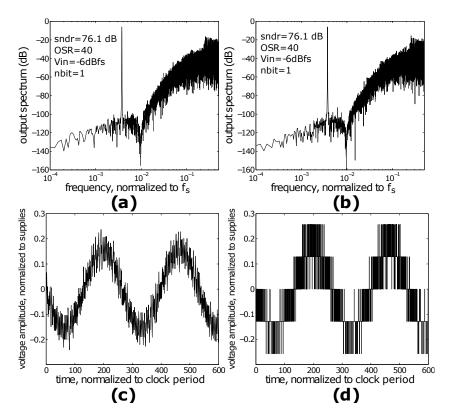

| 3.6 | Simulation results of two 1-bit CT-DSMs with a -6 dBfs input tone.                                                                                                                                                        |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | (a) output spectrum of a conventional 3rd order modulator (b) output spectrum of a VCO-based modulator with the same NTF                                                                                                  |    |

|     | (c) output signal of the first integrator for the conventional modulator                                                                                                                                                  |    |

|     | (d) output signal of the first integrator for the VCO-based modulator                                                                                                                                                     | 35 |

| 3.7 | <ul><li>(a) A VCO based integrator</li><li>(b) and its equivalent continuous-time model</li></ul>                                                                                                                         | 37 |

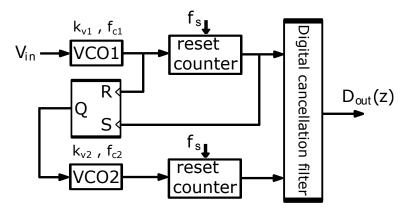

| 3.8 | <ul><li>(a) A First-order noise shaping quantizer consisting of a VCO and a reset-counter,</li><li>(b) an alternative implementation with the same behavior</li><li>(c) and an equivalent continuous time model</li></ul> | 39 |

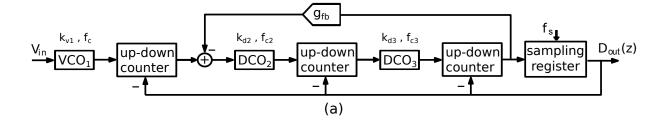

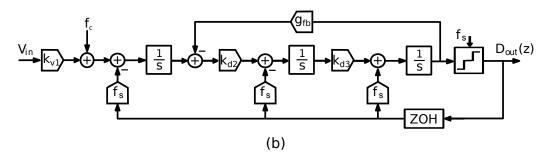

| 3.9 | (a) Proposed architecture of a 3rd-order all-VCO CT-DSM (b) and its equivalent CT-DSM                                                                                                                                     | 40 |

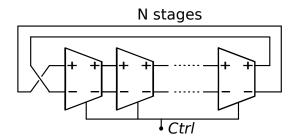

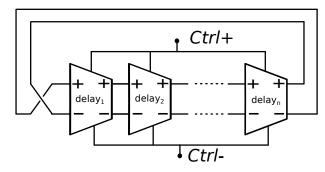

| 4.1 | Ring oscillator with $N$ differential delay elements                                                                                                                                                                      | 43 |

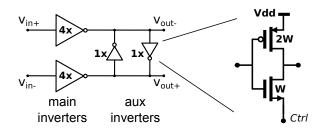

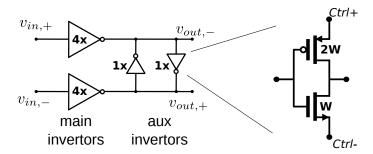

| 4.2 | Delay cell used in the ring oscillator                                                                                                                                                                                    | 44 |

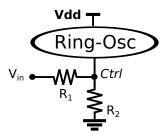

| 4.3 | Ring oscillator with resistive input stage                                                                                                                                                                                | 45 |

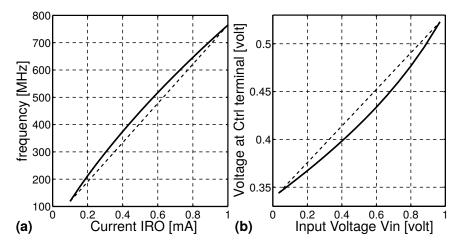

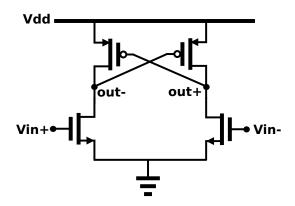

| 4.4 | (a) Tuning curve with current control exhibiting a negative curvature,<br>(b) and Control voltage $V_{ctrl}$ vs the input voltage curve exhibiting a positive curvature.                                                  | 46 |

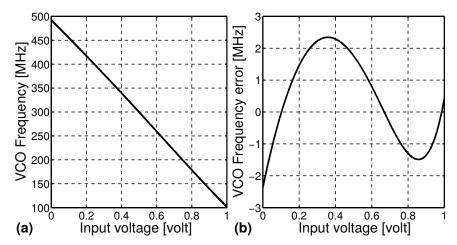

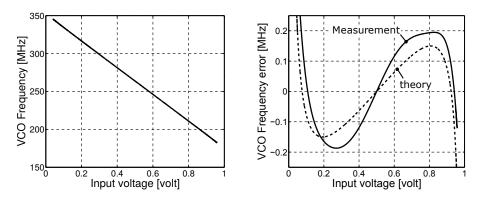

| 4.5 | (a) the voltage to frequency conversion curve of the proposed VCO (b) and the nonlinearity of its frequency error                                                                                                         | 47 |

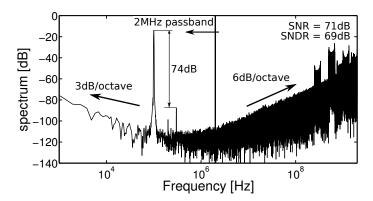

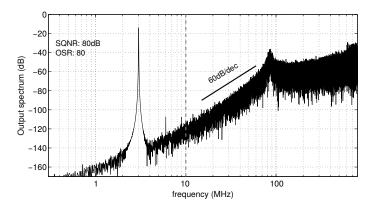

| 4.6 | Output spectrum of the pseudo differential VCO ADC experiment.                                                                                                                                                            | 48 |

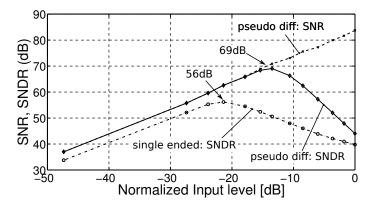

| 4.7 | SNR and SNDR vs. the normalized rail to rail input level (of 2Vpp differentially)                                                                                                                                         | 49 |

| 5.1 | A typical spectrum for the output of an ADSM                                                                                                                                                                              | 53 |

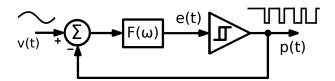

| 5.2 | A general representation of an ADSM                                                                                                                                                                                       | 54 |

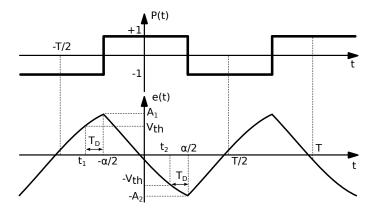

| 5.3 | Typical waveforms for the ADSM in Fig. 5.2                                                                                                                                                                                | 55 |

x List of Figures

| 5.4  | Comparison between simulation results and theory for a 1st order ADSM with a DC input:                                                                                                             |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | a) the difference between the DC level of output and input signals,                                                                                                                                |     |

|      | b) and the carrier frequency                                                                                                                                                                       | 62  |

| 5.5  | Comparison between simulation results and theory for an ADSM with a 1st order passive filter                                                                                                       | 63  |

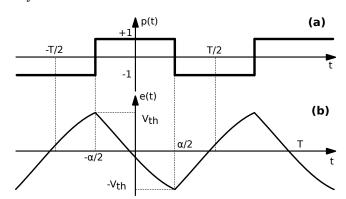

| 5.6  | Average carrier frequency, $\overline{f_c}$ , and the 3rd order distortion, $d_3$ , of a 1st order ADSM as a function of its input amplitude $A. \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 64  |

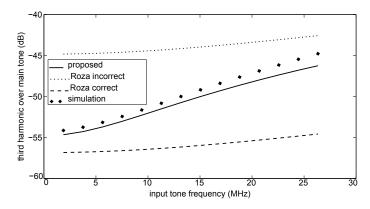

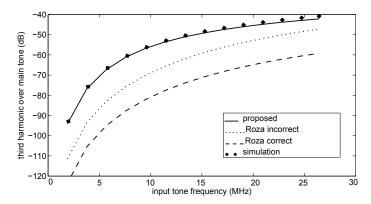

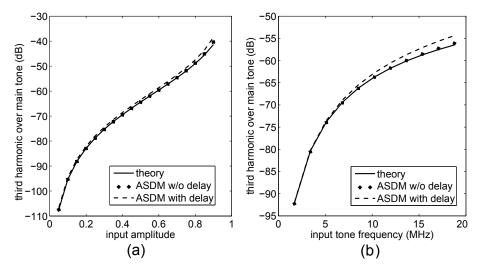

| 5.7  | Comparison between simulation results and theory for the 3rd order harmonic distortion of a 3rd order ADSM over its input frequency                                                                | 65  |

| 5.8  | Average carrier frequency, $\overline{f_c}$ , and 3rd order distortion, $d_3$ , of a 3rd order ADSM vs. the input amplitude, $A$ .                                                                 | 66  |

| 5.9  | General representation of an ADSM,                                                                                                                                                                 |     |

|      | (a) without extra delay in the loop,                                                                                                                                                               |     |

|      | (b) and with loop delay                                                                                                                                                                            | 67  |

| 5.10 | Typical waveforms of an schmitt trigger based ADSM with                                                                                                                                            |     |

|      | delay                                                                                                                                                                                              | 68  |

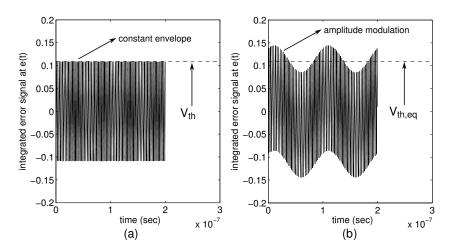

| 5.11 | typical waveforms of two ADSMs,                                                                                                                                                                    |     |

|      | a) without any delay in the loop,                                                                                                                                                                  |     |

|      | b) and with loop delay                                                                                                                                                                             | 73  |

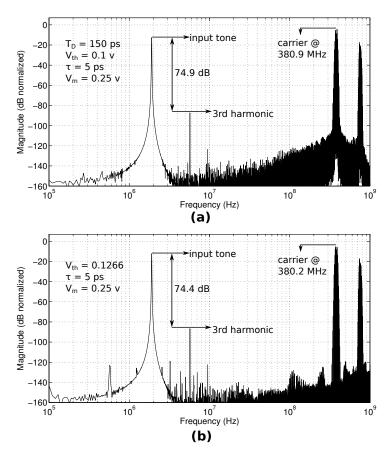

| 5.12 | Output spectrum of two equivalent ADSMs with first order                                                                                                                                           |     |

|      | loop filter,                                                                                                                                                                                       |     |

|      | (a) with some delay in the loop,                                                                                                                                                                   | 7.4 |

| F 10 | (b) and without loop delay                                                                                                                                                                         | 74  |

| 5.13 | Comparing the distortion of two equivalent second order                                                                                                                                            | 7-  |

| - 11 | ADSMs with theory                                                                                                                                                                                  | 75  |

| 5.14 | (a) block diagram of a Passive ADSM,                                                                                                                                                               | 77  |

| F 1F | (b) and its circuit.                                                                                                                                                                               | 77  |

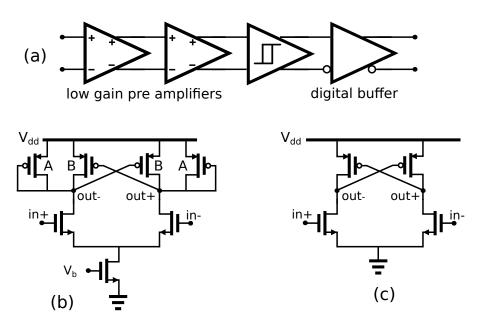

| 5.15 | (a) Overall Schmitt Trigger structure,                                                                                                                                                             |     |

|      | (b) schematic of the Pre amplifier, which (apart from the                                                                                                                                          |     |

|      | sizing) is identical to the Schmitt Trigger's schematic,<br>(c) and the digital buffer circuit                                                                                                     | 79  |

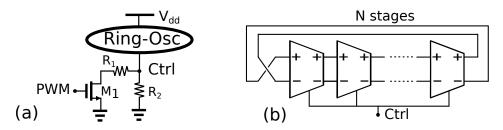

| 5 16 | (a) input circuit of a Two-level Ring oscillator,                                                                                                                                                  | 19  |

| 0.10 | (a) input circuit of a Two-level King oscillator, (b) and the actual ring                                                                                                                          | 80  |

| 5 17 | I/O and nonlinearity plots. (Theory from Eq. 5.53)                                                                                                                                                 | 82  |

| 0.11 | 1/ 5 and nonlinearly proper (Theory non Eq. 9.99)                                                                                                                                                  | 02  |

List of Figures xi

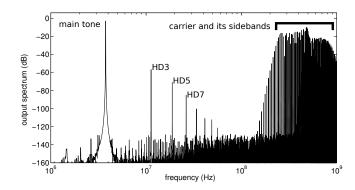

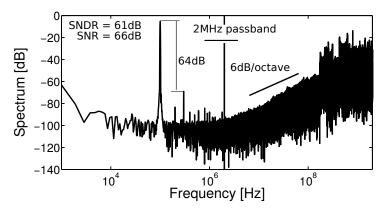

| 5.18 | Output spectrum of the linearized VCO for a 550 mV $_{pp}$ 100 kHz input signal                                                                                                                                                                                           |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.19 | SNR and SNDR vs. the normalized rail to rail input level (of 1 Vpp). (Theory in Eq. 5.54)                                                                                                                                                                                 |

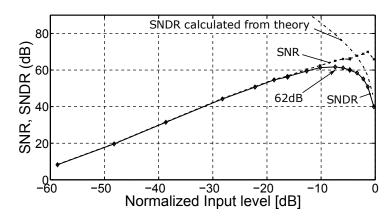

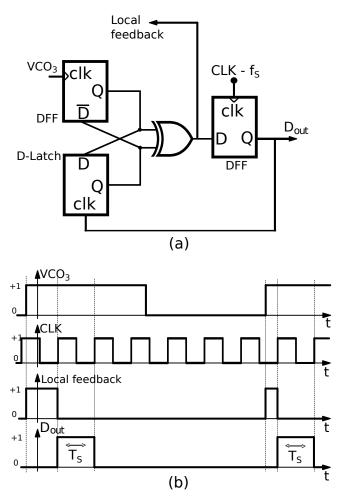

| 6.1  | <ul><li>(a) The proposed implementation of a single phase up-down counter,</li><li>(b) and its timing diagram.</li><li>8</li></ul>                                                                                                                                        |

| 6.2  | (a) The proposed implementation of a reset counter, (b) and its timing diagram                                                                                                                                                                                            |

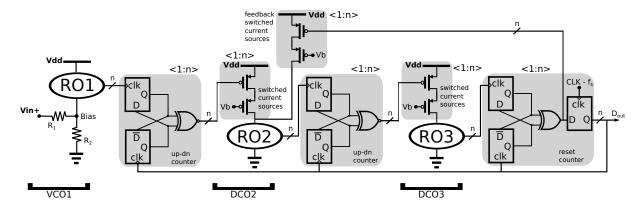

| 6.3  | The proposed implementation of a high order VCO-ADC (with local feedback), where the digital signals are represented by $n$ parallel thermometer encoded bits 900                                                                                                         |

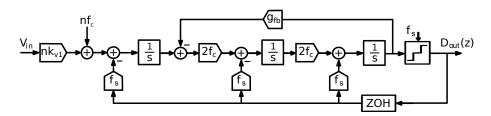

| 6.4  | The equivalent CT-DSM of our implemented VCO-ADC with reduced degree of freedom                                                                                                                                                                                           |

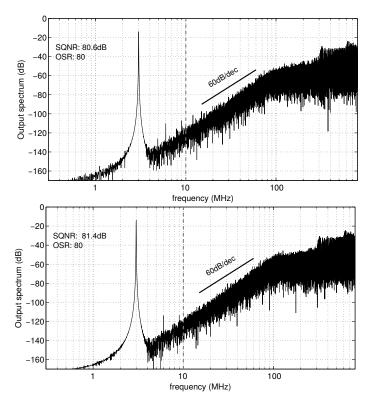

| 6.5  | Output spectrum (160K pt FFT) of a behavioral simulation result for the case $f_s$ =1.6 GHz, $f_c$ =250 MHz and n=9: (a) the actual structure of Fig. 6.3 (b) the equivalent continuous time model of Fig. 6.4 9:                                                         |

| 6.6  | Ring Oscillator core                                                                                                                                                                                                                                                      |

| 6.7  | Differential delay element used in the Ring Oscillator core . 9-                                                                                                                                                                                                          |

| 6.8  | The level-shifter for RO2 and RO3                                                                                                                                                                                                                                         |

| 6.9  | The output spectrum (160K pt FFT) of a behavioral simulation result for the case $f_s$ =1.6 GHz, $f_c$ =250 MHz and n=9, where a level shifter delay of 700 ps is inserted after each VCO                                                                                 |

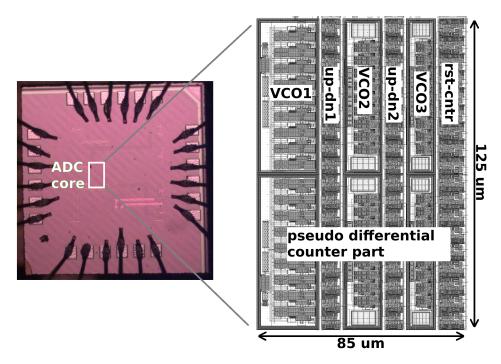

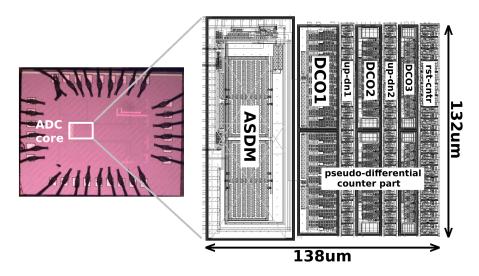

| 6.10 | Chip microscope photograph with annotated layout 9                                                                                                                                                                                                                        |

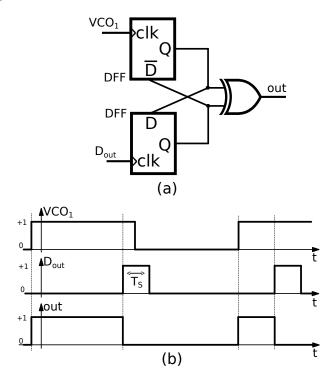

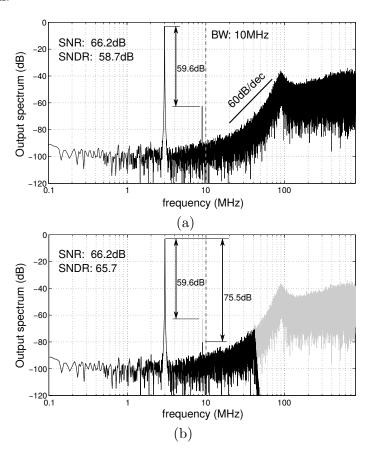

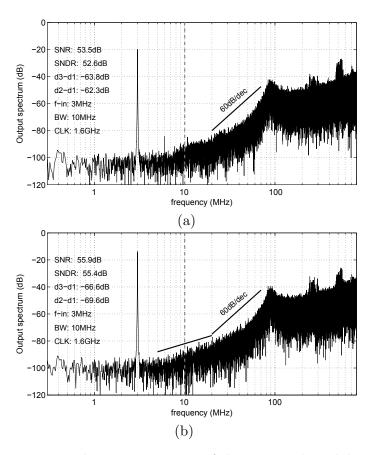

| 6.11 | Measured output spectrum (160K pt FFT) for the case of $f_c = 250$ MHz and $f_s = 1.6$ GHz with a 3 MHz input tone with an amplitude of a 650mVpp differentially: (a) normal (pseudo-differential) output, (b) partially decimated (pseudo-differential) output with off- |

| C 10 | line digital calibration overlayed on the raw output 96                                                                                                                                                                                                                   |

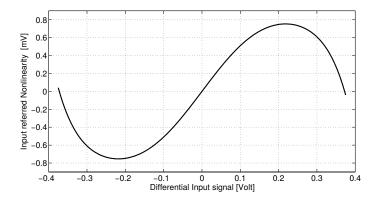

| 0.12 | Static nonlinearity plot of the ADC for the case of of $f_c = 250$ MHz and $f_s = 1.6$ GHz in the pseudo differential configuration                                                                                                                                       |

|      |                                                                                                                                                                                                                                                                           |

xii List of Figures

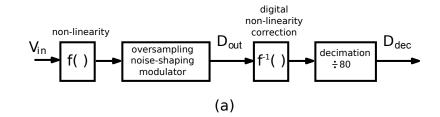

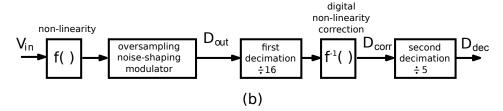

| 6.13 | Block diagram of an oversampling converter with off-line dig-                            |      |

|------|------------------------------------------------------------------------------------------|------|

|      | ital calibration:                                                                        |      |

|      | a) conventional setup discussed in this section,                                         |      |

|      | b) and setup used in this work                                                           | 101  |

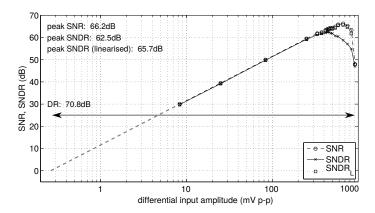

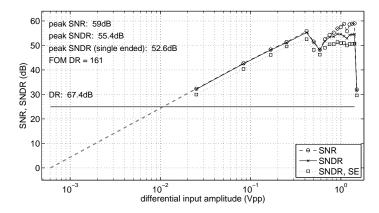

| 6.14 | Dynamic range plot for the case of $f_c = 250$ MHz, $f_s = 1.6$ GHz and 10 MHz bandwidth | 102  |

| C 15 |                                                                                          | 102  |

| 0.15 | Baseband FFT plot for the case of two-tone input signal                                  |      |

|      | of two tones near 9 MHz with the same peak-to-peak signal                                |      |

|      | level as for the plot of Fig. 6.11 (650mVpp differentially): (a)                         |      |

|      | normal (pseudo-differential) output, (b) (pseudo-differential)                           |      |

|      | output with off-line digital calibration                                                 | 103  |

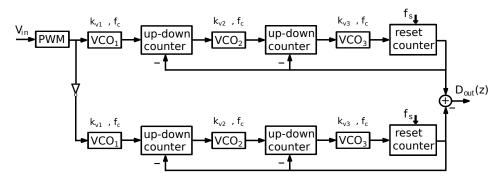

| 7 1  | Custom level representation of the managed record differen                               |      |

| 7.1  | System level representation of the proposed pseudo differen-                             | 100  |

| 7.0  | tial 3rd order VCO-ADC with PWM pre-coding                                               | 108  |

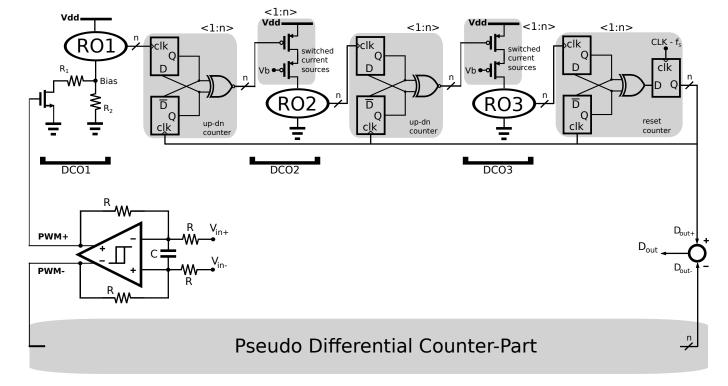

| 7.2  | The circuit level implementation for the system proposed in                              | 100  |

|      | Fig. 7.1                                                                                 | 109  |

| 7.3  | A photograph of the fabricated die                                                       | 110  |

| 7.4  | Measured output spectrum of the presented modulator with                                 |      |

|      | a sine wave input voltage, $V_{pp} = 400 \ mv$ ,                                         |      |

|      | (a) single-ended measurement,                                                            |      |

|      | (b) pseudo-differential measurement                                                      | 111  |

| 7.5  | The SNR/SNDR curve of the measured ADC                                                   | 112  |

| 7.6  | Measured output spectrum of the single-ended modulator                                   |      |

|      | with a sine wave input voltage, $V_{pp} = 600 \ mV$                                      | 113  |

| 7.7  | The output spectrum of a system level noise-less simulation                              |      |

|      | of the modulator with a sine wave input voltage, $V_{pp} = 600 \ mV$                     | .113 |

| 7.8  | Measured output spectrum of the modulator on a linear scale                              |      |

|      | for input sine wave with a small amplitude                                               | 114  |

# List of Tables

| 6.1 | Comparison with related work                             | 104 |

|-----|----------------------------------------------------------|-----|

| 7.1 | Performance summary of the presented works in this book. | 115 |

xiv List of Tables

## Summary

This work aims at exploring new ways of realizing analog functions in time based blocks, instead of voltage based ones. The two functions that were of utmost importance to this work are integration and quantization. Using these two functions one can implement important analog blocks, such as analog filters and analog to digital converters.

The main incentive for time-domain signal processing is to benefit from the digital blocks that are becoming faster and more efficient in the newer CMOS technologies. Moreover, in the more advanced CMOS processes it has become more challenging to design these functions in the voltage domain. This is partly due to the fact the transistors can only deliver a smaller gain, the threshold voltage of the transistors is not dropping as rapidly as the supply voltage, and this loss of voltage headroom is causing dynamic-range loss.

This book investigates linear, low-voltage, low-area, solutions for the design of Continuous-Time Delta Sigma Modulators (CT-DSM) with high orders of quantization noise shaping. In this pursuit we have proposed the design of, and showcased the implementation of, high order VCO-Based ADC's, linear VCO's, and Asynchronous Delta Sigma Modulators (ADSM). All of the presented designs are digital friendly and make use of no traditional analog building blocks, like op-amps and highly linear transconductors. Being digital friendly means having the potential to benefit from technology scaling and being synthesizable using digital design flow.

On a system level, a new VCO-based CT-DSM structure is presented. In this system the combination of a VCO (Voltage Controlled Oscillator) and some digital blocks (referred to as up-down counter) is used as an integrator. The quantizer of the modulator is also VCO-based. Since a VCO can be implemented using an RO (Ring Oscillator), it can be very simple and digital friendly. In this manner a high order CT-DSM can be designed using only these blocks. Typical CT-DSM techniques, such as local feedback can

be incorporated in this novel structure. Many circuit level innovations and simplifications are presented to make the implementation of this modulator possible. The final circuit level solution is very simple to design and size. Therefore, it is expected to be easy to migrate from one technology node to another. The linearity of this modulator is limited by that of the first VCO on the signal path.

A thorough theoretical work is carried out in modeling an ADSM to predict its linearity performance. ADSM's are a family of PWM's (Pulse Width Modulator) that have many applications, like linearizing a VCO-based ADC. It is also proven this block can be implemented using only a Schmitt trigger and a passive loop filter, which is also simple to design and can benefit from technology scaling. Previous implementations of an ADSM or a PWM, presented in literature, required either an op-amp based or  $g_mC$  based integrator. The effect of delay in the loop of an ADSM is also studied and accurate equations to predict the linearity and oscillation frequencies of an ADSM with loop delay are extracted. As a proof of concept, a passive ADSM is implemented in 65nm CMOS technology. The design is operational under a 1 V supply and has more than 10 bit linearity over a 10 MHz bandwidth.

A circuit level solution is presented to design a voltage controlled ring oscillator with high linearity. The implemented prototype of this block was shown to be much more linear than previous works – in other works the non-linearity of the VCO is not mentioned, it is only stated that the VCO has severe non-linearity and should be compensated using different methods. This block can be used as the first VCO in a high order CT-DSM. This block determines the linearity of the overall modulator. A prototype is implemented in the 65 nm technology and the measured voltage to frequency conversion curve of the VCO for a rail-to-rail input shows a small 0.6 % deviation from an ideal line. Measurements on a pseudo-differential setup proved that the second harmonic distortion of the VCO can be heavily suppressed.

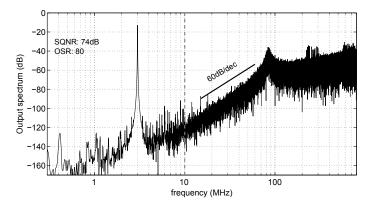

As a proof of concept, for the first time a 3rd order VCO-based CT-DSM is implemented in the low power version of a 65nm technology for a 10 MHz bandwidth. This prototype shows a measured performance of 71/66.2/62.5 dB DR/SNR/SNDR at a 10 MHz bandwidth while consuming 1.8 mW from a 1.0 V analog and 1.9 mW from a 1.2 V digital supply. With digital calibration, the nonlinearity could be pushed below the noise level, leading to an improved peak SNDR of 66 dB. The modulator covers a small

Summary xvii

silicon area of only  $0.01 \text{ mm}^2$ .

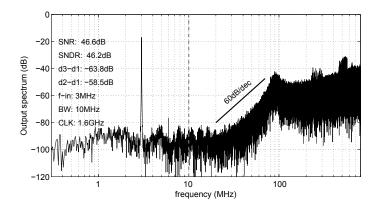

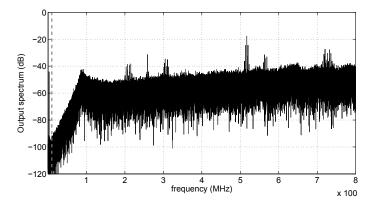

As a second attempt to design a linear mostly digital low voltage high order VCO based CT-DSM, an ADSM is used before the first VCO to linearize it. A proof of concept is implemented in the low power version of a 65 nm technology for a 10 MHz bandwidth. This prototype shows a measured performance of 67.4/59/55.4 dB DR/SNR/SNDR at a 10 MHz bandwidth while consuming 2.3 mW from a 1.0 V analog and 2 mW from a 1.2 V digital supply. The modulator covers a silicon area of 0.018 mm<sup>2</sup>.

List of the publications that have resulted from this work can be found here [1-7].

## Samenvatting

Het doel van dit werk is het verkennen van nieuwe manieren om analoge functionaliteit te realiseren in het zogenaamde "tijdsdomein" in plaats van het gebruikelijke "spanningsdomein". Er zijn twee basisbewerkingen die de grondslag vormen van de rest van dit werk. Deze basisbewerkingen zijn enerzijds *integratie* en anderzijds *kwantisering*. Op basis van deze twee basisbewerkingen kan men belangrijke analoge bouwblokken realiseren, zoals analoge filters en analoog-naar-digitaal omzetters.

De belangrijkste stimulans om over te stappen naar "tijdsdomein"signaalverwerking is om te proberen profijt te halen uit het feit dat de

digitale blokken steeds sneller en efficiënter worden in de nieuwere CMOStechnologieën. Bovendien, in de diep-submicron CMOS-processen die vandaag bijna standaard zijn, wordt het steeds moeilijker om deze functies te

realiseren in het "spanningsdomein". Dit is deels te wijten aan het feit

dat de diep-submicron-transistoren slechts een lage versterking kunnen realiseren. Verder is er het probleem dat de voedingsspanning enorm veel

verlaagd is, terwijl de drempelspanning van de transistoren niet evenredig

mee verlaagd is. Het gevolg hiervan is dat er niet veel ruimte is om een

acceptabele spanningszwaai te realiseren. Dit stelt uiteraard problemen als

men een groot dynamisch bereik wil realiseren.

Deze tekst onderzoekt lineaire oplossingen voor het ontwerp van Delta Sigma Modulatoren op basis van filters die in continue tijd werken (Engels: Continuous Time Sigma Delta Modulator, afgekort CT-DSM). Hierbij is het de bedoeling dat deze circuits bij een lage voedingsspanning kunnen werken en dat ze een kleine chipoppervlakte innemen. Tijdens onze zoektocht hebben we verscheidene ontwerpsmethodes voorgesteld en die ook gedemonstreerd met praktische implementaties. In het bijzonder, hebben we Analoog-naar-Digitaal Omzetters op basis van VCO's voorgesteld die, in tegenstelling tot wat tot nu toe haalbaar was, een hoge orde van spectraal kneden realiseren. Verder hebben we een zeer lineaire VCO voorgesteld

en Asynschrone Delta Sigma Modulatoren (ASDM). Al de voorgestelde technieken en gerealiseerde ontwerpen leunen dicht aan bij digitale circuits (Engels: "digital friendly"): ze vereisen geen veeleisende traditionale analoge bouwblokken zoals operationele versterkers, of lineaire transconductantietrappen. Integendeel, alle voorgestelde circuits zouden in principe zelfs gedeeltelijk gesynthetiseerd kunnen worden met standaard digitale ontwerpssoftware.

Op systeemniyeau, werd een nieuwe CT-DSM-structuur op basis van VCO's gepresenteerd. In dit systeem wordt de combinatie van een VCO en een aantal digitale blokken (die we kunnen beschouwen als een op-en-neerteller) gebruikt als een analoge integrator. Ook de kwantiseereenheid van de modulator is gebaseerd op een VCO. Aangezien een VCO kan worden uitgevoerd met behulp van een ringoscillator (RO), kan een dergelijk VCO heel eenvoudig zijn en zelfs bijna als een digitaal circuit beschouwd worden. Door meerdere van deze integratoren te combineren, kan een CT-DSM van hoge orde worden gemaakt. Typische verfijningen die in CT-DSM toegepast kunnen worden, zoals het gebruikt van lokale terugkoppeling, kunnen ook in deze nieuwe structuur worden opgenomen. Om de praktische realisatie van een prototype modulator mogelijk te maken, werden nog verscheidene innovaties en vereenvoudigingen op circuitniveau voorgesteld. De oplossing die we uiteindelijk op circuitniveau voorstellen, is zeer eenvoudig te ontwerpen en te dimensioneren. Daarom verwachten we dat dergelijke circuits gemakkelijk te migreren zullen zijn van de ene technologieknoop naar een andere. De voorgestelde structuur heeft echter één beperking: namelijk dat de lineariteit van de modulator wordt beperkt door die van de eerste VCO in het signaalpad.

In deze context, werd een grondige theoretische studie uitgevoerd om de niet-lineariteit van een ADSM te voorspellen. ADSM's zijn een familie van PWM's (Puls Breedte Modulatoren), die vele toepassingen hebben. De toepassing die ons interesseerde is het linearizeren van onze VCO-ADC. Bij onze studie, is aangetoond dat dit blok kan worden geïmplementeerd op basis van een Schmitt-trigger en verder een volledig passief lusfilter. Dit zijn weliswaar analoge circuits, maar ze zijn zo eenvoudig dat het ontwerp ervan geen enkel probleem stelt, zelfs in de geschaalde CMOS-technologie van vandaag. Eerdere implementaties van een ADSM of PWM, die in de literatuur werden beschreven, vereisten steeds een actieve integrator (met een operationele versterker of een lineaire transconductantietrap). Het effect van de vertraging in de lus van een ADSM werd ook bestudeerd en nauwkeurige

Samenvatting xxi

vergelijkingen om de lineariteit en de oscillatiefrequentie van een ADSM met lusvertraging te voorspellen werden voorgesteld. Als demonstrator, werd een passieve ADSM geïmplementeerd in 65 nm CMOS-technologie. Het ontwerp is operationeel bij een voedingsspanning van 1 volt en behaalt meer dan 10 bit lineariteit bij een bandbreedte van 10 MHz.

Daarnaast werd ook een oplossing op circuitniveau voorgesteld om een VCO met een hoge lineariteit te realiseren. De lineariteit van ons geïmplementeerd prototype van dit circuit bleek grootteordes beter te zijn dan de voorgaande "state-of-the-art". Dit circuit kan dan worden gebruikt als de eerste VCO in onze CT-DSM met spectrale kneding van hoge orde. We hadden al vermeld dat de eerste VCO in deze nieuwe architectuur de lineariteit van de totale modulator bepaalt. Ons prototype is geïmplementeerd in een 65 nm CMOStechnologie en de gemeten spanning naar frequentie omzettingscurve van de VCO, vertoont voor een volledige signaalzwaai van de onderste voedingslijn naar de bovenste voedingslijn slechts 0.6 % niet-lineariteit (afwijking van de ideale lijn). Daarenboven kan het circuit ook in een pseudo-differentiële opstelling gebruikt worden, waarbij de prestaties nog verder verbeterd werden doordat de tweede-orde vervorming van de VCO hierdoor sterk wordt onderdrukt.

Als proof-of-concept, hebben we de voorgestelde concepten dan gecombineerd in een CT-DSM op basis van VCO's. Dit is de eerste keer dat een circuit met 3de orde spectrale kneding van de kwantiseringsruis werd gedemonstreerd. Het ontwerp werd gedaan in de zogenaamde "low power" versie van een 65 nm-technologie. De signaalbandbreedte was 10 MHz. De gemeten prestaties van ons prototype zijn: een DR/SNR/SNDR van 71/66.2/62.5 dB bij een bandbreedte van 10 MHz en een verbruik van 1.8 mW aan de analoge voeding van 1.0 V en 1.9 mW aan de digitale voeding van 1.2V. Met digitale kalibratie kunnnen de fouten door nietlineariteit beneden het ruisniveau worden geduwd, waardoor een betere piek SNDR van 66dB behaald werd. De modulator neemt een zeer kleine chipoppervlakte in van slechts 0.01 mm².

Daarna hebben we een tweede poging gedaan om een lineaire bijnadigitale CT-DSM op basis van VCO's te ontwerpen. Weer werd een lage voedingsspanning en een hoge-orde van spectrale kneding van de kwantiseringsruis beoogd. Hierbij werd nu een ADSM gebruikt die voor de eerste VCO in het circuit werd geplaatst met als doel de ADC als geheel te lineariseren. Een proof-of-concept circuit van dit idee werd geïmplementeerd, opnieuw "low power" versie van een 65 nm-technologie. Hierbij werd ook

gemikt op een signaalbandbreedte van 10 MHz. De gemeten prestaties van dit prototype bij een bandbreedte van 10 MHz zijn: een DR/SNR/SNDR van 67.4/59/55.4 dB bij een verbruik van 2.3 mW aan de analoge 1.0 V voeding en 2 mW aan de digitale 1.2 V voeding. Deze modulator neemt een nog steeds een zeer kleine chipoppervlakte in van 0.018 mm² (zij het iets groter dan het eerste prototype).

# Glossary of symbols and abbreviations

ADC analog-to-digital converter

ADSM asynchronous delta sigma modulator

BWbandwidth CTcontinuous time

CT-DSM continuous time delta sigma modulator

DAC digital-to-analog converter

decibel dBdecdecade

DEM dynamic element matching

DRdynamic range

DSM delta sigma modulator

DTdiscrete time

DT-DSM discrete time delta sigma modulator

DWA data weighted averaging

FBfeedback FFfeedforward FSfull scale

trans-conducting amplifier gm

LSB least significant bit most significant bit **MSB** NRZ non-return-to-zero NTF noise transfer function OSR oversampling ratio PWMpulse width modulator Q quantization noise PM

phase margin

#### xxiv

| RO | ring oscillator |

|----|-----------------|

| RZ | return-to-zero  |

SCR switched-capacitor-resistor SDR signal-to-distortion ratio

SNDR signal-to-noise-and-distortion ratio

SNR signal-to-noise ratio

SQNR signal-to-quantization-noise ratio

STF signal transfer function

THD total harmonic distortion

VCO voltage controlled oscillator

ZOH zero-order hold

### Chapter 1

### Introduction

Traditionally, high-performance Analog-to-Digital converters (ADCs) have heavily relied on conventional analog building blocks such as operational amplifiers, transconductors and comparators [8–14].

Unfortunately, in today's ultra deep sub-micron CMOS technologies these building blocks become increasingly difficult to design because of limited voltage headroom due to the low supply voltage combined with reduced raw 'analog' performance of the elementary transistors (e.g. gain, matching, 1/f noise) [15]. Moreover these analog circuits have poor portability to other technology nodes and efficient testing is a specialty in itself [16].

For this reason, researchers have attempted to find more 'digital' solutions for these traditionally analog blocks. A promising approach here, are the VCO-based ADCs [17–26]. If the VCO-core is a ring-oscillator, this corresponds to a 'nearly digital' implementation. A Ring Oscillator consists a loop of inverters or buffers, with an input dependent propagation delay, which are easy to design in every given technology.

Such a VCO-ADC was shown to exhibit first-order quantization noise shaping and to have very similar behavior as a first-order  $\Sigma\Delta$  modulator [20]. However, in the vast majority of the VCO-ADC designs that have been published, the VCO is still combined with sophisticated analog building blocks (i.e. opamps, transconductors, ...), e.g. [17–19]. The reason for this is to solve the two fundamental problems of VCO-ADC's. First, VCO-ADC's have poor linearity, and second, they have only first order noise shaping. In this book it is attempted to solve both deficiencies while avoiding sophisticated analog building blocks. A low supply voltage and low silicon area consumption have been the main targets through out this

exploration.

VCO-ADCs suffer from nonlinearity problems because the linearity of the voltage to frequency conversion of most VCOs is very poor. This problem can be tackled by combining the VCO-ADC with established analog techniques such as feedback. However, there are also digital-friendly solutions such as digital (self)-calibration [23–28]. And of course, the most simple solution would be to start from a VCO-ADC that has sufficient linearity, which is explored in this dissertation, where a very simple circuit for a linear ring-oscillator based VCO is proposed.

Another potential solution to solve the linearity issue is to convert the input voltage into a two-level signal where the information is stored in the duty cycle of the resulting square-wave using an Asynchronous Delta Sigma Modulator (ADSM) or a Pulse Width Modulator (PWM). This method is known as 'PWM pre-coding' [29–31]. Until now all reported implementations either required an op-amp, a highly linear ramp source, or a linear gm cell [30–32] ('gm' stands for a trans-conducting amplifier). In practice such high-performance analog circuits are difficult to implement at today's low supply voltages (of the order of 1 Volt) and hence are to be avoided. An alternative would be an ADSM with a passive RC loop filter [2, 3, 29]. However, it is not obvious how such a passive ADSM should be designed as to achieve simultaneously high bandwidth and good linearity. For this reason, until now, such a circuit has not yet been demonstrated in practice. In this work, we explain how such a passive ADSM linearization of a VCO can be designed to achieve good overall performance. The validity of the presented theory is confirmed by measurements on an implemented prototype.

As mentioned earlier, the second reason why most VCO-ADCs are combined with analog techniques is that, to the authors' knowledge, all publications of 'implemented' mostly digital VCO-ADC prototypes only exhibit first-order quantization noise shaping [23–28]. In some implementations a VCO-ADC is used as a noise shaping quantizer, to operate as the last integrator in the chain of integrators in a Continuous-Time Delta Sigma Modulator (CT-DSM). In this manner, the preceding integrators would be implemented in the traditional analog manner, using op-amp or gm-C based structures. So, in these approaches the challenge of designing traditional analog blocks would still remain.

This manuscript also contributes on this border and presents the design of – and measurements on – a linear 'mostly digital' VCO-ADC with 3rd

order quantization noise shaping. The idea of a high order VCO-ADC is first introduced on a system level, then a circuit level solution is proposed that can achieve high orders of quantization noise shaping using only VCO-based integrators and other digital blocks.

#### 1.1 Dissertation organization

This dissertation is organized as follows:

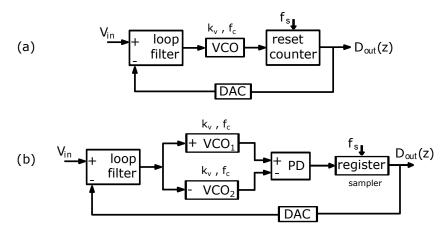

Chapter 2 will examine some of the previous works in the field of VCO based ADC design. The key target is to implement a CT-DSM using VCO based integrators and avoid using traditional op-amp based loop filters as much as possible. System level solutions to improve the linearity and increase the order of quantization noise shaping will be discussed.

Chapter 3 introduces the system level concepts that are at the basis of our high-order noise shaping VCO-ADC. In this chapter it is shown that the combination of a VCO and a digital block called "up-down counter" can be used as an integrator in the loop of a CT-DSM and can eventually lead to a high order CT-DSM with only VCO-based integrators. In the following chapters we will propose circuit level implementations for this modulator.

The linearity of a VCO-based CT-DSM is limited by that of its first VCO. In chapter 4 a linear voltage controlled ring oscillator structure is proposed. This circuit level solution is further verified through measurement results. Later on in chapter 6 this circuit will be used as the first VCO of a high order all-VCO CT-DSM.

In Chapter 5 PWM pre-coding technique for linearizing the first VCO is examined. An ADSM structure is chosen to create PWM pulse signals. A full study is done on the behavioral model of an ADSM to predict its linearity and carrier frequency. The effect of loop delay is also analyzed separately. Eventually, a circuit level implementation of an ADSM is proposed. The effectiveness of the proposed circuit in linearizing a VCO is then verified by examining the measurement results of a ADSM-VCO combination.

Chapter 6 showcases the first prototype of a 3rd order modulator of this type (VCO-based CT-DSM). This chip uses the linear VCO introduced in chapter 4. Many circuit level innovations are introduced to make this design possible. The resulting ADC is measured to have a competitive noise and linearity performance, while being operational under a low supply voltage.

The core of the chip occupies many times less silicon area than its conventional CT-DSM counterparts. The measurement results are compared with some of the more relevant prior works.

In chapter 7 a second implementation of a 3rd order VCO-based CT-DSM is presented. In order to have a linear ADC, this design uses the ADSM-VCO combination introduced in chapter 5. The resulting modulator is then compared to the design proposed in chapter 6. It is, afterwards, discussed why the chip with ADSM linearization technique is inferior to the chip in chapter 6 in almost every aspect.

Chapter 8 concludes the dissertation and discusses future directions for this research.

### Chapter 2

### Previous work on VCO-ADC

In this chapter first we will provide some basic background knowledge about Nyquist Rate and Over-Sampling Analog to Digital Converters. Then we will give the motivations for designing Discrete Time or Continuous Time Delta Sigma Modulators (CT-DSM). Afterwards we will examine some of the previous works in the field of VCO based ADC design.

The key target is to implement a CT-DSM using VCO based integrators and avoid using traditional op-amp based loop filters as much as possible. System level solutions to improve the linearity and increase the order of quantization noise shaping will be discussed. Continuous-Time integrators and a quantizer are the main ingredients for developing such a modulator. The idea is to replace these with their VCO based equivalents.

#### 2.1 Basics of Analog to Digital Conversion

An analog to digital converter, which is fundamentally a mixed-signal block, converts a continuous-time (CT) analog voltage to a discrete-time discrete-amplitude digital stream, or in other words "digitizes" it. So this digitization is applied to the both aspects of the input signal, its amplitude and its time. Digitization in the time domain is commonly known as sampling, and digitization in the voltage domain is known as quantizing.

The performance of such a conversion is limited by its sampling speed and quantization accuracy. Sampling puts a limit on the signal bandwidth and quantization adds noise. In this section we will discuss the two major ADC families. In the first group the quantization noise has a white (flat) spectrum, like Nyquist-rate ADCs, and in the second family the quantization noise is "shaped" such that its effect is minimized in the frequency range that is of our interest, like Delta Sigma Modulators.

#### 2.1.1 Nyquist rate ADC

Figure 2.1: (a) A sampling quantizer as a Nyquist rate ADC,

- (b) separating the sampling and quantizing functions, and

- (c) adding anti-aliasing low pass filter.

A sampling quantizer, shown in Fig. 2.1(a), is the simplest implementation of an ADC. Here  $V_{in}$  is the continuous-time (CT) input voltage, CLK represent the clock signal with a frequency of  $f_s$ , and  $D_{out}$  is the digital output stream, which is both discrete-time (DT) and quantized in value.

The two functions of sampling and quantizing can be performed separately while one functionality follows the other. In this manner the system shown in Fig. 2.1(b) is strictly equivalent to the one in Fig. 2.1(a). The input voltage is sampled at the constant rate of  $f_s$ , resulting in the DT signal of  $Y_s$ . If the input bandwidth is limited and the sampling rate is high enough there will be no loss of information. The maximum bandwidth that the input signal can have to ensure a lossless transformation is  $f_s/2$ . In other words, the sampling frequency should be at least twice the input

bandwidth,  $f_s = 2 * f_B$ . This is commonly known as the Nyquist rate.

With a good approximation, the quantizer can be modeled as a linear gain, G, with an additive white noise with a variance of  $G^2\sigma^2/12$ , where  $\sigma$  is the quantization step in the input. In this manner, the Dynamic Range (DR) of the ADC can be calculated.

DR is defined as the ratio of the full-scale input power to the input power at which the signal-to-noise ratio (SNR) is one. SNR is defined as the ratio of the signal power to the noise power at the output. If the ADC doesn't introduce any distortion for larger signals the DR would normally be equal to the SNR for the full-scale input. For this ADC for an input sine wave  $A_x \sin(\omega_{in}t)$  we have:

$$\frac{\text{signal power}}{\text{noise power}} = \frac{G^2 A_x^2 / 2}{G^2 \sigma^2 / 12}$$

(2.1)

The accuracy of a quantizer is often reported in its number of bits, nbit, instead of its step size,  $\sigma$ . They can be interchanged like this:

$$\sigma = \frac{2 * A_x\{max\}}{2^{nbit} - 1} \tag{2.2}$$

So the dynamic range of this ADC will be:

$$DR = \frac{3}{2}(2^{nbit} - 1)^2 \tag{2.3}$$

The SNR that only includes the quantization noise is often referred to as signal-to-quantization-noise ratio (SQNR). These values are normally reported in dB scale. For this ADC we can have:

$$DR = SQNR_{max}[dB] = 6.02nbit + 1.76$$

(2.4)

#### 2.1.2 Over-sampling ADC

One of the known problems associated with sampling a CT signal (and converting it to a DT signal) is aliasing. For example, if an out of band blocker with an arbitrary frequency of  $f_s + f_x$  is present in the signal  $V_{in}$  in Fig. 2.1(b), after sampling the aliasing effect will move this unwanted signal to the frequency of  $f_s - f_x$ . This aliased blocker could therefore fall into the band of interest and degrade the performance of the ADC. To avoid this an anti-aliasing low pass filter should precede the sampler, as shown in Fig. 2.1(c). Since we want to maximally benefit from the bandwidth

that the sampling quantizer (or the Nyquist rate ADC) can provide, the anti-aliasing filter should have a very sharp slope, which can be a serious design challenge.

This problem can be overcome by increasing the sampling frequency of the sampling quantizer to relax the design specifications on the slope of the anti-aliasing filter. Besides, since the quantization noise has a white spectrum a smaller portion of it will fall into the desired bandwidth. In other words, by increasing the sampling ratio by a factor two the quantization noise power in the baseband would be decreased by the same factor and the SNR will improve by the same factor, or 3 dB. The ratio of the new clock frequency over the Nyquist rate, 2 \* fB, is known as the Over Sampling Ratio,  $OSR = f_s/(2 * f_B)$ . So, the DR for an over-sampling ADC will be obtained as:

$$DR = SQNR_{max}[dB] = 6.02nbit + 1.76 + 10\log_{10}OSR$$

(2.5)

#### 2.1.3 Discrete Time Delta Sigma Modulator

As mentioned earlier, the quantization noise doesn't come from the sampling function of the ADC but from its quantization function. So, in order to further benefit from the quantization noise reduction of over-sampling ADC one could pass the quantization noise through a high pass filter (a differentiator). This is known as quantization noise shaping. A common method for this is Delta Sigma modulation, shown in Fig. 2.2(a).

Here the loop filter is a discrete-time low pass filter, typically implemented using opamps and switch-cap structure. Let's assume a simple case where the loop filter is a first order integrator,  $H(z) = \frac{z^{-1}}{1-z^{-1}}$ . The quantizer can be modeled as a linear gain, G, and an additive quantization noise, Q(z). For simplicity let's assume a gain of 1 both for the quantizer and the DAC. In this way the output,  $D_{out}(z)$  is a function of two inputs, V(z) which is the sampled version of the input, and Q(z). Using superposition we can write:

$$D_{out}(z) = STF(z).V(z) + NTF(z).Q(z)$$

(2.6)

STF (signal transfer function) is the TF from the input to the output of the modulator and NTF (noise transfer function) is the TF from added quantization noise to the output. For the system shown in Fig. 2.2(a), assuming H(z) is a first order integrator, we can simply calculate:

Figure 2.2: (a) System level structure of a typical DT-DSM, without additional feed-forward or local feedback paths, and (b) a DT-DSM with a more general loop filter.

$$STF(z) = \frac{D_{out}(z)}{V(z)} = \frac{H(z)}{1 + H(z)} = z^{-1}$$

(2.7)

This means that the input signal appears unchanged at the output with a delay of one clock cycle. As for the NTF we have:

$$NTF(z) = \frac{D_{out}(z)}{Q(z)} = \frac{1}{1 + H(z)} = 1 - z^{-1}$$

(2.8)

This shows that the quantization noise is shaped by a first order high pass transfer function. The DR of this system is:

$$DR = SQNR_{max}[dB] = 6.02nbit + 1.76 + 30\log_{10}OSR - 10\log_{10}\frac{\pi^2}{3}$$

(2.9)

Compared with eq. 2.5, we can see that here increasing the OSR can improve the DR three times faster.

A general structure of DT-DSM is shown in Fig. 2.2(b). Once again the output can be written as a linear function of its two inputs, like eq. 2.6. For this case we can calculate:

$$STF(z) = \frac{D_{out}(z)}{V(z)} = \frac{L_0(z)}{1 - L_1(z)}$$

(2.10)

and,

$$NTF(z) = \frac{D_{out}(z)}{Q(z)} = \frac{1}{1 - L_1(z)}$$

(2.11)

By properly designing  $L_0(z)$  and  $L_1(z)$  a higher order NTF can be realized while keeping STF just a few delays. A simple example of a high pass NTF of L order is:

$$NTF(z) = (1 - z^{-1})^{L} (2.12)$$

For this case the DR will be:

$$DR = 6.02nbit + 1.76 + 10(2L+1)\log_{10}OSR - 10\log_{10}\frac{\pi^{2L}}{2L+1}$$

(2.13)

Thus, the DR improves with a rate of 2L+1 as the OSR increases, which is a great improvement over simple oversampling. As a result, the number bits required to achieve a given DR is considerably less in a DT-DSM than in a Nyquist rate ADC.

#### 2.1.4 Continuous Time Delta Sigma Modulator

$\Delta\Sigma$  ADCs, or DSMs, are divided into two different categories based on the location of the sampler. In a discrete-time DSM (DT-DSM), as shown in Fig. 2.2, the sampler is located at the input stage and switched cap filters are normally used to precess the discrete time signals. In a continuous time DSM (CT-DSM), as shown in Fig. 2.3, the sampling function happens just before the quantization, and the two functions can be merged to a single block.

The quantization noise shaping characteristic of a CT-DSM is very similar to that of a DT-DSM and its order is equal to the number of integrators in its loop filter. Fig. 2.3(b) shows a typical structure of a CT-DSM with an order of k without additional feed-forward or local feedback paths, [33].

It has been argued in the literature that a CT-DSM can operate at a higher clock frequency compared to a DT-DSM, because the latter is limited by the speed of the switches and charging time of the capacitors.

Figure 2.3: (a) System level structure of a typical CT-DSM, without additional feed-forward or local feedback paths, and (b) a CT-DSM of the kth order.

More importantly, in a CT-DSM the sampler is located after the loop filter. As a result, this filter also operates as an anti-aliasing filter, which can save some power and chip area.

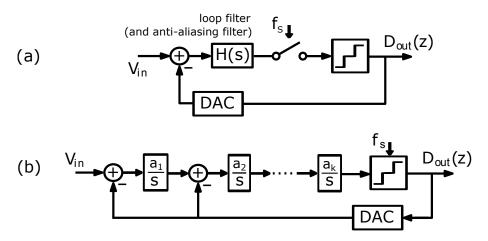

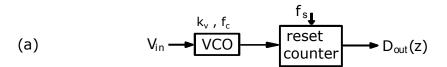

#### 2.2 First order VCO-ADC

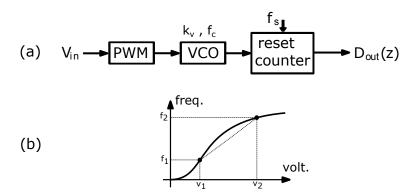

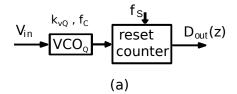

The combination of a VCO and a reset counter, shown in Fig. 2.4(a) is often used as either a stand-alone ADC with first order quantization noise shaping or as a noise shaping quantizer in the loop of a high order CT-DSM [20, 24, 25, 29, 30, 34–40].

The VCO converts the input voltage,  $V_{in}$ , to a square wave of which the frequency is proportional to the input voltage. Then the reset counter counts the number of rising edges of the square wave in every clock cycle. This way, it quantizes the phase which is the integral of the frequency. The reset function compensates this integration with an inherent differentiation. Apart from the quantization error, the resulting digital output signal  $D_{out}$  will be equal to:

$$D_{out} \approx \frac{f_{vco}}{f_s} = \frac{f_c + k_v V_{in}}{f_s} \tag{2.14}$$

where  $f_{VCO}$  stands for the VCO output frequency,  $f_c$  for the free run-

Figure 2.4: (a) an open-loop first order VCO based ADC, and (b) and (c) its equivalent model.

ning (zero input) frequency of the VCO,  $k_v$  for the gain of the VCO and  $f_s$  for the sampling frequency.

In a previous work [20] a thorough study of first order VCO-based ADC's has been done and different parameters of the modulator, such as SQNR or DR have been obtained as functions of the VCO and sampler parameters, such as the VCO's gain  $(k_v)$ , OSR, input amplitude  $(A_x)$  number of phases  $(n_p)$ , and sampling frequency  $(f_s)$ .

$$SQNR = 6.02nq - 3.41 + 30\log_{10}OSR + 20\log_{10}(\operatorname{sinc}(\frac{1}{2OSR}))$$

(2.15)

where  $nbit = \log_2(2A_xk_vn_p/f_s)$  is the resolution of the quantizer.

As expected, the SQNR of a VCO ADC is similar to that of first order DSM in terms of quantization noise shaping and dependency on OSR (referring to the term  $30\log_{10}OSR$  in the equation above.)

An equivalent system is depicted in Fig. 2.4(b), [29]. In this model the quantization, sampling, and differentiation functions (which previously happened simultaneously in the reset counter) are separated. The conversion from frequency to phase domain is modeled as an integrator. The

quantizer represents the fact that we don't have full access to the output phase of the VCO, but only to its cycles. In other words, only a full cycle can be counted. After sampling, the output is differentiated in the digital domain.

Although this VCO-ADC is an open loop structure, in Chapter 3 it will be shown that it is strictly equivalent to a first order closed loop CT-DSM, similar to the one shown in Fig. 2.4.

What makes a VCO based integrator interesting is the fact that the output phase of the VCO is by definition the integrated frequency, and in that regard a VCO is an ideal integrator with an infinite gain at DC, a luxury that is impossible to obtain in a conventional op-amp based integrator.

#### 2.2.1 Circuit level considerations

One of the main ideas behind a VCO-ADC, shown in Fig. 2.4, is to have a simple design that can ideally be synthesizable using digital flow design tools. Such a circuit would be relatively easy to migrate from one technology node to another. For this reason, it is of interest to look for circuit level solutions that are as "digital" as possible.

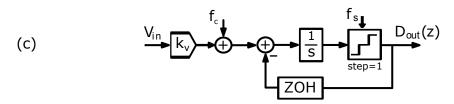

Figure 2.5: (a) a typical structure for a voltage controlled Ring Oscillator (b) a voltage controlled inverting delay stage, used in an RO.

Given this motivation, a Ring Oscillator (RO) is often used to manifest the VCO. An example of a typical RO is shown Fig. 2.5(a). An RO is an unstable loop of inverters, or delay stages. Such delay elements can be designed with a minimal number of transistors, which makes them a suitable option for low voltage applications. Another benefit of an RO is the fact that it has multiple output phases that can be processed in parallel using digital blocks.

It is commonly known that RO's have a relatively linear current to frequency conversion curve, so the main challenge would be to develop a linear transconductance stage to convert the input voltage into current to drive the RO. Many implementations for such a block already exists, a simple solution for this is shown in Fig. 2.5(b) as an example [18]. As the figure shows, the input voltage Vin+, and its complementary counterpart Vin-drive two trans-conducting transistors. This complementary structure, that uses a trans-conducting NMOS and PMOS at the same time, is chosen to minimize the even order harmonics that exists in the non-linear voltage to current conversion curve of a CMOS transistor.

In the VCO-ADC shown in Fig. 2.4(a) the RO is then followed by a reset counter, and since the different phases of the RO can be processed in parallel, each phase will be driving a separate, and rather simple, reset counter. The outputs of these counters will then be added in a digital adder that follows them.

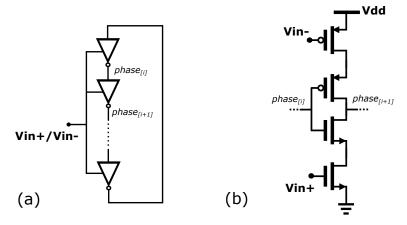

Fig. 2.6(a) shows a typical implementation for a single-phase reset counter [18], where VCO[i] is one of the output phases of the voltage controlled RO, and  $f_s$  is the sampling clock frequency. This particular circuit is triggered by both rising and falling edges of the VCO. The timing diagram of this reset counter is shown in Fig. 2.6(b).

An important parameter that the designer should take into account is the fact that the output phases of the RO are not rail-to-rail signals. Therefore, a level shifter can be used for the conversion. In some implementations, the first DFF in Fig. 2.6(a) is replaced with a SAFF (sense-amplifier-based flip-flop) to overcome this problem.

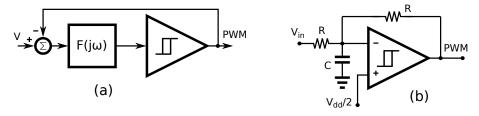

# 2.3 PWM pre-coding

One of the main issues of the system shown in Fig. 2.4(a) is the fact that the linearity of the overall ADC is limited by that of the VCO, which typically has a poor linearity performance in its voltage to frequency curve.

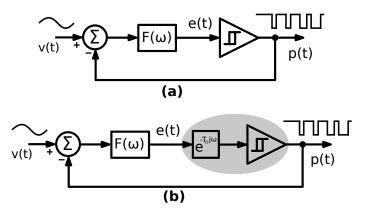

One of the system level solutions to overcome this issue is to put a Pulse-Width Modulator (PWM) before the VCO on the signal path, Fig. 2.7(a). The PWM will convert the input voltage to a two level signal,  $v_1$  and  $v_2$ , which will eventually drive the VCO, corresponding to only two instan-

Figure 2.6: (a) a common implementation for a single phase reset-counter, (b) its timing diagram

taneous frequency values, Fig. 2.7(b). In this manner the non-linearity curve of the VCO wouldn't matter anymore, because that dotted line, connecting the two operating points, would be the new voltage to frequency curve, which is always inherently linear. This technique is known as PWM pre-coding [29–31, 41, 42].

The PWM has a gain of one for the baseband signal and is used in series on the signal path, that's why it will always directly contribute to the noise and power budget of the system.

The designer should also take the aliasing effects of the PWM into account. A PWM signal has high frequency spurs around its carrier, and its harmonics, that can alias into baseband. It is normally expected that the anti-aliasing characteristics of a CT-DSM can alleviate this problem, but it is possible that a first order VCO-ADC, which is equivalent with a first order CT-DSM, cannot suppress these spurious tones (spurs) enough for a given SNR requirement.

Figure 2.7: (a) the system level representation of the PWM pre-coding technique for VCO-ADC linearization.

(b) the effect of PWM pre-coding technique on the non-linearity curve of a VCO.

Also worth noticing is the fact that the VCO is, in this configuration, basically operating as mixer. The average frequency of the VCO and high frequency spurs of the PWM can mix, inter-modulate, and eventually get down converted into baseband. These effects will further be discussed in Chapters 5 and 7.

#### 2.4 Coarse-fine structure

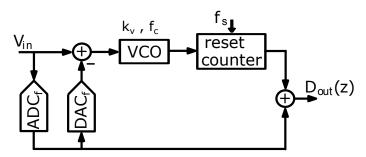

Another method to improve the linearity of a VCO-ADC is to reduce its input swing. By simply reducing the input voltage swing, applied directly to the VCO in Fig. 2.4(a), one can improve the linearity of the overall ADC. But it is obvious that this will be at the cost of SNR (Signal to Noise Ration) and DR (Dynamic Range) loss.

Coarse-fine structure, shown in Fig. 2.8, is a system level solution to reduce the swing of the VCO in a VCO-ADC. In this modulator the input voltage is first applied to a high speed coarse ADC with low accuracy, typically a flash ADC, annotated as  $ADC_f$  on the figure. The output of  $ADC_f$  is then subtracted from the input using a DAC (Digital to Analog Converter). The resulting quantization error signal is much smaller than  $V_{in}$  and as a result the non-linearity of the VCO would be much less significant.

The output of  $ADC_f$  will then be added as MSB (Most Significant Bits) to the digital output of the reset counter, representing the LSB (Least

Figure 2.8: System level representation of a Coarse-fine VCO-ADC structure, also know as 0-1 MASH VCO-ADC or residue canceling VCO-ADC.

Significant Bits). The overall ADC has no loss of DR due to swing reduction and will have a first order quantization noise shaping.

One of the drawbacks of this structure is the fact that it heavily depends on the DAC gain accuracy. Any mismatch between the DAC and the feed-forward path will increase the swing on the VCO and will degrade the linearity performance of the ADC. One way to improve this problem is to use this ADC as a noise shaping quantizer in a closed-loop high-order CT-DSM. This way the remaining non-linearity of this ADC will be suppressed by the preceding integrators in the loop of the CT-DSM.

Another downside of this scheme is the fact that the power consumption of the overall ADC would typically be doubled, compared to a conventional VCO-ADC with similar DR (Dynamic Range).

Also worth mentioning is the lack of anti-aliasing filtering which inherently exists in a conventional VCO-ADC. In a coarse-fine structure the flash ADC would require an analog low-pass filtering before it to avoid aliasing problems.

This technique is often referred to in the literature as '0-1 MASH VCO-ADC' or residue canceling VCO-ADC, [22, 43–45].

# 2.5 Voltage-to-phase VCO-based ADC

As explained in the previous section, a VCO is a perfect frequency to phase integrator. In order to extract the phase information of the VCO, one could sample the phase, as it was the case in Fig. 2.4(a). In that approach the integration function of the VCO was compensated by differentiation in digital domain using a reset-counter. That method is often referred to as

'voltage-to-frequency VCO-based ADC' [46-48].

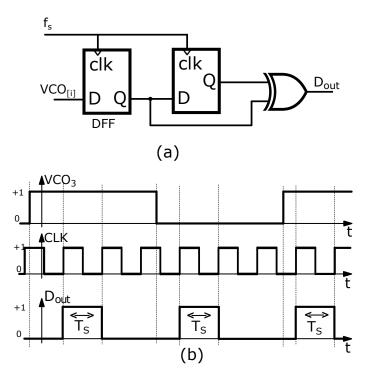

Figure 2.9: (a) a voltage-to-phase VCO based integrator,

- (b),(c) its system level equivalents,

- (d) a first order voltage-to-phase VCO based ADC.

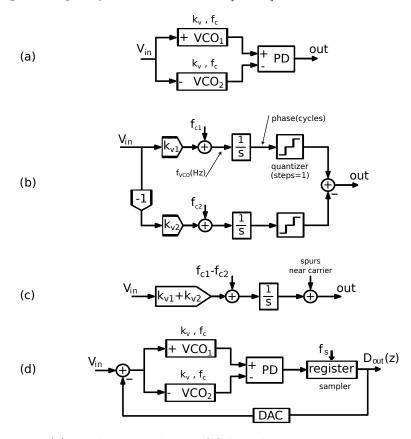

Another method for extracting the phase information of a VCO is using the VCO-based integrator shown in Fig. 2.9(a). In this pseudo differential method, the input signal is applied to two complementary VCO's and the difference between their output phases is detected using a Phase Detector (PD). The output of the PD, which is a pseudo digital Continuous-Time signal, is the integrated version of the input, plus some high frequency spurs around the carrier of the VCO,  $f_c$ . As a result, this structure can be used as a CT integrator in any loop filter, including CT-DSM applications.

A system level model of this integrator is shown in Fig. 2.9(b). Two different values are assumed for the gain and carrier frequency of the two

VCO's in order to address the potential issue of mismatch. the quantization function represents the fact that the PD only responds to the rising edges of the VCO output, or in other words, the phase information of the VCO is only available at the end of a full cycle.

As Fig. 2.9(c) shows, the mismatch between the gain of the two VCO's is not important and the overall gain of the integrator equals their summation. The mismatch between the carrier frequency of the two VCO's, on the other hand, translates as a DC offset to the input and will also appear as a DC offset at the output after putting the integrator in a closed loop. The high frequency spurs due to the quantization in the PD is also modeled in this figure.