Een klok-en-data-herstelcircuit en MAC-voorverwerkingseenheid aan meerdere snelheden met laag vermogen voor 40 Gbit/s gecascadeerde bit-verwevende passieve optische netwerken

A Low Power, Multi-Rate Clock-and-Data Recovery Circuit and MAC Preprocessor for 40 Gbit/s Cascaded Bit-Interleaving Passive Optical Networks

Arno Vyncke

Promotoren: prof. dr. ir. X. Yin, prof. dr. ir. G. Torfs Proefschrift ingediend tot het behalen van de graad van Doctor in de ingenieurswetenschappen: elektrotechniek

UNIVERSITEIT GENT Vakgroep Informatietechnologie Voorzitter: prof. dr. ir. D. De Zutter Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2016 - 2017

ISBN 978-90-8578-946-8 NUR 959 Wettelijk depot: D/2016/10.500/78

#### A Low Power, Multi-Rate Clock-and-Data Recovery Circuit and MAC Preprocessor for 40 Gbit/s Cascaded Bit-Interleaving Passive Optical Networks

Arno Vyncke Publicly defended on November 16, 2016

#### Members of the examination board

- prof. dr. ir. R. Van de Walle (Chairman)

- prof. dr. ir. J. Bauwelinck (Secretary)

- prof. dr. ir. X. Yin (Supervisor)

- prof. dr. ir. G. Torfs (Supervisor)

- prof. dr. ir. J. Doutreloigne

- dr. ir. B. Lannoo

- prof. dr. L. Wosinska

- INTEC, Ghent University, Belgium

- ELIS, Ghent University, Belgium

- University of Antwerp, Belgium

- KTH Royal Institute of Technology, Sweden

### Dankwoord

Het is zover. Na wat een eeuwigheid leek, ligt het boek er. Toen ik in 2010 begon bij de Design onderzoeksgroep was het schrijven van een doctoraatsthesis iets wat in de verre toekomst lag. Maar de jaren glijden voorbij, elk jaar gevuld met interessante projecten, uitdagingen en nieuwe plannen. Zoals men zegt, de tijd vliegt als je je amuseert. En het is door mij te amuseren dat ik vandaag, 6 jaar later, met enige trots terugblik op het werk dat ik de afgelopen jaren verricht heb. Hoewel dit boek enkel het werk rond CBi-PON belicht, was dit niet mijn enige project. Door de verschillende projecten waarin ik betrokken raakte, kon ik mij verdiepen in de wereld van de digitale electronica – zowel FPGAs als ASICs. Ten slotte kreeg ik de kans om mijn bijdrage te leveren door de CABINET ASIC te ontwerpen in het kader van GreenTouch en het Europese DISCUS project, waardoor er ook analoog ASIC ontwerp aan te pas kwam.

Ik begon aan mijn avontuur met drie vrienden, die er voor zorgden dat de voorbije 6 jaar aangenaam doorgebracht konden worden. Legendarische Glee-nights, het doen verschijnen van BBQs op plaatsen waar ze nodig – maar niet gewenst – waren. We begonnen samen aan een klein avontuur in 2010, vandaag zijn we samen bezig aan een veel groter avontuur: de Bi-FAST spin-off. Renato, Timothy, Ramses, bedankt voor de voorbije jaren, het huidige jaar, en de komende jaren. Met jullie aan mijn zijde weet ik dat mij niet zal vervelen en dat we onze dromen kunnen waarmaken.

Door de omgeving waarin we werken veranderen de collega's vrij snel, maar gelukkig zijn er een aantal vaste waarden. Johan en Scott, bedankt voor jullie steun in ons verhaal, de leiding van het labo en het zorgen voor steeds weer nieuwe, uitdagende projecten. Guy, bedankt om samen de uitdaging die de CABINET was tot een goed einde brengen en waar nodig steeds erop te wijzen dat alles eigenlijk al opgelost is, op die eenvoudige implementatiestap na. Jean, jij was er bij vanaf mijn eerste contact met het labo, tijdens ons fantastische VOP – waarvan ik nog steeds vind dat je je wil had moeten doordrijven – en bent doorheen de jaren toch ook net iets meer geworden dan zomaar een collega. Mike, bedankt om administratief alles in goede banen te leiden, ik ben blij dat ik het niet zelf moest doen. Ik wil ook onze vakgroepvoorzitter prof. De Zutter te bedanken voor de aangeboden faciliteiten en prof. Vandewege en prof. Qiu om het labo te brengen tot waar het vandaag staat.

Ik dien ook Christophe te bedanken, die mij met zijn engelengeduld in de wereld van de bit-interleaving PON introduceerde, en steeds klaarstond om zijn kennis en ervaring met mij te delen, zowel in het domein van de elektronica als daarbuiten. Jasmien, Jochen, Elber, Lucien en Elena, dank jullie voor de leuke jaren.

En dan zijn er nog de jonge, onbezonnen collega's, Bart, Koen, Wouter, Michaël, Marijn, Joris, Haolin, Gertjan, Manolo, Hubert, Hannes, Laurens, Michiel en José. Het is een plezier met jullie samen te werken en ik ben er van overtuigd dat jullie in de komende jaren voor nog veel mooie resultaten zullen zorgen.

Maar er is meer in het leven dan werk. Het zijn mijn vrienden die er voor zorgen dat ik de nodige rust vind in mijn hoofd wanneer nodig. Zij zijn het die vol interesse vragen waar ik mee bezig ben, er meestal weinig van snappen en dat ook helemaal niet erg vinden. Aan jullie allemaal: bedankt om een deel uit te maken van mijn leven.

Uiteraard wil ik ook mijn ouders, mama en papa, bedanken, die mij steeds alle kansen gegeven hebben om te doen waar ik interesse had en mij de brede, positieve kijk op het leven gegeven hebben waar ik dagelijks van geniet. Toendertijd misschien niet altijd met evenveel goesting, maar als ik er nu op terugblik ben ik blij al die ervaringen te mogen meegemaakt hebben. Ook mijn zus Elke verdient een woordje van bedanking, als grote zus heeft ze altijd goed voor mij gezorgd en dat probeert ze nog steeds wanneer nodig, met succes. Ook mijn schoonouders, Dirk en Hilde, verdienen hier de nodige erkenning. Jullie hebben mij de voorbije jaren opgenomen als jullie eigen zoon, en dat voelt goed. Er wordt beweerd dat schoonouders niet altijd een cadeau zijn, dus ik denk dat ik op dat vlak de hoofdvogel afgeschoten heb. Elise, die de voorbije jaren alles van zeer dichtbij mocht meemaken. De lange werkuren door de passie waarmee ik met elektronica bezig was. De nog langere uren dat ik niet thuis was, omdat ik toch vond dat ik daarnaast ook een robot moest bouwen. Of aan een 24-uurs-programmeerwedstrijd moest deelnemen. Of omdat ik nu toch echt een eigen bedrijf moest op touw proberen zetten. Ik ben enorm blij dat we elkaar gevonden hebben, en kan me geen betere levensgezel inbeelden. Bedankt om me mijn dromen te laten volgen, en me daar steeds in te steunen. Bedankt voor je luisterend oor, al begrijpt het misschien niet altijd wat ik zeg. Bedankt om jouw dag met mij te delen.

Gent, november 2016

Arno Vyncke

iv

"Sometimes I think the surest sign that intelligent life exists elsewhere in the universe is that none of it has tried to contact us." Calvin (Bill Watterson) v

## Table of Contents

| Da | ankwo  | oord     |                                                | i     |

|----|--------|----------|------------------------------------------------|-------|

| Ne | ederla | ndse sa  | menvatting                                     | xxiii |

| Er |        |          |                                                | xxvii |

| Li |        |          |                                                | xxxi  |

| 1  | Intr   | oductio  | n                                              | 1     |

|    | 1.1    | On the   | corigins of Internet                           | 2     |

|    |        | 1.1.1    | From ARPANET to the Internet - a brief history | 2     |

|    | 1.2    | A Trul   | y Inconvenient Truth                           | 7     |

|    |        | 1.2.1    | Ecological and Economical Impact               | 8     |

|    | 1.3    | Towar    | ds sustainable communication                   | 9     |

|    | 1.4    | Next-g   | generation networks                            | 10    |

|    |        | 1.4.1    | Advances in the access network                 | 10    |

|    |        |          | 1.4.1.1 Copper limitations                     | 11    |

|    |        |          | 1.4.1.2 All-optical access networks            | 12    |

|    |        | 1.4.2    | Passive Optical Networks                       | 14    |

|    |        | 1.4.3    | The metro-access convergence - Long-Reach PONs | 14    |

|    | 1.5    | Challe   | nges of next-generation networks               | 15    |

|    | 1.6    | Overv    | iew of the work                                | 17    |

|    | 1.7    | Organi   | ization of this dissertation                   | 18    |

| 2  | Bit-   | Interlea | wing PON                                       | 23    |

|    | 2.1    | The ne   | eed for BiPON                                  | 23    |

|    | 2.2    | An ove   | erview of PON protocols                        | 24    |

|    |        | 2.2.1    | Multiplexing schemes                           | 24    |

|    |        | 2.2.2    | PON Standards                                  | 26    |

|    |        | 2.2.3    | Next-generation PONs: NG-PON                   | 29    |

|    |        |          | 2.2.3.1 NG-PON1                                | 29    |

|     |         | 2.2.3.2 NG-PON2                                    |

|-----|---------|----------------------------------------------------|

|     | 2.2.4   | Power consumption in PONs                          |

|     |         | 2.2.4.1 Energy saving                              |

|     |         | 2.2.4.2 Future                                     |

|     | 2.2.5   | (X)G-PON power deficiency                          |

| 2.3 | Bit-int | erleaving PON                                      |

|     | 2.3.1   | Bit-based TDMA                                     |

|     | 2.3.2   | Dynamic Bandwidth Allocation                       |

|     | 2.3.3   | Upstream traffic                                   |

| 2.4 | Demor   | nstrated Results                                   |

|     | 2.4.1   | FPGA-based Implementation                          |

|     | 2.4.2   | ASIC Implementation                                |

| 2.5 | Conclu  | usion                                              |

| C   |         |                                                    |

|     |         | it-interleaving PON 43                             |

| 3.1 |         | Access convergence & Long-Reach PON 43             |

|     | 3.1.1   | Impact on the ONU   45     LD DON Complexity   45  |

| 2.2 | 3.1.2   | LR-PON Conclusion                                  |

| 3.2 | C       | BiPON to the next level                            |

|     | 3.2.1   | Power deficiency of BiPON                          |

|     | 3.2.2   | Lack of suitable optical components                |

| 2.2 | 3.2.3   | Leveraging the complexity of electronics 47        |

| 3.3 |         | Ied Bit-Interleaving PON: Concept    47            |

|     | 3.3.1   | CBi Network Topology                               |

|     | 3.3.2   | Downstream rates                                   |

|     | 3.3.3   | CBi Devices                                        |

|     |         | 3.3.3.1 CBi Interleaver                            |

|     |         | 3.3.3.2 CBi Repeater                               |

|     | 224     | 3.3.3.3 CBi End-ONT                                |

|     | 3.3.4   | CBi Frame Composition                              |

|     |         | 3.3.4.1 CBi Header: SYNC Field                     |

|     |         | 3.3.4.2 CBi Header: RNID Field                     |

|     |         | 3.3.4.3 CBi Header: BWMAP Field 56                 |

| 2.4 | Casa    | 3.3.4.4 Scrambling                                 |

| 3.4 |         | led Bit-Interleaving PON: 3-Level Instantiation 58 |

|     | 3.4.1   | 3-Level Cascaded Bit-interleaving PON 58           |

|     | 2.4.2   | 3.4.1.1 Rates                                      |

|     | 3.4.2   | CBi Frame Configuration                            |

|     | 3.4.3   | CBi Interleaver Implementation                     |

3

|   |      | 3.4.4<br>3.4.5 |             | T Application-Specific Integrated Circuit eater Implementation | 60<br>61 |

|---|------|----------------|-------------|----------------------------------------------------------------|----------|

|   |      | 3.4.6          | CBi End-    | ONT Implementation                                             | 61       |

|   | 3.5  | Conclu         | ision       |                                                                | 62       |

| 4 | Desi | gn of th       | e CABIN     | ET ASIC                                                        | 65       |

|   | 4.1  | System         | n Architect | ure                                                            | 65       |

|   |      | 4.1.1          | Inputs .    |                                                                | 66       |

|   |      | 4.1.2          | Outputs     |                                                                | 67       |

|   | 4.2  | Analog         | g Front End | d: Clock and Data Recovery                                     | 67       |

|   |      | 4.2.1          | Input But   | ffer                                                           | 69       |

|   |      | 4.2.2          | CDR Top     | oology                                                         | 69       |

|   |      |                | 4.2.2.1     | Line rate dependence                                           | 70       |

|   |      |                | 4.2.2.2     | Need for clock and data recovery                               | 70       |

|   |      |                | 4.2.2.3     | Need for deserialization                                       | 71       |

|   |      |                | 4.2.2.4     | CDR Topology Selection                                         | 71       |

|   |      |                | 4.2.2.5     | PLL-based CDR Operation                                        | 73       |

|   |      |                | 4.2.2.6     | A sub-sampling CDR                                             | 74       |

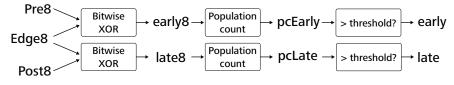

|   |      | 4.2.3          | Phase De    | tector                                                         | 75       |

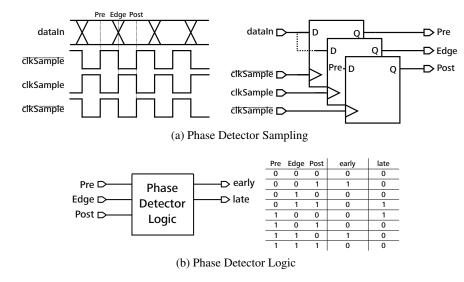

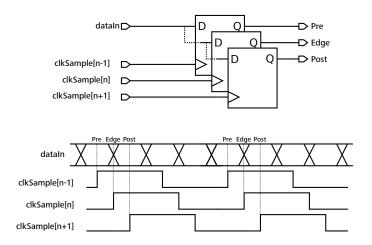

|   |      |                | 4.2.3.1     | Phase Detector Architecture                                    | 76       |

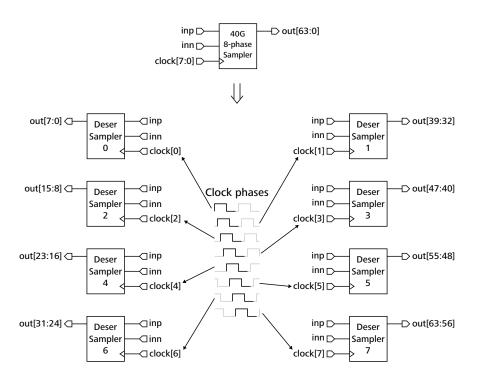

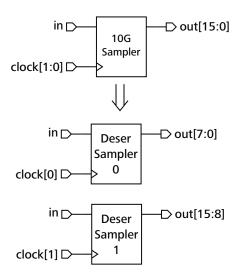

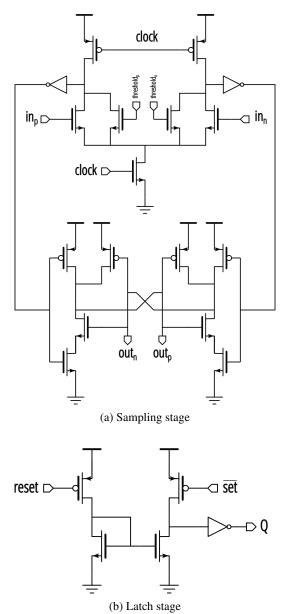

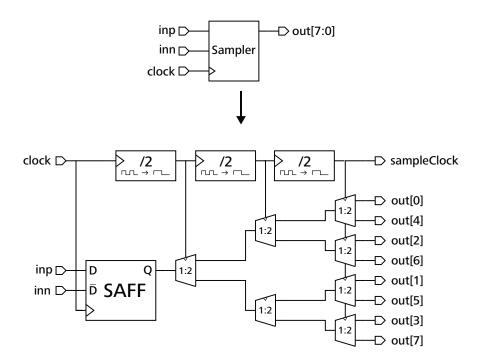

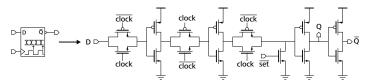

|   |      |                | 4.2.3.2     | Sampling Stage Implementation                                  | 78       |

|   |      |                | 4.2.3.3     | Phase Detector Logic Implementation .                          | 78       |

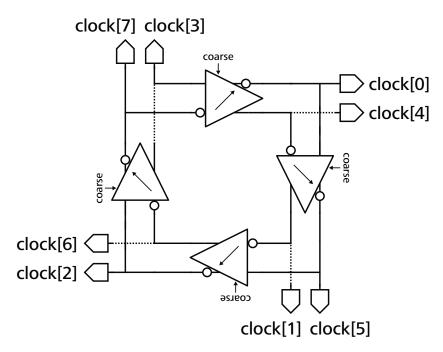

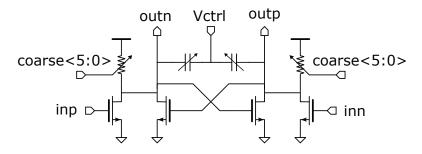

|   |      | 4.2.4          | Voltage C   | Controlled Oscillator                                          | 85       |

|   |      |                | 4.2.4.1     | Phase Noise                                                    | 85       |

|   |      |                | 4.2.4.2     | VCO Architecture                                               | 85       |

|   |      |                | 4.2.4.3     | 40 GHz Voltage-Controlled Oscillator                           | 86       |

|   |      |                | 4.2.4.4     | 10/2.5 GHz Voltage-Controlled Oscillator                       | 90       |

|   |      | 4.2.5          | Charge P    | ump and Loop Filter Sizing                                     | 93       |

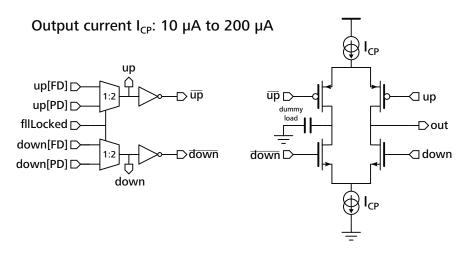

|   |      |                | 4.2.5.1     | Charge Pump implementation                                     | 99       |

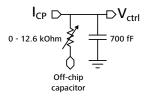

|   |      |                | 4.2.5.2     | Loop Filter implementation                                     | 100      |

|   |      | 4.2.6          | CDR Loc     | cking Behavior                                                 | 100      |

|   | 4.3  | MAC I          | Preprocess  | or                                                             | 103      |

|   |      | 4.3.1          |             | ization procedure                                              | 103      |

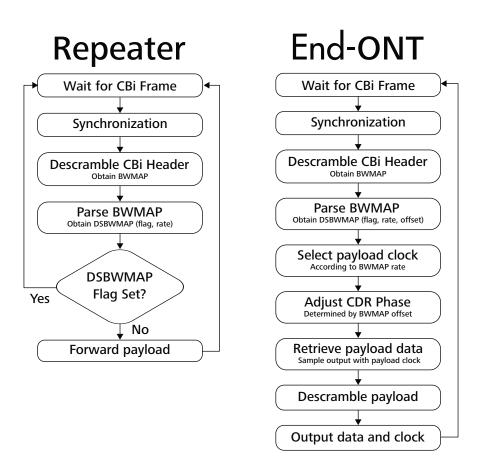

|   |      | 4.3.2          | Repeater    | Mode                                                           | 103      |

|   |      | 4.3.3          | End-ON7     | Г Mode                                                         | 106      |

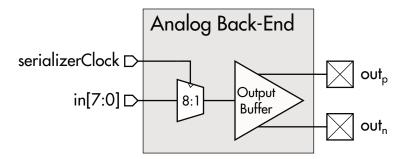

|   | 4.4  | Analog         |             | 1                                                              | 106      |

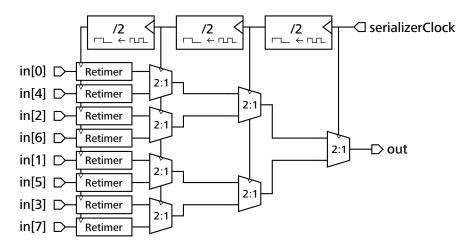

|   |      | 4.4.1          | 8:1 Serial  | lizer                                                          | 107      |

|   |      | 4.4.2          |             | uffer                                                          | 107      |

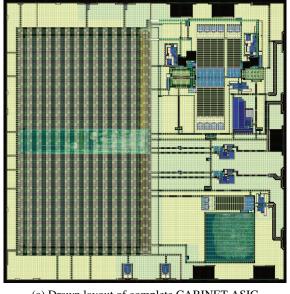

|   | 4.5  | CABIN          |             | Layout                                                         | 108      |

ix

|   | 4.6 | Conclusion                                             | 8  |

|---|-----|--------------------------------------------------------|----|

| 5 | Exp | perimental results 11                                  | 5  |

|   | 5.1 | Measurement setup                                      | 5  |

|   | 5.2 | Measurement strategy                                   | 6  |

|   | 5.3 | Building blocks verification                           | 7  |

|   |     | 5.3.1 Voltage-Controlled Oscillator                    | 7  |

|   |     | 5.3.1.1 Output serializer                              | 2  |

|   |     | 5.3.2 Frequency Locked Loop                            | 2  |

|   |     | 5.3.2.1 40 Gbit/s FLL                                  | 3  |

|   |     | 5.3.2.2 10 Gbit/s FLL                                  | 25 |

|   |     | 5.3.2.3 2.5 Gbit/s FLL                                 | 7  |

|   |     | 5.3.3 Samplers                                         | 9  |

|   |     | 5.3.4 Clock-and-Data Recovery                          | 0  |

|   |     | 5.3.4.1 Switching from FLL to PLL 13                   | 0  |

|   |     | 5.3.4.2 Supply voltage ripple                          | 2  |

|   |     | 5.3.4.3 CDR Conclusion                                 | 2  |

|   |     | 5.3.5 FLL-based Data Recovery                          | 3  |

|   | 5.4 | MAC preprocessor verification                          | 3  |

|   | 5.5 | Power consumption measurement                          | 6  |

|   | 5.6 | Power consumption reduction in the network 13          | 8  |

|   |     | 5.6.1 2010 baseline network (GreenTouch reference net- |    |

|   |     | work)                                                  | 8  |

|   |     | 5.6.2 2020 GreenTouch network                          | 9  |

|   |     | 5.6.3 Power consumption reduction                      | 0  |

|   |     | 5.6.3.1 ONU Power consumption 14                       | 0  |

|   |     | 5.6.3.2 Remote Node Power consumption 14               | -2 |

|   | 5.7 | Conclusion                                             | -2 |

| 6 | Con | nclusions and Future work 14                           | 7  |

|   | 6.1 | Summary of this work                                   | 7  |

|   | 6.2 | Next-generation networks outlook                       | 9  |

|   | 6.3 | Future work                                            | 9  |

# List of Figures

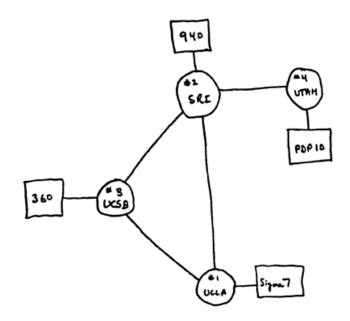

| 1.1  | First ARPANET with 4 nodes [1]                          | 3  |

|------|---------------------------------------------------------|----|

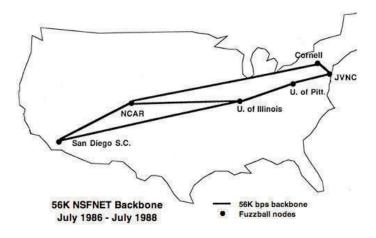

| 1.2  | Original NSFNet with 56 kbit/s backbone [2]             | 3  |

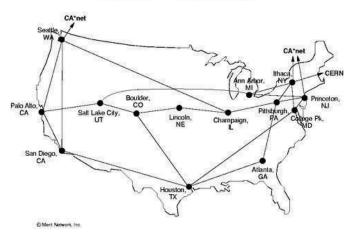

| 1.3  | Intermediary NSFNet with T1 backbone (1.5 Mbit/s) [3] . | 4  |

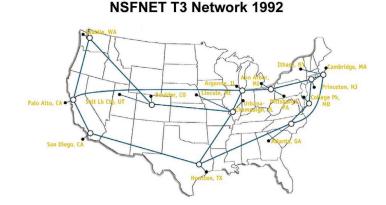

| 1.4  | Final NSFNet with T3 backbone (45 Mbit/s) [4]           | 5  |

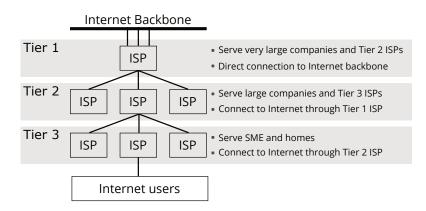

| 1.5  | Internet Service Provider Tiers                         | 6  |

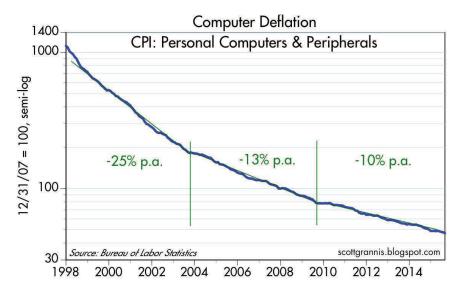

| 1.6  | Personal Computer Price Evolution (1998 - 2015) [5]     | 7  |

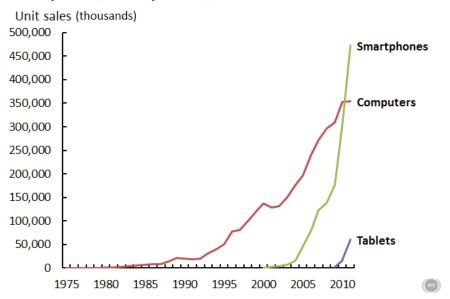

| 1.7  | Computers, smartphones and tablet sales evolution [6]   | 8  |

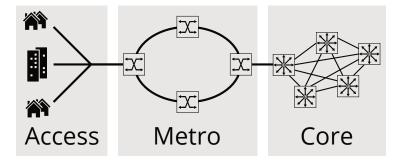

| 1.8  | Modern telecommunication network hierarchy              | 10 |

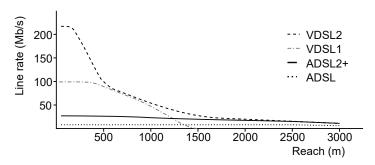

| 1.9  | Rate vs Reach for different xDSL Technologies [10]      | 11 |

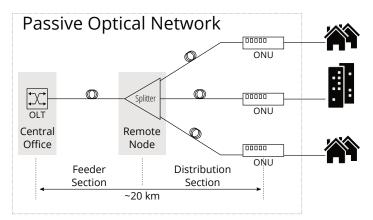

| 1.10 | Passive Optical Network                                 | 14 |

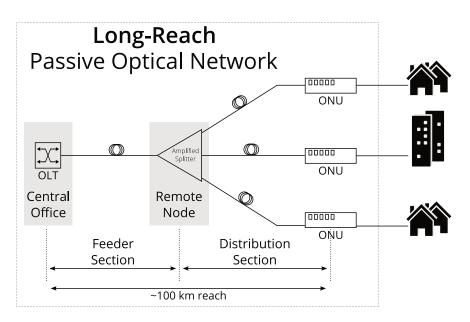

| 1.11 | Long-Reach Passive Optical Network                      | 15 |

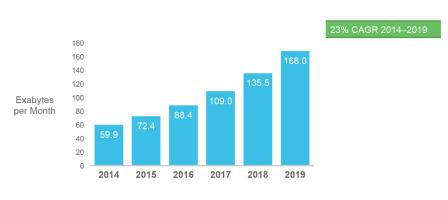

| 1.12 | IP Data traffic Forecast [14]                           | 16 |

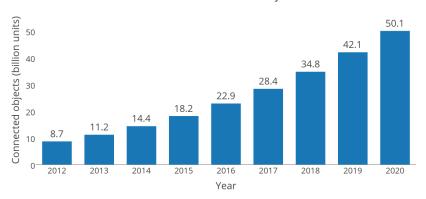

| 1.13 | Forecast of Internet-Connected Devices in 2013 [15]     | 16 |

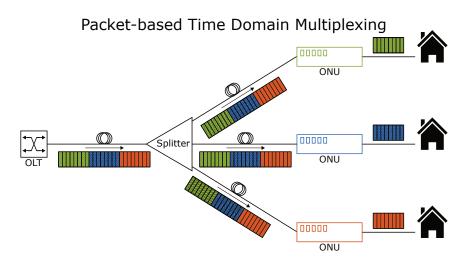

| 2.1  | Packet-based Time Domain Multiplexing                   | 25 |

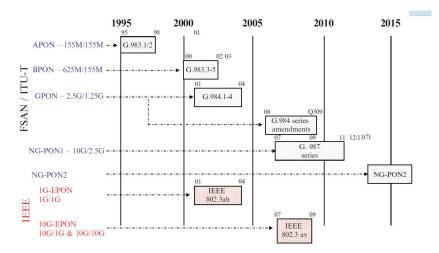

| 2.2  | PON Standardization Timeline [5]                        | 26 |

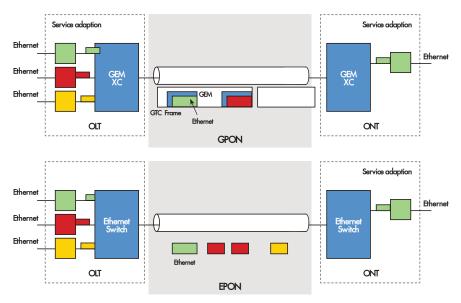

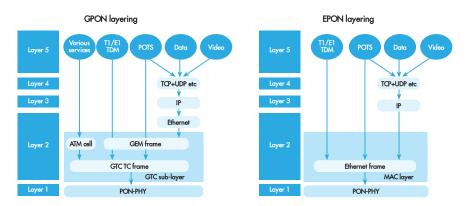

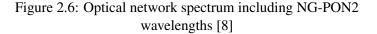

| 2.3  | Generic Framing Procedure (GFP) in GPON and EPON [6]    | 28 |

| 2.4  | GPON vs EPON Protocol [6]                               | 29 |

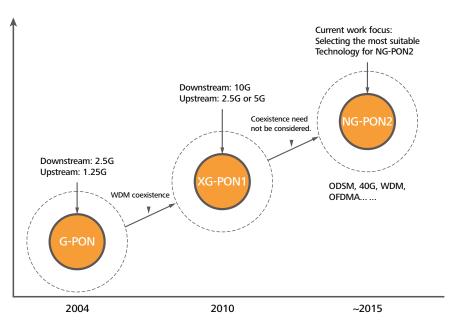

| 2.5  | FSAN Next-Generation PON Roadmap in 2010 [7]            | 30 |

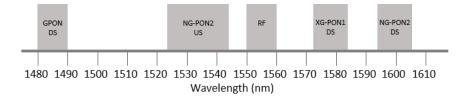

| 2.6  | Optical network spectrum including NG-PON2 wavelengths  |    |

|      | [8]                                                     | 31 |

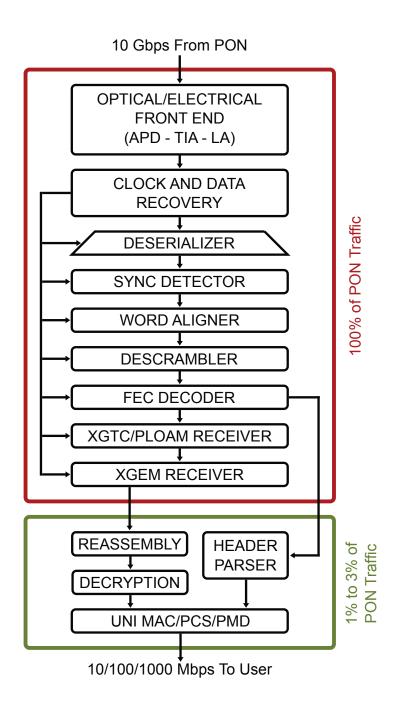

| 2.7  | XG-PON Processing                                       | 33 |

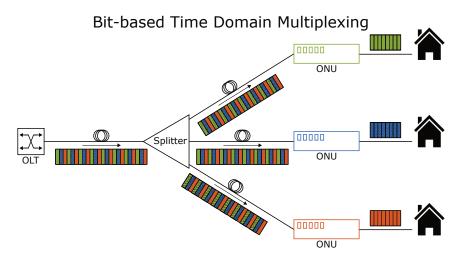

| 2.8  | Bit-based TDMA                                          | 34 |

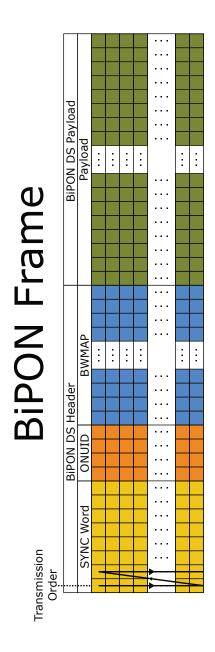

| 2.9  | BiPON Frame Structure                                   | 35 |

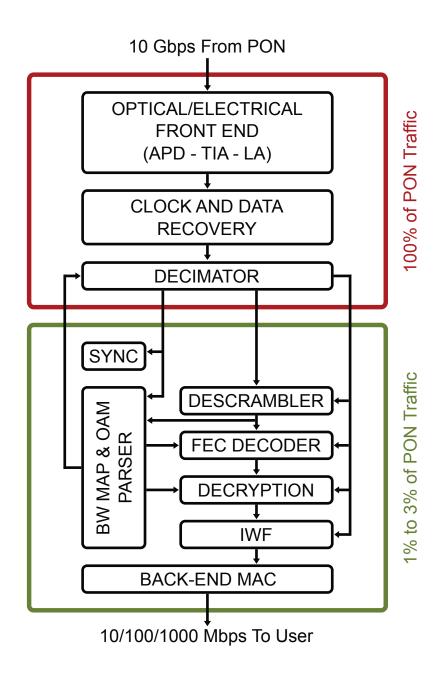

| 2.10 | BiPON Processing                                        | 37 |

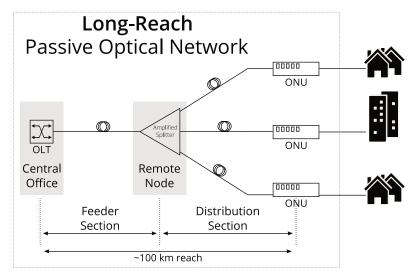

| 3.1  | Long-Reach PON                                          | 44 |

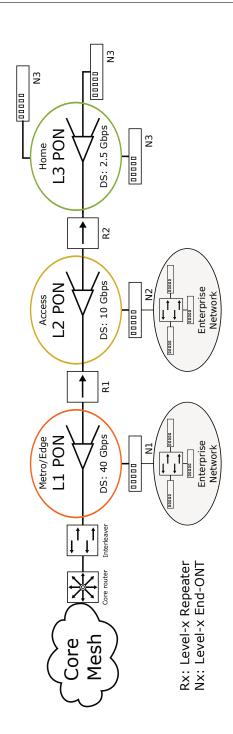

| 3.2  | Cascaded Bit-Interleaving PON Network Architecture      | 49 |

| 3.3  | CBi Devices Operation                                   | 50 |

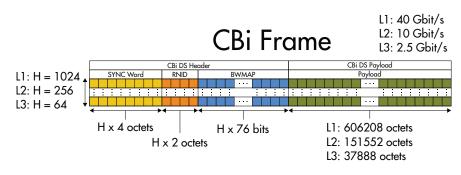

| 3.4  | CBi Frame Composition                                   | 53 |

| 3.5  | 3-Level Cascaded Bit-interleaving PON Instantiation     | 59 |

| 3.6  | CBi Frame Configuration                                              | 60  |

|------|----------------------------------------------------------------------|-----|

| 3.7  | CBi Interleaver Block Diagram                                        | 60  |

| 3.8  | CBi Repeater Implementation Block Diagram                            | 61  |

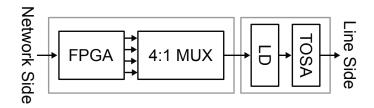

| 3.9  | CBi End-ONT Implementation Block Diagram                             | 61  |

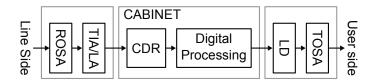

|      |                                                                      |     |

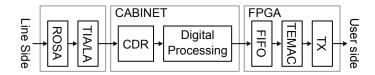

| 4.1  | CABINET System Architecture                                          | 66  |

| 4.2  | Analog Front-End                                                     | 68  |

| 4.3  | Input Buffer schematic                                               | 68  |

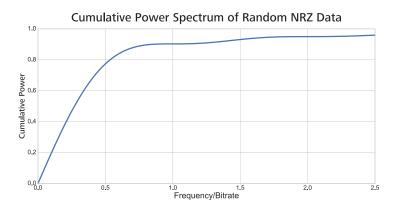

| 4.4  | Cumulative power spectrum of random NRZ data [1]                     | 69  |

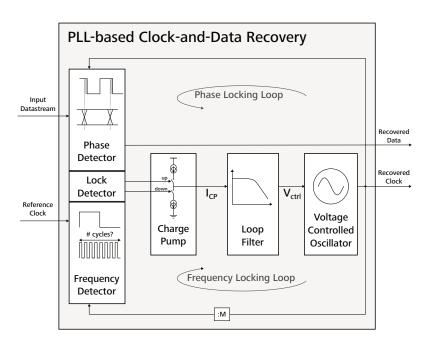

| 4.5  | Simplified block diagram of a PLL-based CDR using an                 |     |

|      | external reference clock                                             | 73  |

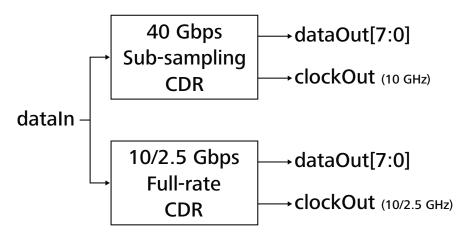

| 4.6  | CABINET Multi-rate CDR Configuration                                 | 75  |

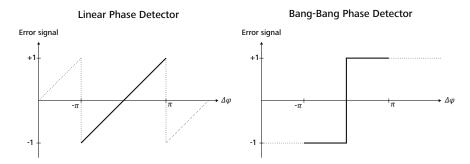

| 4.7  | Linear vs Bang-Bang Phase Detector                                   | 76  |

| 4.8  | Bang-Bang Phase Detector Operation                                   | 77  |

| 4.9  | 40 Gbit/s Sub-sampling BB-PD Operation                               | 78  |

| 4.10 | Samplers configuration for 40 Gbit/s CDR: 8 clock phases             | 79  |

| 4.11 | Samplers configuration for 10/2.5 Gbit/s CDR: 2 clock phases         | 79  |

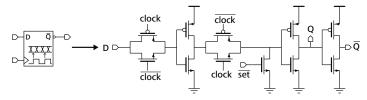

| 4.12 | Sense-Amplifier based Flip-Flop schematic                            | 80  |

| 4.13 | Sampler with 1:8 Deserializer                                        | 81  |

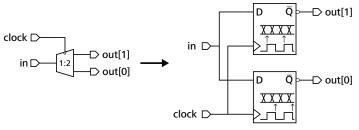

|      | 1:2 Deserializer                                                     | 82  |

|      | Reduction of <i>early8/late8</i> signals to <i>early/late</i> signal | 83  |

|      | 40 GHz Voltage-Controlled Oscillator                                 | 86  |

|      | 40 GHz VCO Delay Cell                                                | 87  |

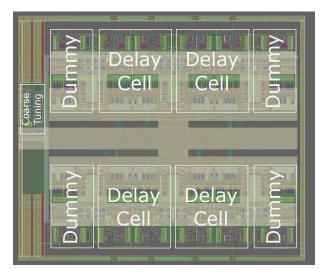

|      | 40 GHz VCO Delay Cell Physical Implementation                        | 88  |

|      | 40 GHz VCO Simulation                                                | 89  |

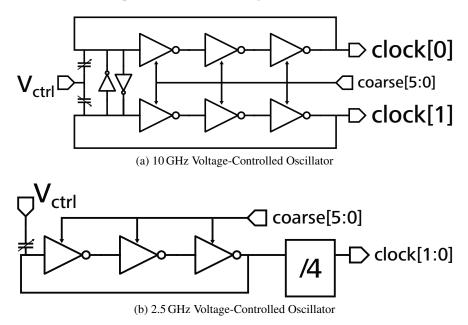

|      | 10/2.5 GHz Voltage-Controlled Oscillator                             | 90  |

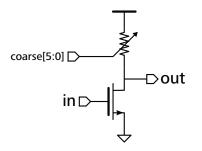

|      | 10 GHz VCO Delay Cell                                                | 91  |

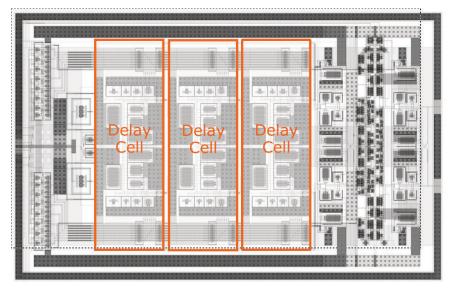

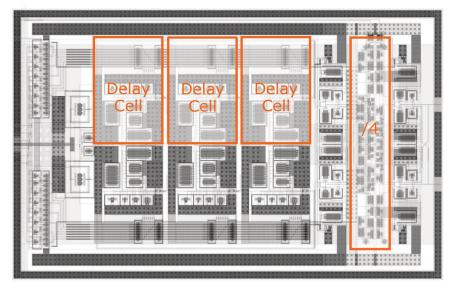

|      | Layout of 10/2.5 GHz VCO: same block in different con-               | / 1 |

|      | figurations                                                          | 92  |

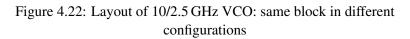

| 4 23 | 10 GHz VCO Simulation                                                | 94  |

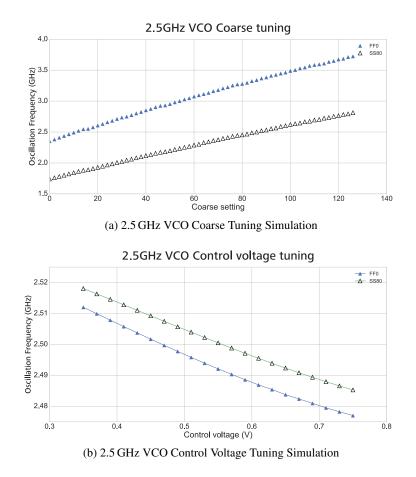

|      | 2.5 GHz VCO Simulation                                               | 95  |

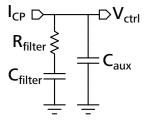

|      | Loop Filter Architecture                                             | 96  |

|      |                                                                      | 100 |

| 4.27 |                                                                      | 100 |

| 4.28 |                                                                      | 100 |

|      | •                                                                    | 101 |

|      |                                                                      | 102 |

|      | 1 5                                                                  | 104 |

| 4.31 |                                                                      |     |

|      | 6                                                                    | 106 |

| 4.33 | 8:1 Serializer                                                       | 107 |

| 4.34 | Complete CABINET ASIC: drawn layout versus manufac-    |     |

|------|--------------------------------------------------------|-----|

|      | tured ASIC                                             | 109 |

| 5.1  | CABINET Testboard                                      | 116 |

| 5.2  | CABINET Testboard connected to Testplatform            | 117 |

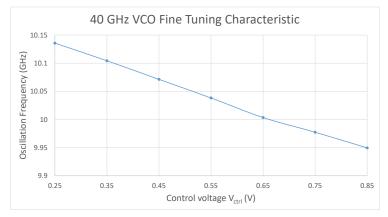

| 5.3  | 40 GHz VCO Measurement Results                         | 119 |

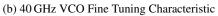

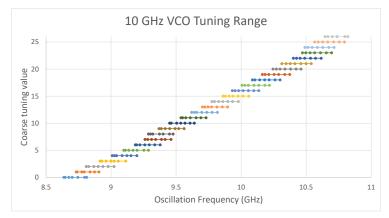

| 5.4  | 10 GHz VCO Measurement Results                         | 120 |

| 5.5  | 2.5 GHz VCO Measurement Results                        | 121 |

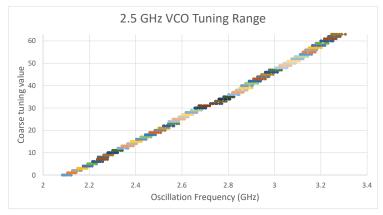

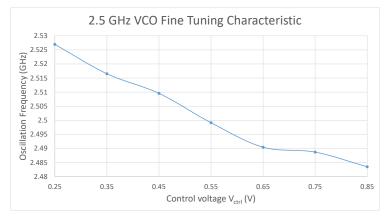

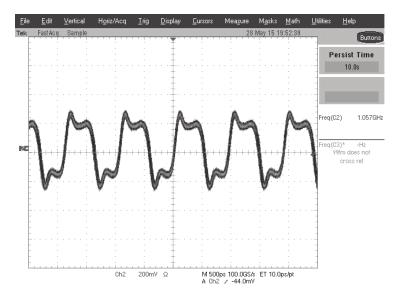

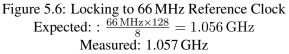

| 5.6  | 40 Gbit/s FLL Locking to 66 MHz Reference Clock        | 123 |

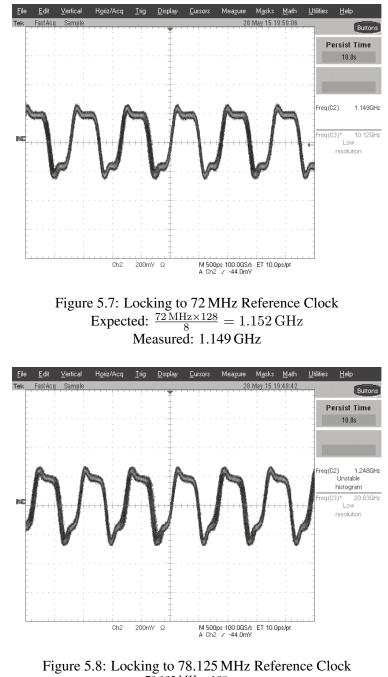

| 5.7  | 40 Gbit/s FLL Locking to 72 MHz Reference Clock        | 124 |

| 5.8  | 40 Gbit/s FLL Locking to 78.125 MHz Reference Clock    | 124 |

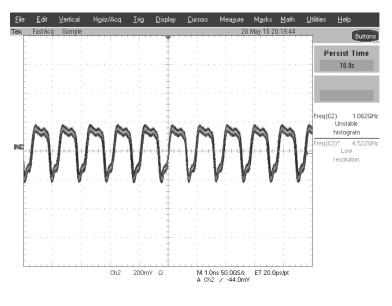

| 5.9  | 10 Gbit/s FLL Locking to 66 MHz Reference Clock        | 125 |

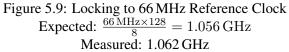

| 5.10 | 10 Gbit/s FLL Locking to 72 MHz Reference Clock        | 126 |

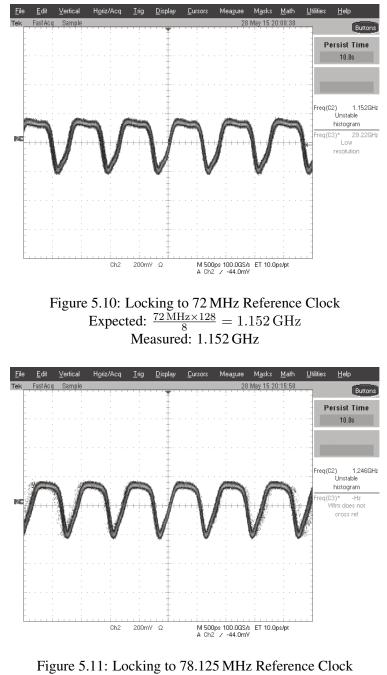

| 5.11 | 10 Gbit/s FLL Locking to 78.125 MHz Reference Clock    | 126 |

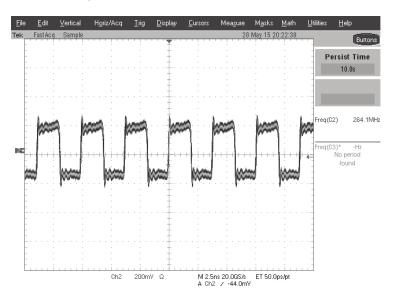

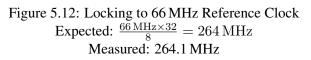

| 5.12 | 2.5 Gbit/s FLL Locking to 66 MHz Reference Clock       | 127 |

| 5.13 | 2.5 Gbit/s FLL Locking to 72 MHz Reference Clock       | 128 |

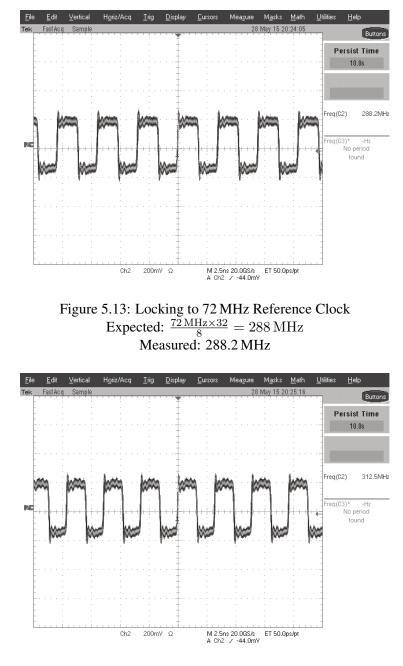

| 5.14 | 2.5 Gbit/s FLL Locking to 78.125 MHz Reference Clock . | 128 |

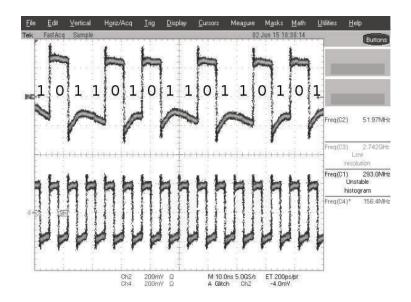

| 5.15 | 25 Gbit/s Sampler Measurement - Pattern 1              | 131 |

| 5.16 | 28 Gbit/s Sampler Measurement - Pattern 1              | 131 |

| 5.17 | 28 Gbit/s Sampler Measurement - Pattern 2              | 132 |

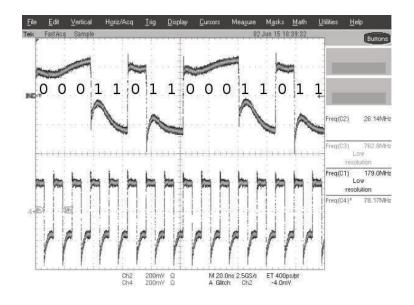

| 5.18 | 2.5 Gbit/s End-ONT Data Recovery: Frame length         | 134 |

| 5.19 | FLL-based 2.5 Gbit/s End-ONT Data Recovery RNID = 38   |     |

|      | Payload pattern: 0xA6 = 0b10100110                     | 135 |

| 5.20 | FLL-based 2.5 Gbit/s End-ONT Data Recovery RNID = 54   |     |

|      | Payload pattern: 0xB6 = 0b10110110                     | 135 |

| 5.21 | FLL-based 2.5 Gbit/s End-ONT Data Recovery RNID = 70   |     |

|      | Payload pattern: 0xC6 = 0b11000110                     | 136 |

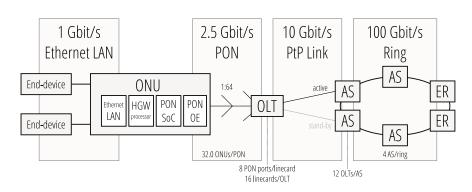

|      | 2010 baseline network (GreenTouch reference network)   | 138 |

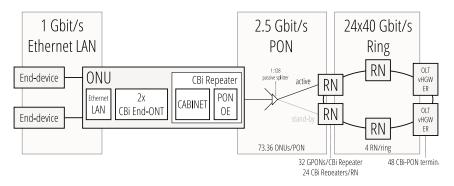

| 5.23 | 2020 GreenTouch network                                | 139 |

## List of Tables

| 1.1 | 2015-2020 Italian Network Forecast: Device Density and          |     |

|-----|-----------------------------------------------------------------|-----|

|     | Business-As-Usual (BAU) Energy Requirements [9]                 | 11  |

| 1.2 | Advantages of optical fiber [10]                                | 13  |

| 2.1 | PON Standards [3, 4]                                            | 27  |

| 2.2 | Estimated dynamic power consumption XG-PON vs BiPON on FPGA [9] | 39  |

| 2.3 | Estimated dynamic power consumption XG-PON vs BiPON on FPGA [9] | 39  |

| 3.1 | Downstream data rate relations in CBi PON                       | 50  |

| 3.2 | Line rate relations in CBi PON                                  | 55  |

| 3.3 | SYNC Words                                                      | 55  |

| 3.4 | RNID Encoding                                                   | 56  |

| 3.5 | BWMAP Flag Subfield                                             | 56  |

| 3.6 | DSBWMAP Downsampling Rates                                      | 57  |

| 3.7 | Rates in proposed CBi-PON                                       | 58  |

| 4.1 | Sampling clocks subset by Channel Selection                     | 77  |

| 4.2 | Phase Detector Reduction examples (threshold = $3$ )            | 83  |

| 4.3 | Phase Detector Data Selection (10/2.5 Gbit/s CDR)               | 84  |

| 4.4 | Phase Detector Data Selection (40 Gbit/s CDR)                   | 84  |

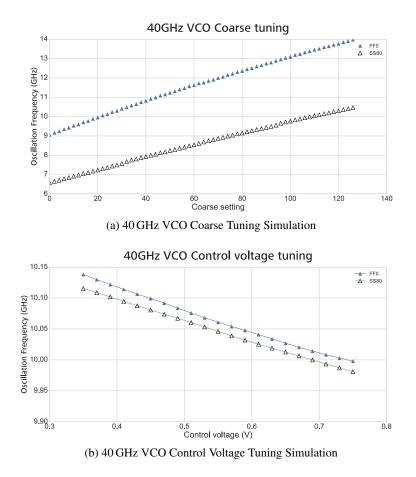

| 4.5 | Post-layout simulation performance of 40 GHz VCO                | 88  |

| 4.6 | Post-layout simulation performance of 10/2.5 GHz VCO .          | 93  |

| 4.7 | CDR Design component values                                     | 99  |

| 5.1 | VCO Gain: Simulated versus Measured at desired oscilla-         | 118 |

| 5.2 | tion frequency                                                  | 118 |

|     | Expected output pattern per channel                             |     |

| 5.3 | L3 CBi Frame Payloads                                           | 133 |

| 5.4 | Calibration factor determination based on measurements in |     |

|-----|-----------------------------------------------------------|-----|

|     | 2.5 Gbit/s End-ONT Mode                                   | 137 |

| 5.5 | CABINET power extrapolations                              | 137 |

| 5.6 | CABINET Upstream power extrapolations                     | 140 |

| 5.7 | CABINET Power scaling with operating frequency            | 141 |

| 5.8 | Remote Node Power consumption including all factors       | 143 |

#### xvi

### Acronyms

**10GE-PON** 10 Gbit/s Ethernet PON.

ADSL Asymmetric Digital Subscriber Line.

APON Asynchronous Transfer Mode (ATM) PON.

ASIC Application-Specific Integrated Circuit.

BAU Business-As-Usual.

BiPON Bit-interleaving PON.

BPON Broadband PON.

**BWMAP** Bandwidth Map.

CABINET CAscaded Bit-Interleaving eNd tErmination/repeaTer.

CapEx Capital Expenditure.

**CBi-PON** Cascaded Bit-interleaving PON.

CDR Clock-and-Data Recovery.

CML Current-Mode Logic.

CMOS Complementary Metal-Oxide-Semiconductor.

CO Central Office.

CP Charge Pump.

**DBA** Dynamic Bandwidth Allocation.

DLL Delay Locked Loop.

- **DSBWMAP** Downstream Bandwidth Map.

- **DSL** Digital Subscriber Line.

- **EFM** Ethernet in the First Mile.

- **EPON** Ethernet PON.

- FLL Frequency Locked Loop.

- FP7 Seventh Framework Programme.

- FPGA Field-Programmable Gate Array.

- FSAN Full Service Access Network.

- FTTC Fiber-To-The-Curb.

- FTTH Fiber-To-The-Home.

- FTTP Fiber-To-The-Premises.

- G-PON Gigabit-capable PON.

- **ICT** Information and Communication Technology.

- **IEEE** Institute of Electrical and Electronics Engineers.

- IL Injection Locked.

- **IP** Internet Protocol.

- **ISDN** Integrated Services Digital Network.

- **ISP** Internet Service Provider.

- ITU International Communication Unit.

- **IXP** Internet eXchange Point.

- LA Limiting Amplifier.

- LAN Local Area Network.

LD Laser Driver.

LR-PON Long-Reach PON.

MAC Medium Access Control.

NG-PON2 Next-Generation PON 2.

NNI Network-to-network interface.

$\boldsymbol{NRZ}\ \ Non-Return$  to Zero.

**O-E-O** Optical-Electrical-Optical.

**ODN** Optical Distribution Network.

**OFDM** Orthogonal Frequency Division Multiplexing.

**OLT** Optical Line Terminal.

P2MP Point-to-MultiPoint.

PC Personal Computer.

PD Phase Detector.

**PI** Phase Interpolator.

PLL Phase Locked Loop.

PN Phase Noise.

**PON** Passive Optical Network.

PWM Pulse-Width Modulation.

RN Remote Node.

**RNID** Repeater/End-ONT Identifier.

**ROSA** Receiver Optical Sub-Assembly.

SA-FF Sense Amplifier based Flip-Flop.

**TDM** Time Division Multiplexing.

TDMA Time Division Multiple Access.

TIA Transimpedance Amplifier.

TOSA Transmitter Optical Sub-Assembly.

TWDM Time and Wavelength Division Multiplexing.

**UI** Unit Interval.

**USBWMAP** Upstream Bandwidth Map.

VCO Voltage Controlled Oscillator.

**VDSL2** Very-high-bit-rate Digital Subscriber Line 2.

**WDM** Wavelength Division Multiplexing.

WWW World Wide Web.

**XG-PON** 10-Gigabit-capable PON.

## Nederlandse samenvatting — Summary in Dutch —

Gedurende de laatste paar jaar is het dataverkeer exponentieel gestegen, en er wordt voorspeld dat het einde van deze groei nog niet in zicht is. Deze groei wijst op een steeds sterker verbonden wereld, wat vele voordelen met zich meebrengt: gemakkelijke toegang tot kennis, toename in productiviteit door efficiënte communicatie en het eenvoudig delen van rekenkracht. Deze voordelen hebben echter een prijs. De laatste jaren is er een sterke bewustwording opgekomen met betrekking tot de negatieve impact op het milieu die communicatienetwerken hebben als direct gevolg van hun enorme vermogenverbruik.

Onderzoek heeft aangetoond dat het vermogenverbruik van communicatienetwerken een significant en groeiend deel van het totale globale vermogenverbruik inneemt. Rekening houdend met de verbluffende groei die het dataverkeer nog steeds ondergaat, is het duidelijk dat de volgende-generatie netwerken een sterk verbeterde vermogensefficiëntie zullen moeten hebben indien we deze groei willen volhouden. Deze waarneming heeft geleid tot het oprichten van het GreenTouch consortium in 2010, die als missie had aan te tonen dat de energie-efficiëntie van communicatienetwerken verbeterd zou kunnen worden met een factor  $1000 \times$  tegen 2020, vergeleken met het door GreenTouch gedefinieerd *baseline netwerk* dat opgebouwd werd met de meest energie-efficiënte apparatuur beschikbaar in 2010.

Dit proefschrift stelt het Gecascadeerde Bit-verwevende Passief Optisch Netwerk (CBi-PON) voor, welke een van de vast-toegangsnetwerk technologieën ontwikkeld binnen GreenTouch is. De CABINET ASIC wordt geïntroduceerd als een instantiatie van een generiek CBi apparaat dat gebruikt kan worden om een CBi-PON uit te rollen. Vermogenmetingen op de CABINET laten ons toe de vermogenverbruiksreductie te schatten van een volgende-generatie netwerk dat een CBi-PON gebruikt in plaats van een meer traditioneel Passief Optisch Netwerk. Het onderzoek voor dit proefschrift werd uitgevoerd in het kader van het GreenTouch CBI project en het EU FP7 DISCUS project, beide projecten die technologieën ontwikkelen die moeten leiden tot duurzame communicatienetwerken.

In Hoofdstuk 1 wordt de lezer bekend gemaakt met de oorsprong van het Internet, om zo de nodige context te verschaffen waarbinnen het werk voor dit proefschrift werd uitgevoerd. Het hoofdstuk vervolgt met het onthullen van de problemen met de huidige communicatienetwerken, waarbij zowel de ecologische als de economische impact besproken wordt.

Vervolgens wordt de huidige *core-metro-access* architectuur voorgesteld en worden typische getallen gegeven om aan te tonen waarom het vermogenverbruik van de *access* en *metro* delen het leeuwendeel van het totale vermogenverbruik voor zich nemen, te wijten aan het enorme aantal apparaten in het netwerk. Het access netwerk wordt besproken, waarbij de beperkingen van koper, de verschuiving naar optische toegangsnetwerken en het concept van passieve optische netwerken worden behandeld. De metro-access convergentie door de introductie van *Long-Reach* PONs wordt aangehaald als de meest recente ontwikkeling. De uitdagingen voor volgendegeneratie netwerken worden besproken, waaruit de twee belangrijkste uitdagingen voortkomen: (1) hoge bandbreedtes per gebruiker en (2) flexibele bandbreedte-allocatie, beiden gecombineerd met laag vermogenverbruik.

De Bit-verwevende PON (BiPON), die de basis vormt waarop de Gecascadeerde Bit-verwevende PON gebouwd is, wordt kort voorgesteld in Hoofdstuk 2. Het hoofdstuk start met een overzicht van de verschillende PON protocollen, om zo de lezer te voorzien van het referentiekader waarbinnen BiPON ontwikkeld werd. Daaropvolgend wordt de belangrijke paradigmaverschuiving van pakket-gebaseerde *Time Division Multiplexing* (TDM) naar bit-gebaseerde TDM uitgelegd en wordt de ingebouwde dynamische bandbreedte-allocatie toegelicht. Het hoofdstuk eindigt met het presenteren van de enorme vermogensreductie van  $35 \times$  tot  $180 \times$  die te danken is aan het gebruik van BiPON.

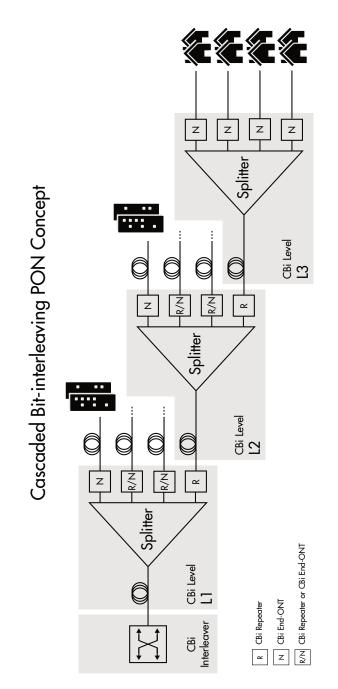

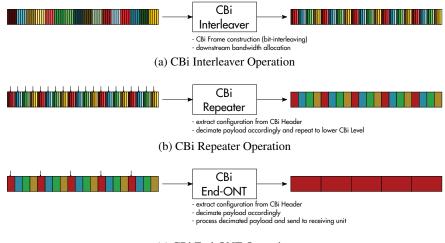

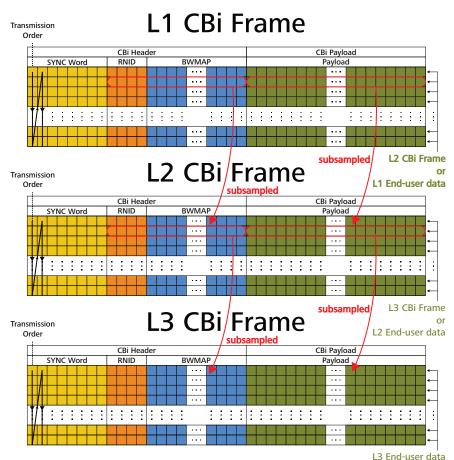

Hoofdstuk 3 bespreekt de metro-access convergentie en Long-Reach PONs als een oplossing voor volgende-generatie netwerken. Een van de mogelijke problemen is de impact op de prijs en het vermogenverbruik van de Optische Netwerk Eenheid (ONU) bij de eindgebruiker. Deze kan aangepakt worden door BiPON tot het volgende niveau te verheffen door meerdere, gecascadeerde niveaus van BiPON te implementeren: de Gecascadeerde Bit-verwevende PON (CBi-PON). Het hoofdstuk vervolgt met de introductie van de CBi netwerktopologie en de verschillende CBi apparaten nodig in een CBi-PON: CBi Interleaver, CBi Repeater en CBi End-ONT. Details worden gegeven rond de compositie van het CBi Frame en een 3-niveau instantiatie van een CBi-PON wordt gepresenteerd. Deze instantiatie gebruikt een generiek CBi apparaat welke zowel de rol van CBi Repeater, als die van CBi End-ONT kan opnemen: de CABINET.

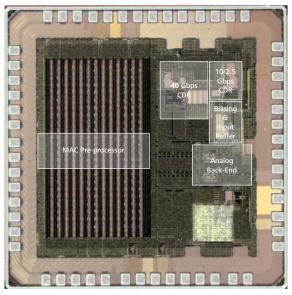

Het ontwerp en de implementatie van de CABINET ASIC wordt besproken in Hoofdstuk 4. De systeemarchitectuur wordt voorgesteld en deze bestaat uit drie grote delen: (1) de analoge front-end, (2) de Medium Access Control (MAC) voorverwerkingseenheid en (3) de analoge back-end.

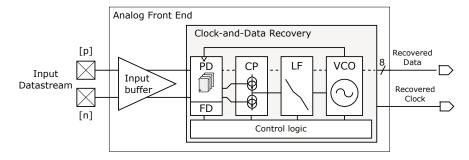

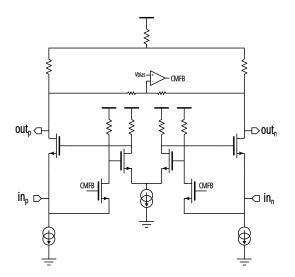

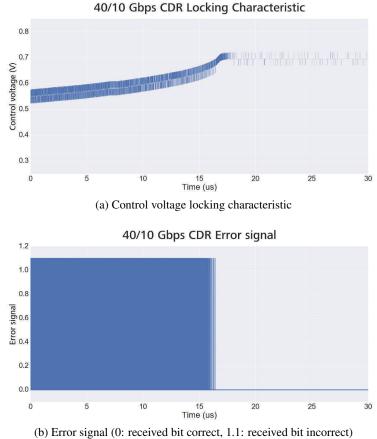

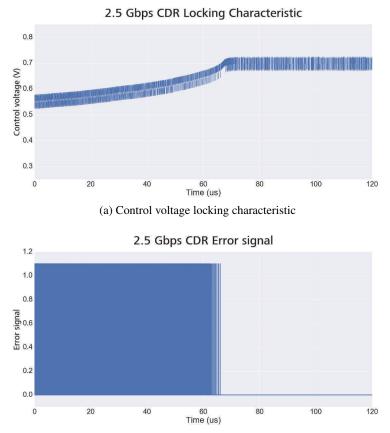

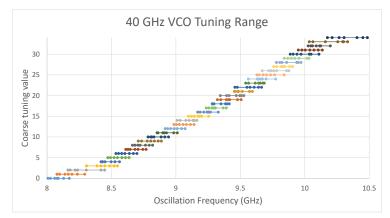

De analoge front-end bestaat uit een klok-en-data herstelcircuit (CDR) aan meerdere snelheden. De topologiekeuze van de CDR wordt verklaard en de keuzes worden toegelicht die toelaten om de CDR te ontwerpen in de geest van BiPON: de snelheid zo vroeg mogelijk in de verwerkingsketen reduceren. Bijgevolg is de 40 Gbit/s CDR een *sub-sampling* CDR, wat wil zeggen dat deze niet alle databits herstelt. De kritische bouwblokken worden behandeld: de fasedetector, bemonsteraar, spanningsgestuurde oscillatoren (40 GHz, 10 GHz en 2.5 GHz), *charge pump* en lusfilter. De dimensionering wordt besproken en de simulatieresultaten tonen aan dat alle CDRs *locken* zoals verwacht.

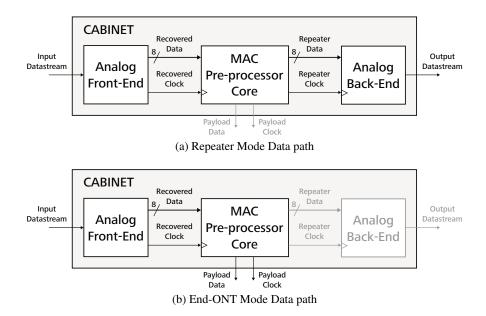

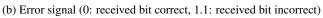

Volgend op de analoge front-end wordt de MAC-voorverwerkingseenheid besproken. De MAC-voorverwerkingseenheid is een puur digitale blok, welke de herstelde databits van de analoge front-end neemt en verwerkt volgens het CBi-PON protocol om zo de correcte data te bepalen zodat deze doorgestuurd kan worden (CBi Repeater) of naar een FPGA gezonden kan worden voor verdere verwerking (CBi End-ONT). In het geval van de CBi Repeater serialiseert de analoge back-end de uitgang van de MACvoorverwerkingseenheid tot een enkele datastroom die doorheen het lagere CBi niveau gestuurd kan worden. De details van de implementatie van deze analoge back-end worden gegeven op het einde van Hoofdstuk 4. Het hoofdstuk sluit af met een visualisatie van de CABINET ASIC layout.

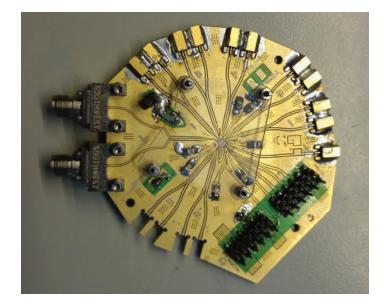

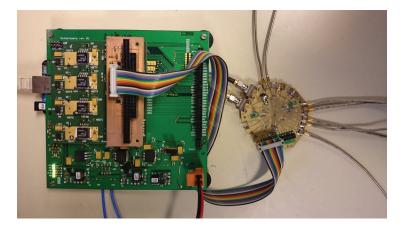

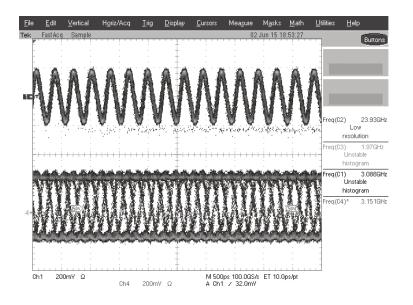

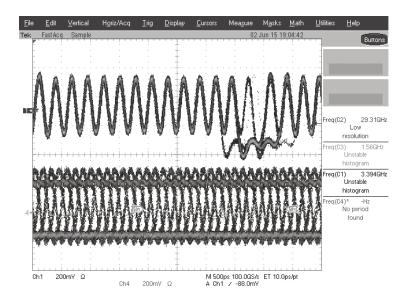

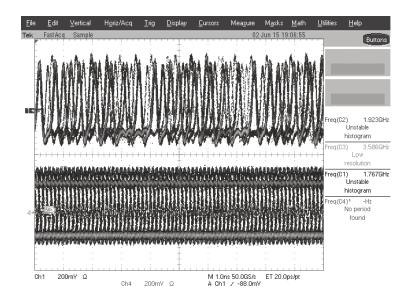

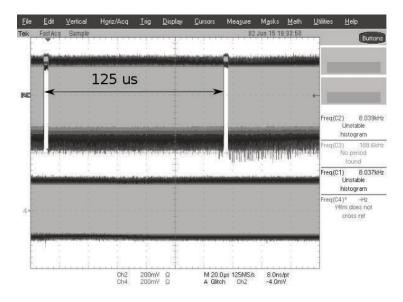

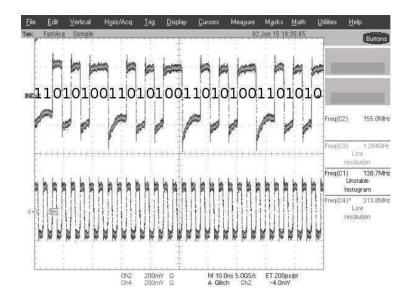

In het eerste deel van Hoofdstuk 5 worden de meetresultaten van de CA-BINET ASIC voorgesteld. De spanningsgestuurde oscillatoren (VCO's) zijn gemeten en er is aangetoond dat ze werken zoals verwacht - al is hun gevoeligheid aan de voedingsspanning hoger dan geanticipeerd. Daarenboven werden er problemen waargenomen met de *serializer*, vermoedelijk veroorzaakt door problemen met de klokdistributie. De *Frequency Locked Loop* (FLL) werkt zoals verwacht voor alle snelheden. Hoewel de bemonsteraars de mogelijkheid tonen om een enkele bit te bemonsteren aan 28 Gbit/s, heeft de bemonsterklok die afgeleid is van de VCO's te veel jitter om een goede bemonstering te bekomen. Bijgevolg geven de metingen op de CDR-werking van de CABINET geen bevredigende resultaten. Gebruikmakend van dataherstel op basis van de FLL waren we wel in staat 2.5 Gbit/s datastromen correct te herstellen en de werking van de MACvoorverwerkingseenheid werd geverifieerd op deze datastromen. Uit de vermogensmetingen van deze correct werkende modus werden vermogenverbruiksschattingen voor alle modi geëxtrapoleerd.

In het tweede deel van het hoofdstuk worden de geëxtrapoleerde schattingen van het vermogenverbruik aangewend om de reductie in vermogenverbruik te berekenen die de toepassing van een CBi-PON kan betekenen. De referentie waartegen het vermogenverbruik vergeleken wordt is het 2010 baseline netwerk zoals gedefinieerd door het GreenTouch consortium. Het vermogenverbruik van een ONU daalt van 1.5 W tot 0.4 W, of een vermogenverbruik-reductiefactor van  $3.7 \times$ . De Remote Node gebruikt in CBi-PON verbruikt slechts 21.17 mW/ONU en vervangt de sterk verbruikende aggregatieswitch die 121 mW/ONU verbruikt, wat zich vertaalt in een vermogenverbruik-reductiefactor van  $5.7 \times$ .

Dit proefschrift wordt afgesloten met Hoofdstuk 6, waarin het werk wordt samengevat, een vooruitzicht wordt gegeven op volgende-generatie netwerken en een toelichting wordt gegeven over het werk dat verder nog kan gebeuren in de context van CBi-PON en volgende-generatie netwerken in het algemeen.

### English summary

During the last couple of years, data traffic has been rising exponentially and it is predicted that this growth is not going to end anytime soon. This growth indicates a more connected world which brings numerous benefits: easier access to knowledge, productivity increases due to efficient communication and facilitated sharing of computing power. However, these benefits come with a price. Over the past few years a stronger awareness has risen with respect to the negative environmental impact communication networks have as a direct result of their massive power consumption.

Research has shown that the power consumption of communication networks is taking up a significant and growing share of the total global power consumption. Taking into account the staggering growth data traffic is still undergoing, it is clear next generation networks are going to require a much improved power efficiency if we want to sustain this growth. This observation led to the foundation of the GreenTouch consortium in 2010, which made it its mission to show that the energy efficiency of communication networks could be improved by a factor of  $1000 \times$  by 2020, compared to the GreenTouch-defined baseline network which was built using the most energy efficient equipment available in 2010.

This dissertation presents the Cascaded Bit-interleaving PON (CBi-PON), which is one of the Fixed Access Network technologies developed within GreenTouch. The CABINET ASIC is introduced as an instantiation of a generic CBi Device that can be used to deploy a CBi-PON. Power measurements on the CABINET allow us to estimate the power consumption reduction that can be expected from a next generation network that uses a CBi-PON instead of the more traditional Passive Optical Networks. The research conducted for this dissertation was performed as part of the Green-Touch CBI project and the EU FP7 DISCUS project, both projects that aim to develop technologies resulting in sustainable communication networks.

In Chapter 1, the reader is introduced to the origins of the Internet to provide the required context in which the work for this dissertation was performed. The chapter continues to reveal the issues with current communication networks, highlighting both the ecological as the economical impact.

Subsequently, the current *core-metro-access* architecture is presented and typical numbers are given to show why the power consumption of *access* and *metro* tiers constitute the lion's share of the total power consumption due to the vast amount of devices in the network. The access network is discussed, covering the copper limitations, the move to all-optical access networks and the concept of passive optical networks. Finally, the metro-access convergence with the introduction of Long-Reach PONs is presented as the latest development. The challenges of next-generation networks are discussed, arriving at two main challenges: (1) high bandwidths per user and (2) flexible bandwidth allocation, both combined with lower power consumption.

The Bit-interleaving PON (BiPON), which forms the basis on which the Cascaded Bit-interleaving PON is built, is briefly introduced in Chapter 2. The chapter starts off with an overview of the different PON protocols, in order to provide the reader with the necessary reference frame in which BiPON was developed. Next, the important paradigm-shift from packet-based Time Division Multiplexing (TDM) to bit-based TDM is explained and the built-in dynamic bandwidth allocation is highlighted. The chapter ends by presenting the enormous power savings of  $35 \times$  up to  $180 \times$  associated to the use of BiPON.

Chapter 3 discusses the metro-access convergence and Long-Reach PONs as a solution for next-generation networks. One of the possible issues is the impact on the cost and the power consumption of the Optical Network Unit (ONU). This can be mitigated by taking BiPON to the next level by implementing multiple, cascaded levels of BiPON: the Cascaded Bit-interleaving PON (CBi-PON). The chapter continues to introduce the CBi Network Topology and the different CBi Devices required in a CBi-PON: CBi Interleaver, CBi Repeater and CBi End-ONT. Details are given on the CBi Frame composition and finally a 3-level instantiation of a CBi-PON is presented. This instantiation uses a generic CBi Device which can serve both as CBi Repeater and CBi End-ONT: the CABINET.

The CABINET ASIC design and implementation is discussed in Chapter 4. The system architecture is presented and three main parts are identified: (1) the Analog Front-End, (2) the Medium Access Control (MAC) preprocessor and (3) the Analog Back-End.

The Analog Front-End consists of a multi-rate Clock-and-Data Recovery (CDR) circuit. The choice of CDR topology is clarified, as well as the choices made to design the CDR in the spirit of the Bit-interleaving PON: reducing the rate as early in the chain as possible. As a result, the 40 Gbit/s CDR is a sub-sampling CDR, which means it is not recovering all data bits. All critical building blocks are covered: the Phase Detector, Sampler, Voltage-Controlled Oscillators (40 GHz, 10 GHz and 2.5 GHz), Charge Pump and Loop Filter. The sizing is discussed and simulation results show that all CDRs lock as expected.

Following the Analog Front-End, the MAC preprocessor is discussed. The MAC preprocessor is a purely digital block, which takes in the recovered data bits from the Analog Front-End and processes them according to the CBi-PON protocol to determine the correct data to either forward (CBi Repeater) or send to an FPGA for further processing (CBi End-ONT). In the case of a CBi Repeater, the Analog Back-End serializes the MAC preprocessor output to a single data stream that can be sent through the lower CBi Level. The details of the implementation of this Analog Back-End are given at the end of Chapter 4. The chapter is concluded with a visualization of the CABINET ASIC layout.

In the first part of Chapter 5, the measurement results of the CABINET ASIC are presented. The VCOs are measured and shown to operate as expected - although their power supply sensitivity is higher than anticipated. Furthermore, issues were detected with the serializer, most likely caused by the clock distribution. However, the Frequency Locked Loop (FLL) is verified to operate as expected for all rates. While the samplers show the ability to sample a single bit at 28 Gbit/s, the sampling clock which is derived from the VCOs contains too much jitter to obtain any good data sampling. As a result, the measurements on the CDR operation of the CABINET could not produce satisfying results. Using FLL-based data recovery, we were able to recover 2.5 Gbit/s data streams correctly and the MAC preprocessor was verified to operate as expected for these data streams. From the power measurements on this correctly operating mode, power measurements for all modes were extrapolated.

In the second part of the chapter, the extrapolated power estimates are used to calculate the power consumption reduction which the use of a CBi-PON could bring. The reference to which the power consumption is compared is the 2010 baseline network as defined by the GreenTouch consortium. Comparing the power consumption of an ONU, which drops from 1.5 W

to 0.4 W, a power consumption reduction factor of  $3.7 \times$  is shown. The Remote Node used in the CBi-PON consumes only 21.17 mW/ONU and replaces the power-hungry Aggregation Switch that consumes 121 mW/ONU, which translates to a power consumption reduction factor of  $5.7 \times$ .

The dissertation is concluded with Chapter 6, which summarizes the work performed, gives an outlook on next-generation networks and highlights future work that could be done in the context of CBi-PON and next-generation networks in general.

## List of publications

#### **Publications in international journals**

- A. Vyncke, G. Torfs, C. Van Praet, M. Verbeke, A. Duque, D. Suvakovic, H. Chow, and X. Yin, *The 40 Gbps Cascaded Bit-interleaving PON [invited]*, Optical Fiber Technology

- M. Verbeke, P. Rombouts, A. Vyncke, and G. Torfs, *Influence of jitter on limit cycles in bang-bang clock and data recovery circuits*, IEEE Transactions on Circuits and Systems I Regular Papers, vol. 62, no. 6, July 1, 2015, pp. 1463-1471

- T. De Keulenaer, G. Torfs, Y. Ban, R. Pierco, R. Vaernewyck, A. Vyncke, Z. Li, J. H. Sinsky, B. Kozicki, X. Yin, and J. Bauwelinck, 84 Gbit/s SiGe BiCMOS duobinary serial data link including serialiser/deserialiser (SERDES) and 5-tap FFE, IET Electronic Letters, vol. 51, no. 4, February 19, 2015, pp. 343-345

- X. Z. Qiu, X. Yin, J. Verbrugghe, B. Moeneclaey, A. Vyncke, C. Van Praet, G. Torfs, J. Bauwelinck, and J. Vandewege, *Fast synchronization 3R burst-mode receivers for passive optical networks [invited tutorial]*, Journal of Lightwave Technology, vol. 32, no. 4, February 15, 2014, pp. 644-659

- C. Van Praet, G. Torfs, A. Vyncke, E. Matei, P. Cautereels, and J. Bauwelinck, *Fast H.264 intra prediction for network video processing*, IEICE Electronics Express, vol. 10, no. 12, June 2, 2013, pp. 1-6

#### **Publications in international conferences**

• J. Van Kerrebrouck, T. De Keulenaer, J. De Geest, R. Pierco, R. Vaernewyck, A. Vyncke, M. Fogg, M. Rengarajan, G. Torfs, and

J. Bauwelinck, 100 Gb/s serial transmission over Copper using duobinary signaling, Designcon, Santa Clara, California, USA, January 19-21, 2016

- A. Vyncke, G. Torfs, M. Verbeke, C. Van Praet, H. Chow, D. Suvakovic, A. Duque, and X. Yin, A Low Power 40 Gbit/s Cascaded Extension to Bit-Interleaving Optical Networks Enabling Next-Generation Metro/Access Connectivity, 20th Annual Symposium of the IEEE Photonics Benelux Chapter, Brussels, Belgium, November 26-27, 2015

- A. Vyncke, G. Torfs, M. Verbeke, C. Van Praet, H. Chow, D. Suvakovic, A. Duque, and X. Yin, *Voltage controlled oscillators for 40 Gbit/s cascaded bit-interleaving PON*, Advances in Wireless and Optical Communications (RTUWO 2015), 5-6 November 2015, Riga, Latvia, November 5-6, 2015, pp. (1-4)

- A. Vyncke, G. Torfs, M. Verbeke, and X. Yin, An 8-phase 10 GHz Voltage Controlled Ring Oscillator for 40 Gbit/s BiPON Clock-and-Data Recovery, 11th Conference on PhD Research in Microelectronics and Electronics (IEEE PRIME 2015), Glasgow, United Kingdom, June 29 - July 2, 2015, pp. (1-4)

- A. Vyncke, G. Torfs, M. Verbeke, C. Van Praet, H. Chow, D. Suvakovic, A. Duque, and X. Yin, *CBI-PON: a Low Power Solution offering Flexible Bandwidth Allocation for 40 Gbit/s Next generation Metro/Access Networks*, IEICE Information and Communication Technology Forum 2015 (ICTF 2015), Manchester, United Kingdom, June 3-5, 2015, pp. (1-4)

- X. Yin, H. Chow, A. Vyncke, D. Suvakovic, G. Torfs, A. Duque, D. van Veen, M. Verbeke, T. Ayhan, and P. Vetter, *CBI: a scalable energy-efficient protocol for metro/access networks [invited]*, 2014 IEEE Online Conference on Green Communications (OnlineGreen-Comm), November 12-14, 2014, pp. 126-131

- G. Torfs, X. Yin, A. Vyncke, M. Verbeke, J. Bauwelinck, Solutions for a single carrier 40 Gbit/s downstream long-reach passive optical network [invited], 16th International Telecommunications Network Strategy and Planning Symposium (Networks 2014), vol. fri.20.2, Funchal, Madeira, Portugal, September 17-19, 2014, pp. 1-5

- X. Yin, X. Z. Qiu, G. Torfs, C. Van Praet, R. Vaernewyck, A. Vyncke, J. Verbrugghe, B. Moeneclaey, M. Ruffini, D. B. Payne, and J. Bauwelinck, *Performance evaluation of single carrier 40-Gbit/s downstream for long-reach passive optical network*, 18th International Conference on Optical Network Design and Modeling (ONDM 2014), Stockholm, Sweden, May 19-22, 2014, pp. 162-167

- J. Bauwelinck, R. Vaernewyck, J. Verbrugghe, W. Soenen, B. Moeneclaey, C. Van Praet, A. Vyncke, G. Torfs, X. Yin, X. Z. Qiu, J. Vandewege, N. Sotiropoulos, H. de Waardt, R. Cronin, G. Maxwell, T. Tekin, P. Bakopoulos, C. P. Lai, and P. D. Townsend, *High-speed electronics for short-link communication [invited]*, 39th European Conference and Exhibition on Optical Communication (ECOC 2013), vol. Mo.4.F.4, London, UK, September 22-26, 2013, pp. 164-166

- W. Soenen, R. Vaernewyck, A. Vyncke, and J. Bauwelinck, *Evaluation of a discrete 4-PAM optical link for future automotive networks*, Annual Symposium of the IPS Benelux Chapter, pp. 69-72, November, 29-30, 2012, Mons, Belgium

#### **Publications in national conferences**

• A. Vyncke, Digital Assistant Processor Relieves Analog Designer Headaches, 13th FEA PhD Symposium, December 5, 2012, Ghent, Belgium

#### **Chapters in books**

• A. Vyncke, G. Torfs, M. Verbeke, C. Van Praet, H. Chow, D. Suvakovic, A. Duque, and X. Yin, *Design and measurement of VCOs for 40 Gbit/s Cascaded Bit-Interleaving PON*, 1st International IEEE Conference on Advances in Wireless and Optical Communications 2015, Latvia, Riga, 5-6 November, 2015. Riga: RTU Press, 2015, pp.91-104. ISBN 978-9934-10-758-0

# Introduction

Mankind has always displayed a strong desire to communicate. Languages were invented, writing was developed and for years these were the main means of communication. By the second half of the 19th century, scientific progress enabled an extraordinary pace at which new communication technologies became available: printing, photography, telegraphy, telephony, .... With the introduction of the Internet, an unprecedented convenience in communication was born. Providing a number of virtually unlimited direct connections to anywhere in the world, the Internet fulfills mankind's need for communication like no technology ever before.

Remarkably, even though the Internet has become such an important part of everyday life, there is a general ignorance regarding the infrastructure allowing the Internet to achieve the impressive world-wide connectivity that is provided. As this infrastructure forms the context in which the research in this dissertation has been conducted, this introductory chapter starts off with a brief history of how the Internet originated. Subsequently, the current form of the Internet's infrastructure is described and this chapter is concluded by discussing next-generation networks and the challenges these will be facing.

#### **1.1** On the origins of Internet

Even though most of us use the Internet on a daily basis, few really know the underlying infrastructure that enables us to send each other messages, instantly see news from all around the world or stream movies at home in high definition quality. Despite its current ubiquitousness, the road to today's world-wide network was not an easy one. In what follows, a brief overview is given on how the Internet originated and how our communication networks are organized today.

#### **1.1.1 From ARPANET to the Internet - a brief history**

The birth of the Internet took place during the Cold War. At that moment in time there was only one network available in the United States: the AT&T telephone network. The design of the AT&T network used a centralized architecture, making it extremely vulnerable to malfunctions or attacks. Of course, the risk of losing all means of communication while under a constant threat of a nuclear attack was not a favorable position to be in.

Moreover, at that time, DARPA (Defense Advanced Research Projects Agency - the US Defense Research Department) had acquired multiple research computers on different geographical locations. Enabling communication between these computers was considered advantageous, since it would make the capabilities of a computer installed at one site accessible by a research group located at a different one. Furthermore, the possibility to share data would significantly improve collaboration between the different research groups.

To address these needs, DARPA developed the first ever packet-switching network, setting up a connection between four different nodes: the UCLA (University of California, Los Angeles), SRI (Stanford Research Institute), UCSB (University of California, Santa Barbara) and the University of Utah (Figure 1.1). This network, coined ARPANET, became a reality in September 1969 with the first successful transmission of data between the UCLA and SRI, and is considered the precursor of the Internet. However, it was still very different from the Internet as we know it today. As the number of sites connected to ARPANET quickly grew, the TCP/IP protocol was developed in 1983 to handle compatibility issues on the network. This allowed more computers to easily connect to ARPANET, leading to an even more rapid growth.

In 1986 the National Science Foundation (NSF) had created a couple of supercomputer centers at several universities, and the NSF introduced NSFNet

Figure 1.1: First ARPANET with 4 nodes [1]

Figure 1.2: Original NSFNet with 56 kbit/s backbone [2]

as a way to connect the different supercomputer sites, as shown in Figure 1.2. In the same year, Berkeley released BSD (Berkeley Software Distribution) Unix, a multi-user operating system including a complete version of TCP/IP (Transmission Control Protocol/Internet Protocol).

With the release of BSD Unix, which was free, colleges and universities started to create local area networks. Since they used TCP/IP, they could connect these smaller networks to NSFNet, effectively creating an internetwork: a network consisting of networks, where NSFNet was functioning as the so-called *backbone* of the internetwork.

#### NSFNET T1 Network 1991

Figure 1.3: Intermediary NSFNet with T1 backbone (1.5 Mbit/s) [3]

During this time, the NSFNet backbone had a bandwidth of 56 kilobits per second. Its popularity grew tremendously, requiring NSF to upgrade the NSFNet backbone speed to 1.5 Mbit/s (T1) by 1988, which was only 2 years after its conception. The growing popularity of NSFNet can partly be explained by the introduction of the Domain Name Service (DNS) system in 1984. Until then, computers were addressed by their Internet Protocol (IP) address, which is difficult to remember (e.g. 74.125.228.194). The DNS system can be thought of as an automatic phonebook, allowing one to use an easy to remember name (e.g. google.com), which is then translated by the DNS system to the correct IP address. Eliminating the need to memorize complicated numbers definitely facilitated the adoption of NSFNet by the broader public.

Since ARPANET did not receive a bandwidth upgrade, it was no longer

Figure 1.4: Final NSFNet with T3 backbone (45 Mbit/s) [4]

relevant, causing it to be disconnected from the Internet in 1990. NSFNet on the other hand had to be upgraded again in 1991 (Figure 1.3) up to 45 Mbit/s (T3) to support the ever-increasing data traffic. The NSFNet with the T3 backbone as it was in 1992 is visualized in Figure 1.4.

The introduction of several commercial networks, which were interconnected using the federal-funded, academic-oriented NSFNet caused a disruption in the philosophy regarding how the Internet should be organized. As a result, the NSFNet backbone service was shut down in 1995 and replaced by a multitude of commercial backbone service providers. Network Access Points provided traffic exchanges between the different commercial networks, a task that later would be performed by Internet eXchange Points (IXPs).

At this point in time, other countries had already connected their networks to the US network, making the Internet an international concept. The interconnection between the different backbone networks was provided by IXPs, which is still the case today.

Today, so many commercial Internet Service Providers exist, that they are categorized in 3 different tiers which are hierarchically interconnected, as shown in Figure 1.5. A Tier 1 Internet Service Provider (ISP) operates at the highest level, and only a few exist. A Tier 1 has an extensive network, covering a large area. Tier 1 ISPs typically have so called *peering agreements*: agreements that define how Tier 1 ISPs make use of each other's network to provide world-wide connectivity to their customers.

Compared to a Tier 1 ISP, a Tier 2 ISP has a more limited coverage span and

Figure 1.5: Internet Service Provider Tiers

needs to buy Tier 1 capacity to route the data traffic of its customers over the Tier 1 network that provides the desired global connectivity. Finally, at the lowest level are the Tier 3 ISPs. These typically operate at regional level, such as Proximus and Telenet in Belgium, and deliver Internet connectivity to end-users. Of course, these Tier 3 ISPs have contracts in place with either Tier 1 or Tier 2 ISPs to provide that service to their end-customers.

Historically, Internet traffic was routed over existing telephone copper cables. Those were once installed when deploying the telephone network and were readily available. Therefore it was cost-effective to re-use these. However, due to the rapid growth of the Internet, the data traffic increased exponentially. This urged ISPs to upgrade parts of the network to support higher bandwidths. For a few years new techniques allowed to keep using copper cable, but in the end optical fiber had to be installed to provide the needed bandwidths.

Because of the hierarchical nature of the networks, it was logical to upgrade the core network to optical fiber first, while the copper cable access network remained untouched. Throughout the years, more and more parts of the access network have been replaced by optical fiber, up to the point that we can talk about *the last mile*: only the part of the network that connects your house to the first aggregation switch is still in copper. That means a large share of the legacy copper network has already been replaced by optical fiber today. However, since optical fiber was installed merely as a drop-in replacement for copper cable, the network as a whole does not exploit all advantages of optical fiber. Therefore, new network infrastructures which take into account the availability of optical fiber during the design could improve the network's performance.

#### **1.2 A Truly Inconvenient Truth**

In 1990 the World Wide Web (WWW) was invented, a service running over the Internet, allowing anyone with a connection to the world-wide network to access information from across the globe within seconds. Around this time, the consumer market started offering truly affordable Personal Computers (PCs). Thanks to this evolution, households everywhere soon had access to the WWW and its growth continues to this day.

Figure 1.6: Personal Computer Price Evolution (1998 - 2015) [5]

Over the years PCs have become more affordable than ever and new technologies have enabled the development of portable devices such as laptops, tablets and smartphones. All of these are devices with impressive computational power for a fraction of the price of a PC in the early days. However, today the computational power of these devices is not the main interest of their owners. Owing to the widespread availability of Internet connectivity, these devices have become communication tools rather than computational ones. The evolution of electronics prices (Figure 1.6) combined with manufacturers truly flooding the market with devices (Figure 1.7) has gradually changed the *one-device-per-household* to a *multiple-devices-perperson* scenario. With communication devices penetrating every aspect of our everyday lives, it would be ignorant to deny this has a significant impact on our society.

Computers, smartphones, and tablet sales: 1975-2011

Figure 1.7: Computers, smartphones and tablet sales evolution [6]

#### 1.2.1 Ecological and Economical Impact

It is often hard to predict the impact of a new technology, while it might have far-reaching consequences. In the case of the Internet numerous obvious advantages were associated with rolling out such as network: reduced traveling, worldwide knowledge and resources sharing, .... As a result, the Information and Communication Technology (ICT) sector has exhibited a rapid growth, offering a multitude of benefits to its adopters, but resulting at the same time in an increasingly large impact on the world.

For example, the global power consumption of communication networks in 2012 has been estimated at 350 TWh [7], or a staggering 1.8% of the total global power consumption at that time. As long as the Internet was of modest size, the power consumption to keep the network up and running was limited. However, with the network deployed today the power consumption has truly exploded and will continue to do so if no action is taken in the very near future.

The high power consumption associated with our Internet usage is an issue both from an ecological as from an economical point of view. The ecological impact is very hard to estimate, since some of the benefits of having the Internet at our disposal actually have a positive impact on the global ecological footprint. However, with an estimated power consumption this high, one can hardly argue the ecological impact of our communication networks is not going to be significant.

Economically, one can easily understand the cost of energy becomes a major issue: at an estimated average cost of 8 eurocent/kWh, the energy to keep our communication networks turned on in 2012 was about 28 billion euro. You don't need to be an economical mastermind to see that a serious power consumption reduction is economically appealing.

Moreover, concern is rising regarding increased energy-dependency. With such vast amounts of energy needed to support our communication, any hiccup in energy production or distribution might be catastrophic for our economy. Furthermore, in [8] the author wonders if state-of-the-art ICT might become only accessible to those countries with nearly unlimited energy resources. Such a situation would result in an economic inequality recently described as the *digital divide*.

#### **1.3** Towards sustainable communication

Over the past few years, multiple initiatives have been started in an effort to reduce the impact of communication networks on the environment, while still addressing the needs future networks have. In the context of this dissertation, two of these initiatives are highlighted here.

**GreenTouch** The GreenTouch consortium was founded in 2010 with the goal of reducing the power consumption of communication networks to a tiny fraction of what it is today. Realizing this goal basically means reinventing communication networks, which would require involvement of the diverse organizations throughout ICT. Therefore, a consortium was formed to bring all these organizations together.

**DISCUS** As part of the EUs Seventh Framework Programme (FP7), this project aims to exploit demonstrated technology and concepts needed to define and develop a radically new architectural concept that can enable an integrated wireless and Fiber-To-The-Premises (FTTP) future network which addresses the economic, energy consumption, capacity scaling, evolutionary, regulatory and service demand challenges arising from a FTTP enabled future. The key target of the DISCUS project is a cost-effective architecture for ubiquitous broadband services overcoming the digital divide.

#### **1.4** Next-generation networks

Modern telecommunication networks are constructed as a three-level hierarchical network (Figure 1.8), where each level is called a tier, not to be confused with the ISP tiers mentioned earlier. Each tier can roughly be identified with a geographical entity. The *core tier*, which typically uses a mesh topology, is responsible for interconnecting continents and countries, spanning distances ranging from hundreds to thousands of kilometers.

Figure 1.8: Modern telecommunication network hierarchy

The *metro tier* corresponds to a metropolitan area, and can roughly be seen as the area a large city covers. Metro networks consist of a ring topology interconnecting several Central Offices (COs) over tens to hundreds of kilometers.

The *access tier* is the lowest level and provides connectivity to the enduser. Access networks are designed to operate on distances of a few to tens of kilometers. Contrary to the core and metro tier, the access tier is deployed in a variety of configurations, such as bus, star or ring topologies. Due to the hierarchical construction of a modern telecommunication network it is clear the amount of network devices deployed in the access tiers far outnumbers those in the core tiers (Table 1.1). Therefore, small power consumption reductions in access network devices potentially have a much bigger impact on the complete system than high power consumption reductions in power-hungry devices in the core network.

#### 1.4.1 Advances in the access network

Contrary to the core and metro networks, where the interconnection medium is optical fiber, the access network historically uses copper cable: the twisted

|        | Power consumption<br>(W/device) | # of devices | BAU<br>(GWh/yr) |

|--------|---------------------------------|--------------|-----------------|

| Home   | 10                              | 17,500,000   | 1,533           |

| Access | 1,280                           | 27,344       | 307             |

| Metro  | 6,000                           | 1,750        | 92              |

| Core   | 10,000                          | 175          | 15              |

Table 1.1: 2015-2020 Italian Network Forecast: Device Density and BAU

Energy Requirements [9]

pair telephone cable network and the coaxial cable CATV networks were readily available when the access networks had to be deployed. The Capital Expenditure (CapEx) costs associated with installing fiber are very high, and it would not have been sensible to ignore readily deployed networks with, at that time, more than enough bandwidth available.

#### 1.4.1.1 Copper limitations

The legacy networks were installed with a completely different use-case in mind, and therefore used low-cost copper cables. Therefore, the copper access networks have serious impairments: not only do they have a limited bandwidth, they suffer from high losses, dispersion problems and crosstalk issues.

Figure 1.9: Rate vs Reach for different xDSL Technologies [10]

However, thanks to the development of several impressive advanced transmission techniques, service providers have steadily been able to provide their customers with higher data rates, despite the low quality copper cables they are using. Unfortunately, these advanced techniques can only support limited distances. This is illustrated in Figure 1.9, where different Digital Subscriber Line (DSL) technologies are displayed with their maximum supported data rate versus distance between transmitter and receiver. The original Asymmetric Digital Subscriber Line (ADSL) could support up to 80% of the maximum data rate over distances longer than 3 km. On the other hand, Very-high-bit-rate Digital Subscriber Line 2 (VDSL2) supports a much higher data rate, but cannot support this data rate on distances over 200m. The emerging G.fast standard supports data rates up to 1.1 Gbit/s over a distance of 70m, but this quickly drops to 200 Mbit/s at distances of 200m. Although impressive achievements, this is not a sustainable way to cope with the ever-increasing demand for higher bandwidth. Moreover, these advanced transmission techniques all require extensive signal processing, making these solutions very power hungry.

#### 1.4.1.2 All-optical access networks

At the time the technological advancements made a commercial all-optical access network possible, the cost of such a network was way too high to even consider. Today, the situation has changed: optical fiber offers a multitude of advantages over copper cable, as summarized in Table 1.2. Therefore, a Fiber-To-The-Home (FTTH) infrastructure is desirable, where optic fiber is distributed to every subscriber's premise [11]. Despite all technological advantages, converting a legacy copper access network to an all-optical access network requires a dazzling investment, which explains why this topology has not been globally deployed at this time.

However, the limited distances supported by the currently used advanced transmission techniques have already forced service providers to adopt an intermediate solution: Fiber-To-The-Curb (FTTC). FTTC is a hybrid fiber access solution which consists of routing fiber to a cabinet in the street, close to the end-user, without requiring to install fiber to every single end-user. In an FTTC scenario, the connection from the cabinet to the end-user, which is still copper, is known as the *last mile*. Converting this last mile to optic fiber is very expensive, owing to the cost of the required civil works. Although this is quite the investment, more and more service providers start to recognize it would turn their current situation of bandwidth scarcity to one of bandwidth abundance, which enables long term growth and creates potential for additional services on the network.

| Property                | Advantage                                                                                                                                                                                                                                                      |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Size                    | The total diameter of an optical fiber (core, cladding and protection jacket) measures about $400 \mu\text{m}$ , a significant reduction from the 6mm diameter of coaxial cable. This is advantageous in cramped conduits in buildings and underground layout. |

| Weight                  | Due to the mass density difference and the smaller size, optical fiber yields a 10 to 30 % weight reduction compared to copper cable.                                                                                                                          |

| Bandwidth               | Fiber has very high bandwidth, supporting data rates over 100 Tbit/s across one single standard SMF, as experimentally proven in [12].                                                                                                                         |

| Loss                    | Optical fiber has an attenuation less than 0.2 dB/km at 1550 nm, enabling transmission over several tens of kilometers without amplification.                                                                                                                  |

| Electrical interference | Since light is used, electromagnetic fields have<br>no influence on transmission making it ideal<br>in environments where strong electromagnetic<br>fields are present.                                                                                        |

| Crosstalk               | Very little light escapes an optical fiber, resulting<br>in very good crosstalk characteristics.                                                                                                                                                               |

| Dispersion              | At 1550 nm the dispersion of optical fiber is about 17 ps/(nm.km), while at 1300 nm it can be reduced to 0.                                                                                                                                                    |

| Environmental           | Flammable or explosive environments pose no issue, since no sparks are ever generated by optical fiber.                                                                                                                                                        |

| Material availability   | While copper is mined, and is scarce, silica is<br>composed of oxygen and silicon, both available<br>abundantly.                                                                                                                                               |

| Multiplexing            | A single fiber supports multiplexing of many wavelengths, increasing the potential datarate.                                                                                                                                                                   |

Table 1.2: Advantages of optical fiber [10]

#### 1.4.2 Passive Optical Networks