Chatterjee, I., Uren, M. J., Karboyan, S., Pooth, A., Moens, P., Banerjee, A., & Kuball, M. (2017). Lateral Charge Transport in the Carbon-Doped Buffer in AlGaN/GaN-on-Si HEMTs. IEEE Transactions on Electron Devices. DOI: 10.1109/TED.2016.2645279

Peer reviewed version

Link to published version (if available): 10.1109/TED.2016.2645279

Link to publication record in Explore Bristol Research PDF-document

This is the author accepted manuscript (AAM). The final published version (version of record) is available online via IEEE at http://ieeexplore.ieee.org/document/7820083/. Please refer to any applicable terms of use of the publisher.

# University of Bristol - Explore Bristol Research General rights

This document is made available in accordance with publisher policies. Please cite only the published version using the reference above. Full terms of use are available: http://www.bristol.ac.uk/pure/about/ebr-terms.html

# Lateral Charge Transport in the Carbon-doped Buffer in AlGaN/GaN-on-Si HEMTs

I. Chatterjee, *Member, IEEE*, M. J. Uren, *Member, IEEE*, S. Karboyan, A. Pooth, P. Moens, A. Banerjee, M. Caesar and M. Kuball, *Senior Member, IEEE*

Abstract—Dynamic R<sub>ON</sub> and ramped substrate bias measurements are used to demonstrate size and geometry dependent dispersion in power transistors. This is due to a novel lateral transport mechanism in the semi-insulating carbon-doped GaN buffer in AlGaN/GaN HEMTs. We propose that the vertical field generates a 2D hole gas at the bottom of the GaN:C layer, with hole flow extending outside the isolated area. The device-todevice variation is due to a combination of widely spaced preferential leakage paths through the structure and lateral transport from those paths to trapping sites. The spread of the 2DHG outside the active area of the device strongly affects the result of substrate ramp measurements producing major differences between single and multifinger devices. In dynamic RON recovery measurements, single-finger devices show large device-to-device variation, with multifinger devices showing a small variation with the transient comprising the superposition of the recovery transient of multiple small single-finger devices.

*Index Terms*—GaN-on-Silicon, HEMTs, current collapse, dynamic *R*<sub>ON</sub>, power transistors, 2D Hole Gas

## I. INTRODUCTION

GaN based high-electron-mobility transistors (HEMTs) are being actively developed for high power, high voltage switching applications [1, 2]. By using a 2-D electron gas (2DEG) in GaN based heterojunctions and by benefiting from the high bandgap of GaN and its related alloys, low onresistance  $(R_{ON})$  and high blocking voltages can be realized at the same time [3, 4]. When employing standard approaches to improve the lateral breakdown strength, such as intentional incorporation of carbon (C) dopants, dynamic on-resistance (a time dependent on-resistance resulting from charge storage in either surface or bulk traps that can affect the performance of the device during switching) degrades significantly [5]-[8] impacting the power device efficiency. Surface trapping can be very effectively controlled by the use of field plates [9], but bulk trapping is inherent in all single-heterojunction HEMTs due to the necessity to include deep-level dopants in the GaN buffer to control bulk leakage and short-channel effects [10, 11]. Carbon has a complex range of deep levels in the gap, but the most important is an acceptor sitting 0.9 eV above the valence band [12]. With some compensation, this means that the buffer is weakly p-type with a low hole density, and hence high

resistivity, giving long time constants for charging processes (a hole density of only  $10^4$  cm<sup>-3</sup> was inferred in [13]). Charge trapping in the buffer leads to significant current collapse. Thus, it is necessary to understand the charge storage and transport in the various layers of the buffer to predict the long term stability of these devices. Substrate bias experiments provide an excellent tool to study charge trapping and transport in the buffer and effectively distinguish surface and bulk induced current collapse [14-16]. Monitoring the substrate bias dependence of the channel conductivity, and its dispersion as the ramp-rate and temperature are varied, allowed a model for the transport within each layer within the buffer to be constructed [13, 17-19]. Substrate bias ramps have been used to link buffer leakage in the upper part of the epitaxy to dynamic  $R_{ON}$  dispersion [20, 21].

Interpretation of substrate measurements has normally used the assumption that all transport is vertical and so 1-D models are appropriate. However, deviations from the 1D behavior have previously been observed locally within the device associated with enhanced leakage under contact regions [13] impacting transport within the isolated area. In this work, dynamic  $R_{ON}$  and back-bias measurements were used to investigate transport and trapping in the buffer and show that lateral conduction within the buffer can occur outside the isolated device region. An important consequence is that the assessment of single-finger test devices is not necessarily characteristic of the behavior of multiple-finger transistors and cannot accurately represent trapping issues in such devices. The proposed model to explain this behavior is that the vertical field results in the formation of a 2-D hole gas (2DHG) layer at the heterojunction between the bottom of the GaN:C layer and the AlGaN based strain relief layer (SRL). 2DHGs have been widely discussed as occurring at GaN based heterojunctions and have been exploited in active devices [22]-[26]. Here we show for the first time that a parasitic 2DHG within the buffer can also have a strong impact on the substrate bias dependence. As a result, the substrate biasing technique, which is an important tool in understanding trapping behavior in these devices, must be used with caution as it can give inconsistent results between single-finger and multiple-finger transistors. Interestingly the 2DHG had a more limited effect on dynamic  $R_{\rm ON}$  due to the local sinking of holes by the source contact, although clear device size dependence was still apparent.

This work was supported by the UK EPSRC "PowerGaN" project via grant no. EP/K0114471/1 and by the E<sup>2</sup>COGAN project.

I. Chatterjee was with the School of Physics at the University of Bristol. He is presently with Airbus Defence and Space, Friedrichshafen, Germany. (e-mail: indranil.chatterjee@airbus.com)

M. J. Uren, S. Karboyan, A. Pooth, and M. Kuball are with the Center for Device Thermography and Reliability (CDTR), H. H. Wills Physics Laboratory, University of Bristol, BS8 1TL, Bristol, UK;

P. Moens, A. Banerjee and M. Caesar are with ON Semiconductor, Oudenaarde, Belgium.

#### II. EXPERIMENTAL DETAILS

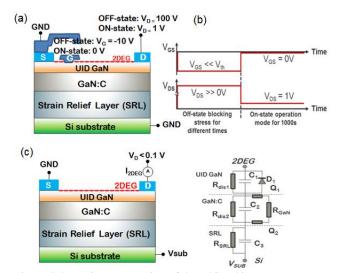

Devices were processed as part of the development of a 650V GaN power process. Sheet resistance of the 2DEG is ~400 Ohm/sq. Hall mobility and 2DEG density are ~1750 cm<sup>2</sup>/Vs and ~9x10<sup>12</sup> cm<sup>-2</sup> respectively. The MISHEMT devices use a Si<sub>3</sub>N<sub>4</sub> gate dielectric and show excellent performance and cross-wafer uniformity. The devices have pinch-off voltage of ~-7V and no evidence of surface current collapse [27]–[29]. The epitaxial layer structure, as shown schematically in Fig. 1, used an undoped channel region, an intentionally carbon doped GaN buffer (GaN:C), an Al(Ga)N based strain relief layer (SRL) with heterojunction at the GaN:C to SRL interface, all grown on 6-inch p-type Si.

The device structure and measurement setups are shown in Fig. 1. Two experiments were undertaken: firstly, a conventional drain transient measurement to evaluate dynamic  $R_{\rm ON}$ , and secondly a substrate bias ramp. Dynamic  $R_{\rm ON}$ measurements were undertaken at room temperature (RT) and 80°C. All the devices tested had gate and source field plates thereby strongly reducing or eliminating surface trapping effects. They were biased in the off-state with  $V_{GS} = -10V$  and  $V_{\rm DS} = 100 \text{V}$  for 1000 seconds before switching to the on-state with  $V_{GS} = 0V$ ,  $V_{DS} = 1V$ . This corresponds to a "worst case"  $V_{DS}$ for dynamic R<sub>ON</sub> measurement in this technology [29, 30, 31]. The on-state current, I<sub>DON</sub>, was then recorded for 1000s allowing the device to return towards equilibrium. Three different transistors were used for the study: single finger, two finger and multifinger power devices, having the same intrinsic source to drain geometry apart from gate width. The singlefinger transistor has a drain on only one side (S-G-D arrangement) and a gate width of 100µm and implant isolated active area of 100×50µm. The 2-finger transistor is symmetric to the drain electrode, again has 100µm wide fingers, and is a S-G-D-G-S sub-cell of the large power transistor. The power transistor has multiple wider fingers with an active area of 2.75×1mm.

The substrate ramp uses the change in conductivity of the 2DEG in the HEMT as a ramped substrate-bias is applied to the silicon wafer to monitor changes in the vertical electric field in the buffer below the 2DEG [13, 17]. Changes in the channel conductivity (with  $V_{GS}=0V$ ) can then be used to quantify bulk charge storage and trapping. The ramped voltage generates a vertical displacement current through the "leaky dielectric" buffer. The ramprate of ~1V/s is chosen so that the displacement current is comparable to the thermally generated leakage current of typical carbon doped GaN and hence will display dispersion associated with transport in that layer. Fig. 1(c) shows the lumped-element representation of the device structure including the primary vertical leakage paths and capacitances normally used to interpret substrate bias experiments assuming 1D conduction [11, 13-19]. Only negative substrate bias,  $V_{SUB}$ , is considered here since this corresponds to the polarity experienced under the drain in a transistor under OFF state conditions. The substrate ramp experiments were carried out with a maximum of 0.1V on the drain and with the gate grounded. All three types of device were tested.

Fig. 1: Schematic cross-section of the AlGaN/GaN HEMT power transistor with (a) dynamic  $R_{ON}$  and (b) back-biasing experimental details (c) 1D lumped-element representation of the device structure [16].

### III. EXPERIMENTAL RESULTS

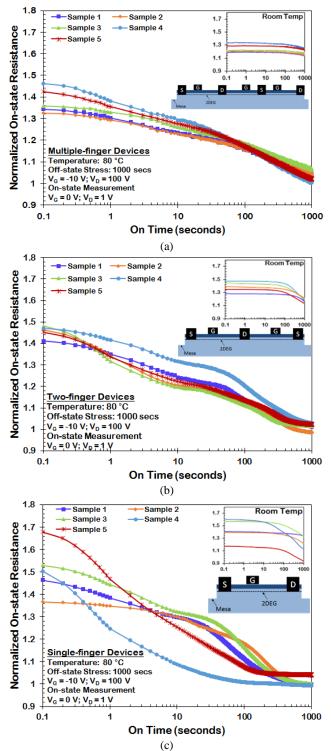

Fig. 2 shows the dynamic  $R_{\rm ON}$  measurements for the three device types, normalized to on-state resistance value before stress, at room temperature (inset) and 80°C. Several samples (five shown) of each kind have been measured to give an indication of the device-to-device variation. The roomtemperature measurements for the large devices in Fig. 2(a)show saturation at short times, with the measurement range extending over 4 decades in time insufficient to observe full recovery at that temperature after 1000s [31]. However, when comparing measurements collected at RT and 80°C, the data suggests that the broad distribution of time constants actually extends over at least 6 decades in time for all the tested devices, with very similar behavior seen in all devices. Pulsed measurements of comparable wafers reported in [29] showed similar magnitude dynamic  $R_{ON}$  4ms after stress. By contrast, the single-finger devices in Fig. 2(c) show a summation of a small number (two or three) of individual time-constant responses that are different in each device but with those time constants are distributed over the same 6 decades, indicating that the large multi-finger device behavior is a superposition of multiple small single-finger devices having discrete and distributed time constants. The two-finger devices shown in Fig. 2(b) show behavior that is intermediate between that seen in the single finger and the large devices. We note that pulse IV measurements at room temperature using 1µs ON, 1ms OFF pulses at  $V_{DS}$ =50V showed less than 10% current collapse on these devices.

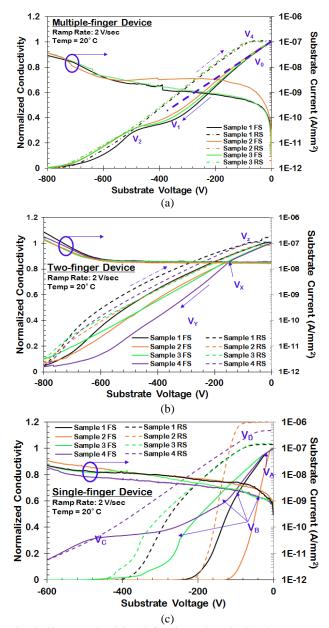

Complementary substrate-bias experiment results are shown in Fig. 3. Fig. 3a shows the 2DEG conductivity normalized to initial conductivity and the vertical leakage through the structure with respect to the substrate voltage for three large transistors. Ramping the substrate bias applied to the silicon resulted in a change in the electric field below the 2DEG and hence a change in 2DEG channel charge and  $I_D$ . The ramp rate was sufficiently slow for the silicon substrate to be in equilibrium and was considered as a metallic back

Fig. 2: On resistance after switching from off-state ( $V_{GS} = -10V$ ,  $V_{DS} = 100V$ ) to on-state ( $V_{GS} = 0$ ,  $V_{DS} = 1V$ ) of five samples of each of (a) multiple-finger, (b) two-finger and (c) single-finger devices at room temperature. The measurements are normalized to the on resistance before stress.

contact. As the device is ramped from 0V to -800V at 2V/s, initially the structures demonstrated a capacitive behavior corresponding to the epitaxial stack behaving as an insulator ie the current dropped linearly with voltage at a rate consistent with the expected Si back-gate extrapolated pinch-off voltage of ~ -730V, blue dashed line. Another way of looking at this

Fig. 3: Sheet conductivity (left axis) and vertical leakage current (right axis) of (a) three AlGaN/GaN multiple-finger power transistors, (b) four two-finger power transistors and (b) four single-finger power transistors during a ramp of the substrate bias from 0 to  $-V_{SUB}$  and back to 0V. The sheet conductivity measurements are normalized to the drain current before substrate at  $V_{SUB} = 0V$ . (FS: Forward Sweep = 0 to  $-V_{SUB}$ ; RS: Reverse Sweep =  $-V_{SUB}$  to 0V)

is that the back-gate transconductance (the rate of change of 2DEG conductivity with substrate voltage) was constant in this region. At  $V_0$ , the conductivity started decreasing at a faster rate before starting to saturate at voltage  $V_1$ . The transconductance increased again at  $V_2$  leading to pinch-off at around -800V. On the return sweep significant hysteresis was observed between -500V and 0V. The saturation observed at  $V_4$  led to a return to almost the same 2DEG conductivity at 0V as initially. This indicates almost no net stored charge after bias stress. The basic behavior is apparently very similar to that observed in [13] with positive charge storage between  $V_1$  and  $V_2$  and its neutralization

between  $V_4$  and 0V. The device to device variation for these large devices was minimal. In contrast to the multiple-finger devices, the single-finger transistors showed very high deviceto-device variability in their response despite very similar presubstrate stress channel carrier density across the wafer (<10% variation). Fig. 3c shows the substrate bias dependence for four indicative transistors illustrating the range of behaviors observed. All the devices started out with a capacitive behavior, but beyond voltage  $V_A$ , the back-gate transconductance increased significantly by a factor between 1× and 7× compared to the large devices. Most devices went directly to pinch-off at only-100 to -400V, but a small proportion showed a saturation and pinch-off more similar to that seen in the larger devices. On the return sweep, all the devices showed indications of positive charge storage after reaching 0V i.e. the normalized channel current had increased. The two-finger transistors (Fig. 3b), show an intermediate behavior between the multiple-finger and single-finger devices but were closer in behavior to that of the large devices. Most of these samples showed primarily capacitive behavior, while one of the samples (sample 4) had an increased back-gate transconductance at V<sub>X</sub>. On reverse sweep, all the samples showed only small amounts of positive charge storage after reaching 0V.

#### IV. DISCUSSION

The results shown in the previous section presents a contrasting picture between the dynamic  $R_{ON}$  and substrate bias experiments. While the dynamic  $R_{ON}$  experiments showed that the large multiple-finger device behavior is a superposition of multiple small single-finger devices, the substrate bias experiments showed a dramatic effect of device size.

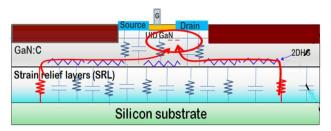

In the substrate bias experiment results, in all the devices, up to  $V_0$ ,  $V_A$ , or  $V_X$  at about -50 to -100V bias, capacitive coupling dominated, which in terms of the equivalent circuit shown in Fig. 1c indicates that resistive leakage is less than the displacement current of  $C_{TOT} dV_{SUB}/dt$ , where  $C_{TOT}$  is equal to the series capacitance of  $C_1$ ,  $C_2$  and  $C_3$ . However for the singlefinger devices there was a large increase in back-gate transconductance for  $|V_{SUB}| > |V_A|$  which varied from device to device. In terms of the 1D transport model presented in Fig. 1(c) the behavior can be explained in two ways: a) an increase in leakage through the SRL (drop in  $R_{SRL}$ ), which however was not observed in Fig. 3, or b) by an increase in the capacitance between the 2DEG and the Si, which cannot be explained with the 1D model. However, if we relax the 1D assumption, Fig. 4 shows how such an apparent leakage/capacitance increase could arise associated with the creation of a low resistance lateral leakage path. This lateral conductive path would leave  $C_1, C_2$  unchanged but would increase  $C_3$  and hence increase the back-gate transconductance. Given the device epitaxial structure (shown in Fig. 1(a)), a plausible candidate for this path is a 2DHG at the heterojunction at the top of the SRL. As the field across the epitaxial stack increases, thermally generated holes within the GaN:C layer will flow vertically leaving ionized acceptors in the GaN:C layer and forming a hole accumulation layer at the heterojunction. In this case, the threshold for its creation  $V_{SUB}$

Fig: 4: Schematic diagram showing the location of the 2DHG at the bottom of the GaN:C layer where the band-offset between the GaN:C and SRL creates a blocking junction. Widely spaced preferential leakage paths are shown through the SRL.

seems to be -50 to -100V. The inset to Fig. 4 shows schematically the resulting band diagram at the bottom of the C-doped GaN layer. The 2DHG can form provided the heterojunction is sufficiently high to form a blocking barrier, with the threshold voltage,  $V_{T2DHG}$ , for formation of the 2DHG determined by polarization charge and compensating donor (not acceptor) density. Note that  $V_{\text{T2DHG}}$  has no first order dependence on the carbon acceptor density as long as it is greater than the donor density. The implantation used for isolation only damages about the top hundred nanometers of the structure, suppressing the 2DEG channel, but has no impact below this, meaning that the 2DHG can extend outside the active device area and in principle an unrestricted spread of the 2DHG could occur into the implant isolated area extending over the entire wafer. This allows the original assumption of a 1D current flow to be relaxed, and results in an increase in the SRL capacitance,  $C_3$ , and hence an increase in the back-gate transconductance, as was observed especially for the singlefinger devices. In practice, the implied increase in  $C_3$  is limited and different in each device, suggesting that the distance that the holes flow laterally is also limited and different for each device. This distance can be very roughly estimated based on the observation that the back-gate transconductance of the single-finger devices varied between  $1 \times$  and  $7 \times$  larger than the value for the large device. Hence, and since  $C_1, C_2 >> C_3$ , it can be inferred that the area over which the holes spread is roughly between  $1 \times$  and  $7 \times$  larger than the single-finger transistor isolated area. That active area is  $5000\mu m^2$  so the area would increase up to 35,000µm<sup>2</sup> or a circle of diameter ~200µm. So, charge flows up to 50-100µm outside the isolated device area. To explain the variability seen in Fig. 3c, it can be postulated that the leakage through the SRL is dominated by leakage along discrete extended defects whose separation is comparable to, or larger than the isolated area of the small single-finger devices. It is now well known that leakage in GaN P-N diodes occurs along dislocations with high screw component [32] and here we assume that a small proportion of those paths dominates the leakage. These randomly separated discrete leakage paths with separation ~100µm would provide a source of electrons which could neutralize the spreading 2DHG and pin its potential closer to the Si substrate as shown schematically in Fig. 4. So every individual small single-finger device would have a different spread of 2DHG around that device giving rise to the device-todevice variation. This increased area and hence SRL capacitance,  $C_3$ , will result in an increase in the field dropped in the UID GaN layer and result in the early pinch-off of the device (as seen in Fig. 3c). The positive charge seen after the return ramp to 0V would correspond to the hole charge stored

Fig. 5: Schematic representation of the hole transport path during the on-state recovery transient. The negative ionized carbon acceptor charge exposed during the off-state stress is circled [24], as is the single extended-defect leakage path which allows holes to flow from the contacts.

outside the isolated area flowing back into the active device. It is important to note that the current flowing along each vertical leakage path needed to pin the 2DHG potential is very small and only needs to exceed the displacement current which for our ramprate is only ~0.3pA.

In the case of the multi-finger large devices, the maximum lateral hole flow distance outside the active area would be much smaller than the mm-scale active device dimension so it would apparently behave as a 1D structure, with the lateral spreading effect of the 2DHG having little impact. We assume that most of the threading vertical leakage paths would intersect an Ohmic contact and would act as a resistive potential divider between the contact and substrate potentials, and so would not have any strong impact on the potential of the 2DHG. Hence in the large devices, other features of the ramps seen in Fig. 3(a) can be interpreted using the straightforward 1D transport model of Fig. 1c employed in [17]. So the positive charge storage in the buffer seen between  $V_1$  and  $V_2$  can be attributed to hole leakage from the 2DEG channel via a non-Ohmic band-to-band leakage path possibly by a trap-assisted- tunneling process although other possibilities exist [33, 34]. For voltages above  $|V_2|$  where the leakage through the SRL exceeds the substrate ramp induced displacement current, leakage could occur more uniformly by a mechanism such as electron tunneling from the Si substrate, however it is more likely that the preferred path would be along extended defects, including those leakage paths inferred to be present from the measurements on single-finger devices.

The situation for the dynamic  $R_{ON}$  measurement is quite different from the substrate ramp, and the impact of the 2DHG is likely to be small. When the device is biased in the OFF state positive and negatively charged regions will form in the buffer in response to the vertical and lateral electric fields [30]. The key difference from the substrate ramp is that in OFF state the source contacts will act as a sink for any free holes since there is a forward biased diode between the GaN:C and that contact. Depending on the size of the leakage path between the drain and the GaN:C layer, holes may flow laterally outside the active area in the case of the single finger device, however in general any exposed positive charge in the buffer is likely to be principally in the form of ionized donor charge. When the device is switched to the ON-state, the recovery transient shown in Fig. 2 results from the neutralization of the stored negative charge located between gate and drain (and which is responsible for the dynamic  $R_{ON}$ ), presumably as ionized carbon acceptors. The carbon doped layer is p-type so the process of neutralizing

the excess ionized acceptors will require lateral hole transport within that layer [13, 17, 29]. We propose that in this process variant the large device-to-device variation in the on-state recovery transient observed in the single-finger devices results from the wide variation in distance that the holes have to drift/diffuse from the vertical leakage paths that will act as sources of holes in the ON-state. Fig. 5 shows schematically the transport process that would be involved in the recovery transient when there are two extended-defect leakage paths located outside the active area. The different distances that the holes must flow from a preferential leakage path to the ionized acceptors would result in a different recovery time associated with each leakage path and provide an explanation for the device-to-device variation observed. For large devices, the leakage paths would almost all reside within the device active area but would still provide the source of holes in the ON-state with superposition resulting in the small device-to-device variation.

## V. CONCLUSIONS

This work demonstrates size and geometry dependent dispersion in power transistors. We interpret this as showing clear evidence for a lateral transport mechanism outside the device isolated area in GaN:C doped HEMTs. We propose that the device-to-device variation is due to a combination of widely spaced (100µm scale separation) leakage paths through the structure and lateral transport from those paths to trapping sites. A 2DHG is present in the buffer, created only when there is an applied vertical field, that augments the lateral charge transport within the carbon doped GaN layer. The spread of the 2DHG outside the active area of the device strongly affects the result of substrate ramp measurements producing major differences between single and multifinger devices. In dynamic RON recovery measurements, single-finger devices show large device-to-device variation, with multifinger devices showing a small variation with the transient comprising the superposition of the recovery transient of multiple small devices. It is clear, that understanding dynamic  $R_{ON}$  dispersion can require not only a full understanding of the point defect deep acceptor and donor density together with any sheet charge layers within the epitaxy, but also the distribution and leakage properties of the extended defects.

#### ACKNOWLEDGEMENTS

The authors would like to thank the members of the Materials and Devices for Energy and Communication group and the Centre for Device Thermography and Reliability (CDTR) at the University of Bristol for valuable discussion.

#### REFERENCES

- B. J. Baliga, "Gallium nitride devices for power electronic applications," Semicond. Sci. Technol. Vol. 28, p. 074011, 2013.

- [2] M. Ishida, T. Ueda, T. Tanaka, and D. Ueda, "GaN on Si technologies for power switching devices," *IEEE Trans. Electron Devices*, vol. 60, pp. 3053–3059, 2013.

- [3] E. Bahat-Treidel, F. Brunner, O. Hilt, E. Cho, J. W€urfl, and G. Tr€ankle, "AlGaN/GaN/GaN:C back-barrier HFETs with breakdown voltage of over 1 kV and low RON × A," *IEEE Trans. Electron Devices*, vol. 57, pp. 3050–3058, 2010.

- [4] R. Chu, A. Corrion, M. Chen, R. Li, D. Wong, D. Zehnder, B. Hughes, and K. Boutros, "1200-V normally off GaN-on-Si field-effect transistors

with low dynamic on-resistance," *IEEE Electron Device Lett.* 32, 632–634, 2011.

- [5] J. Würfl, E. Bahat-Treidel, F. Brunner, M. Cho, O. Hilt, A. Knauer, P. Kotara, O. Krueger, M. Weyers, and R. Zhytnytska, "Device breakdown and dynamic effects in GaN power switching devices: dependencies on material properties and device design," *ECS Trans.* 50, 211–222 (2013).

- [6] J. Würfl, O. Hilt, E. Bahat-Treidel, R. Zhytnytska, P. Kotara, F. Brunner, O. Krueger, and M. Weyers, "Techniques towards GaN power transistors with improved high voltage dynamic switching properties," *IEEE Int. Elec. Dev. Meeting (IEDM)*, 2013.

- [7] S. C. Binari, P. B. Klein, and T. E. Kazior, "Trapping effects in GaN and SiC microwave FETs," *Proc. IEEE*, vol. 90, no. 6, pp. 1048–1058, Jun. 2002.

- [8] C. Poblenz, P. Waltereit, S. Rajan, S. Heikman, U. K. Mishra, and J. S. Speck, "Effect of carbon doping on buffer leakage in AlGaN/GaN high electron mobility transistors", *J. Vac. Sci. Technol.*, *B* 22(3), 1145 (2004).

- [9] E. Bahat-Treidel, O. Hilt, F. Brunner, V. Sidorov, J. Würfl, and G. Tränkle, "AlGaN/GaN/AlGaN DH-HEMTs breakdown voltage enhancement using multiple grating field plates (MGFPs)," *IEEE Trans. Electron Devices* 57, 1208–1216 (2010).

- [10] M. J. Uren, J. Möreke, and M. Kuball, "Buffer design to minimize current collapse in GaN/AlGaN HFETs," *IEEE Trans. Electron Devices*, vol. 59, no. 12, pp. 3327–3333, Dec. 2012.

- [11] S. Stoffels, M. Zhao, R. Venegas, P. Kandaswamy, S. You, T. Novak, Y. Saripalli, M. V. Hove, and S. Decoutere, "The physical mechanism of dispersion caused by AlGaN/GaN buffers on Si and optimization for low dispersion," *IEEE Elec. Dev. Meeting*, 2015, pp. 911-914.

- [12] J. L. Lyons, A. Janotti, and C. G. Van de Walle, "Carbon impurities and the yellow luminescence in GaN", *Appl. Phys. Lett.* 97(15), 152108 (2010).

- [13] M. J. Uren, M. Silvestri, M. Cäsar, G. A. M. Hurkx, J. A. Croon, J. Šonský, and M. Kuball, "Intentionally Carbon-Doped AlGaN/GaN HEMTs: The Necessity for Vertical Leakage Paths," *IEEE Elec. Dev. Lett.*, vol. 35, pp. 327-329, 2014.

- [14] M. Marso, M. Wolter, P. Javorka, P. Kordos, and H. Luth, "Investigation of buffer traps in an AlGaN/GaN/Si high electron mobility transistor by backgating current deep level transient spectroscopy," *Appl. Phys. Lett.*, vol. 82, pp. 633-635, Jan 27 2003.

- [15] S. Yang, C. H. Zhou, Q. M. Jiang, J. B. Lu, B. L. Huang, and K. J. Chen, "Investigation of buffer traps in AlGaN/GaN-on-Si devices by thermally stimulated current spectroscopy and back-gating measurement," *Appl. Phys. Lett.*, vol. 104, p. 013504, Jan 2014.

- [16] C. H. Zhou, Q. M. Jiang, S. Huang, and K. J. Chen, "Vertical Leakage/Breakdown Mechanisms in AlGaN/GaN-on-Si Devices," *IEEE Elec. Dev. Lett.*, vol. 33, pp. 1132-1134, Aug 2012.

- [17] M. J. Uren, M. Cäsar, M. A. Gajda, and M. Kuball, "Buffer Transport Mechanisms in Intentionally Carbon Doped GaN Heterojunction Field Effect Transistors" *Appl. Phys. Lett.*, vol. 104, p. 263505, 2014.

- [18] A. Pooth, M. J. Uren, M. Casar, T. Martin, and M. Kuball, "Charge movement in a GaN-based hetero-structure field effect transistor structure with carbon doped buffer under applied substrate bias", *J. Appl. Phys.*, vol. 118, p. 215701, 2015.

- [19] H. Yacoub, D. Fahle, M. Eickelkamp, A. Wille, C. Mauder, M. Heuken, H. Kalisch, and A. Vescan, "Effect of stress voltage on the dynamic buffer response of GaN-on-silicon transistors," *J. Appl. Phys.*, vol. 119, p. 135704, 2016.

- [20] M. J. Uren, M. Silvestri, M. Cäsar, J. W. Pomeroy, G. A. M. Hurkx, J. A. Croon, J. Šonský, and M. Kuball, "Need for Defects in Floating-Buffer AlGaN/GaN HEMTs," *CS-MANTECH*, Denver, 2014, pp. 317-319.

- [21] P. Moens, A. Banerjee, A. Constant, P. Coppens, M. Caesar, Z. Li, S. Vandeweghe, F. Declercq, B. Padmanabhan, W. Jeon, J. Guo, A. Salih, M. Tack, M. Meneghini, S. Dalcanale, A. Tajilli, G. Meneghesso, E. Zanoni, M. Uren, I. Chatterjee, S. Karboyan, and M. Kuball, "(Invited) Intrinsic Reliability Assessment of 650V Rated AlGaN/GaN Based Power Devices: An Industry Perspective," *ECS Transactions*, vol. 72, pp. 65-76, 2016.

- [22] B. Jogai, "Parasitic Hole Channels in AlGaN/GaN Heterojunction Structures," *Phys. Stat. Sol.* (b), vol. 233, pp. 506-518, 2002.

- [23] S. Acar, S. B. Lisesivdin, M. Kasap, S. Özçelik, and E. Özbay, "Determination of two-dimensional electron and hole gas carriers in AlGaN/GaN/AlN heterostructures grown by Metal Organic Chemical Vapor Deposition," *Thin Solid Films*, vol. 516, pp. 2041-2044, 2/29/ 2008.

- [24] T. Zimmermann, M. Neuburger, M. Kunze, I. Daumiller, A. Denisenko, A. Dadgar, A. Krost, and E. Kohn, "P-channel InGaN-HFET structure

based on polarization doping," IEEE Elec. Dev. Lett., vol. 25, pp. 450-452, 2004.

- [25] A. Nakajima, Y. Sumida, M. H. Dhyani, H. Kawai, and E. M. S. Narayanan, "High Density Two-Dimensional Hole Gas Induced by Negative Polarization at GaN/AlGaN Heterointerface," *Applied Physics Express*, vol. 3, p. 3, 2010.

- [26] H. Hahn, B. Reuters, S. Geipel, M. Schauerte, F. Benkhelifa, O. Ambacher, H. Kalisch, and A. Vescan, "Charge balancing in GaN-based 2-D electron gas devices employing an additional 2-D hole gas and its influence on dynamic behaviour of GaN-based heterostructure field effect transistors," J. Appl. Phys., vol. 117, p. 8, Mar 2015.

- [27] P. Moens, C. Liu, A. Banerjee, P. Vanmeerbeek, P. Coppens, H. Ziad, A. Constant, Z. Li, H. De Vleeschouwer, J. Roig-Guitart, P. Gassot, F. Bauwens, E. De Backer, B. Padmanabhan, A. Salih, J. Parsey, and M. Tack, "An industrial process for 650V rated GaN-on-Si power devices using in-situ SiN as a gate dielectric," *IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD)*, 2014, pp. 374-377.

- [28] P. Moens, P. Vanmeerbeek, A. Banerjee, J. Guo, C. Liu, P. Coppens, A. Salih, M. Tack, M. Caesar, M. J. Uren, M. Kuball, M. Meneghini, G. Meneghesso, E. Zanoni, "On the Impact of Carbon-Doping on the Dynamic Ron and Off-state Leakage Current of 650V GaN Power Devices", *IEEE ISPSD*, May 2015.

- [29] P. Moens, A. Banerjee, M. J. Uren, M. Meneghini, S.Karboyan, I. Chatterjee et al. "Impact of buffer leakage on intrinsic reliability of 650V AlGaN/GaN HEMTs", *IEDM Tech. Digest*, Dec 2015.

- [30] M. J. Uren, M. Caesar, S. Karboyan, P. Moens, P. Vanmeerbeek, and M. Kuball, "Electric Field Reduction in C-Doped AlGaN/GaN on Si High Electron Mobility Transistors," *IEEE Elec. Dev. Lett.*, vol. 36, pp. 826-828, 2015.

- [31] S. Karboyan, M. J. Uren, S. Martin Horcajo, J. W. Pomeroy, I. Chatterjee, P. Moens, A. Banerjee, M. Caesar, and M. Kuball, "Dynamic-Ron in Small and Large C-doped AlGaN/GaN-on-Si HEMTs", Proc. CS MANTECH 2016, Miami, USA, May 2016.

- [32] Y. Zhang, H. Y. Wong, M. Sun, S. Joglekar, L. Yu, N. A. Braga, R. V. Mickevicius, and T. Palacios, "Design space and origin of off-state leakage in GaN vertical power diodes," *IEEE International Electron Devices Meeting (IEDM)*, 2015, pp. 35.1.1-35.1.4.

- [33] D. S. Li, H. Chen, H. B. Yu, H. Q. Jia, Q. Huang, and J. M. Zhou, "Dependence of leakage current on dislocations in GaN-based lightemitting diodes", J. Appl. Phys. 96(2), 1111–1114 (2004).

- [34] X. A. Cao, J. A. Teetsov, F. Shahedipour-Sandvik, and S. D. Arthur, "Microstructural origin of leakage current in GaN/InGaN light-emitting diodes", J. Cryst. Growth 264(1–3), 172–177 (2004).