# **CRANFIELD UNIVERSITY**

# **TAO FENG**

# ETHERNET-BASED AFDX SIMULATION AND TIME DELAY ANALYSIS

# SCHOOL OF AEROSPACE, TRANSPORT AND MANUFACTURING

MSc by Research Thesis Academic Year: 2015 - 2016

Supervisor: Dr Huamin Jia February 2016

#### **CRANFIELD UNIVERSITY**

# SCHOOL OF AEROSPACE, TRANSPORT AND MANUFACTURING

MSc by Research Thesis

Academic Year 2015 - 2016

**TAO FENG**

# ETHERNET-BASED AFDX SIMULATION AND TIME DELAY ANALYSIS

Supervisor: Dr Huamin Jia February 2016

© Cranfield University 2016. All rights reserved. No part of this publication may be reproduced without the written permission of the copyright owner.

### **ABSTRACT**

Nowadays, new civilian aircraft have applied new technology and the amount of embedded systems and functions raised. Traditional avionics data buses design can't meet the new transmission requirements regarding weight and complexity due to the number of needed buses. On the other hand, Avionics Full Duplex Switched Ethernet (AFDX) with sufficient bandwidth and guaranteed services is considered as the next generation of avionics data bus. One of the important issues in Avionics Full Duplex Switched Ethernet is to ensure the data total time delay to meet the requirements of the safety-critical systems on aircraft such as flight control system.

This research aims at developing an AFDX time delay model which can be used to analyse the total time delay of the AFDX network. By applying network calculus approach, both  $(\sigma,\rho)$  model and Generic Cell Rate Algorithm (GCRA) model are introduced. For tighter time-delay result, GCRA model is applied. Meanwhile, the current AFDX network simulation platform, FACADE, will be enhanced by adding new functions. Moreover, avionics application simulation modules are developed to exchange data with FACADE. The total time delay analysis will be performed on the improved FACADE to validate this AFDX network simulation platform in several scenarios. Moreover, each scenario is appropriated to study the association between total time delay performance and individual variable.

The results from updated FACADE reflect the correlation between total time delay and certain variables. Larger BAG and more switches between source and destination end systems introduce larger total time delay while  $L_{\text{max}}$  could also affect the total time delay. However, the results illustrate that the total time delays from updated FACADE are much larger than GCRA time delay model which could up to 10 times which indicates that this updated FACADE needs further improvement.

#### Keywords:

Avionics Full-Duplex Switched Ethernet, Network Calculus, Arrival Curve, Service Curve, GCRA, Total Time Delay

## **ACKNOWLEDGEMENTS**

Firstly, I would like to thank my supervisor, Dr. Huamin Jia, for his constant support and guidance to my research. Without his advice, my research could not be completed successfully.

Some people help me with my research. I would like to express my appreciation to Mr. Baochua Wu, Mr. Qingming Song, Mr. Yu Lu, Mr. Chaoqun Chen, Mr. Jian Zhang, Mr. Dexin Xu, Mr. Yang Guo, Ms. Xiaojie Zeng, Ms. Lijuan Sun, Ms. Wenjing Wang, for their generous help either on study and living during the research.

I would like to thank COMAC (Commercial Aircraft Corporation of China) for giving me this opportunity to undertake this research, as well as the constant support and help. Special thanks also to Cranfield University, for giving me the chance to promote myself.

Finally, I deeply appreciate my wife, my family and friends for having supported me at all the times.

# **TABLE OF CONTENTS**

| ABSTRACT                                                             | i     |

|----------------------------------------------------------------------|-------|

| ACKNOWLEDGEMENTS                                                     | iii   |

| LIST OF FIGURES                                                      | . vii |

| LIST OF TABLES                                                       | X     |

| 1 INTRODUCTION                                                       | 1     |

| 1.1 Background and Motivation                                        | 1     |

| 1.2 Research Objectives                                              | 2     |

| 1.3 Thesis Structure                                                 | 3     |

| 1.4 Summary                                                          |       |

| 2 LITERATURE REVIEW                                                  |       |

| 2.1 AFDX Introduction                                                | 7     |

| 2.1.1 End System                                                     | 8     |

| 2.1.2 Virtual Links                                                  | 10    |

| 2.1.3 AFDX Switch                                                    | 12    |

| 2.1.4 Latency and Jitter                                             |       |

| 2.1.5 Network Topology                                               | 14    |

| 2.2 AFDX Delay Research Techniques                                   |       |

| 2.3 AFDX Simulation Techniques                                       |       |

| 2.3.1 Real-time Software AFDX Network Simulation                     | 18    |

| 2.3.2 Programming Software AFDX Network Simulation                   |       |

| 2.4 Summary                                                          |       |

| 3 Network Calculus Model and AFDX Delay Analysis                     |       |

| 3.1 Data Flow Features in Data Network Concepts Cumulative Functions |       |

| 3.2 Virtual Delay                                                    |       |

| 3.3 Arrival Curves                                                   |       |

| 3.3.1 Definition of Arrival Curve                                    |       |

| 3.3.2 Affine Arrival Curves                                          |       |

| 3.3.3 Stair Functions as Arrival Curves                              |       |

| 3.3.4 Leaky Bucket and Generic Cell Rate Algorithm                   |       |

| 3.4 Service Curves                                                   |       |

| 3.5 Network Delay Bound                                              |       |

| 3.6 AFDX Network Time Delay Analysis                                 |       |

| 3.6.1 AFDX Network Time Delay Model                                  |       |

| 3.6.2 AFDX Traffic and Service Model                                 |       |

| 3.6.3 End-to-End Delay of GCRA Model                                 |       |

| 3.7 Total Time Delay Analysis                                        |       |

| 3.8 Summary                                                          | 48    |

| 4 DEVELOPMENT OF FACADE AND AVIONICS APPICATION                      |       |

| SIMULATION PLATFORM                                                  |       |

| 4.1 The Framework of FACADE                                          | 49    |

| 4.2 Data Exchange Behaviour                                   | 52        |

|---------------------------------------------------------------|-----------|

| 4.3 Detailed Design of Avionics Application Simulation Module | s54       |

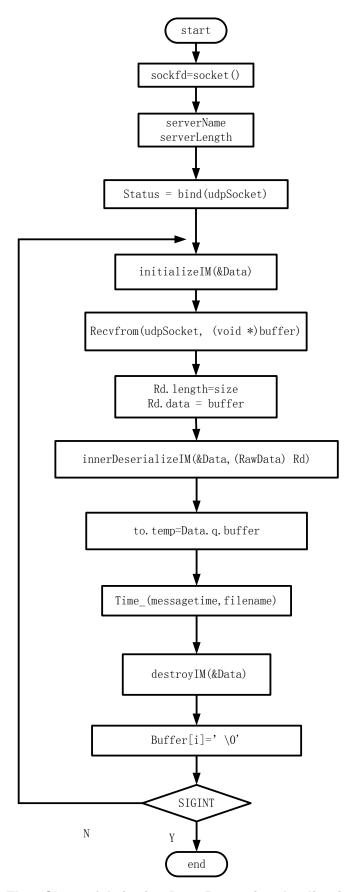

| 4.3.1 Avionics Data Transmission Application Module           | 54        |

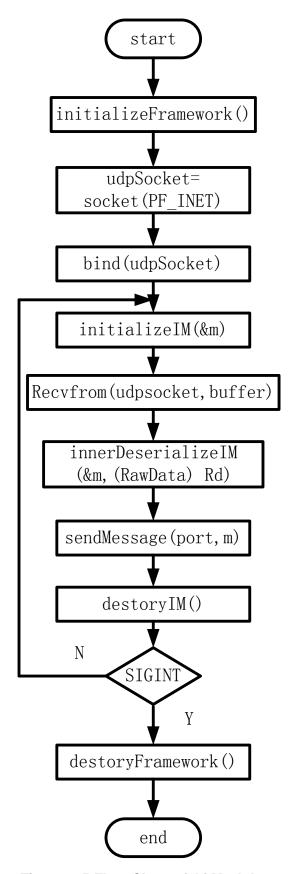

| 4.3.2 Avionics Data Reception Application Module              | 58        |

| 4.4 Detailed Function Design of FACADE Platform               | 61        |

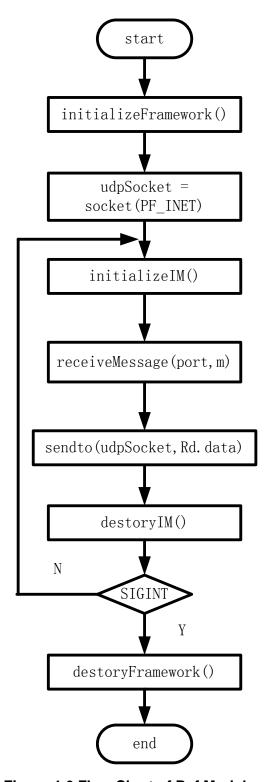

| 4.4.1 Af Module                                               | 61        |

| 4.4.2 Raf Module                                              | 63        |

| 4.4.3 CreateDB Module                                         | 65        |

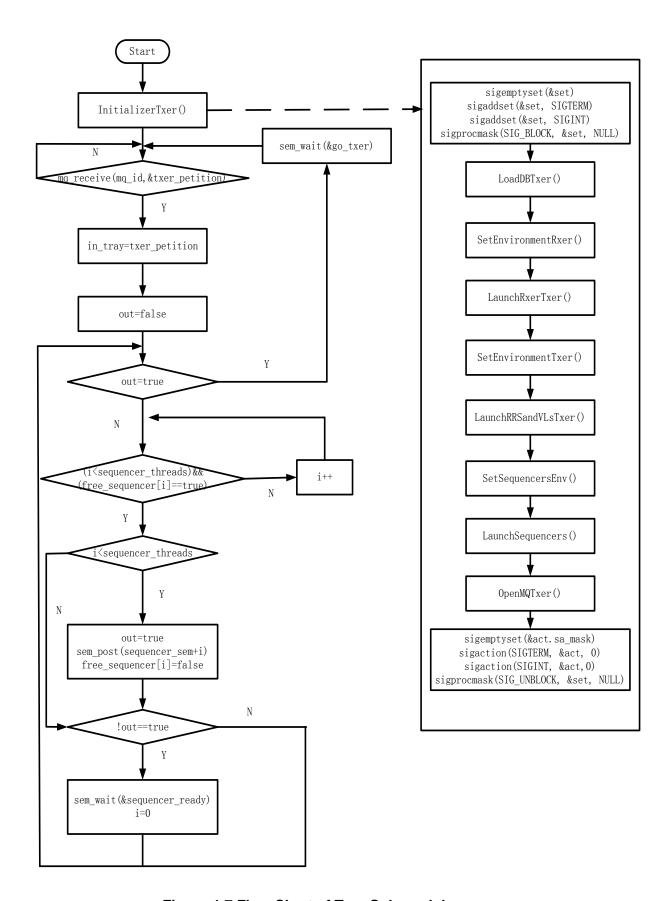

| 4.4.4 FACADE Module                                           | 66        |

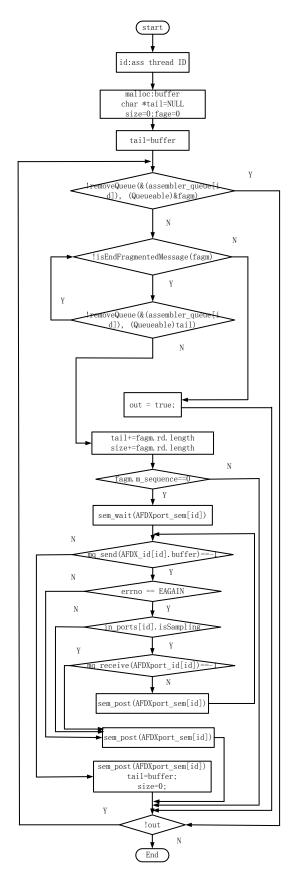

| 4.5 Execution of Simulation Platform                          | 84        |

| 4.5.1 Execution of FACADE Platform                            | 84        |

| 4.5.2 Execution of Avionics Application Simulation Modules    | 85        |

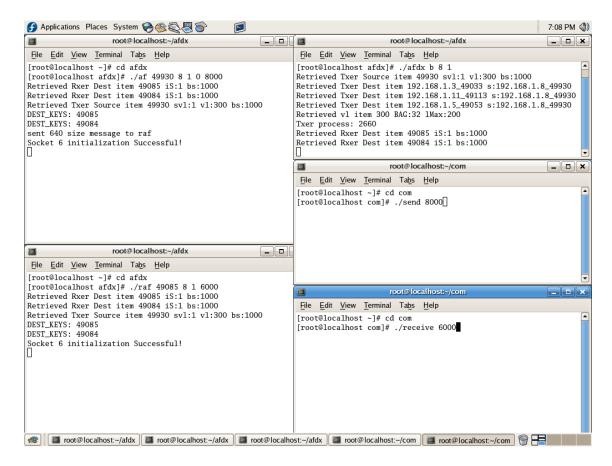

| 4.6 Validation of Platform                                    | 85        |

| 4.7 Summary                                                   | 87        |

| 5 EXPERIMENT DESIGN AND EXECUTION                             | 89        |

| 5.1 Introduction                                              | 89        |

| 5.2 Time Synchronization                                      | 90        |

| 5.3 Experiment Detailed Design and Total Time Delay Calculu   | s 92      |

| 5.3.1 Experiment 1(Variable L <sub>max</sub> )                | 92        |

| 5.3.2 Experiment 2 (Variable BAG)                             | 94        |

| 5.3.3 Experiment 3 (Variable Amount of Destination End So     | urces) 95 |

| 5.3.4 Experiment 4 (Variable Amount of Virtual Links)         | 97        |

| 5.3.5 Experiment 5 (Variable Amount of Traverse Switches)     | 99        |

| 5.4 Experiment States                                         | 100       |

| 5.5 Experiment Data Analysis                                  | 102       |

| 5.5.1 Normal Distribution Test                                | 102       |

| 5.5.2 Experiment Data Analysis                                | 105       |

| 5.6 Summary                                                   | 120       |

| 6 CONCLUSIONS AND FUTURE WORK                                 | 121       |

| 6.1 Introduction                                              | 121       |

| 6.2 Conclusions                                               | 122       |

| 6.3 Future Work                                               | 123       |

| REFERENCES                                                    | 126       |

# **LIST OF FIGURES**

| Figure 1-1 Thesis Structure                                            | 5    |

|------------------------------------------------------------------------|------|

| Figure 2-1 Illustration of AFDX Network                                | 8    |

| Figure 2-2 Source End System                                           | 9    |

| Figure 2-3 Unregulated and Regulated Flow                              | 9    |

| Figure 2-4 Destination End System                                      | . 10 |

| Figure 2-5 AFDX Network Packet Format                                  | . 11 |

| Figure 2-6 Chart of Virtual Link                                       | . 11 |

| Figure 2-7 AFDX Switch                                                 | . 12 |

| Figure 2-8 AFDX Star Topology                                          | . 15 |

| Figure 2-9 The AFDX End System and Switch System Simulation Model [26] | 19   |

| Figure 2-10 The Architecture of The Experiments [33]                   | . 20 |

| Figure 2-11 MAST Toolset Environment [34]                              | . 21 |

| Figure 2-12 TrueTime Simulation Model [4]                              | . 22 |

| Figure 3-1 Cumulative Function in Network                              | . 24 |

| Figure 3-2 Input and Output Function [53]                              | . 25 |

| Figure 3-3 Horizontal Deviation                                        | . 27 |

| Figure 3-4 Arrival Curve [53]                                          | . 28 |

| Figure 3-5 Leaky Bucket Controller [53]                                | . 30 |

| Figure 3-6 Service Curve [53]                                          | . 34 |

| Figure 3-7 The Horizontal Deviation Between f and g                    | . 35 |

| Figure 3-8 AFDX Network Time Delay                                     | . 35 |

| Figure 3-9 End System Delay Model                                      | . 36 |

| Figure 3-10 AFDX Switch Time Delay Model                               | . 37 |

| Figure 3-11 Virtual Link Model Cross End System and Switch             | . 39 |

| Figure 3-12 Delay Bound For Single Virtual Link Cross Scheduler        | . 40 |

| Figure 3-13 Switch Scheduling [39]                                     | . 43 |

| Figure 4-1 Architecture of FACADE                                      | . 49 |

| Figure 4-2 Simulation Platform Data Exchange Behaviour                 | . 54 |

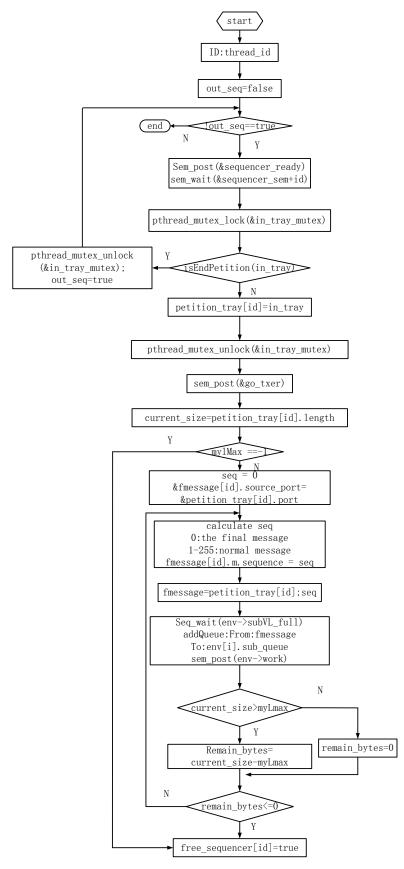

| Figure 4-3 Flow Chart of Avionics Data Transmission Application Modu  | ıle 57 |

|-----------------------------------------------------------------------|--------|

| Figure 4-4 Flow Chart of Avionics Data Reception Application Module.  | 60     |

| Figure 4-5 Flow Chart of Af Module                                    | 62     |

| Figure 4-6 Flow Chart of Raf Module                                   | 64     |

| Figure 4-7 Flow Chart of Txer Sub module                              | 69     |

| Figure 4-8 Flow Chart of Sequencer Sub module                         | 72     |

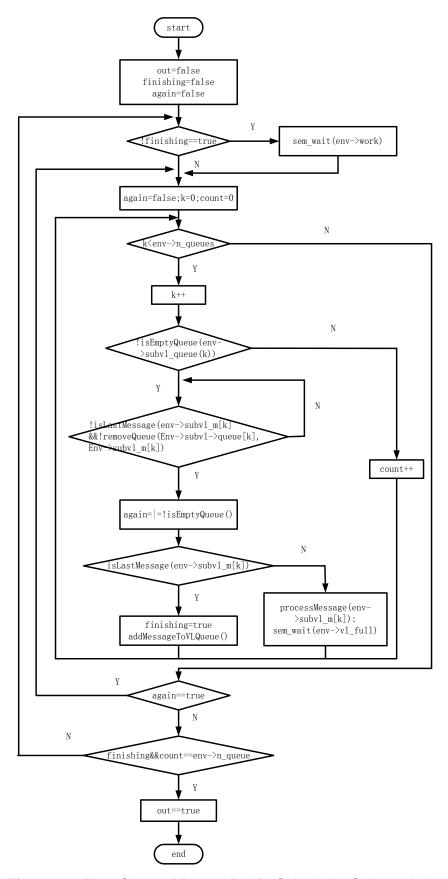

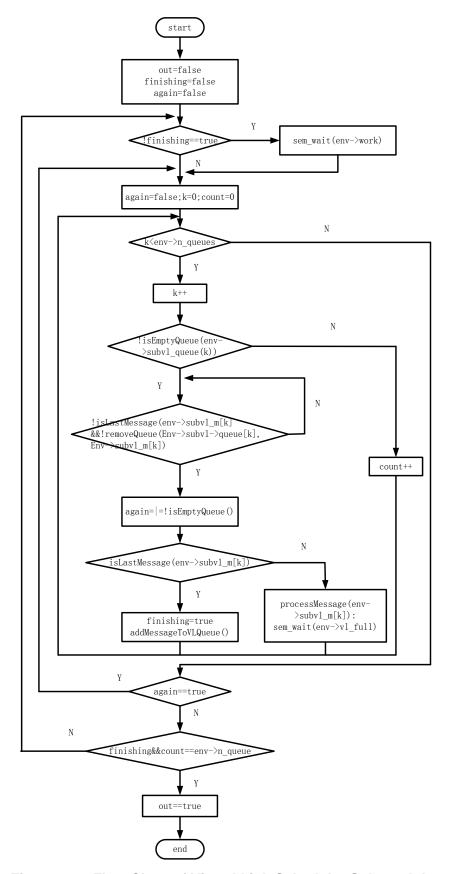

| Figure 4-9 Flow Chart of Round Robin Scheduler Sub module             | 74     |

| Figure 4-10 Flow Chart of Virtual Link Scheduler Sub module           | 76     |

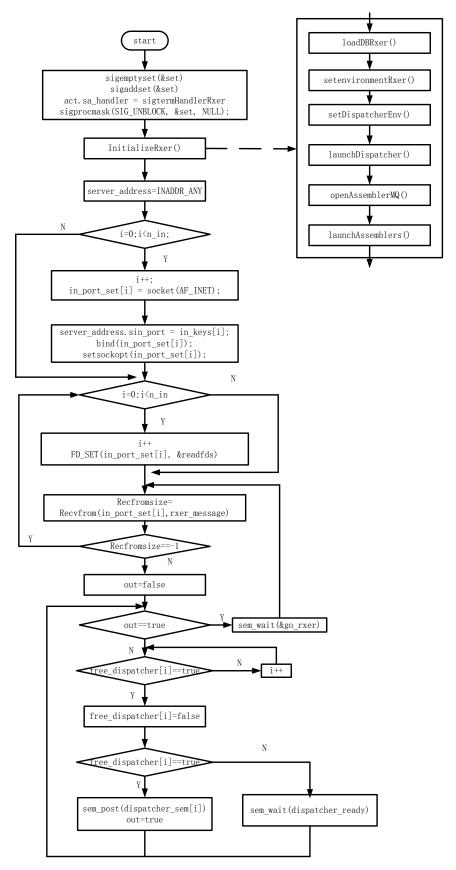

| Figure 4-11 Flow Chart of Rxer Sub module                             | 79     |

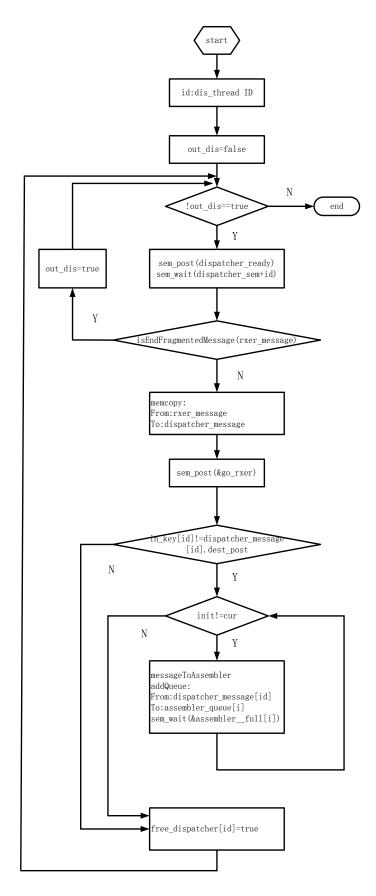

| Figure 4-12 Flow Chart of Dispatcher Sub module                       | 81     |

| Figure 4-13 Flow Chart of Assembler Sub module                        | 83     |

| Figure 4-14 Preparation of FACADE and Avionics Application 9 platform |        |

| Figure 4-15 Data Exchange of FACADE and Avionics Application 9        |        |

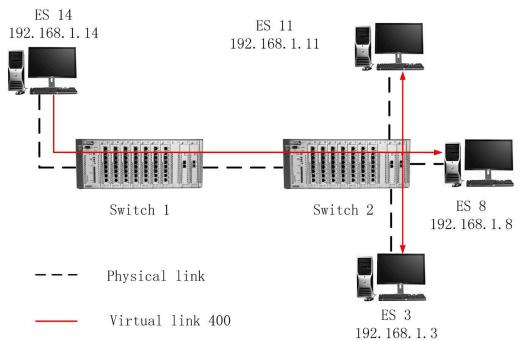

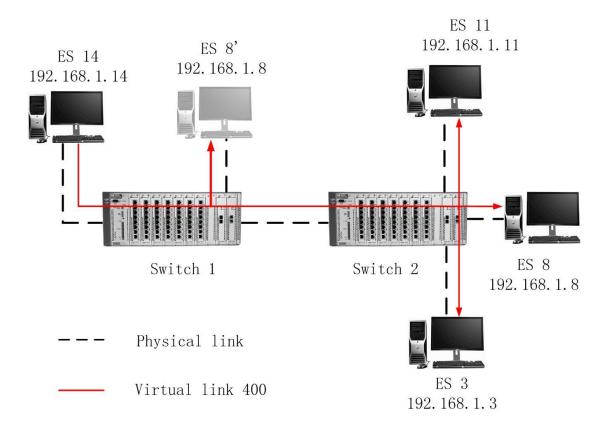

| Figure 5-1 Diagram of Experiment 1                                    | 93     |

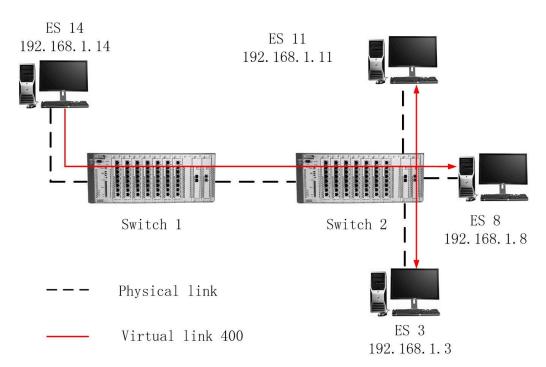

| Figure 5-2 Diagram of Experiment 2                                    | 95     |

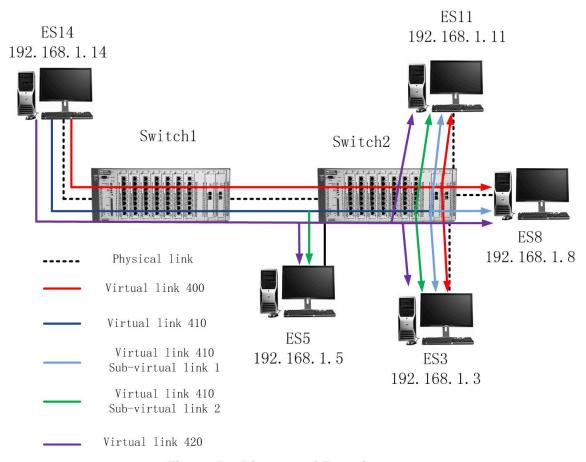

| Figure 5-3 Diagram of Experiment 3                                    | 97     |

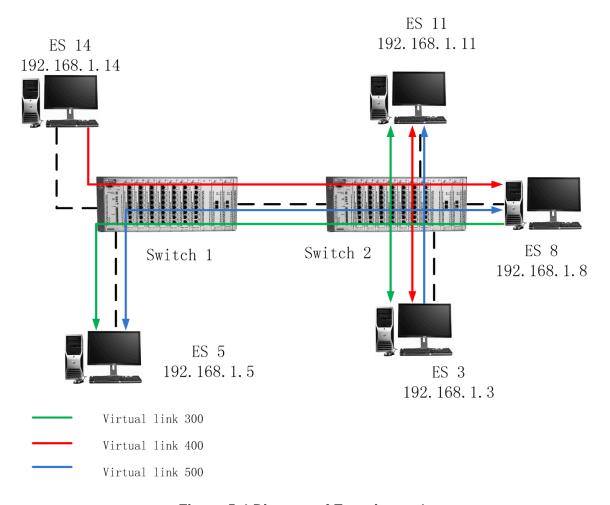

| Figure 5-4 Diagram of Experiment 4                                    | 98     |

| Figure 5-5 Diagram of Experiment 5                                    | 99     |

| Figure 5-6 Normality Test Result of Experiment 1                      | 102    |

| Figure 5-7 Normality Test Result of Experiment 2                      | 103    |

| Figure 5-8 Normality Test Result of Experiment 3                      | 103    |

| Figure 5-9 Normality Test Result of Experiment 4                      | 104    |

| Figure 5-10 Normality Test Result of Experiment 5                     | 104    |

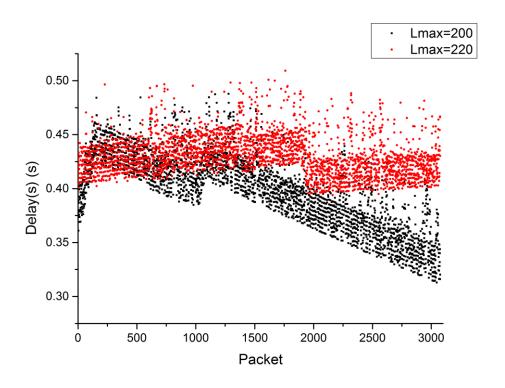

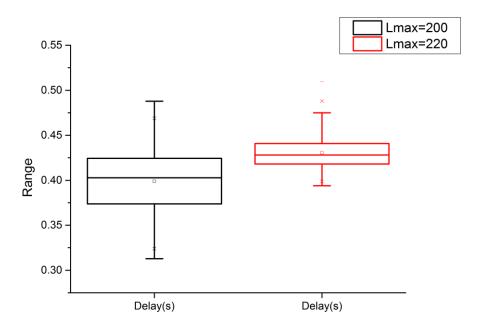

| Figure 5-11 Scatter Chart of Experiment 1                             | 106    |

| Figure 5-12 Box Chart of Experiment 1                                 | 107    |

| Figure 5-13 Statistics Data of Experiment 1                           | 107    |

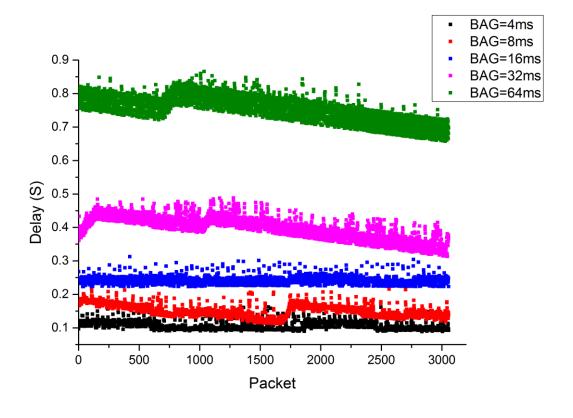

| Figure 5-14 Scatter Chart of Experiment 2                             | 108    |

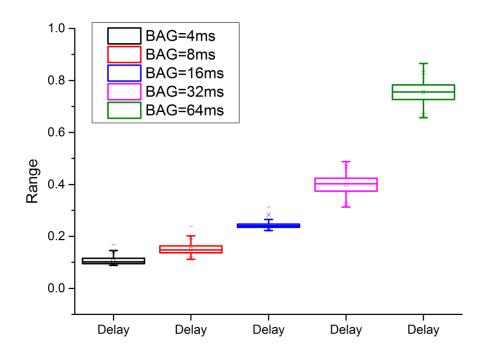

| Figure 5-15 Box Chart of Experiment 2                                 | 110    |

| Figure 5-16 Statistics Data of Experiment 2 | 110 |

|---------------------------------------------|-----|

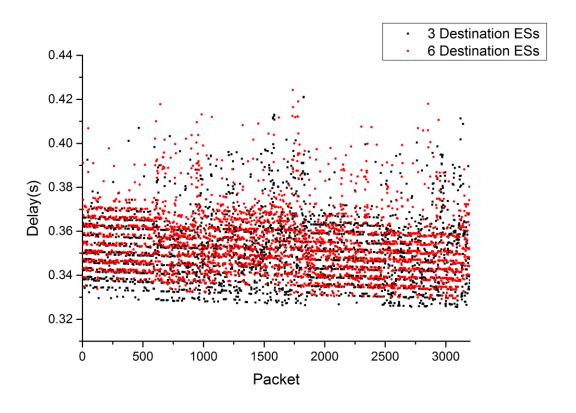

| Figure 5-17 Scatter Chart of Experiment 3   | 112 |

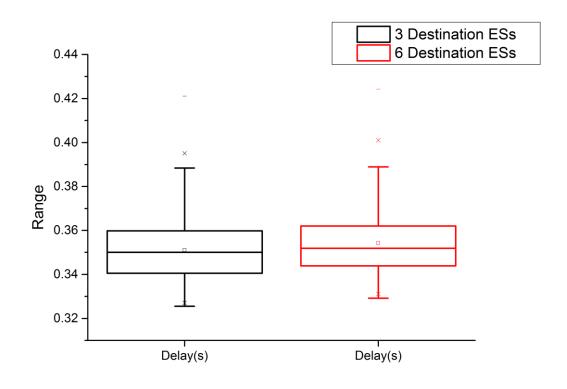

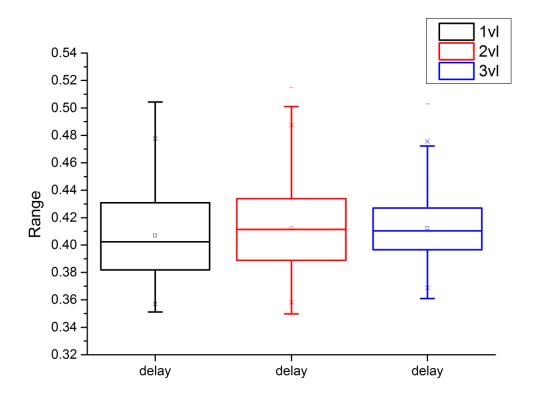

| Figure 5-18 Box Chart of Experiment 3       | 113 |

| Figure 5-19 Statistics Data of Experiment 3 | 113 |

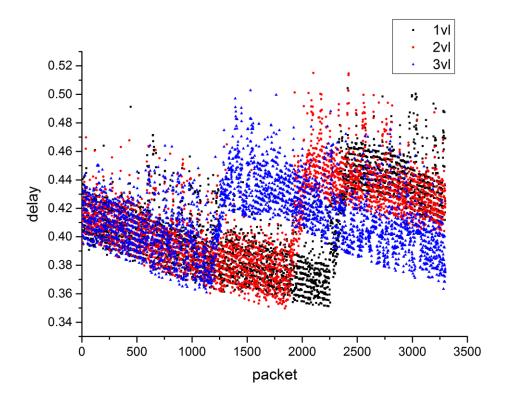

| Figure 5-20 Scatter Chart of Experiment 4   | 114 |

| Figure 5-21 Box Chart of Experiment 4       | 116 |

| Figure 5-22 Statistics Data of Experiment 4 | 116 |

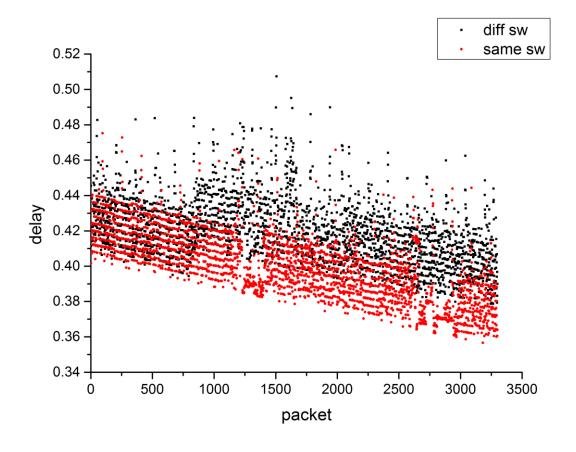

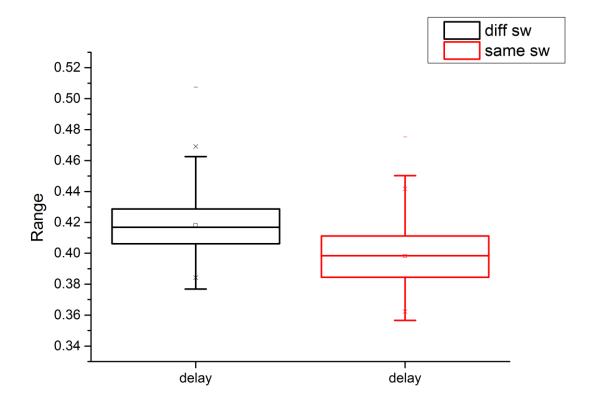

| Figure 5-23 Scatter Chart of Experiment 5   | 117 |

| Figure 5-24 Box Chart of Experiment 5       | 118 |

| Figure 5-25 Statistics Data of Experiment 5 | 119 |

# **LIST OF TABLES**

| Table -                              | 4-1 Fu                                       | unctions in AD        | TA Module   | 9       |   |    |    | 55  |

|--------------------------------------|----------------------------------------------|-----------------------|-------------|---------|---|----|----|-----|

| Table 4-2 Functions in ADRA Module58 |                                              |                       |             |         |   | 58 |    |     |

| Table                                | Table 4-3 Functions in CreateDB Module6      |                       |             |         |   |    | 65 |     |

| Table                                | 5-1 To                                       | otal Time Dela        | y of Experi | iment 1 |   |    |    | 94  |

| Table                                | 5-2 To                                       | otal Time Dela        | y of Experi | iment 2 |   |    |    | 95  |

| Table                                | Table 5-3 Total Time Delay of Experiment 396 |                       |             |         |   |    |    |     |

| Table                                | 5-4 To                                       | otal Delay Tim        | e of Experi | iment 4 |   |    |    | 99  |

| Table                                | 5-5 To                                       | otal Time Dela        | y of Exper  | iment 5 |   |    |    | 100 |

|                                      |                                              | Comparison nent 1)    |             |         | - |    | •  | -   |

|                                      |                                              | Comparison nent 2)    |             |         | - |    | -  | -   |

|                                      |                                              | Comparison nent 3)    |             |         | - |    | •  | -   |

|                                      |                                              | Comparison nent 4)    |             |         |   |    |    |     |

|                                      |                                              | Comparison<br>ment 5) |             |         | - |    | -  | -   |

#### LIST OF ABBREVIATIONS

ADRA Avionics Data Reception Application

ADTA Avionics Data Transmission Application

AFDX Avionics Full Duplex Switched Ethernet

API Application Programming Interface

ARINC Aeronautical Radio, Incorporated

BAG Band Allocated Gap

BIP Behaviour, Interaction, Priority

CRC Cyclic Redundancy Code

CSMA/CD Carrier Sense Multiple Access with Collision Detection

DSPN Deterministic and Stochastic Petri Nets

FIFO First In First Out

GCRA Generic Cell Rate Algorithm

GPS Generalized Processor Sharing

IEEE Institute of Electrical and Electronics Engineers

IMA Integrated Modular Avionics

IP Internet Protocol

LAN Local Area Network

LRU Line-replaceable Unit

MAC Media Access Control

RTA Response Time Analysis

UDP User Datagram Protocol

#### 1 INTRODUCTION

## 1.1 Background and Motivation

Since the demands of transportation growing rapidly, new civilian aircraft are designed and manufactured. These new aircraft have applied new technology and the amount of embedded systems and functions are raise. IMA (Integrated Modular Avionics) at platform level and communication multiplexing at network level have been proposed for keeping both system capacity and maintainability. Traditional avionics data buses such as ARINC 429 and MIL-STD-1553 with limited bandwidth can't meet the data exchange capacity of those new civilian aircraft.

Avionics Full Switched Ethernet (AFDX), also known as ARINC 664 P7, has been widely applied in modern aircraft, such as A380 and B787. With sufficient bandwidth (100 times larger than MIL-STD-1553), low cost and redundancy management, AFDX is considered as the next generation avionics data bus.

AFDX network multiplexes huge amounts of data flows over a full duplex switched Ethernet. All these data flows have to compete for sharing network resource which makes the data exchange behaviour uncertain. AFDX introduces specific mechanisms such as the virtual link to guarantee the deterministic of data communication behaviour. Upper bound time delay could be employed to prove this determinism. Moreover, time delay reflects the transmission capacity of the network. Thus, studies on AFDX time delay should be conducted.

It is not common for every researcher studies the AFDX network performance on industrial AFDX network. Simulation approaches could be proposed since it simulates the AFDX network environment with conventional software and hardware. Thus, the cost of the simulation is acceptable. With the simulation environment, studies of the AFDX network could be quickly conducted. Moreover, it could be utilised by the AFDX system designers for AFDX network design. Moreover, the simulation environment could help AFDX system

designers during their design period. The duration of design could be reduced and the cost could be decreased.

Recently, studies on AFDX time delay analyses have several approaches. Theoretical approaches propose mathematical techniques to obtain the tighter AFDX network time delay. Meantime, the simulation approaches are used for verification and give more accurate results. Simulation with real-time software which excluded network hardware is proposed to simulate certain scenario. Without hardware influence considering, this simulation is not similar to the industrial environment. Programming software simulation with network hardware, on the other hand, tries to simulate the industrial environment which is more realistic. Till now, few researchers focus on AFDX simulation with software implementation combined network hardware.

In this project, the time delay model of AFDX network is introduced by applying Network Calculus. Then programming software simulation with network hardware involved AFDX network simulation platform FACADE is developed. Moreover, this simulation platform is suitable for AFDX network experiment purposes. Besides, the total time delay of the AFDX network and the associations between total time delay and several variables are deduced and the comparison between calculus and experiment delay is made. In conclusion, this project plans to benefit the design of avionics data bus by offering designers possible approaches to optimise the performance of total time delay, in the academic or industrial area.

# 1.2 Research Objectives

This research aims to develop methods and platform to analyse and evaluate AFDX system design requirements and network time delays to provide AFDX system designer with a design verification tool. Several measurable research objectives have been identified and outlined as follows:

- a) Modelling the AFDX time delay.

- b) Improving the current AFDX network simulation platform, FACADE by introducing three new functions, including the loss data detect function,

invalid data detect function and communication time record function. Developing avionics application simulation modules which could communicate with FACADE platform.

- c) Testing the improved FACADE simulation platform.

- d) Detecting the associations between the total time delay and certain variables.

#### 1.3 Thesis Structure

This project consists of five main phases which are background knowledge comprehension, AFDX time delay model by Network Calculus, platform understanding and modifications, experiments design and execution as well as data collection and analysis. These steps act as the time sequence. All these phases are listed below:

#### Phase 1: Background knowledge comprehension

In this phase, contextual comprehension of the research and related knowledge should be studied first. AFDX network standard and its related standard should be investigated elaborative. It is essential for the researcher to understand AFDX network characteristics as well as data exchange behaviour. Since the simulation bases on the AFDX standard, a literature review on AFDX network is conducted. After that, the research approaches proposed by other researchers were reviewed.

#### Phase 2: AFDX time delay model by Network Calculus

This section aims to study the time delay model of the AFDX network using Network Calculus. The whole AFDX network consists of three main components which are end system, AFDX switch and physical propagation. In this project, traffic regulator in end system is considered as powerful enough which will not impose extra delay to transmission. The primary analysis part of the switch is scheduler. Moreover, the physical propagation can be assumed upper bound by some constant value. All these three delays compose the total delay time of the AFDX network.

#### Phase 3: Platform understanding and modifications

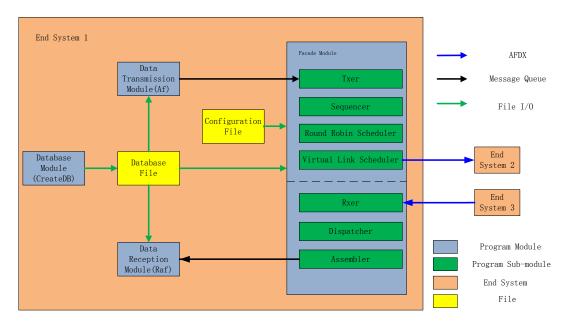

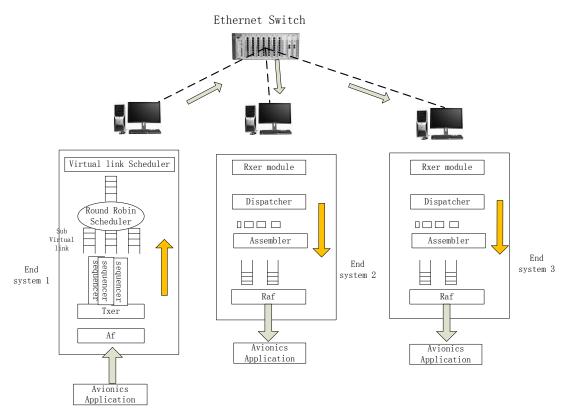

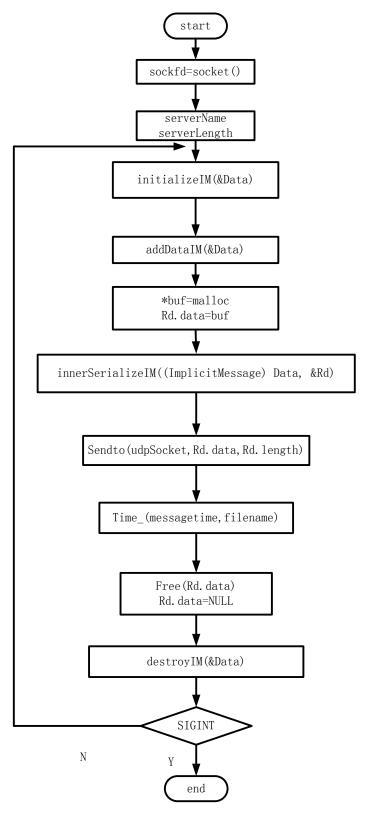

Since the simulation platform framework architecture proposed in this research is as same as the previous work, comprehension of this simulation platform should be carried out instantly. At first, the theses written by previous researchers are studied. The requirement analyses contained in those articles help the author to understand the initial motivation of this platform easily. The detailed framework description makes the author comprehend the grand architecture effortlessly. Certain modifications have been made to develop this platform suitable for the following experiment after containing the previous simulation platform. The Af module has been modified into an AFDX data packets reception interface of the AFDX network while Raf module has been changed into an AFDX data packets transmission interface of the AFDX network. The particular part of the data has been proposed for data check function. Time record function and data packet counting function are also invited for experiment purpose. Moreover, two new modules are implemented as avionics application on the end system. One is used to send AFDX data while the other module is proposed to receive AFDX data.

### Phase 4: Experiments design and execution

In this phase, the experiments which focus on computing total time delay and associations between target variables and total time delay are design first. Several variables which may influence the total time delay performance of AFDX network are listed as below:  $I_{max}$ , BAG of virtual link, the amount of destination end systems in one specific virtual link, the amount of virtual links in one AFDX network and the amount of switches between source end system and target destination end system. After design, each experiment will be executed and the experiment issues will be stated as well as the experiment data.

#### Phase 5: Data collection and analysis.

This phase is employed to collect and analyse the data of those five experiments. Firstly, data are gathered from each experiment separately. Then those data will be examined respectively. In this phase, the associations between total time delay and  $I_{max}$ , BAG, the amount of destination end systems

in one particular virtual link, the amount of virtual links in one AFDX network and the amount of switches between source end system and target destination end system will be studied. The normal test is executed to detect whether student's t-test can analyse the obtained data. The scatter chart, as well as box chart, are applied to the data analysis section. The comparison between calculus total time delay and experiment total time delay are carried out.

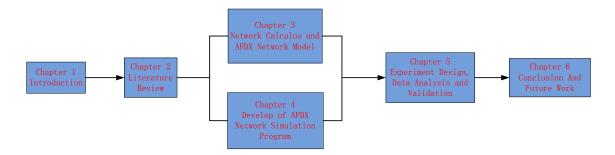

As represent in Figure 1-1, there are six chapters in this thesis including chapter 1. In chapter 2, studies on AFDX network and recently related studies are summarised. Chapter 3 invites the Network Calculus and then time delay model of the AFDX network will be analysed. The detailed design of AFDX network simulation platform and avionics application simulation modules are described in chapter 4. Chapter 5 focuses on the design of the experiments which are utilised to detect the associations between total time delay and several variables. Moreover, chapter 5 represents the experiments states, analysis and deduction of those obtained data. The comparison between calculus delay and experiment delay is carried out. In chapter 6, the key findings and future work are illustrated and concluded.

**Figure 1-1 Thesis Structure**

# 1.4 Summary

In this chapter, the background and motivation of this project have been introduced first. AFDX is considered as the next generation of avionics data bus, the time delay which reflects the performance of AFDX network should be studied. Simulation of AFDX network makes research more easily to be

conducted. Secondly, the objectives of this project are represented. Finally, the structure of this thesis is listed.

### **2 LITERATURE REVIEW**

#### 2.1 AFDX Introduction

AFDX has already applied on Airbus A380, A350, Boeing 787, COMAC ARJ21, and other aircraft. ARINC 664 standards, also known as AFDX (short for Avionics Full Duplex Switched Ethernet), has been published in 2005. AFDX [1][8][9] transmission rate up to 100Mb/s which is 1000 times faster than its predecessor ARINC 429. The deterministic behaviour and redundant architecture meet the avionics requirement. Nowadays, most future civil transport aircraft are going to adopt this standard communication network [2].

IEEE 802.3 is a LAN (local area network) technology which provides network access service. Devices connect to switches or other infrastructure devices by various types of cables. AFDX standard is based on Ethernet technologies especially IEEE 802.3. As the commercial 802.3 hardware are low cost, AFDX tries to use them as much as possible. Although IEEE 802.3 provides high exchange communication capacity, it could not meet the safety-critical avionics systems' requirements due to its uncertain data exchange behaviour and frame loss. AFDX has introduced a new mechanism to overcome these problems which IEEE 802.3 has. To determine the communication behaviour, AFDX adds the virtual link. The virtual link with a maximum dedicated bandwidth provides quaranteed maximum network transmission delay. Redundancy management is proposed to solve the frame loss issue. For each virtual link, frames are transmitted across both redundant networks. Meanwhile, the "First Valid wins" policy is applied. The first frame reaches either two networks is accepted while the second frame is just discarded. This redundancy management guarantees the data exchange when any one network component fails.

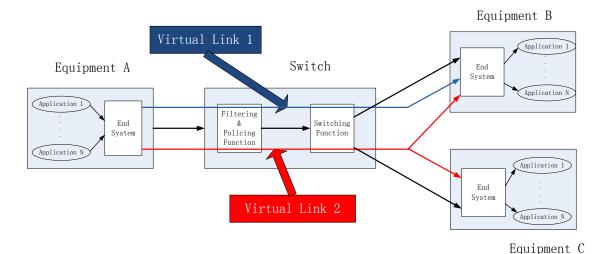

AFDX network consists of three elements which are end system, AFDX switch and virtual link.

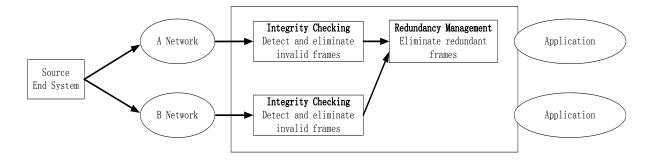

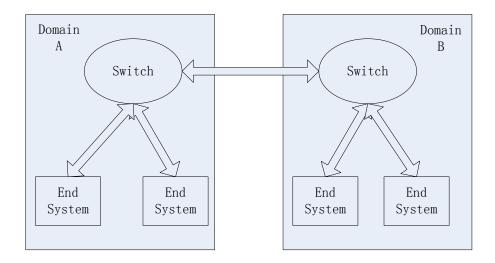

**Figure 2-1 Illustration of AFDX Network**

Figure 2-1 represents these three elements. End system is working as a source or receptor of AFDX data on the network. Source end system receives data from source avionics application and transfers those data to destination end system. After destination avionics application receives data from destination end system, the transmission finished. During the transmission, data are transmitting on virtual links between source and destination end systems. AFDX switch is proposed to connect end systems to network, receive, handle and transmit the data to destination end system.

#### 2.1.1 End System

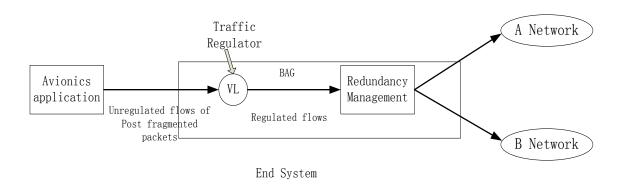

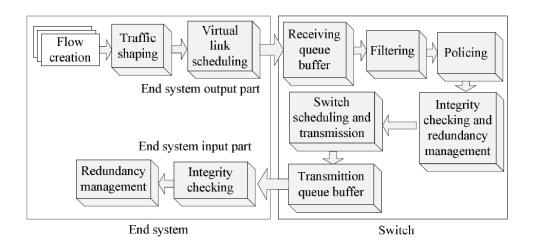

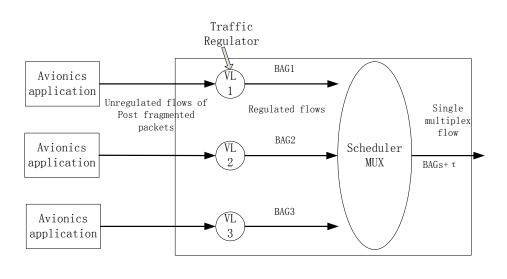

End system (or avionic computing LRUs) exchanges data (messages) based on the concept of virtual links with traffic shaping, redundancy management, integrity checking and routing provided by AFDX switches using configuration tables. Avionics application sends the data to end system with unregulated flows of post fragmented packets. Traffic regulator in end system shapes those uncontrolled flows into regulated flows according to Bandwidth Allocation GAP of each virtual link.

Figure 2-2 Source End System

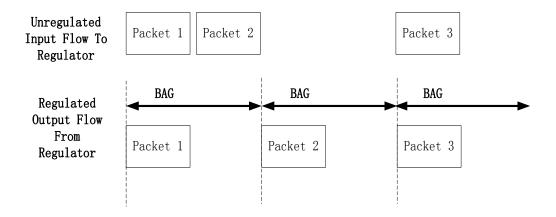

Bandwidth Allocation GAP, also known as BAG, is the minimum time interval in the millisecond of the first bit of two consecutive frames of the same virtual link. BAG is used for managing data flow. (See Figure 2-3). BAG values equal to 2<sup>k</sup> ms interval, (k is an integer from 0 to 7).

Figure 2-3 Unregulated and Regulated Flow

After shaping, each flow will send no more than one frame in every interval of BAG. Then each frame in the flow will be forwarded to both networks by redundancy management. By using redundancy management, data communication could continue even one complete network lost.

Destination End System

Figure 2-4 Destination End System

After data frames across network and reach destination end system, integrity checking will first detect and eliminate invalid frames. Then the "First valid wins" policy is introduced which means that the first valid data frame reaches the redundancy management will be accepted and transferred to avionics application.

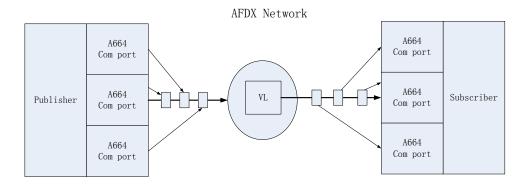

#### 2.1.2 Virtual Links

A virtual link has these characters:

A virtual link is a logical connection which connects one end system to one or more end systems. Network designer can configure the upper bound bandwidth of each virtual link [2].

The bandwidth of a virtual link can be allocated by end system and would not be affected by other partitions which use this virtual link.

Each virtual link should not exceed its upper bound size and transmission rate which will be checked by the switch. These parameters store in the switch, follow by the switch and end systems. The switch can also change virtual link priorities to secure the performance of time-sensitive messages.

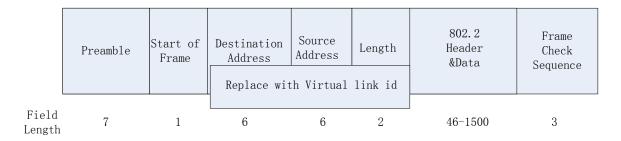

Ethernet switch receives incoming frames from the input port and routes them to output port base on the destination address in Ethernet transmission. In AFDX network, virtual link ID is invented as a unique mark of a virtual link (See Figure 2-5). This mark replaces source address, target address(es) and data

content amount of the frame which stores in switch's configuration table. Virtual link id represents the source of the virtual link where the frame comes.

**Figure 2-5 AFDX Network Packet Format**

A virtual link is a logical connection for network data in transmission— see Figure 2-6. The upper bound of latency and jitter are guaranteed due to the network bandwidth is allocated. The virtual link connects source end system and destination end system(s) together by using the switch which means that an end system may be designed only to receive VLs and not transmit virtual links, or on the contrary. In that way, an end system could have zero virtual links, neither originates or receives. The virtual link sends frames for end system. A virtual link can only have one end system as the source, but one or more destination end systems are permitted.

The sub-virtual link is introduced to use the virtual link more efficient. One virtual link could possess up to 4 sub-virtual links. Each sub-virtual link follows First In, First Out regulation. Each First In, First Out queue is accessed by virtual link using round robin algorithm.

Figure 2-6 Chart of Virtual Link

#### 2.1.3 AFDX Switch

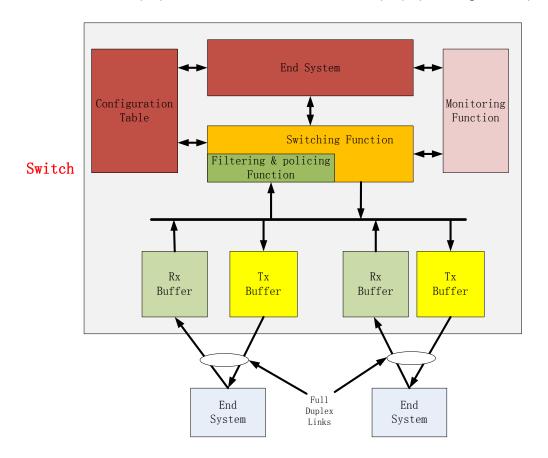

Based on 802.3 Ethernet techniques, AFDX is a full duplex network. The transmission medium connected each end system is a network cable which contains two pairs of wires. Those two pairs of wires have different functions, one is to send frame (Tx), the other is to receive frame (Rx). (See Figure 2-7)

Figure 2-7 AFDX Switch

AFDX switch has several blocks. Filtering and policing function filters frames base on rules such as frame integrity, frame length and destination. Switching function routes frames to their destinations through appropriate output ports. The configuration data which controls the switch are stored in the configuration table. End system in AFDX switch is utilised to receive and transfer data. The monitoring function is introduced to monitor and log all operations of the switch.

The switch has two kinds of buffers. Rx buffers are used to store incoming frames while Tx buffers are used to store outgoing frames. Both buffers operate under FIFO mechanism. Switch processor checks all the incoming frames

virtual link IDs sequences. All the sequences should follow the same order as Rx FIFOs. These frames whose sequences are correct will be transferred to the proper Tx buffers, waiting for transmission.

To avoid contention, buffers are used by the switch. Breach of traffic contract might overflow input buffer caused network data loss, is protected by fault containment. Switch buffer allocated to one end system which could manage the contention when two or more end systems send messages to that end system.

Redundancy guarantees a high degree of availability. For instance, cluster switches and two logical connections. CRC, one of the error detection mechanisms, is used to ensure the high integrity. Messages are delayed inevitably due to the process of resolving contention which called as latency.

Switch controls the data traffic in the data bus, following the configuration in the configuration table. As the subsystems have their specific requirements of the network performance, the network designer has to meet these demands which are proposed by avionics application designer during their design. The configuration table considered as an avionics application designer's requirements set for network performance to supply the avionics applications. Network designer expresses all the network performances designed for the avionics applications in the configuration table. As the switch can read the configuration table, it is possible for network performances to meet the demands of avionics applications. This mechanism achieves the certification for network and avionics applications since the designers monitor data bus performance and collect evidence for identification.

#### 2.1.4 Latency and Jitter

Two types of latency, latency in transmission and latency in reception, are defined in ARINC 664 P7.

The definition of latency in transmission is the duration of the last bit of an avionics application data which is ready to be sent by end system and the last bit of the corresponding Ethernet frame transfer to the physical media.

The definition of latency in reception is the duration of the last bit of an avionics application data accepted by the physical media and the last bit of the corresponding data is available to the end system avionics application.

According to ARINC 664 P7, the upper bound latency of the end system in transmission should be less than 150µs+frame delay. The upper bound latency of the end system in reception should be less than 150µs.

The time one end system receives a message from the other end systems could be different, even from the same end system. The upper bound time subtracting lower bound time is Jitter. Several aspects could affect Jitter such as Network topology, hardware, the number of virtual links on a single port. Each virtual link has a maximum allowable jitter which stores in the configuration file.

#### 2.1.5 Network Topology

At first, Ethernet was not used on aircraft. It is used for the commercial general purpose, to connect devices, terminals as well as systems together and to communicate with each other, air traffic control systems, weather broadcasting systems and navigation systems for instance. As passengers' entertainment systems aboard on the plane, Ethernet was used to connect each device to one domain for management and data sharing.

In Figure 2-8, the devices are divided into two different domains. These two domains connect into a star topology network by two switches.

From this figure, ARINC 664 P7 terminals comprise the avionics systems which are part of each domain. In each domain, the network is connected to the switch which is called domain switch. End systems in same domain communicate with each other by domain switch. When end systems exchanging data in different domains, data are routed through each domain switch, from source to destination.

Figure 2-8 AFDX Star Topology

## 2.2 AFDX Delay Research Techniques

Several technical methods have been proposed to analyse and evaluate AFDX network delay performances.

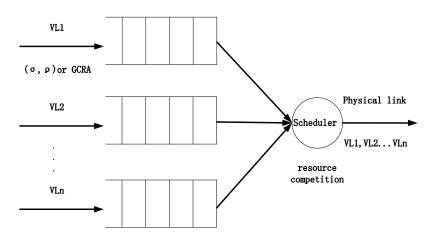

Network calculus (or worst case Network Calculus) theory is one of the most common theoretical approaches which is used to obtain end-to-end upper bound delay [4] [5] [6]. The network calculus could provide the mathematical upper bound latency of any network element which possesses queue capability. Moreover, this approach could obtain queue-size bounds as well. As the worst case scenario considers each node crossed by a given flow and calculus maximum possible jitter caused by the previously node, the results obtained by Network calculus is obviously pessimistic [11]. This theory is mainly used for avionics network certification. In the communication network, the arrival curve and service curve are introduced to describe the characteristics of data flows and the scheduler multiplex respectively. A scheduler or multiplexer is a device which receives several input data flows and then forwards those streams into a single line. Thus, the arrival curve is used to represent virtual links in [7]. The network calculus approach obtains a pessimistic upper bound delay which can hardly be reached. To get a tighter computation, several optimizations are taken by researchers. The 'Group' concept is introduced to Network Calculus to obtain more accurate delay values. Those virtual links which come out from the same multiplexer and transfer into another multiplexer together are treated as 'Group'.

These virtual links share at least two paths which will not be serialized by the following multiplexers after they have been serialized by the first one. By utilising this concept, less delay spent in multiplexers. Tighter bounds are obtained up to 40% better than Network Calculus without 'group' [12]. Periodic Virtual Link, a virtual link sends frames strictly periodically, is also introduced to gain a more precisely upper bound delay [13]. Periodic virtual link is schedulable with the offset which can obtain a reduction of 49% upper bound delay than network calculus approach.

Due to the massive configuration work on the real network, exact stochastic analysis of industrial avionics network is impracticable. Pessimistic stochastic analysis [15], considered as an approximation of the exact stochastic analysis, is applied to solve this issue. The pessimistic stochastic analysis provides a guaranteed upper bound end-to-end delay which is greater than the exact stochastic analysis. Based on the pessimistic assumptions, the stochastic network calculus approach is a pessimistic analysis. This approach provides a probabilistic upper bound delay of a given flow which belongs to a specific network. By comparing the pessimistic upper bound delay with the industrial AFDX network experiment upper bound delay, pessimistic upper bound delay is no more than four times than the experiment one [16].

Trajectory approach [10] is applied to get the upper bound on end-to-end upper bound delay in distributed systems [11]. In Trajectory approach, the switch output port is treated as a process node. For a packet m from flow f, the trajectory approach will identify all the impacts of end-to-end delay on every node this packet cross. This approach is suitable for the scenario for a group of sporadic data flows without considering when the packets arrived. Trajectory approach focuses on the trajectory of a packet in worst case scenario rather than any visited node in the holistic approach. This approach only considers the possible scenario. As a timing analysis approach, trajectory approach concentrates on given flow, trace a packet and construct the packet sequences in each passing node. This approach is used for obtaining the upper bound arrival times for every packet. According to [14], Trajectory approach is more

precious than the Network Calculus. The 'Group' concept is also applied in Trajectory approach to obtain a better upper bound delay. By utilizing this concept, 10% better tighter average upper bounds are obtained than the Trajectory approach without 'group'.

The response time analysis (RTA) technique has been used extensively to schedulability experiment and other characteristics for the diverse real-time operating system [17] [18] [19] [20]. RTA bases on the critical instant and busy period. A critical instant allows detecting the worst response time for the given task. Each task of simultaneous activation from fixed priority scheduling of single processor is a critical instant [21]. Response time represents the end-to-end delay which means the worst-case response time is the upper bound of the end-to-end delay. By detecting the response time of each task in an interval starting at a critical instant as soon as the job been released and comparing the result to the related deadline, schedulability test for the periodic task set can be acquired as well as the sporadic task. The multiplexer in AFDX can be represented as a processor while RTA is introduced to the worse-case data transmitting delay analysis in the real-time operating system [4].

In [22] [23], the Petri Net Theory is proposed to simulate the AFDX network for AFDX modelling and performance analysis. A deterministic and stochastic Petri nets (DSPN) model is achieved. In this model, data frame length is 791 bytes. Three sub models contains in DSPN model are periodic message control sub model, event message sub model and message transmission sub model. The periodic message control and event message represent the end system in AFDX network while the message transmission sub model expresses the AFDX switch. Authors compute the network load, the time delay of this model and believe this model can be applied to AFDX simulation. Since the switch queue end-to-end delay is not considered in this simulation, it still not similar to the realistic AFDX network.

Alur and Dill first introduced the timed automata [24]. It is a finite automata with real and positive variables increasing uniformly with time. A transition has three labels which are a condition on clock values, actions and the new value of clock.

The model checking approach bases on timed automata is proposed to evaluate the performance of the AFDX contains investigating each state of the system as well as detecting an exact worst-case end-to-end delay [25]. This approach is used to represent the AFDX network action by time. For the end system, each state of the frame is represented by a node and the transition expresses the transmission action. For switch, each node represents a location in the queue of the transmit port. Time of transition will be upgraded after each action. The delay can be obtained by calculus the deviation of the new value and old value of clock. The model checking approach has detected all the possible states of the system. Thus, authors believe that an exact worst-case end-to-end delay has been obtained as well as its related scenario. The authors also uncertain if this approach can be applied to a realistic AFDX network.

### 2.3 AFDX Simulation Techniques

#### 2.3.1 Real-time Software AFDX Network Simulation

Experiments have to be taken to obtain realistic results. Those results are used to verify the designs. Since not every researcher can utilise a realistic AFDX network environment to study the behaviour and performance of the AFDX network, simulations have been carried out to fix this issue.

The Network simulation 2 (NS2) is proposed to simulate the AFDX network [26] [27]. Figure 2-9 represents the simulation model of the AFDX network end system and switch system. NS2 simulates the functions of the end system and AFDX switch. In end system, the NS2 application layer protocol is used as an application procedure queue. By utilising the traffic shaping sub-function, the flow-shaper is achieved on the queue. The multiplexer is realized by the virtual link scheduling algorithm while the de-multiplexer possesses the redundancy and integrity functions. The AFDX switch and virtual link are also obtained by NS2, which shows that using NS2 for AFDX simulation is practicable. In AFDX switch, the filtering and policing function are simulated by the filtering and policing function in NS2. The switch scheduling algorithm is used to simulate the multiplexer and de-multiplexer. A queue with limited delay and allocated

bandwidth is employed to simulate the virtual link. After that, this simulation is proposed to research end-to-end delay performance. The results show that the jitter of this simulation is between -0.5 ms and 0.5 ms which meets the requirement of ARINC 664 P7.

Figure 2-9 The AFDX End System and Switch System Simulation Model [26]

The QNAP2 [29] (Queuing Network Analysis Package) is applied to simulate the AFDX network [28]. QNAP2, a commercial package, can be utilised to analyse the performance of queuing network by analytical and simulation approaches. In this software, the end system is represented by four types of queues which are application queues, regulator queues, "Multiplexer" queue and the "DeMultiplexer" queue. The switch is represented by three different queues which are input queues, "CPU" buffer and output queues. The measurements units are also introduced in this simulation. Each frame has placed a time-stamp for obtaining the duration time. This simulation has also been validated which proves that the QNAP2 can be used for AFDX network simulation for end-to-end delay research. The results show that the max delay of simulation is much larger than the mean delay.

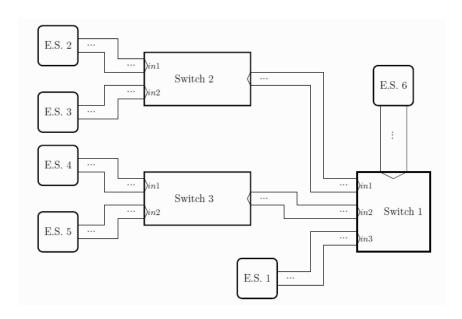

The BIP [32] (Behaviour, Interaction, Priority) framework, partially achieved in the IF toolset [30] and the PROMETHEUS tool [31], is proposed for modelling the AFDX network. BIP is a language which can build components from atomic components, connect and priority relations. The atomic components are utilised to build systems. The connects provide possible interactions between systems.

The priority relations select possible interaction. By using BIP, the end system and AFDX switch are simulated. An AFDX experiment architecture is achieved (See Figure 2-10). Several scenarios have also been tested to validate this simulation which proves that this simulation is suitable for the end-to-end delay performance research.

Figure 2-10 The Architecture of The Experiments [33]

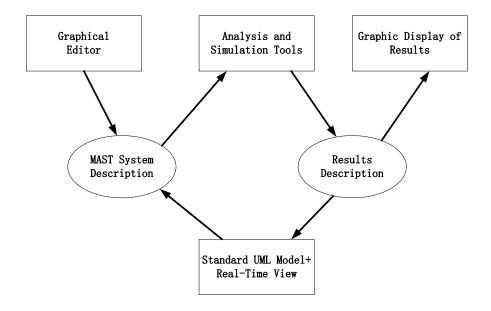

The MAST suite is suitable for simulating a real-time system [34]. As an event-driven model, MAST can build complex dependence patterns of diverse tasks [36]. This characteristic makes the MAST ideal object-oriented and event-driven architecture for real-time systems. Offset-based techniques are also applied to the MAST for accurate results. Figure 2-11 represents the tools which will be included in the MAST. As the simulation model is a distributed system, several response-time analysis approaches for the processors [47] [48] [49] [50] [51] are proposed and combined with the composition approach [52]. Then the MAST is used to simulate the AFDX network. After obtaining the result by MAST, authors compare their results with the model checking approach, Network Calculus, Network Calculus with grouping, Trajectory approach and optimized Trajectory approach. The comparison represents that the results gain from MAST are only slightly better than Network Calculus and more pessimistic than other approaches [35].

Figure 2-11 MAST Toolset Environment [34]

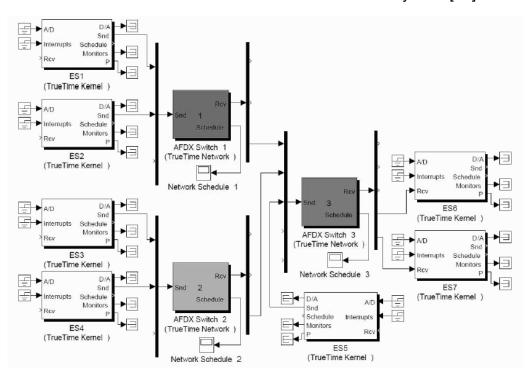

The TrueTime [38] is a real-time network simulation software platform. In [4], authors utilise TrueTime to simulate an AFDX network for evaluating the response time analysis technique. The simulation model is represented in Figure 2-12. Three different scheduling policies proposed to this simulation are BAG-based, rate-based and FCFS schemes. Among these scheduling policies, BAG-based shows the smallest end-to-end delay. In [39], authors utilise the TrueTime to study the Generic Cell Rate Algorithm (GCRA) model which gives a tighter upper bound delay than the  $(\sigma, \rho)$  model.

## 2.3.2 Programming Software AFDX Network Simulation

A programming software simulation of the AFDX end system is established on VxWorks Operating System [40]. This simulation contains the traffic shaper as well as the virtual link scheduler. The source end system is achieved by introduced the transmitting algorithm to Tx process while the destination end system is obtained by introduced the receiving algorithm to Rx process. Then the simulation is carried out on Power PC 7448 and bridge tsi109. According to the experimental results, this software implementation obtains a better jitter performance than the theoretical one which means the simulation is successful. An AFDX emulator is achieved in Ada and verified under the realistic environment by PCs and switches [41]. In this simulation, the scheduler task

and the listener task are introduced for sending data and receiving data respectively. Outbound buffer and inbound buffer are established as virtual links. The outbound buffer has four internal FIFO queues which use as the sub-virtual link. The internal queues can also fragment messages sent by avionics application. Research in [42] uses C++ to simulate an AFDX network for OMNET++. A software named A-Stack [43] is also used as AFDX software simulation platform. This commercial software is certified by DO-178B Level A standard which is a software consideration in the airborne system [44].

Figure 2-12 TrueTime Simulation Model [4]

# 2.4 Summary

This chapter introduces AFDX and related studies. Firstly, AFDX and relative knowledge are listed. Then the research approaches of AFDX have been reviewed. The theoretical approaches are utilised to obtain the mathematical network performances. At the same time, the simulations approaches are used for verification. Simulation with the real-time software which excluded network hardware is not similar to the realistic environment while the programming

software simulation with network hardware is more similar to the real AFDX network.

# 3 Network Calculus Model and AFDX Delay Analysis

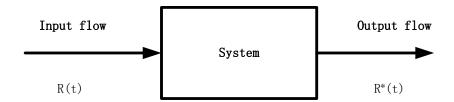

# 3.1 Data Flow Features in Data Network Concepts Cumulative Functions

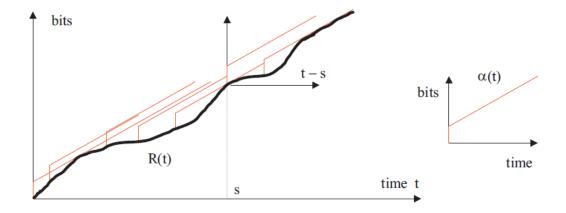

In the Network Calculus, the cumulative function or flow, R(t), is defined as the aggregate of bits which can be seen on the data flows in time interval [0,t]. In the network, a system which could be a switch or an end system handles the input data and sends them with a variable delay. As represented in Figure 3-1, both R(t) and R\*(t) are the cumulative functions. R(t), an input function, demonstrates the total input data of the input flow in the time interval [0,t]. R\*(t), an output function, represents the entire output data of the output flow in the time interval [0,t].

Figure 3-1 Cumulative Function in Network

The cumulative function is considered as a wide-sense increasing function. Moreover, when t equals to 0, the cumulative function also equals to 0 as convention. Take Figure 3-1 for instance, R(0)=0 and  $R^*(0)=0$ . Both discrete and continuous time models can apply this cumulative function. A minimum granularity can always be defined in the realistic world, for instance, bit, word, cell or even packet, hence discrete time with a limited aggregate of values for a cumulative function can be granted. However, a continuous time is more convenient to consider no matter cumulative function is continuous or not. A fluid model is proposed to describe the continuous function while the left or right-continuous function is used to describe an uncontinuous function.

Three types of cumulative functions are listed below. The first function is the discrete time model cumulative function which time t can be represented as  $t \in N = \{0, 1, 2, 3,...\}$ . The second function is a fluid mode cumulative function

which time t can be represented as  $t \in R+ = [0,+\infty)$  and R is a continuous function. The third function is the general, continuous time model cumulative function which time t can be represented as  $t \in R+$  and R is a left- or right-continuous function.

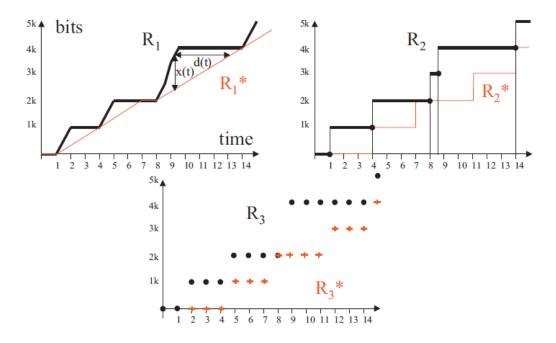

Figure 3-2 Input and Output Function [53]

A single server queue is represented in Figure 3-2, both the input function and output function. In this figure, each packet has to wait 3 time units until it been served. The output function  $R_1^*$  which is a fluid model serves the packet when the first bit has been received and the packet departures one bit after another at a fixed rate. For instance, the initial packet arrives during the times 1 to 2 and departures during the times 1 to 4. The output function  $R_2^*$  serves the packet when it has been received completely and is considered leave the system only when this packet has been entirely transmitted. This mechanism is considered as the store and forward mechanism. In  $R_2^*$ , after time 1, the first packet arrives instantly and departures instantly at time 4. In the output function  $R_3^*$ , the first packet arrives at time 2 and leaves at time 5 which is considered as a discrete time model.

The cumulative function R(t) is assumed that it has a derivative  $\frac{dR}{dt} = r(t)$  such that  $R(t) = \int_0^t r(s) ds$  which is a fluid model. Then the function r is considered as the rate function.

If the time slot  $\delta$  is chosen and sampled by

$$S(n) = R(n\delta) \tag{3-1}$$

A continuous time model cumulative function R(t) could be mapped into a discrete time model cumulative function S(n),  $n \in N$ .

This mapping could lead to an information loss. A continuous time model cumulative function can be obtained without information loss from S(n),  $n \in N$  by letting:

$$R'(t) = S(\left[\frac{t}{\delta}\right])$$

(3-2)

In this formula, the cumulative function R is always left-continuous.

By using the formula (3-1), any result obtained from a continuous time model could also be used to the discrete time. In general, the ATM applies the discrete time model while the continuous time model is introduced to dealing with the variable size packets, even not a fluid model.

# 3.2 Virtual Delay

As long as the input and output functions are confirmed, the delay can be obtained.

For a lossless system, the virtual delay at time t is  $d(t) = \inf\{\tau \ge 0 : R(t) \le R^*(t + \tau)\}.$

The virtual delay is considered as the horizontal deviation (The deviation of the input and output function in the horizontal (See Figure 3-3). If the input and output function are continuous (fluid model), then it can be seen from the Figure 3-1 that  $R^*$  (t +d (t)) = R(t) and that d(t) is the smallest value fitting this formula.

Figure 3-3 Horizontal Deviation

In Figure 3-2, the values of virtual delay are different for these three models. In the first subfigure, the delay of the first packet which the last bit experienced is d (2) equals to 2 time units. Moreover, the virtual delay equals to d (1) which is 3 time units on the second subfigure. The virtual delay of the fourth packet on subfigure 2 is d (8.6) equals to 5.4 time units. It takes 2.4 units of waiting time and 3 units of service time to complete the transmission.

### 3.3 Arrival Curves

#### 3.3.1 Definition of Arrival Curve

To provide the guarantees to data flows, the traffic sent by the sources should be limited. Arrive curve is proposed to limit this traffic. The concept of arrival curve is defined below.

Define  $\alpha$ , which is a wide-sense increasing function. If  $t \ge 0$  and only if for  $s \le t$  while the flow R is constrained by  $\alpha$ , then

$$R(t) - R(s) \le \alpha(t - s) \tag{3-3}$$

In this way, the  $\alpha$  is the arrival curve of the function R and the R can be called  $\alpha$ -smooth.

As shown in Figure 3-4, the condition is over a set of overlapping intervals.

Figure 3-4 Arrival Curve [53]

### 3.3.2 Affine Arrival Curves

For instance, if  $\alpha(t)=r\tau$ , it is to say that, for any time interval  $\tau$ , the total number of bits of the flow is no more than  $r\tau$ . It also can be said that this flow has a peak rate. One example is that the fast Ethernet has a restriction rate of 100M/s.

If  $\alpha(t) = b$  while b is constant, it means that an arrival curve of the flow will send flow less than b.

According to their relationship with leaky buckets, the affine arrival curves  $\gamma_{r,b}$  can be represented below:

$\gamma_{r,b}$  (t) = rt+b for t > 0 and 0 otherwise is proposed.

If  $\gamma_{r,b}$  is the arrival curve of one flow, it means that b bits of data will be transferred each time. At the same time, the maximum transmission rate is less than r b/s. In the arrival curve, b represents the burst tolerance and r expresses the rate. Figure 3-4 illustrates these two parameters.

### 3.3.3 Stair Functions as Arrival Curves

The arrival curve is represented as the form  $kv_{T,\tau}$  in the ATM. Meanwhile,  $v_{T,\tau}$  is used to express the stair function which is listed below:

$$V_{T,\tau}(t) = \left[\frac{t+\tau}{T}\right]$$

for t > 0 and 0 otherwise.

$v_{T,\tau}(t)=v_{T,0}(t+\tau)$ , then  $V_{T,\tau}$  can be considered as the results from  $v_{T,0}$  by a time shift to the left. In this equation, the time interval is represented as T and the tolerance is expressed as  $\tau$ . Both parameters are illustrated in time units. Take an ATM flow for example that a flow transfers fixed size packets and up to k unit of data. Assume all packets are separated by the T time units.  $Kv_{T,0}$  is the arrival curve of this flow.

If one stream is multiplexed with other streams, it can be considered that the packets of this flow are sent to a queue. At the same time, those flows multiplexed with this flow are also sending data to this same queue. This queue introduces a variable delay which can be considered has a maximum bound equal to  $\tau$  time units. In this scenario, if R(t) represents the input function while  $R^*(t)$  is the output function, both functions are for the flow at the multiplexer. As  $R^*(s) \leq R(s-\tau)$ , it can be deduced that:

$$R^*(t) - R^*(s) \le R(t) - R(s - \tau) \le K v_{T,0}(t - s + \tau) = K v_{T,\tau}(t - s)$$

(3-4)

Then  $Kv_{T,\tau}$  is the arrival curve of R\*. It can be inferred that a periodic flow, T represents its period, and k is the fixed size of the packet. If this flow has a variable delay which is less than  $\tau$ , then  $Kv_{T,\tau}$  can be utilised to represent its arrival curve. The function  $v_{T,\tau}$  is utilised to demonstrate the minimum time interval between packets.

R(t) is utilised as a left-continuous cumulative function of a flow, while time is discrete or continuous. If this flow sent packets which size are all fixed. Meanwhile, all these packets sizes are k data units and arrival with no time delay.  $t_n$  is proposed to represent the arrival time of the nth packet, the properties which illustrated below have the same meaning:

1. for all m, n,

$$nT - \tau \le t_{m+n} - t_m$$

2.  $kv_{T,\tau}$  is the arrival curve of the flow.

Since all the packets sizes are k data units and the packets generate consecutively, it can be inferred that the R(t) can be represented as nk, while n  $\in$  N. Moreover, the time interval between two consecutive packets is  $\geq T - \tau$ .

R(t) is the input function of one flow while the  $\alpha(t)$  is assumed as a wide increasing function. For both functions,  $t \ge 0$ . Set  $\alpha_I(t)$  the limit of  $\alpha$  at t. It can be assumed that  $\alpha_I(t) = \sup_{s < t} \alpha(s)$ . Moreover, if the function R(t) has an arrival curve which is  $\alpha$ , then  $\alpha_I$  is also the arrival curve of the function R(t).

R(t) is the input function of one flow,  $t \in R+$ , or a discrete time flow R(t) while  $t \in N$ . If this flow sends packets at a fixed size k with no delay, then for some T and  $\tau$ , set  $r = \frac{k}{T}$  and  $b = k(\frac{\tau}{T}+1)$ . Then this function R(t) is constrained by  $\gamma_{r,b}$  or by  $kv_{T,\tau}$ .

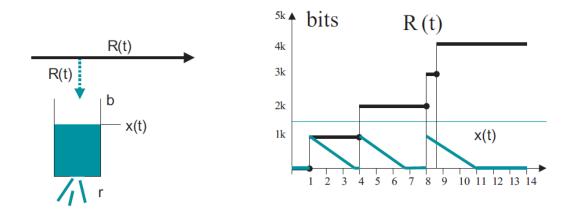

# 3.3.4 Leaky Bucket and Generic Cell Rate Algorithm

The data of the flow input function R(t) could be analysed by creating a Leaky Bucket Controller. It assumes that the bucket is empty at first and then will contain the fluid which size is b. There is a hole in the bucket and the contents in it would leak at a rate of r units until it is empty.

If the function R(t), known as the amount of data, would not cause the overflow in the bucket, the data is declared conformant. Otherwise, it is non-conformant. The definition of Leaky Bucket is shown in Figure 3-5. The overflow data which can't be poured into the bucket is considered as "non-conformant" data.

Figure 3-5 Leaky Bucket Controller [53]

A buffer with an input function R(t), which the service rate is r. This rate r is set as a fixed rate. In the beginning, there is no data in this buffer. Assumed that all

data received into the buffer during the time interval [0, t], the data in buffer at time t can be illustrated as below:

$$x(t) = \sup_{s:s < t} \{R(t) - R(s) - r(t - s)\}$$

(3-5)

Considering a leaky bucket controller, b is utilised to represent the bucket size. r is proposed to express the leak rate of this controller. It can be said that the arrival curve  $\gamma_{r,b}$  constrains the flow of this leaky bucket controller. The following properties are also correct:

- 1. The flow of conformant data has  $\gamma_{r,b}$  as an arrival curve of these conformant data which consist the flow;

- 2. All data is conformant if  $\gamma_{r,b}$  is the arrival curve of the input function.

- R(t) is the input function of one flow. Meantime, this flow sends data at fixed size k data units and has no time delay. This input function R(t) can be discrete or continuous. Moreover, the function R(t) is left-continuous. The properties illustrated below have the same meaning:

- 1. the flow is conformant to GCRA(T,  $\tau$ )

- 2. kv<sub>T,T</sub> is an arrival curve of this flow

A flow obeys the GCRA (T,  $\tau$ ) which transfers packets at a fixed size. It is said that this flow also can be represented as the leaky bucket controller. The parameters of this leaky bucket controller r and b can be illustrated as below:

$$b = \left(\frac{\tau}{T} + 1\right)\delta\tag{3-6}$$

$$r = \frac{\delta}{r} \tag{3-7}$$

The packet size is represented by  $\delta$  in units of data.

Considering a set of I leaky bucket controllers (or GCRAs), r<sub>i</sub> expresses the rate of the leaky bucket controller i while the b<sub>i</sub> represents the tolerant of the same controller i, for 1≤i≤I. The flow of the conformant data has an arrival curve as:

$$\alpha(t) = \min_{1 \le i \le l} \left( \gamma_{r_i, b_i}(t) \right) = \min_{1 \le i \le l} (r_i t + b_i)$$

(3-8)

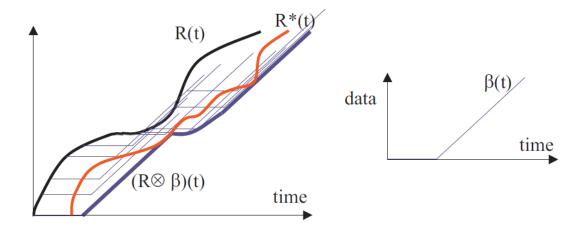

## 3.4 Service Curves

As mentioned above, the arrival curve is proposed to constrain the flows of the integrated services networks. Guarantees to flows are needed for reservations purposes which are done by packet schedulers [54]. The service curve is introduced to abstract the details of the packet scheduling. Two examples are presented to get a better understanding of the service curve.

The first example of a scheduler is a Generalized Processor Sharing (GPS) node [55]. A GPS node serves several flows simultaneously. Each flow is set at a given rate. Moreover, the node has some backlogs as well. The guarantee is that during a time window t, if the given rate of the node is r, thus it receives data which amount is, at least, equal to rt. Since the GPS node bases on a fluid model, it only can be considered as a theoretical concept. In the real network, node transfers with packets.

Consider a GPS node with an input function R and output function  $R^*$ . The given rate is r. In this scenario, assumed overflow will not occur. For all time t, considered  $t_0$  as the beginning of the last busy period for the flow up to time t. It can be obtained that:

$$R^*(t) - R^*(t_0) \ge r(t - t_0)$$

(3-9)

In this part, the function R is assumed as left-continuous. At time  $t_0$  there is no data which means backlog equals to 0 as R  $(t_0) - R^* (t_0) = 0$ . Combining this formula with the formula (3-9):

$$R^*(t) - R(t_0) \ge r(t - t_0)$$

(3-10)

Then it can be shown that, for all time t:  $R^*(t) \ge \inf_{0 \le s \le t} [R(s) + r(t-s)]$ , which can be written as

$$R^* \ge R \otimes \gamma_{r,0} \tag{3-11}$$

In the formula (3-11), the operational character ⊗ represents the min-plus convolution. F is a wide-sense increasing function equals to zero when negative

arguments. If f and g are two curves of F, the min-plus convolution can be represented as  $(f \otimes g)(t) = \inf_{0 \le u \le t} (f(t-u) + g(u))$ .

Here is the second example. Assume a network node which the maximum delay of a given flow R is bounded by T. The first in, first out mechanism is proposed in this example. The delay bound could be translated to  $d(t) \le T$  for all t. Since  $R^*$  is always wide-sense increasing, according to the definition of d(t), it can be obtained that  $R^*$  (t + T)  $\ge R(t)$ . On the contrary, it can be deduced that if  $R^*$  (t + T)  $\ge R(t)$ , then  $d(t) \le T$ . It can be said that if  $R^*$  (t + T)  $\ge R(t)$  for all t, the maximum delay is bounded by T. This formula can also be expressed as

$$R^*(s) \ge R(s-T) \tag{3-12}$$

for all  $s \ge T$ .

The "impulse" function  $\delta T$  defined by

$$\delta T(t) = 0 \text{ if } 0 \le t \le T \text{ and } \delta T(t) = +\infty \text{ if } t > T.$$

For any wide-sense increasing function x(t), defined for  $t \le 0$ ,  $(X \otimes \delta T)(t) = X(t-T)$  if  $t \ge T$  and  $(X \otimes \delta T)(t) = X(0)$  otherwise. Then the maximum delay can thus be illustrated as

$$R^* \ge R \otimes \delta T \tag{3-13}$$

It can be seen from these two examples above that an input-output relationship of the same form is inferred (formula (3-12) and (3-13)).

Figure 3-6 Service Curve [53]

Consider a system S with a flow through it. This flow has the input and output function which are R and R\*. It can be said that system S offers to the flow a service curve  $\beta$  if and only if  $\beta$  is wide sense increasing. At the same time,  $\beta(0) = 0$  and  $R^* \ge R \otimes \beta$ .

If the service curve  $\beta$  is continuous, it means that for all t, when  $t_0 \le t$

$$R^*(t) \ge R_l(t_0) + \beta(t - t_0) \tag{3-14}$$

Where  $R_l(t_0) = \sup_{\{s < t_0\}} R(s)$  is the limit to the left of R at  $t_0$ . If R is left-continuous, then  $R_l(t_0) = R(t_0)$ .

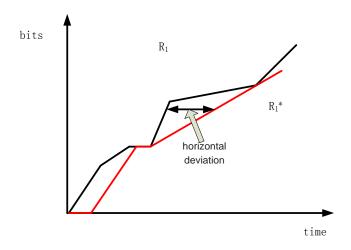

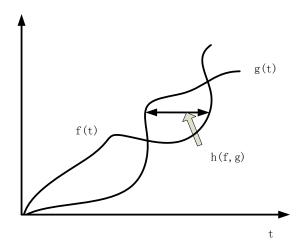

# 3.5 Network Delay Bound

In the network calculus, one important quantity is the maximum horizontal deviation between two curves f and g of the function F. The function F is a widesense increasing function equals to zero when negative arguments. This horizontal deviation is represented as h(f,g) while  $h(f,g) = \sup_{t \geq 0} \{\inf\{d \geq 0 | f(t) \leq g(t+d)\}\}$

Figure 3-7 The Horizontal Deviation Between f and g

Assume a flow, constrained by the arrival curve  $\alpha$ , traverses a system that offers a service curve of  $\beta$ . The virtual delay d(t) for all t satisfies: d(t)  $\leq$  h( $\alpha$ , $\beta$ ). Then h( $\alpha$ , $\beta$ ) is the network delay bound this flow experiences.

# 3.6 AFDX Network Time Delay Analysis

# 3.6.1 AFDX Network Time Delay Model

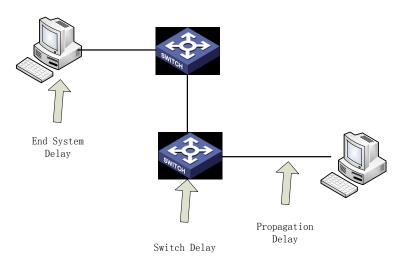

Three delays which consist of the AFDX network delay are the end system delay, the AFDX switch delay and the propagation delay (See Figure 3-8).

Figure 3-8 AFDX Network Time Delay

The end system delay is consisted of the Band Allocated Gap, the scheduler delay and the hardware process delay.

The switch delay is consisted of the scheduler delay and hardware process delay.

The propagation delay is consisted of the frames transmission delay and the signal transmission delay.

## 3.6.1.1 End System Time Delay Model

The end system is used to send and to receive the AFDX packets between the avionics applications and the AFDX switches. All these packets are generated by the avionics applications and transmitted through the virtual links. The traffic regulator introduces the BAG to control the traffic rate on each virtual link which constraints the bandwidth utility of each virtual link. The scheduler handles the concurrency data traffic depending on the particular scheduling mechanism which introduces the additional latency (See Figure 3-9).

End System

Figure 3-9 End System Delay Model

#### 3.6.1.2 Switch Model

An AFDX switch is proposed to receiving the AFDX packets from the source end system and forwarding those packets to the destination end systems.

Usually, the AFDX switch contains one FIFO buffer for each output port. Also, the input ports buffers are not involved. This is common in switch models [14][15][56].

An example of the AFDX switch model for virtual link scheduling is shown in Figure 3-10.

Figure 3-10 AFDX Switch Time Delay Model

The Ethernet frames transmit through the exclusive buffers of input ports. It is known that the minimum size of the frame is 576 bits while the minimum interframe gap is 96 bit times. When the 10 Mb/s Ethernet is proposed, the minimum transmission time is 57.6+9.6 microseconds. If this frame transmits on 100Mb/s Ethernet, the transmission time is 5.76+0.96 microseconds.

This switch module forwards the received packet from the input port to destination virtual link queue by checking a static forwarding table. This check needs a stationary time cost no matter how large the packet size is. To meet this requirement, a powerful forwarding capacity of AFDX switch should possess which can transfer each received packet to its corresponding output port queue before the next packet arrives.

As shown in Figure 3-10, the structure of multiple virtual links queues and a scheduler consolidated at each output port are familiar to the end system. In this section, the output waiting in the queue is the main delay component which

will be analysed. Messages at each output port in the virtual link queues will be scheduled and then transferred into the physical link.

#### 3.6.2 AFDX Traffic and Service Model

In this part, a brief introduction to the theory of network calculus will be given, and then the approaches utilising network calculus to represent the AFDX data flows and the entities will then be illustrated.

According to [53], the network data flows can be modelled by the leaky bucket or generic cell rate algorithm, i.e. the  $(\sigma,\rho)$  model and the GCRA model. The rate-latency function  $\beta(t) = R \cdot (t-T)$  is the general way to illustrate the service curve of AFDX network. In this formula, R is the service rate while T is the sum of AFDX node initial time and the queuing delay [57] [58].

#### 3.6.2.1 AFDX Illustration with Network Calculus

The AFDX virtual link is usually described by the leaky bucket model which illustrates the virtual link flow after being regulated by the BAG and before this flow enters the end system scheduler. The arrival curve of this model can be represented as below:

$$\alpha_0(t) = \frac{L_{max}}{RAG}t + L_{max} \tag{3-15}$$

Where:

$L_{max}$  represents the largest frame size of this virtual link.

*BAG* expresses the minimum time interval between two consecutive frames of the same virtual link.

In this project, the traffic regulator is assumed to be powerful enough which can process and transfer frames instantly. No extra delay is imposed. Thus, the delay from traffic regulator will be added to the end-to-end delay for obtaining the total time delay.

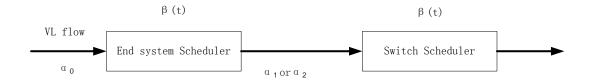

The AFDX data flow leaves the end system but before enters the first switch is modelled and represented in Figure 3-11. Since there is only one end system scheduler for various virtual links, it also assumes that the scheduler in end system brings a jitter  $\tau$ . Then the  $(\sigma,\rho)$  and GCRA model can be expressed as follows.

Figure 3-11 Virtual Link Model Cross End System and Switch

According to the  $(\sigma,\rho)$  model, the virtual link coming out from the end system is modelled as

$$\alpha_1(t) = \frac{L_{max}}{BAG}t + L_{max}(1 + \frac{\tau}{BAG})$$

(3-16)

Where:

$L_{max}$  is as same as represent by formula (3-15).

BAG is as same as represent by formula (3-15).

$\tau$  is jitter imposed by the scheduler in the end system.

According to [53],  $\tau$  can be measured but should be excluded from the end-to-end delay. Therefore, the sustainable rate of flow  $\sigma$  is  $L_{max}$  / BAG, and burst  $\rho$  is  $L_{max}$  .  $(1 + \frac{\tau}{BAG})$ .

When the GCRA model is applied, the virtual link flow can be illustrated as

$$\alpha_2(t) = L_{max} \left[ \frac{(t+\tau)}{BAG} \right]$$

(3-17)

Where:

$L_{max}$  is as same as represent by formula (3-16).

*BAG* is as same as represent by formula (3-16).

$\tau$  is as same as represent by formula (3-16).

The periodic tasks usually utilise the GCRA model to illustrate their flow characters, especially the network flows.

The rate-latency service curve proposed to illustrate the service capability of the scheduler of the switch and end system is listed below:

$$\beta(t) = R(t - T_0 - T_s)$$

(3-18)

Where:

*R* is the service rate of the output port of end system or switch, for instance, 10/100 Mbps in AFDX network.

$T_0$  represents the initial time of system.

$T_s$  expresses the queuing delay due to the resource competition among the virtual links.

As mentioned before, the horizontal distance between the arrival curve and service curve is the end-to-end delay bound. Basing on the "Pay Burst Only Once" phenomenon, once a data flow traverses several service nodes, the sequential service nodes can be treated as one integrated node. For this integrated node, its service curve is the convolution of the service of all the nodes which have been consolidated into this integrated node.

#### 3.6.2.2 End-to-End Delay Analysis

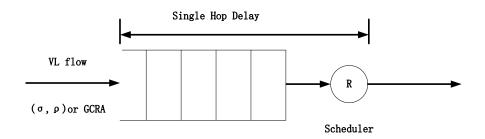

As can be seen in Figure 3-12, a single flow passes the switch scheduler is shown. In this section, the latency of this flow will be analysed, both GCRA model and  $(\sigma,\rho)$  model. Since this model is as same as the general process sharing model, the queuing delay  $T_s$  in formula (3-18) is set to 0.

Figure 3-12 Delay Bound For Single Virtual Link Cross Scheduler

(Delay bound for  $(\sigma,\rho)$  model) An AFDX node S has a rate latency service curve  $\beta$ . As defined in the formula (3-18), the service curve  $\beta(t) = R(t-T_0-T_s)$ . Since the  $T_s$  equals to 0, the service curve is  $\beta(t) = R(t-T_0)$ . Assume that the arrival curve of the input flow follows the  $(\sigma,\rho)$  model. Thus, it can be assumed that the delay bound of the flow traverses the node is