## Large Graphs on multi-GPUs

Enrico Mastrostefano

Submitted to the Department of Computer Science

in partial fulfillment of the requirements for the Degree of

Doctor of Philosophy in Computer Science

at the Sapienza University of Rome

January 9, 2013

## Introduction

A network can be defined as a set of interconnected nodes. This simple model describes many different phenomena and it is used in a wide range of disciplines from physics and biology to social sciences.

Over the years the size of the investigated networks has grown, leading to the definition of the so called large-scale networks which include hundred million or even billions of nodes. A well known and widely studied example is the World Wide Web, whose size is steadily growing: currently the number of web pages is tens of billions. Protein interaction networks, the human brain, the metabolic interaction networks, transportation networks and social networks are some other examples [48, 49, 61].

Different experimental studies, carried out in the last two decades, revealed that large-scale networks tend to form complex structures. Nodes tend to aggregate in dense clusters. Inside each cluster, several nodes, called hubs, have a large number of links whereas the most part of the other nodes have few [17, 34, 65, 74, 76].

From the theoretical point of view, large-scale networks can be described by using probabilistic graph models. They are generative models that permit to create a graph on the basis of some probabilistic rules. Through the use of these representations it is possible to study the time evolution of the network, 4 Introduction

*i.e.*, how nodes and links are added and removed from the network.

On the other hand, structural properties of networks are evaluated by means of common graph algorithms, like the minimum spanning tree or the Breadth First Search (BFS). Graph traversal algorithms like BFS are of fundamental importance in many practical applications (a traversal is a systematic method of exploring all vertices and edges in a graph). BFS serves as a building block for many other algorithms and is employed to compute important metrics used to characterize the network. For instance, BFS serves to identify community structures, that is, how vertices are connected each other, or to compute the *centrality* of a vertex, that is a measure of the importance of the vertex in the graph.

Due to the huge size, the traversal of large graphs is quite demanding in terms of both computational and memory resources, namely, it must be performed by using parallel computing architectures. Unfortunately, most graph algorithms are memory intensive and have irregular memory access patterns that strongly depend on the structure of the graph. These features make them ill-suited to modern high performance platforms. Nevertheless, several authors in the last few years have successfully implemented high performance graph traversals on both parallel and distributed architectures. They demonstrated that, by following appropriate strategies, graph algorithms can be accelerated by using modern supercomputers [13, 42, 30, 79].

There is a wide variety of parallel supercomputers but they can be grouped in two major categories: shared memory and distributed memory architectures. Shared memory systems have many advantages from the programming point of view but are limited both in the size of the memory and in the number of processors. On the other end, distributed systems are more difficult to program but can have thousands of computing nodes. In principle, with the help of a distributed architecture there is no limit to the size of the network that can be studied.

We focus our work on the development of a distributed algorithm to perform a BFS visit on a large graph. For the implementation of the computational part we resort to clusters of Graphic Processing Units (GPUs).

Generally, a distributed system is a cluster of computing nodes interconnected via a wired network. Communications are typically implemented by using the Message Passing Interface (MPI) primitives. Each node is a system in itself that can be equipped with a single- or a multi-core CPU. For the GPU clusters, each node hosts also one or more GPU devices. To carry out computations, the nodes of the cluster must exchange data each other.

Graph algorithms are notoriously difficult to parallelize. They have low arithmetic intensity: the time spent in computation is less then the time spent performing memory access operations. In a distributed environment, data can be in a remote memory, thus, most of the execution time, is spent sending and receiving data over the communication network. Moreover, communication patterns are irregular, the number and the size of messages exchanged may vary during the execution of the algorithm. As a consequence the performance bottleneck is represented by the communication among nodes [79, 51, 23].

To obtain a significant improvement on a single GPU and to scale by using multiple GPUs, we developed a novel algorithm. We propose a technique for mapping threads to data that achieves a perfect load balance by leveraging prefix-sum and a binary search operations. To reduce the communication overhead, we perform a pruning operation on the set of edges that needs to be exchanged at each BFS level. The result is an algorithm that exploits at its best the parallelism available on a single GPU and minimizes communication

6 Introduction

among GPUs. As far as we know this is the first attempt to implement a graph algorithm on multi-GPUs clusters.

Our code was submitted to the Graph 500 benchmark, a new graph-theoretical challenge. To complement the compute-intensive Top 500, Graph 500 evaluates performances of modern supercomputers on data-intensive applications. By using 128 GPUs we entered the Graph 500 list at position number 20 (November 2011 ranking).

Communication among GPUs that are located on different nodes of the cluster, involves the hosting CPU. Data must be transferred to the CPU before and after any MPI call. This requirement imposes an additional overhead to the data transfer. To overcome the issue several solutions have been proposed both at hardware and software level. One of these solutions is the APEnet+ interconnection technology. It allows for the transfer of data directly from GPU to the communication link by means of the *GPUdirect* feature, introduced in the latest NVIDIA cards.

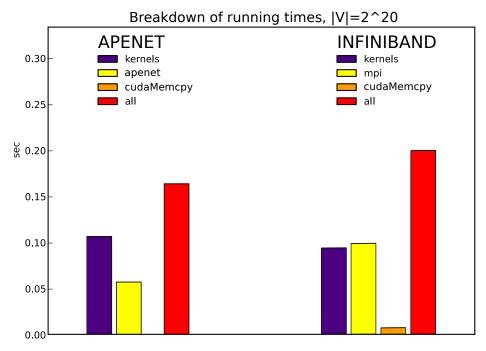

We adapted our original algorithm to use the *GPUdirect* technology. Our results, albeit preliminary, show a clear advantage with respect to classical interconnection technology (Infiniband). This result is of great interest considering that, these technologies, are an essential part of research efforts, towards the definition of a general mechanism for direct communication among GPUs.

The present dissertation is organized as follows. In the first Chapter we describe the problem of analyzing large graphs. We summarize the basic properties of large-scale networks and introduce some probabilistic models. Then we describe the serial BFS algorithm and the level synchronous BFS, which is of considerable importance in the parallel implementation of the

BFS. In the second Chapter we illustrate the GPU features and the CUDA programming model. The third Chapter deals with parallel BFS on shared memory systems; multi-core CPU and (single) GPU fall within this category. We describe two different algorithms to perform parallel BFS and give a short review of some recent works on both multi-core CPU and GPU. In the fourth Chapter we present our original study: the development of a distributed BFS. We report the issues related to the problem and review related works. We present our solution for a multi-GPUs cluster interconnected via the standard Infiniband technology and finally we extend our work to support the APEnet+ technology.

8 Introduction

# Contents

| In | trod | uction                                    |  | 3  |  |

|----|------|-------------------------------------------|--|----|--|

| 1  | Lar  | ge Graphs                                 |  | 11 |  |

|    | 1.1  | Random Graphs                             |  |    |  |

|    |      | 1.1.1 Basic graph notions                 |  | 13 |  |

|    |      | 1.1.2 Erdös-Rény random graphs            |  | 14 |  |

|    | 1.2  | Real world graph                          |  | 16 |  |

|    |      | 1.2.1 Real-world graph generators         |  | 17 |  |

|    | 1.3  | Analysis of large graphs                  |  | 19 |  |

|    |      | 1.3.1 Graph representation and serial BFS |  | 20 |  |

|    |      | 1.3.2 Level synchronous BFS               |  | 24 |  |

| 2  | GP   | Us and CUDA overview                      |  | 27 |  |

|    | 2.1  | The CUDA programming model                |  | 29 |  |

|    | 2.2  | SIMT Architecture                         |  | 33 |  |

|    | 2.3  | Memory Hierarchy                          |  | 34 |  |

|    | 2.4  | CUDA streams                              |  | 35 |  |

|    | 2.5  | Clusters of GPUs                          |  | 36 |  |

| 3  | Par  | allel BFS on shared memory systems        |  | 39 |  |

10 CONTENTS

|   | 3.1                      | Overv                              | Overview of shared memory systems                    |    |  |  |

|---|--------------------------|------------------------------------|------------------------------------------------------|----|--|--|

|   | 3.2                      | Overv                              | iew of parallel algorithms for BFS                   | 41 |  |  |

|   | 3.3                      | Parall                             | el BFS on multi-cores CPU                            | 45 |  |  |

|   | 3.4                      | Parall                             | el BFS on GPU                                        | 47 |  |  |

| 4 | Par                      | allel B                            | FS on distributed memory systems                     | 55 |  |  |

|   | 4.1                      | Relate                             | ed Works                                             | 59 |  |  |

|   | 4.2                      | 2 BFS on a multi-GPUs architecture |                                                      |    |  |  |

|   |                          | 4.2.1                              | Graph generation                                     | 62 |  |  |

|   |                          | 4.2.2                              | Distributed data structure                           | 63 |  |  |

|   |                          | 4.2.3                              | Straightforward implementation                       | 66 |  |  |

|   | 4.3                      | Optin                              | nized BFS on a multi-GPU platform                    | 69 |  |  |

|   |                          | 4.3.1                              | Motivation                                           | 69 |  |  |

|   |                          | 4.3.2                              | Algorithm overview                                   | 70 |  |  |

|   |                          | 4.3.3                              | Results                                              | 75 |  |  |

|   |                          | 4.3.4                              | Graph 500 benchmark                                  | 78 |  |  |

|   |                          | 4.3.5                              | Comparison among implementations on different archi- |    |  |  |

|   |                          |                                    | tectures                                             | 83 |  |  |

|   | 4.4                      | APEn                               | et interconnection                                   | 87 |  |  |

|   |                          | 4.4.1                              | APEnet                                               | 87 |  |  |

|   |                          | 4.4.2                              | Implementation on APEnet                             | 89 |  |  |

| 5 | Cor                      | ıclusio                            | ns and future works                                  | 93 |  |  |

|   | 5.1                      | Summ                               | nary                                                 | 93 |  |  |

|   | 5.2                      | Future                             | e work                                               | 96 |  |  |

|   | 5.3 Space-time trade off |                                    |                                                      |    |  |  |

## Chapter 1

# Large Graphs

A number of natural and artificial phenomena may be described by using networks, i.e. sets of interconnected nodes. Over the years, the size of the studied networks has grown. Nowadays, networks with millions of vertices and hundred million or even billions of edges are studied after being extracted starting from huge datasets. A well know and widely studied example is the Internet. Internet represents also the infrastructure of the World Wide Web, a network made of hyperlinks, and of many Social Networks, that represent relationships among individuals (or web sites where people waste their time). The size of the Internet is growing fast: currently the number of web pages may be 30 billion or more <sup>1</sup>, and the number of connected—devices is probably more than a billion.

Social networks are very attractive for many researchers in the area of sociology, history, epidemiology and economics. Well established social networks like Facebook, MSN Messenger or Twitter have hundred million links. Protein interaction networks, the human brain and the metabolic interaction

<sup>&</sup>lt;sup>1</sup>http://www.worldwidewebsize.com/

networks are some examples from biology. The human brain network is one of the most complex with its  $\sim 10^{11}$  nodes[48, 49, 61].

Networks, like those mentioned above, are often described as large graphs having millions of vertices and billions of edges. The theoretical formalization of such large graphs falls within the theory of random graphs. Several probabilistic/stochastic models have been proposed to mimic their structure and evolution. New metrics have been introduced to better characterize their properties. Those metrics are computed on the basis of common graph algorithms, like single source shortest path, minimum spanning tree and Breadth First Search (BFS).

Even the execution of a simple algorithm, like BFS, on a graph with billions of edges, requires the use of a parallel computing architecture. While serial algorithms on graphs have been widely studied and can be efficiently implemented, the corresponding parallel versions are still lacking behind. Parallel graph algorithms are challenging for many reasons (as we will discuss in the following). For instance, most algorithms are memory intensive and have irregular memory access patterns that strongly depend on the structure of the graph. These features make them ill-suited to modern high performance architectures. Nevertheless, recent studies [13, 42, 30] have demonstrated that, with appropriate strategies, graph algorithms can be accelerated by using modern parallel supercomputers.

This chapter is devoted to an introduction to large graphs and the breadth first search algorithm, whereas, in the next chapter, we will introduce the main features of modern GPUs.

### 1.1 Random Graphs

Random graphs are powerful mathematical models to study large networks. They are generative models that permit to produce a graph on the basis of some probabilistic rules. Most often the models do not impose a certain property to the network but rather give general principles or mechanisms of edge creation that lead to the rise of a global statistical property or distribution in the network [46].

Many models aim at describing the structure and also the evolution of the network over time, i.e. how nodes and edges are added and removed from the network. In the present work, we are not interested in the evolution of the graph but only in its structure.

In the next two sections we report few basic definitions and notions on (random) graphs.

#### 1.1.1 Basic graph notions

G(V, E) is a graph G whose vertices v belong to the set V and whose edges  $e = (u, v); u, v \in V$  belong to the set E. N = |V| is the number of vertices in G whereas, M = |E| is the number of edges. We will denote the number of vertices and edges with |V| and |E| or N and M.

G can be:

- **directed**: if the pair (u, v) is oriented.

- weighted: if each edge e has associated a scalar value  $p_e$ .

- multi-graph: there can be multiple edges between two vertices.

- simple: unweighted, undirected graph containing neither graph loops nor multiple edges.

Unless explicitly stated, we consider only simple graphs.

A path between two vertices  $u, v \in V$  is a sequence of edges from u to v. A closed path in which some vertices are repeated is called **cycle**. G is said to be **connected** if there exist a path between any two vertices in V. A **tree** is a connected graph with no cycle. A graph can have many **connected components**, i.e., subsets of nodes that are connected. If G is simple and every pair of distinct vertices is connected by a unique edge, then G is **complete**. Given any two nodes  $u_1$ ,  $u_2$  in G, the **distance**, is measured as the shortest path that connects them. The **diameter** is the maximum distance in G.

The **degree** of a node is defined as the number of edges incident to the vertex. The total degree of G then is  $\sum_{v \in V} deg(v) = 2|E|$ . The degree of a vertex is an important metric, many structural properties of graphs can be deduced from the knowledge of the degree of all the nodes.

#### 1.1.2 Erdös-Rény random graphs

The earliest probabilistic generative model for graphs was the random graph model introduced by Erdös and Rény in 1960 [32] and Gilbert in 1959 [35].

Consider a set of vertices V=1,...,n and let an edge between any two nodes, i and j, be formed with probability p, where 0 . The formation of edges is independent. The corresponding graph is <math>G(n,p). This is a binomial model of link formation, which gives rise to a manageable set of calculations regarding the resulting structure. The average number of edges on the graph as a whole is  $\frac{1}{2}n(n-1)p$ , whereas the average degree of a vertex is:

$$z = \frac{n(n-1)p}{n} = (n-1)p \simeq np,$$

where the approximation holds for large values of n.

One interesting feature, originally demonstrated by Erdös and Rény, is that, when the value of z varies, from 0 to a positive integer, the model shows a phase transition, exactly in z = 1. For z < 1, there are few edges in the graph and most vertices are disconnected from each other. However, when z is approaching the value of 1, there is one largest component that contains a finite fraction F of the total number of vertices. The size of F scales linearly with the size of F and it is called giant component. The size of the other components in the graph remains constant as the graph size increases. It can be proved that, for a large value of F0, the size of the remaining components is of order log(n).

We can calculate some statistics that describe the graph. For instance, we can find the degree distribution fairly easily. The degree distribution of a random graph describes the probability that a given node has degree d. The probability that a given node i has exactly k edges is:

$$P(d = k) = \left(\frac{n-1}{k}\right) p^k (1-p)^{n-1-k}$$

For large values of n and small values of p the binomial expression can be approximated by the Poisson distribution. Both binomial and Poisson distributions are strongly peaked about the mean d, and have a large tail that decays rapidly as 1/k.

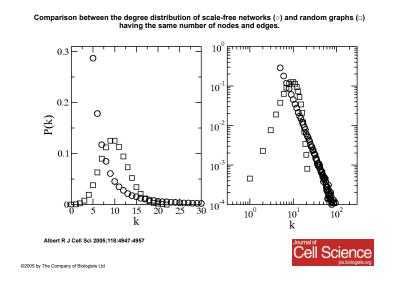

The degree distribution provides a number of information about the structure of the graph. For instance, a Poisson distribution implies that most vertices have a degree close to the average value (see figure 1.1).

The main drawback of the random graph model is that it produces graphs that fail to match real-world networks.

16 Large Graphs

### 1.2 Real world graph

Many studies show that the features of real world (large) networks cannot be described with the classical random graph model.

The most important difference is that, real world networks exhibit a power law distribution of the degree:  $P(d=k)=Ck^{-\gamma},\ k\to\infty$ .

The power law distribution has been found in various real datasets like, for instance:

- World Wide Web: considering pages as vertices and links as edges [17].

- Internet: at the level of so-called "autonomous systems" <sup>2</sup> [34].

- Citation network: in which the nodes are papers and citations are links [65].

- Protein-protein interaction networks [74].

In figure 1.1 are plotted, for comparison, the Poisson distribution and a power law with  $\gamma=3$ .

In order to mimic the power law distribution, Barabasi and Albert [17] proposed the preferential attachment model. Instead of adding edges with uniform probability, edges are connected to vertices with a probability proportional to their popularity. Suppose to add a vertex to the graph, then edges are added one at time. The probability that the new vertex will be attached to vertex i is given by:  $\pi_i = k_i / \sum_j k_j$ .

Erdös and Rény graphs have small diameter, but have few triangles. Real-world graphs, like those from social networks, contain many (if A and B are friends and A and C are friends, then it is fairly likely that B and C

<sup>&</sup>lt;sup>2</sup>An autonomous system is a group of computers within which data flow is handled autonomously, while data flow among groups is conveyed over the public Internet

are also friends). To construct a network with small diameter and positive density of triangles, Watts and Strogatz [76] started from a ring lattice with n vertices and k edges per vertex, then rewired each edge with a probability p, connecting one end to a vertex chosen at random. The resulting graph is connected by definition and has short diameter, it is in fact called small-world graph.

The power law distribution is often called scale-free distribution and, networks that obey that distribution, are called scale-free networks.

The skewed distribution associated with real-world graphs implies that some special vertices, called hubs, have an huge number of neighbors whereas most of them have few (see fig 1.1). As we shall discuss below, this property has negative side effects on the parallel implementation of graph algorithms since it can lead to a severe imbalance of workload among the tasks (see section 1.3.2). On the other end, the small diameter property, has positive consequences. For instance, the number of iterations of a parallel BFS is proportional to the diameter of the graph (see section 1.3.2).

It is worth noting that most of real-world networks can be represented by means of a sparse graph that is, the number of edges is much smaller than the maximum number of possible edges:  $|E| \ll |V|^2$ .

### 1.2.1 Real-world graph generators

In parallel with the study of the structural properties of real-world graphs, there has been an effort to find practical mechanisms to generate graphs that have the desired properties. As stated in [47] to have realistic generators is important for at least two reasons. First they allow to simulate a graph for testing theoretical hypothesis and can be used to simulate different scenarios. Second they give some insights on the networks properties thus helping the

Figure 1.1. Comparison between the degree distribution of scale-free networks ( $\circ$ ) and random graphs ( $\square$ ) having the same number of nodes and edges. For clarity the same two distributions are plotted both on a linear (left) and logarithmic (right) scale. The bell-shaped degree distribution of random graphs peaks at the average degree and decreases fast for both smaller and larger degrees, indicating that these graphs are statistically homogeneous. By contrast, the degree distribution of the scale-free network follows the power law  $P(k) = Ak^{-3}$ , which appears as a straight line on a logarithmic plot. The continuously decreasing degree distribution indicates that low-degree nodes have the highest frequencies. However, there is a broad degree range with non-zero abundance of very highly connected nodes (hubs) as well. Note that the nodes in a scale-free network do not fall into two separable classes corresponding to low-degree nodes and hubs, but every degree between these two limits appears with a frequency given by P(k).

development of theoretical models. One of the most successful generator is the R-MAT generator [25]. It is based on a Recursive Matrix approach, in which the adjacency matrix that represents the graph is recursively subdivided and then populated, following certain probabilistic rules. The whole matrix is divided in four partitions, each partition has associated a probability: a, b, c, d. Then, each partition is again divided in four and this procedure is repeated until the simple cell is reached.

This model has gained much popularity, for instance, the novel Graph 500 benchmark chose this generator to create the input graph that has to be analyzed.

By changing the value of the four parameters, a, b, c, d the properties of the produced graph vary accordingly. For a=b=c=d=0.25 the model reproduces the standard, Erdös-Rényi, random graph. On the other end, the values a=0.57, b=0.19, c=0.19, and d=0.05, provides a steep degree distribution power-law graph. This produces a maximum degree of approximately  $200.000=2^{17.64}$ , with  $2^{25}$  vertices and  $2^{28}$  edges [58].

Our work, and most of the studies that we will review, rely on an R-MAT generator to produce large graphs with the desired properties.

### 1.3 Analysis of large graphs

Specific properties of large graphs are described by means of a set of new metrics. For instance, the *betweenness centrality* measures the centrality of a node in a network. It is equal to the number of shortest paths from all vertices to all others that pass through that node.

As already stated, the size of the most interesting graphs requires the use of parallel computing systems. However, graph algorithms are a typical example of applications for which it is not simple to have a sizeable advantage by using parallel computing architectures. To gain a better understanding of the issues due to implementation of algorithms with irregular memory access patterns, like those in use for studying graphs, many recent studies focus on (apparently) simple problems. Several communities have proposed computational challenges having as subject graphs. For instance, the 9 DI-

20 Large Graphs

MACS challenge [1] aims at finding shortest path in graphs, the Graph 500 [2] benchmark uses BFS as its core, SSCA#2 benchmark is composed of four kernels operating on large scale directed multi-graphs [5]. Hereafter we focus on BFS.

Breadth first search is a simple graph algorithm that is widely used as a building block for more complex algorithms. For instance it can be used to find the connected components in a graph or to compute the shortest path between two vertices. It is representative of a class of algorithms for which is hard to obtain a significant speed up from parallelization.

In the following sections, we discuss the serial BFS and the level synchronous BFS algorithm. The latter is of considerable importance in the implementation of parallel algorithms.

#### 1.3.1 Graph representation and serial BFS

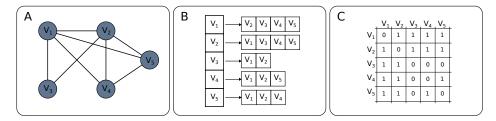

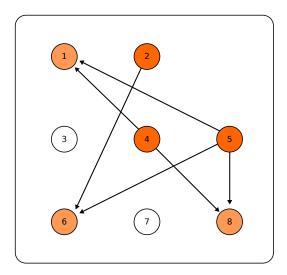

There are two common ways to represent a graph G = (V, E): with either a set of adjacency lists or an adjacency matrix. The adjacency list representation is preferable when the graph is **sparse** i.e.  $|E| << |V|^2$  because is more compact. The adjacency matrix should be preferred when the graph is **dense** i.e.  $|E| \sim |V|^2$ . The adjacency list representation of a graph is implemented via a set of |V| lists, one for each vertex of the graph. For each  $u \in V$  the adjacency list of u contains all the vertices v such that there is an edge (u, v) in E (see figure 1.2).

Given the graph G = (V, E) and a source (or root) vertex s, the breadth first search explores each edge of G to discover all vertices that are reachable from s. BFS is widely studied because it is part of more complex algorithms. Here we summarize only those aspects that will be relevant for the rest of the present work, for further information see [27].

**Figure 1.2.** In panel A is represented an undirected graph G(V,E)=G(5,16). In panel B is provided the adjacency list representation of G. Panel C is the adjacency matrix of G.

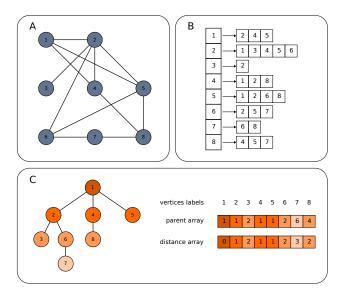

Algorithm (1) presents an implementation of the BFS, where the graph G is undirected and represented as an adjacency list (fig 1.3 A, B).

#### Algorithm 1 Serial BFS

```

1: d[u] \leftarrow -1, \forall u \in V

2: p[u] \leftarrow -1, \forall u \in V

3: d[s] = 0

4: p[s] = s

5: enqueue(Q, s)

6: while Q \neq \emptyset do

u \leftarrow dequeue(Q)

8:

for each v \in Adj[u] do

if p[u] == -1 then

9:

10:

p[v] = u

d[v] = d[u] + 1

11:

enqueue(Q, v)

12:

end if

13:

end for

14:

15: end while

```

The algorithm starts by visiting the source vertex s; its distance d[s] and its predecessor p[s] (line 3-4) are set, then the vertex is enqueued in Q. At each iteration, the first vertex of the queue is dequeued, all its neighbors are inspected and, if the value of their distance and/or predecessor are not set (line 9), that is they have never been seen, they are added to the queue. The

22 Large Graphs

algorithm ends when all reachable vertices have been visited and the queue is empty.

**Figure 1.3.** In panel A is represented an undirected graph. In panel B is provided the adjacency list representation of the graph. Panel C shows the result of one BFS visit started from vertex 1. On the left is depicted the BFS-tree rooted at 1. On the right, the parent and the distance arrays. The colors highlight different levels of the BFS.

The BFS procedure "expands the frontier between discovered and undiscovered vertices uniformly across the breadth of the frontier"  $^3$ , so that, all vertices at distance k are discovered before any vertices at distance k+1. At the end of the procedure, the distance array contains the shortest path from s to any reachable vertex in the graph [27]. The array of predecessors or parent contains a BFS-tree rooted at s: each index of the array is a vertex in the graph and the corresponding value is the predecessor in the BFS-tree. It is worth noting that BFS explores only the connected component that contains the source vertex s.

$<sup>^3</sup>$ From [27]

**Table 1.1.** The table is referred to the graph in figure (1.3). The BFS is started at vertex 1 and new vertices visited are added to next level, according to algorithm (1).

| BFS LEVEL | CQ    | NLFS                    | NQ    |

|-----------|-------|-------------------------|-------|

| 0         | 1     | 2,4,5                   | 2,4,5 |

| 1         | 2,4,5 | 1,3,4,5,6,1,2,8,1,2,6,8 | 3,6,8 |

| 2         | 3,6,8 | 2,2,5,7,4,5,7           | 7     |

| 3         | 7     | 6,8                     |       |

Figure (1.3 C) depicts the result of the algorithm (1) applied to the graph shown in fig. (1.3). Table 1.1 shows the levels of the BFS performed on the graph represented in figure (1.3).

The time complexity of the BFS is given by the time for the queue operation that is O(V), plus the time for scanning each adjacency list, that is O(E). The initialization takes O(V) and thus the total time, O(V + E), is linear in the size of the adjacency list.

#### 1.3.2 Level synchronous BFS

Breadth first search, as many graph algorithms, is memory-bound and memory access patterns are fine-grained and irregular. These features cause poor performances on shared memory systems, that are cache-based [13, 7]. On a distributed memory system the running time of the algorithm is dominated by the communication part [79, 23, 73] and is difficult to outperform the sequential version. Most of the parallel implementations, on both type of architectures, are based on the level synchronous BFS algorithm.

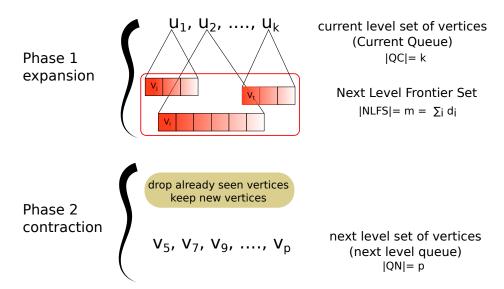

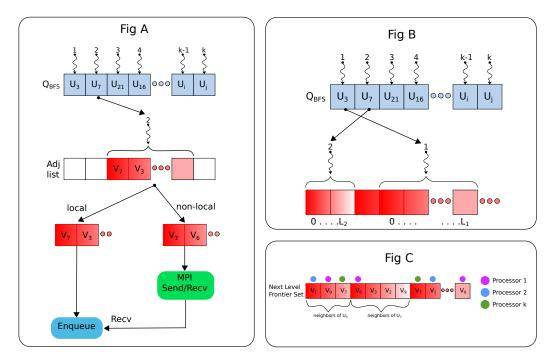

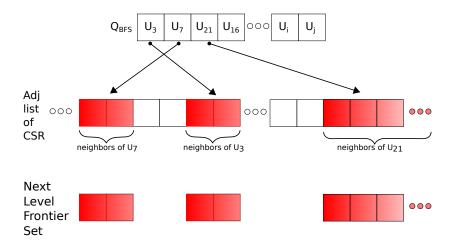

In the level synchronous BFS, the current queue, CQ, is seen as a current level set of vertices. For each vertex in the current level, all its neighbors must be visited. In parallel systems, this operation, is always carried out in parallel. The set of all neighbors composes the *Next Level Frontier Set* (NLFS). From the NLFS only new vertices are selected to build the queue for the next level (figure 1.4).

The BFS visit is divided into levels with a distance from the root that increases at each subsequent level. For a graph with diameter D, the number of levels visited by the algorithm will be at least D/2 and at most D, depending on where the search is initiated.

This method is referred in literature as **Level Synchronous BFS** because, to ensure the correctness of the computation in a parallel implementation, a synchronization is required at the end of each level.

As shown in figure 1.4, the total number of elements in the CQ is |CQ| = k. The total number of elements in the NLFS is  $\sum_{i=0}^{k} d_{u_k}$ , the sum of all degrees of vertices in the queue.

Real-world graphs have skewed degree distributions (see section 1.2). While many of the vertices have a small number of neighbors, hubs can have thousands. The degrees of the vertices may differ from each other, by

**Figure 1.4.** BFS phases: In the first phase, all neighbors of each vertex in the current queue are inserted in the NLFS. In the second phase vertices already seen in the NLFS are removed. The remaining vertices are inserted in the next level queue. The total number of elements in the NLFS is equal to the sum of the degrees of all elements in the queue.

several orders of magnitude. Consequently the NLFS can be greater than the queue by several order of magnitude. Moreover, it will expand and contract very quickly. Thus, the number of BFS levels is always small compared to the number of elements in the graph.

If there are k tasks, one for each element of the queue, during the expansion phase, each task has to visit the neighbors of its element. The workload among tasks is clearly unbalanced.

It is important to realize that, the size of the NLFS, is much greater than the size of the other structures used in the algorithm. Thus, for most implementations, the number of memory accesses during the BFS is in the order of the NLFS size.

Now suppose that the graph is stored as an adjacency lists structure,

26 Large Graphs

and is loaded in the main memory of the system. At the beginning of each iteration of the algorithm, each task reads a vertex from the CQ. Then it starts to visit the neighbors of its vertex. Task 1 starts to visit the adjacency list of vertex  $u_1$ , Task 2 visits the adjacency list of  $u_2$  and so on. The adjacency lists are not always in contiguous memory locations. The more distant they are, the more expensive it will be to visit them, in terms of memory accesses.

The vertices in the queue, change at each iteration, as well as the vertices in the NLFS. Thus, memory accesses, are irregular and not predictable. It should also be clear, by now, that they strongly depend on the structure of the graph. For real-world graphs, the situation is exacerbated by the enormous difference in the size of adjacency lists.

In Chapter 3 we will describe the issues in a parallel implementation on a shared memory system. Distributed systems have different issues, related to the communication among tasks, that will be described in Chapter 4.

## Chapter 2

## GPUs and CUDA overview

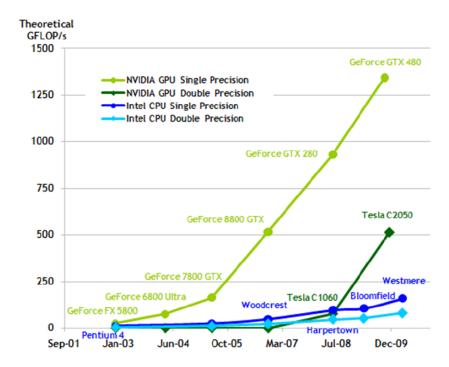

In the last 5 years, driven by a steadily growing request for real-time, high-definition 3D graphics, Graphic Processor Units or GPUs have evolved becoming highly parallel, multi-threaded, processors with huge computing power and very high memory bandwidth, as illustrated by Figure 2.1.

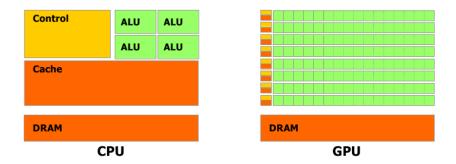

The reason behind the discrepancy in floating-point processing capability between the CPU and the GPU is that the GPU is specialized for compute-intensive, highly parallel computations - exactly what graphics rendering is about - and therefore designed such that more transistors are devoted to data processing rather than data caching and flow control, as schematically illustrated by Figure 2.2.

In general, the GPU is especially well-suited to address problems that can be expressed as data-parallel computations - the same program is executed on many data elements in parallel - with high arithmetic intensity - the ratio of arithmetic operations to memory operations. Because the same program is executed for each data element, there is a lower requirement for sophisticated flow control, and because it is executed on many data elements and has high

Figure 2.1. Floating-Point operations per second for a CPU and a GPU.

arithmetic intensity, the memory access latency can be hidden with calculations instead of resorting to large data caches. Data-parallel processing maps data elements to parallel processing threads. Many applications that process large data sets can use a data-parallel programming model to speed up the computations. In 3D rendering, large sets of pixels and vertices are mapped to parallel threads. Similarly, image and media processing applications such as post-processing of rendered images, video encoding and decoding, image scaling, stereo vision, and pattern recognition can map image blocks and pixels to parallel processing threads. As a matter of fact, many algorithms, beside image rendering, may be accelerated by data-parallel processing, from general signal processing or physics simulations to computational finance or computational biology.

Figure 2.2. In a GPU more transistor are devoted to data processing.

In November 2006, NVIDIA introduced CUDA, a general purpose parallel computing architecture (with a new parallel programming model and instruction set architecture) that leverages the parallel compute engine in NVIDIA GPUs to solve many complex computational problems in a more efficient way than on a CPU. CUDA comes with a software environment that allows developers to use C as a high-level programming language.

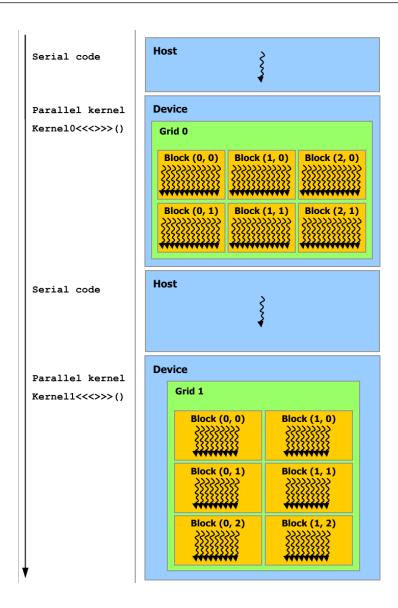

## 2.1 The CUDA programming model

The advent of multi-core CPUs and many-core GPUs means that mainstream processor chips are now parallel systems. Furthermore, their parallelism continues to scale with Moore's law. The challenge is to develop application software that transparently scales its parallelism to leverage the increasing number of processor cores, much as 3D graphics applications transparently scale their parallelism to many-core GPUs with widely varying numbers of cores. The CUDA parallel programming model is designed to overcome this challenge while maintaining a low learning curve for programmers familiar with standard programming languages such as C. At its core are three key abstractions, a hierarchy of thread groups, shared memories, and barrier syn-

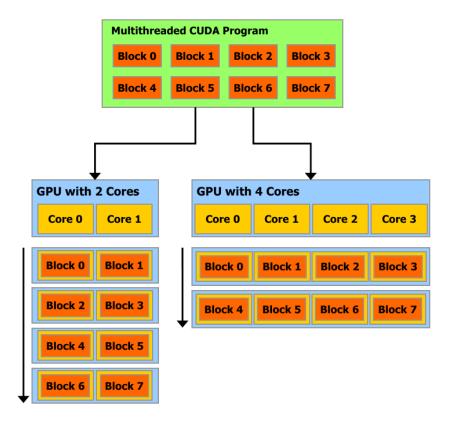

chronization, that are simply exposed to the programmer as a minimal set of language extensions. These abstractions provide fine-grained data parallelism and thread parallelism, nested within coarse-grained data parallelism and task parallelism. They guide the programmer to partition the problem into coarse sub-problems that can be solved independently in parallel by blocks of threads, and each sub-problem into finer pieces that can be solved cooperatively in parallel by all threads within the block. This decomposition preserves language expressivity by allowing threads to cooperate when solving each sub-problem, and at the same time enables automatic scalability. Indeed, each block of threads can be scheduled on any of the available processor cores, in any order, concurrently or sequentially, so that a compiled CUDA program can execute on any number of processor cores as illustrated by Figure 2.3, and only the runtime system needs to know the physical processor count.

This scalable programming model allows the CUDA architecture to span a wide market range by simply scaling the number of processors and memory partitions.

CUDA C extends C by allowing the programmer to define C functions, called kernels, that, when called, are executed N times in parallel by N different CUDA threads, as opposed to single execution like regular C functions. Each thread that executes the kernel is given a unique thread ID that is accessible within the kernel through a built-in threadIdx variable.

For convenience, threadIdx is a 3-component vector, so that threads can be identified using a one-dimensional, two-dimensional, or three-dimensional thread index, forming a one-dimensional, two-dimensional, or three-dimensional thread block. This provides a natural way to invoke computation across the elements in a domain such as a vector, matrix, or volume. The index of a

**Figure 2.3.** A multithreaded program is partitioned into blocks of threads that execute independently from each other, so that a GPU with more cores will automatically execute the program in less time than a GPU with fewer cores.

thread and its thread ID relate to each other in a straightforward way: for a one-dimensional block, they are the same; for a two-dimensional block of size (Dx, Dy), the thread ID of a thread of index (x, y) is (x + yDx); for a three-dimensional block of size (Dx, Dy, Dz), the thread ID of a thread of index (x, y, z) is (x + yDx + zDxDy).

There is a limit to the number of threads per block, since all threads of a block are expected to reside on the same multiprocessor and must share the limited memory resources available on that core. On current GPUs, a thread

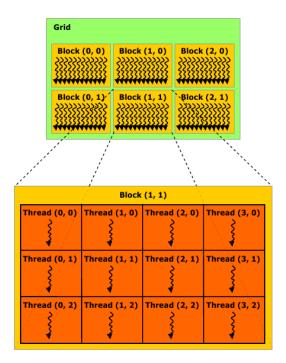

Figure 2.4. Grid of thread blocks.

block may contain up to 1536 threads. However, a kernel can be executed by multiple equally-shaped thread blocks, so that the total number of threads is equal to the number of threads per block times the number of blocks. Blocks are organized into a one-dimensional, two-dimensional or tri-dimensional grid of thread blocks as illustrated by Figure 2.4. The number of thread blocks in a grid is usually dictated by the size of the data being processed or the number of processors in the system, which it can greatly exceed.

The number of threads per block and the number of blocks per grid are specified in the kernel call. Each block within the grid can be identified by a multi-dimensional index accessible within the kernel through the built-in blockIdx variable. The dimension of the thread block is accessible within the kernel through the built-in blockDim variable.

Thread blocks are required to execute independently: it must be possible to execute them in any order, in parallel or in series. This independence requirement allows thread blocks to be scheduled in any order across any number of cores as illustrated by Figure 2.3, enabling programmers to write code that scales with the number of cores. Threads within a block can cooperate by sharing data through some shared memory and by synchronizing their execution to coordinate memory accesses. More precisely, one can specify synchronization points in the kernel by calling a specific intrinsic function that acts as a barrier at which all threads in the block must wait before any is allowed to proceed. For efficient cooperation, the shared memory is expected to be a low-latency memory near each processor core (much like an L1 cache).

#### 2.2 SIMT Architecture

GPU is a multiprocessor designed to execute hundreds of threads concurrently. To manage such a large number of threads, it employs a unique architecture called SIMT (Single-Instruction, Multiple-Thread). The multiprocessor manages threads in groups of 32, called warps. Individual threads composing a warp start together but have their own instruction address counter and register state and are therefore free to branch and execute independently. When one or more thread blocks are assigned to the multiprocessor, it divides them into warps and each warp is then scheduled for execution. A warp executes one common instruction at a time, so, to obtain the highest concurrency and the best performances, all 32 threads should have the same execution path. If threads diverge to follow different conditional branches, the warp serially executes each branch. However branch divergence occurs

only at the warp level. Different warps always execute instruction independently.

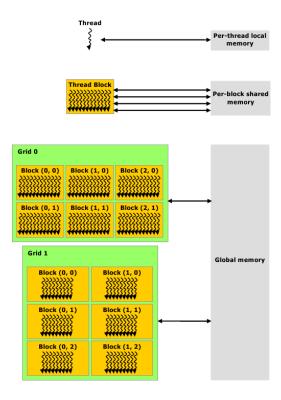

### 2.3 Memory Hierarchy

CUDA threads may access data from multiple memory spaces during their execution as illustrated by Figure 2.5. Each thread has private local memory. Each thread block has shared memory visible to all threads in the block and with the same lifetime as the block. All threads have access to the same global memory. There are also two additional read-only memory spaces accessible by all threads: the constant and texture memory spaces. The global, constant, and texture memory spaces are optimized for different memory usages (see [63]). Texture memory also offers different addressing modes, as well as data filtering, for some specific data formats (see [63]). The global, constant, and texture memory spaces are persistent across kernel launches by the same application.

As illustrated by Figure 2.6, the CUDA programming model assumes that the CUDA threads execute on a physically separate device that operates as a coprocessor to the host running the C program. This is the case, for example, when the kernels execute on a GPU and the rest of the C program executes on a CPU. The CUDA programming model also assumes that both the host and the device maintain their own separate memory spaces in DRAM, referred to as host memory and device memory, respectively. Therefore, a program manages the global, constant, and texture memory spaces visible to kernels through calls to the CUDA runtime (see [63]). This includes device memory allocation and deallocation as well as data transfer between host and device memory.

Figure 2.5. GPU memory hierarchy.

#### 2.4 CUDA streams

CUDA supports concurrency within an application through *streams*. A stream is a sequence of commands that are executed in order. Different streams, on the other hand, may execute their commands out of order with respect to each other or concurrently. The amount of execution overlap between two streams depends on the order in which the commands are issued to each stream and whether or not the GPU supports overlap of data transfer and kernel execution. Further information about *streams* can be found in the CUDA documentation [63].

**Figure 2.6.** Heterogeneous programming: serial code executes on the host whereas parallel code executes on the device.

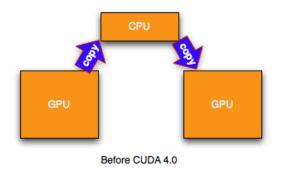

## 2.5 Clusters of GPUs

When the size of a problem is too large for the memory of a single GPU (that currently is limited to a few GBytes) or there is the need to reduce the time

Figure 2.7. Data exchange between GPUs before CUDA 4.0

to solution, it is possible to resort to *clusters* of GPUs. In general, GPUs can not exchange data directly. In CUDA, up to version 4.0, the CPU had to be always involved in the communication as shown in Figure 2.7. For every data exchange between two GPUs, it was necessary to:

- upload data to the CPU (a device to host memory copy operation)

- if the GPUs were controlled by different CPUs, then exchange data among CPUs. The Message Passing Interface (MPI) could be used for that purpose to guarantee portability and scalability when GPUs are plugged into systems interconnected by networks (e.g., Infiniband).

- download data to the GPU (host to device memory copy)

thus realizing an MPI+CUDA hybrid programming scheme. The need to explicitly copy data between device and host memories, before and after any MPI transfer call represents an issue from both efficiency and simplicity of programming viewpoint.

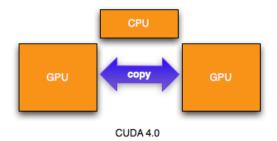

Actually, CUDA 4.0 introduced the possibility to carry out memory copy operations directly between two different GPUs. If such mechanism, named

Figure 2.8. Direct memory copy between GPUs enabled by CUDA 4.0

in CUDA as *peer-to-peer*, is enabled, then the copy operation no longer needs to be staged through the CPU (see Figure 2.8) and is therefore faster.

However, only recent NVIDIA GPUs support the *peer-to-peer* mechanism. Moreover the source and the target GPU must be connected to the same PCI-e root complex so the general issue remains unsolved.

Recently, two widely used MPI implementations, OpenMPI [4] and MVA-PICH2 [3], started to offer the possibility to specify GPU memory pointers in MPI functions, relieving the programmer from the management of data transfers between GPU and CPU memories.

This feature represents an essential part of research efforts, taking place at both hardware and software levels, aimed towards the definition of a general mechanism for direct communication among GPUs, (at least without explicit involvement of CPUs). On the hardware-side, research focuses on the development of interconnection technologies able to transfer data from GPU memory straight to the communication link. One solution supporting this approach is the APEnet infrastructure (see section 4.4.1).

# Chapter 3

# Parallel BFS on shared memory systems

# 3.1 Overview of shared memory systems

There is a great variety of shared memory parallel systems, very different from each other. Generally, they have in common the ability for all processors to access all memory, as a global address space. Changes in a memory location due to a processor are visible to all other processors. However, each processor has its own cache memory. A cache memory is a smaller and faster memory, which stores copies of the data from the most recently used main memory locations. Whenever one cache is updated with information that may be used by other processors, the change needs to be reflected to the other processors (cache coherence).

From the programming point of view, the global address space provides a user-friendly perspective to memory. Data sharing among tasks is both fast and *almost* uniform, due to the proximity of memory to CPUs. The

main drawback is that synchronization, required to ensure correct access to global memory, is a responsibility of the programmer. Moreover, to improve performances, programmers must resort to cache optimization techniques [13, 7].

The problem of accessing shared data can be generalized by considering shared resources. A mechanism for ensuring that only one process accesses a particular resource at a time is to establish sections of code involving the resource as so-called critical sections and arrange that only one such critical section is executed at a time. Several mechanisms, like the mutual exclusion, can be applied to ensure that the result of the operation will be correct. This is a classic problem covered in many textbooks [78]. In a shared memory system, parallel operations are executed concurrently by different threads. To ensure correctness in the critical sections of the code, programmers must implement synchronization barriers and thread-safe functions. Thread safe functions can be invoked from multiple threads simultaneously and always produce correct results. Typically, these functions exploit several types of atomic operations <sup>1</sup>.

As discussed in chapter 2, NVIDIA GPUs have their own programming model. At the block level, the programmer can use barriers to enforce synchronizations among threads. Critical sections can be implemented via a set of dedicated functions that in CUDA are called atomic-functions.

However, in CUDA, does not exist a cheap mechanism to synchronize threads that belong to different blocks. The programming model encourages the development of programs that are a sequence of distinct kernels. The

<sup>&</sup>lt;sup>1</sup>In concurrent programming, an operation (or set of operations) is atomic, linearizable, indivisible or un-interruptible if it appears to the rest of the system to occur instantaneously. Atomicity is a guarantee of isolation from concurrent processes. Additionally, atomic operations commonly have a succeed-or-fail definition, they either successfully change the state of the system, or have no apparent effect.

kernel itself acts like a synchronization barrier among all the blocks (there are several algorithms that benefit from this programming paradigm, as an example the prefix-sum, see [71]).

In the next section we introduce the pseudocode for the parallel BFS algorithm. Then we review recent works on both CPU and GPU architectures.

# 3.2 Overview of parallel algorithms for BFS

"Parallel BFS is similar to the sequential version, which starts with a source vertex s and visits levels of the graph one after the other using a queue to keep track of vertices that have not yet been visited. The main difference is that each level is going to be visited in parallel" (source: Blelloch [22]).

Algorithms (2) and (3) describe two versions of parallel BFS. The main difference between the two is that the former uses a queue whereas the latter doesn't. Algorithm 2 is a simple extension of the serial version where the for loop on line 6 is carried out in parallel (the parallelization of loop 7 is straightforward only on some architectures and, for the sake of simplicity, we will discuss it later). As for the corresponding serial version, it performs a linear amount of work, i.e., the time complexity is O(N + M).

The pseudo-code 2 does not show that, to ensure correctness in a shared memory system, the parallel enqueue operation and the update of the parent array, must be implemented in a careful way. As a matter of fact, the update of the parent array gives rise to a benign race condition, but the enqueue operation requires special care to ensure correctness and to achieve good performances.

To clarify the issue, suppose to be in a shared memory system where different parallel operations are executed by different threads. Each thread

#### Algorithm 2 Level synchronous parallel BFS, with queues

CQ: Current level Queue NQ: Next level Queue

```

1: p[u] = -1, \forall u \in V

2: CQ, NQ \leftarrow \emptyset

3: p[s] = s

4: engueue(CQ, s)

5: while CQ \neq \emptyset do

for all u in CQ in parallel do

6:

for all v \in Adj[u] (in parallel) do

7:

if p[v] == -1 then

8:

9:

p[v] = u

10:

engueue(NQ, v)

end if

11:

12:

end for

end for

13:

CQ \leftarrow NQ

14:

NQ \leftarrow \emptyset

15:

16: end while

```

#### Algorithm 3 Level synchronous parallel BFS, without queues

C: Current level set, C has |V| elements

N: Next level set, N has |V| elements

V is the set of all vertices of the graph G(V,E).

```

1: p[u] \leftarrow -1, \forall u \in V

2: \ C, N \leftarrow \emptyset

3: p[s] = s

4: C[s] = s

5: while C \neq \emptyset do

for all u in C in parallel do

6:

if C[u] != 0 then

7:

for all v \in Adj[u] do

8:

9:

if p[v] == -1 then

10:

p[v] = u

N[v] = v

11:

end if

12:

end for

13:

14:

end if

15:

end for

16:

C \leftarrow N

N \leftarrow \emptyset

17:

18: end while

```

is in charge for one vertex in the queue. In figure 3.1 is depicted the third iteration of algorithm 2 on the graph from section 1.3.1. The iteration starts with vertices 2, 4, 5 in the CQ. Vertex 8 is discovered simultaneously by the two threads in charge of vertices 4 and 5. These two threads then enter the loop on line 5. Both will write p[8] in an unpredictable order. However, this is a benign race condition, any thread writes, the resulting BFS-tree will be valid: the operation is idempotent. Once that the parent array is updated, threads enter the critical section, i.e., they have to update the queue (line 10). The enqueue operation must be realized with a safe thread-parallel function that, atomically, increases the queue counter, and then inserts the new element.

During the same iteration, also the vertices 1 and 3 are discovered by two distinct threads (see figure 3.1). However, the vertex 1 will not be added to the queue, because of the **if** instruction on line 8. (It is noteworthy that, in algorithm 2 and 3, the parent array is used to record the state of vertices, i.e. if they are visited or not, most implementations use a separate array to keep track of visited vertices).

In table 3.1 are shown the arrays used in the BFS algorithm (without copy removal) with their corresponding elements, for each iteration of the BFS. By comparison with table 1.1, it is apparent that the parallel version introduces redundant work. If multiple copies are allowed in NQ, the array may expand exponentially [22] and the resulting performances degrade. Addressing this problem is not easy and may require to redesign the algorithm.

Algorithm 3 solves this problem at the cost of performing a greater, asymptotically, amount of work.

In algorithm 2, at the beginning of each iteration, |V| threads are created and each thread is in charge for one element of the array C. The algorithm

**Figure 3.1.** In figure is shown the third level of the BFS started at vertex 1. In parallel BFS the same vertex can be reached by two or more edges. As an example, vertices 4 and 5 find vertex 8 from two different edges, whereas vertices 2 and 5 visit vertex 6. This can lead to store and process redundant information during the run of the BFS.

**Table 3.1.** The table refers to the graph in figure (1.3). The BFS is started at vertex 1 and new visited vertices are added to next level, according to algorithm (2). The algorithm doesn't prune the NLFS from multiple copies of the same vertices (see text for details).

| BFS LEVEL | CQ              | NLFS                            | NQ              |

|-----------|-----------------|---------------------------------|-----------------|

| 0         | 1               | 2,4,5                           | 2,4,5           |

| 1         | 2,4,5           | 1,3,4,5,6,1,2,8,1,2,6,8         | 1,3,6,1,8,1,6,8 |

| 2         | 1,3,6,1,8,1,6,8 | 2,4,5,2,2,5,7,2,4,5,4,5,7,2,4,5 | 7,7             |

| 3         | 7,7             | 6,8,6,8                         |                 |

starts, and each thread reads its element in the array C. Those threads, whose elements are not zero (lines 6-7), visit the neighbors of their vertices and set the parent when necessary (lines 8-13). Then, C and N are swapped. The algorithm stops when the array C is empty.

In this algorithm there is no need for a queue, which means that there are

no critical sessions. All the races among threads are benign. Moreover, the array C has a fixed size and doesn't have multiple copies of the same vertices. This strategy has his own shortcomings. At the end of each BFS level it is necessary to insert a synchronization barrier  $^2$ . Even worse, |V| threads are created and launched at the beginning of each iteration, regardless the number of the elements in the queue (or the number that have actually to be inspected during the iteration). In the worst case, the algorithm performs a  $O(N^2 + M)$  amount of work.

## 3.3 Parallel BFS on multi-cores CPU

In the last few years, several studies of high performance computing, have tackled the problem of traversing a large graph with real-world properties (see Section 1.2).

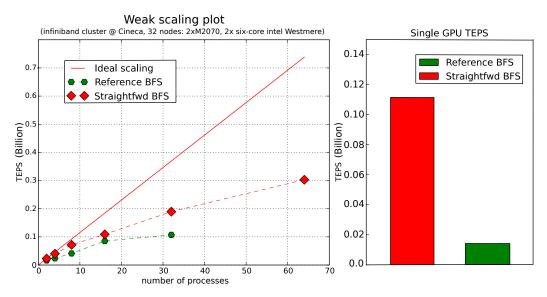

Most often, the graph is generated by using special generators, like the R-MAT generator, that we have introduced in Section 1.2.1). We will refer to synthetic real-world graphs as R-MAT graphs. A new metric to evaluate performances has been introduced by the Graph 500 benchmark and has been adopted by most of recent works. This metric measures the number of Traversed Edges Per Second (TEPS) during the BFS visit.

Different solutions have been proposed to mitigate the effect of irregular memory access patterns, synchronization overhead and parallel insertion in the BFS queue.

In 2006, Bader and Madduri [13] designed a parallel BFS for the Cray

<sup>&</sup>lt;sup>2</sup>Hong *et al.* noticed however that synchronization have a small impact if the input graph have real-world properties. First the number of levels is limited. Second, the computational-intensive parts are restricted to only a small fraction of levels.

MTA-2 architecture <sup>3</sup>. Their implementation is based on algorithm 2. Loops on line 5 and 9 are parallelized by suitable compiler directives. Their implementation uses optimized functions that atomically update the value of the distance array (that is the output of their BFS) and insert elements in the queue. They reported almost the same performance on R-MAT and random graphs. For an R-MAT graph with 200 millions vertices and 1 billions edges the code reached 0.5 GTEPS, by using 40 processors [7].

In 2010, Agarwal et al. [7] developed a multi-core multi-socket parallel BFS for Intel Nehalem platforms. They implemented a level synchronous BFS like algorithm 2. The first optimization they introduced is the use of a global bitmask to mark visited vertices. This greatly reduces the working size of the inspected set of vertices. They reported an improvement of the processing rate by a factor of four (number of reads per unit time). The graph and the bitmap were partitioned thorough the CPU-sockets so that only local vertices were updated locally, information about non-local vertices were exchanged. They noticed that those communications affect the performance and developed a lightweight communication mechanism among groups of cores residing on different sockets. With a 64 threads enabled Nehalem EX, they reported 1 GTEPS for a R-MAT graph with 128 million vertices and 4 billion edges.

An interesting algorithm has been proposed in 2011, by Beamer et al. [20] for the Graph 500 benchmark. They introduced a bottom-up approach in the BFS visit. Basically, they noticed that, during each level of the BFS there are a great number of wasted attempts to become a parent of a neighbor. By using a bitmap to mark visited vertices reduces those attempts but there is still redundant work, because each vertex on the frontier tries to become

<sup>&</sup>lt;sup>3</sup>Shared memory system

the parent of its neighbors. Instead of doing this, in their algorithm, each unvisited vertex attempts to find any parent among its neighbors (a neighbor is a parent if it is part of the frontier). In this approach, each child writes by itself its parent and there is no need of atomic operations. Their results are really remarkable, with a quad-socket 40-core Intel Xeon E7-8870 they report 5.1 GTEPS for a graph with 256 million vertices and 4B billion undirected edges. They ranked 19 on the Graph 500 list, in November 2011.

Other solutions have been proposed in [36, 68, 38]. Optimizations are always directed to improve bandwidth utilization and cache performances.

### 3.4 Parallel BFS on GPU

Many studies, in recent years, demonstrated that applications having a regular access pattern in memory and a high arithmetic intensity (ratio between number of arithmetic and memory access operations) can be successfully ported to GPU with a significant speed up in the execution time. Algorithms with irregular memory access patterns, however, have been proved to be more challenging and exhibit less spectacular improvements.

The main drawback, with algorithms that have an irregular "flow" is that data structures vary at running time. During the BFS visit, at each iteration, the size of the queue and of the NLFS vary greatly.

In the CUDA programming model <sup>4</sup>, the number of threads and blocks is statically assigned before the kernel starts and cannot be modified at run time. Thus, the programmer typically implements a static mapping between threads and data elements. With a static mapping, there is the risk of having either too few threads, thus serializing most of the work, or too many threads,

<sup>&</sup>lt;sup>4</sup>CUDA 5.0, that has been recently released, supports dynamic thread allocation.

thus incurring in an unnecessary overhead for the generation and the release of resources.

For instance, a naive way to map threads to data is to assign a thread (defined on a 1D grid in the CUDA sense) to each vertex in the queue so that the loop in line 6 of algorithm 2 will be executed in parallel. With this assignment, the loop in line 7 is serialized, thus limiting the number of active threads to the number of elements in the CQ.

Several works, having as target a single GPU, have adopted a different strategy, based on algorithm 3. The static assignment of tasks to vertices trivially maps to the data parallel GPU model. The work flow of each thread is independent from other threads. Those implementations suffer two main problems. First, the overhead associated with the launch of a constant number of threads, even if they are not necessary. Second, the number of threads is actually too small to visit the NLFS in parallel. In the most computationally-intensive levels of the BFS, the work is almost serialized.

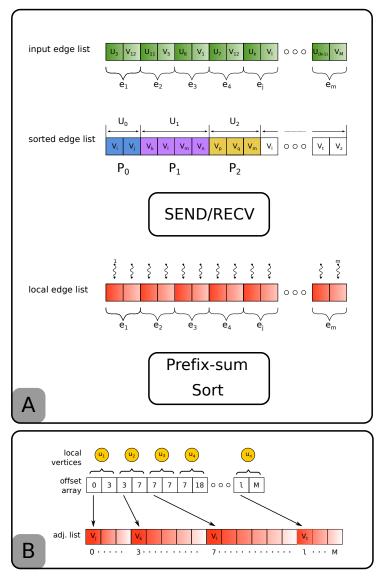

To bypass the problem of the static mapping, the resources actually required, can be computed at run time. For instance, once the CQ is built, it is possible to calculate the total number of elements in the NLFS. This implies that, in principle, we can run a kernel that computes the number of threads and their offsets. Each offset corresponds to the index of the element to which the thread will be assigned and will be used to correctly map threads to data. Then, a second kernel, can actually performs the work (it can be the status look-up of vertices in the NLFS). It turns out that, in some situations, it is convenient to adopt such parallelization-strategy, instead of using the static assignment. Unfortunately, the implementation of such strategy, is not straightforward.

Summing up, the main issue, on a single device, is finding the right map-

ping of data to threads so that the full power of the GPU is exploited. The irregular flow of the algorithm, limits the number of concurrent working threads. Compared to the CPU, another possible issue is the amount of global memory that is limited to 6 GBytes for the latest NVIDIA FERMI GPUs (whereas commodity CPUs can have hundreds of GBytes). This limits the size of the graph that can be visited.

In 2007, Harish et al., [37] implemented a parallel BFS based on algorithm 3, by using a CUDA enabled GPU (Nvidia GTX 280 with 1028 MByte of memory). To mitigate the overhead of having |V| threads running at each BFS iteration, they implemented an optimization, based on vertex-list compaction, that reduces the number of active threads. The synchronization between two subsequent levels of the BFS is implemented by splitting the problem in two kernels. The first kernel uses two arrays that hold, respectively, the old and the new frontier, in order to prevent read-after-write inconsistencies. The second kernel swaps the frontiers and update the visited array. Due to the limited size of the device memory, the size of the graph they can visit is small, compared to the ones that can be visited with multicore CPUs. They reported an execution time of 0.5 sec for a R-MAT graph with 10 million vertices and 120 million edges.

In 2009, Deng et al., [29] implemented the graph traversal by means of the Sparse-Matrix Vector product (SMVP). They developed their own implementation of the SMVP on CUDA. Their target are Electronic Design Automation (EDA) applications, thus, the size and the kind of the graphs they visited cannot be directly compared to those we have seen so far.

In 2010, Luo *et al.*, [50] developed a new algorithm to perform a BFS on a CUDA GPU (Nvidia GTX280). Their algorithm is queue-based, like algorithm 2. However, to avoid the critical section of the parallel queue

insertion, they introduced a hierarchical queue structure.

The idea is that, once the lower-level queues have been created, then the location of each element in the higher-level queue are also known and it is possible to copy the elements to the higher-level queue in parallel. To completely avoid collisions in the building of the hierarchical queue, they implemented the first queue-level at the warp level (see section 2.2). It is important to notice that to guarantee correctness the low level insertion in the queue is achieved via an atomic operation. They reported effective speed-up with respect to the implementation in [37] for all the input graphs.

For instance for a scale-free graph with average degree  $\sim 6$  and 10M vertices they reported a running time is 0.483s. However, for this kind of graph, they need to pre-process the graph and convert it to a near-regular graph, by splitting the big-degree nodes (the same idea has been previously used in [55]).

In order to achieve better performances, in 2010, Hong et al. [41] introduced a warp-centric programming model. Instead of assigning different tasks to each thread, they allocated a chunk of tasks to each CUDA warp. During neighbors expansion, the SIMD lanes of the warp, are used to visit the adjacency lists of vertices assigned to the warp. They tackled directly the mapping of data to threads, thus obtaining better results at the cost of greater programming difficulties.

In a subsequent work [42] they proposed a hybrid CPU/GPU method that takes advantage of the GPU only for the most computationally-expensive levels of the BFS. They implemented algorithm 3, on the CPU and used the optimization proposed in [7]. For the CPU (Nehalem Xeon X5550) they reported nearly 0.8 GTEPS for an RMAT graph with 32 million vertices and 1 billion edges. The CPU+GPU version shows some improvements with

respect to the CPU only version but cannot be tested on graph of such size. They reported 0.9 GTEPS for 32 million vertices and 240 millions edges on a Fermi Tesla 2050.

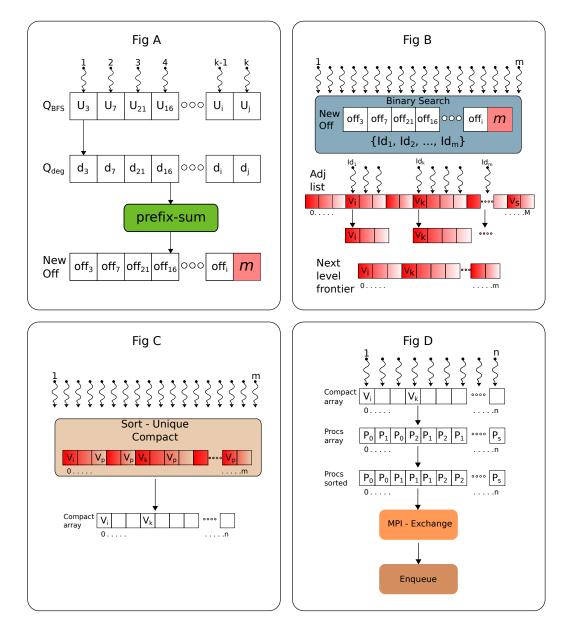

In 2011, Merrill et al., [30] noticed that GPU architecture is not well suited for problems that require dynamic and irregular data movement within shared data structures. Their work is focused on parallelization strategies that permit to map in an effective way threads to data, given their dynamic allocation requirements. They suggest that, an efficient prefix sum operation allows for a reorganization in which a sparse and uneven work becomes an uniform and dense one. Moreover, they individuate as the basic element of computation the CTA (Cooperative Thread Array), i.e., a block in the CUDA programming model. Instead of assigning data to each thread, they assigned chunks of data to the CTA.

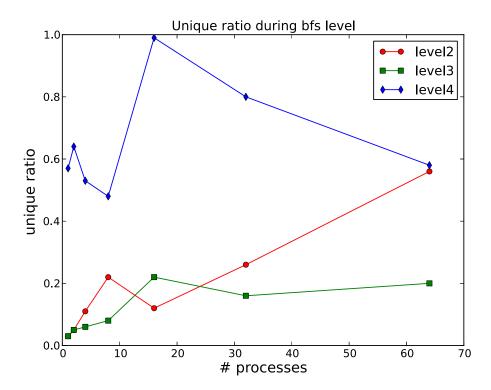

Their work is the first that incorporates fine-grained (not global) parallel adjacency list expansion at the CTA level. This means that large neighbors lists are cooperatively strip-mined at the full width of the CTA. Another important feature is the local duplicate detection which eliminates most of the race conditions and redundant work. They reported a detailed analysis of the expansion and contraction mechanism of the BFS over subsequent levels pointing out that, the removal of duplicates, can reduce the number of vertices in the NLFS by one order of magnitude. To achieve better performances and also reduce the memory occupancy, they implemented a global bitmask array to keep track of visited vertices. With a NVIDIA TESLA 2050, they report 1.8 GTEPS for an R-MAT graph wit 2 million vertices and 32 million edges. Their GPU implementation of the BFS is the fastest currently available (with really remarkable performances) but the size of the supported graphs remains bounded by the GPU memory size.

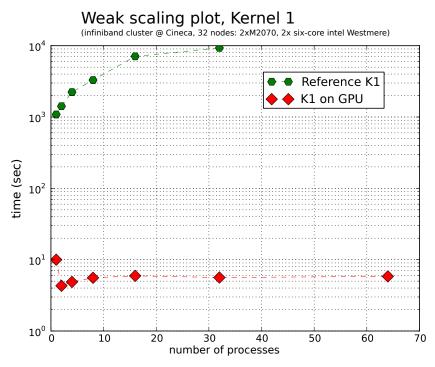

In the same paper the authors developed a multi-GPU version of the code. The multi-GPU implementation relies on the VMA technology that supports up to four devices, with a unified memory address space. By using four GPUs, they report a result of 8 GTEPS, however, this result, refers to the visit of a graph with an average degree equal to 256, a pretty high value. For an input graph with an average degree equal to 16, the code does not exceed 3 GTEPS. This value can be considered as a marginal improvement with respect to the speed-up that the same authors report comparing their results with those achievable on a single CPU (as an example with the result in [7]). As a matter of fact, the reported strong scaling, discussed in [30] is not spectacular: "We observe 1.5x, 2.1x, and 2.5x speedups when traversing a R-MAT graph with 2 million vertices and 128 million edges using two, three, and four GPUs, respectively" <sup>5</sup>. Our distributed implementation have a similar speed-up but using an Infiniband interconnection. In Chapter 4 (see section 4.3.5) we provide a more detailed comparison and discussion.

| Authors      | Graph Type | Num. of Vertices | ef | GTEPS | Num Processors | Arch. Type    | Output   |

|--------------|------------|------------------|----|-------|----------------|---------------|----------|

| Agarwal [7]  | R-MAT      | $2^{21}$         | 16 | 0.6   | 2 sockets      | Nehalem EP    | parent   |

| Agarwal [7]  | R-MAT      | $2^{21}$         | 16 | 0.65  | 4 sockets      | Nehalem EX    | parent   |

| Hong [42]    | R-MAT      | $2^{25}$         | 8  | 0.4   | 2 sockets      | Nehalem X5550 | distance |

| Hong [42]    | R-MAT      | $2^{25}$         | 8  | 0.64  | 1              | Tesla C2050   | distance |

| Hong [42]    | R-MAT      | $2^{25}$         | 8  | 0.68  | 1              | CPU+GPU       | distance |

| Hong [42]    | R-MAT      | $2^{21}$         | 8  | 0.6   | 1              | CPU+GPU       | distance |

| Merrill [30] | R-MAT      | $2^{21}$         | 16 | 1.8   | 1              | Tesla C2050   | distance |

| Merrill [30] | R-MAT      | $2^{21}$         | 16 | 3.2   | 4              | Tesla C2050   | distance |

| Merrill [30] | R-MAT      | $2^{24}$         | 16 | 3.0   | 4              | Tesla C2050   | distance |

**Table 3.2.** Comparison of different implementations of BFS on shared memory systems. The column ef is the average degree so that, the number of edges is ef times the number of vertices. While all the input graphs are R-MAT, the exact values of the coefficients are available only for [30]. The output of the algorithm is also important when comparing performances: the computation of the distance array is faster with respect to the computation of the parent array. We tried to compare similar instances of input whenever possible.

$<sup>^{5}</sup>$ from [54]

| Authors      | Graph Type | Num. of Vertices | ef  | GTEPS | Num Processors     | Arch. Type    | Output   |

|--------------|------------|------------------|-----|-------|--------------------|---------------|----------|

| Bader [13]   | R-MAT      | $2^{27}$         | 5   | 0.5   | 40                 | Cray MTA-2    | distance |

| Agarwal [7]  | R-MAT      | $2^{20}$         | 16  | 1.1   | 2 sockets          | Nehalem EP    | parent   |

| Agarwal [7]  | R-MAT      | $2^{22}$         | 64  | 1.3   | 4 sockets          | Nehalem EX    | parent   |

| Hong [42]    | R-MAT      | $2^{25}$         | 16  | 0.9   | 1                  | CPU+GPU       | distance |

| Hong [42]    | R-MAT      | $2^{25}$         | 64  | 0.93  | 2 sockets          | Nehalem X5550 | distance |

| Merrill [30] | R-MAT      | $2^{21}$         | 64  | 8.3   | 4                  | Tesla C2050   | distance |

| Merrill [30] | R-MAT      | $2^{20}$         | 256 | 3.5   | 1                  | Tesla C2050   | distance |

| Beamer [20]  | R-MAT      | $2^{28}$         | 16  | 5.1   | 4 sockets/40 cores | Westmer-EX    | parent   |

**Table 3.3.** Best performances reported by different authors for BFS on shared memory systems.

In tables 3.2 and 3.3 we report the results of some of the works described so far. The column ef is the average degree of the input graph. The number of edges is ef times the number of vertices (the term ef stands for edgefactor, see section 4.2.1). The first table is a comparison of similar results (similar size of the input graph and similar average degree) whereas the second table shows the best performances achieved by the various implementations discussed. Results obtained by [20] and [30] are noteworthy. Unfortunately, both implementations relies on optimization techniques that cannot be used in a distributed implementation. We will discuss this topic in more details in Chapter 4, after we have introduced the basic concepts of the distributed version of the BFS algorithm.

# Chapter 4

# Parallel BFS on distributed memory systems

Very large graphs do not fit the memory of a single system. To study them it is necessary to resort to a distributed memory architecture. Generally, a distributed system is a cluster of computing nodes interconnected via a wired network. Each node is a system in itself that can be equipped with a single-or a multi-core CPU. To carry out computations, the nodes of the cluster, must exchange data each other. Graph algorithms have low arithmetic intensity, that is, during the execution, the time spent in computation is a small fraction of the whole. On a single processor, most of the time is spent in read and write operations from/to memory. In a distributed environment, data can be in a remote memory, thus, most of the execution time is spent sending and receiving data over the communication network. It is noteworthy that, latencies involved in communication are very high, compared to those introduced by the access to data in memory. Moreover, the communication patterns involved in graph algorithms, are irregular. Both the size of the

messages and the set of senders/receivers vary during the execution.

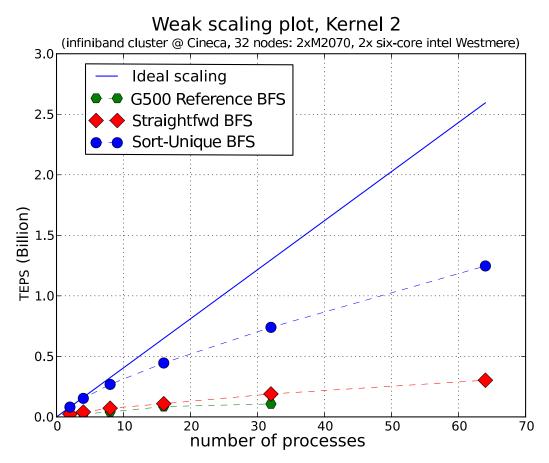

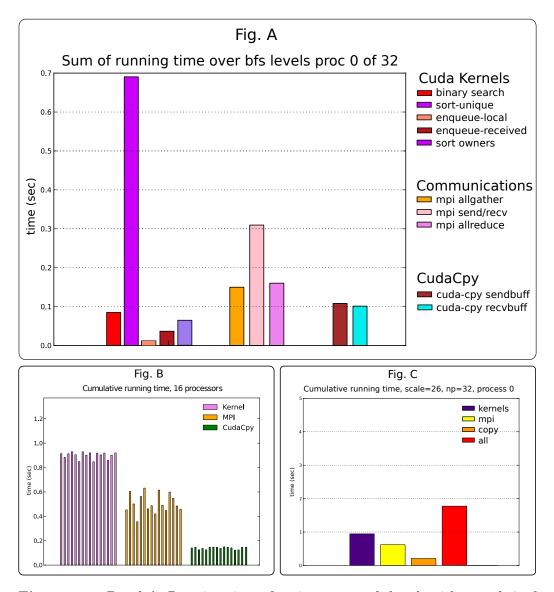

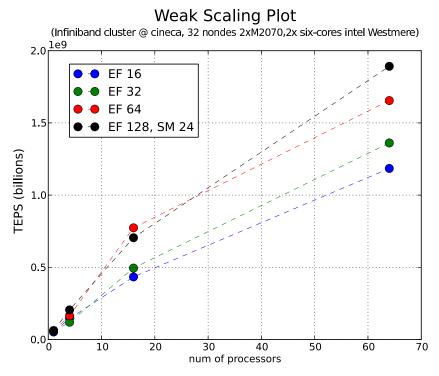

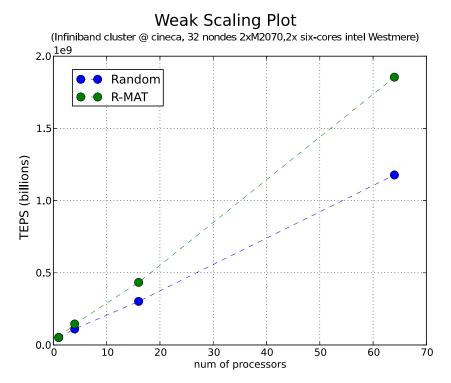

It is not surprising therefore, that, as reported by many authors, [79, 51, 23], the bottleneck of a distributed BFS, is the communications among nodes.