## PROBING TECHNIQUE FOR ENERGY DISTRIBUTION OF POSITIVE CHARGES IN GATE DIELECTRICS AND ITS APPLICATION TO LIFETIME PREDICTION

SHARIFAH FATMADIANA WAN MUHAMAD HATTA

## A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS OF LIVERPOOL JOHN MOORES UNIVERSITY FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

December 2013

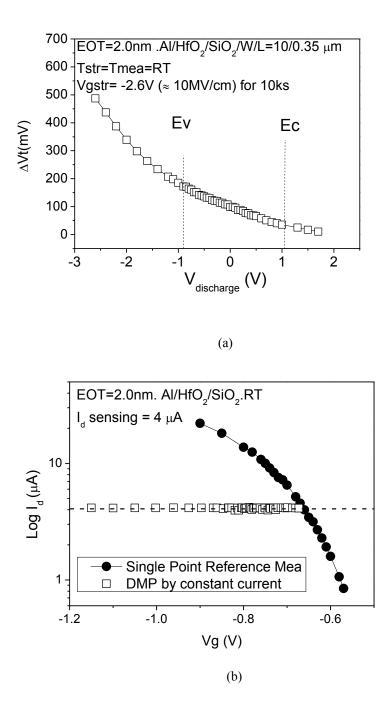

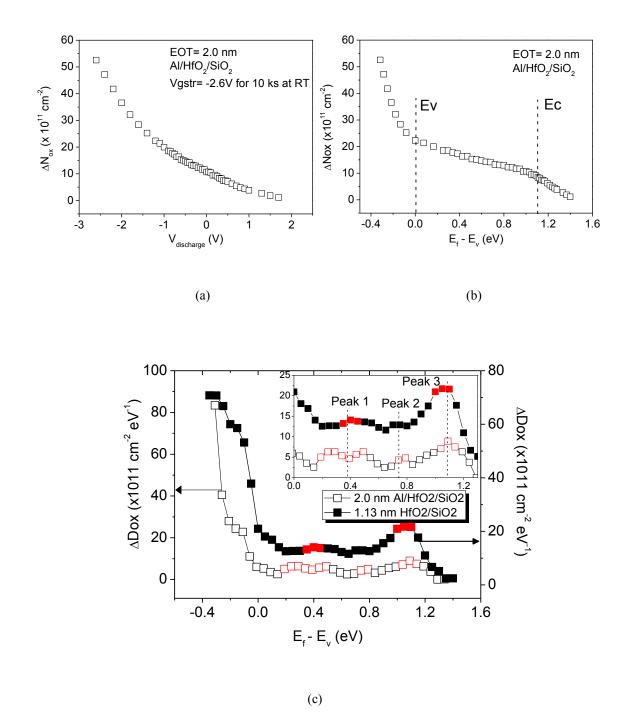

#### ABSTRACT

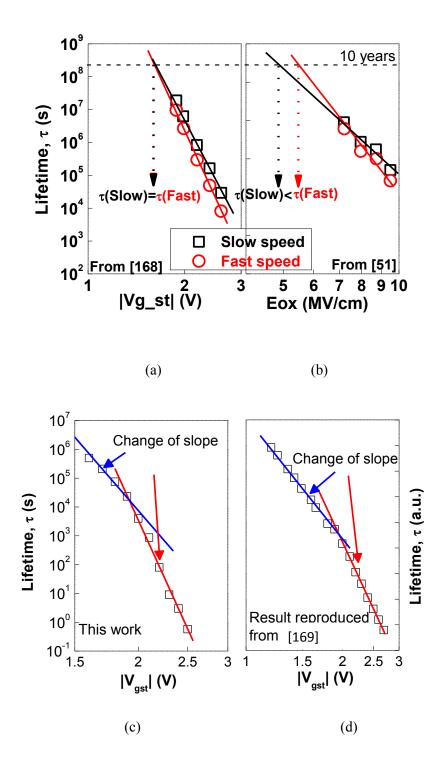

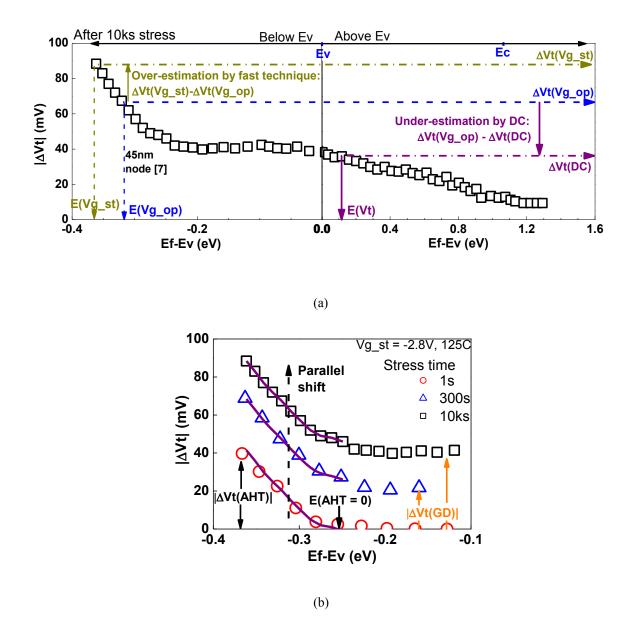

The continuous reduction of the dimensions of CMOS devices has increased the negative bias temperature instability (NBTI) of pMOSFETs to such a level that it is limiting their lifetime. This increase of NBTI is caused mainly by three factors: an increase of nitrogen concentration in gate dielectric, a higher operation electrical field, and a higher temperature. Despite of many years' research work, there are questions on the correctness of the NBTI lifetime predicted through voltage acceleration and extrapolation. The conventional lifetime prediction technique measures the degradation slowly and it typically takes 10 ms or longer to record one threshold voltage shift. It has been reported that NBTI can recover substantially in this time and the degradation is underestimated. To minimize the recovery, ultra-fast technique has been developed and the measurement time has been reduced to the order of microseconds. Once the recovery is suppressed, however, the degradation no longer follows a power law and there is no industry-wide accepted method for lifetime prediction. The objective of this project is to overcome this challenge and to develop a reliable NBTI lifetime prediction technique after freezing the recovery. To achieve this objective, it is essential to have an in-depth knowledge on the defects responsible for the recovery.

It has been generally accepted that the NBTI recovery is dominated by the discharge of trapped holes. For the thin dielectric (e.g. < 3 nm) used by current industry, all hole traps are within direct tunnelling distance from the substrate and their discharging is mainly controlled by their energy levels against the Fermi level at the substrate interface. As a result, it is crucial to have the energy distribution of positive charges (PC) in the gate dielectric, but there is no technique available for probing this energy profile. A major achievement of this project is to develop a new technique that

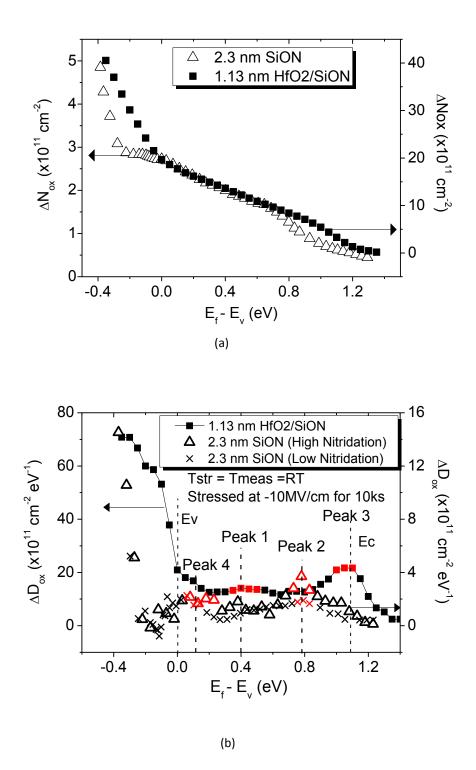

can probe the energy distribution of PCs both within and beyond the silicon energy gap. After charging up the hole traps, they are allowed to discharge progressively by changing the gate bias, Vg, in the positive direction in steps. This allows the Fermi level at the interface to be swept from a level below the valence band edge to a level above the conduction band edge, giving the required energy profile. Results show that PCs can vary by one order of magnitude with energy level. The PCs in different energy regions clearly originate from different defects. The PCs below the valence band edge are asgrown hole traps which are insensitive to stress time and temperature, and substantially higher in thermal SiON. The PCs above the valence band edge are from the created defects. The PCs within bandgap saturate for either longer stress time or higher stress temperature. In contrast, the PCs above conduction band edge, namely the antineutralization positive charges, do not saturate and their generation is clearly thermally accelerated. This energy profile technique is applicable to both SiON and high-k/SiON stack. It is found that both of them have a high level of as-grown hole traps below the valence band edge and their main difference is that there is a clear peak in the energy density near to the conduction band edge for the High-k/SiON stack, but not for the SiON.

Based on this newly developed energy profile technique and the improved understanding, a new lifetime prediction technique has been proposed. The principle used is that a defect must be chargeable at an operation voltage, if it is to be included in the lifetime prediction. At the stress voltage, some as-grown hole traps further below Ev are charged, but they are neutral under an operation bias and must be excluded in the lifetime prediction. The new technique allows quantitative determination of the correct level of as-grown hole trapping to be included in the lifetime prediction. A main advantage of the proposed technique is that the contribution of as-grown hole traps is experimentally measured, avoiding the use of trap-filling models and the associated fitting parameters. The successful separation of as-grown hole trapping from the total degradation allows the extraction of generated defects and restores the power-law kinetics. Based on this new lifetime prediction technique, it is concluded that the maximum operation voltage for a 10 years lifetime is substantially overestimated by the conventional prediction technique. This new lifetime prediction technique has been accepted for presentation at the 2013 International Electron Devices Meeting (IEDM).

#### ACKNOWLEDGEMENTS

*Alhamdulillah*. I thank god for the strength and ease He has given me in completing this long-journey of PhD.

Firstly, I owe my deepest gratitude to my principle supervisors Professor Jian F. Zhang and Associate Professor Dr. Norhayati Soin. Without their guidance and unconditional support over the last 3 years, this thesis would not have been made possible. I also would never have made it this far by the unwavering supervision and support given by Dr. Zhigang Ji. I am forever indebted to you. Words could not express my gratitude to him.

Secondly, I would like to send my thank you to my second supervisor, Dr. Weidong Zhang who has been so kindly to support me and help me in solving the many questions I had.

I must also thank my dear colleagues in LJMU as well as in UM. Dr. Brahim Benbakhti, Dr. Meng Duan, Dr. Baojun Tang, Mr. Jigang Ma, Dr. Daniel Lin and Ms. Hanim Hussin, thank you all.

Last but not least, I send my deepest thanks to my loving husband, Mr Shahrin Abd. Samat. Thank you for being there always all throughout my journey. And, also thank you to my family for their support and love.

# TABLE OF CONTENTS

| Abstractii                                                                                                      |   |

|-----------------------------------------------------------------------------------------------------------------|---|

| Acknowledgements                                                                                                | 1 |

| Table of Contents                                                                                               |   |

| List of Abbreviations                                                                                           |   |

| List of Symbols                                                                                                 | 1 |

| Introduction                                                                                                    |   |

| 1.1 History of the MOSFETs' Reliability                                                                         | L |

| 1.2 Negative Bias Temperature Instability                                                                       | 3 |

| 1.3 Models of Negative Bias Temperature Instability                                                             | 5 |

| 1.3.1 Reaction-Diffusion (RD) model                                                                             | 5 |

| 1.3.2 Hole Trapping and RD model                                                                                | 7 |

| 1.3.3 Two-components Model (Huard)10                                                                            | C |

| 1.3.4 CET Mapping Model12                                                                                       | 2 |

| 1.3.5 As-grown Generation (AG) Model13                                                                          | 3 |

| 1.4 Positive Charges Formation in Gate Dielectric1                                                              | 5 |

| 1.4.1 Confusions in Positive Charges1                                                                           | 5 |

| 1.4.2 Framework                                                                                                 | ô |

| 1.5 The rationale of the project work                                                                           | Э |

| 1.6 Organization of the thesis 20                                                                               | C |

| Devices and Test Facilities 22                                                                                  | 2 |

| 2.1 Introduction                                                                                                | 2 |

| 2.2 Devices                                                                                                     | 5 |

| 2.3 Conventional characterization and stress techniques                                                         | 7 |

| 2.3.1 Conventional $I_d$ -V <sub>g</sub> technique                                                              | 7 |

| 2.3.2 Conventional Charge Pumping (CP) technique                                                                | Э |

| 2.3.3 Conventional Capacitance-Voltage (C-V) technique                                                          | 4 |

| 2.4 On-The-Fly (OTF) techniques                                                                                 | Э |

| 2.5 Pulse $I_d$ - $V_g$ techniques                                                                              | 2 |

| 2.5.1 Experimental Setup                                                                                        | 3 |

| 2.5.2 Calibration of Pulse Measurement System4                                                                  | 5 |

| 2.6 Data Smoothing Procedures                                                                                   | Э |

| 2.7 Conclusions                                                                                                 | 3 |

| Energy Distribution of Positive Charges in Gate Dielectric : Probing Technique and Impacts of Different Defects | 4 |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 3.2 Devices and Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56                                                                                             |

| 3.3 The Technique for Energy Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 61                                                                                             |

| 3.4 Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 67                                                                                             |

| 3.4.1 Different Types of PCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67                                                                                             |

| 3.4.2 Effects of stress time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68                                                                                             |

| 3.4.3 Impacts of stress temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70                                                                                             |

| 3.4.4 Effects of nitridation technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71                                                                                             |

| 3.4.5 Effects of interface states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73                                                                                             |

| 3.5 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76                                                                                             |

| Application of Energy Probing Technique on High-k devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77                                                                                             |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 77                                                                                             |

| 4.2 Devices and Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 78                                                                                             |

| 4.2.1 Comparison of Energy Probing at Constant current vs Constant voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 79                                                                                             |

| 4.3 Comparison of the energy distribution in Hf-based devices of different gate stacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 84                                                                                             |

| 4.3.1 Energy Distribution of positive charges in HfO <sub>2</sub> /SiON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 85                                                                                             |

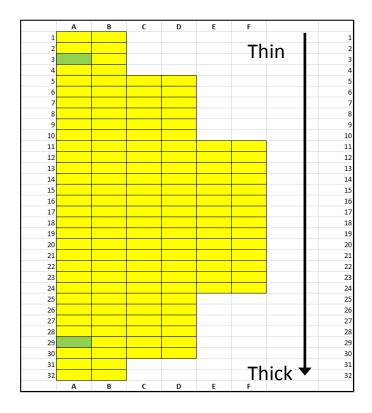

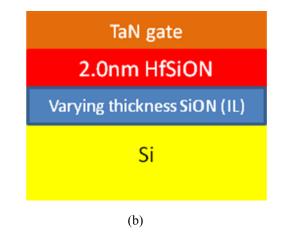

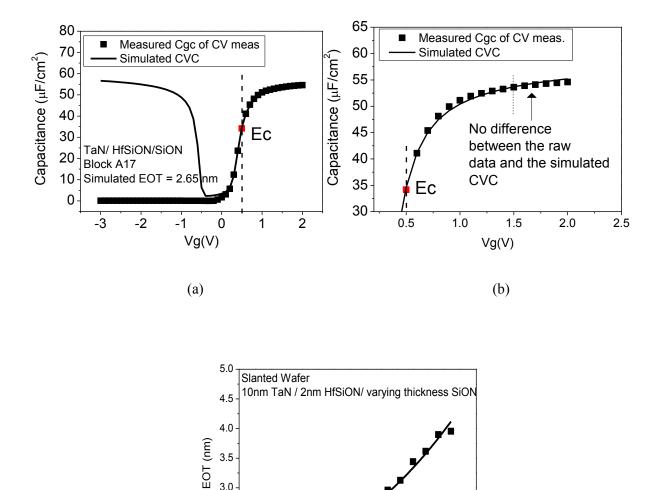

| 4.3.2 Energy Distribution of positive charges in TaN/HfSiON with varying IL SiON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 90                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~~                                                                                             |

| 4.3.3 TIN / HfSiON/ SION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 98                                                                                             |

| 4.3.3 TiN / HfSiON/ SiON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 102                                                                                            |

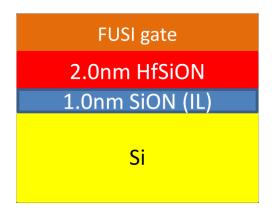

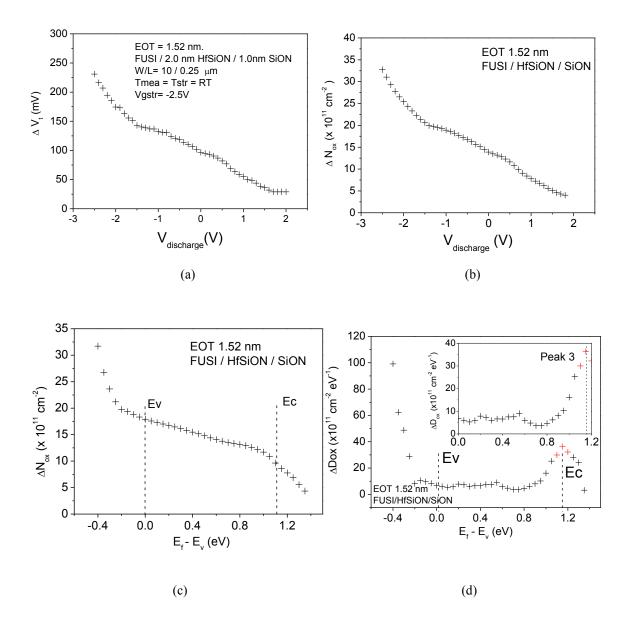

| 4.3.4 FUSI/ HfSiON / SiON 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LO2<br>LO4                                                                                     |

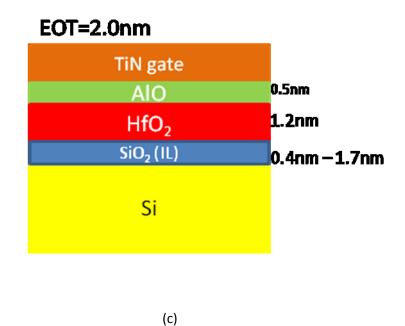

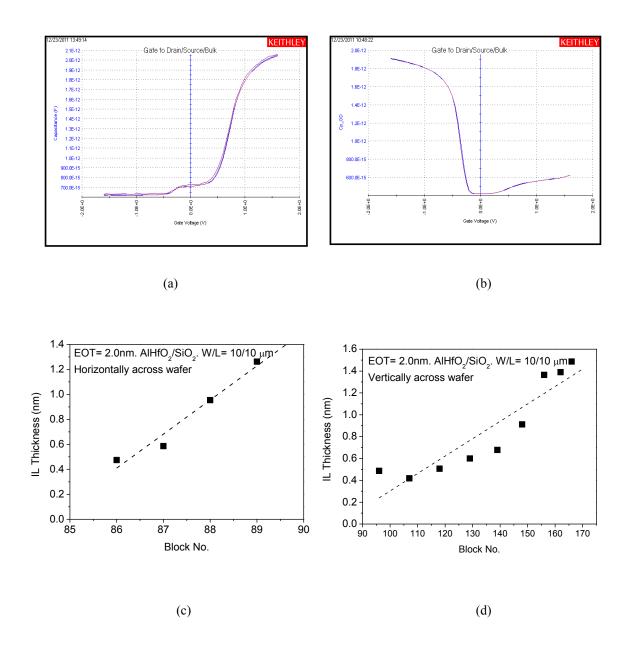

| 4.3.4 FUSI/ HfSiON / SiON 1<br>4.4 Energy Distribution of the Al-capped HfO <sub>2</sub> 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LO2<br>LO4<br>LO5                                                                              |

| <ul> <li>4.3.4 FUSI/ HfSiON / SiON</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LO2<br>LO4<br>LO5<br>L11                                                                       |

| <ul> <li>4.3.4 FUSI/ HfSiON / SiON</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LO2<br>LO4<br>L05<br>L11<br>L13                                                                |

| 4.3.4 FUSI/ HfSiON / SiON       1         4.4 Energy Distribution of the Al-capped HfO2       1         4.4.1 Device characteristics       1         4.5 Conclusion       1         Negative Bias Temperature Instability Lifetime Prediction: Problems and Solutions       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LO2<br>LO4<br>L05<br>L11<br>L13<br>L13                                                         |

| 4.3.4 FUSI/ HfSiON / SiON       1         4.4 Energy Distribution of the Al-capped HfO2       1         4.4.1 Device characteristics       1         4.5 Conclusion       1         Negative Bias Temperature Instability Lifetime Prediction: Problems and Solutions       1         5.1 Introduction       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 102<br>104<br>105<br>111<br>113<br>113<br>113                                                  |

| 4.3.4 FUSI/ HfSiON / SiON       1         4.4 Energy Distribution of the Al-capped HfO2       1         4.4.1 Device characteristics       1         4.5 Conclusion       1         Negative Bias Temperature Instability Lifetime Prediction: Problems and Solutions       1         5.1 Introduction       1         5.2 Pitfalls of the Lifetime Prediction based on the slow DC and fast pulse measurements 1                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 102<br>104<br>105<br>111<br>113<br>113<br>114                                                  |

| 4.3.4 FUSI/ HfSiON / SiON       1         4.4 Energy Distribution of the Al-capped HfO2       1         4.4.1 Device characteristics       1         4.5 Conclusion       1         Negative Bias Temperature Instability Lifetime Prediction: Problems and Solutions       1         5.1 Introduction       1         5.2 Pitfalls of the Lifetime Prediction based on the slow DC and fast pulse measurements 1       1         5.2.1 The Sources of Overestimation and Underestimation of the Lifetime       1                                                                                                                                                                                                                                                                                                                                                           | 102<br>104<br>105<br>111<br>113<br>113<br>114<br>117<br>119                                    |

| 4.3.4 FUSI/ HfSiON / SiON       1         4.4 Energy Distribution of the Al-capped HfO2       1         4.4.1 Device characteristics       1         4.5 Conclusion       1         4.5 Conclusion       1         Negative Bias Temperature Instability Lifetime Prediction: Problems and Solutions       1         5.1 Introduction       1         5.2 Pitfalls of the Lifetime Prediction based on the slow DC and fast pulse measurements 1       1         5.2.1 The Sources of Overestimation and Underestimation of the Lifetime       1         5.3 A new method for Lifetime Prediction       1                                                                                                                                                                                                                                                                   | 102<br>104<br>105<br>111<br>113<br>113<br>113<br>114<br>117<br>119                             |

| <ul> <li>4.3.4 FUSI/ HfSiON / SiON</li> <li>1</li> <li>4.4 Energy Distribution of the Al-capped HfO2</li> <li>1</li> <li>4.4.1 Device characteristics</li> <li>1</li> <li>4.5 Conclusion</li> <li>1</li> <li>Negative Bias Temperature Instability Lifetime Prediction: Problems and Solutions</li> <li>1</li> <li>5.1 Introduction</li> <li>5.2 Pitfalls of the Lifetime Prediction based on the slow DC and fast pulse measurements 1</li> <li>5.2.1 The Sources of Overestimation and Underestimation of the Lifetime</li> <li>1</li> <li>5.3 A new method for Lifetime Prediction</li> <li>1</li> <li>5.3.1 A step-by-step guide for lifetime prediction</li> </ul>                                                                                                                                                                                                     | 102<br>104<br>105<br>111<br>113<br>113<br>113<br>114<br>117<br>119                             |

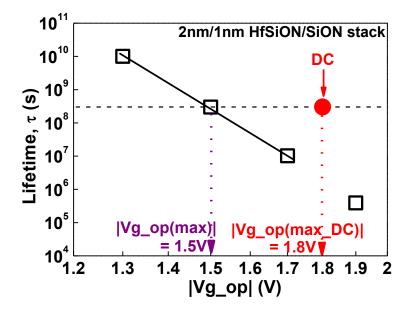

| <ul> <li>4.3.4 FUSI/ HfSiON / SiON</li> <li>1</li> <li>4.4 Energy Distribution of the Al-capped HfO2</li> <li>1</li> <li>4.4.1 Device characteristics</li> <li>1</li> <li>4.5 Conclusion</li> <li>1</li> <li>Negative Bias Temperature Instability Lifetime Prediction: Problems and Solutions</li> <li>1</li> <li>5.1 Introduction</li> <li>5.2 Pitfalls of the Lifetime Prediction based on the slow DC and fast pulse measurements 1</li> <li>5.2.1 The Sources of Overestimation and Underestimation of the Lifetime</li> <li>1</li> <li>5.3 A new method for Lifetime Prediction</li> <li>5.3.1 A step-by-step guide for lifetime prediction</li> <li>1</li> <li>5.3.2 Estimating Vg_op (max) for a τ of 10 years</li> </ul>                                                                                                                                           | 102<br>104<br>105<br>111<br>113<br>113<br>114<br>117<br>119<br>125<br>127                      |

| 4.3.4 FUSI/ HfSiON / SiON14.4 Energy Distribution of the Al-capped HfO214.4.1 Device characteristics14.5 Conclusion14.5 Conclusion1Negative Bias Temperature Instability Lifetime Prediction: Problems and Solutions15.1 Introduction15.2 Pitfalls of the Lifetime Prediction based on the slow DC and fast pulse measurements 15.2.1 The Sources of Overestimation and Underestimation of the Lifetime15.3 A new method for Lifetime Prediction15.3.1 A step-by-step guide for lifetime prediction15.3.2 Estimating Vg_op (max) for a $\tau$ of 10 years15.4 Application of the proposed lifetime prediction technique to devices from different                                                                                                                                                                                                                           | 102<br>104<br>105<br>111<br>113<br>113<br>114<br>117<br>119<br>125<br>127                      |

| 4.3.4 FUSI/ HfSiON / SiON       1         4.4 Energy Distribution of the Al-capped HfO2       1         4.4.1 Device characteristics       1         4.5 Conclusion       1         4.5 Conclusion       1         Negative Bias Temperature Instability Lifetime Prediction: Problems and Solutions       1         5.1 Introduction       1         5.2 Pitfalls of the Lifetime Prediction based on the slow DC and fast pulse measurements 1       1         5.2.1 The Sources of Overestimation and Underestimation of the Lifetime       1         5.3 A new method for Lifetime Prediction       1         5.3.1 A step-by-step guide for lifetime prediction       1         5.3.2 Estimating Vg_op (max) for a τ of 10 years       1         5.4 Application of the proposed lifetime prediction technique to devices from different fabrication processes       1 | 102<br>104<br>105<br>111<br>113<br>113<br>114<br>117<br>119<br>125<br>127<br>127               |

| 4.3.4 FUSI/ HfSiON / SiON       1         4.4 Energy Distribution of the Al-capped HfO2       1         4.4.1 Device characteristics       1         4.5 Conclusion       1         Negative Bias Temperature Instability Lifetime Prediction: Problems and Solutions       1         5.1 Introduction       1         5.2 Pitfalls of the Lifetime Prediction based on the slow DC and fast pulse measurements 1       5         5.2.1 The Sources of Overestimation and Underestimation of the Lifetime       1         5.3.1 A step-by-step guide for lifetime prediction       1         5.3.2 Estimating Vg_op (max) for a τ of 10 years       1         5.4 Application of the proposed lifetime prediction technique to devices from different fabrication processes       1         5.5 Conclusion       1                                                          | 102<br>104<br>105<br>111<br>113<br>113<br>114<br>117<br>119<br>125<br>127<br>130<br>132<br>133 |

| 6.3 Conclusions for Application of Energy Probing Technique on High-k                 | devices 136 |

|---------------------------------------------------------------------------------------|-------------|

| 6.4 Conclusions for Negative Bias Temperature Instability Lifetime Prediced Solutions |             |

| 6.5 Future Work                                                                       | 139         |

| References                                                                            |             |

| APPENDIX                                                                              |             |

| LIST OF PUBLICATIONS                                                                  |             |

# LIST OF ABBREVIATIONS

| Abbreviation     | Signification                                     |

|------------------|---------------------------------------------------|

| СР               | Charge Pumping                                    |

| CV               | Capacitance-Voltage                               |

| ЕОТ              | Equivalent Oxide Thickness                        |

| HCI              | Hot Carrier Injection                             |

| HfO <sub>2</sub> | Hafnium Oxide                                     |

| HfSiON           | Hafnium Silicate Oxide Nitride                    |

| IL               | Interfacial Layer                                 |

| MOSFET           | Metal Oxide Semiconductor Field Effect Transistor |

| NBTI             | Negative Bias Temperature instability             |

| SILC             | Stress Induced Leakage Current                    |

| SiON             | Silicon Oxide Nitride                             |

| TaN              | Tantalum Nitride                                  |

| TDDB             | Time Dependent Dielectric Breakdown               |

| TiN              | Titanium Nitride                                  |

## LIST OF SYMBOLS

| Symbol                          | Description                             | Unit             |

|---------------------------------|-----------------------------------------|------------------|

| $\mu_{eff}$                     | Effective mobility                      | cm⁻²/V-s         |

| $\mathcal{E}_{SiO2}$            | Dielectric constant of SiO <sub>2</sub> |                  |

| ${m \mathcal E}_{Si}$           | Dielectric constant of Si               |                  |

| $arepsilon_0$                   | Electric permittivity of vacuum         | F/cm             |

|                                 | Dielectric constant of the              |                  |

| $arepsilon_{\prime L}$          | interfacial layer                       |                  |

| C <sub>ox</sub>                 | Oxide capacitance                       | F                |

| E <sub>f</sub>                  | Fermi level                             | eV               |

|                                 | Effective surface field in the Si       |                  |

| E <sub>eff</sub>                | substrate                               | MV/cm            |

| f                               | Frequency                               | Hz               |

| g <sub>m</sub> , G <sub>m</sub> | Transconductance                        | S                |

| ١ <sub>d</sub>                  | Drain current                           | А                |

| L                               | Mask channel length                     | μm               |

| L <sub>D</sub>                  | Debye length                            | ст               |

| N <sub>A</sub>                  | Substrate doping density                | cm⁻³             |

| N <sub>it</sub>                 | Interface trap density                  | cm <sup>-2</sup> |

|                                 | Intrinsic carrier concentration         |                  |

| n <sub>i</sub>                  | in Si substrate                         | cm <sup>-3</sup> |

| q                               | One electron charge                     | С                |

| R                               | Feedback resistance                     | Ω                |

| Т                               | Temperature                             | °C               |

| V <sub>d</sub>                  | Drain voltage                           | V                |

| V <sub>fb</sub>                 | Flat band voltage                       | V                |

| Vg                              | Voltage applied on the gate             | V                |

| V <sub>t</sub>                  | Threshold voltage                       | V                |

| $\Delta V_t$                    | Threshold voltage shift                 | V                |

| W                               | Mask channel width                      | μm               |

|                                 |                                         |                  |

# **1** Introduction

#### 1.1 History of the MOSFETs' Reliability

The integrated circuits (ICs) were invented in 1958 by J.Kilby at Texas Instruments. Soon after, Frank Wanlass from Fairchild had described the first CMOS logic gate (NMOS and PMOS) in 1963. The first ICs produced in the early seventies had only a few hundreds of transistors integrated based on bipolar technology. The Metal Oxide Semiconductor (MOS) had only arrived several years later due to its instability caused by the presence of minute amounts of alkali elements in the gate dielectric, which subsequently leads to a shift of the threshold voltage of the transistor during operation.

Due to the high power consumption in bipolar circuits, MOS technology had gradually made its way into the scene. The problem relating to the high power consumption can be dealt with as the dimensions of the MOS devices can be scaled down easily compared to other transistor types. Though MOS circuits have lower power consumption, the MOSFETs are relative slower than their bipolar counterparts. Initially the NMOS had obtained a wider acceptance but due to the increase in integration density, its high power consumption became unacceptable once more. Eventually in the eighties, the CMOS processes were widely adopted. However even before the CMOS was widely accepted, the defects presented in the CMOS technologies had been investigated ever since its first generation in 1960s [1,2].

The rapid miniaturization of circuits by the downscaling trend of the transistor sizes has been seen to evolve ever since. Through transistor scaling, one can obtain a better performance-to-cost ratio of products which induces the exponential growth of the semiconductor market. The Moores' Law [3-7] is popular in the semiconductor industry which predicts the number of transistor used per chip to double every 18 months or so. The industry is currently faced with the increasing importance of new trends which are the "More Moore" and "More than Moore" (MtM) where added value to device is provided by incorporating functionalities that do not necessarily scale according to the Moore's Law. These trends are made effective in microelectronic products where there are non-digital functionalities incorporated such as an assembly of various components, for instance passive components on a printed circuit board (PCB). The combined need for digital and non-digital functionalities in an integrated system is distinctly reflected as a dual trend in the recent International Technology Roadmap for Semiconductors (ITRS). The "More Moore" trend is to define the rapid miniaturization of digital functions while the MtM defines functional diversification of semiconductor-based devices. The non-digital functionalities is claimed to be contributing to the rapid miniaturization of electronic systems too, though not to the same extent as that of the digital functionality. The relevance of this new trend in CMOS technologies has been extensively reported in the ITRS, 2011 edition [8].

The rapid scaling for enhanced performance had also pushed existing CMOS materials closer to their intrinsic reliability limits and hence reliability issues are observed to be of significance and tend to change as the transistor dimensions are downscaled. One of the early reliability issue emerged in the 1970s was the contamination, such as mobile ions which can induce instability [9]. This was eventually overcome by the realization of handling the devices in a clean-room environment. In the 1980s, even as the downscaling of the transistor dimensions continued, the operation voltage was maintained at a constant 5 V. This results in higher electrical field in the device and hot carriers were limiting the lifetime of nMOSFETs [10,11]. Gate leakage further became a big threat under the operating bias as the gate oxide was thinner than 3 nm. In the 1990s, the time-dependent-dielectric breakdown (TDDB) [12] was the main reliability concern. Later as the year steps into the new millennium, the lifetime of MOSFETs were threatened by negative bias temperature instability (NBTI), which will be elaborated in the following section. In the future, the degradation-induced time dependent device variability is predicted to be of a major issue [13]. However this variability issue is out of the scope conducted in the work of this thesis, and hence will not be further elaborated.

### 1.2 Negative Bias Temperature Instability

The negative bias temperature instability (NBTI) is one of the dominant reliability concerns in analog and digital CMOS technologies. This instability specifically occurs in pMOSFETs employed by current technology generations. The common observation resulting to this instability is that the threshold voltage of the transistor may increase

over time, followed by a reduction in the drive current. This ultimately degraded the circuit performance and decreases its lifetime.

The NBTI is one of the earliest reported instabilities occurring in the MOSFETs. In 1967, Deal et al [2] had studied NBTI in integrated circuits and in 1977, Jeppson and Svennsson [14] developed a theory based on the generalized reaction-diffusion (RD) model to explain the kinetics of NBTI. They observed that the defect generation followed a power law dependence against time, with a power factor ranging from 0.2 to 0.3. The role of relaxation and bulk traps were discussed.

NBTI received relatively less attention in the early 1980s however, due to the emergence of the NMOS technology and the buried channel PMOS [15]. In the late 1980s and early 1990s, the NBTI issue begins to become a concern due to the application of dual poly gate, though the hot carrier injection (HCI) dominates the device reliability issue. Not until the CMOS technology starts to scale below the 130 nm technology node [16-19] that the issue of NBTI is revisited. The rapid scaling of the CMOS technology results the following dominating trends: the first is that the oxide electric field increases significantly as a result the reduction in oxide thickness, without a corresponding reduction in the supply voltage. The voltage scaling reduces the HCI and TDDB effects, but the increase in field and temperature enhances the NBTI effects for both analog and digital circuits. Secondly, in order to reduce the gate leakage and boron penetration effects, oxynitride are adapted into the CMOS technology extensively. Since then, there were reports [20-22] to demonstrate that nitridation enhances NBTI and positive change formation.

The study of the NBTI involves the large negative bias stressing (which ranges from 5 - 12 MV/cm) at temperatures ranging from the room temperature to elevated temperatures (100° C - 200° C). After a preset stress time, the sample is cooled down to room temperature and its device characteristics are measured. The effects of the negative bias temperature stress is observed from the degradation suffered by the critical device parameters, specifically the threshold voltage, subthreshold slope, the transconductance, mobility and the drain current. This stress-measure-stress cycle is repeated and the time of stress extends to typically  $10^3$  to  $10^5$  s.

### **1.3 Models of Negative Bias Temperature Instability**

There are various reports published in trying to explain the physical mechanism behind NBTI. The most prevalent of these reports are that of Alam [23] which suggests of the reaction-diffusion (RD) theory and Huard et al [24] which suggests the existence of two independent components (Recoverable, Dr, and Permanent, Dp) where each has its own different mechanism. In addition, Grasser et al [25] used a defect spectroscopy technique which entails the distribution map of defect properties. Another model which explains the kinetics of NBTI measured under the worst case condition is proposed by Z.Ji et al [26] which combines the effect of as-grown defects with that of the generated defects (The AG model).

#### 1.3.1 Reaction-Diffusion (RD) model

The RD model was first proposed by Jeppson and Svennsson [14] and the model was further adapted by Alam [23] and has since been used extensively to explain the mechanism of the NBTI [27-35]. The physical process behind this RD model is that the degradation is initiated by the electrochemical reaction at the SiO<sub>2</sub>/Si interface, which converts the precursors into interface states and releases a hydrogenous species. The hydrogenous species then diffuse away from the interface and this diffusion process limits the generation of interface states. The kinetic equation [36] that describes the interface reaction is as below

$$\frac{\delta N_{ii}}{\delta t} = k_f (N_0 - N_{ii}) - k_r N_{ii} H_{ii}^{\frac{1}{a}}$$

$$(1)$$

*Generation Annealing*

where  $k_f$  is the oxide field dependent forward dissociation rate constant and  $k_r$  the annealing rate constant. N<sub>0</sub> denotes the initial number of electrically inactive Si-H bonds and  $H_{it}$  is the interfacial hydrogen concentration whereas *a* is the order of the reaction (*a*=1 for the atomic hydrogen, H<sub>0</sub> and *a*=2 for the molecular hydrogen, H<sub>2</sub>) [37]. The forward and backward reaction is controlled by the hydrogen density at the interface. Therefore the transport mechanism of the hydrogen species away from the interface characterizes the degradation mechanism and thus controlling the device's parameters for instance the threshold voltage shift. After sufficient trap generation, the rate of the generation of traps is limited by the diffusion of hydrogen.

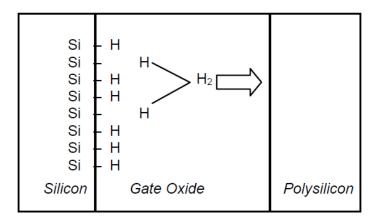

Fig. 1.1 illustrates the schematic description of the reaction-diffusion model which interprets interface trap generation. Broken Si-H bonds at the Si-SiO<sub>2</sub> interface create interface traps, Si+ and hydrogen species, H. Some H converts to hydrogen molecules, H<sub>2</sub>. Diffusion of hydrogen away from the Si/SiO<sub>2</sub> interface controls the interface trap generation at the Si/SiO<sub>2</sub> interface, thus resulting to NBTI. Thinner oxides have brought the polysilicon gate closer to the Si/SiO<sub>2</sub> interface and therefore increasing NBTI susceptibility since hydrogen diffuse much faster in polysilicon than in oxide [38]. From the illustration presented in Fig. 1.1, it is obvious that as the gate oxide is further scaled to meet the current demand for scaled CMOS technologies, the interface trap concentration would significantly increase and thus, enhancing NBTI.

Fig. 1.1 Schematic description of the reaction-diffusion model to interpret the BTI-induced interface trap generation phenomena.

#### 1.3.2 Hole Trapping and RD model

There are reports [39] which claim the pitfalls of the reaction-diffusion model. It is claimed that the RD model is unable to reproduce recovery characteristics [40-43]. In contrast to the experimental observation of the different relaxation magnitudes at

different recovery biases, this model predicts a bias-independent recovery. Hence, some reports concluded that the RD model is not the answer in explaining the NBTI mechanism and that the NBTI is not controlled by diffusion. The RD model theory was widely accepted until around the year 2006 when the hydrogen diffusion was suggested to be dispersive instead [44-50]. The pioneering authors of the RD model had then revised the model [51] by claiming that in addition to  $\Delta N_{it}$ , stresses may also cause hole trapping in pre-existing bulk oxide traps ( $\Delta N_{hole}$ ) and at relatively higher stress bias, additional hole trapping in newly generated bulk oxide traps ( $\Delta N_{ot}$ ). The authors had conducted a lifetime prediction for differently processed SiON pMOSFETs by utilising their H-H<sub>2</sub> R-D framework for  $\Delta N_{it}$  and link this framework with an analytical expression for  $\Delta N_{hole}$  (= A\*(1-exp(-t/ $\tau)^{\beta}$ )) in order to represent the mechanism for fast, quickly saturating (<1s) hole trapping in pre-existing bulk oxide defects.

In addition to the theory based in the diffusion and dispersion of hydrogen, the concept of hole trapping is widely acknowledged, particularly in explaining the NBTI, by the concept of recoverable hole trapping. Elastic tunnelling is used to model the process of hole trapping in which the holes tunnel into pre-existing traps at various distances away from the interface. Elastic hole trapping is defined to be first-order temperature independent and linearly dependent on the stress field [52].

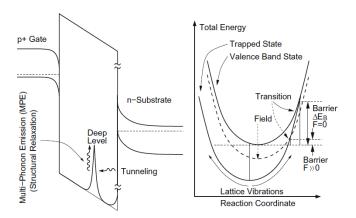

There are also hole trapping models which are based on a dispersion of activation energies which results in a 1/f-noise behaviour for a homogeneous distribution. It was assumed that the holes can be captured through a thermally activated multiphonon emission (MPE) process into deep near-interfacial states/border traps and into oxygen vacancies called E' centres. [53,54]. The difference between the MPE from the

conventionally invoked elastic tunnelling is that the MPE is temperature activated and its mechanism is assumed be derived under negligible electric fields. Hence, due to this non-field dependence assumption, it is difficult to use MPE to explain the mechanism of NBTI. An extension of the MPE is the multiphonon-field-assisted tunnelling (MPFAT) [55,56] in which it is an extension of the MPE to the large electric field, developed for the emission of particles from deep traps. Fig. 1.2 presents the energy band diagram of the MPFAT process for a clearer representation of this hole trapping mechanism.

Fig. 1.2 The multiphonon-field-assisted tunneling (MPFAT) process used to explain the experimental data: elastic tunneling into deep states is only allowed when the excess energy of holes can be released via a multiphonon emission process during structural relaxation. The probability for a thermionic transition over the barrier  $\Delta E_B$  has been estimated as  $\exp(-\beta\Delta E_B)$  using 1D reaction-coordinate calculations, with  $\beta = 1/kBT$ . Application of an electric field shifts the total energy of the valence band state(dashed line), increasing the transition probability by  $\exp(F^2=F_c^2)$ . [25]

On the hole trapping kinetics and capture cross sections, after carefully eliminating the simultaneous neutralization and generation process by using the substrate hole injection technique, it has been shown that hole trapping follows the first order reaction model well with two well separated capture cross sections,  $\sigma$ :

$$Ne = \sum_{i=1}^{2} N_{i} [1 - \exp(-\sigma_{i}Qh)]$$

(2)

where *Ne* is the effective density of trapped holes by assuming all traps are at the oxide/Si interface [57-60]. *N<sub>i</sub>* is the saturation level of traps with a capture cross section of  $\sigma_i$ . *Qh* is the number of holes injected into the oxide that can fill traps. The two extracted capture cross sections are in the order of  $10^{-13} \sim 10^{-14}$  cm<sup>2</sup> and  $10^{-15}$  cm<sup>2</sup>, respectively [57-60]. It is proposed that oxygen vacancies are hole traps [58,60] and the smaller trap is hydrogen-related [60].

However, the RD populist would suggest that hole trapping remains to give a nonsignificant impact on the NBTI and had reflected that the hole trapping is merely a small threat in which its effect can be easily eradicated by removing the initial experimental data up to 1 sec so as to unveil the RD degradation mechanism [51].

#### 1.3.3 Two-components Model (Huard)

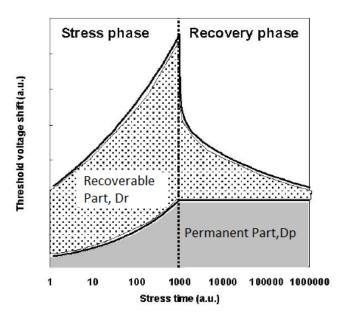

A break from the RD tradition was brought about by the work of Huard [61] from STMicroelecronics where the author strongly suggested that hole trapping made important contribution to the degradation. He had explained that the NBTI is made up of two independent components, which are the recoverable component and the permanent component and these two distinct components demonstrate different voltage, temperature and process dependences. Fig. 1.3 describes the general scheme of the model presented by Huard et al [61]. The permanent component is suggested to be consisting of equal proportion of the interface states and positive fixed charges (1:1 relationship). It was also shown that this component will gradually reach total recovery after long thermal anneals [62].

Fig. 1.3 General scheme of NBTI degradation consisting of permanent and recoverable parts [61].

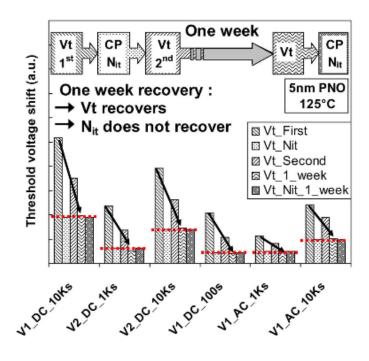

Fig.1.4  $\Delta V_t$  Charge Pumping-induced recovery observed after one week of anneal. The V<sub>t</sub> shift continue to recover to reach the same level as Nit. [61]

Fig. 1.4 is the experimental observation which demonstrates the recovery of the threshold voltage after one week of annealing, eventually leading to the recovery of the positive charge to the same level as the Nit. Hence leading to the justification that of the 1:1 correlation between the interface states and the positive fixed charges which makes up the permanent component. The recoverable component on the other hand comprises of the hole trapping/detrapping processes to pre-existing defects in the dielectrics.

#### **1.3.4 CET Mapping Model**

Recently a physics-based analytic model was proposed by [63] to capture the BTI degradation mechanism during DC, AC and duty-factor dependent stress as well as BTI mechanism during recovery. The model is essentially based on the earlier proposed capture/emission time (CET) maps [64,65] which are used to extract accurate NBTI-relevant defect parameters. The extraction of capture and emission time constants,  $\tau_c$  and  $\tau_e$ , which corresponds to stress and recovery respectively, were reported in earlier literatures [66,67]. The CET map is formed by also including the information extracted from the temperature- and field-dependencies ( $\tau_c$ s and  $\tau_e$ s) in order to gain insight in the physical processes. A determination of averaged time constants is obtained by extracting the averaged values for  $\tau_c$  and  $\tau_e$  from repetitive measurements. The typical number of measurements that needed for the formation of this model can resort to hundred or more and the main parameters are the gate voltage, the length of excitation pulse and the temperature.

#### 1.3.5 As-grown Generation (AG) Model

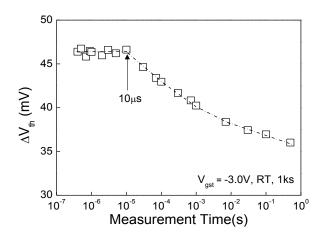

It has been reported in many literatures that lifetime prediction using quasi-dc measurement may result in a substantial error due to the significant recovery which may occur during the measurement. This resorts in the use of ultra-fast pulse measurements, where time was reduced to the order of microseconds, when carrying out the Vg acceleration tests. Ji et al [26] however, has reported of the substantial error of the lifetime prediction at a worst case scenario when the recovery is suppressed and the Vg-acceleration method was used. The Vg acceleration models commonly used by various literatures in lifetime prediction are the power law model,  $|Vg_st|^{-\alpha}$  and the exponential model exp(- $|Vg_st|$ ). The detailed [26] investigation reports on how these models failed to predict the correct lifetime under operational voltage, Vg\_op. This is since the NBTI kinetics no longer follow a simple power law.

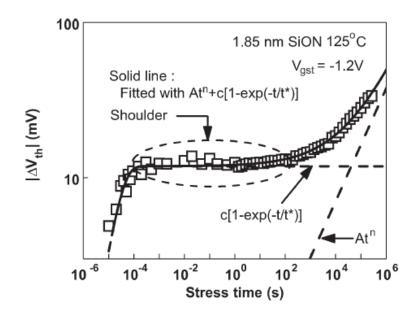

Ji et al [26] proposed a new model to predict the NBTI lifetime at the operational bias, Vgop, and the ultra-fast pulse measurements were used to validate this model. They had observed a distinct 'shoulder' in the NBTI kinetics, which is insensitive to temperature. Fig.1.5 presents the kinetic feature of the 'shoulder' sensed by the ultra-fast pulse measurement. The presence of this 'shoulder' is claimed to be the effect of the saturated charging of as-grown defects which dominated during the initial period of stress. Subsequent to this initial period, a rise in the  $\Delta V_{th}$  is observed suggesting the generation of new defects.

Fig. 1.5 Kinetic feature of a 'shoulder' measured by the ultra-fast pulse measurement  $\Delta V_{th}$  sensed at  $|V_g|$  =1.2V. [26]

The charging kinetics of the AHT is reported to generally follow the first-reaction model [57,58], whereas the generation of new defects follows a power law [68-70]. Hence, by combining the first-reaction model and the power law, the authors proposed the following expression to reflect the kinetics of the NBTI under the worst case scenario:

$$\Delta V_{th} = A_t^{n} + c \left( 1 - e^{-t/t^*} \right)$$

(3)

where for a given stress temperature and bias, A, n, c and t\* are constants and were obtained by fitting experimental data with the least-square errors.

All the models mentioned above have been shown to be able to fit the test data, but the real acid-test for a model is whether it can predict NBTI when test data are not available. Unfortunately, little information and efforts have been made to test the prediction ability of the proposed models. The AG model is the only model that the authors [26] demonstrated that it can not only fit the test data over ten orders of magnitude in time, but also predict the  $\Delta V_{th}$  two orders of magnitude ahead where no test data were used to fit the model. By combining the first-order model for the AHTs and the power law for generating new defects,  $\Delta V_{th}$  can be modelled over ten orders of stress time. This kinetic model is then used to predict the NBTI lifetime. This prediction ability makes the AG model stand out from the rest.

#### **1.4 Positive Charges Formation in Gate Dielectric**

#### **1.4.1 Confusions in Positive Charges**

Positive charges (PC) in gate dielectrics play an important role in NBTI. There are confusions relating to their understanding of their generation mechanisms and dependencies. Extensive works have been carried out in an attempt to characterize them. Two types of positive charges have been reported. One of them is the trapped hole that once fully recovered to its precursor state, will need a further hole injection to be recharged. Another type of positive charge is known to be recoverable and easily be positively recharged under a negative bias without switching on the hole injection [71,72]. This type of positive charge is referred to by various names, including anomalous positive charges [73,74], slow states [75], border traps [76], and switching oxide traps [77]. The formation of the anomalous positive charge (APC) remains to be a confusion among the published literatures and the understanding of the characteristics of this positive charge type is still poor. There might be more than one type of APC and there have been a lack of evidence to clarify the relation between the APC and the trapped hole.

This confusion has been brought to light by Zhang et al [78] in which they showed that the anomalous behaviour originates from the simultaneous presence of different types of positive charges in  $SiO_2$ . This is further elaborated in the next section where the framework of the positive charge is given.

#### 1.4.2 Framework

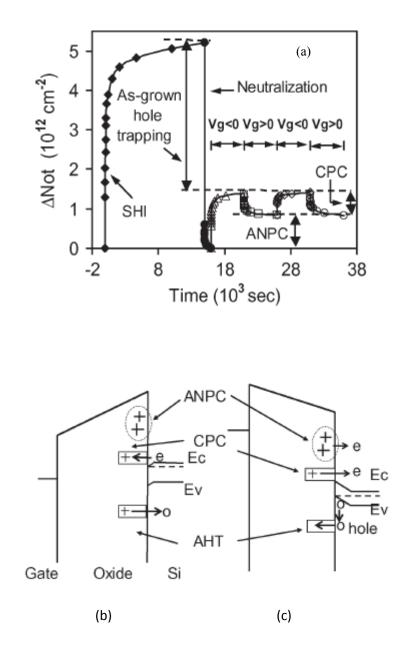

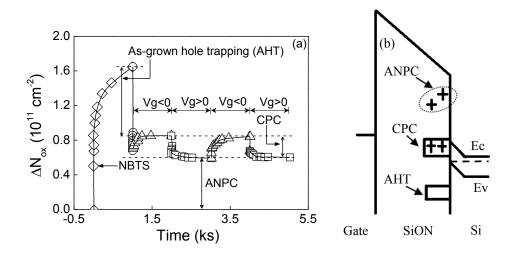

It has been reported [78-81] that there are three different types of hole traps in the SiO<sub>2</sub>: the cyclic positive charge (CPC), the anti-neutralization positive charge (ANPC), and the as-grown hole trapping (AHT). It was shown that the CPC and ANPC are generated traps and that the AHT, regardless of its distance from the SiO2 interface, does not contribute to the generation of the new traps. The CPC can be repeatedly charged and discharged under  $E_{ox} = \pm 5$  MV/cm. Another interesting property of the CPC is that it is insensitive to temperature. The ANPC can be easily positively charged without hole injection and but is difficult to neutralize. The ANPC, which is a thermally activated defect, can eventually be neutralised by high electron injection. However, the higher the energy level of the ANPC, the less number of electrons are able to reach the defect in order to neutralize it. In contrast to the ANPC, subsequent to neutralization, AHT cannot be recharged without hole injection. The initial charge state of the as-grown hole traps is neutral since it is energetically located below Ev.

Fig.1.6 [80] describes the separation of the three types of positive charges. Fig 1.6 (a) illustrates the procedure of how these positive charges was separated. A pMOSFET was stressed by Substrate Hole Injection (SHI) to form the positive charges. Subsequent neutralization was carried out by Fowler Nordheim Injection (FNI). After the neutralization, a positive and negative bias with the magnitude of oxide field of  $E_{ox}=\pm 5$  MV/cm, was alternately applied with all other terminals grounded.

Figs.1.6 (b) and (c) [80] illustrate the energy levels of each types of these positive charges during their neutralization and recharging respectively. It was reported that the neutralization and charging of the CPC only involves the electron tunnelling at the same energy level. The ANPC on the other hand has an energy level above the conduction band edge of Si hence making its neutralization difficult. AHT cannot be recharged under the same Eox=-5 MV/cm without switching on of SHI, since their energy level is well below Si Ev and can only be reached by hot holes.

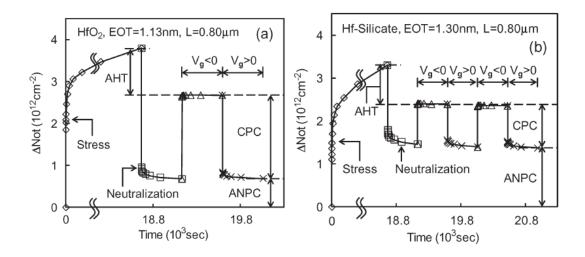

It was also shown that this framework can be applied to the PCs formed under different stress conditions, such as NBTI stresses, and in high-k/SiON stacks. For example, Figs. 1.7 (a) and (b) [80] present the positive charges in the HfO<sub>2</sub> and Hf-Silicate respectively after NBTI stresses. It has been reported that the PCs in high-k/SiON stack are dominated by the interfacial SiON layer [81].

Fig.1.6 Separation of three types of positive charges: as-grown hole trapping (AHT), cyclic positive charges (CPC) and anti neutralization positive charges (ANPC). [80]

Fig.1.7 Separation of three types of positive charges: AHT, CPC and ANPC in Si-based Hf devices [80]

#### 1.5 The rationale of the project work

Although a framework has been proposed for the PCs in gate dielectrics, it only gives a rule-of-the-thumb estimation of the energy levels of different types of PCs. Before this project, there is no probing technique that can extract the energy of PCs both within and beyond Si bandgap. Without this detailed energy distribution, not only our understanding of PCs is limited, but also there is a lack of confidence in the predicted NBTI lifetime for the threshold voltage. As a result, there is an urgent need for developing a new probing technique that can give detailed energy distribution of PCs in gate oxides both within and beyond Si bandgap. The <u>central objective of this project</u> is to develop such a technique and then use it to show the shortcomings of the lifetime prediction technique currently used by the industry.

Part of the PhD period (1 <sup>1</sup>/<sub>2</sub> years) was conducted in Kuala Lumpur, whereby the background research on NBTI was conducted together with initial simulation and experimental work. The work conducted in Kuala Lumpur had resulted in 3 journal

papers and 3 conference papers. The later part of the PhD period (2 years), consisting fully of experimental work, was conducted in Liverpool John Moores University (LJMU). The major output from the work conducted at the LJMU is the publication in the IEEE Transaction of Electron Devices and the invitation for a presentation at the 2013 International Electron Devices Meeting.

#### **1.6 Organization of the thesis**

This thesis is organized as follows:

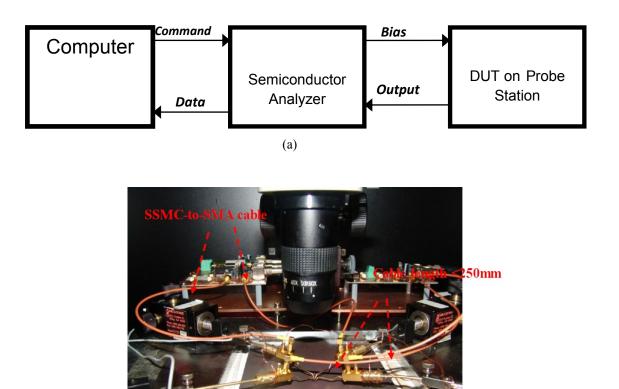

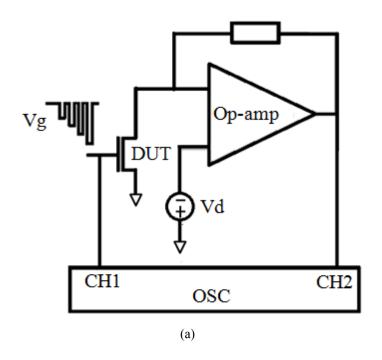

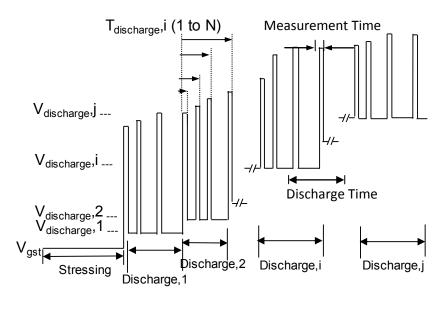

Chapter 2 comprises a review of the characterization techniques used in investigating Negative Bias Temperature Instability (NBTI), which includes both conventional and fast techniques. The DC transfer characteristic, capacitance-voltage (C-V), On-The-Fly (OTF) and fast pulse  $I_d$ -V<sub>g</sub> measurements are reviewed.

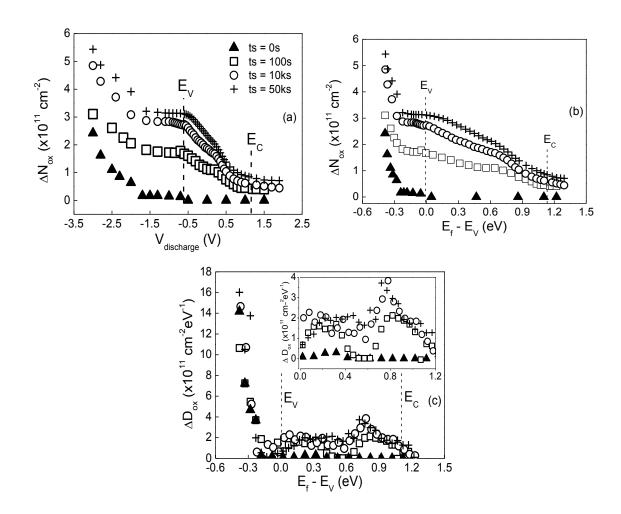

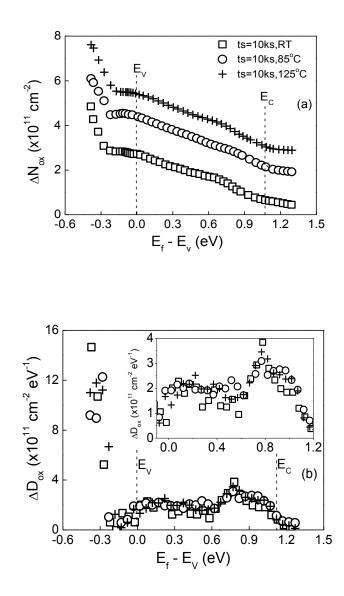

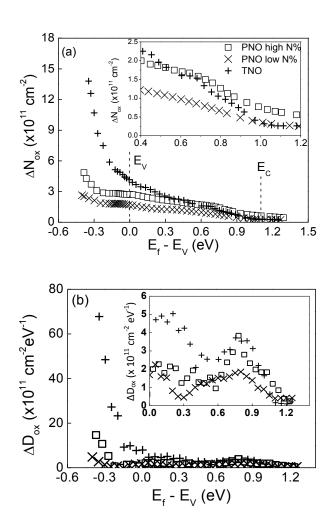

Chapter 3 comprises of the comprehensive demonstration of the probing technique in obtaining the energy distribution of positive charges (PCs) in the dielectric which is extracted within and beyond the Si bandgap. The study will show that the PCs have a broad energy distribution and the results strongly support the existence of different types of PCs.

Chapter 4 comprises of the impact of CMOS processes on the defects and their energy distributions. It will be demonstrated that the newly proposed energy distribution

technique is applicable not only to conventional single-layered SiON devices but also to various advanced high-k gate stacks. The energy distribution of different high-k devices will be investigated, including both HfO<sub>2</sub>/SiON and the AlO-capped high-k/SiON stack. Attention will be paid to their differences from the pure SiON samples.

In Chapter 5, the application of the newly developed technique will be explored to predict the device lifetime. It will demonstrate how the current conventional technique used by the industry, as well as the advanced fast pulse measurement method suggested by other works is not suitable for lifetime prediction due to their incorrect inclusion of defects in the prediction. A new lifetime prediction method which can readily be implemented in the industry will be proposed, based on the energy distribution technique.

Chapter 6 summarizes the work presented in this thesis. Finally the direction for future work is suggested.

# 2

## **Devices and Test Facilities**

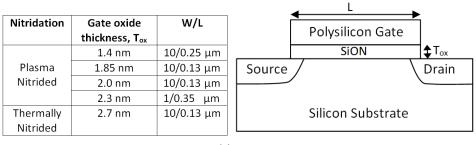

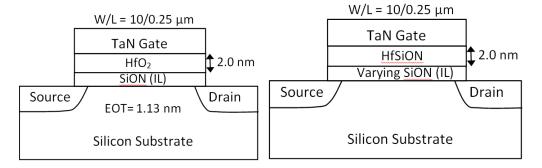

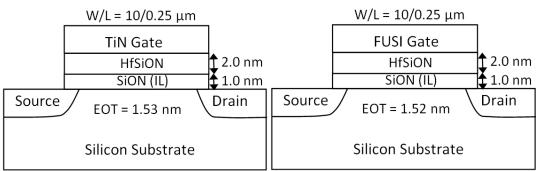

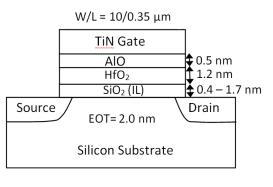

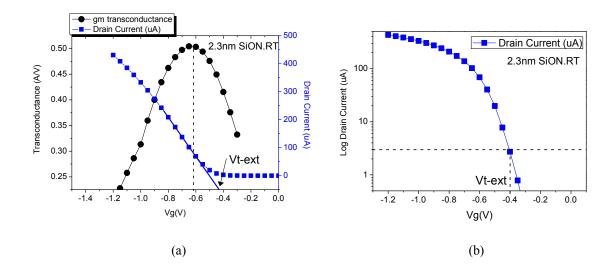

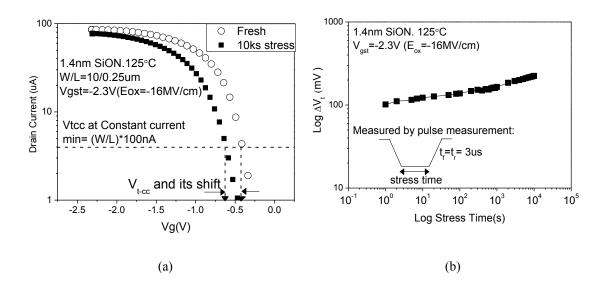

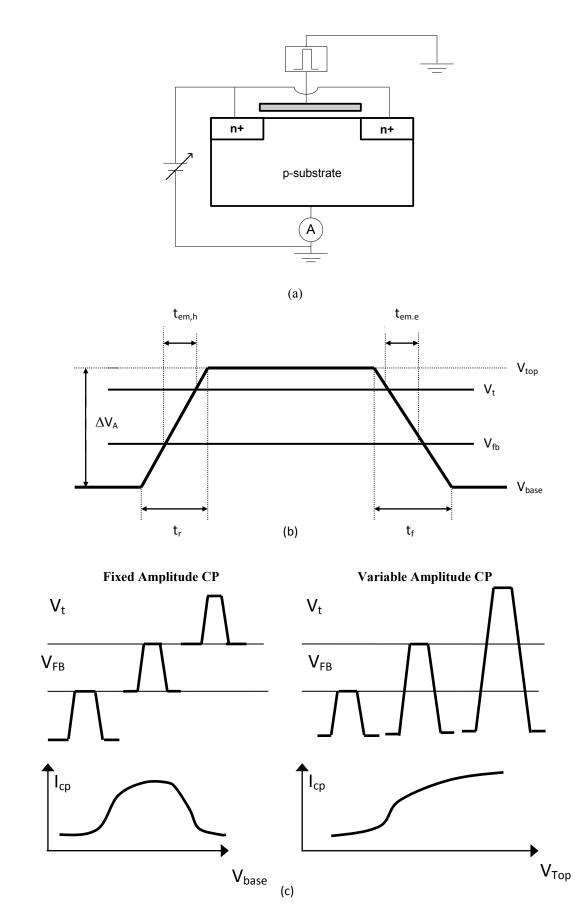

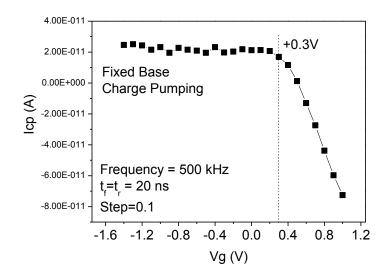

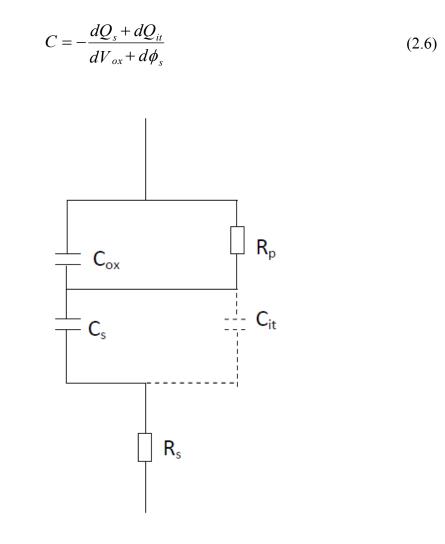

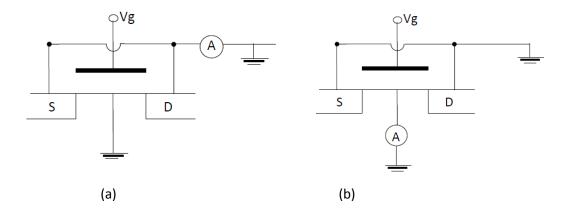

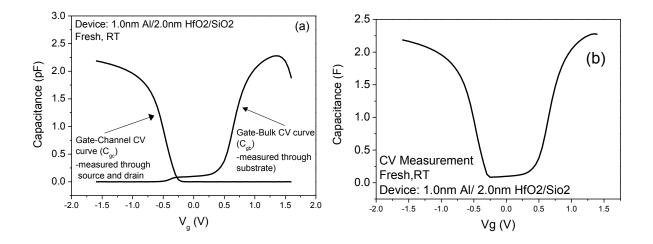

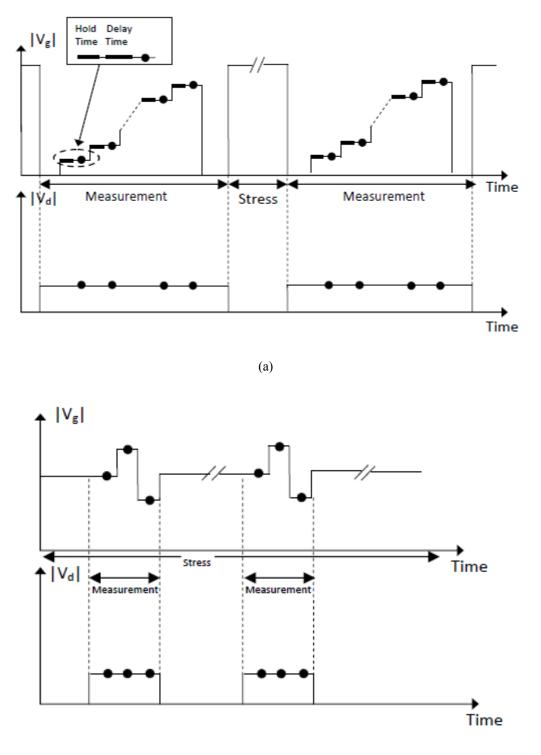

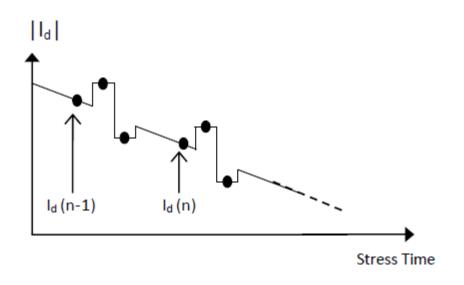

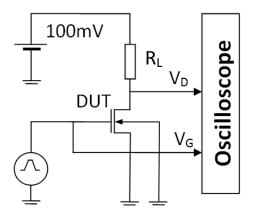

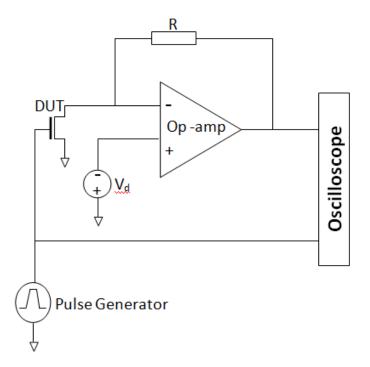

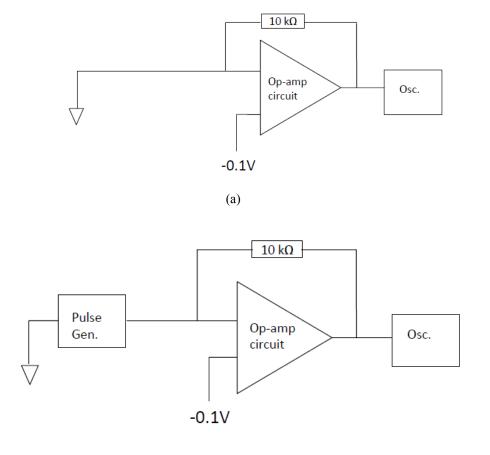

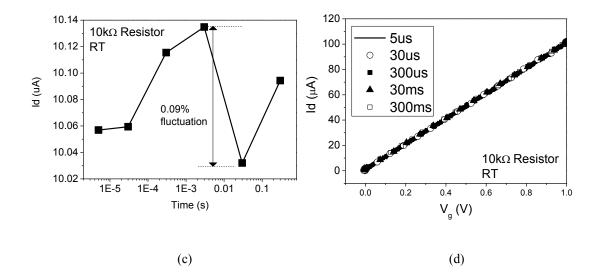

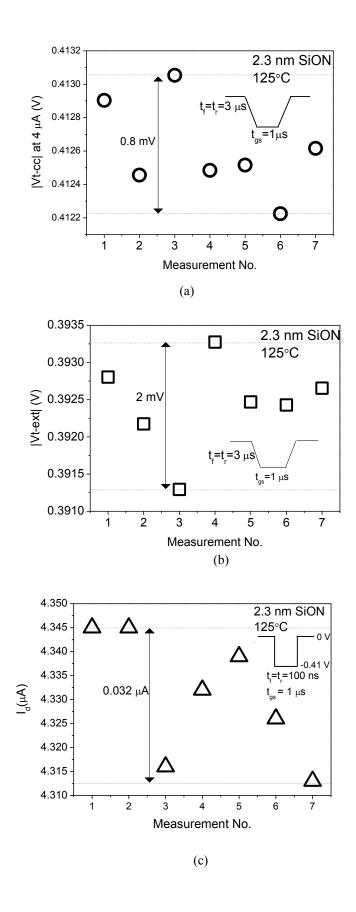

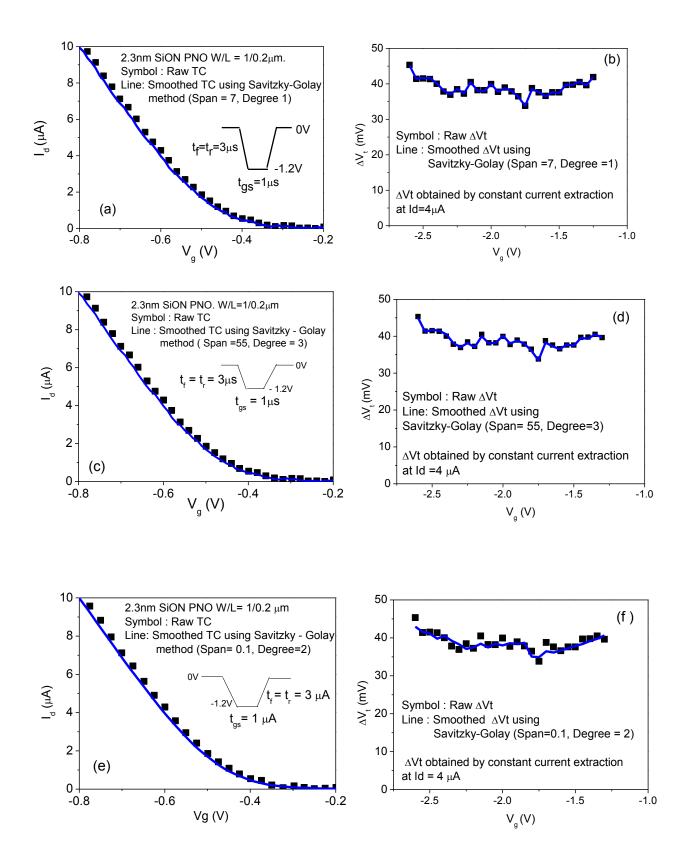

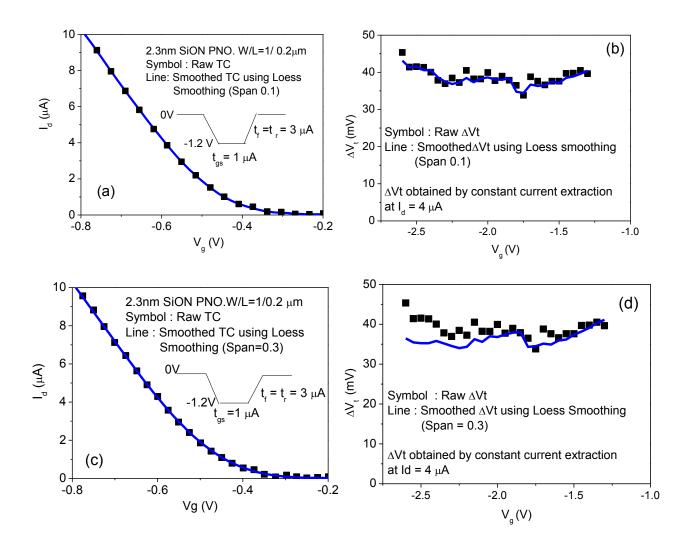

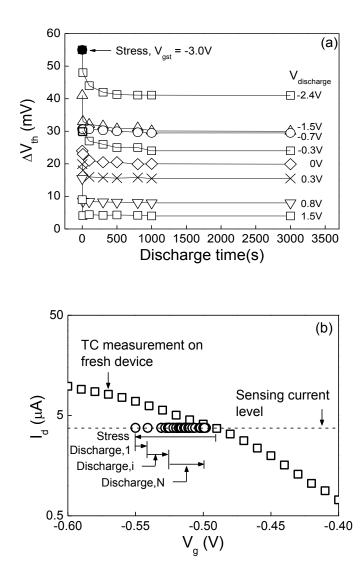

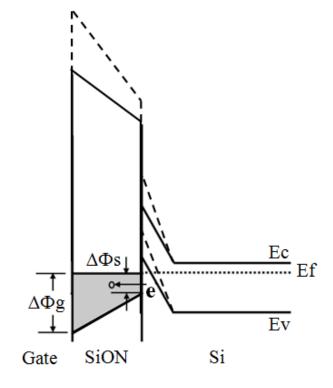

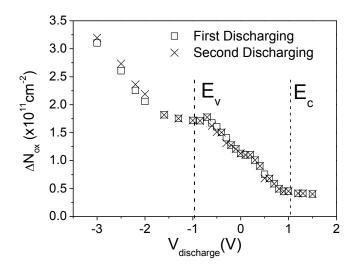

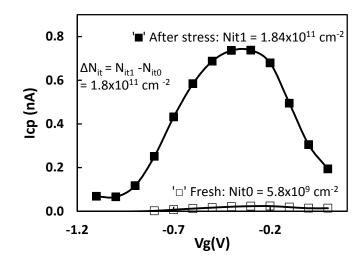

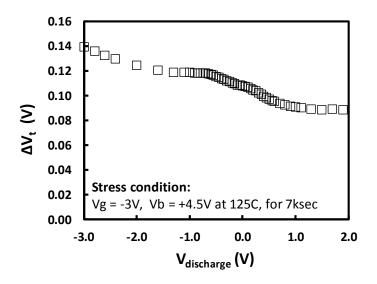

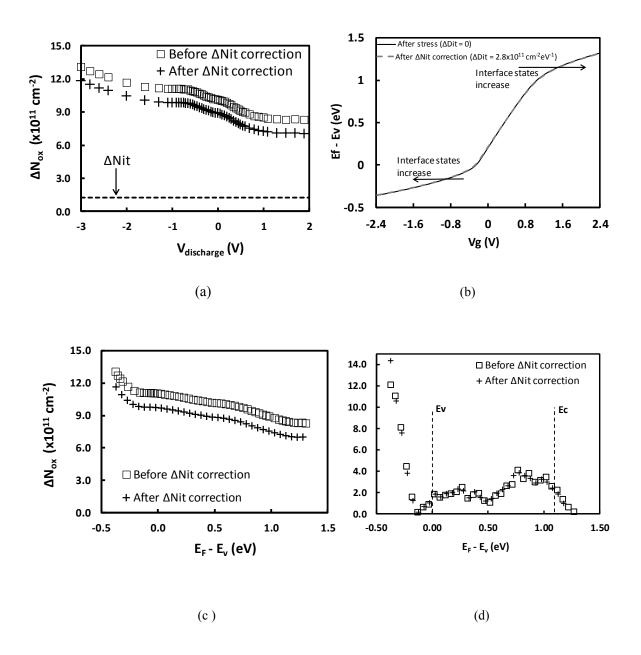

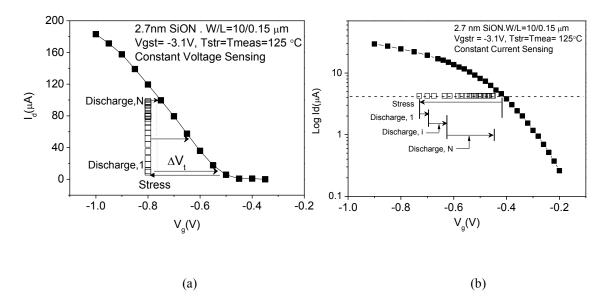

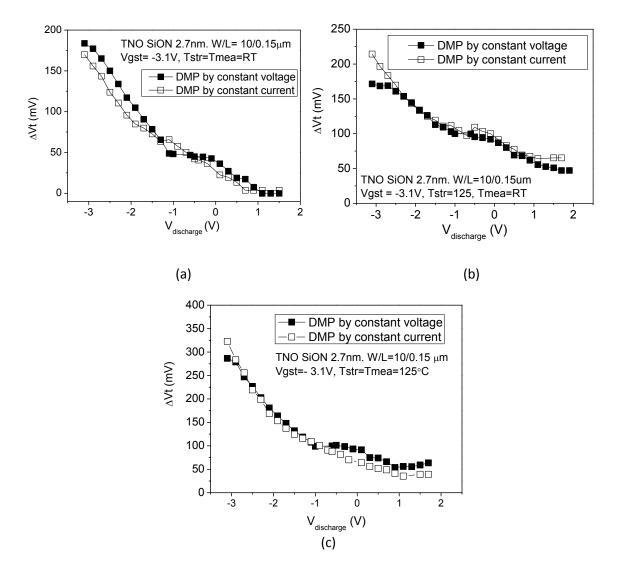

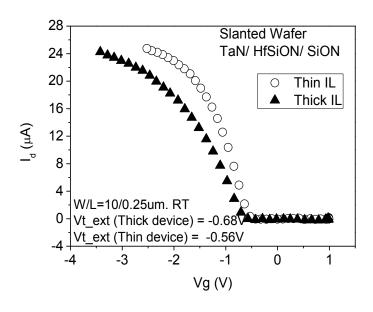

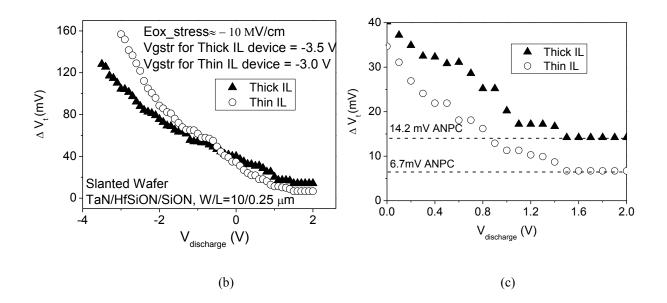

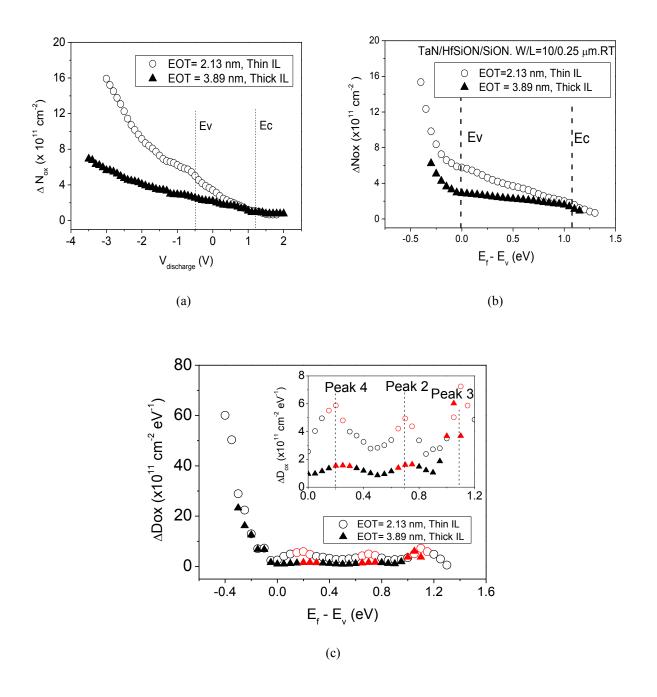

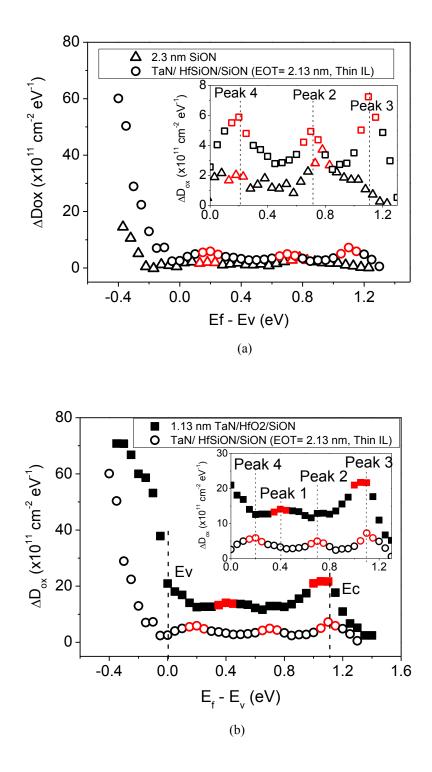

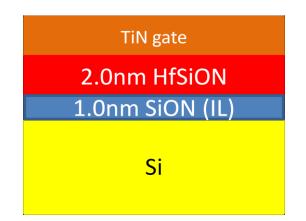

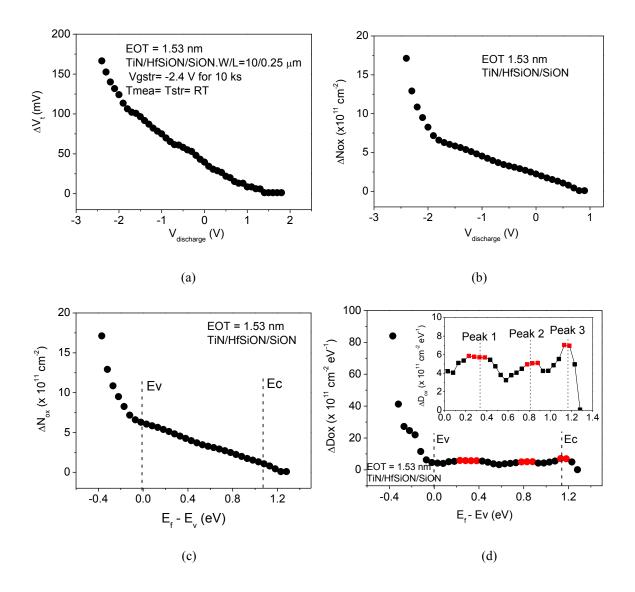

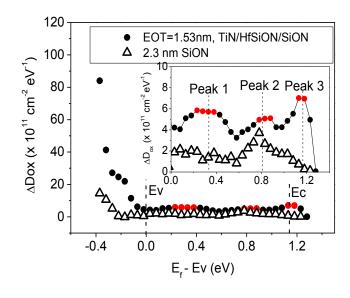

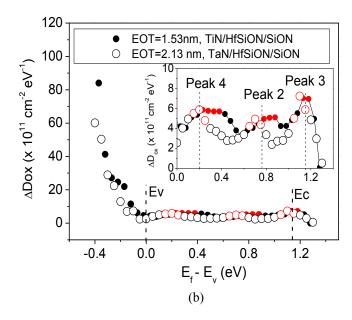

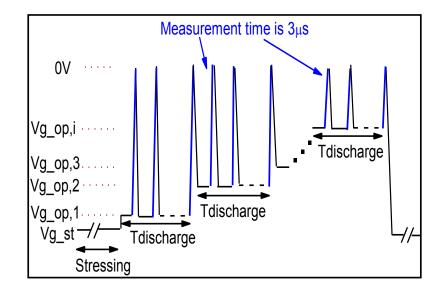

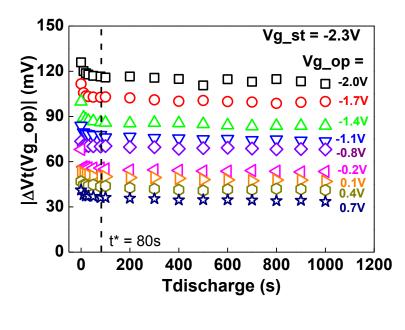

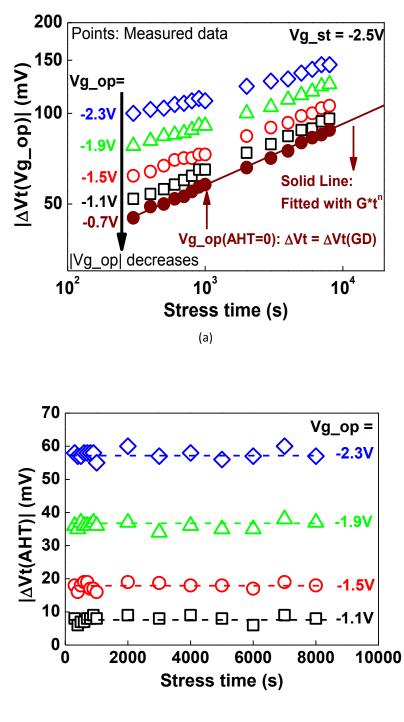

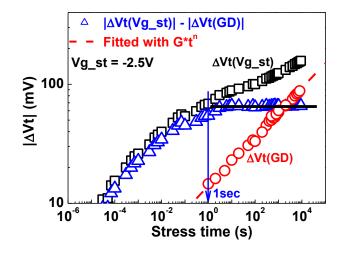

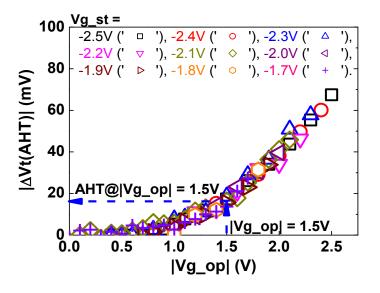

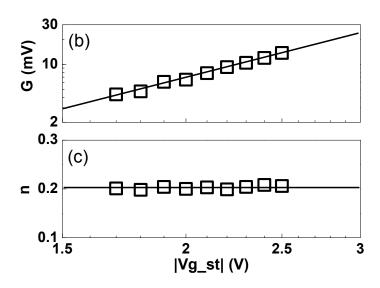

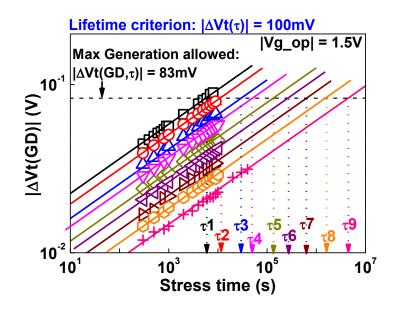

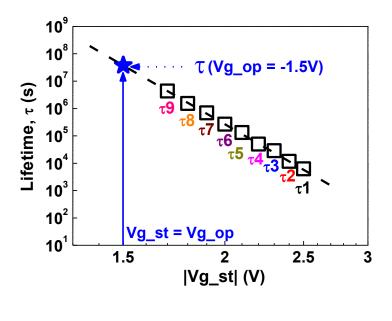

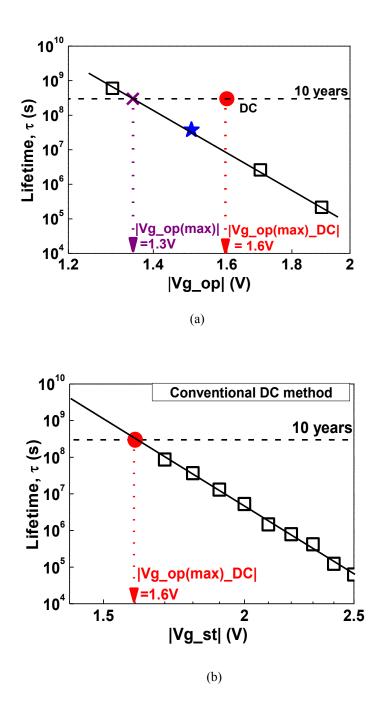

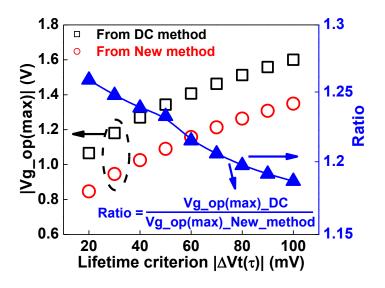

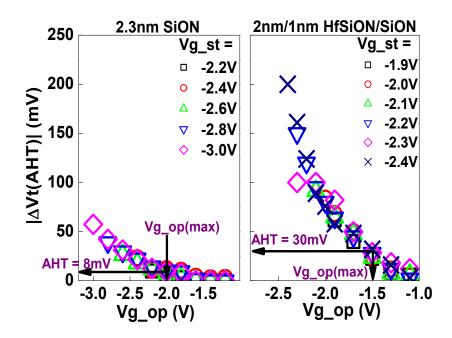

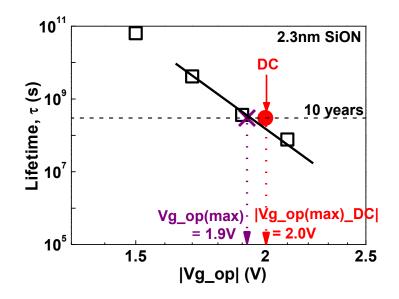

#### 2.1 Introduction