### **Original citation:**

Ortiz Gonzalez, Jose, Alatise, Olayiwola M., Hu, Ji, Ran, Li and Mawby, P. A. (Philip A.). (2016) An investigation of temperature sensitive electrical parameters for SiC power MOSFETs. IEEE Transactions on Power Electronics.

### **Permanent WRAP URL:**

http://wrap.warwick.ac.uk/85100

### **Copyright and reuse:**

The Warwick Research Archive Portal (WRAP) makes this work by researchers of the University of Warwick available open access under the following conditions. Copyright © and all moral rights to the version of the paper presented here belong to the individual author(s) and/or other copyright owners. To the extent reasonable and practicable the material made available in WRAP has been checked for eligibility before being made available.

Copies of full items can be used for personal research or study, educational, or not-for profit purposes without prior permission or charge. Provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

### Publisher's statement:

"© 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting /republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works."

### A note on versions:

The version presented here may differ from the published version or, version of record, if you wish to cite this item you are advised to consult the publisher's version. Please see the 'permanent WRAP URL' above for details on accessing the published version and note that access may require a subscription.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

IEEE TRANSACTIONS ON POWER ELECTRONICS

# An Investigation of Temperature Sensitive Electrical Parameters for SiC Power MOSFETs

Jose Ortiz Gonzalez *Student Member, IEEE*, Olayiwola Alatise, Ji Hu, Li Ran *Senior Member, IEEE*, and Philip Mawby, *Senior Member, IEEE*

Abstract—This paper examines dynamic Temperature Sensitive Electrical Parameters (TSEPs) for SiC MOSFETs. It is shown that the output current switching rate  $(dI_{DS}/dt)$  coupled with the gate current plateau (IGP) during turn-ON would be the most effective under specific operating conditions. Both parameters increase with the junction temperature of the device as a result of the negative temperature coefficient of the threshold voltage. The temperature dependency of  $dI_{DS}/dt$  has been shown to increase with the device current rating (due to larger input capacitance) and external gate resistance ( $RG^{EXT}$ ). However, as  $dI_D s/dt$  is increased by using a small  $R_G^{EXT}$ , parasitic inductance suppresses the temperature sensitivity of the drain and gate current transients by reducing the "effective gate voltage" on the device. Since the temperature sensitivity of  $dI_{DS}/dt$  is at the highest with maximum  $R_G^{EXT}$ , there is a penalty from higher switching losses when this method is used in real time for junction temperature sensing. This paper investigates and models the temperature dependency of the gate and drain current transients as well as the compromise between the increased switching loss and the potential to implement effective condition monitoring using the evaluated TSEPs.

Index Terms— Power Semiconductor Devices, Power MOSFETs, Switching Transients, Temperature Measurement

### I. INTRODUCTION

CONDITION monitoring of power electronic devices involves ascertaining the state of health of the devices during field operation. This can be used, through lifetime estimation and operational management, for prolonging the service of the converter and minimizing the damage. The junction temperature of the power device is often used as an indicator of device condition [1]. Devices that have been subjected to numerous power and temperature cycles typically exhibit higher junction-to-case thermal resistances resulting from solder cracks, die attach voiding and may also exhibit higher source and gate contact resistance [2]. This is due to the constant thermo-mechanical stresses resulting from the

This work was supported by the UK Engineering and Physical Science Research Council (EPSRC) through the Underpinning Power Electronics Devices Theme (EP/L007010/1) and the Components Theme (EP/K034804/1).

Jose Ortiz Gonzalez, Olayiwola Alatise, Li Ran and Philip Mawby are with the School of Engineering, University of Warwick, CV4 7AL, Coventry, UK. (e-mail: j.a.ortiz-gonzalez@warwick.ac.uk, o.alatise@warwick.ac.uk, l.ran@warwick.ac.uk, p.a.mawby@warwick.ac.uk)

Ji Hu was with the School of Engineering, University of Warwick, CV4 7AL, Coventry, UK. (e-mail: kimi aspire@hotmail.com).

semiconductor/die-attach/substrate like the interfaces or the wirebond/source metal interface. The most effective and direct way of sensing the condition of the device is to integrate temperature and current sensors directly with the chip. This is usually done for industrial organizations using custom made power devices fabricated specifically for targeted applications, hence, such design solutions are usually not available for generic power devices. Another effective method of condition monitoring is using TSEPs to estimate the indirectly through the junction temperature temperature dependence of an electrical parameter. Using TSEPs the temperature can be estimated during on-line and off-line operation. This is a wide area of research, with several TSEPs proposed and evaluated [3]. In [4-7], the threshold voltage is proposed as a TSEP using the known negative temperature coefficient of the threshold voltage to estimate the junction temperature during device switching. However, the time resolution required by the measurement instruments coupled with the background noise makes this a difficult technique to implement especially since 2 sensors are needed. Other reports have cited the IGBT on-state voltage drop as a TSEP at both low and high currents [8-10] and results have shown that it can be an effective way for monitoring the degradation of the power module [11]. In [12] the discharge time of the Miller capacitance is used as a TSEP and a circuit capable of detecting its temperature dependency is presented. However, using the Miller capacitance discharge time in SiC is complicated by the fact that SiC devices typically have significantly smaller parasitic capacitance than silicon IGBTs/MOSFETs because of the smaller die size. Furthermore, this technique is difficult to implement in SiC MOSFETs since the turn-OFF dV/dt is not as temperature sensitive as it is in silicon IGBTs [13]. The fast switching rate in SiC MOSFETs coupled with parasitic inductances induces electromagnetic oscillations in the voltage and current characteristics [14]. Furthermore, oscillations in the drainsource voltage resulting from source inductance are transmitted back to the gate voltage characteristics through the Miller capacitance [15], hence, monitoring the gate transient as a TSEP is complicated. In [16], harmonic analysis of an IGBT converter output is used as a TSEP whereas in [17, 18] the temperature dependency of the gate current in MOSFETs and IGBTs has been used as a TSEP for condition monitoring with promising results demonstrated. In the case of Si

mismatch in the coefficients of thermal expansion at critical

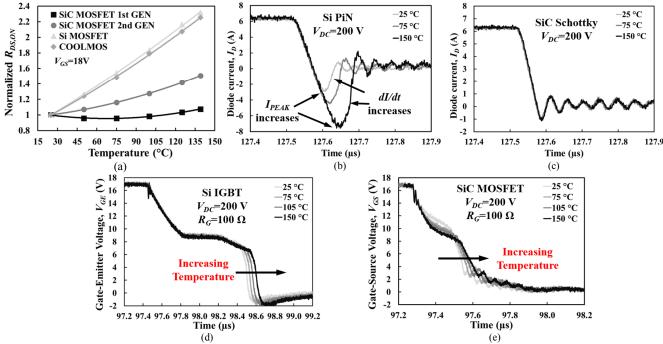

Fig. 1. (a) ON-state resistance as a function of temperature for different MOSFET technologies, (b) Silicon PiN diode reverse recovery characteristics at different temperatures, (c) SiC Schottky diode turn-OFF characteristics at different temperatures, (d) Silicon IGBT gate voltage during turn OFF at different temperatures (e) SiC MOSFET gate voltage during turn OFF at different temperatures

MOSFETs, the switching rate during turn ON was evaluated as a TSEP in [19], and the characteristics of SiC MOSFETs [20-22] suggest that the dynamic properties of SiC during turn ON can be a suitable TSEP.

MOSFETs have demonstrated higher conversion efficiency and power density through reduced conduction and switching losses based on the material properties of silicon carbide [23]. SiC devices are gaining popularity and if their potential is to be maximized, the question of condition monitoring will become an important topic. Due to the wide bandgap in SiC (~3.3 eV), the intrinsic carrier concentration is lower and more thermal energy is needed to excite carriers across the bandgap. As a result, SiC devices allow operation at high temperature exceeding 200°C. This fact makes condition monitoring of SiC MOSFETs using TSEPs a challenging task. The temperature dependency of the on-state resistance in SiC is not linear [24] and is low. Fig. 1(a) shows the measured ON-state resistances of different MOSFET technologies at different temperatures including two 1.2 kV SiC MOSFETs (from Cree/Wolfspeed with datasheet reference CMF10120D and C2M0160120D), a 1.2 kV silicon **IXYS** MOSFET (from with datasheet reference IXFX20N120P) and a 900 V CoolMOS device (from Infineon with datasheet reference IPW90R340C3). It can be seen that the SiC MOSFETs show the lowest temperature sensitivity as far as the ON-state resistance is concerned, with the Cree/Wolfspeed second generation device showing higher temperature sensitivity than the first generation. Fig. 1(b) shows the reverse recovery characteristics of a silicon PiN diode during turn-OFF at different temperatures where it can be seen that the reverse recovery charge increases with temperature [25]. This is due to the positive temperature coefficient of minority carrier lifetime which has the effect to increase the stored charge in the diode drift region. Fig. 1(c) shows the turn-OFF transient of the SiC Schottky diode at different temperatures where it can be seen that there is no noticeable temperature sensitivity in the switching transients. Fig. 1(d) presents the gate voltage ( $V_{GE}$ ) turn-OFF transient of a 1.2 kV Si IGBT, where the temperature sensitivity of the discharge of the Miller capacitance can be easily observed, especially when a large gate resistance is used. The temperature sensitivity of the IGBT  $V_{GE}$  turn-OFF transient results from the bipolar nature of the device since minority carrier lifetime increases with temperature and the rate of the  $V_{CE}$  transient depends on the lifetime. In the case of silicon carbide MOSFETs, Fig. 1 (e), the significantly faster  $V_{DS}$ transient resulting from a much lower Miller capacitance results in a non-flat Miller plateau [20] and the unipolar nature of the device means there is less temperature sensitivity since there are no minority carriers.

Furthermore, the switching energy in SiC actually reduces as the temperature increases, thereby causing the device to dissipate less power during operation [21]. Hence, using the losses as a TSEP is therefore not straight-forward in SiC MOSFETs. In this paper it is shown that the temperature dependency of the current commutation rate  $(dI_{DS}/dt)$  and the gate current plateau  $I_{GP}$  can be the effective TSEPs. However, this becomes more challenging at high current commutation rates because parasitic inductances affect the temperature sensitivity of the gate and drain current transients. This paper will show that the temperature dependency of the  $dI_{DS}/dt$  and the gate current depends on the current rating (the die size) of the device as well as the external gate resistance. This dependency is based on the device capacitances and internal

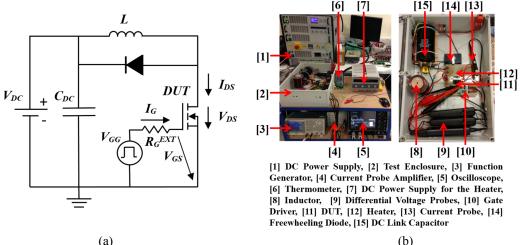

Fig. 2. (a) Electrical schematic of the experimental setup, (b) Experimental setup

gate resistances which affect the  $dI_{DS}/dt$  and its temperature sensitivity through parasitic inductance. Section II analyses the gate/drain current and its temperature dependency through analytical modelling and experimental measurements. Section II also discusses and models the impact of parasitic inductance on the temperature sensitivity of the  $I_{DS}$  turn ON transient. Section III discusses the load current and DC link voltage dependency of  $dI_{DS}/dt$  and  $I_{GP}$  and shows how it can be decoupled from its temperature sensitivity while Section IV concludes the paper.

## II. ANALYTICAL MODELLING OF THE GATE AND DRAIN CURRENT TEMPERATURE SENSITIVITY

The double pulse test set-up shown in Fig. 2 has been used for characterizing the turn-ON transient of SiC power MOSFETs at different temperatures, using a small temperature controlled heater attached to the discrete device. A 2 mH inductor L, a 470  $\mu$ F DC link capacitor  $C_{DC}$  and a 1.2 kV SiC Schottky diode with datasheet reference C4D10120A from Cree/Wolfspeed are the other elements of the test configuration. The electrical schematic and the test rig used are presented in Fig. 2(a) and Fig. 2(b) respectively. The measurements were performed at a DC link voltage  $V_{DC}$ =200 V, load current  $I_{DS}$ =9 A, gate driver voltage  $V_{GG}$ =0/18 V and a range of external gate resistances from  $R_G^{EXT}=10 \Omega$  to 220  $\Omega$ . A Tektronix current probe model TCP312 in conjunction with a Tektronix probe amplifier model TCPA300 were used for measuring the current. The current rating of the probe is 30 A DC, with a bandwidth of 100 MHz and a rise time of 3.5 ns.

The oscilloscope used for capturing the data was a Lecroy Wavesurfer 104MXs-B, with a bandwidth of 1 GHz and a rise time of 300 ps.

It is a general observation that the current commutation rate  $(dI_{DS}/dt)$  increases with temperature during the turn-ON transient of SiC power MOSFETs [20, 21] however what has not been adequately investigated is the impact of temperature on the gate current plateau and how this, together with the turn-ON  $dI_{DS}/dt$  can be used as a TSEP for junction temperature sensing in SiC power MOSFETs. The turn-ON of a MOSFET is described in [26-28]. The idealized plots of the gate current  $(I_G)$ , the drain-source current  $(I_{DS})$  and the gatesource voltage  $(V_{GS})$  transients for a SiC MOSFET during turn-ON at a low (25°C) and high (150 °C) junction temperatures are shown in Fig. 3(a). Fig. 3(b) shows experimental measurements for a 1.2 kV/42 A SiC MOSFET from Cree/Wolfspeed with datasheet reference CMF20120D. As can be seen from the measurements, the turn-ON  $dI_{DS}/dt$ increases with temperature, the gate-current plateau  $(I_{GP})$ increases with temperature and the gate voltage plateau  $(V_{GP})$ reduces with increasing temperature. During the turn-ON transient of the SiC MOSFET, the total gate current supplied by the gate driver is given by the time dependent combination of 3 stages described by (1), where  $I_G$  is the total gate current,  $C_{GS}$  is the gate source capacitance,  $C_{GD-HV}$  is the Miller capacitance at high drain voltage,  $C_{GD-LV}$  is the Miller capacitance at low drain voltage,  $V_{GG}$  is the gate drive voltage,  $R_G^{EXT}$  is the external gate resistance,  $R_G^{INT}$  is the internal gate resistance and  $V_{GP}$  is the plateau voltage.

$$I_{G} = \begin{cases} \frac{C_{GS}}{(C_{GS} + C_{GD-HV})} \frac{V_{GG}}{(R_{G}^{INT} + R_{G}^{EXT})} e^{\frac{t-t_{0}}{(R_{G}^{INT} + R_{G}^{EXT})(C_{GS} + C_{GD-HV})}} & for \ t_{0} < t < t_{1} \\ \frac{V_{GG} - V_{GP}}{R_{G}^{INT} + R_{G}^{EXT}} & for \ t_{1} < t < t_{2} \\ \frac{C_{GS}}{(C_{GS} + C_{GD-LV})} \frac{V_{GG} - V_{GP}}{(R_{G}^{INT} + R_{G}^{EXT})(C_{GS} + C_{GD-LV})} & for \ t_{2} < t < t_{3} \end{cases}$$

Fig. 3. (a) Idealized I<sub>G</sub>, I<sub>DS</sub> and V<sub>GS</sub> turn-ON transients for a SiC MOSFET at different temperatures, (b) Measured I<sub>G</sub>, I<sub>DS</sub> and V<sub>GS</sub> turn-ON transients for a SiC MOSFET at different temperatures

Assuming that the MOSFET gate is triggered at time  $t_0$  according to Fig. 3(a), between time  $t_0$  and  $t_I$ , the gate current charges the input capacitance  $C_{ISS}$  which is given by the sum of the gate-source capacitance  $(C_{GS})$  and the Miller capacitance  $(C_{GD})$ .

$$C_{ISS} = C_{GS} + C_{GD} \tag{2}$$

Depending on the RC time constant of the gate transient,  $V_{GS}$  will reach  $V_{TH}$  at time  $t_{TH}$  which is between  $t_0$  (when the gate is triggered) and  $t_1$  (when  $V_{GS}=V_{GP}$ ). The load current starts to rise at time  $t_{TH}$  and reaches its maximum at  $t_1$ , causing the  $V_{DS}$  across the MOSFET to fall to its on-state value thereby charging the Miller capacitance between  $t_1$  and  $t_2$ . The threshold voltage and time it takes for  $V_{GS}$  to rise to  $V_{TH}$  ( $t_{TH}-t_0$ ) have been presented as TSEPs for silicon MOSFETs [19]. Equation (3) models  $t_{TH}$ .

$$t_{TH} - t_0 = (R_G^{INT} + R_G^{EXT})C_{ISS} \ln \left(\frac{V_{GG}}{V_{GG} - V_{TH}}\right) =$$

$$= (R_G^{INT} + R_G^{EXT})C_{ISS} \ln \left(\frac{V_{GG}}{V_{GG} - \left(V_{TH}|_{25^{\circ}C} - \left|\frac{dV_{TH}}{dT}\right|(T_j - 25)\right)}\right)$$

(3)

As  $I_{DS}$  reaches the load current,  $V_{GS}$  reaches its plateau value ( $V_{GP}$ ) and the gate current reaches its plateau value ( $I_{GP}$ ). The gate voltage plateau ( $V_{GP}$ ) is given by (4).

$$V_{GP} = V_{TH} + \sqrt{\frac{I_{LOAD}L_{CH}}{\mu C_{OX}W_{CH}}}$$

$$\tag{4}$$

where  $\mu$  is the effective mobility,  $W_{CH}$  the MOSFET channel width,  $C_{OX}$  the gate oxide capacitance density and  $L_{CH}$  the MOSFET channel length. The 2 temperature sensitive parameters that determine the value of  $V_{GP}$  in (4) are the threshold voltage ( $V_{TH}$ ) and the effective mobility of the electrons in the channel of the MOSFET ( $\mu$ ).  $V_{TH}$  reduces with temperature as a result of temperature induced bandgap narrowing, which increases the intrinsic carrier concentration of the semiconductor thereby making the channel easier to invert [26]. The temperature dependency of  $V_{TH}$  is given by (5).

$$\frac{dV_{TH}}{dT} = \frac{d\psi_B}{dT} \left( 2 + \frac{1}{c_{OX}} \sqrt{\frac{\varepsilon_{SIC} q N_A}{\psi_B}} \right)$$

where

$$\frac{d\psi_B}{dT} \approx \frac{1}{T} \left[ \frac{E_g(0)}{2q} - |\psi_B| \right] \tag{6}$$

$\Psi_B$  is the potential difference between the Fermi level and the intrinsic Fermi level,  $\varepsilon_{SiC}$  is the dielectric constant of silicon carbide,  $N_A$  the doping density, q the electron charge and  $E_g(0)$ the band-gap energy at T=0 K. According to the datasheets and previously presented measurements [29, 30] the threshold voltage is higher for Si MOSFETs however, both SiC and Si MOSFETs have a similar  $dV_{TH}/dT$ . The effective mobility ( $\mu$ ) also reduces with temperature as a result of increased phonon scattering reducing the relaxation time between carrier-tolattice scattering events. The negative temperature coefficient of  $V_{TH}$  will reduce  $V_{GP}$  while the negative temperature coefficient of  $\mu$  will increase  $V_{GP}$ . Hence, assuming a constant load current, the more dominant parameter will determine the temperature behavior of  $V_{GP}$  with temperature.  $V_{GP}$  reduces with temperature in SiC MOSFETs while it is less temperature sensitive for Si MOSFETs.

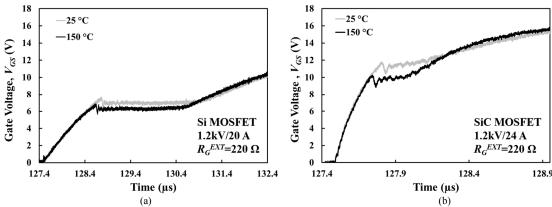

Fig. 4(a) shows the  $V_{GS}$  turn-ON transient for a 1.2 kV/20 A Si MOSFET while Fig. 4(b) shows the same measurements for a 1.2 kV/24 A SiC MOSFET. These measurements where performed with a low  $dI_{DS}/dt$  corresponding to an  $R_G^{EXT}$ =220  $\Omega$ . In this figure, some of the characteristics that define the switching of SiC MOSFETs [20] are clearly identified, namely (i) the higher value of the gate voltage plateau  $(V_{GP})$  caused by a lower transconductance compared to the silicon MOSFET (ii) a non-flat Miller plateau compared to the silicon MOSFET and (iii) a significantly reduced  $V_{GS}$  transient duration in the SiC MOSFETs as a result of the lower input capacitance compared to the silicon MOSFET. It should however be noted that at high  $dI_{DS}/dt$ , the presence of parasitic inductance in the path of  $I_{DS}$  masks the changing behavior of  $V_{GP}$  with temperature since the oscillations in  $I_G$ ,  $V_{GS}$  and  $V_{DS}$  dominate the measured transient characteristics.

Between time  $t_1$  and  $t_2$ , the Miller capacitance is charged and the  $V_{DS}$  transient occurs. At the end of  $t_2$ , the  $V_{DS}$  transient is complete and the  $V_{GS}$  resumes its exponential rise to  $V_{GG}$  but with a larger time constant since the Miller capacitance has increased due to its dependency on the  $V_{DS}$ . Between time  $t_0$  and  $t_1$  corresponding to the idealized switching transients shown in Fig. 3(a), the gate voltage ( $V_{GS}$ ) and its time derivative is given respectively by (7) and (8).

$$V_{GS} = V_{GG} \left( 1 - e^{-\frac{t - t_0}{(R_G^{NT} + R_G^{EXT})C_{ISS}}} \right)$$

(7)

$$\frac{dV_{GS}}{dt} = \frac{V_{GG}}{(R_G^{INT} + R_G^{EXT})C_{ISS}} e^{-\frac{I - I_0}{(R_G^{INT} + R_G^{EXT})C_{ISS}}}$$

(8)

When the gate voltage reaches the threshold voltage  $V_{TH}$ , the current starts to flow. Between time instants  $t_{TH}$  and  $t_{I}$ , assuming the MOSFET drain current is in saturation, the drain-source current ( $I_{DS}$ ) and its time derivative is given by (9) and (10) respectively.

$$I_{DS} = \frac{\beta}{2} (V_{GS} - V_{TH})^2 \tag{9}$$

$$\frac{dI_{DS}}{dt} = \beta (V_{GS} - V_{TH}) \frac{V_{GG}}{(R_G^{INT} + R_G^{EXT})C_{ISS}} e^{-\frac{t - l_0}{(R_G^{INT} + R_G^{EXT})C_{ISS}}}$$

(10)

The temperature dependency of the current commutation rate  $(dI_{DS}/dt)$  during turn-ON can be calculated by taking the derivative of (10) with respect to temperature and is given by (11).

$$\frac{d^{2}I_{DS}}{dt \cdot dT} = \frac{V_{GG}e^{-\frac{I-I_{0}}{(R_{G}^{NT} + R_{G}^{ET})C_{RS}}}}{(R_{G}^{NT} + R_{G}^{EXT})C_{ISS}} \left(\beta \left| \frac{dV_{TH}}{dT} \right| - (V_{GS} - V_{TH}) \left| \frac{d\beta}{dT} \right| \right) (11)$$

Fig. 4. (a) The  $V_{GS}$  turn-ON transient for the Si MOSFET at 25 °C and 150 °C, (b) The  $V_{GS}$  turn-ON transient for the SiC MOSFET at 25 °C and 150 °C

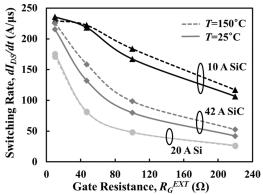

Fig. 5. The measured switching rate as a function of  $R_G^{\rm EXT}$  for the different technologies at 25 °C and 150 °C

Given the temperature characteristics of different power MOSFETs, (11) can be used to identify the temperature sensitivity of the switching rate as a potential TSEP for condition monitoring. The switching rate of different MOSFET technologies has been measured and shown as a function of the external gate resistance ( $R_G^{EXT}$ ) in Fig. 5 for 25 °C and 150 °C measurements. By comparing the switching rate measured at both temperatures, it can be seen that the switching rate of the silicon MOSFET is temperature invariant while that of the SiC MOSFETs increases with temperature for larger  $R_G^{EXT}$ . The 3 factors affecting  $dI_{DS}/dt$  and its temperature sensitivity, namely device technology, current rating and external gate resistance, are evaluated in the following subsections.

### A. Impact of Device Technology on $dI_{DS}/dt$ as a TSEP

Equation (11) applies to all MOSFET technologies, however, the behavior of  $dI_{DS}/dt$  with respect to temperature differs according to the device technology, as the measurements on Fig. 5 show. Measurements from literature and datasheets show that for SiC MOSFETs, the turn-ON  $dI_{DS}/dt$  increases with temperature [21, 29, 31], while for silicon MOSFETs devices [32], the turn-ON  $dI_{DS}/dt$  is either temperature invariant or decreases with temperature. The reason for this is due to  $d\beta/dT$ , which is very low in SiC MOSFETs but is negative in silicon MOSFETs.  $\beta$  is dependent on temperature through the effective channel mobility which decreases as temperature increases but can be considered constant for SiC MOSFETs due to its wide bandgap characteristics [33].

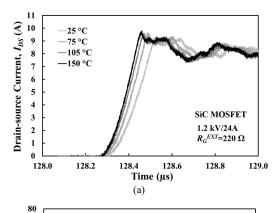

Fig. 6(a) and Fig. 6(b) show the turn-ON drain-source ( $I_{DS}$ ) and gate ( $I_G$ ) current transients for a 1.2 kV/24 A SiC MOSFET. The measurements were done using an external gate resistance  $R_G^{EXT}$  of 220  $\Omega$  and it can be seen that the turn-ON  $dI_{DS}/dt$  and the gate current plateau both increase with temperature. In the case of silicon and silicon carbide MOSFETs, the drain current transient shifts leftwards in time as the temperature is increased due to the negative temperature coefficient of the threshold voltage causing the device to switch sooner at higher temperatures. In the case of silicon MOSFETs, the  $dI_{DS}/dt$  does not increase with temperature so the current transients are approximately parallel, since the  $d\beta/dT$  counteracts  $dV_{TH}/dT$  [32], thereby making  $dI_{DS}/dt$  less temperature sensitive. However, in SiC MOSFETs,  $d\beta/dT$  can

Fig. 6. (a) Drain-source current  $(I_{DS})$  for a 24 A SiC MOSFET during turn-ON at different temperatures, (b) Gate current  $(I_G)$  for a 24 A SiC MOSFET during turn-ON at different temperatures

be neglected over the temperature range selected [33], hence  $dI_{DS}/dt$  increases with temperature due to  $dV_{TH}/dT$ .

### B. Impact Impact of Device Current Rating on $dI_{DS}/dt$ as a TSFP

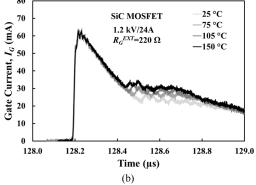

The turn-ON current commutation rate of the SiC MOSFET has been identified as a potential TSEP. However, the temperature sensitivity of  $dI_{DS}/dt$  in SiC power MOSFETs needs to be investigated as a function of the device current rating. Fig. 7(a) shows the drain-source and gate current transient during turn-ON for a 1.2 kV/42 A SiC MOSFET while Fig. 7(b) shows similar measurements for the 1.2 kV/10 A SiC MOSFET. In both measurements the external gate resistance used is 220  $\Omega$ . It can be seen by comparing Fig. 7(a) and Fig. 7(b), that the temperature sensitivity of  $dI_{DS}/dt$  is smaller for the 10 A SiC power MOSFET compared to the 42 A SiC MOSFET. The temperature sensitivity of the gate current plateau ( $I_{GP}$ ) is also higher for the 42 A MOSFET. Due to the fact that the 10 A die is physically smaller compared to the 42 A die, it has a smaller switching time constant which can be expressed as the product of the total input resistance and the total input capacitance i.e.  $(R_G^{EXT} + R_G^{INT})C_{ISS}$ . According to the datasheets, the 10 A SiC MOSFET has an input capacitance of 0.259 nF while the 42 A device has an input capacitance of 1.915 nF. The result is significantly higher  $dI_{DS}/dt$  in the 10 A MOSFET as can be seen in Fig. 5 where significantly higher  $dI_{DS}/dt$  is measured in the 10 A SiC MOSFET compared to the 42 A SiC MOSFET. It can also be seen from Fig. 5 that at low external  $R_G^{EXT}$ , the temperature sensitivity of  $dI_{DS}/dt$  reduces for both SiC MOSFETs. A large external gate resistance of 220  $\Omega$  was used in these

Fig. 7. (a). Drain-source current ( $I_{DS}$ ) and gate current ( $I_G$ ) for the 1.2kV/42 A SiC MOSFET during turn-ON at different temperatures, (b). Drain-source current ( $I_{DS}$ ) and gate current ( $I_G$ ) for the 1.2kV/10 A SiC MOSFET during turn-ON at different temperatures

measurements, partially to limit the impact of the internal gate resistance (which is 5  $\Omega$  for the 42 A SiC MOSFET and 11.4  $\Omega$  for the 10 A device) and to improve the time resolution of the gate current plateau. However, in practical applications where there is a need to minimize switching losses and expedite the fast switching potential of SiC MOSFETs, a smaller gate resistance is preferable. As will be shown later, this increases the impact of the parasitic inductance which affects the effectiveness of  $dI_{DS}/dt$  as a TSEP in SiC MOSFETs.

### C. Impact of the External $R_G$ on $dI_{DS}/dt$ as a TSEP

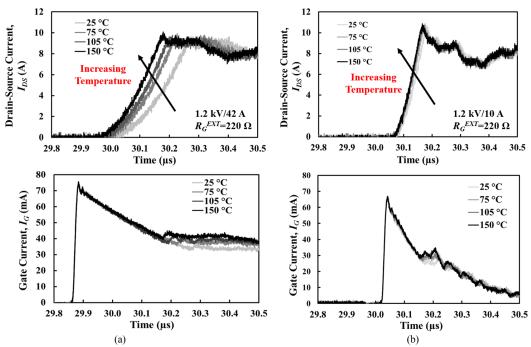

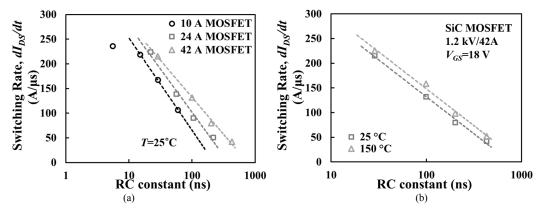

In this subsection, the effectiveness of the turn-ON  $dI_{DS}/dt$  as a TSEP in SiC MOSFETs is investigated over a range of external gate resistance for devices of 3 different current ratings.—The  $dI_{DS}/dt$  was calculated as the slope of the linear regression of the drain current for the 3 SiC MOSFETs (10 A, 24 A and 42 A) and the results are presented in Table I. In this table, the switching time constant, which is given by  $(R_G^{EXT} + R_G^{INT})C_{ISS}$  is used to compare the switching rates of the different devices. Fig. 8(a) and 8(b) are the graphical representation of the plots presented in table I. Fig. 8(a) shows

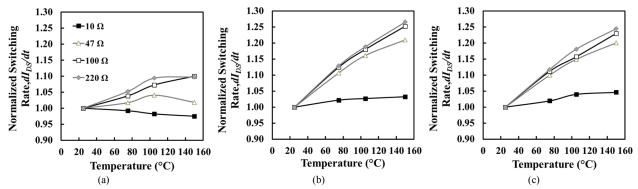

the switching rate as a function of the RC constant for the 3 SiC MOSFETs (10 A, 24 A and 42 A) evaluated at a temperature of 25 °C. It can be observed that the 3 devices have similar maximum switching rates for the smaller RC constants, but in the case of the 10 A SiC MOSFET, the  $dI_{DS}/dt$  is limited by the impact of the inductance on the load path. Fig. 8(a) shows the MOSFETs with a higher transconductance will exhibit a higher switching rate compared to a lower one even if they are switched with the same RC time constant. Hence, in Fig. 8(a), the 42 A MOSFET switches with the highest switching rate because transconductance increases with the current rating. Fig. 8(b) shows the measured  $dI_{DS}/dt$  as a function of the RC constant for the 42 A SiC MOSFET at 25 °C and 150 °C, where the reduced temperature sensitivity at lower RC constants, i.e. lower  $R_G^{EX}$ , can be seen. Figs. 9(a), 9(b) and 9(c) show the normalized  $dI_{DS}/dt$  as a function of temperature for different external gate resistances ( $R_G^{EXT}$ ) in the 10 A, 24 A and the 42 A SiC MOSFETs respectively. The results here generally show that the temperature sensitivity of  $dI_{DS}/dt$  decreases with the external gate resistance as well as with the current rating i.e. to use  $dI_{DS}/dt$  as a TSEP, the SiC MOSFET must be driven

TABLE I: SWITCHING RATE DURING TURN-ON FOR THE EVALUATED 1.2 KV SIC MOSFETs AT DIFFERENT TEMPERATURES AND EXTERNAL GATE RESISTANCES

| Device                                                 | 10 A SiC MOSFET<br>(C2M0280120D) |       |       |       | 24 A SiC MOSFET<br>(CMF10120D) |       |       |       | 42 A SIC MOSFET<br>(CMF20120D) |       |       |       |

|--------------------------------------------------------|----------------------------------|-------|-------|-------|--------------------------------|-------|-------|-------|--------------------------------|-------|-------|-------|

| $(R_G^{INT}+R_G^{EXT})C_{ISS}$ (ns)                    | 5.5                              | 15.1  | 28.9  | 59.9  | 21.9                           | 56.2  | 105.4 | 216.8 | 28.7                           | 99.6  | 201.1 | 430.9 |

| $dI_{DS}/dt$ , $T = 25 ^{\circ}\text{C}$ (A/ $\mu$ s)  | 235.8                            | 218.3 | 167.3 | 106.6 | 223.9                          | 138.9 | 90.1  | 51.1  | 215.5                          | 132.0 | 80.0  | 42.1  |

| $dI_{DS}/dt$ , $T = 75 \circ_C (A/\mu s)$              | 234.0                            | 222.1 | 173.8 | 112.1 | 228.8                          | 153.7 | 101.3 | 57.6  | 219.7                          | 145.1 | 88.9  | 47.0  |

| $dI_{DS}/dt$ , $_{T=105}$ $\circ_{\rm C}$ (A/ $\mu$ s) | 231.6                            | 227.2 | 179.5 | 116.6 | 229.9                          | 161.2 | 106.3 | 60.7  | 224.0                          | 151.6 | 92.5  | 49.7  |

| $dI_{DS}/dt$ , $T=150$ °C (A/ $\mu$ s)                 | 229.9                            | 222.3 | 184.1 | 116.9 | 231.2                          | 168.0 | 112.9 | 64.6  | 225.4                          | 158.4 | 98.4  | 52.4  |

Fig. 8. (a) The measured turn-ON  $dI_{DS}/dt$  as a function of the RC constant for the evaluated SiC MOSFETs at 25 °C, (b) The measured turn-ON  $dI_{DS}/dt$  as a function of the RC constant for 42 A SiC MOSFETs at 25 °C and 150 °C

Fig. 9. (a) Normalized  $dI_{DS}/dt$  as a function of temperature for different  $R_G^{EXT}$  in the 1.2 kV/10 A SiC MOSFET, (b) Normalized  $dI_{DS}/dt$  as a function of temperature for different  $R_G^{EXT}$  in the 1.2 kV/24 A SiC MOSFET, (c) Normalized  $dI_{DS}/dt$  as a function of temperature for different  $R_G^{EXT}$  in the 1.2 kV/42 A SiC MOSFET

with a large external gate resistance and the technique is most effective when the device current rating is high.

To understand the reduction of temperature sensitivity of  $dI_{DS}/dt$  at small  $R_G^{EXT}$  and at smaller current ratings, it is important to re-derive the equations of  $dI_{DS}/dt$  and its temperature sensitivity with the added effect of the parasitic source inductance  $(L_S)$  [34, 35]. Equations (12) and (13) model the turn-ON  $I_{DS}$  for the MOSFET and its time derivative respectively. However, the presence of the source inductance means that the source voltage can no longer be assumed to be zero but instead is given as the product of the source inductance and the  $dI_{DS}/dt$ .

$$I_{DS} = \frac{\beta}{2} (V_G - V_S - V_{TH})^2$$

where  $V_S = L_S \frac{dI_{DS}}{dt}$  (12)

$$\frac{dI_{DS}}{dt} = \beta \left( V_G - L_S \frac{dI_{DS}}{dt} - V_{TH} \right) \left( \frac{dV_G}{dt} - L_S \frac{d^2 I_{DS}}{dt^2} \right)$$

(13)

Equation (13) is a  $2^{nd}$  order ODE that can be simplified by assuming a constant  $dI_{DS}/dt$  whose derivative  $(d^2I_{DS}/dt^2)$  is therefore zero. This assumption does not reduce the accuracy of the proposed model as will be seen later. Hence, the turn-ON  $dI_{DS}/dt$  can be expressed using (14).

$$\frac{dI_{DS}}{dt} = \frac{\beta \left(V_G - V_{TH} \right) \left(\frac{dV_G}{dt}\right)}{1 + \beta L_S \left(\frac{dV_G}{dt}\right)}$$

(14)

When (14) is combined with (8), the resultant equation is given by (15)

$$\frac{dI_{DS}}{dt} = \frac{\beta (V_G - V_{TH}) \left( \frac{V_{GG}}{(R_G^{INT} + R_G^{EXT})(C_{ISS})} e^{\frac{t - t_0}{(R_G^{INT} + R_G^{EXT})(C_{ISS})}} \right)}{1 + \beta L_S \left( \frac{V_{GG}}{(R_G^{INT} + R_G^{EXT})(C_{ISS})} e^{-\frac{t - t_0}{(R_G^{INT} + R_G^{EXT})(C_{ISS})}} \right)}$$

(15)

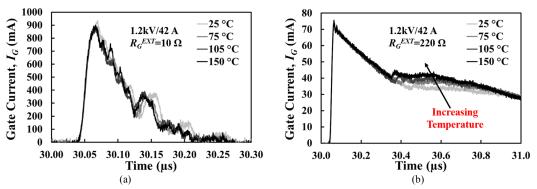

Figs. 10(a) and 10(b) show the gate current measurements for the 42 A SiC MOSFET using a  $R_G^{EXT}$ =10  $\Omega$  and a  $R_G^{EXT}$ =220  $\Omega$  respectively. It can be seen from Fig. 10, that the temperature dependency of the gate current plateau is higher for the large external gate resistance and the impact of the oscillations has also been minimized.

Equation (15) is useful for understanding how the current commutation rate is determined by the external gate resistance and temperature in the presence of parasitic inductance in the source-drain current path. It is well understood that reducing the  $R_G^{EXT}$  increases  $dI_{DS}/dt$ , however, the rate at which this occurs also depends on the parasitic capacitances, the internal gate resistance, the parasitic inductance and temperature.

Fig. 10. (a). The measured turn-ON gate current for the 42 A SiC MOSFET at different junction temperatures with  $R_G^{EXT}$ =10  $\Omega$ , (b) The measured turn-ON gate current for the 42 A SiC MOSFET at different junction temperatures with  $R_G^{EXT}$ =220  $\Omega$

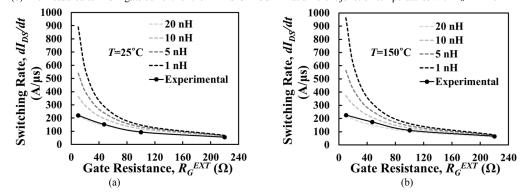

Fig. 11. (a) The modelled and measured turn-ON  $dI_{DS}/dt$  for the 42 A SiC MOSFET showing the impact of parasitic inductance at 25 °C, (b) The modelled and measured turn-ON  $dI_{DS}/dt$  for the 42 A SiC MOSFET showing the impact of parasitic inductance at 150 °C

Using (15),  $dI_{DS}/dt$  has been calculated for the 1.2kV/42 A SiC MOSFETs for different external gate resistances, temperatures and parasitic inductances. The  $dI_{DS}/dt$  has been calculated for a load current  $I_{DS}$  of 9 A and assuming a constant mobility for the SiC MOSFET as has been discussed in Subsection II-a. Datasheet parameters were used in (15) and these include  $C_{ISS}$ being 1.915 nF,  $V_{GG}$  being 18 V, internal gate resistance  $R_G^{INT}$ being 5  $\Omega$  and the threshold voltage being 3.2 V at 25 °C and 2.3 V at 150 °C. Fig. 11(a) shows the results of the model for different  $R_G^{EXT}$  and parasitic inductance together with experimental measurements at 25 °C while Fig. 11(b) shows similar modeling and measurement results at 150 °C. It can be seen that the model and measurements agree at large  $R_G^{EXT}$ , however, as  $R_G^{EXT}$  is reduced and  $dI_{DS}/dt$  is increased, the model matches the measurements when parasitic inductance is accounted for. The model shows that the parasitic inductance is within the range of 15 to 20 nH. By comparing the modelled and measured  $dI_{DS}/dt$  at the different temperatures for the different  $R_G^{EXT}$ , it was observed that the positive temperature coefficient of  $dI_{DS}/dt$  reduced with decreasing  $R_G^{EXT}$  as a result of the parasitic inductance. And this effect was more apparent at high  $dI_{DS}/dt$  which explains why the 10 A SiC MOSFET (with significantly reduced input capacitance) exhibited a  $dI_{DS}/dt$  that was temperature insensitive at low  $R_G^{EXT}$ . Hence, this shows that the parasitic inductance reduces the temperature sensitivity of  $dI_{DS}/dt$ . It is important to mention that the impact of the parasitic inductance  $L_S$  not only limits the temperature sensitivity of  $dI_{DS}/dt$  as shown in this paper, but it can also be used as a temperature sensor if there is an additional terminal connected to the internal source of the

power module so that the voltage drop across the parasitic inductance can be sensed. This method of using internal terminals across the stray inductance has been proposed for identifying the turn-off delay in IGBTs [36]. Equation (12) suggests that the voltage across the stray inductance can be used for identifying  $dI_{DS}/dt$  and junction temperatures in SiC MOSFETs.

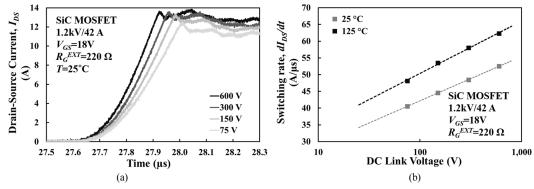

### III. RESULTS FOR CONDITION MONITORING IMPLEMENTATION

If the switching rate is to be used as a TSEP for condition monitoring in SiC power MOSFETs, then its relationship with other parameters like load current and DC link voltage must be calibrated. Any load current and/or voltage dependency of  $dI_{DS}/dt$  should be decoupled from its temperature dependency so that it can be used for junction temperature sensing. The measurements and analysis presented in section II were performed using a DC link voltage of 200 V which is well below the 1200 V rated blocking voltage of the devices studied. Considering an application point of view, DC link voltages of 300 to 600 V are widely used in applications like automotive drivetrains [37], hence the evaluation of  $dI_{DS}/dt$ and its temperature sensitivity at those voltage levels should be investigated. The dependency of the switching rate on the DC link voltage and temperature has been investigated by experimental measurements. The results are shown in Fig. 12(a) where the turn-ON current transient has been shown for different DC link voltages for the 42A SiC power MOSFET at a temperature of 25 °C switched with  $R_G^{EXT}$ =220  $\Omega$ . The DC link voltage values ( $V_{DC}$ ) are 75 V, 150 V, 300 V and 600 V.

Fig. 12. (a) Drain-source ( $I_{DS}$ ) for the 42 A SiC MOSFET during turn-ON for different DC link voltages, (b)  $dI_{DS}/dt$  for the 42 A SiC MOSFET during turn-ON as a function of the DC link voltage at 25 °C and 125 °C

Fig. 12(b) shows the measured  $dI_{DS}/dt$  characteristics as a function of the DC link voltage for two temperatures, namely 25 °C and 125 °C.

It can be seen from Fig. 12(a) that the turn-ON switching rate is increasing with the supply voltage. This is due to the fact that the input capacitance reduces with increasing DC supply voltage as a result of the voltage-dependent Miller capacitance. The Miller capacitance is comprised of a series combination of an oxide capacitance and a voltage dependent depletion capacitance that increases as the supply voltage reduces. Increasing the supply voltage increases the depletion width and hence reduces the Miller capacitance [26]. Hence, at low  $V_{DC}$ , the high Miller capacitance slows down the MOSFET. Since the DC link voltage is usually held constant in voltage source converter applications, the dependency of  $dI_{DS}/dt$  on  $V_{DC}$  is not critical in its use as a TSEP. In addition,

by analyzing the switching rate as a function of the supply voltage for two temperatures presented in Fig. 12(b), it can be seen that the temperature sensitivity of the switching rate is constant for the different DC voltages evaluated. As the DC voltage is increased from 75 V to 600 V,  $dI_D s/dt$  increases with temperature by 20%. However, as the nominal switching rate is affected by the DC link voltage value, the use of  $dI_D s/dt$  as TSEP would require an initial calibration.

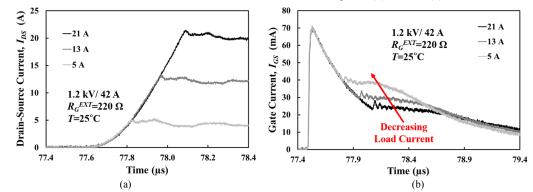

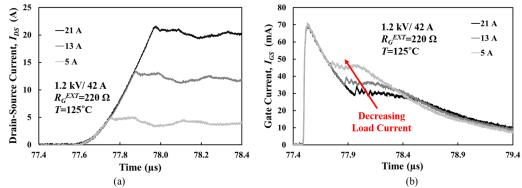

The impact of the load current on the switching transient is presented in Fig. 13. Fig. 13(a) shows the turn-ON drain-source current characteristics of the 42 A SiC power MOSFET switched with  $R_G$ =220  $\Omega$  for 3 different load currents namely 5, 13 and 21 A at 25 °C. Fig. 13(b) shows the corresponding gate current characteristics of the SiC MOSFET during turn-ON. These characteristics are repeated at 125 °C as can be seen in Figs. 14(a) and 14(b) where the turn-ON  $I_{DS}$  and  $I_G$

Fig. 13. (a) The measured  $I_{DS}$  turn-ON current transients for different load currents in the 1.2 kV/42 A SiC MOSFET at 25 °C, (b) The measured  $I_{CS}$  turn-ON current transients for different load currents in the 1.2 kV/42 A SiC MOSFET at 25 °C

Fig. 14. (a) The measured  $I_{DS}$  turn-ON current transients for different load currents in the 1.2 kV/42 A SiC MOSFET at 125 °C, (b) The measured  $I_{GS}$  turn-ON current transients for different load currents in the 1.2 kV/42 A SiC MOSFET at 125 °C

transients are shown at a higher temperature. It can be seen from Fig. 13 and Fig. 14 that the instantaneous switching rate of  $I_{DS}$  is independent of the load current while the gate current plateau is inversely proportional to the load current. Since the gate current plateau occurs at the time instant that  $I_{DS}$  reaches the load current, then for the same switching rate, the gate current plateau will increase with decreasing load current. This is due to the fact that the transition point of the gate current from the  $C_{GS} + C_{GD-HV}$  (high Miller capacitance) charging phase to the  $C_{GS} + C_{GD-LV}$  (low Miller capacitance) charging phase occurs after the full load current has been reached.

In the case of the gate current plateau, if the load current is known, the junction temperature can be deduced from the plateau value, especially when a high  $R_G^{EXT}$  is used as shown by the results in Fig. 13(b) and Fig. 14(b). If the load current is changing, using the gate current plateau as a TSEP will require separating the effect of the load current change from the effect of the junction temperature. As can be seen in Fig 13(b) and Fig 14(b), it is possible to measure the same gate current plateau at 2 different junction temperatures and load currents. For example, a gate current plateau of 30 mA results from a load current of 21 A at 125 °C while the same gate current plateau also results from a load current of 13 A and a junction temperature of 25 °C.

The gate current plateau ( $I_{GP}$ ) can be calculated from the gate current characteristics shown in Fig. 3(a) at the time instant when the gate current transits from the gate-source capacitance charging component to the Miller capacitance charging component and it can be expressed as

$$I_{GP} = \frac{C_{GS}}{(C_{GS} + C_{GD-HV})} \cdot \frac{V_{GG}}{(R_G^{INT} + R_G^{EXT})} \cdot \frac{V_{GG}}{(R_G^{INT} + R_G^{EXT})(C_{GS} + C_{GD-HV})}$$

(16)

where  $t_1$  is the time when  $V_{GS}$  becomes equal to  $V_{GP}$ . The time  $t_1-t_0$  can be expressed as the sum of the current rise time and the time it takes for  $V_{GS}$  to reach  $V_{TH}$ .

$$t_1 - t_0 = t_{rise} + (t_{TH} - t_0) = \frac{I}{\left(\frac{dI_{DS}}{dt}\right)} + (t_{TH} - t_0)$$

(17)

where the current rise time is given by the ratio of the current to the switching rate. Hence,  $I_{GP}$ , according to the equations above, will increase with decreasing load current and increase with junction temperature.

Using the switching rate as a TSEP requires the ability to measure high  $dI_{DS}/dt$ . Recent power modules include current sensors embedded, hence, the evaluation **of** these sensors for measuring temperatures in SiC power MOSFETs could be the next step. In addition, intelligent gate drivers with closed loop control and dI/dt feedback and control have been presented and evaluated for IGBTs. Here, the voltage across the parasitic inductance of the power module is used for measuring the switching rate [38, 39] thus requiring an auxiliary emitter connection. Recent advances in current sensors like Rogowski coils with high dI/dt detection [40] or magnetoresisitive

current sensors [41] suggest that the identification of the temperature by means of the switching rate can be feasible.

The ability to change the gate drive resistance during operation [42], by using an intelligent programmable gate driver [43, 44], could also enable this technique of junction temperature sensing without suffering the penalty of increased switching losses. The devices will be driven at high switching rates (using reduced gate drive resistances) and at the occasional instants when junction temperature sensing becomes necessary, a higher gate resistance is used momentarily for monitoring the temperature dependent switching parameters. Hence, the device switching rate will only be slowed down when junction temperature sensing is required, which will be occasional. Slowing down the switching transients for improving the sensitivity of a TSEP can have impact in the operation of a converter, if the temperature is to be estimated online. Slowing down the turn-OFF transient can improve the temperature sensitivity of the turn OFF delay of IGBTs and MOSFETs, as it was shown in Figs. 1(d) and 1(e), but it could affect the operation of the converter in the case that fixed dead times are implemented. In the case of slowing down the turn-ON for enabling the junction temperature measurement, if the turn-OFF of the transistor is done at the nominal switching rate, the use of fixed dead times would not be affected.

### IV. CONCLUSION

The junction temperature of SiC power MOSFETs can be measured for on-line condition monitoring using the turn-ON current switching rate  $(dI_{DS}/dt)$  and the gate current transient. The turn-ON  $dI_{DS}/dt$  and the gate current plateau both linearly increase with temperature. Using device mathematical models, it has been demonstrated that the negative temperature coefficient of the threshold voltage and the temperature invariance of the channel mobility is the reason behind the positive temperature coefficient of  $dI_{DS}/dt$  in SiC MOSFETs. In silicon MOSFETs, the negative temperature coefficient of threshold voltage is balanced by the negative temperature coefficient of the channel mobility, hence,  $dI_{DS}/dt$  is temperature invariant. However, the temperature sensitivity of  $dI_{DS}/dt$  and  $I_{GP}$  is reduced by high speed switching due to the presence of parasitic inductance. The source parasitic inductance has the effect of slowing the device down and reducing the temperature sensitivity of the turn-ON  $dI_{DS}/dt$ . Dynamic models have been presented which correctly predict how the parasitic inductance limits the temperature sensitivity of  $dI_{DS}/dt$ . The switching rate increases with the DC link supply voltage and it will require an initial calibration to be used as a TSEP, however the temperature sensitivity is approximately the same for the DC link voltages evaluated. In the case of the gate current plateau, it depends on both temperature and load current, hence it needs decoupling. For both TSEPs, reducing the switching rate improves the temperature sensitivity. However to exploit the benefits of SiC power devices, fast switching is recommended for reducing the switching losses although this will be at the expense of effective junction temperature sensing using the TSEPs identified in this paper. Hence, either the device is slowed

down at the expense of higher switching losses or intelligent gate drivers with the capability of variable gate drive impedance are used. These have been demonstrated in recent research, together with fast sensors for  $dI_{DS}/dt$  control. In this case, the device would be slowed down occasionally to measure the junction temperature whenever the information is needed.

#### REFERENCES

- [1] S. Yang, D. Xiang, A. Bryant, P. Mawby, L. Ran, and P. Tavner, "Condition monitoring for device reliability in power electronic converters: A review," *IEEE Transactions on Power Electronics*, vol. 25, no. 11, pp. 2734-2752, 2010

- [2] M. Ciappa, "Selected failure mechanisms of modern power modules," Microelectronics Reliability, vol. 42, no. 4–5, pp. 653-667, April, 2002.

- [3] Y. Avenas, L. Dupont, and Z. Khatir, "Temperature measurement of power semiconductor devices by thermo-sensitive electrical parameters; A review," *IEEE Transactions on Power Electronics*, vol. 27, no. 6, pp. 3081-3092, 2012

- [4] H. Chen, V. Pickert, D. J. Atkinson, and L. S. Pritchard, "On-line monitoring of the mosfet device junction temperature by computation of the threshold voltage," in *Power Electronics, Machines and Drives*, PEMD 2006. The 3rd IET International Conference on, 2006, pp. 440-444

- [5] I. Bahun, N. Čobanov, and Ž. Jakopović, "Real-time measurement of IGBT's operating temperature," Automatika – Journal for Control, Measurement, Electronics, Computing and Communications, vol. 52, no. 4, 2011

- [6] M. A. Eleffendi and C. M. Johnson, "Evaluation of on-state voltage  $V_{CE}(ON)$  and threshold voltage  $V_{TH}$  for real-time health monitoring of IGBT power modules," in Power Electronics and Applications (EPE'15 ECCE-Europe), 17th European Conference on, 2015, pp. 1-10.

- [7] H. Chen, B. Ji, V. Pickert, and W. Cao, "Real-time temperature estimation for power MOSFETs considering thermal aging effects," *IEEE Transactions on Device and Materials Reliability*, vol. 14, no. 1, pp. 220-228, 2014.

- [8] P. Ghimire, A. R. d. Vega, S. Beczkowski, S. Munk-Nielsen, B. Rannested, and P. B. Thogersen, "An online V<sub>CE</sub> measurement and temperature estimation method for high power IGBT module in normal PWM operation," in *International Power Electronics Conference (IPEC-Hiroshima 2014 ECCE ASIA)*, 2014, pp. 2850-2855.

- [9] A. Amoiridis, A. Anurag, P. Ghimire, S. Munk-Nielsen, and N. Baker, "V<sub>CE</sub>-based chip temperature estimation methods for high power IGBT modules during power cycling; A comparison," in *Power Electronics* and Applications (EPE'15 ECCE-Europe), 2015 17th European Conference on, 2015, pp. 1-9.

- [10] X. Perpiña, J. F. Serviere, J. Saiz, D. Barlini, M. Mermet-Guyennet, and J. Millán, "Temperature measurement on series resistance and devices in power packs based on on-state voltage drop monitoring at high current," *Microelectronics Reliability*, vol. 46, no. 9, pp. 1834-1839, 2006.

[11] B. Ji, X. Song, W. Cao, V. Pickert, Y. Hu, J. W. Mackersie, and G.

- [11] B. Ji, X. Song, W. Cao, V. Pickert, Y. Hu, J. W. Mackersie, and G. Pierce, "In situ diagnostics and prognostics of solder fatigue in IGBT modules for electric vehicle drives," IEEE Transactions on Power Electronics, vol. 30, no. 3, pp. 1535-1543, 2015.

- [12] V. K. Sundaramoorthy, E. Bianda, R. Bloch, D. Angelosante, I. Nistor, G. J. Riedel, F. Zurfluh, G. Knapp, and A. Heinemann, "A study on IGBT junction temperature (*T<sub>J</sub>*) online estimation using gate-emitter voltage (*V<sub>GE</sub>*) at turn-off," *Microelectronics Reliability*, vol. 54, no. 11, pp. 2423-2431, 2014.

- [13] A. Bryant, S. Yang, P. Mawby, D. Xiang, L. Ran, P. Tavner, and P. R. Palmer, "Investigation into IGBT dV/dt during turn-off and its temperature dependence," *IEEE Transactions on Power Electronics*, vol. 26, no. 10, pp. 3019-3031, 2011.

- [14] B. Callanan. (2011). Application considerations for SiC MOSFETs. Available: <a href="http://www.wolfspeed.com/power/tools-and-support/application-notes/">http://www.wolfspeed.com/power/tools-and-support/application-notes/</a>

- [15] S. Jahdi, O. Alatise, J. A. O. Gonzalez, R. Bonyadi, L. Ran, and P. Mawby, "Temperature and switching rate dependence of crosstalk in Si-IGBT and SiC power modules," IEEE Transactions on Industrial Electronics, vol. 63, no. 2, pp. 849-863, 2016.

- [16] D. Xiang, L. Ran, P. Tavner, S. Yang, A. Bryant, and P. Mawby, "Condition monitoring power module solder fatigue using inverter harmonic identification," *IEEE Transactions on Power Electronics*, vol. 27, no. 1, pp. 235-247, 2012.

- [17] H. Niu, and R. D. Lorenz, "Sensing power MOSFET junction temperature using gate drive turn-on current transient properties," *IEEE Transactions on Industry Applications*, vol. 52, no. 2, pp. 1677-1687, 2016

- [18] N. Baker, S. Munk-Nielsen, F. Iannuzzo, and M. Liserre, "IGBT junction temperature measurement via peak gate current," *IEEE Transactions on Power Electronics*, vol. 31, no. 5, pp. 3784-3793, 2016.

- [19] D. Barlini, M. Ciappa, M. Mermet-Guyennet, and W. Fichtner, "Measurement of the transient junction temperature in MOSFET devices under operating conditions," *Microelectronics Reliability*, vol. 47, no. 9– 11, pp. 1707-1712, September, 2007.

- [20] C. DiMarino, "High Temperature Characterization and Analysis of Silicon Carbide (SiC) Power Semiconductor Transistors," Master of Science in Electrical Engineering, Virginia Polytechnic Institute and State University, 2014.

- [21] S. Jahdi, O. Alatise, P. Alexakis, L. Ran, and P. Mawby, "The impact of temperature and switching rate on the dynamic characteristics of silicon carbide Schottky barrier diodes and MOSFETs," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 1, pp. 163-171, 2015.

- [22] J. Ortiz Gonzalez, O. Alatise, J. Hu, L. Ran, and P. Mawby, "Temperature sensitive electrical parameters for condition monitoring in SiC power MOSFETs," presented at the 8th IET International Conference in Power Electronics, Machines and Drives, Glasgow, 2016.

- [23] J. Millán, P. Godignon, Xavier Perpiñà, Amador Pérez-Tomás, and J. Rebollo, "A survey of wide bandgap power semiconductor devices," IEEE Transactions on Power Electronics, vol. 29, no. 5, pp. 2155-2163, 2014.

- [24] G. Wang, J. Mookken, J. Rice, and M. Schupbach, "Dynamic and static behavior of packaged silicon carbide MOSFETs in paralleled applications," in *IEEE Applied Power Electronics Conference and Exposition APEC 2014*, 2014, pp. 1478-1483.

[25] H. Luo, W. Li, and X. He, "Online high-power P-i-N diode chip

- [25] H. Luo, W. Li, and X. He, "Online high-power P-i-N diode chip temperature extraction and prediction method with maximum recovery current di/dt," *IEEE Transactions on Power Electronics*, vol. 30, no. 5, pp. 2395-2404, 2015.

- [26] B. J. Baliga, Fundamentals of Power Semiconductor Devices, Springer, 2008.

- [27] A. D. Pathak. (2001). MOSFET/IGBT drivers theory and applications. Available: <a href="http://www.ixys.com/documents/appnotes/ixan0010.pdf">http://www.ixys.com/documents/appnotes/ixan0010.pdf</a>

- [28] A. Wintrich, U. Nicolai, W. Tursky, and T. Reimann, Application Manual Power Semiconductors 2nd ed.: SEMIKRON International GmbH, 2015.

- [29] C. DiMarino, Z. Chen, M. Danilovic, D. Boroyevich, R. Burgos, and P. Mattavelli, "High-temperature characterization and comparison of 1.2 kV SiC power MOSFETs," in *IEEE Energy Conversion Congress and Exposition ECCE*, 2013, pp. 3235-3242.

- [30] Z. Zhang, F. Wang, L. M. Tolbert, and B. J. Blalock, "Active gate driver for crosstalk suppression of SiC devices in a phase-leg configuration," *IEEE Transactions on Power Electronics*, vol. 29, no. 4, pp. 1986-1997, 2014

- [31] Z. Chen, Y. Yao, M. Danilovic, and D. Boroyevich, "Performance evaluation of SiC power MOSFETs for high-temperature applications," in *Power Electronics and Motion Control Conference (EPE/PEMC)*, 2012 15th International, 2012.

- [32] I. M. Filanovsky, and A. Allam, "Mutual compensation of mobility and threshold voltage temperature effects with applications in CMOS circuits," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 48, no. 7, pp. 876-884, 2001.

- [33] M. Hasanuzzaman, S. K. Islam, L. M. Tolbert, and M. T. Alam, "Temperature dependency of MOSFET device characteristics in 4H- and 6H-silicon carbide (SiC)," *Solid-State Electronics*, vol. 48, no. 10–11, pp. 1877-1881, October, 2004.

- [34] J. Wang, H. S. h. Chung, and R. T. h. Li, "Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance," *IEEE Transactions on Power Electronics*, vol. 28, no. 1, pp. 573-590, 2013.

- [35] A. Elbanhawy. (2008). Effect of source inductance on MOSFET rise and fall times. Available: <a href="http://www.maplesoft.com/applications/view.aspx?SID=5730">http://www.maplesoft.com/applications/view.aspx?SID=5730</a>

- [36] H. Luo, Y. Chen, P. Sun, W. Li, and X. He, "Junction temperature extraction approach with turn-off delay time for high-voltage high-

- power IGBT modules," *IEEE Transactions on Power Electronics*, vol. 31, no. 7, pp. 5122-5132, 2016

- [37] B. J. Baliga, "Chapter 9 IGBT Applications: Transportation," in *The IGBT Device*, William Andrew Publishing, 2015, pp. 223-275.

- [38] Z. Wang, X. Shi, L. M. Tolbert, F. Wang, and B. J. Blalock, "A di/dt feedback-based active gate driver for smart switching and fast overcurrent protection of IGBT modules," IEEE Transactions on Power Electronics, vol. 29, no. 7, pp. 3720-3732, 2014.

- [39] Y. Lobsiger, and J. W. Kolar, "Closed-Loop di/dt and dv/dt IGBT Gate Driver," IEEE Transactions on Power Electronics, vol. 30, no. 6, pp. 3402-3417, 2015.

- [40] A. Ahmed, L. Coulbeck, A. Castellazzi, and C. M. Johnson, "Design and test of a PCB Rogowski coil for very high dI/dt detection," in Power Electronics and Motion Control Conference (EPE/PEMC), 2012 15th International, 2012.

- [41] R. Slatter, M. Brusius, and H. Knoll, "Magnetoresistive current sensors as an enabling technology for ultra-high power density electric drives," presented at the 9th International Conference on Integrated Power Electronics Systems, 2016.

- [42] Andreas Volke and M. Hornkamp, IGBT modules. Technologies, driver and application, Second ed.: Infineon Technologies AG, 2012.

- [43] K. Miyazaki, S. Abe, M. Tsukuda, I. Omura, K. Wada, M. Takamiya, et al., "General-purpose clocked gate driver (CGD) IC with programmable 63-level drivability to reduce Ic overshoot and switching loss of various power transistors," in *IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2016, pp. 1640-1645.

- [44] A. Shorten, W. T. Ng, M. Sasaki, T. Kawashima, and H. Nishio, "A segmented gate driver IC for the reduction of IGBT collector current over-shoot at turn-on," in 2013 25th International Symposium on Power Semiconductor Devices & IC's (ISPSD), 2013, pp. 73-76.

Jose Ortiz Gonzalez (S'15) received a degree in electrical engineering in 2009 from the University of Vigo, Vigo, Spain. From 2010 to 2012, he was a Support Technician in the Department of Electronics Technology, University of Vigo. Since 2013, he has been with the School of Engineering, University of Warwick, Coventry, U.K., as Power Electronics Research Assistant while working towards the Ph.D. degree in power electronics. His current research

interests include condition monitoring, reliability, circuits and device evaluation.

Olayiwola Alatise received the BEng degree (first-class Hons.) in electronic engineering and the PhD degree in Microelectronics and Semiconductors from Newcastle University, U.K., in 2005 and 2008. In June 2008, he joined NXP where he designed, processed and qualified discrete power trench MOSFETs for automotive applications and switched-mode power supplies. In November 2010, he became a Science City Research Fellow at the University of Warwick,

UK, where he has been serving as Associate Professor of Electrical Engineering since August 2012. His research interests include investigating advanced power semiconductor materials and devices for improved energy conversion efficiency.

**Ji Hu** received the B.Sc. degree in electronic and electrical engineering from Northumbria University, Newcastle upon Tyne, U.K., in 2011. He received the M.Sc. degree in energy and power electronics and the PhD degree in power electronics from the University of Warwick, U.K. in 2013 and 2016. His research interest is on the reliability and robustness of high voltage SiC power devices and finite element device simulations.

Li Ran (M'98–SM'07) received the Ph.D. degree in power systems engineering from Chongqing University, Chongqing, China, in 1989. He was a Research Associate with the Universities of Aberdeen, Nottingham, and Heriot-Watt, at Aberdeen, Nottingham, and Edinburgh in the UK, respectively. He became a Lecturer in power electronics with Northumbria University, Newcastle upon Tyne, U.K., in 1999 and was seconded to Alstom Power Conversion, Kidsgrove, U.K., in 2001. Between 2003 and 2012, he was with Durham University, Durham, U.K. He

joined the University of Warwick, Coventry, U.K., as a Professor in power electronics - systems in 2012. His research interests include the application of power electronics for electric power generation, delivery and utilization.

Philip A. Mawby (S'85–M'86–SM'01) received the B.Sc. and Ph.D. degrees in electronic and electrical engineering from the University of Leeds, Leeds, U.K., in 1983 and 1987, respectively. His Ph.D. degree was focused on GaAs/AlGaAs heterojunction bipolar transistors for high-power radio frequency applications at the GEC Hirst Research Centre, Wembley, U.K. In 2005, he joined the University of Warwick, Coventry, U.K., as the Chair of power electronics. He was also

with the University of Wales, Swansea, U.K., for 19 years and held the Royal Academy of Engineering Chair for power electronics, where he established the Power Electronics Design Center. He has been internationally recognized in the area of power electronics and power device research. He was also involved in the development of device simulation algorithms, as well as optoelectronic and quantum-based device structures. He has authored or coauthored more than 100 journal and conference papers. His current research interests include materials for new power devices, modeling of power devices and circuits. Professor Mawby has been involved in many international conference committees, including the ISPSD, EPE, and the ESSDERC. He is a Chartered Engineer, a Fellow of the IET, and a Fellow of the Institute Physics. He is a Distinguished Lecturer for the IEEE Electron Devices Society.