A Modular IGBT Based Current Flow Controller for Multi-terminal HVDC Grids

Hatem Yassin Mohamed Elhady Diab

A thesis submitted in partial fulfilment of the requirement of Staffordshire University for the degree of Doctor of Philosophy

August 2016

### Acknowledgments

First of all, I am grateful to the Almighty God for establishing me to complete this thesis.

I would like to deeply thank my principle supervisor Professor Sarath Tennakoon for his valuable advice, excellent guidance and effective support. Also Dr Chris Gould my second supervisor is much thanked.

Special thanks to Professor Mostafa Marei, the external supervisor for his endless efforts and support throughout the project duration, his guidance is effectively reflected on the quality of the work produced.

I would like to acknowledge faculty staff members Dr. Soliman, Professor Claude, Professor Mansour and my colleagues Hesham, Hussein, Soheil, Samir and Monday for all their support.

My sincere thanks to Mr. Graham Preece and Mr. Dave Martin for their continuous technical support and fast response in all laboratories and logistic queries, thanks for doing your work with passion.

I would also like to acknowledge Arab Academy for Science and Technology for funding my PhD project.

I would like to express my gratitude to my lifetime friend, Mahmoud Al Wadie, for all his support and encouragement. I am really lucky to have you as a second brother, always present whenever I need you, I would have never gone that far without you by my side. A heartfelt gratitude goes to engineer Ismail Taha, thank you for being my inspiration and I will never forget your precious advice.

Most importantly, I would like to thank my Family members; my mother, father, my brother Karim, my grandmother, Moshira, Tarek, Salma and Dodo for all the mental and physical support that they gave me, they all made my journey full of many unforgettable moments.

Last but not least, no words can describe how I feel towards my lovely wife Omnia, she gave away everything she had just to give me full support and worked day and night to make me feel comfortable; so I can complete my studies on the highest possible standards. May god bless her and my beloved son Mourad and keep them by my side as long as I live.

#### Abstract

Offshore wind turbines are preferred rather than onshore ones for their numerous advantages, such as land saving, higher wind speeds and higher power generation. However, AC power transmission would fail to deliver the generated power economically over distances longer than 80 kilometres using submarine cables. The more feasible option is to use High Voltage DC (HVDC) power transmission for offshore wind generation. Unlike AC transmission systems that have established power and current flow control methods, DC power transmission systems have only reliable power flow control techniques for point to point systems, which makes it one of the challenges preventing realisation of Multi Terminal HVDC grids (MT-HVDC) as cables may be subjected to higher currents causing overloading and thermal problems. Different HVDC power flow control schemes are suggested by controlling the AC/DC converters such as voltage droop control and voltage margin control. Other methods of power and current flow control based on the connection of new power electronic equipment to the grid have been also proposed.

This thesis presents operation and control of an IGBT based Current Flow Controller (CFC) for MT-HVDC grid applications. The CFC is studied in its preliminary two-port configuration and possible modes of operation and dynamic models are produced. An extended topology is proposed to allow the CFC to be connected to more than two cables at a time. Although the proposed extended CFC topology is simple in construction and gave acceptable results in most case studies, it has shown some drawbacks in certain case studies where controlled currents have significant differences in magnitudes. To resolve this problem, a generalized Modular CFC (MCFC) topology is proposed which allows each current to be controlled independently and overcome the extended topology's drawback. Moreover, a reduced count switch count topology is proposed which reduces the MCFC cost by half in cases of unidirectional current flow control.

All proposed control strategies and topologies are validated using both computer simulation through MATLAB/SIMULINK and PSCAD/EMTDC software packages and experimental validation through Rapid Control Prototyping (RCP) with the aid of Opal RT real time simulator. Studies carried throughout this thesis show that the proposed MCFC may play an important role in current flow control applications in MT-HVDC grids due to its low cost, small footprint and accurate performance.

### Table of Contents

| Acknow                                        | vledgments                                                                                                                                                                                                                                                                                                                                                                                 | I       |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Abstrac                                       | xt                                                                                                                                                                                                                                                                                                                                                                                         | III     |

| Table of                                      | f Contents                                                                                                                                                                                                                                                                                                                                                                                 | V       |

| List of A                                     | Abbreviations                                                                                                                                                                                                                                                                                                                                                                              | X       |

| List of S                                     | Symbols                                                                                                                                                                                                                                                                                                                                                                                    | XI      |

| Chapte                                        | er 1. Introduction                                                                                                                                                                                                                                                                                                                                                                         | 1       |

| 1.1                                           | Background                                                                                                                                                                                                                                                                                                                                                                                 | 2       |

| 1.1                                           | 1.1 Current developments in wind energy                                                                                                                                                                                                                                                                                                                                                    | 3       |

| 1.1                                           | 1.2 Offshore wind energy                                                                                                                                                                                                                                                                                                                                                                   |         |

| 1.2                                           | Research Motivation                                                                                                                                                                                                                                                                                                                                                                        | 6       |

| 1.3                                           | Research Aim and Objectives                                                                                                                                                                                                                                                                                                                                                                | 8       |

| 1.4                                           | Thesis Structure                                                                                                                                                                                                                                                                                                                                                                           | 9       |

| 1.5                                           | Publications                                                                                                                                                                                                                                                                                                                                                                               | 9       |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                            |         |

| Chapte                                        | er 2. Emergence of High Voltage DC and Multi-terminal DC g                                                                                                                                                                                                                                                                                                                                 | grids12 |

| Chapte<br>2.1                                 | er 2. Emergence of High Voltage DC and Multi-terminal DC g                                                                                                                                                                                                                                                                                                                                 | -       |

| -                                             |                                                                                                                                                                                                                                                                                                                                                                                            |         |

| 2.1                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                               |         |

| 2.1<br>2.2                                    | Introduction<br>High Voltage DC Transmission<br>High Voltage DC Converter Stations                                                                                                                                                                                                                                                                                                         |         |

| 2.1<br>2.2<br>2.3                             | Introduction<br>High Voltage DC Transmission<br>High Voltage DC Converter Stations<br>3.1 Line commutated current source converter                                                                                                                                                                                                                                                         |         |

| 2.1<br>2.2<br>2.3<br>2.3<br>2.3               | Introduction<br>High Voltage DC Transmission<br>High Voltage DC Converter Stations<br>3.1 Line commutated current source converter                                                                                                                                                                                                                                                         |         |

| 2.1<br>2.2<br>2.3<br>2.3<br>2.3<br>2.3<br>2.3 | Introduction       Introduction         High Voltage DC Transmission       Introduction         High Voltage DC Converter Stations       Introduction         3.1       Line commutated current source converter         3.2       Self-commutated voltage source converter                                                                                                                |         |

| 2.1<br>2.2<br>2.3<br>2.3<br>2.3<br>2.3        | Introduction                                                                                                                                                                                                                                                                                                                                                                               |         |

| 2.1<br>2.2<br>2.3<br>2.3<br>2.3<br>2.3        | Introduction         High Voltage DC Transmission         High Voltage DC Converter Stations         3.1       Line commutated current source converter         3.2       Self-commutated voltage source converter         3.3       Multi-level converter topologies         2.3.3.1       Diode clamped multilevel converter                                                             |         |

| 2.1<br>2.2<br>2.3<br>2.3<br>2.3<br>2.3        | Introduction         High Voltage DC Transmission         High Voltage DC Converter Stations         3.1       Line commutated current source converter         3.2       Self-commutated voltage source converter         3.3       Multi-level converter topologies         2.3.3.1       Diode clamped multilevel converter         2.3.3.2       Flying capacitor multilevel converter |         |

| 2.1<br>2.2<br>2.3<br>2.3<br>2.3<br>2.3        | IntroductionHigh Voltage DC TransmissionHigh Voltage DC Converter Stations3.1Line commutated current source converter3.2Self-commutated voltage source converter3.3Multi-level converter topologies2.3.3.1Diode clamped multilevel converter2.3.3.2Flying capacitor multilevel converter2.3.3.3H-bridge cascaded multilevel converter                                                      |         |

| 2.                                                              | 3.4 A                                                                         | AC/DC converters summary                                                                                                                                                                                                      |                                                                |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 2.4                                                             | HVD                                                                           | C Transmission System Configurations                                                                                                                                                                                          | 29                                                             |

| 2.                                                              | 4.1 F                                                                         | Point to point connections                                                                                                                                                                                                    | 29                                                             |

|                                                                 | 2.4.1.1                                                                       | Monopolar connections                                                                                                                                                                                                         | 29                                                             |

|                                                                 | 2.4.1.2                                                                       | Bipolar connections                                                                                                                                                                                                           |                                                                |

|                                                                 | 2.4.1.3                                                                       | Back to back connections                                                                                                                                                                                                      | 31                                                             |

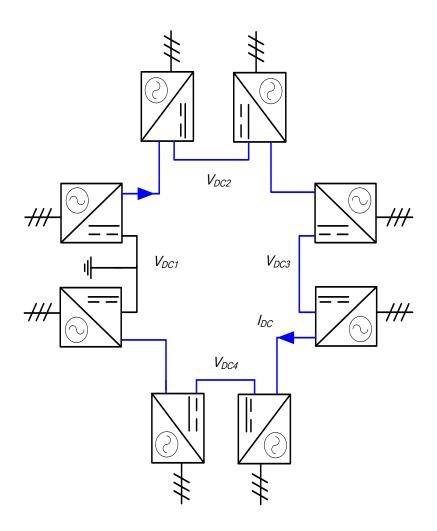

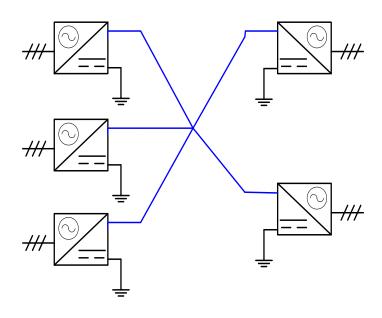

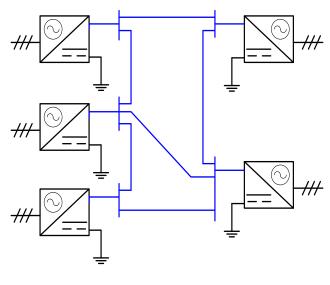

| 2.                                                              | 4.2 N                                                                         | Aulti-terminal connections                                                                                                                                                                                                    | 32                                                             |

|                                                                 | 2.4.2.1                                                                       | Series connections                                                                                                                                                                                                            | 32                                                             |

|                                                                 | 2.4.2.2                                                                       | Parallel connections                                                                                                                                                                                                          | 33                                                             |

| 2.5                                                             | Chall                                                                         | enges for the Realisation of MTDC grids                                                                                                                                                                                       | 35                                                             |

| 2.                                                              | 5.1 I                                                                         | DC Fault Currents                                                                                                                                                                                                             | 35                                                             |

| 2.                                                              | 5.2 A                                                                         | Absence of DC transformer                                                                                                                                                                                                     | 37                                                             |

| 2.                                                              | 5.3 F                                                                         | Power flow control                                                                                                                                                                                                            |                                                                |

| 2.6                                                             | Summ                                                                          | nary                                                                                                                                                                                                                          | 39                                                             |

|                                                                 | • ~                                                                           |                                                                                                                                                                                                                               |                                                                |

| Cnapt                                                           | er 3. Cu                                                                      | Irrent and Power Flow Control in DC grids                                                                                                                                                                                     | 40                                                             |

| •                                                               |                                                                               |                                                                                                                                                                                                                               |                                                                |

| 3.1                                                             | Introc                                                                        | luction                                                                                                                                                                                                                       | 41                                                             |

| 3.1<br>3.2                                                      | Introc<br>Volta                                                               | luction<br>ge Margin Control                                                                                                                                                                                                  | 41<br>41                                                       |

| 3.1<br>3.2<br>3.3                                               | Introc<br>Volta<br>Volta                                                      | luction<br>ge Margin Control<br>ge Droop control                                                                                                                                                                              | 41<br>41<br>43                                                 |

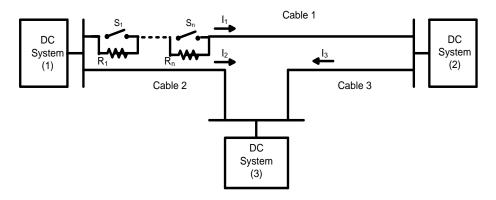

| 3.1<br>3.2<br>3.3<br>3.4                                        | Introc<br>Volta<br>Volta<br>Curre                                             | luction<br>ge Margin Control<br>ge Droop control<br>nt control using series resistors                                                                                                                                         | 41<br>41<br>43<br>45                                           |

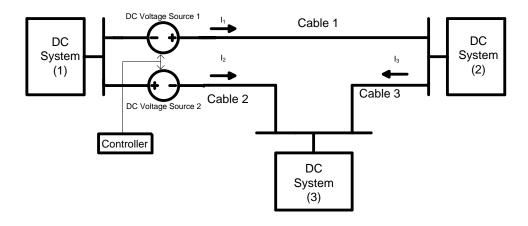

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                 | Introc<br>Volta<br>Volta<br>Curre<br>Curre                                    | luction<br>ge Margin Control<br>ge Droop control<br>nt control using series resistors<br>nt control by injection of series voltage                                                                                            | 41<br>41<br>43<br>45<br>46                                     |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.                           | Introc<br>Volta<br>Volta<br>Curre<br>Curre<br>5.1 C                           | luction<br>ge Margin Control<br>ge Droop control<br>nt control using series resistors<br>nt control by injection of series voltage<br>Controlled series voltage sources                                                       | 41<br>43<br>45<br>46<br>46                                     |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.<br>3.<br>3.               | Introc<br>Volta<br>Volta<br>Curre<br>5.1 C<br>5.2 S                           | luction<br>ge Margin Control<br>ge Droop control<br>nt control using series resistors<br>nt control by injection of series voltage<br>Controlled series voltage sources<br>Geries DC/DC converters                            | 41<br>41<br>43<br>45<br>46<br>46<br>46<br>48                   |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.<br>3.<br>3.<br>3.<br>3.   | Introc<br>Volta<br>Volta<br>Curre<br>5.1 C<br>5.2 S<br>5.3 A                  | luction                                                                                                                                                                                                                       | 41<br>41<br>43<br>45<br>46<br>46<br>46<br>48<br>48             |

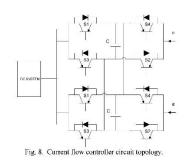

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.<br>3.<br>3.<br>3.6        | Introc<br>Volta<br>Volta<br>Curre<br>5.1 C<br>5.2 S<br>5.3 A<br>The C         | luction<br>ge Margin Control<br>ge Droop control<br>nt control using series resistors<br>nt control by injection of series voltage<br>Controlled series voltage sources<br>Geries DC/DC converters<br>Current flow controller | 41<br>43<br>45<br>46<br>46<br>46<br>48<br>48<br>51             |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.<br>3.<br>3.<br>3.<br>3.   | Introc<br>Volta<br>Volta<br>Curre<br>5.1 C<br>5.2 S<br>5.3 A<br>The C         | luction                                                                                                                                                                                                                       | 41<br>43<br>45<br>46<br>46<br>46<br>48<br>48<br>51             |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.<br>3.<br>3.<br>3.6<br>3.7 | Introc<br>Volta<br>Volta<br>Curre<br>5.1 C<br>5.2 S<br>5.3 A<br>The C<br>Summ | luction<br>ge Margin Control<br>ge Droop control<br>nt control using series resistors<br>nt control by injection of series voltage<br>Controlled series voltage sources<br>Geries DC/DC converters<br>Current flow controller | 41<br>41<br>43<br>45<br>46<br>46<br>46<br>48<br>48<br>51<br>52 |

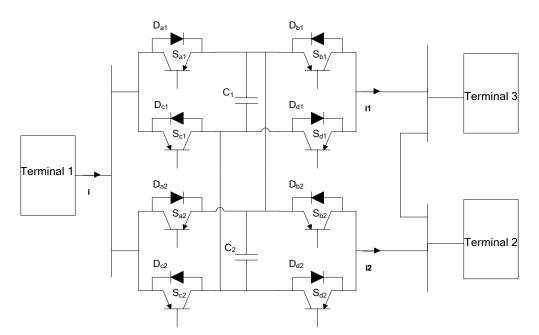

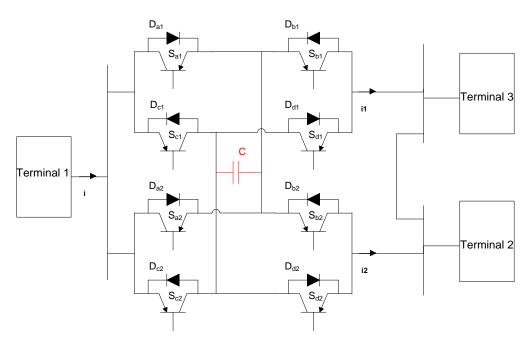

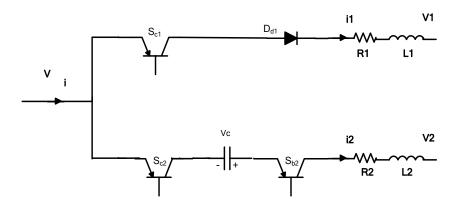

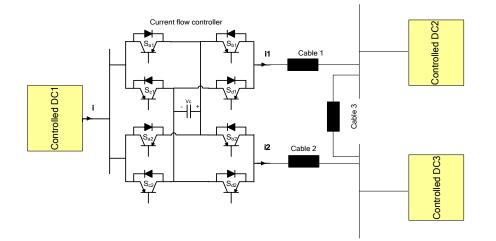

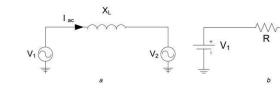

| 4.2 | Top | bology                         | 55 |

|-----|-----|--------------------------------|----|

|     | -   | erating principle              |    |

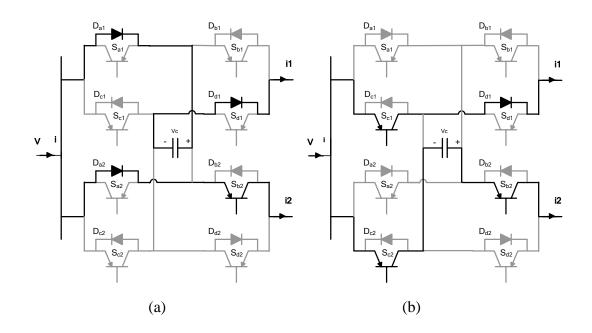

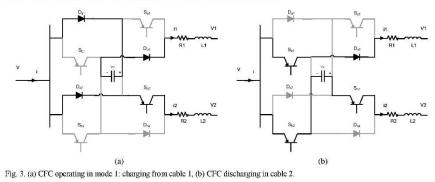

| 4.4 | Мо  | des of operation               | 58 |

| 4.4 | .1  | Operation in forward direction | 59 |

|      | 4.4.1.   | .1 Mode 1: $i_1 > i_2$                  | 59  |

|------|----------|-----------------------------------------|-----|

|      | 4.4.1.   | .2 Mode 2: $i_2 > i_1$                  | 60  |

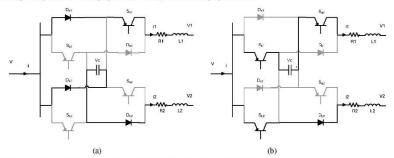

| 4.4  | 4.2      | Operation in reverse direction          | 60  |

|      | 4.4.2.   | .1 Mode 3: $i_1 > i_2$                  | 60  |

|      | 4.4.2.   | 2 Mode 4: $i_2 > i_1$                   | 61  |

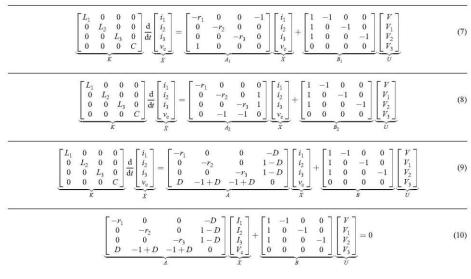

| 4.5  | Dyn      | namic modelling                         | 63  |

| 4.6  | Con      | ntrol Strategies                        | 66  |

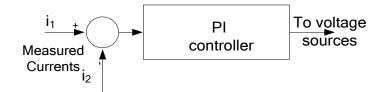

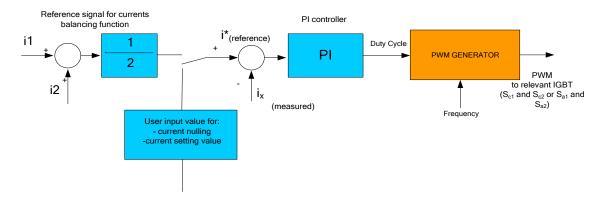

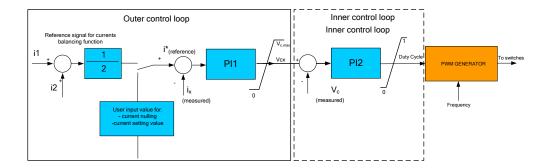

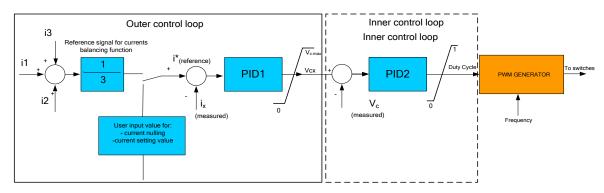

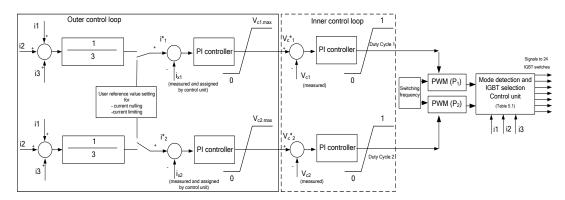

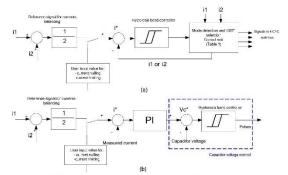

| 4.6  | 6.1      | PI based current control technique      | 66  |

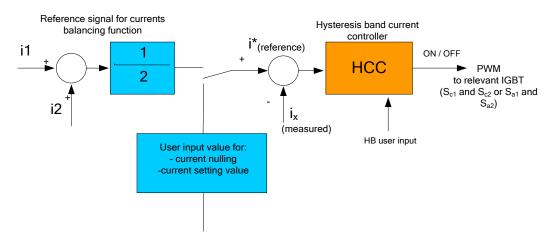

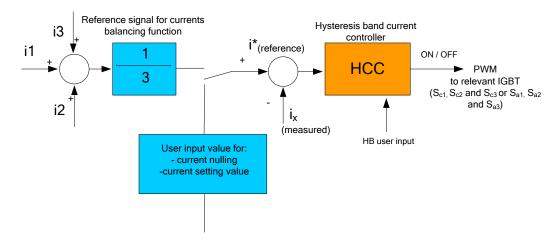

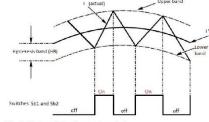

| 4.6  | 6.2      | Hysteresis band current control         | 68  |

| 4.7  | Aut      | omatic mode detection and change unit   | 70  |

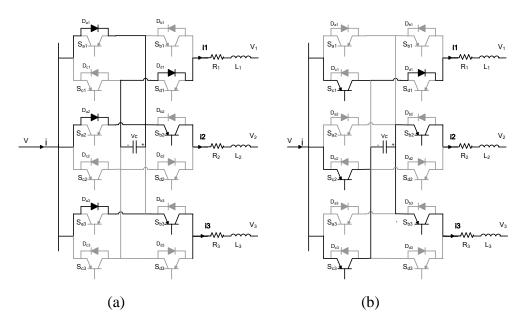

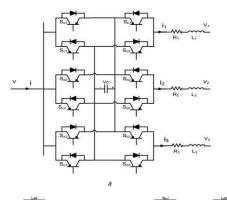

| 4.8  | The      | proposed extended CFC topology          | 72  |

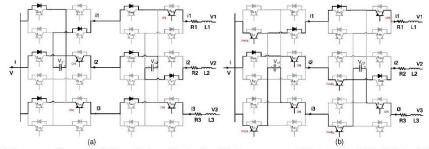

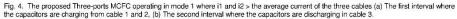

| 4.8  | 8.1      | Modes of operation                      | 73  |

| 4.8  | 8.2      | Dynamic modelling                       | 75  |

| 4.8  | 8.3      | Control strategy                        | 78  |

| 4.9  | Sim      | nulation Results                        | 79  |

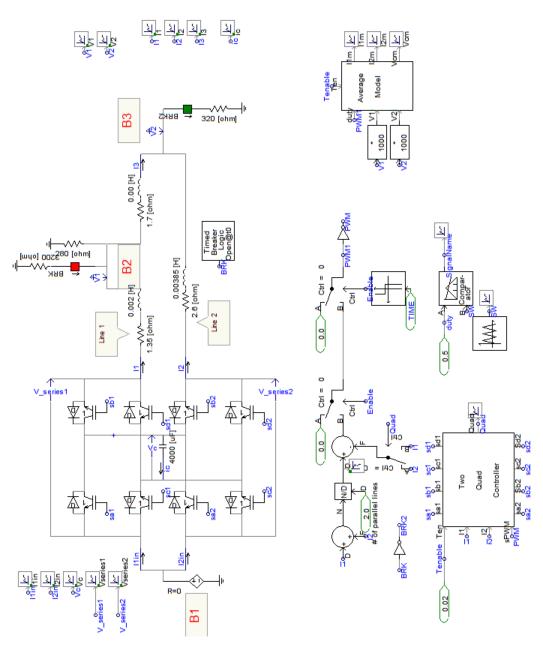

| 4.9  | 9.1      | Two-port CFC                            | 79  |

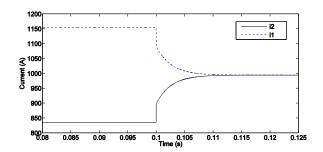

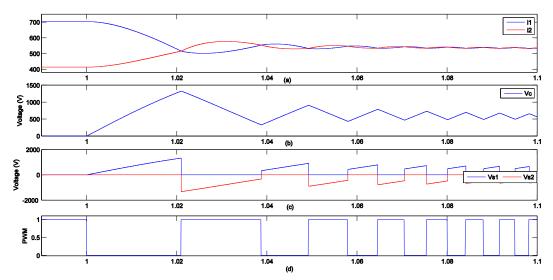

|      | 4.9.1.   | .1 Current balancing using PID control. | 80  |

|      | 4.9.1.   | .2 Current limiting using PID control   | 82  |

|      | 4.9.1.   | .3 Current nulling using PID control    | 83  |

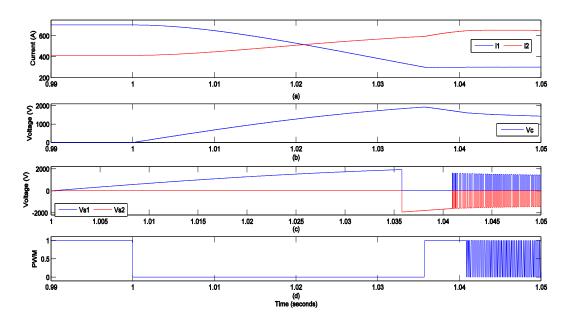

|      | 4.9.1.   | 4 Mode detection and change.            | 84  |

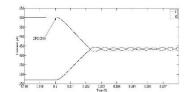

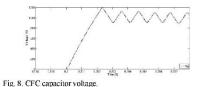

|      | 4.9.1.   | 5 Hysteresis current control            | 86  |

| 4.9  | 9.2      | Extended 3 port CFC                     |     |

|      | 4.9.2.   | 1 Current balancing                     | 90  |

|      | 4.9.2.   | 2 Extended topology limitations         | 92  |

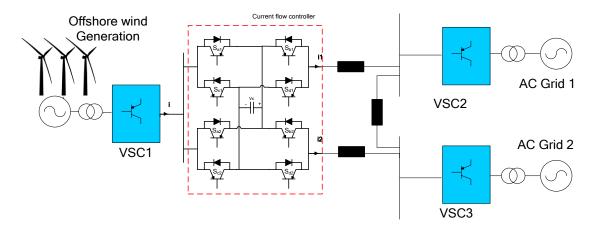

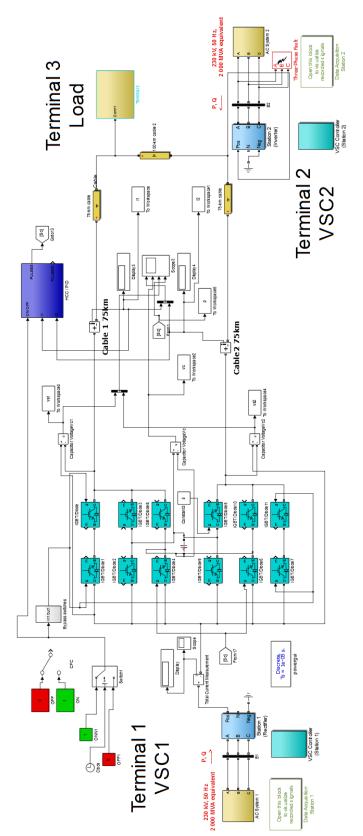

| 4.9  | 9.3      | Testing the CFC in VSC based HVDC grid  | 93  |

|      | 4.9.3.   | .1 Current balancing                    | 95  |

|      | 4.9.3.   | 2 Current limiting                      | 95  |

| 4.9  | 9.4      | Validation of the dynamic model         | 96  |

| 4.10 | S        | ummary                                  | 98  |

|      | <b>-</b> |                                         | 100 |

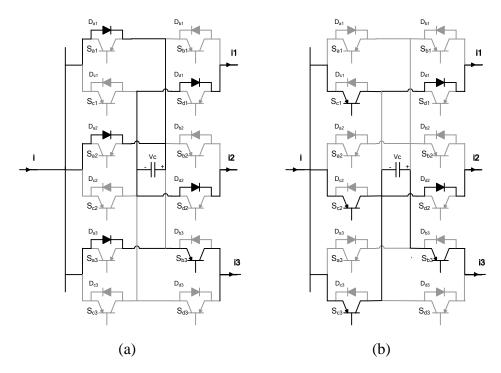

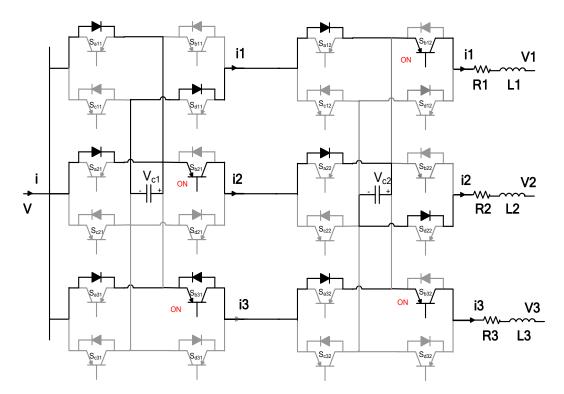

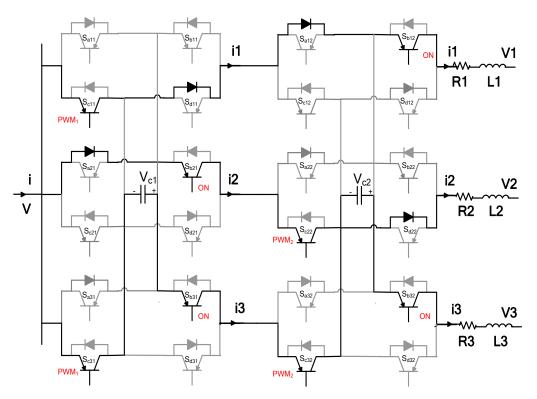

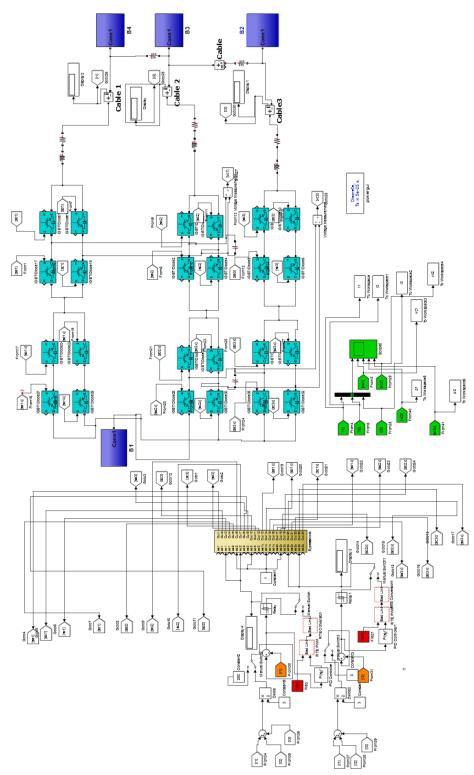

### Chapter 5. The Proposed Generalized Modular Current Flow Controller...100

| 5.1 | Introduction                       | 101 |

|-----|------------------------------------|-----|

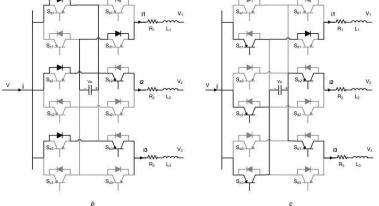

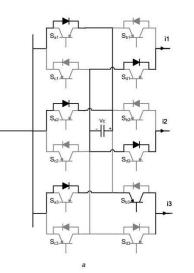

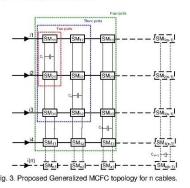

| 5.2 | Proposed Generalized MCFC Topology | 101 |

| 5.3    | Modes     | of Operation                                        |     |

|--------|-----------|-----------------------------------------------------|-----|

| 5.4    | Mathen    | natical Modelling                                   | 106 |

| 5.5    | MCFC      | Control Strategy                                    | 110 |

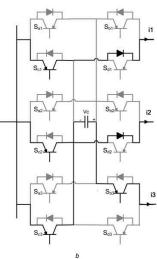

| 5.6    | Propose   | ed Reduced Switches Count Topology                  | 111 |

| 5.7    | Simulat   | tion Results                                        | 113 |

| 5.7    | 7.1 Cu    | rrents balancing: MCFC                              | 114 |

| 5.7    | 7.2 MC    | CFC: setting currents $i_1$ and $i_3$               | 115 |

| 5.7    | 7.3 MC    | CFC: currents nulling                               | 116 |

| 5.8    | Summa     | ry                                                  | 117 |

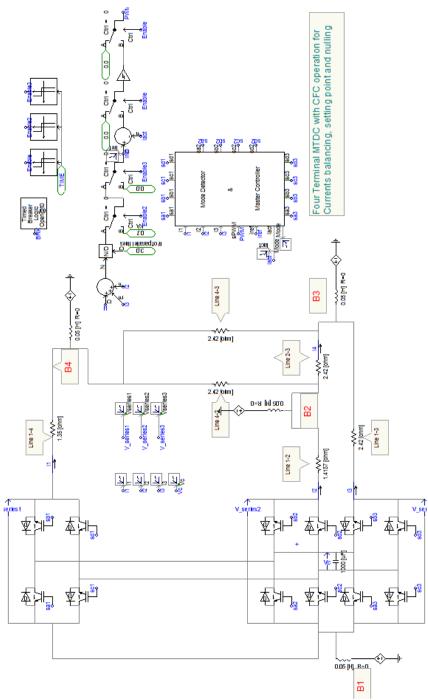

| Chapte | er 6. Exp | erimental Validation                                | 119 |

| 6.1    | Introdu   | ction                                               | 120 |

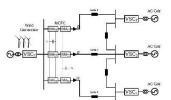

| 6.2    | Experir   | nental System Configuration                         | 120 |

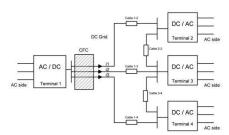

| 6.2    | 2.1 Sca   | aled down MTDC grid                                 |     |

| 6.2    | 2.2 MC    | CFC prototype                                       | 121 |

| 6.2    | 2.3 Co    | ntrollers and user interface                        | 122 |

| 6.3    | Experir   | nental Results                                      |     |

| 6.3    | 3.1 Tw    | vo-port CFC                                         |     |

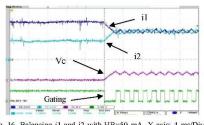

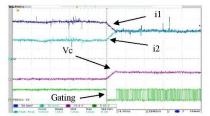

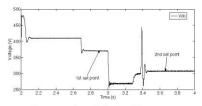

|        | 6.3.1.1   | Current balancing and limiting using PID controller |     |

|        | 6.3.1.2   | Testing of HCC                                      | 127 |

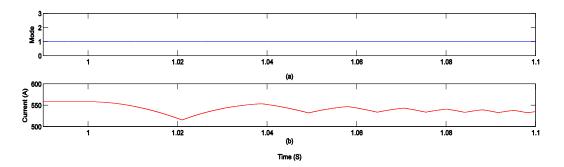

|        | 6.3.1.3   | Mode detection and changing algorithm               |     |

|        | 6.3.1.4   | Effect of varying capacitance                       | 130 |

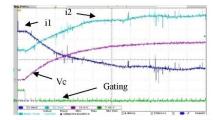

| 6.3    | 3.2 Ex    | tended three-port CFC                               | 131 |

| 6.3    | 3.3 Th    | ree-port MCFC                                       | 132 |

|        | 6.3.3.1   | MCFC current balancing                              | 132 |

|        | 6.3.3.2   | MCFC current setting                                | 133 |

|        | 6.3.3.3   | MCFC current nulling                                | 134 |

| 6.4    | Summa     | ry                                                  | 135 |

| Chapte | er 7. Con | clusions                                            | 136 |

| 7.1    | Conclu    | sions                                               | 137 |

| 7.2    | Summa     | ry of Contributions                                 |     |

| 7.3    |           | mendation for Future Research                       |     |

|        |           |                                                     |     |

| References                                             | 140 |

|--------------------------------------------------------|-----|

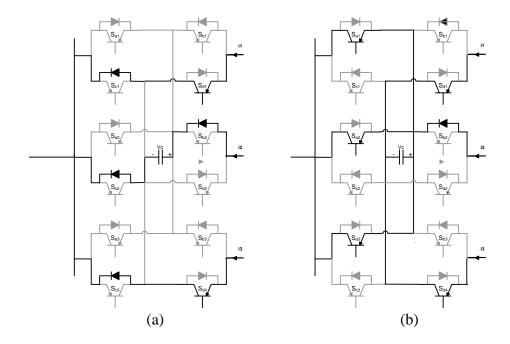

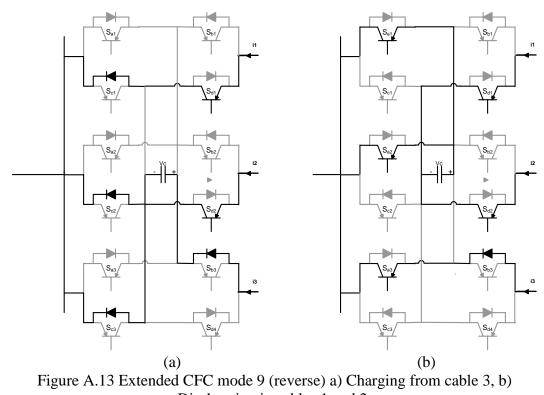

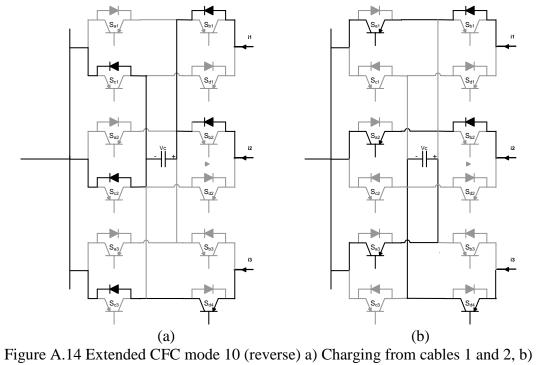

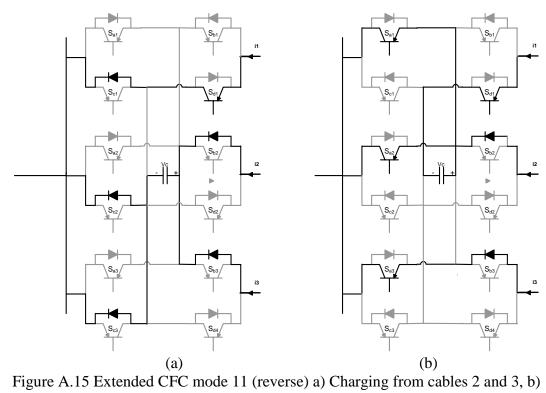

| Appendix A. Current Flow Controller Schematic Diagrams | 155 |

| A.1 Two ports CFC schematics                           | 156 |

| A.2 Three ports CFC (extended topology) schematics     | 158 |

| A.3 Three ports modular CFC schematics                 | 164 |

| A.4 Two Ports CFC Reduced Topology Schematics          | 170 |

| Appendix B. Details of Simulation Models.              | 171 |

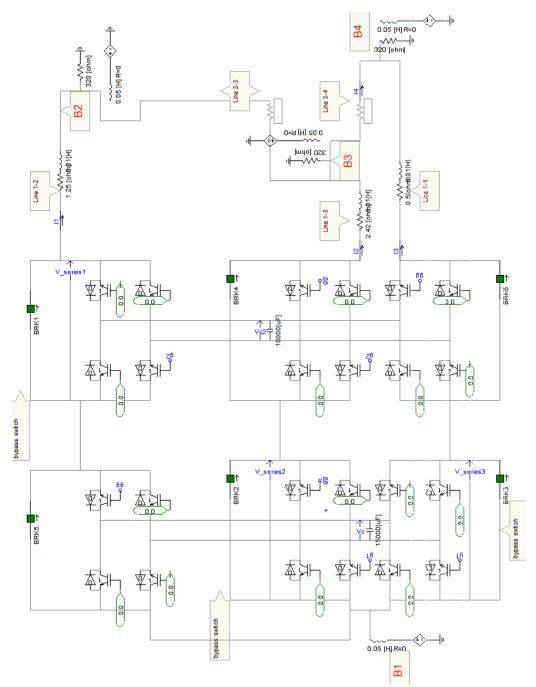

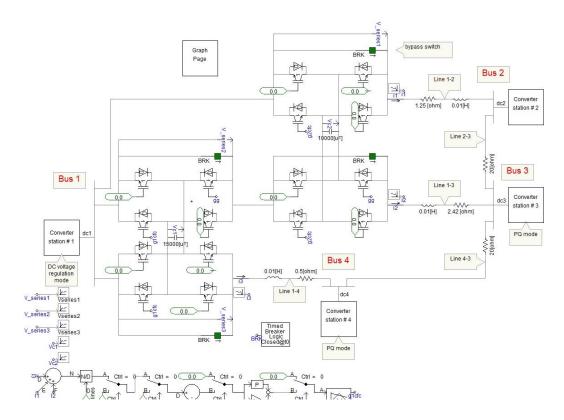

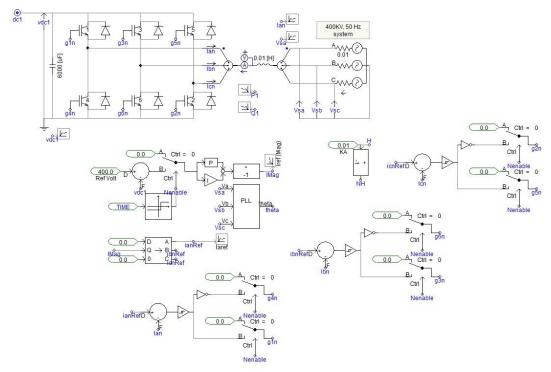

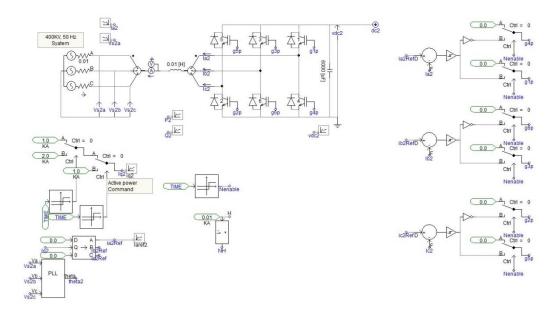

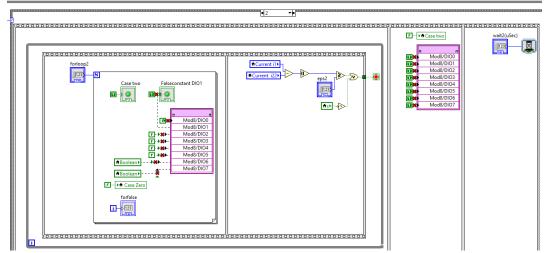

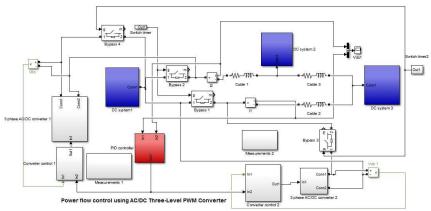

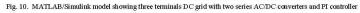

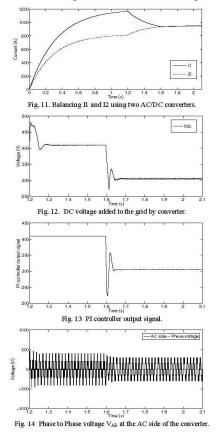

| B.1 MATLAB/SIMULINK Simulation Models                  | 172 |

| B.2 PSCAD/EMDTC Simulation Models                      | 176 |

| Appendix C. Details of Experimental Setup              |     |

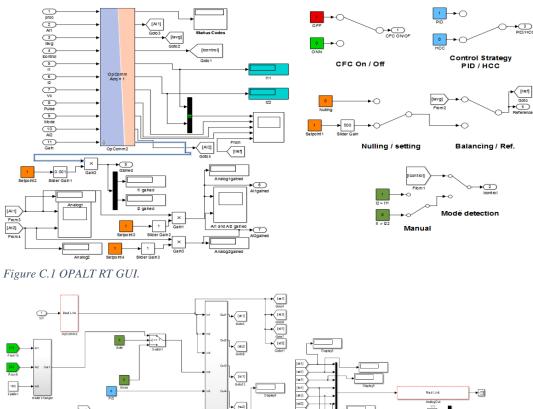

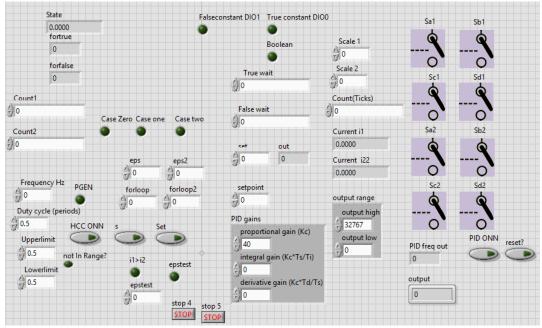

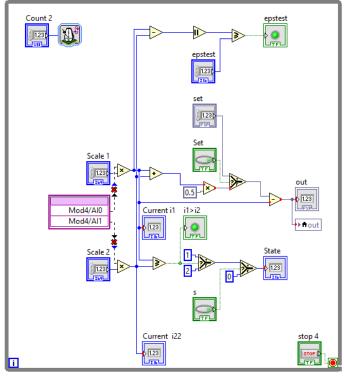

| C.1 OPAL RT Programming Code                           | 184 |

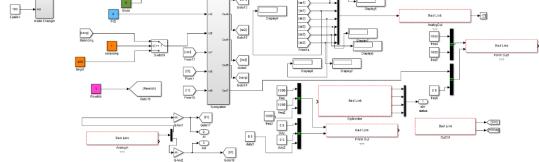

| C.2 LABVIEW Programming Code                           | 185 |

| Appendix D. Selected Publications by the Author        |     |

| Appendix E. Lists of Figures and Tables.               | 224 |

| E.1 List of Figures                                    | 225 |

| E.2 List of Tables                                     | 231 |

### List of Abbreviations

| ANN     | Artificial neural network                         |

|---------|---------------------------------------------------|

| CCC     | Capacitor commutated converter                    |

| CFC     | Current flow controller                           |

| CNC     | Computer numerical control                        |

| CSC     | Current source converter                          |

| FACTS   | Flexible alternating current transmission systems |

| FPGA    | Field programmable gate array                     |

| GTO     | Gate turn off                                     |

| GUI     | Graphical user interface                          |

| HCC     | Hysteresis current control                        |

| HB      | Hysteresis band                                   |

| HVAC    | High voltage AC                                   |

| HVDC    | High voltage direct current                       |

| IGBT    | Insulated gate bipolar transistor                 |

| LCC     | Line commutated converter                         |

| MCFC    | Modular current flow controller                   |

| MMC     | Modular multilevel converter                      |

| MTDC    | Multi terminal direct current                     |

| NI-Crio | National instruments compact rio                  |

| PCB     | Printed circuit board                             |

| PI      | Proportional intergral                            |

| PID     | Proportional integral derivative                  |

| PWM     | Pulse-width modulation                            |

| RCP     | Rapid control prototyping                         |

| SPWM    | Sinusoidal pulse width modulation                 |

| VHDL    | Very high -level design language                  |

| VSC     | Voltage source converter                          |

| WECS    | Wind energy conversion systems                    |

|         | •                                                 |

### List of Symbols

| С                           | Capacitance                                             |

|-----------------------------|---------------------------------------------------------|

| D                           | Diode                                                   |

| е                           | Error signal                                            |

| $f_s$                       | Switching frequency                                     |

| G                           | Neutral point                                           |

| <b>i</b> d                  | d-axis component current                                |

| $i_{dc}$                    | Steady state DC current                                 |

| $i_n$                       | Current flowing in cable n                              |

| L                           | Inductance                                              |

| Р                           | Active power                                            |

| $P^*$                       | Reference active power                                  |

| $P_{loss}$                  | Power loss                                              |

| $P_{max}$                   | Maximum active power                                    |

| $P_{min}$                   | Minimum active power                                    |

| R                           | Cable resistance                                        |

| $t_{off}$                   | Turn off time                                           |

| S                           | Power electronic switch                                 |

| U                           | DC voltage                                              |

| $U^*$                       | Reference DC voltage                                    |

| $U_T$                       | Terminal voltage                                        |

| $V_{a}$ , $V_{b}$ , $V_{c}$ | Three phase voltages                                    |

| $V_c$                       | Capacitor voltage                                       |

| $V_{dc}$                    | Steady state DC voltage                                 |

| $V_o$                       | Output voltage                                          |

| $V_n$                       | Voltage at terminal n                                   |

| X                           | Line impedance                                          |

| 3                           | User defined threshold                                  |

| $\delta$                    | Power angle                                             |

| $\Delta V$                  | Potential difference between sending and receiving ends |

| $\Delta V_{\rm c}$          | Voltage ripple                                          |

| $ ho_{DC}$                  | Droop constant                                          |

## Chapter

1

## Introduction

### 1.1 Background

As more people continue to migrate from rural villages to big cities, the demand for new electrical power installations has increased rapidly in recent years [1]. Conventional fossil fuels such as coal, gas and oil are still the main sources of energy supply for electrical power generation. Although using these types of fuels results in producing the cheapest electricity, their high carbon emissions makes them the main contributor to environmental degradation that is clearly noticed in climate change problems [2]. Additionally, fossil fuels are not renewable and are expected to run out in the future [3]. Nuclear energy is considered to be another highly efficient, reliable and economically competitive energy source for electrical power generation [4]. However, nuclear energy has several political problems and long term environmental concerns, such as the catastrophic events of Ukrainian Chernobyl disaster in 1986 and Fukushima Daiichi nuclear disaster in Japan in 2011[5]. As a result, clean and renewable energy sources such as hydro, wind, solar and biomass became more attractive and several leading countries such as the United States and the United Kingdom have planned to increase the installed capacity of renewable energy resources dramatically over the upcoming few years. Some other countries such as Germany chose to abandon nuclear energy in favour of renewable energy [6].

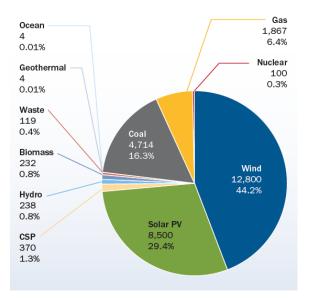

In 2015, 28.9 GW of new power generating capacity was installed in the EU, 2.4 GW more than in 2014. Wind power was the energy technology with the highest installation rate in 2015: 12.8 GW as shown in Figure 1.1, accounting for 44% of all new installations. Solar PV came second with 8.5 GW (29% of 2015 installations) and coal came third with 4.7 GW (16%). Gas installed 1.9 GW (6.4 % of total installations), hydro 238.5 MW (0.8%), biomass 232.4 MW (0.8%), waste 118.5 MW, nuclear 100 MW, geothermal 4.3 MW and ocean 4.1 MW. Peat and fuel oil did not install any capacity in 2015. During 2015, Member States decommissioned 8 GW of coal capacity, 4.3 GW of gas, 3.3 GW of fuel oil, 1.8 GW of nuclear energy capacity, 518 MW of biomass and 281 MW of wind energy [7].

Figure 1.1 Share of new power capacity installations in EU in 2015. Total of 28.9 GW [7].

### 1.1.1 Current developments in wind energy

Wind energy has been utilized since early ages of ancient humans in 5000 BC when boats used wind to sail the river Nile. Also wind mills have converted the kinetic energy of wind into mechanical energy since 200 BC, where it was used for pumping water and grinding in china [8], [9]. In the early 1970s, wind energy started to gain interest for electrical power generation on a small scale as a result of the oil crisis. However, things changed in the 1990s and wind energy emerged as one of the leading sustainable energy resources [10].

Wind power generation gained more attention than other renewable energy resources as it is considered to have a low environmental impact [8], [10], [11]. The reasons can be summarized as follows:

- It offers a low cost alternative for fossil fuels.

- It does not consume any fuel or water and it does not produce any emissions.

- Has good lifetime expectancy of 20–25 years and breaks even its cost in three to six months of generation [7], [12], [13].

- It utilizes less land area per kilowatt-hour of power generation when compared to other resources.

• The wind energy conversion systems (WECS) have experienced a massive technological boost in recent years, increasing its efficiency and reliability.

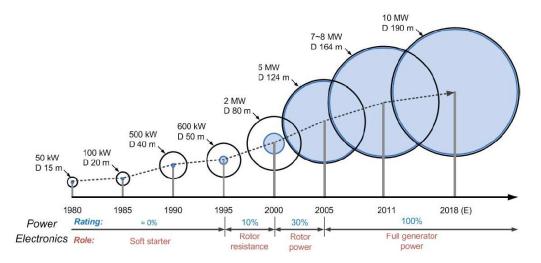

In the 1990s, a single wind turbine was rated at a few kWs; now a single wind turbine can be rated up to 8 MW such as the Vestas V164 turbine introduced in 2014 [14]. Figure 1.2 shows the evolution of wind turbine diameter length and the power electronics from 1980 to 2018 [15].

Figure 1.2 Evolution of wind turbine diameter length and it's power electronics [15].

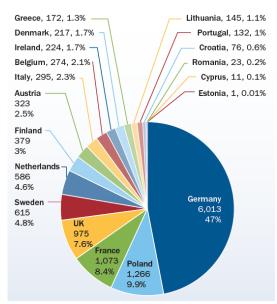

During 2015, 13.8 GW of wind power was installed across Europe, 5.4% more than in the previous year. 12.8 GW of it was in the European Union. Of the capacity installed in the EU, 9.7 GW was onshore and 3 GW was offshore. In 2015, the annual onshore market decreased in the EU by 7.8 %, and offshore installations more than doubled compared to 2014. Overall, EU wind energy annual installations increased by 6.3% compared to 2014 installations. Germany was the largest market in 2015 in terms of annual installations, installing 6 GW of new capacity; 38% of total capacity was installed in Germany. Poland came second with 1.2 GW, more than twice the annual installations in 2014 and one quarter of its national cumulative capacity at the end of 2015. France was third with 1.1 GW and the UK was fourth with 975 MW, 59% of which was offshore (572 MW). Almost half of the new capacity installed in 2015 came from the pioneering markets of Germany and Denmark. This is mainly due to the stability of the regulatory frameworks in these countries, which gives investors visibility on cash flows of future projects and favours investments in wind energy. 47% of all new EU installations in 2015 took place in Germany and 73% occurred in the top four markets, a similar trend to the one seen in 2014. Offshore wind accounted for 24% of total EU wind power installations in 2015, double the share of annual additions in 2014. This confirms the growing relevance of the offshore wind industry in the development of wind energy in the EU [7]. Figure 1.3 shows the EU market shares for new wind energy capacities installed during 2015.

Figure 1.3 EU member state market share of new wind energy capacity installed during 2015 (MW), total 12.8 GW [7].

### **1.1.2 Offshore wind energy**

As the wind technology emerged and the demand for more land use to install new wind farms increased, the idea of forming offshore wind generation platforms evolved [16]. In addition, offshore wind energy projects have one big advantage over the wind energy projects on land, namely more frequent and more powerful wind. Some recent studies have shown that offshore wind blow 40 percent more often than wind on land which means that in the future offshore wind farms can easily outpace

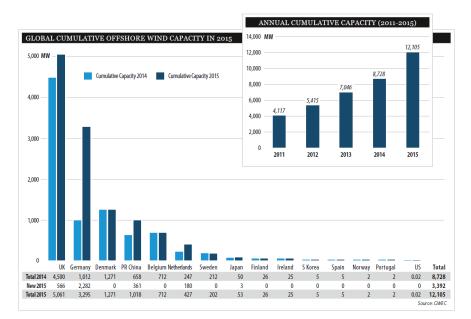

wind projects on land in terms of installed capacity [17]. However, the major disadvantage of offshore wind farms is high construction costs and complex logistics [16]. Structures in offshore wind energy projects need to be strong enough in order to withstand rough weather conditions; the cost of installing an offshore wind turbine was estimated to be double of that onshore per megawatt of capacity in 2010 [18]. Consequently, wind farms need to be large, or otherwise they are not economically viable. Figure 1.4 shows the global cumulative offshore wind capacity, where it can be noted that the United Kingdom is leading the charts by more than 5 GW of installed capacity, followed by Germany, Denmark, China, Belgium, Netherlands and Sweden [19].

Figure 1.4 Global cumulative offshore wind capacity and annual cumulative capacity (2015) [19].

### **1.2 Research Motivation**

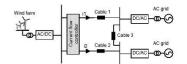

When offshore wind farms are built far into the sea, High Voltage Direct Current (HVDC) is the most viable way to transmit the generated power to shore [20]. However, almost all the available HVDC interconnections are point to point. Data presented in Figure 1.4, indicates that offshore wind energy farms are being installed extensively by European countries in the North Sea area. As a result, industry leaders

and research pioneers proposed the idea of interconnecting such farms with multi terminal HVDC (MT-HVDC) connections and forming the so called "European DC super grid" [21], [22] as shown in Figure 1.5.

Figure 1.5 Proposed European super grid [21].

The collaboration between industry and researchers conducted a joint research group called "friends of the super grid" to work on practically realizing this idea. However, several challenges arose [23], [24] such as the following:

- Absence of reliable DC protection schemes and equipment that are needed to protect the system against Faults.

- The need of DC-DC high voltage transformer, to intertie connections with different voltage levels.

- Absence of power and current flow control methods. The control of the flowing current is important to prevent cables overloading and damage and to achieve dispatch orders.

This research project focuses on contributing to the MT-HVDC concept by offering a solution of precise current flow control in DC grids.

### **1.3 Research Aim and Objectives**

This research studies an IGBT based Modular Current Flow Controller (MCFC) for application in MT-HVDC grids, with the aim of developing a feasible power electronic current control and limiting solution that can be implemented practically to prevent cables overloading and facilitate maintenance. To achieve this aim, the following objectives were set for this investigation:

- To perform a literature review to study AC/DC converter topologies, multi terminal HVDC grid configuration and available power and current flow control methods, especially methods proposed by industry.

- To investigate the available current flow controller (CFC) topology in order to develop all possible operating modes, mathematical model and appropriate control circuits.

- To achieve autonomous operation of the CFC by designing operating mode detection and change control unit, giving it the ability to operate continuously even under sudden load changes.

- To develop a generalized topology to be applied for large MTDC grids and a reduced switch count topology for unidirectional power flow applications.

- To validate all the developed operating modes, control strategies and topologies through both computer simulations and scaled down experimental prototyping.

### 1.4 Thesis Structure

This thesis consists of seven chapters as follows:

- Chapter 1: Introduces the thesis, includes a background on development of wind energy and multi terminal HVDC grids, research motivation and finally research aims and objectives.

- Chapter 2: Discusses current AC/DC converter topologies used in HVDC, MTDC grid configurations and challenges preventing their realisation.

- Chapter 3: Reviews existing current and power flow control methods through either the AC/DC converter control or applying addition equipment to the grid.

- Chapter 4: Presents the proposed current flow controller operating principle, modes of operation, mathematical model, control strategies, extended threeport topology and computer simulation results.

- Chapter 5: Presents the proposed modular generalized topology and reduced switches count topology of the CFC, and their validation through computer simulation.

- Chapter 6: Scaled down laboratory prototype details are demonstrated, and all proposed topologies and control schemes are validated experimentally.

- Chapter 7: Presents general conclusions, summary of contributions and recommendations for future research.

### **1.5 Publications**

Journal papers:

Diab, H.Y., Marei, M.I. and Tennakoon, S.B. "Operation and control of an insulated gate bipolar transistor-based current controlling device for power flow applications in multi-terminal high-voltage direct current grids". *IET Power Electronics*, 9(2), pp.305-315. 2016.

- Diab, H.Y., Marei, M.I., Tennakoon, S.B. and Abdelsalam M. "A Generalized Topology of a Modular Current Flow Controlling Device for Multi-terminal DC Grid Applications" a submitted *IEEE Transaction*.

- Diab, H.Y., Marei, M.I. and Tennakoon, S.B. "A Reduced Switches Count Topology of Current Flow Control Apparatus for MTDC Grids" *Journal of Power Electronics. Vol. 16, No. 5, 2016.*

Conference papers:

- Diab, H.Y., Tennakoon, S., Gould, C. and Marei, M.I. "An investigation of power flow control methods in multi terminal high voltage DC grids". In Power Engineering Conference (UPEC), 2015 50th International Universities (pp. 1-5). IEEE. United Kingdom.

- Diab, H.Y., Tennakoon, S., Gould, C. and Marei, M.I. "An IGBT based current flow controller for use in meshed HVDC grids" *The 5th International Conference on Renewable Power Generation – 2016, IET conference. United Kingdom.*

- Diab, H.Y., Abdelsalam, M., Tennakoon, S., Gould, C. and Marei, M.I. "Real Time Simulation of a Current Flow Controller for High Voltage DC Grids Applications" In Power Engineering Conference (UPEC), 2016 51<sup>st</sup> International Universities. IEEE. Portugal.

- Diab, H.Y., Tennakoon, S. and Abdelsalam, M. "A Current Flow Control Apparatus for Meshed Multi-Terminal DC Grids" *International Symposium* on Electrical Apparatus and Technologies, SIELA 2016. IEEE. Bulgaria.

Co-authored papers:

• Abdelsalam, M., Tennakoon, S. and Diab, H.Y. "An ADALINE Based Capacitor Voltage Estimation Algorithm for MMCs" *International*  Symposium on Electrical Apparatus and Technologies, SIELA 2016. IEEE. Bulgaria.

- Moussa, M., Abdelsalam, M. and Diab, H.Y. "Enhanced Approach for Modelling and Simulation of Modular Multilevel Converter Based Multiterminal DC Grids" 18th International Conference on Modelling & Simulation, UKSIM 2016, IEEE. United Kingdom.

- Abdelsalam, M., Diab, H.Y., Tennakoon, S., Griffiths, A. and Marei, M.I. "Detection and Diagnosis of Sub-Module Faults for Modular Multilevel Converters" In Power Engineering Conference (UPEC), 2016 51<sup>st</sup> International Universities. IEEE. Portugal.

### Chapter

### 2

# **Emergence of High Voltage DC and Multi terminal DC grids**

### 2.1 Introduction

The modern configuration of electrical power generation, transmission and distribution systems has been changed significantly with the increased integration of advanced technologies and power electronics when compared with the conventional power system. In recent decades, new technologies such as smart grids (demand side management, bi-directional smart meters, etc.), Flexible AC Transmission Systems (FACTS) and new renewable power resources such as solar, wind, tidal and wave energy have been added gradually to the power system to enhance its functionality, reliability and continuity. Solar and wind energy, especially offshore, are considered to be the leading alternatives to conventional fossil fuel based systems in Europe generally and in the North Sea area in particular.

This chapter reviews the re-emergence of High Voltage Direct Current (HVDC) power transmission as a serious rival to High Voltage AC (HVAC) transmission and AC grid. Three AC/DC power converters topologies, Line Commutated Converters (LCC), Voltage Source Converters (VSC) and Modular Multilevel Converters (MMC) are reviewed as they form the core of any HVDC transmission network. The possible configurations that are available for forming multi-terminal DC grids are also discussed along with challenges that need to be overcome for the practical realisation of DC grids.

### 2.2 High Voltage DC Transmission

HVDC has been a power transmission option since early 1950s, where the world's first HVDC commercial transmission line was installed between Gotland and the Swedish mainland [25]–[27]. Since then, HVDC started to attract researchers and industry to investigate its feasibility and whether it can be a better substitute to conventional HVAC transmission. Until now, most European offshore wind farms are interconnected to the grids with HVAC [28], as each specific wind farm case in terms of network configuration and power rating play an important role in choosing the best solution. The main advantages that HVDC [28], [29] can offer when compared to HVAC can be summarized as follows:

- Ease of interconnecting two asynchronous grids, for example, the back to back HVDC link between Brazil and Argentina. By connecting two back to back AC/DC converters, AC power is converted to DC and then back to AC with the desired frequency, facilitating power exchange between 50Hz and 60Hz grids.

- Ease of active power control in point to point links.

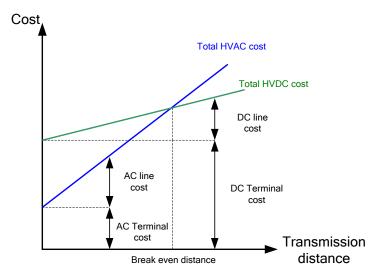

- Lower power losses and cost over long distances of power transmission; in particular, in submarine transmission. This is the major factor that contributes toward HVDC to take over HVAC in offshore wind farm to grid connections. Figure 2.1 illustrates the cost against transmission distance for both overhead and submarine cable transmission. HVAC is more economical in shorter distances as the total cost is low when compared to the high cost of HVDC converter stations. Nevertheless, DC underwater cables rated to transfer an equal amount of power at lower costs than their three-wire AC rivals. On the other hand, transmitting power to long distances is more economical with HVDC as there are no reactive power compensators needed similar to when transporting via HVAC.As a result, HVDC is usually more economical when transmitting power using submarine cables for distances more than 70km [30].

Figure 2.1: Power transmission cost versus distance with both HVDC and HVAC solutions.

The increase of more remote offshore wind farms as well as the desire for establishing international interconnections in the North Sea area [31]–[33] require long transmission networks and reliable power flow controllability. The large shunt capacitance of submarine cables affects HVAC connections causing stability problems and require large reactive power compensation equipment [28]. For these reasons, HVDC became the best available option for forming not only point to point connections, but also offshore multi terminal HVDC power transmission networks.

### 2.3 High Voltage DC Converter Stations

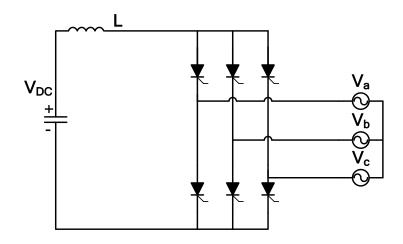

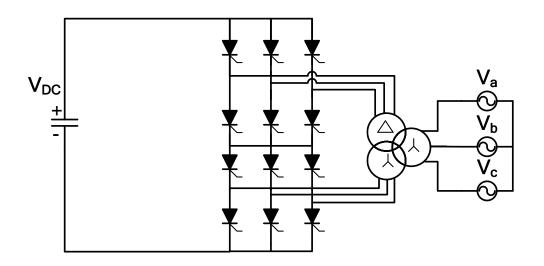

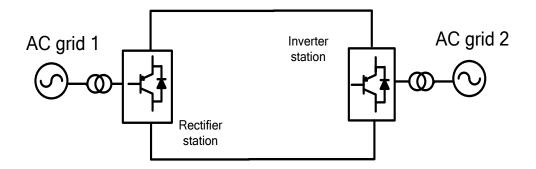

#### **2.3.1** Line commutated current source converter

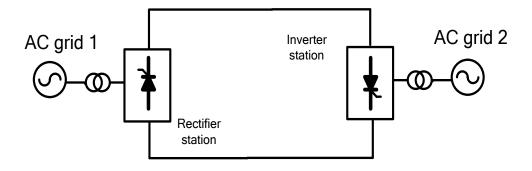

The most recognized and generally utilized in conventional HVDC power transmission is thyristor valve based three phase line commutated converter (LCC) or also known as 6 pulse Graetz bridge shown in Figure 2.2 [34]-[36]. LCC can transmit power in both directions where it can be operated in inverter or rectifier modes by changing the firing angle. If the firing angle is set to less than 90°, the converter is operated in rectification mode and transmits power from the AC side to the DC side. If the firing angle is set to a value between  $90^{\circ}$  and  $180^{\circ}$ , it can be operated as an inverter and power is transmitted from the DC side to the AC side. The high reliability, low cost technology and high power capability have put the LCC in a leading position when it comes to market share [37]. A widely used configuration of LCC is back to back HVDC transmission system shown in Figure 2.3. One major drawback of LCC based HVDC is that it suffers from low order harmonics which need to be treated through installing additional large passive filters. [38]. Despite the low cost and high efficiency of passive filters, they are still limited to specific frequencies. Moreover, they are affected by the system impedance [39] and consume large amount of reactive power due to the operation with AC current lagging the voltage[36], [40].

Figure 2.2: Three phase line commutated converter topology.

Figure 2.3: Back to back LCC based HVDC system.

To overcome these drawbacks, active filters have been proposed for LCC based HVDC systems as shown in Figure 2.4 as they are able to compensate the distorted current waveforms produced by the LCC [39], but on the other hand, more switching losses are introduced to the system as a result [34] and large footprints are lost. Also, a LCC needs to be connected to a strong AC grid to guarantee successful commutation otherwise operational problems may occur if connected to a weak system.

LCC HVDC converters are invariably 12 pulse as shown in Figure 2.5, where two 6 pulse LCC are displaced in phase by  $30^{\circ}$  [35], which leads to 12 pulse operation. The increased number of pulses eliminate all  $6n\pm1$  harmonics;  $5^{th}$ ,  $7^{th}$ ,  $11^{th}$  and  $13^{th}$  harmonics.

Figure 2.4: Active filter connected to LCC-HVDC system.

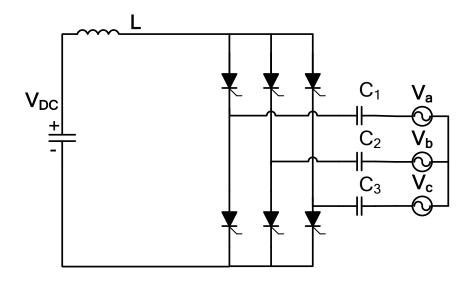

Another similar converter topology proposed is the Capacitor Commutated Converter (CCC) where series capacitors are connected between the converter and the AC grid (see Figure 2.6) allowing connection to weak AC grids, and overcoming LCC's commutation problem [41].

Figure 2.5: 12 pulse Line Commutated Converter circuit topology.

Figure 2.6: Circuit topology of Capacitor Commutated Converter (CCC).

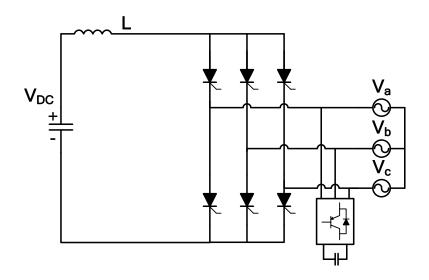

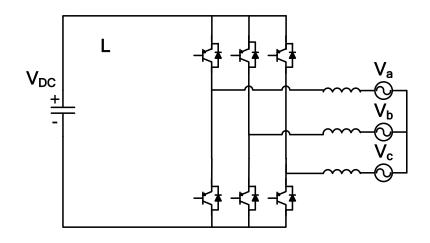

### 2.3.2 Self-commutated voltage source converter

As its name implies, self-commutated Voltage Source Converters (VSC) use selfcommutating switches such as Gate Turn Off Thyristors (GTO) or Insulated Gate Bipolar Transistors (IGBT), as shown in Figure 2.7 [42]. Switches can be switched on or off at any time by on/off gating signals, which is a great advantage in comparison with LCC's thyristor valves which can only be turned off by reducing the anode current below zero [42]. Anti-parallel diodes need to be connected with VSC's switches as IGBTs can only block voltage and permit current in one direction [43], and these diodes provide the ability to dissipate current in the other direction. VSCs give better waveforms as it can be operated in high frequencies, typically around 1 kHz, to get rid of low order harmonics [36]. Another important advantage of VSC technology is that it allows both active and reactive power control independently from each other and DC voltage level [40], allowing VSC converters to be installed at any point in the AC grid without the need of reactive power compensation as well [36].

Figure 2.7: Three phase two level self-commutated – Voltage Source Converter (VSC).

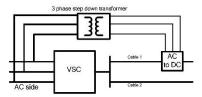

One of the features that attracted researchers and industry leaders to the VSC technology is that it behaves as an amplitude and phase angle controlled voltage source [43], allowing the instant reversal of active power if needed, which gives VSC more potential to act in the converter role in futuristic MTDC grids when compared to LCC [42]. VSCs can also be connected in back to back configuration as shown in Figure 2.8. However, 2 - level VSC converters in its conventional form still need bulky DC link capacitors. VSCs also offer lower power capacities and higher switching losses when compared to LCC converters.

Figure 2.8: Back to back connection using VSC converters.

#### 2.3.3 Multi-level converter topologies

Voltage source converters are thought to be the best choice for the future industry applications for HVDC transmission systems [44]. However, conventional topologies of two-level VSC still suffer from significant drawbacks such as poor performance in case of DC link faults [45], [46].

To make VSCs more feasible, several multi-level converter topologies have been introduced by researchers offering similar but upgraded operation to that of conventional VSC and providing features such as lower voltage stress on IGBT's, low dv/dt, and suppression of low order frequency harmonics and hence decreasing AC side filter footprint and cost [47], [48]. Diode clamped multilevel converter was first introduced in 1980 by [49] and afterwards extended to N levels topology in 1983 by [50]. Flying capacitor multilevel converter is another topology introduced in the early 1990s by [51], [52]. Both topologies suffered from DC link capacitors voltage imbalance, complexity with higher levels and vulnerability to the effect of system impedance [53]. Modular multi-level converters (MMC) emerged firstly in its half-bridge configuration in [54] and offered several advantages such as minimal conversion power losses when compared to other earlier VSC topologies, offer modular functionality to increase voltage level as desired, easy capacitors voltage balancing feature and higher system redundancy [55]. Unfortunately, half bridge MMCs suffer from AC inrush currents during DC link faults and are capable of operating in buck mode that does not provide active power to the AC grid when the DC link voltage decreases under the peak value of line AC voltage [55].

Full bridge MMC was introduced later on which offers similar advantages in addition to the ability of DC faults ride through and the voltage support capability to the AC grid during faults [56]. Also, H-bridge MMC cells can produce bipolar output voltage  $+V_c$  or  $-V_c$  which gives it another reason to be utilized in HVDC transmission and renewable energy interconnecting when compared to unipolar  $+V_c$  output of half bridge MMCs.

Hybrid cascaded H-bridge multilevel converter was proposed as a special type of converter [57]. It offers multilevel output voltage waveform with less number of cells, but still has limited capabilities in interrupting DC faults and AC inrush current and the voltage stress on each switch is relatively high which in turn limits the application of such converter in HVDC transmission systems [58]. The next subsections discuss multilevel converters in more details.

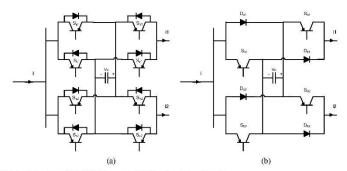

### 2.3.3.1 Diode clamped multilevel converter

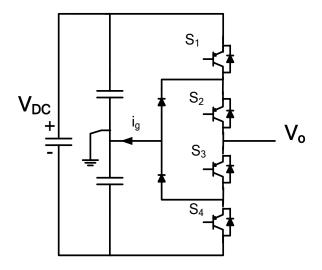

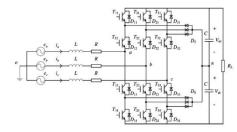

The topology of the diode clamped multilevel converter is formed of clamping diodes and series DC capacitors, each phase of n-level converter (n-1) capacitors are connected in series across the DC side and 2x(n-1) switches are present along with (n-1)x(n-2) clamping diodes. This topology is capable of producing n levels of phase voltage in normal operation [59]. The single phase, three level diode clamped converter topology shown in Figure 2.9 consists of four IGBT switches  $(S_1, S_2, S_3$  and  $S_4$ ) each with its own anti parallel freewheeling diode  $(D_1, D_2, D_3 \text{ and } D_4$  respectively) allowing current flow capability in both directions. Each capacitor is subjected to voltage  $\frac{1}{2}V_{dc}$  and the neutral point *G* is set between both capacitors. These DC link capacitors are charged or discharged when current  $i_g$  flows into the neutral causing neutral-point voltage distortion [53].

Figure 2.9: Single phase three-level diode clamped converter.

The output voltage of this converter  $V_o$  is produced by three switching stages. First, when switches  $S_1$  and  $S_2$  are on and  $S_3$  and  $S_4$  are off, the output is  $\frac{1}{2} V_{dc}$ . Second, when  $S_2$  and  $S_3$  are on and  $S_1$  and  $S_4$  are off, the output voltage is equal to zero. Finally, when  $S_3$  and  $S_4$  are the only switches that are on, the output voltage is  $-\frac{1}{2} V_{dc}$ . The clamping diodes role is to clamp the voltage to  $\frac{1}{2} V_{dc}$  on each switch that is turned off [60]. The topology of the diode clamped converter is relatively complex making it difficult to be constructed in a high number of levels with high number of clamping diodes limiting its practical implementation in high voltage applications [61]. As the levels exceed three, DC link capacitors voltage become unbalanced and further circuits or capacitor voltage balancing techniques are required to solve this problem [62].

### **2.3.3.2 Flying capacitor multilevel converter**

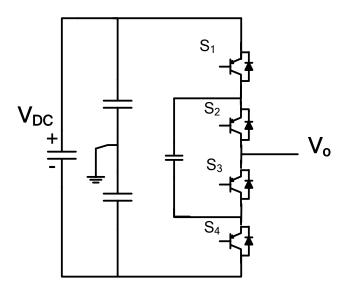

Another topology is the Flying capacitor multilevel converter, where the capacitors are combined with switches to produce different voltage levels by adding or subtracting the capacitor voltages [63]. The voltage stress on each IGBT is equivalent to the voltage rating of each capacitor; hence, for an n-level converter (*n*-1) DC link, capacitors are required as well as  $\frac{1}{2}$  (*n*-1)*x*(*n*-2) flying capacitor per phase. Figure 2.10 illustrates the circuit topology of a single phase three-level flying capacitor multilevel converter.

Figure 2.10: Single phase three-level flying capacitor converter.

The switching states are somehow similar to that of diode clamped converter mentioned earlier, offering three output voltage levels  $\frac{1}{2} V_{dc}$ ,  $\frac{1}{2} V_{dc}$  and 0 [64], [65]. The flying capacitor multilevel converter requires a large number of capacitors at the DC side. For this reason, it is impractical to implement such topology in a high voltage transmission system with a large footprint and high cost of the bulky capacitors [66]; in addition to the DC link voltage imbalance mentioned earlier, the applications of this converter in medium voltage power transmission are limited [67].

### 2.3.3.3 H-bridge cascaded multilevel converter

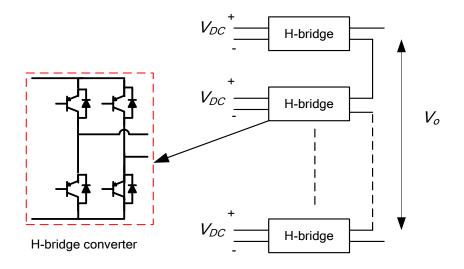

The cascaded H-bridge multilevel converter is basically a set of series connected Hbridge cells each requiring its own independent DC source [68] as shown in Figure 2.11. This type of converter is not used in HVDC power transmission as there is no DC link present. Still, H-bridge cascaded converters are used for integrating photovoltaic cells to the grid [69] and electric vehicles [70].

Figure 2.11: H-bridge cascaded multilevel converter.

### 2.3.3.4 Hybrid H-bridge cascaded multilevel converter

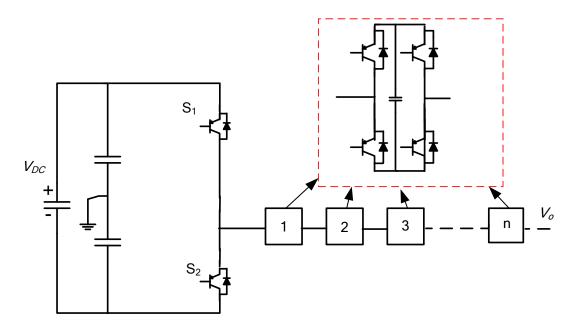

The hybrid H-bridge cascaded multilevel converter's topology is shown in Figure 2.12 with *n* H-bridge cells per phase. The converter can produce up to 4n+1 voltage levels. The voltage rating of each cell capacitor is  $\frac{Vdc}{2n}$  and it is equal to the voltage stress on each H-bridge cell [57].

Figure 2.12: Hybrid H-bridge cascaded multilevel converter.

During DC faults, all IGBT switches including H-bridge cells are switched off, and cell capacitors give reverse voltage to suppress the inrush current from the AC grid. This leads to a state where no active or reactive power is exchanged during DC fault condition. The main switches,  $S_1$  and  $S_2$ , are subjected to high voltage stress of value  $V_{dc}$  which limits the application of this topology in HVDC power transmission.

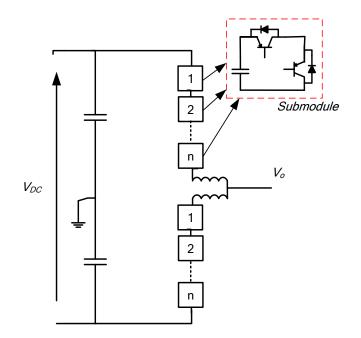

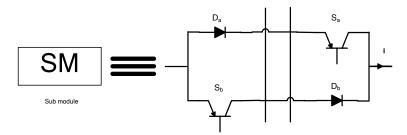

## 2.3.3.5 Half bridge modular multilevel converter

Single phase half bridge based modular multi-level converter topology is demonstrated in Figure 2.13 where it is formed of n half bridge cells per arm that is capable of producing n+1 output voltage levels. The rating of each cell capacitor is  $\frac{Vdc}{n}$  and it is the same value of voltage stress that is subjected to each switch. One of the main advantages of this topology is that the output voltage can have nearly a sinusoidal waveform with increased number of levels. Arm inductors are present to suppress the harmonics in arm currents and to limit the AC inrush current during DC side faults. Sinusoidal Pulse Width Modulation (SPWM) and phase shifted carried

modulation [71] are two major modulation methods commonly used in half-bridge MMC control. Cell capacitor voltage balancing techniques are also introduced [72].

Figure 2.13: Half-bridge modular multilevel converter.

The half-bridge MMC offer several advantages such as the following:

- Low voltage stress on each switching element as mentioned earlier

- No need for bulky capacitors.

- The quality of output waveform increases with the increase of number of levels. Leading to less harmonics and smaller footprints for filters and less cost.

- Decreasing the switching frequency with the increased number of levels leading to less switching losses.

However, this type of converter does not offer DC fault ride through capability and it cannot be controlled in cases of DC link voltage decrease (between 0 and  $V_{dc}$ ) which is a common case with renewable energy generation as wind speed and solar irradiance cannot be controlled. Another disadvantage of half bridge MMC is that it suffers from arm current harmonics and circulating current in each phase having significant increases in conduction losses.

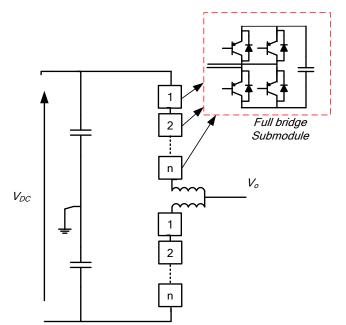

#### 2.3.3.6 Full bridge modular multilevel converter

With similar advantages of that of Half bridge MMC, the Full bridge MMC shown in Figure 2.14 offers low switching frequency which has direct impact on AC side filters size, low voltage stress on IGBT switches, eliminating bulk DC link capacitor, and excellent AC output voltage waveform that is close to sinusoidal. However, as the full bridge MMC involves more switches when compared to half bridge MMC at the same power level, it has a noticeable draw back that it produces higher switching losses. The full bridge MMC started to gain the attention of both industry leaders and researchers as it adds an important advantage to its half bridge rival, which is the DC fault ride through capability by suppressing AC inrush current with reversed cell voltage and is able to keep cell capacitor voltages to the rated value. Some other advantages such as post fault recovery and active power injection to the AC side by utilising the full range of DC link voltage gave the full bridge MMC superiority over all other topologies discussed earlier.

Figure 2.14: Full-bridge modular multilevel converter.

# 2.3.4 AC/DC converters summary

The most famous converter topologies and their functionalities discussed earlier in section 2.3.3 are compared in Table 2-1.

|                                                                                 | Line                                            | Voltage                  | Half bridge | Full bridge |

|---------------------------------------------------------------------------------|-------------------------------------------------|--------------------------|-------------|-------------|

|                                                                                 | Commutated                                      | Source                   | MMC         | MMC         |

| Switching<br>element                                                            | Thyristor                                       | IGBT                     | IGBT        | IGBT        |

| Switching<br>losses                                                             | Very low                                        | High                     | Low         | Acceptable  |

| Operational<br>losses                                                           | Low                                             | High                     | Acceptable  | Acceptable  |

| Active power<br>control                                                         | Yes                                             | Yes                      | Yes         | Yes         |

| Independent<br>reactive and<br>active power<br>control                          | No                                              | Yes                      | Yes         | Yes         |

| Required reactive power                                                         | Yes                                             | No                       | No          | No          |

| Requires<br>filters at AC<br>side                                               | Yes – with<br>large<br>footprint                | Yes – small<br>footprint | No          | No          |

| DC fault ride<br>through<br>capability                                          | Strong                                          | Weak                     | Weak        | Strong      |

| AC fault ride<br>through<br>capability                                          | Yes – with<br>risk of<br>commutation<br>failure | Yes                      | Yes         | Yes         |

| Ability to<br>operate in<br>boost mode<br>during DC<br>link voltage<br>collapse | No                                              | No                       | Yes         | Yes         |

| Manufacturing<br>cost                                                           | Low                                             | Moderate                 | High        | Highest     |

Table 2-1: Comparison between AC/DC converter topologies.

# 2.4 HVDC Transmission System Configurations

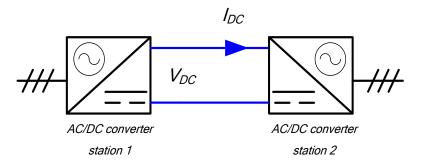

#### 2.4.1 Point to point connections

There are several possible HVDC configurations to interconnect any two AC/DC converters together. In the following three subsections, the Monopolar, Bipolar and back to back configurations are discussed in greater detail [73]–[78].

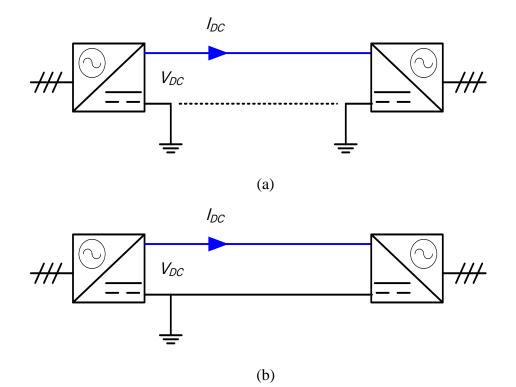

#### **2.4.1.1** Monopolar connections

The monopolar is the most elementary HVDC transmission system arrangement. One pole is used to interconnect the two converter stations together, usually with negative polarity, to minimize corona effects [78]. The monopolar HVDC point to point configuration is possible either with ground return or metallic return as shown in Figure 2.15(a) and Figure 2.15(b), respectively. Ground return arrangement offers lower costs as only one DC cable is needed as shown in Figure 2.15(a). However, in highly populated areas or areas with high earth resistivity, such as fresh water reservoirs, ground return may not be the feasible option to be used. Metallic return can be used in such cases to overcome any environmental or interactions with metal structures. All monopolar configurations suffer from the drawback of losing the whole transmission link if any fault occurs in the converter or to the DC cable.

Figure 2.15: Monopolar HVDC point to point connection a) Ground return b) metallic return.

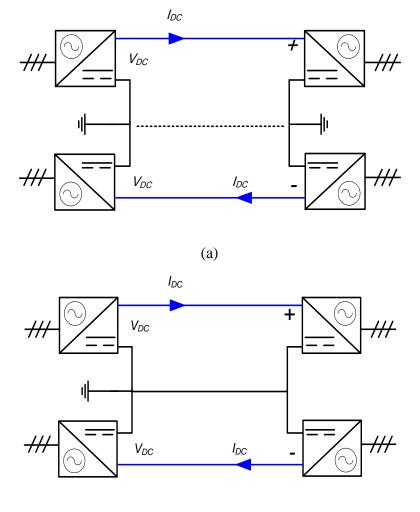

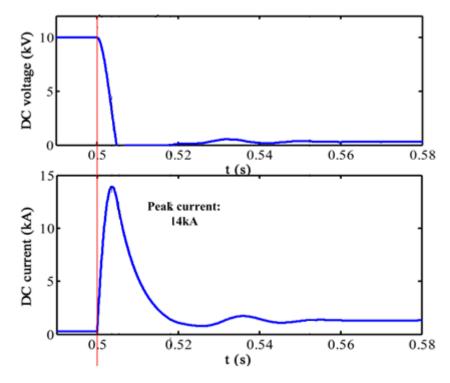

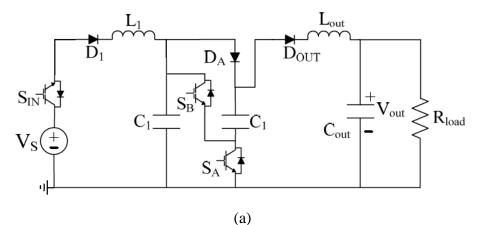

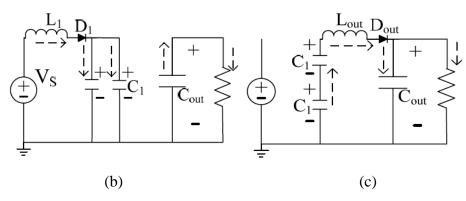

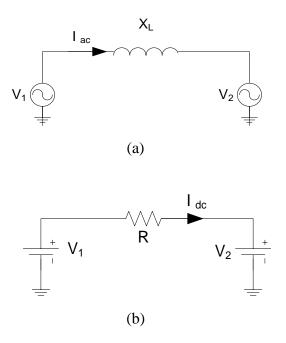

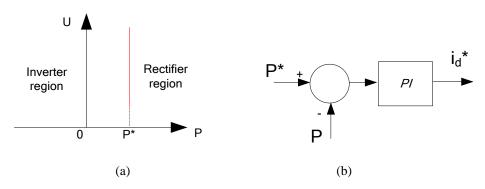

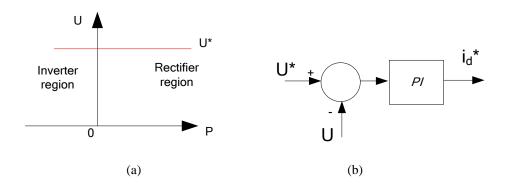

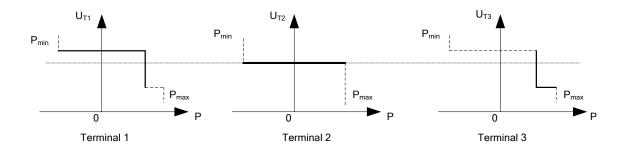

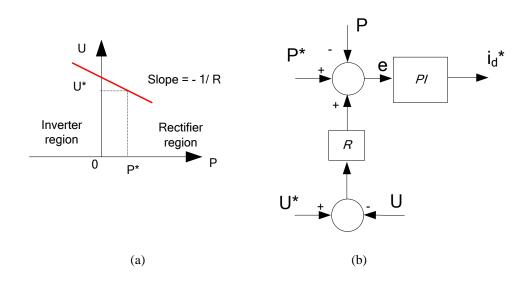

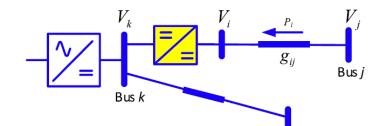

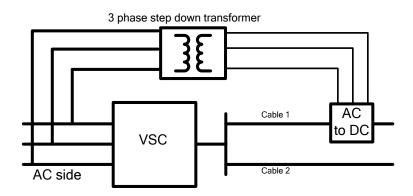

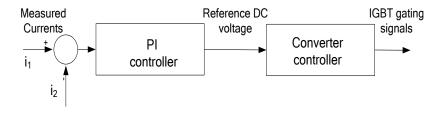

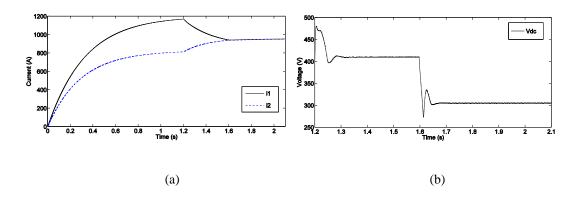

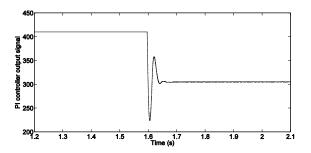

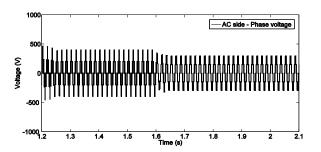

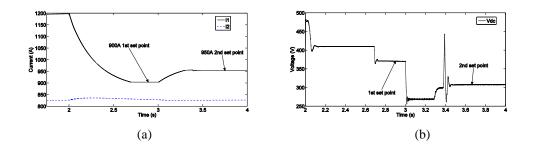

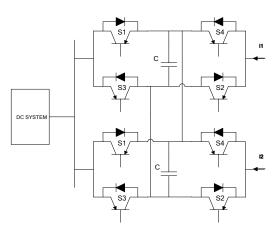

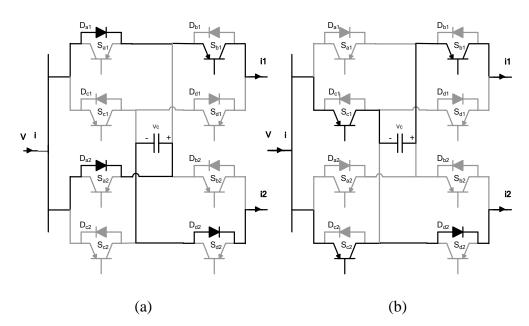

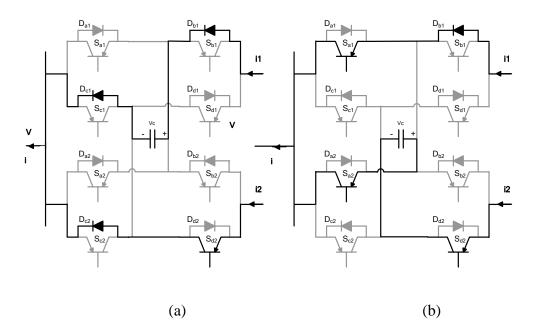

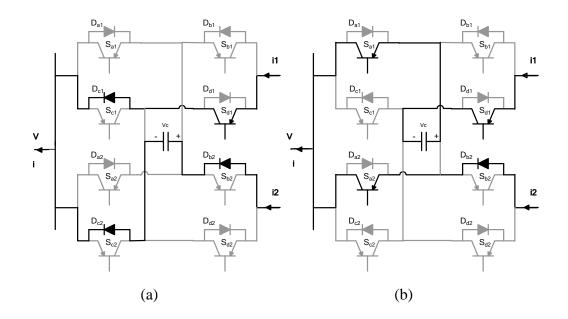

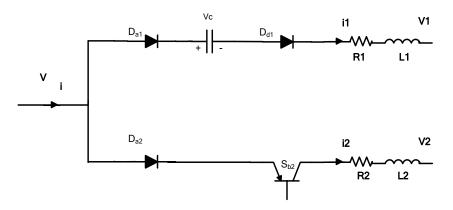

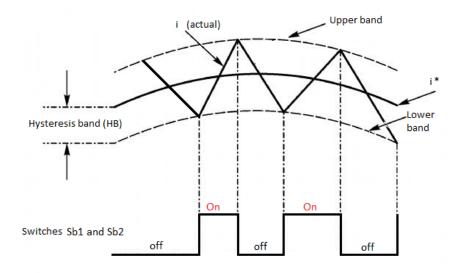

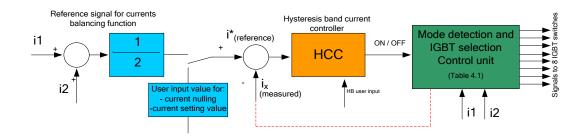

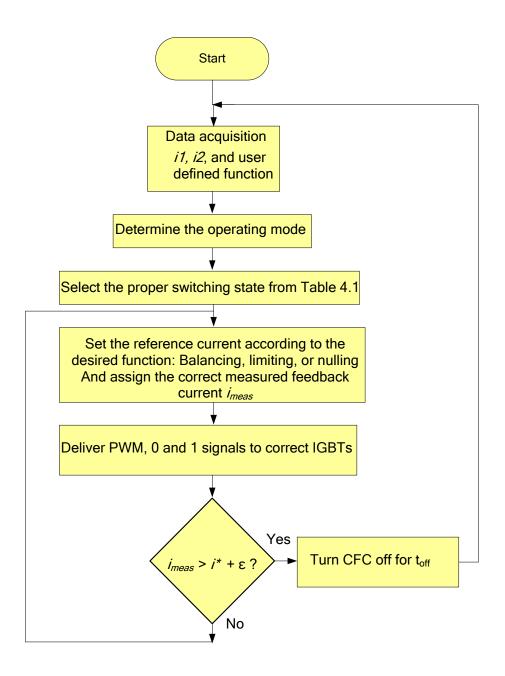

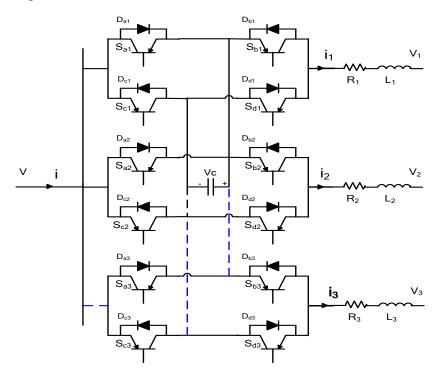

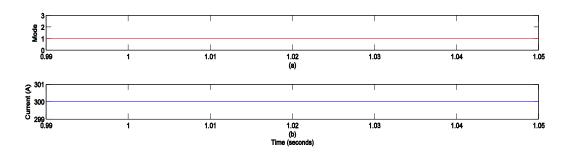

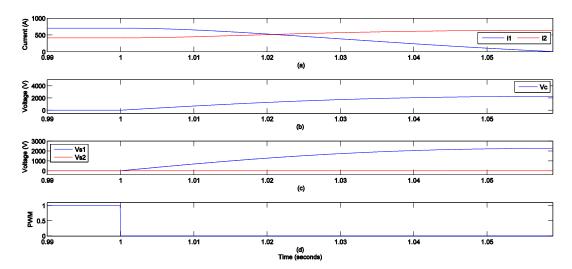

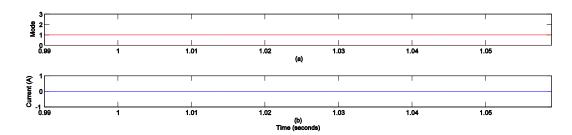

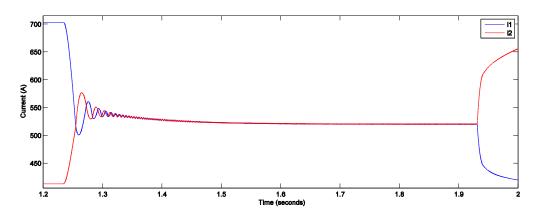

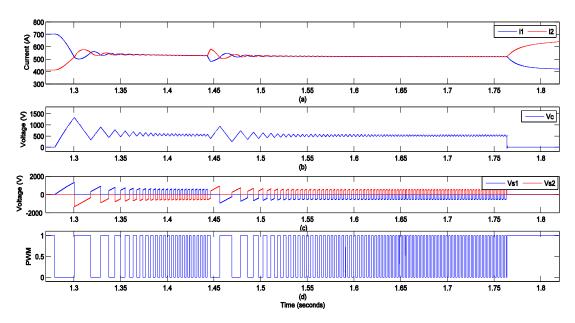

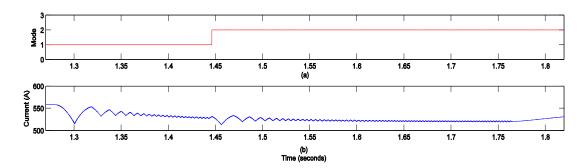

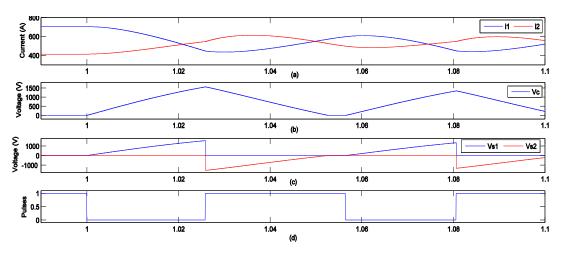

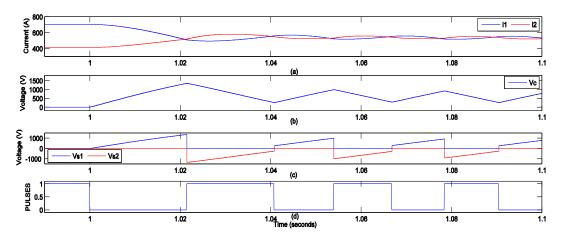

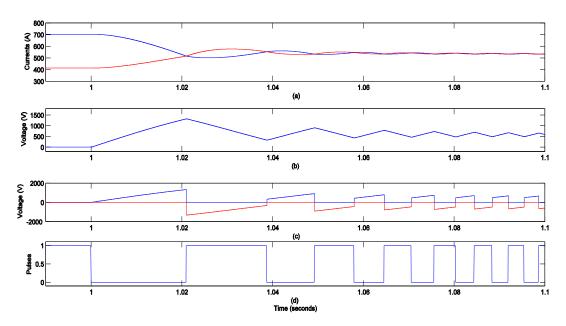

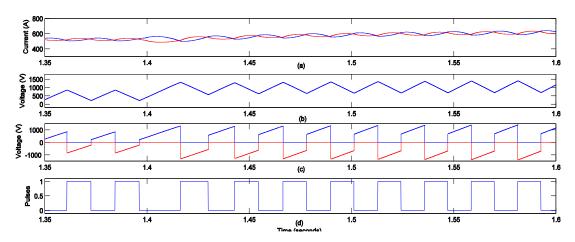

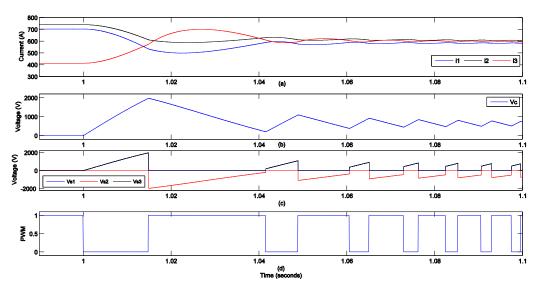

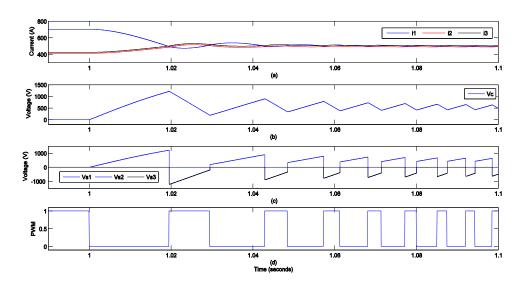

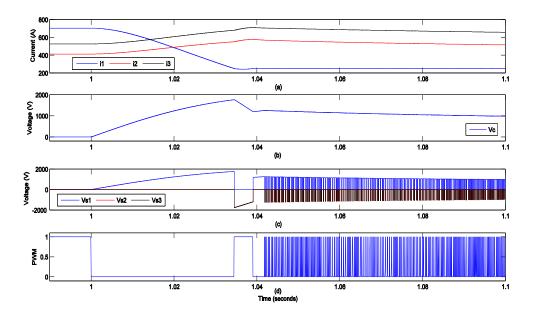

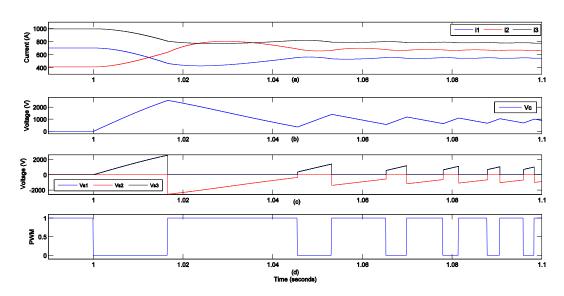

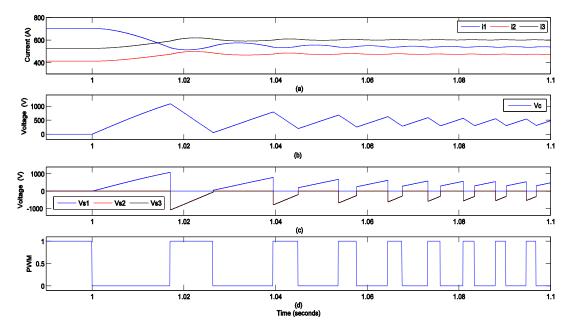

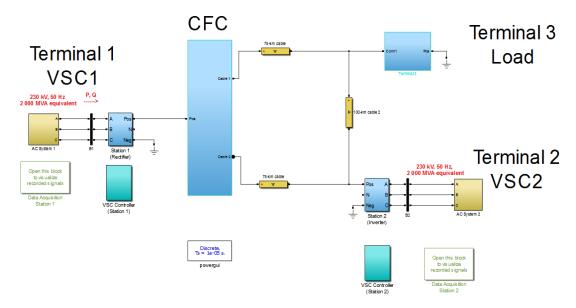

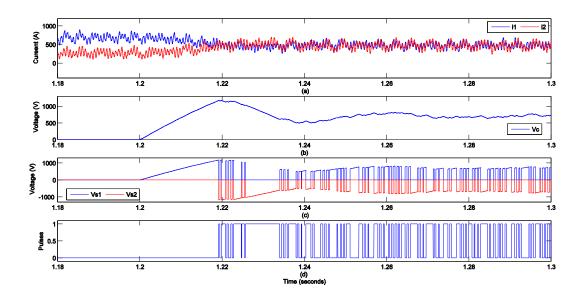

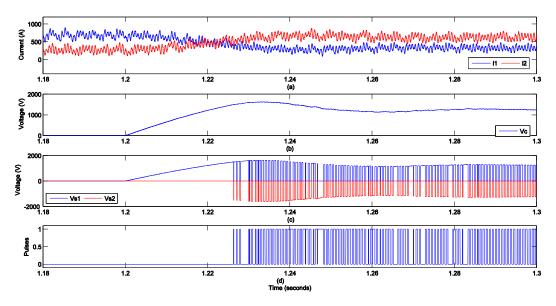

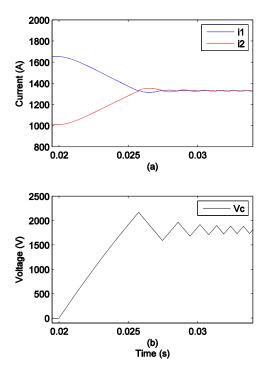

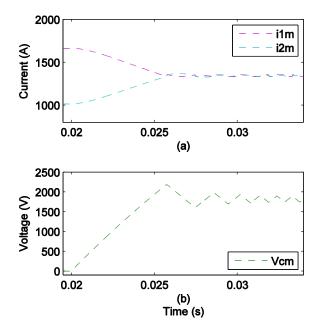

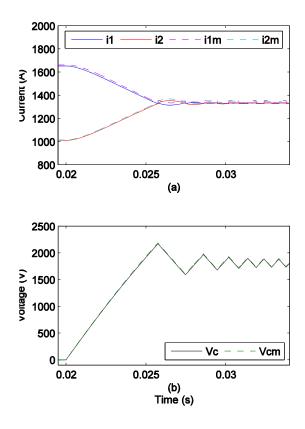

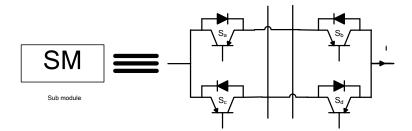

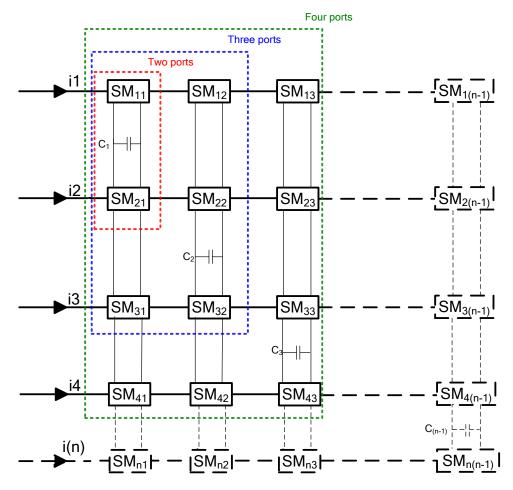

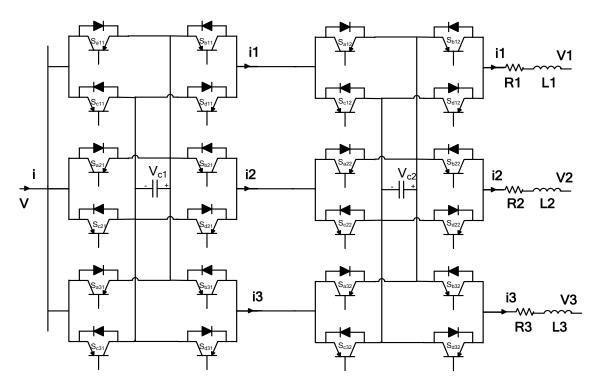

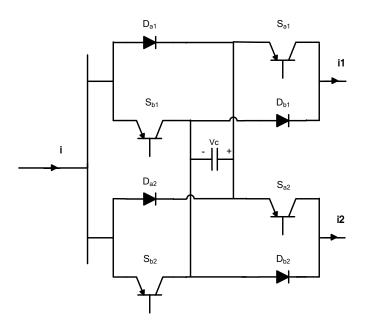

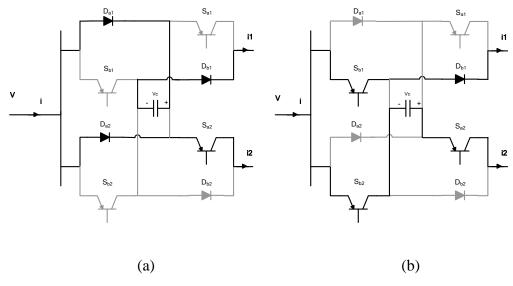

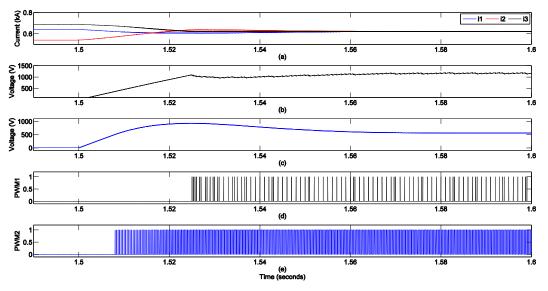

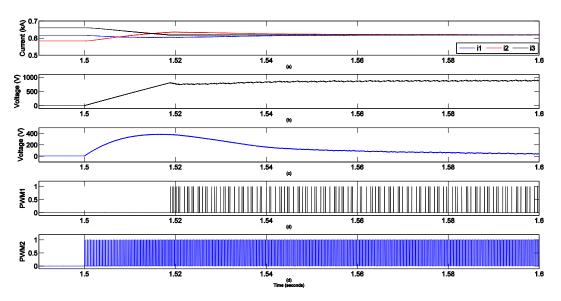

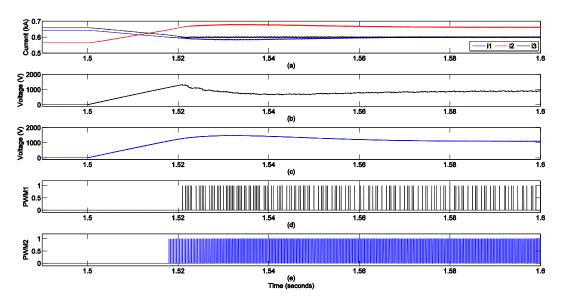

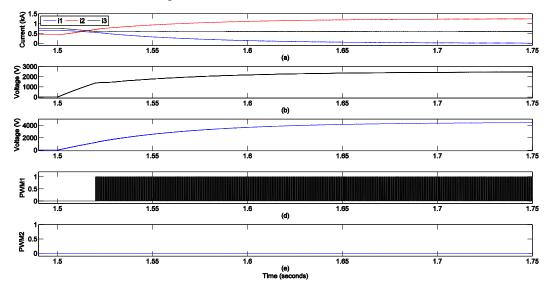

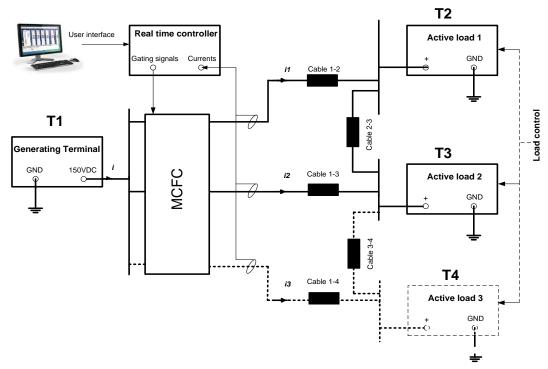

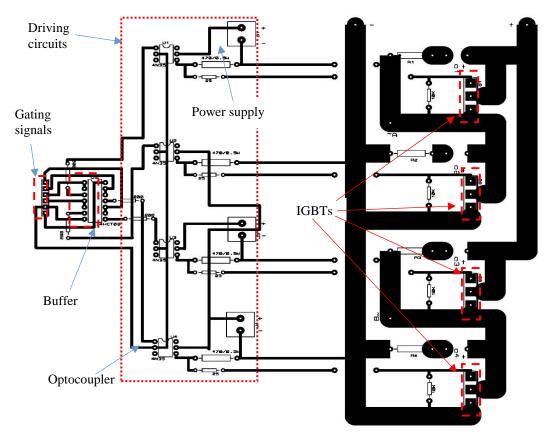

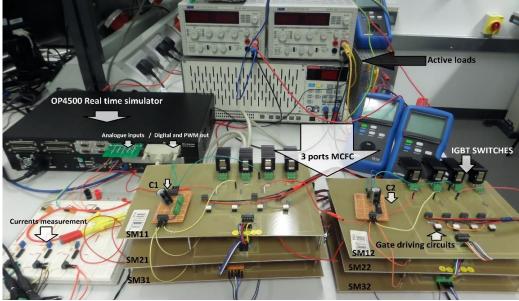

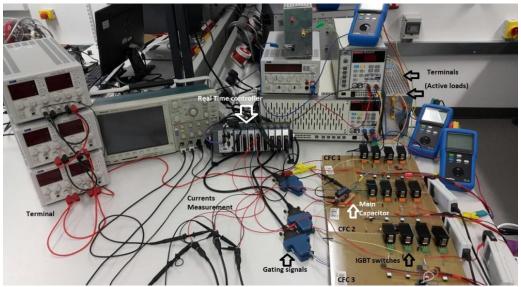

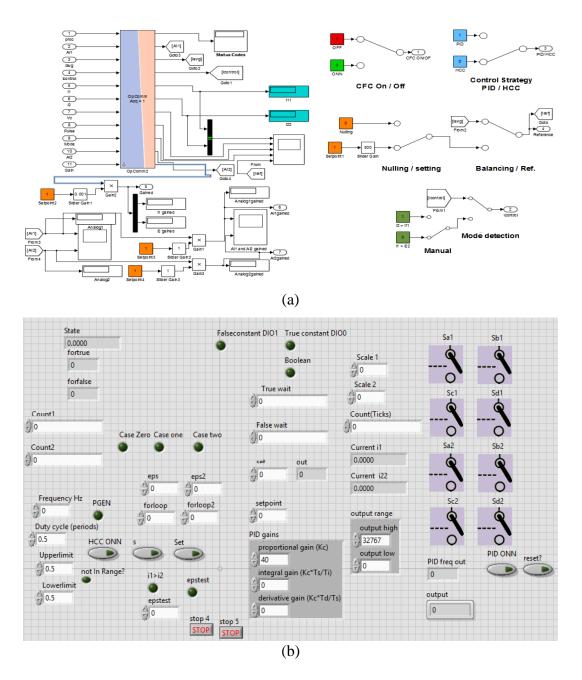

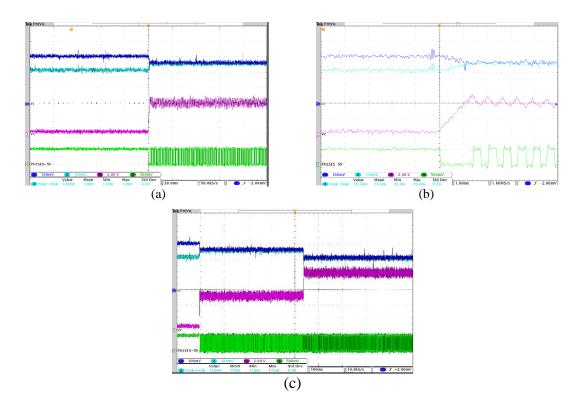

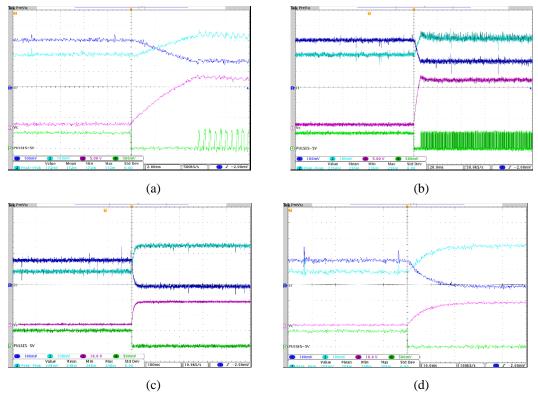

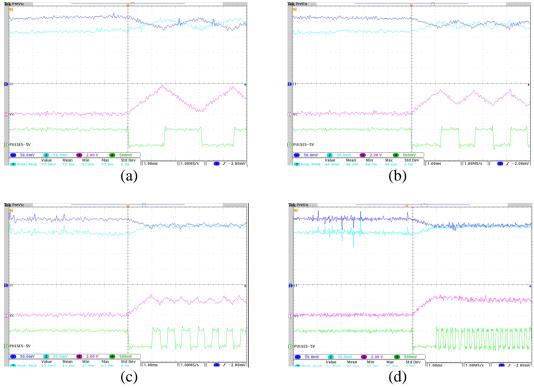

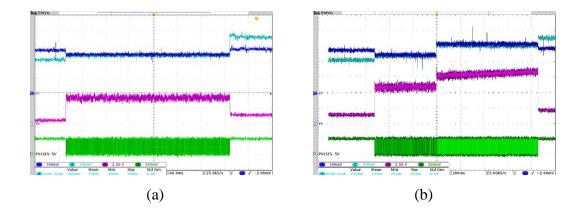

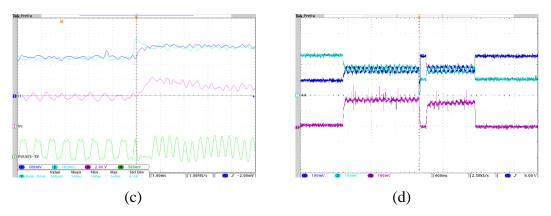

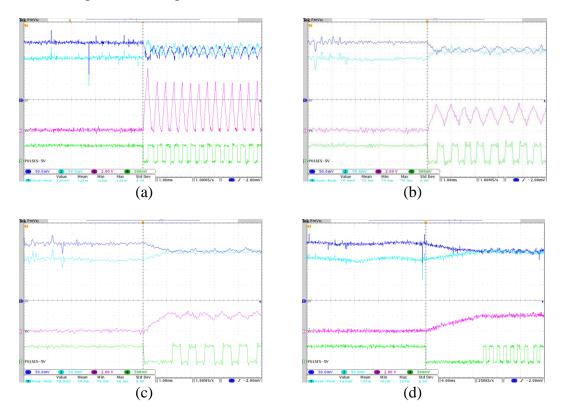

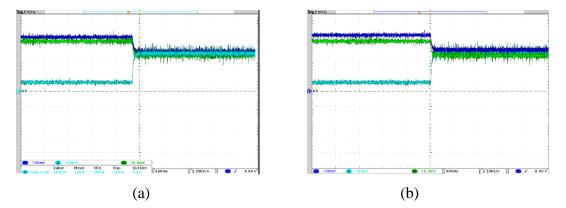

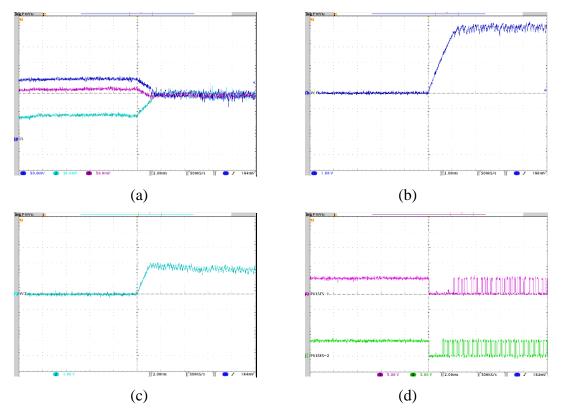

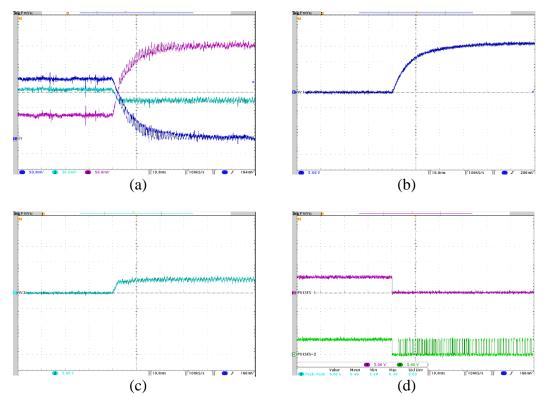

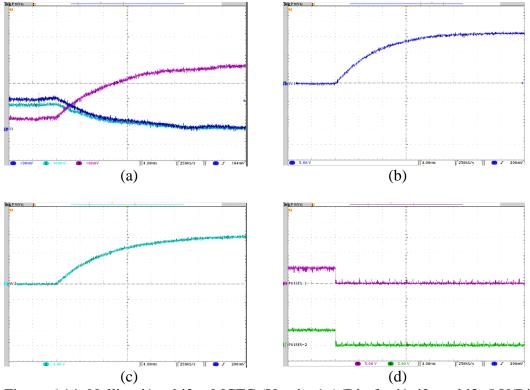

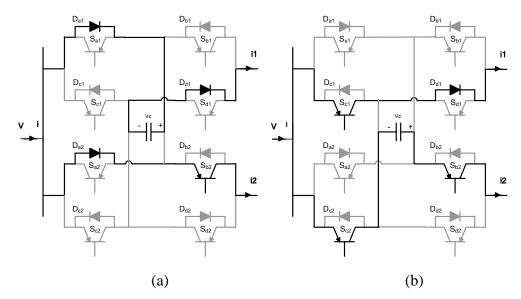

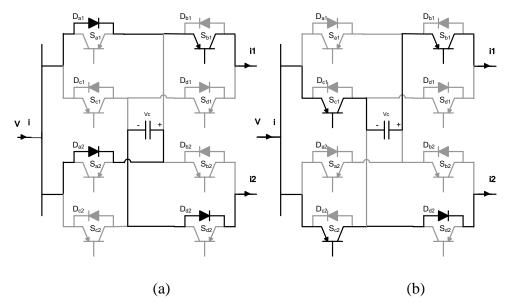

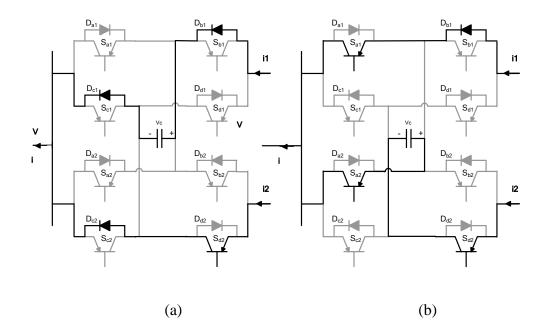

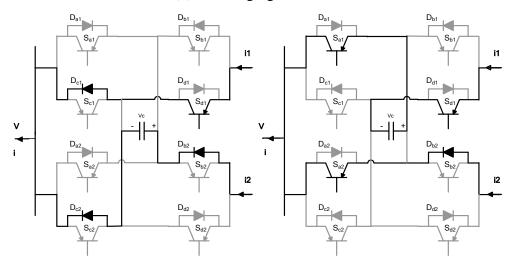

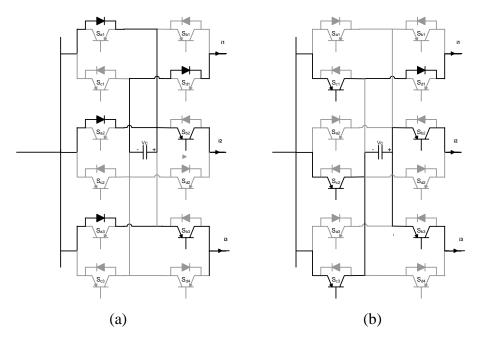

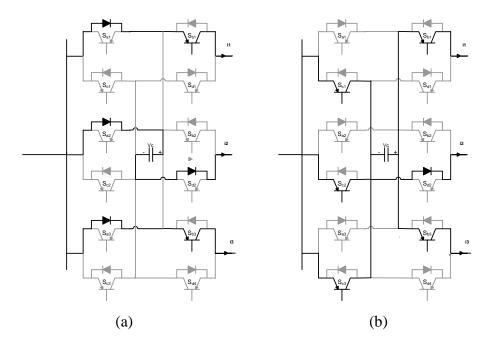

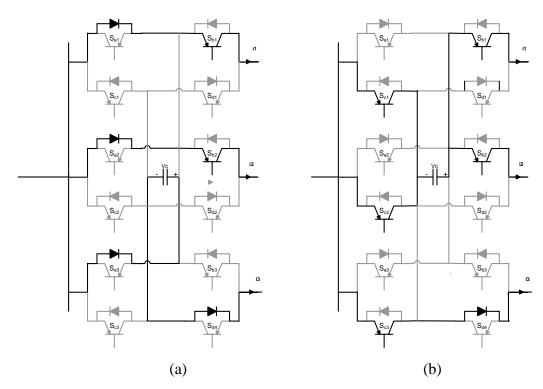

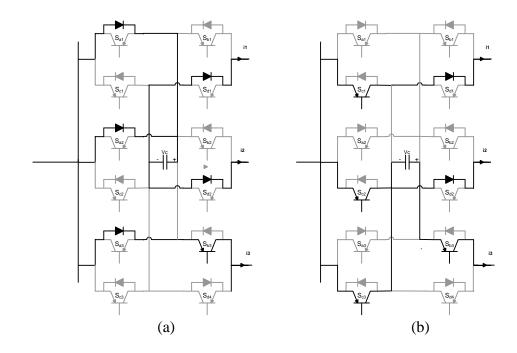

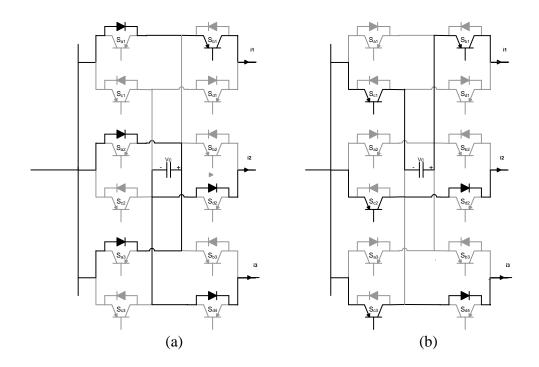

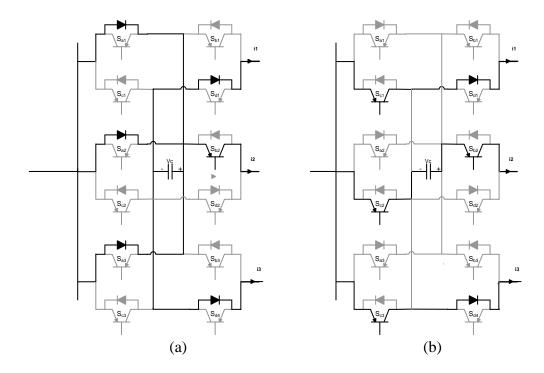

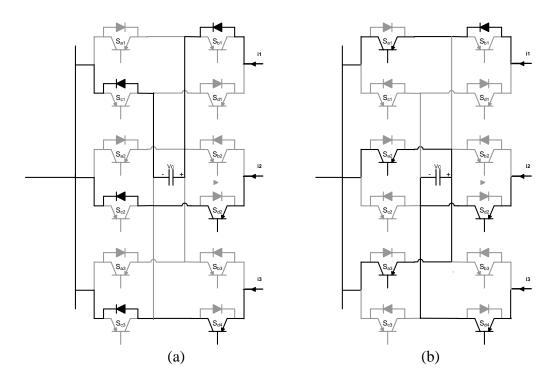

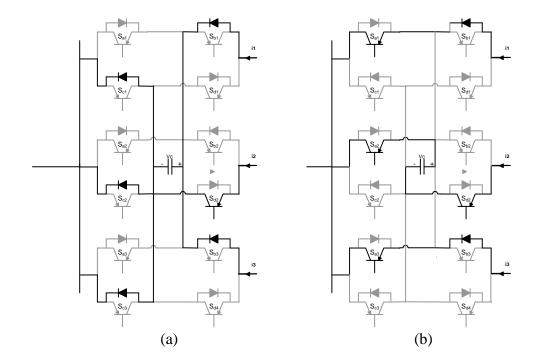

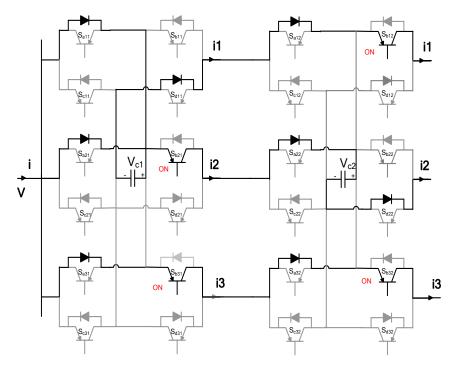

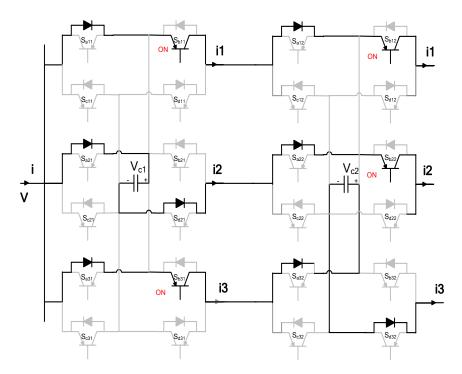

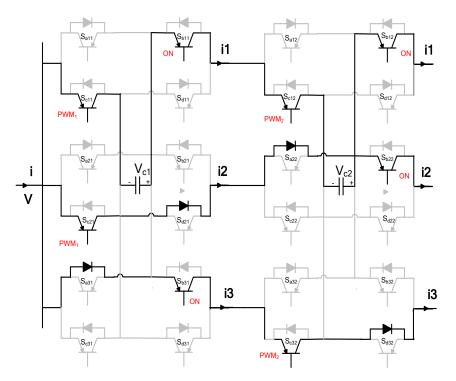

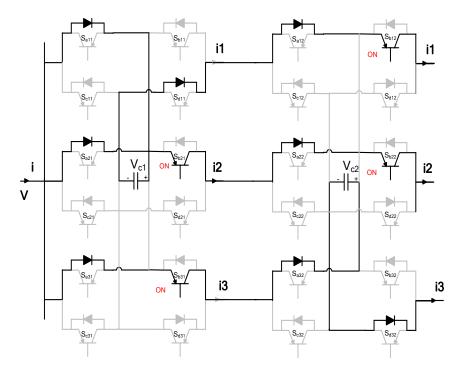

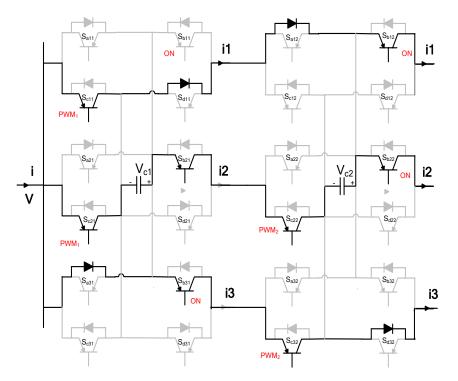

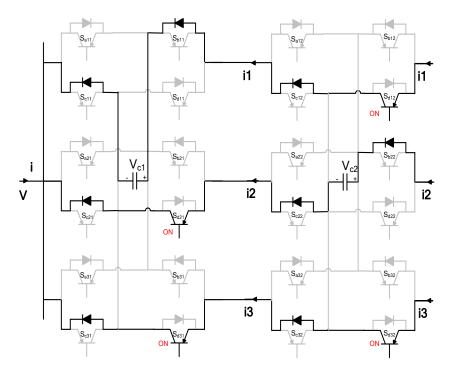

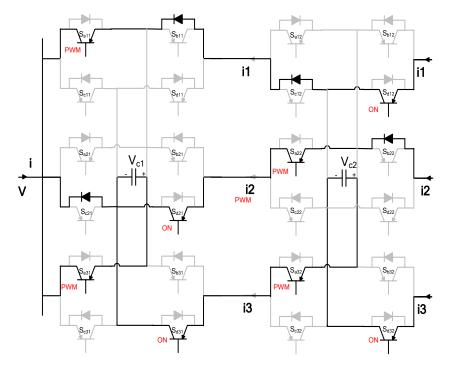

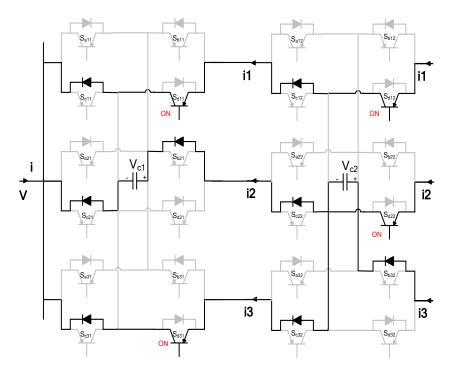

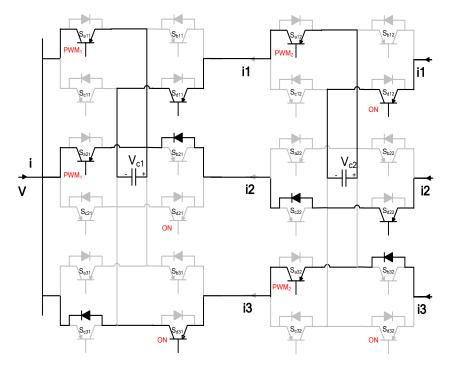

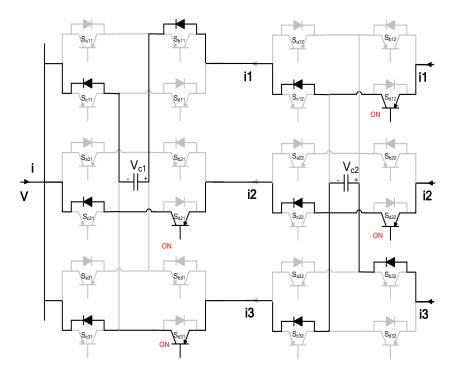

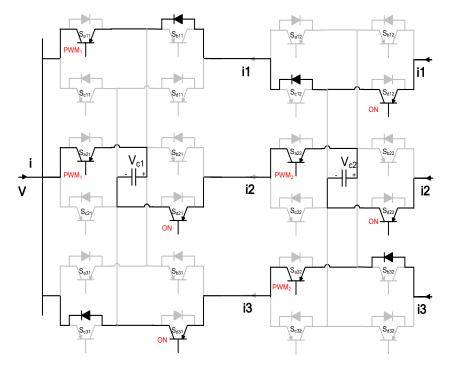

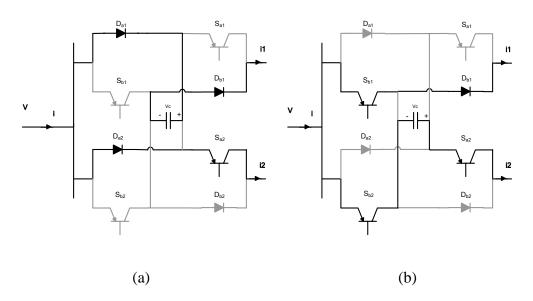

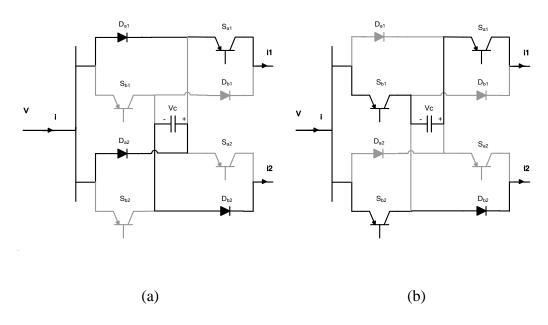

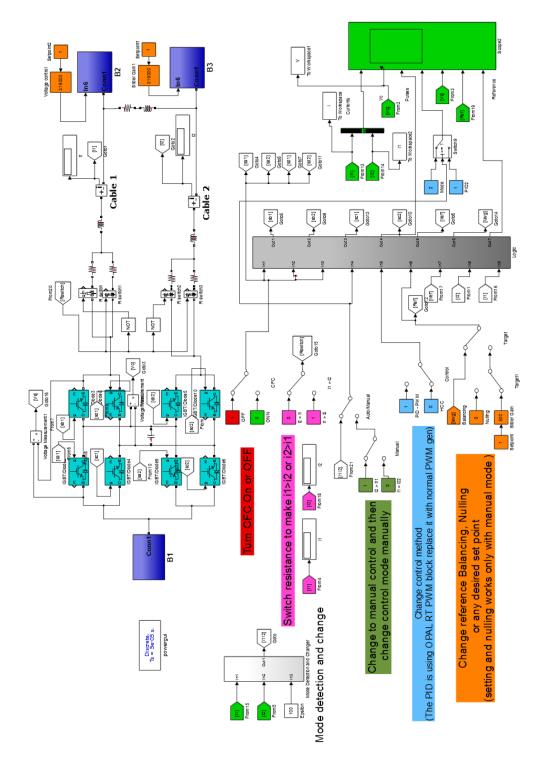

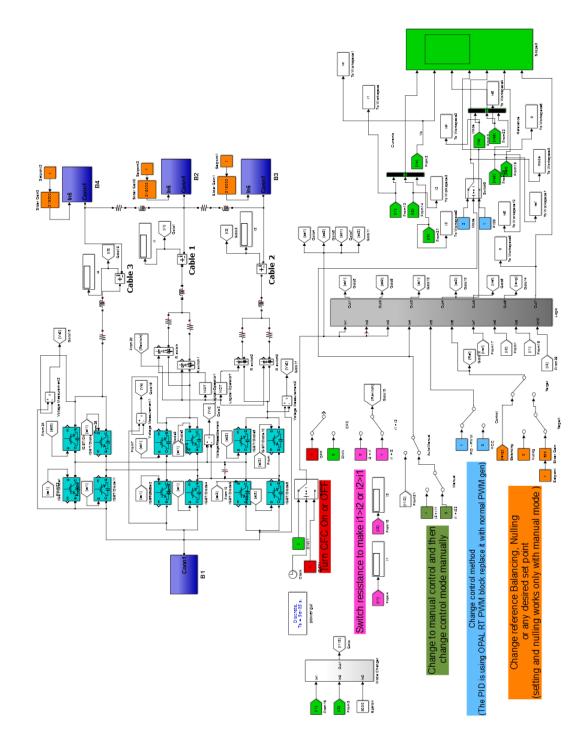

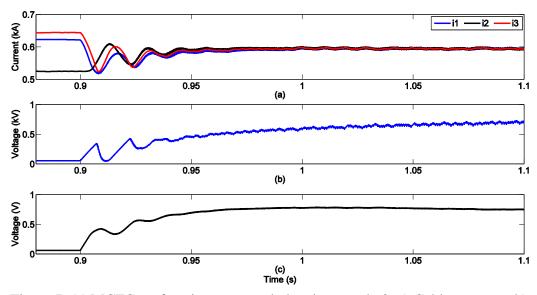

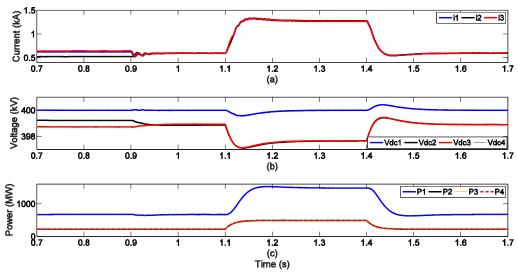

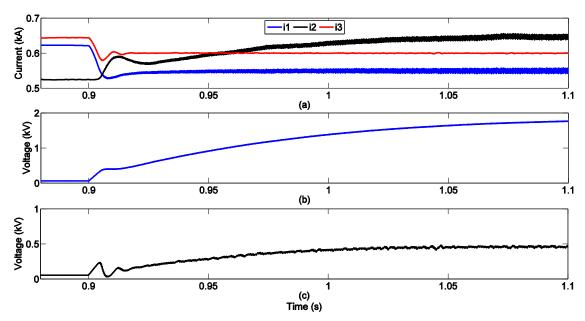

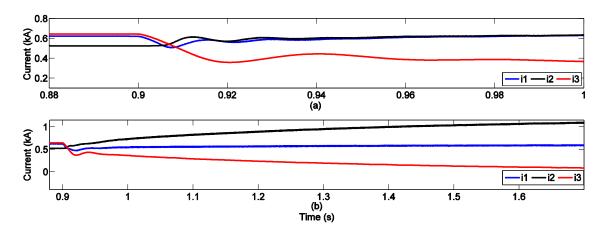

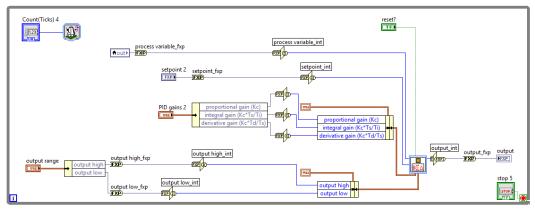

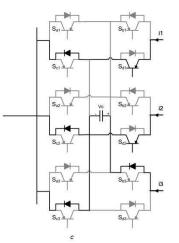

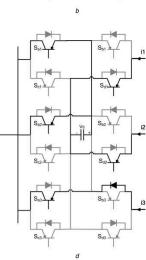

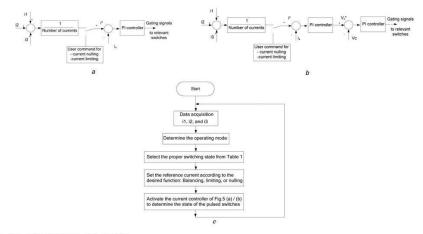

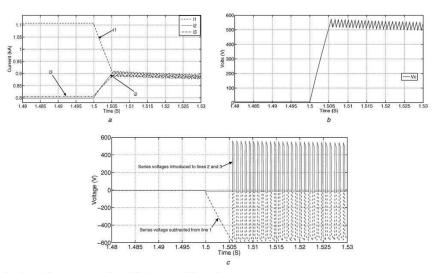

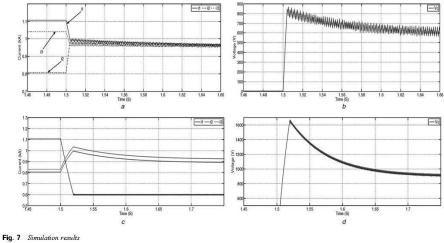

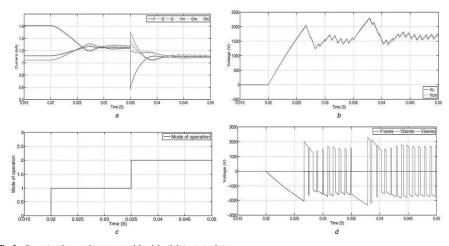

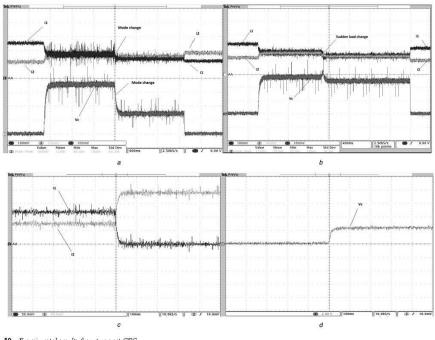

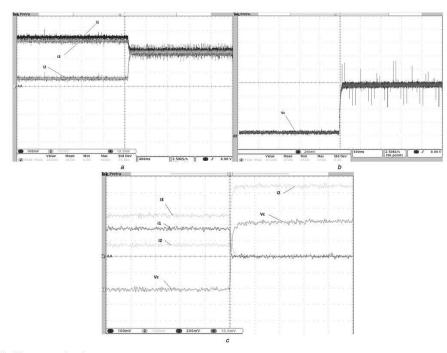

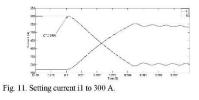

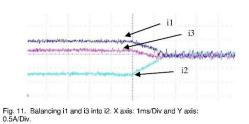

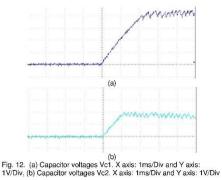

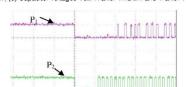

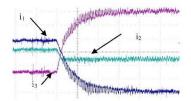

### 2.4.1.2 Bipolar connections