# Sputtered ZnO Thin-Film Transistors With Carrier Mobility Over 50 cm<sup>2</sup>/Vs

Christian Brox-Nilsen, Jidong Jin, Yi Luo, Peng Bao, and Aimin M. Song, Senior Member, IEEE

Abstract—Polycrystalline zinc oxide (ZnO) thin-film transistors with a  $Ta_2O_5$  high-k gate dielectric layer are fabricated by radio-frequency magnetron sputtering at room temperature. Under the optimal deposition conditions, the devices show saturation mobility values over  $50~\text{cm}^2/\text{Vs}$ , an ON/OFF ratio of  $> 10^5$ , and a subthreshold voltage swing of 0.29 V/decade at a low operating voltage of 4 V. This is, to the best of our knowledge, one of the highest field-effect mobility values achieved in ZnO-based thin-film transistors by room-temperature sputtering. The stability of the devices is also examined and the sensitive dependence of the carrier mobility on the deposition conditions is discussed.

Index Terms—High mobility, radio frequency (RF) sputtering, room temperature, thin-film transistor (TFT), zinc oxide (ZnO).

## I. Introduction

**▼** OMMONLY used semiconductors in thin-film transistors (TFTs) for flat-panel displays include polycrystalline silicon (poly-Si) and hydrogenated amorphous silicon (a-Si:H) [1]-[4]. Poly-Si films can have field-effect carrier mobility values between 50 and 100 cm<sup>2</sup>/Vs, but their opacity and nonuniform spatial distribution of grain structures are not ideal for use in large-area displays [2], [5]. On the other hand, a-Si:H TFTs are light sensitive and usually have a mobility < 1 cm<sup>2</sup>/Vs [2], [3], [5], [6]. Relatively high temperatures are also required in a-Si:H and poly-Si processing, making it difficult to incorporate them onto many plastic materials [1], [2], [6]. A promising material system for flat-panel display drivers as well as low cost transparent electronics is metal oxides. Among them, zinc oxide (ZnO) has been studied intensively as a transparent conductor and more recently also as a semiconductor [7]–[9]. Its wide bandgap ( $\sim 3.37$  eV) makes it transparent and high-quality ZnO films have been shown to be insensitive to visible light [5]. Carrier mobility as high as 110 cm<sup>2</sup>/Vs has been reported where ZnO was grown by pulsed-laser deposition with a substrate temperature of 350 °C [10]. ZnO can also be fabricated conveniently at room

Manuscript received May 29, 2013; revised July 23, 2013 and August 16, 2013; accepted August 19, 2013. Date of publication September 6, 2013; date of current version September 18, 2013. This work was supported in part by NanoePrint and in part by an EPSRC KTA project. The review of this paper was arranged by Editor J. Huang.

C. Brox-Nilsen, J. Jin, P. Bao, and A. Song are with the School of Electrical and Electronic Engineering, University of Manchester, Manchester M13 9PL, U.K. (e-mail: broxnilsen@yahoo.com; jinjidong@126.com; p.bao@leeds.ac.uk; a.song@manchester.ac.uk).

Y. Luo is with the NanoePrint, Core Technology Facility, Manchester M13 9NT, U.K. (e-mail: yiluo@sdu.edu.cn).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2013.2279401

temperature, which is highly desirable for flexible electronics on plastic substrates.

ZnO typically exhibits *n*-type carrier conduction even if it is unintentionally doped [4], [11], [12]. The origin of the *n*-type conduction has been under debate [13]–[19]. It was initially believed that the conduction was caused by native defects, such as oxygen vacancies or zinc interstitials. However, recent theoretical research indicated that oxygen vacancies should actually be deep donors and they could not be responsible for the *n*-type conduction. Some studies suggested that unintentional impurities, particularly hydrogen which is present in most growth and characterization environments, may act as shallow donors in ZnO [13]–[17]. It was also argued that zinc interstitials may act as donors in the form of complexes rather than as isolated defects [18], [19].

The choice of suitable gate dielectric materials in ZnO TFTs is often very critical in determining the actual device performance, such as the carrier mobility and threshold voltage. Kang et al. [20] fabricated ZnO TFTs with a Ba<sub>0.6</sub>Sr<sub>0.4</sub>TiO<sub>3</sub> (dielectric constant  $\varepsilon_r = 22$ ) gate insulator doped with Mg (3%), which resulted in a low operating voltage < 6 V and a carrier mobility of 16.3 cm<sup>2</sup>/Vs. Carcia et al. [21] fabricated ZnO TFTs with various gate insulators (HfO<sub>2</sub>, HfSiO<sub>x</sub>, and Al<sub>2</sub>O<sub>3</sub>) grown by atomic layer deposition (ALD), and the highest mobility value achieved was 17.6 cm<sup>2</sup>/Vs with Al<sub>2</sub>O<sub>3</sub> as the gate insulator. Fortunato et al. [3] explored a superlattice of alternating Al<sub>2</sub>O<sub>3</sub> and TiO<sub>2</sub> (ATO) gate insulators grown by ALD. The effective dielectric constant of the ATO superlattice was 16 and the TFTs showed a mobility of 27 cm<sup>2</sup>/Vs. Zhang et al. [22] used Ta<sub>2</sub>O<sub>5</sub> gate insulators and demonstrated a high carrier mobility reaching 60.4 cm<sup>2</sup>/Vs in ZnO TFTs fabricated by radio-frequency (RF) magnetron sputtering. Fortunato et al. [23] also studied ZnO TFTs with  $SiO_xN_y$  gate insulators by RF magnetron sputtering to reduce gate leakage, and a carrier mobility of 70 cm<sup>2</sup>/Vs was achieved.

In this paper, we use room-temperature RF magnetron sputtering to deposit both ZnO and  $Ta_2O_5$  gate insulator, and the experiments show that the device performance depends sensitively on the deposition conditions. Carrier mobility values over  $50~\text{cm}^2/\text{Vs}$  and a low operating voltage of 4 V are achieved under the optimum conditions in a number of devices. The best device exhibits a carrier mobility even reaching  $103~\text{cm}^2/\text{Vs}$ .

## II. EXPERIMENT

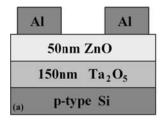

The cross section and top view of the ZnO TFTs are shown in Fig. 1.  $Ta_2O_5$  was chosen because of its high dielectric

Fig. 1. (a) Cross section and (b) top view of the ZnO TFTs.

constant, usually in the range of 18-35 depending on the processing conditions [24]. A p-type silicon wafer was used as both the substrate and bottom gate electrode. The wafer was first cleaned with organic solvents in an ultrasonic bath and then exposed in an UV/ozone cleaner. The Ta<sub>2</sub>O<sub>5</sub> gate insulator and ZnO layer were then deposited at room temperature in a sputtering system that has two magnetrons connected to a 13.56-MHz RF to a power supply. Both targets were purchased from Kurt J. Lesker. The Ta<sub>2</sub>O<sub>5</sub> target had a purity of 99.995%, whereas the ZnO target had a purity of 99.999%. In our experiments, we have tried to optimize a number of fabrication parameters, mainly including argon/oxygen ratio, chamber pressure, RF power, and sample to target distance. The optimal conditions were as follows. The Ta<sub>2</sub>O<sub>5</sub> sputtering was carried out in a mixed atmosphere of argon and oxygen with gas input flow rates of 9 and 3 sccm, respectively, and a chamber pressure of  $13 \times 10^{-3}$  mbar. The target to sample distance for both Ta<sub>2</sub>O<sub>5</sub> and ZnO depositions was 7.5 cm and the RF sputtering input power was 50 W. Before depositing the Ta<sub>2</sub>O<sub>5</sub> layer, the chamber was pumped down to a base pressure of  $3 \times 10^{-6}$  mbar. The deposition time for Ta<sub>2</sub>O<sub>5</sub> was 90 min, which produced a layer thickness of  $\sim$ 150 nm. After Ta<sub>2</sub>O<sub>5</sub> deposition, ZnO was deposited in an argon only atmosphere with an input flow rate of 22 sccm and a chamber pressure of  $29 \times 10^{-3}$  mbar. A deposition time of 20 min produced a  $\sim$ 50-nm-thick ZnO layer. Finally, the source (S) and drain (D) electrodes were fabricated by evaporating Al through a shadow mask, which defined a TFT channel width (W) of 2000  $\mu$ m and a channel length (L) of 60  $\mu$ m as shown in Fig. 1(b). Although other contact materials such as Ti [7] or ITO [8], [12] can be used for ohmic contacts, another commonly used metal, Al, was used here due to the low cost and ease of processing.

In addition, we have carried on the uniformity, stability, and reproducibility studies of the ZnO transistors. There were 6–9 TFTs on each chip and every TFT was tested individually. Five different chips were produced under each set of sputtering deposition condition to test the reproducibility. Some of the devices were also measured for stability tests after one, seven, and 12 days.

# III. RESULTS

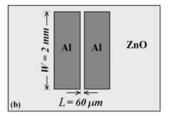

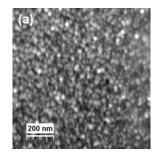

$Ta_2O_5$  layers were fabricated separately for imaging with an atomic force microscope (AFM). A typical micrograph is shown in Fig. 2(a), and an rms roughness of 0.7 nm was obtained. The ZnO morphology was examined using the actual TFTs. The rms roughness was 3 nm, and the AFM image in Fig. 2(b) also shows a range of ZnO grain sizes.

Fig. 2. (a) AFM image of the  $Ta_2O_5$  surface with an rms roughness of 0.7 nm. (b) AFM image of the ZnO surface with an rms roughness of 3 nm.

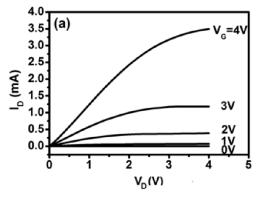

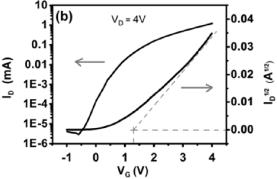

Fig. 3. (a) Output and (b) transfer characteristics of an as-sputtered ZnO TFT. Square root of drain current and a linear fit (dashed line) are also shown in (b).

The capacitance of the as-sputtered Ta<sub>2</sub>O<sub>5</sub> dielectric (without ZnO layer) was measured with an Agilent E4980A Precision LCR meter at 1 kHz. The obtained value was 120 nF/cm<sup>2</sup>. With the thickness of the Ta<sub>2</sub>O<sub>5</sub> film determined by the AFM imaging, the dielectric constant was calculated to be 20.2, comparable with the reported values of RF sputtered Ta<sub>2</sub>O<sub>5</sub> [24]. The output and transfer characteristics of the assputtered ZnO TFTs were measured with an Agilent E5270B Precision Measurement Mainframe.

Most devices showed mobility values > 60 cm<sup>2</sup>/Vs and the best results are shown in Fig. 3. The threshold voltage and saturation field-effect mobility ( $\mu_{\rm sat}$ ) were calculated by fitting a straight line to the plot of the square root of the drain current ( $I_{\rm DS}$ ) versus the gate voltage ( $V_{\rm GS}$ ) according to (1), where  $C_i$  is the capacitance/unit area for the Ta<sub>2</sub>O<sub>5</sub> gate insulator

$$I_{\rm DS} = \frac{C_i \mu W}{2L} (V_{\rm GS} - V_{\rm th})^2 \text{ for } V_{\rm DS} > V_{\rm GS} - V_{\rm th}.$$

(1)

| Channel | Mobility<br>(cm <sup>2</sup> /Vs) | V <sub>th</sub> (V) | On/off ratio              | On Current (mA) | Off current (nA) | SS<br>(V/Dec) | Hysteresis (V) |

|---------|-----------------------------------|---------------------|---------------------------|-----------------|------------------|---------------|----------------|

| 1       | 86                                | 1.1                 | 8×10 <sup>4</sup>         | 0.8             | 10               | 0.30          | 0.45           |

| 2       | 66                                | 0.96                | 2×10 <sup>5</sup>         | 0.99            | 4.9              | 0.28          | 0.24           |

| 3       | 73                                | 0.77                | 1.1×10 <sup>5</sup>       | 1.3             | 9.0              | 0.31          | 0.22           |

| 4       | 82                                | 1.0                 | 4.1×10 <sup>5</sup>       | 1.1             | 2.7              | 0.26          | 0.1            |

| 5       | 100                               | 1.0                 | 1.7×10 <sup>5</sup>       | 1.2             | 7.2              | 0.33          | 0.6            |

| 6       | 68                                | 1.2                 | 2.4×10 <sup>5</sup>       | 0.84            | 3.5              | 0.29          | 0.5            |

| 7       | 86                                | 0.92                | 1.7×10 <sup>5</sup>       | 1.4             | 8.4              | 0.34          | 0.26           |

| 8       | 87                                | 1.2                 | 2.7×10 <sup>5</sup>       | 1.1             | 3.7              | 0.30          | 0.45           |

| 9       | 70                                | 1.6                 | 3.4×10 <sup>5</sup>       | 0.67            | 2.0              | 0.26          | 0.6            |

| mean    | 80±11                             | 1.1±0.3             | (2.2±1.1)×10 <sup>5</sup> | 0.93±0.36       | (5.7±0.3)        | 0.30±0.03     | 0.4±0.2        |

$\label{eq:table_interpolation} TABLE\ I$  Uniformity of Sputtered ZnO TFTs

TABLE II

REPEATABILITY OF SPUTTERED ZnO TFTs FROM FIVE DIFFERENT EXPERIMENTS

| Sample | Mobility<br>(cm <sup>2</sup> /Vs) | V <sub>th</sub> (V) | On/off ratio            | On Current (mA) | Off current (nA) | SS<br>(V/Dec) | Hysteresis<br>(V) |

|--------|-----------------------------------|---------------------|-------------------------|-----------------|------------------|---------------|-------------------|

| HKD26  | 80±11                             | 1.1±0.3             | $(2.2\pm1.1)\times10^5$ | 0.93±0.36       | 5.7±0.3          | 0.30±0.03     | 0.4±0.2           |

| HKD27  | 57±9                              | 1.5±0.2             | $(1.7\pm0.8)\times10^5$ | 0.6±0.2         | 3.5±1.6          | 0.28±0.06     | 0.7±0.1           |

| HKD28  | 55±23                             | 1.5±0.3             | $(3.0\pm3.8)\times10^5$ | 0.5±0.3         | 73±120           | 0.3±0.2       | 0.4±0.2           |

| HKD29  | 65±12                             | 1.2±0.1             | $(3.1\pm1.3)\times10^5$ | 0.95±0.20       | 3.4±1.0          | 0.3±0.07      | 1.1±0.1           |

| HKD31  | 52±29                             | 1.3±0.8             | $(2.0\pm1.2)\times10^5$ | 1.0±0.9         | 4.7±3.5          | 0.30±0.05     | 1.2±0.1           |

The obtained highest saturation mobility was  $103 \text{ cm}^2/\text{Vs}$ . Due to the large W/L ratio ( $\sim 33.3$ ), we did not consider the fringe effects that may affect the mobility evaluation according to literature [25], [26]. A low operating voltage of 4 V was demonstrated with a  $V_{\text{th}}$  of 1.3 V. A high ON/OFF ratio of  $4.1 \times 10^5$  was also achieved. The subthreshold voltage swing (S), defined as the gate voltage needed to increase the subthreshold  $I_{\text{DS}}$  by one decade, is calculated by (2)

$$S = \frac{dV_{\text{GS}}}{d(\log I_{\text{DS}})} \tag{2}$$

where S was estimated from the transfer characteristics to be 0.29 V/decade. This relatively low value was mostly due to the high gate-dielectric capacitance. From S, we can deduce the maximum density of surface states at the semiconductor/dielectric interface as

$$N_{\rm it} = \left[\frac{S\log(e)}{(kT/q)} - 1\right] \frac{C_i}{q}.\tag{3}$$

From the subthreshold value and the unit area capacitance of the  $Ta_2O_5$  layer, we extracted the maximum trap density at the semiconductor/dielectric interface of  $\sim 2.90 \times 10^{12}$  cm<sup>-2</sup>. This is comparable with the value reported in [22].

Due the relatively smooth and uniform  $Ta_2O_5$  and ZnO layers, the fabricated ZnO TFTs showed fairly good uniformity and reproducibility. Table I shows the performance of all nine working ZnO TFT devices in a different sample from that in Fig. 3. The standard deviation of mobility was 11 cm<sup>2</sup>/Vs or  $\pm$  13% with a mean value of 80 cm<sup>2</sup>/Vs. Other parameters of performance, such as threshold voltage, ON/OFF ratio, and subthreshold voltage swing, also showed rather small standard

deviations. Table II shows the performance of five samples that were fabricated with the same deposition condition during a one-month period. In general, all these five samples showed quite similar performance, the mean mobility value was in the range between 52 to 80 cm<sup>2</sup>/Vs. In addition, the values of threshold voltage, ON/OFF ratio, and subthreshold voltage swings were very close for all five devices.

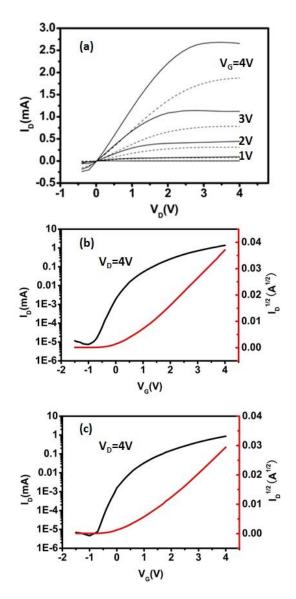

For a sample shelf-life test the characteristics of some ZnO TFTs were first measured soon after the fabrication and then tested again after 12-day storage under ambient conditions. The solid lines in Fig. 4(a) are the results of the as-fabricated device, and the dashed lines are of the device after 12 days.

Without any intentional encapsulations, the device ON-current was reduced from 2.7 to 1.9 mA, but the device still showed a mobility over 50 cm<sup>2</sup>/Vs. The OFF-current, measured under the same conditions, decreased from 8.9 to 5.0 nA, resulting in a slight increase in the ON/OFF ratio from  $2.8 \times 10^5$  to  $4 \times 10^5$ . In addition, the threshold voltage increased from 0.5 to 0.8 V over the 12-day period while the subthreshold voltage swing remained quite stable at  $\sim$ 0.25 V/decade. It can be expected that the device lifetime can be significantly extended by encapsulation as shall be the case in real applications.

The carrier mobility values obtained so far are the field-effect mobility in the saturation region, since it directly relates to the practical device performance of TFTs in most circuit applications. Through plotting the total resistance between source and drain contacts as a function of gate voltage in the linear regime, useful information can be obtained on the contact resistance and mobility at low source-drain voltages. Assuming a gate-voltage-independent contact resistance, the

Fig. 4. (a) Characteristics of ZnO TFTs measured soon after the fabrication (solid lines) and after 12 days storage in air (dashed lines). Transfer characteristics of as-fabricated device (b) after 12 days and (c) square root of drain current.

obtained mobility in the linear regime of the as-fabricated device in Fig. 4 showed a gate-voltage dependence and varied from 26 cm²/Vs at low gate voltages to  $\sim\!50$  cm²/Vs at high gate voltages. This is similar to the gate-voltage dependence of the saturation mobility. The obtained contact resistance is  $\sim\!1.1$  k $\Omega$  for each contact. The contact resistance clearly played a more significant role in high-mobility devices at high gate voltages than in low-performance devices or at lower gate voltages.

## IV. DISCUSSION

The obtained mobility is, to the best of our knowledge, one of the highest values in sputtered ZnO TFTs [22]. The high mobility might be due to a few factors. First, a low RF power as well as a relatively high argon pressure  $(29 \times 10^{-3} \text{ mbar})$  was chosen for our ZnO film deposition.

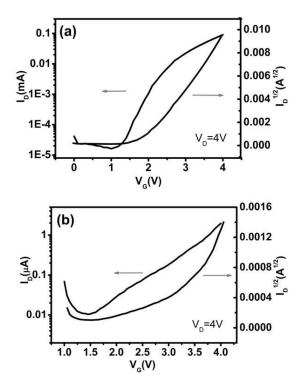

Fig. 5. Transfer characteristics of sputtered ZnO TFT with different oxygen/argon ratios during the sputtering deposition (a) 2.5% and (b) 5%.

This was to reduce the energy of the atoms in the chamber by increasing the number of collisions between gas molecules and thus minimize their damaging bombardment on the  $Ta_2O_5$  dielectric initially and then on the grown ZnO layer, as discussed in [11] and [27]. It was also argued that ZnO TFTs could have a lower stress and better transistor properties for the same reason. Higher stress may increase the number of defects in the active ZnO layer, with a negative effect on the carrier transport and mobility [11]. We also fabricated ZnO films directly on  $Si/SiO_2$  substrate, and the obtained carrier mobility was  $<10~cm^2/Vs$ , showing the critical importance of the gate-dielectric interface.

Furthermore, unlike in the  $Ta_2O_5$  deposition, where a mixture of argon and oxygen was used, our best ZnO layers were deposited in a pure argon atmosphere. We also experimented in mixed argon and oxygen atmospheres for ZnO deposition, where the oxygen flow rate was 2.5% or 5%. As shown in Fig. 5, the performance of ZnO transistor was very significantly affected by the argon/oxygen ratio during sputtering. When a very small amount oxygen (2.5%) flow was introduced, the ON-current was dropped by over one order of magnitude compared with the deposition in pure argon (e.g., in Fig. 3), while the mobility of device was reduced to  $\sim 10 \text{ cm}^2/\text{Vs}$ .

When the oxygen ratio was increased to 5%, the ON-current was further decreased by about two orders of magnitude while the mobility became <1 cm<sup>2</sup>/Vs. Carcia *et al.* [11] also reported on a reduction of mobility when the partial oxygen pressure was increased. They found that the mobile carrier density was decreased at higher oxygen partial pressures,

which would reduce the screening ability of the carriers and result in an increase in the barrier height between ZnO grains and hence a lower mobility. Very recently, Wong *et al.* [28] have reported on a decrease in mobility as the amount of oxygen increased during the growth of gallium-doped ZnO films by pulsed laser deposition. They attributed the reduction of mobility not only to the induced oxygen interstitials, but also to an apparently increased disorder of ZnO crystal grains. The latter resulted in a loss of in-plane alignment of the grains and hence caused more grain boundary scattering in the ZnO film. In addition, the ZnO grain sizes in our samples were relatively large. The effective channel mobility might therefore have been less affected by the grain boundaries.

### V. Conclusion

In conclusion, we have fabricated ZnO TFTs with a  ${\rm Ta_2O_5}$  high-k dielectric by RF magnetron sputtering at room temperature and achieved a saturation mobility as high as 103 cm²/Vs in the best device at a low operating voltage of 4 V. High ON/OFF ratios and low subthreshold swing were also demonstrated. Because the devices were fabricated at room temperature, it is possible to carry out the same film deposition on plastic substrates for practical applications.

### REFERENCES

- [1] J. Nishii, F. M. Hossain, S. Takagi, T. Aita, K. Saikusa, Y. Ohmaki, I. Ohkubo, S. Kishimoto, A. Ohtomo, T. Fukumura, F. Matsukura, Y. Ohno, H. Koinuma, H. Ohno, and M. Kawasaki, "High mobility thin film transistors with transparent ZnO channels," *Jpn. Appl. Phys.*, vol. 42, no. 4A, pp. L347–L349, Apr. 2003.

- [2] E. Fortunato, P. Barquinha, A. Pimentel, A. Gonçalves, A. Marques, L. Pereira, and R. Martins, "Recent advances in ZnO transparent thin film transistors," *Thin Solid Films*, vol. 487, nos. 1–2, pp. 205–211, Sep. 2005.

- [3] E. M. C. Fortunato, P. M. C. Barquinha, A. C. M. B. G. Pimentel, A. M. F. Goncalves, A. J. S. Marques, R. F. P. Martins, and L. M. N. Pereira, "Wide-bandgap high-mobility ZnO thin-film transistors produced at room temperature," *Appl. Phys. Lett.*, vol. 85, no. 13, pp. 2541–2543, Sep. 2004.

- [4] S. Masuda, K. Kitamura, Y. Okumura, S. Miyatake, H. Tabata, and T. Kawai, "Transparent thin film transistors using ZnO as an active channel layer and their electrical properties," *J. Appl. Phys.*, vol. 93, no. 3, pp. 1624–1630, Feb. 2003.

- [5] R. B. M. Cross and M. M. De Souza, "Investigating the stability of zinc oxide thin film transistors," *Appl. Phys. Lett.*, vol. 89, no. 26, pp. 263513-1–263513-3, Dec. 2006.

- [6] K. Long, A. Z. Kattamis, I.-C. Cheng, H. Gleskova, S. Wagner, and J. C. Sturm, "Stability of amorphous-silicon TFTs deposited on clear plastic substrates at 250 °C to 280 °C," *IEEE Electron Device Lett.*, vol. 27, no. 2, pp. 111–113, Feb. 2006.

- [7] U. Ozgur, Y. I. Alivov, C. Liu, A. Teke, M. A. Reshchikov, S. Dogan, V. Avrutin, S.-J. Cho, and H. Morkoc, "A comprehensive review of ZnO materials and devices," *J. Appl. Phys.*, vol. 98, no. 4, pp. 041301-1–041301-103, Aug. 2005.

- [8] R. L. Hoffman, B. J. Norris, and J. F. Wager, "ZnO-based transparent thin-film transistors," *Appl. Phys. Lett.*, vol. 82, no. 5, pp. 733-735, Feb. 2003.

- [9] T. Minami, "Present status of transparent conducting oxide thin-film development for indium-tin-oxide (ITO) substitutes," *Thin Solid Films*, vol. 516, no. 17, pp. 5822–5828, Jul. 2008.

- [10] B. Bayraktaroglu, K. Leedy, and R. Neidhard, "Microwave ZnO thin-film transistors," *IEEE Electron Device Lett.*, vol. 29, no. 9, pp. 1024–1026, Sep. 2008.

- [11] P. F. Carcia, R. S. McLean, M. H. Reilly, and G. Nunes, "Transparent ZnO thin-film transistor fabricated by RF magnetron sputtering," *Appl. Phys. Lett.*, vol. 82, no. 7, pp. 1117–1119, Feb. 2003.

- [12] C. C. Liu, M. L. Wu, K. C. Liu, S.-H. Hsiao, Y. S. Chen, G.-R. Lin, and J. Huang, "Transparent ZnO thin-film transistors on glass and plastic substrates using post-sputtering oxygen passivation," *J. Display Technol.*, vol. 5, no. 6, pp. 192–197, Jun. 2009.

- [13] C. G. Van de Walle, "Hydrogen as a cause of doping in zinc oxide," Phys. Rev. Lett., vol. 85, no. 5, pp. 1012–1015, Jul. 2000.

- [14] C. G. Van de Walle, "Defect analysis and engineering in ZnO," Phys. B, Phys. Condensed Matter, vols. 308–310, pp. 899–903, Dec. 2001.

- [15] A. Janotti and C. G. Van de Walle, "Native point defects in ZnO," *Phys. Rev. B*, vol. 76, no. 16, pp. 165202-1–165202-22, Oct. 2007.

- [16] A. Janotti and C. G. Van de Walle, "New insights into the role of native point defects in ZnO," *J. Crystal Growth*, vol. 287, no. 1, pp. 58–65, Jan. 2006.

- [17] A. Janotti and C. G. Van de Walle, "Fundamentals of zinc oxide as a semiconductor," Rep. Progr. Phys., vol. 72, no. 12. p. 126501, Dec. 2009.

- [18] D. C. Look, "Progress in ZnO materials and devices," J. Electron. Mater., vol. 35, no. 6. pp. 1299–1305, Jun. 2006.

- [19] D. C. Look, G. C. Farlow, P. Reunchan, S. Limpijumnong, S. B. Zhang, and K. Nordlund, "Evidence for native-defect donors in n-type ZnO," *Phys. Rev. Lett.*, vol. 95, no. 22, pp. 225502-1–225502-4, Nov. 2005.

- [20] K. Kang, M.-H. Lim, H.-G. Kim, I.-D. Kim, and J.-M. Hong, "High field-effect mobility ZnO thin-film transistors with Mg-doped Ba<sub>0.6</sub>Sr<sub>0.4</sub>TiO<sub>3</sub> gate insulator on plastic substrates," *Appl. Phys. Lett.*, vol. 90, no. 4, pp. 043502-1–043502-3, Jan. 2007.

- [21] P. F. Carcia, R. S. McLean, and M. H. Reilly, "High-performance ZnO thin-film transistors on gate dielectrics grown by atomic layer deposition," *Appl. Phys. Lett.*, vol. 88, no. 12, pp. 123509-1–123509-3, Mar. 2006.

- [22] L. Zhang, J. Li, X. W. Zhang, X. Y. Jiang, and Z. L. Zhang, "High performance ZnO-thin-film transistor with Ta<sub>2</sub>O<sub>5</sub> dielectrics fabricated at room temperature," *Appl. Phys. Lett.*, vol. 95, no. 7, pp. 072112-1–072112-3, Aug. 2009.

- [23] E. Fortunato, A. Pimentel, L. Pereira, A. Gonçalves, G. Lavareda, H. Águas, I. Ferreira, C. N. Carvalho, and R. Martins, "High field-effect mobility zinc oxide thin film transistors produced at room temperature," J. Non-Crystalline Solids, vols. 338–340, pp. 806–809, Jun. 2004.

- [24] S. Ezhilvalavan and T. Y. Tseng, "Preparation and properties of tantalum pentoxide (Ta<sub>2</sub>O<sub>5</sub>) thin films for ultra large scale integrated circuits (ULSIs) application—A review," *J. Mater. Sci., Mater. Electron.*, vol. 10, no. 1, pp. 9–31, Mar. 1999.

- [25] K. Okamura, D. Nikolova, N. Mechau, and H. Hahn, "Appropriate choice of channel ratio in thin-film transistors for the exact determination of field-effect mobility," *Appl. Phys. Lett.*, vol. 94, no. 7, pp. 183503-1–183503-3, May 2009.

- [26] K. Okamura and H. Hahn, "Potential distribution in channel of thin-film transistors," Appl. Phys. Lett., vol. 101, no. 1, pp. 013504-1-013504-5, Jul. 2012.

- [27] K. Tominaga, S. Iwamura, I. Fujita, Y. Shintani, and O. Tada, "Influence of bombardment by energetic atoms on c-axis orientation of ZnO films," *Jpn. J. Appl. Phys.*, vol. 21, no. 7, pp. 999–1002, Jul. 1982.

- [28] L. M. Wong, S. Y. Chiam, J. Q. Huang, S. J. Wang, J. S. Pan, and W. K. Chim, "Role of oxygen for highly conducting and transparent gallium-doped zinc oxide electrode deposited at room temperature," *Appl. Phys. Lett.*, vol. 98, no. 2, pp. 022106-1–022106-3, Jan. 2011.

**Christian Brox-Nilsen** received the Ph.D. degree in electrical and electronic engineering from the University of Manchester, Manchester, U.K., in 2010.

He is currently an Engineer of thin film electronics ASA, Solli Oslo, Sweden.

**Jidong Jin** received the Ph.D. degree in electrical and electronic engineering from the University of Manchester, Manchester, U.K., in 2013.

His current research interests include metal-oxide-based electronic devices, flexible electronics, and displays.

Yi Luo received the Ph.D. degree in physics from the University of Nottingham, Nottingham, U.K., in 2005.

He is currently a Professor with the School of Physics, Shandong University, Jinan, China.

**Peng Bao** received the Ph.D. degree in physics from Nanjing University, Nanjing, China, in 2004.

He is currently a Research Associate with the School of Physics and Astronomy, University of Leeds, Leeds, U.K.

**Aimin M. Song** (M'02–SM'07) received the Ph.D. degree in physics from the China Academy of Science, Beijing, China, in 1995.

He has been a Professor of nanoelectronics with the School of Electrical and Electronic Engineering, University of Manchester, Manchester, U.K., since 2006.