## Design of Ultra Low Power Analog-to-Digital Converter for Ambulatory EEG Recording

by

Dina Reda El-Damak

B.Sc., Ain Shams University (2007) M.Sc., Ain Shams University (2010)

| M | ASSACHUSETTS INSTITUTI<br>OF TECHNOLOGY | Ē |

|---|-----------------------------------------|---|

|   | MAR 2 0 2012                            |   |

|   | LIBRARIES                               |   |

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of **ARCHIVES**

Master of Science in Electrical Engineering and Computer Science

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

### February 2012

© Massachusetts Institute of Technology 2012. All rights reserved.

Author ..... Department of Electrical Engineering and Computer Science December 16, 2011

Certified by...... Anantha P. Chandrakasan Joseph F. and Nancy P. Keithley Professor of Electrical Engineering Thesis Supervisor

Accepted by ...... Leslie A. Kolodziejski Chairman, Department Committee on Graduate Students

## Design of Ultra Low Power Analog-to-Digital Converter for Ambulatory EEG Recording

by

Dina Reda El-Damak

Submitted to the Department of Electrical Engineering and Computer Science on December 16, 2011, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering and Computer Science

#### Abstract

Portable acquisition of biopotential signals requires the design of compact, energy efficient circuits and systems. Such systems typically include analog-to-digital converter for digitizing signals from AFE and feeding it to DBE. An Ultra low power ADC is designed in this work to be integrated within scalable EEG SoC. The full system can capture EEG signals through 1 up to 8 parallel differential channels that are time division multiplexed into a single ADC. The ADC has a fixed resolution of 10 bits which is sufficient for extraction of bio-markers for seizure detection. A SAR ADC architecture is chosen for this design as it is highly energy efficient for medium to high resolution applications with low speed requirements. A differential capacitive DAC is utilized to enhance the CMRR. Concepts of split-capacitor array and sub-DAC are combined to reduce the DAC area and power consumption. Charge pumps are used to boost the control voltage of sampling switches. The ADC performs a conversion every 16 clock cycle while being governed by a self-resetting SAR logic. The sampling rate can be scaled up to 32 kHz by varying the clock frequency to accommodate different number of channels used.

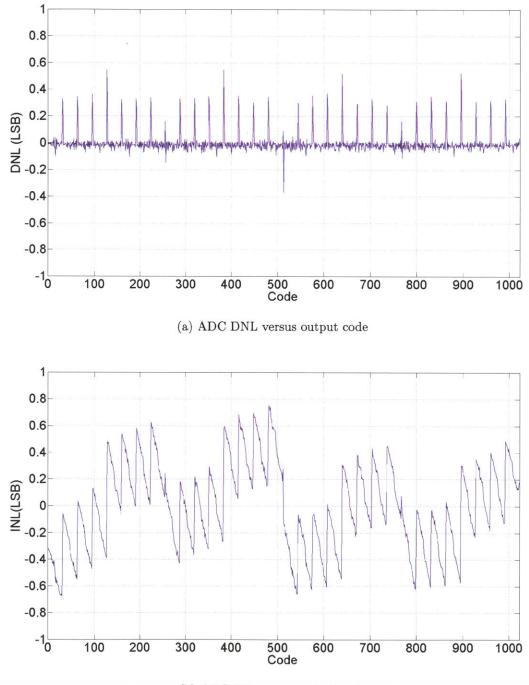

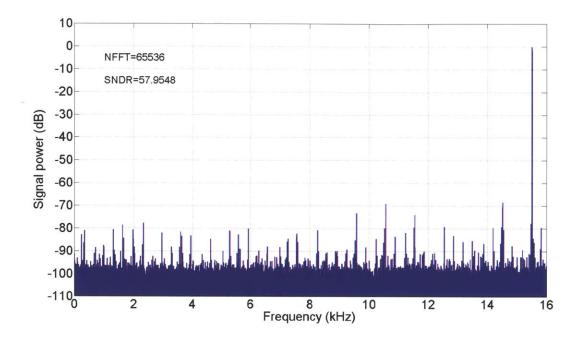

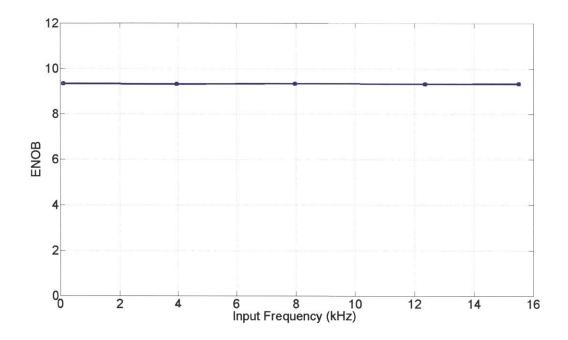

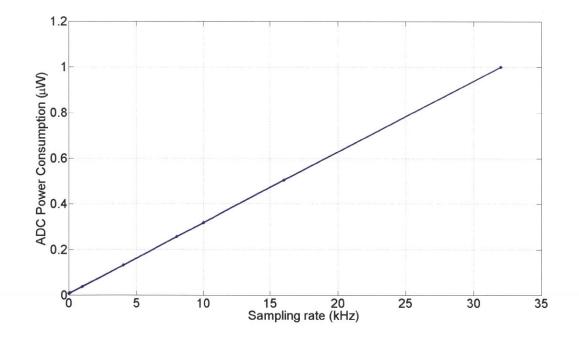

The ADC was designed and fabricated in a 0.18  $\mu$ m CMOS technology. The entire ADC core consumes 1  $\mu$ W from 1 V supply at a sampling rate of 32 kHz. The ADC has a maximum DNL and INL of 0.55 LSB and 0.75 LSB respectively. The SNDR and SFDR of the converter are measured at a sampling rate of 32 kHz and 15.5 kHz input tone to be 57.9 dB and 68.5 dBFS respectively. The ADC FOM is 51 fJ/Conv-Step.

Thesis Supervisor: Anantha P. Chandrakasan Title: Joseph F. and Nancy P. Keithley Professor of Electrical Engineering

## Acknowledgements

First, i would really like to express my deepest gratitude to my advisor Prof. Anantha Chandrakasan for giving me this great opportunity to join his team. I would like to thank him for all his encouragement and support through out the project and for giving a chance to a little girl from the far-end of the world. Being part of his group was one of my greatest dreams and forever i would be indebted.

I am really grateful to Marcus Yip for his great support through out the design and testing phases. Marcus has a very deep understanding of all aspects of SAR ADCs and i am really thankful for all his help.

I would really like to thank Prof. Jerald Yoo and Long Yan for making a great project team. I am really grateful to Prof. Jerald for all his help and support through out the project specially with full system integration and verification.

I would like to thank Patrick Mercier and Marcus Yip for the library of custom standard cells. I would like also to thank all my colleagues in AnanthaGroup for making a wonderful team, i really enjoyed being part of and special thanks to Margret, our administrative assistant, for all her sincere help.

Last but never least, i would really like to thank my parents, my grandmother, my sister Angie and brother-in-law Mohamed for all their encouragement and support. To my parents, i hope you would know that i always feel that i am the luckiest girl on earth to have loving parents like you. You have been always there for me even when we are thousands of miles away. Just listening to supportive words from you makes all the stress and tiredness go away. You are the greatest bless i have in my life and i hope with this thesis i can just draw on your faces a little smile.

.

# Contents

| 1 | $\mathbf{Intr}$ | oducti  | on                                   | 15 |

|---|-----------------|---------|--------------------------------------|----|

|   | 1.1             | System  | n Requirements                       | 16 |

|   |                 | 1.1.1   | Resolution                           | 16 |

|   |                 | 1.1.2   | Sample Rate                          | 16 |

|   |                 | 1.1.3   | Scalability                          | 17 |

|   |                 | 1.1.4   | Input Interface                      | 17 |

|   |                 | 1.1.5   | Conversion Plan                      | 17 |

|   | 1.2             | Archit  | ecture Selection                     | 17 |

|   | 1.3             | Thesis  | Organization                         | 18 |

| 2 | Arc             | hitectu | re and Circuit Design                | 19 |

|   | 2.1             | Succes  | sive Approximation Conversion Basics | 19 |

|   |                 | 2.1.1   | Single-ended SAR ADC                 | 20 |

|   |                 | 2.1.2   | Differential SAR ADC                 | 22 |

|   | 2.2             | Global  | l Architecture                       | 23 |

|   | 2.3             | Capac   | itive DAC                            | 25 |

|   |                 | 2.3.1   | Sub-DAC Interpolation                | 28 |

|   |                 | 2.3.2   | Split Capacitor Array                | 30 |

|   |                 | 2.3.3   | DAC Layout                           | 32 |

|   | 2.4             | Comp    | arator                               | 33 |

|   | 2.5             | Switch  | nes                                  | 35 |

|   |                 | 2.5.1   | Purging Switches                     | 35 |

|   |                 | 2.5.2   | Sampling Switches                    | 37 |

|   |      | 2.5.3 Reference Switches  | 38 |

|---|------|---------------------------|----|

|   | 2.6  | Charge Pump               | 39 |

|   | 2.7  | SAR Control Logic         | 39 |

|   | 2.8  | Summary                   | 45 |

| 3 | Test | ing and Characterization  | 47 |

|   | 3.1  | Test Setup                | 47 |

|   | 3.2  | Characterization          | 50 |

|   |      | 3.2.1 Static Linearity    | 50 |

|   |      | 3.2.2 Dynamic Performance | 52 |

|   |      | 3.2.3 Power Consumption   | 54 |

|   | 3.3  | Summary                   | 56 |

| 4 | Con  | clusions and Future Work  | 59 |

|   | 4.1  | Conclusions               | 59 |

|   | 4.2  | Future Work               | 60 |

| A | Tes  | t Setup                   | 63 |

# List of Figures

| 1-1  | Top-level architecture of biopotential acquisition system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1-2  | ADC architectures comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18 |

| 2-1  | Basic architecture of SAR ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20 |

| 2-2  | Timing diagram of the bit-cycling phase of 4 bit SAR ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21 |

| 2-3  | 4 bit SAR ADC utilizing binary weighted capacitive DAC $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21 |

| 2-4  | Differential 4 bit SAR ADC utilizing binary weighted capacitive DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22 |

| 2-5  | ADC architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24 |

| 2-6  | SAR ADC conversion plan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25 |

| 2-7  | ADC during sampling phase (purging switches are not shown for clarity)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26 |

| 2-8  | ADC during bit-cycling phase of MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26 |

| 2-9  | ADC during bit-cycling phase if MSB=1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27 |

| 2-10 | ADC during bit-cycling phase if MSB=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27 |

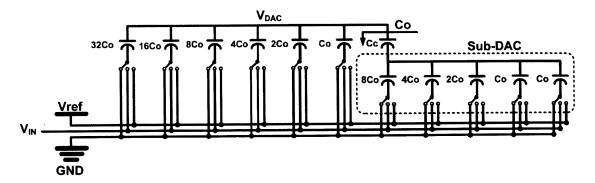

| 2-11 | Binary weighted DAC with 6 bit main-DAC and 4 bit sub-DAC $\ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28 |

| 2-12 | The DAC effective capacitive divider while individually connecting the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | bottom plate of each capacitor in the main-DAC to $V_{\rm ref}$ and the rest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | of capacitors to ground $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29 |

| 2-13 | The<br>venin equivalent circuit for analysing passive sub-DAC $\ . \ . \ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29 |

| 2-14 | Applying split capacitor array technique to 3 bit binary weighted ca-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | pacitive DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30 |

| 2-15 | Step 1 of bit-cycling: Connecting the bottom plates of the MSB array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|      | to $V_{\text{ref}}$ and the rest of the capacitors to ground $\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\$ | 30 |

| 2-16 | Up transition for a split capacitor array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31 |

| 2-17 | Down transition using conventional switching method                                                              | 32 |

|------|------------------------------------------------------------------------------------------------------------------|----|

| 2-18 | Down transition using split capacitor array                                                                      | 32 |

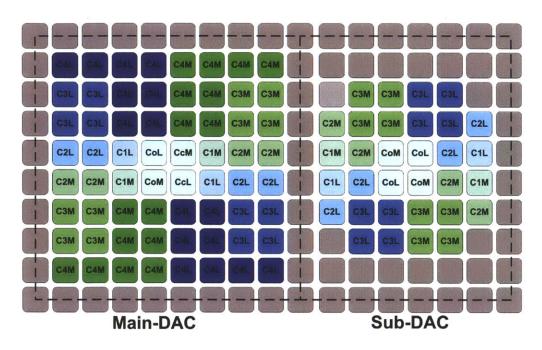

| 2-19 | DAC common-centroid Layout with minimized edge effect                                                            | 33 |

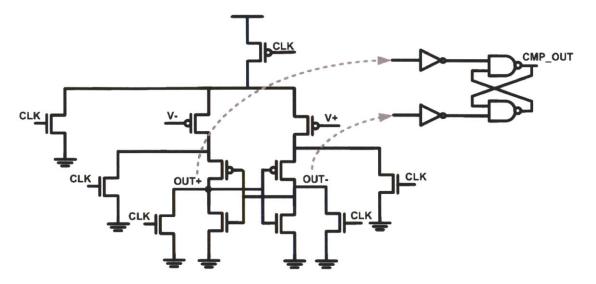

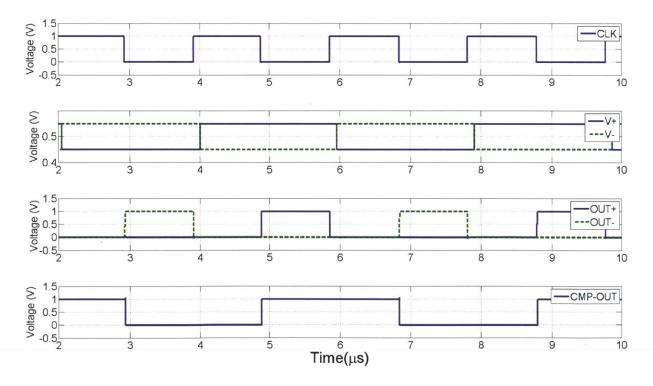

| 2-20 | Schematic of dynamic latched comparator                                                                          | 34 |

| 2-21 | Comparator sample transient waveforms while using 512 kHz Clock $% \mathcal{L}^{2}$ .                            | 34 |

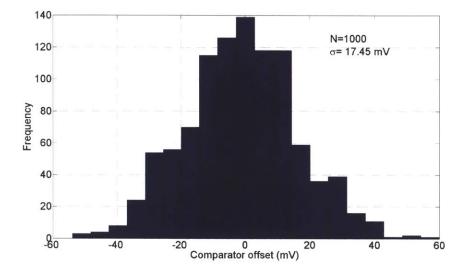

| 2-22 | Histogram of the comparator input refered offset using 1000 monte                                                |    |

|      | carlo iterations                                                                                                 | 35 |

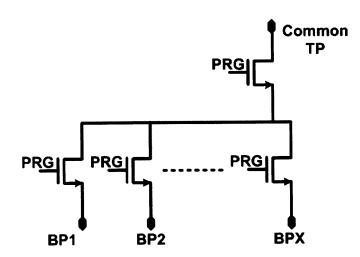

| 2-23 | Switches connected to the bottom plate of each DAC capacitor $\ldots$                                            | 36 |

| 2-24 | Purging switches for array of capacitors with common top plate (TP)                                              | 36 |

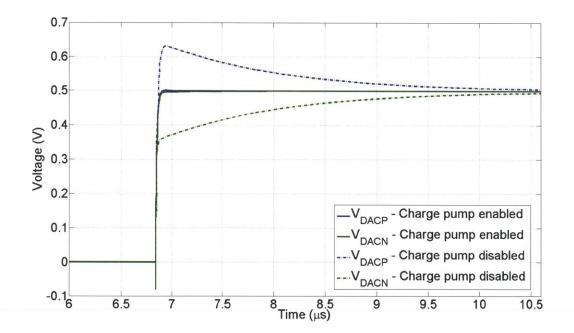

| 2-25 | $\mathrm{V}_{\mathrm{DACP}}$ and $\mathrm{V}_{\mathrm{DACN}}$ while enabling and disabling the charge pumps dur- |    |

|      | ing the sampling of a differential input of 1 V with a common mode                                               |    |

|      | voltage of 0.5 V using 512 kHz clock                                                                             | 37 |

| 2-26 | Binary DAC during sampling                                                                                       | 38 |

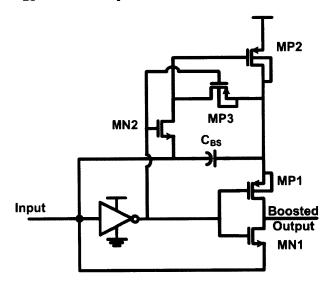

| 2-27 | Schematic of the charge pump used to boost the input sampling switches                                           |    |

|      |                                                                                                                  | 39 |

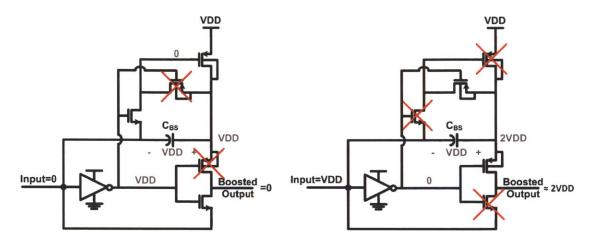

| 2-28 | Charge pump operation                                                                                            | 40 |

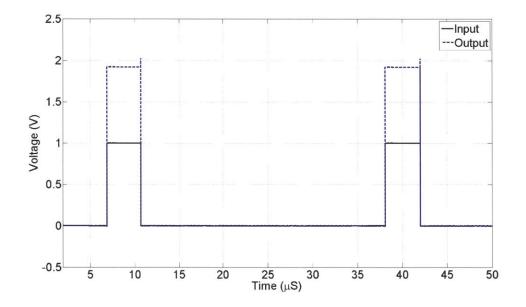

| 2-29 | Simulation of the input and output voltage of charge pump $\ldots$ .                                             | 40 |

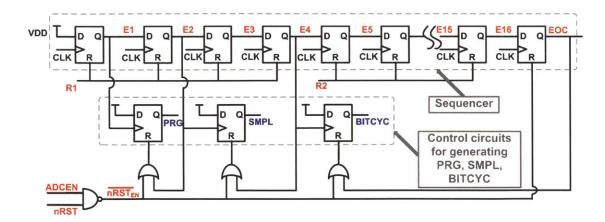

| 2-30 | SAR sequencer and logic for generating PRG, SMPL and BITCYC $$ .                                                 | 41 |

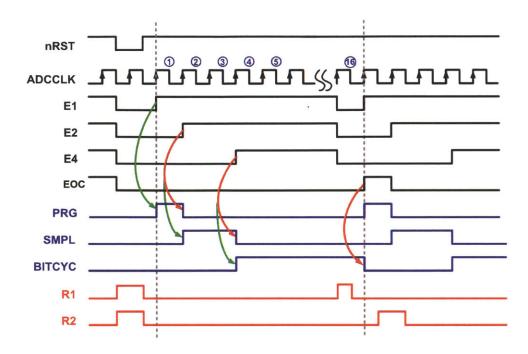

| 2-31 | Sequencer timing diagram and overhead circuit to generate purging                                                |    |

|      | signal                                                                                                           | 42 |

| 2-32 | overlap prevention of BITCYC and SMPL signal                                                                     | 42 |

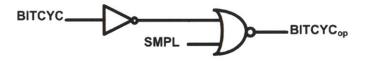

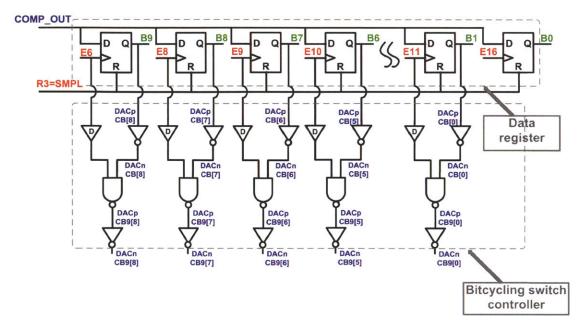

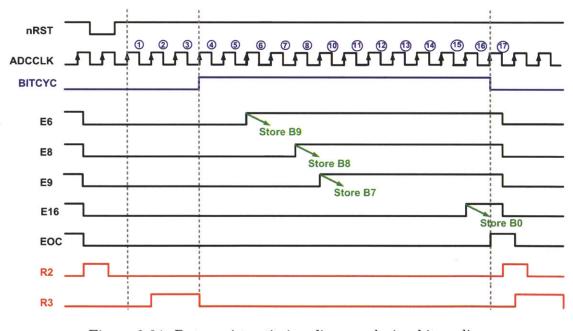

| 2-33 | Data register for storing output of the comparator during bit-cycling                                            |    |

|      | and logic for generating the DAC control signals during bit-cycling . $\ .$                                      | 43 |

| 2-34 | Data register timing diagram during bit-cycling                                                                  | 43 |

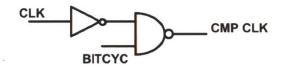

| 2-35 | Generation of comparator clock                                                                                   | 44 |

| 2-36 | Generation of internal reset signals                                                                             | 44 |

| 2_37 |                                                                                                                  |    |

| 2-01 | Timing diagram of reset strategy                                                                                 | 45 |

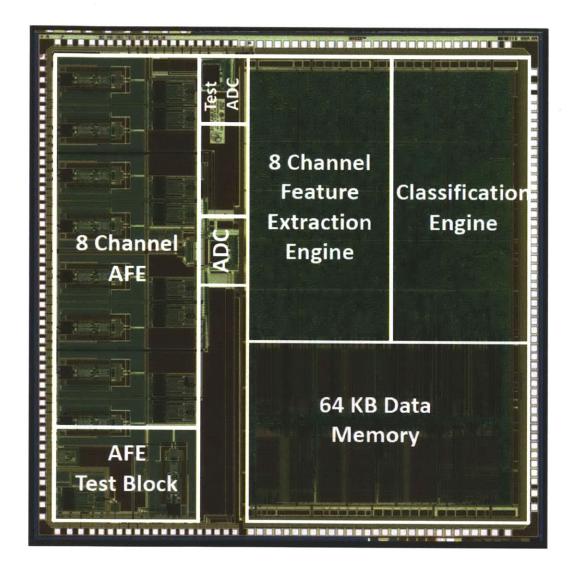

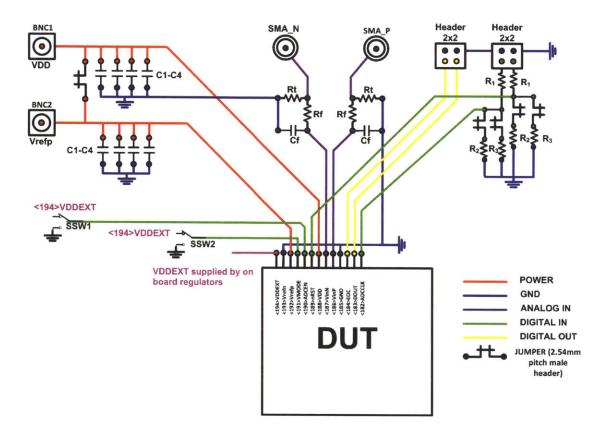

| 3-1  | Micrograph of the full chip, courtesy of Prof. Jerald Yoo at Masdar                   |    |  |  |  |  |  |  |

|------|---------------------------------------------------------------------------------------|----|--|--|--|--|--|--|

|      | Institute of Science and Technology                                                   | 48 |  |  |  |  |  |  |

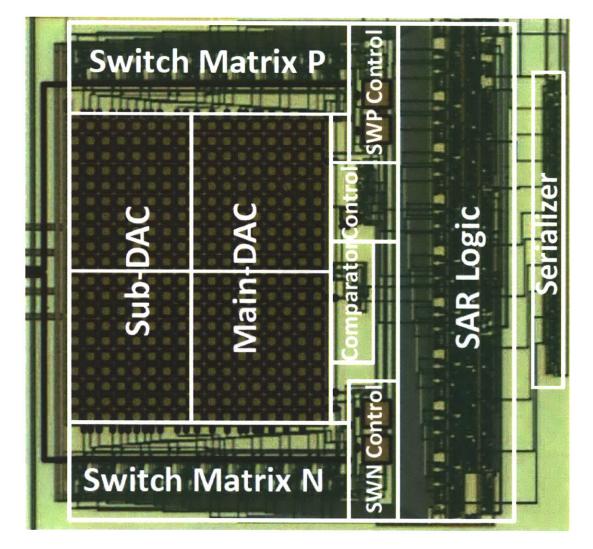

| 3-2  | Micrograph of the full ADC and the serializer                                         | 49 |  |  |  |  |  |  |

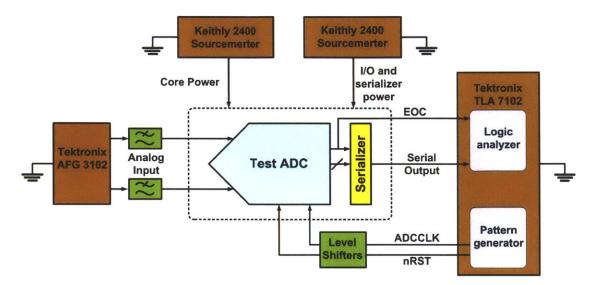

| 3-3  | Schematic of the test setup                                                           | 51 |  |  |  |  |  |  |

| 3-4  | Test PCB photograph                                                                   | 51 |  |  |  |  |  |  |

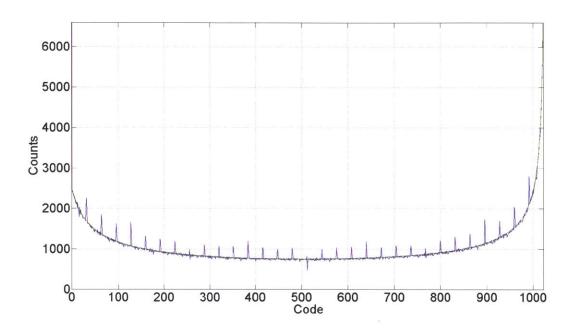

| 3-5  | Code density histogram of the ADC                                                     | 52 |  |  |  |  |  |  |

| 3-6  | ADC Differential and Integral non-linearity versus output code                        | 53 |  |  |  |  |  |  |

| 3-7  | FFT of the ADC output with 15.5 kHz input signal $\ldots$ $\ldots$ $\ldots$           | 54 |  |  |  |  |  |  |

| 3-8  | ENOB versus ADC input signal frequency at sampling rate of 32 kHz $$                  | 55 |  |  |  |  |  |  |

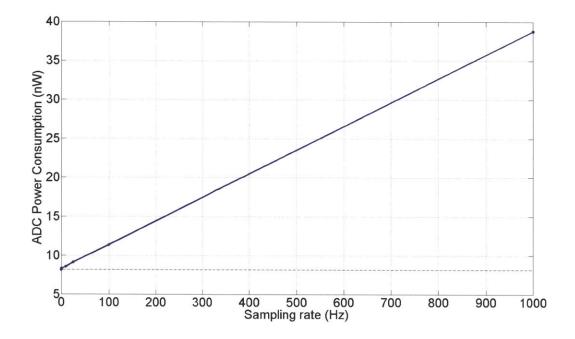

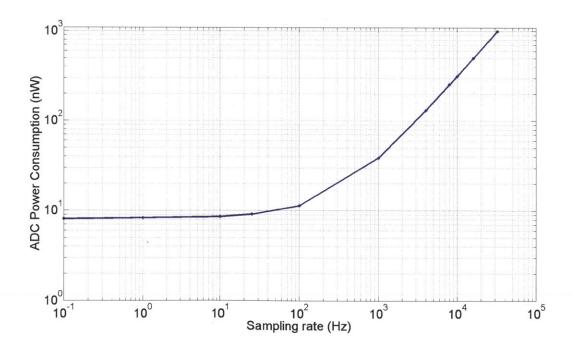

| 3-9  | Average Power consumption of the ADC versus sampling rate $\ldots$ .                  | 55 |  |  |  |  |  |  |

| 3-10 | Linear plot of the power consumption of the ADC versus sampling rate                  |    |  |  |  |  |  |  |

|      | below 1 kHz                                                                           | 57 |  |  |  |  |  |  |

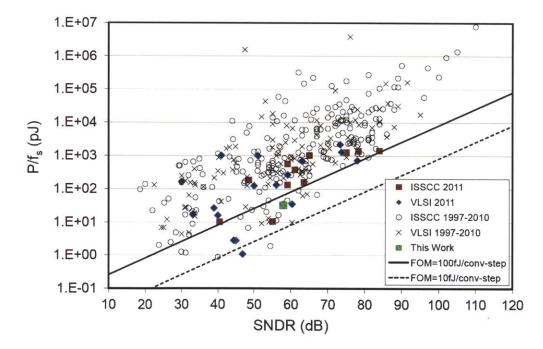

| 3-11 | Log-log plot of the power consumption of the ADC versus sampling rate $% \mathcal{A}$ | 57 |  |  |  |  |  |  |

| 3-12 | Comparison of the ADC to the state-of-the art ( Data adopted from B.                  |    |  |  |  |  |  |  |

|      | Murmann, "ADC Performance Survey 1997- 2010," http://www.stanford.edu/mur-            |    |  |  |  |  |  |  |

|      | mann/adcsurvey.html)                                                                  | 58 |  |  |  |  |  |  |

| A-1  | Partition of the schematic of the board showing the necessary connec-                 |    |  |  |  |  |  |  |

|      | tions for the stand alone ADC                                                         | 64 |  |  |  |  |  |  |

# List of Tables

| 3.1 | Summary of ADC performance parameters | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 58 |

|-----|---------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| A.1 | ADC pin definition                    | • | • | • | • | • | • |   | • |   |   | • |   |   |   |   | 64 |

## Chapter 1

## Introduction

Ambulatory monitoring of biopotential signals is crucial for enhancing health care service. It enables better diagnosis and treatment of a disease, delivering remote health service while reducing its overall cost [1].

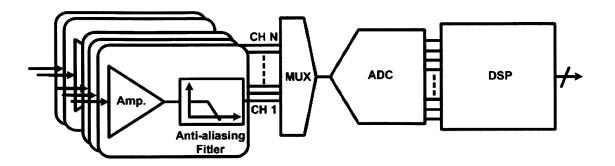

Figure 1-1 depicts a generic system for vital signal acquisition. It incorporates an analog front-end to amplify the signals produced by the sensors, analog to digital converter and digital signal processor. The system can involve multiple channels that are combined together using multiplexer. Thus, the design of analog to digital converters with ultra-low power dissipation and relatively compact size is mandatory for such systems. The ADC presented in this thesis is utilized in EEG SoC for seizure detection and recording. The design parameters of the ADC are mainly controlled by system specifications which will be presented in the rest of this chapter. However, the final design can be still utilized in various bio-potential acquisition systems that capture signals with similar bandwidth requirements to EEG.

The rest of this chapter derives the main design parameters of the ADC from system requirements. Then a survey of different ADC topologies is presented for architecture selection. The last section provides an overview of thesis organization.

Figure 1-1: Top-level architecture of biopotential acquisition system

## **1.1** System Requirements

The ADC implemented in this thesis is integrated within a scalable EEG SoC for seizure detection and recording. The full system can capture EEG signals through 1 up to 8 parallel differential channels that are time division multiplexed into a single ADC. The number of the operating channels in the Analog Front-End (AFE) and corresponding ADC sampling frequency are controlled by the Digital Back End (DBE). The ADC supplies the DBE with digital word and an End-of-Conversion (EOC) signal to latch the data. The ADC design parameters are optimized to satisfy the system design requirements and are briefly presented in the next subsections.

#### 1.1.1 Resolution

The ADC resolution is set by the SNR requirements of seizure detection algorithm in the system. A resolution of 10 bits is chosen for this design which is sufficient for extraction of bio-markers for seizure detection by DBE.

#### 1.1.2 Sample Rate

The EEG signal occupies the frequency spectrum from 0.1 to 100 Hz [1]. Thus, the ADC sampling frequency should exceed 200 Hz to satisfy Nyquist requirements. In order to relax the the roll-off of anti-aliasing filters in the AFE, a sampling frequency of 4 kHz is chosen. This allows for optimizing the power consumption and the design

of the whole chip since sharp cut-off analog filters are power consuming. Decimation filter is used in the DBE to minimize the required computation [2].

#### 1.1.3 Scalability

Since the full-chip can be configured to operate one channel only or two or four or eight, the ADC sampling frequency should be scalable. The ADC should have a sampling rate of 4N kHz where N is the number of channels used.

#### **1.1.4** Input Interface

A fully differential ADC architecture is adopted in this design. It enhances the common-mode rejection ratio and eliminates the second order harmonics. This boosts the robustness of the whole system at the expense of higher deign complexity and higher power consumption which will be detailed in chapter 2.

#### 1.1.5 Conversion Plan

The MUX, ADC and DBE should be synchronized for the proper operation of the full system. The ADC is supplied a RST signal at start-up for initialization and a clock signal of scalable frequency. The ADC should provide the DBE with an output and EOC every 16 clock cycles regardless of the number of channels used. Thus, the ADC clock frequency should be equal to 16 times the required sampling rate.

## **1.2** Architecture Selection

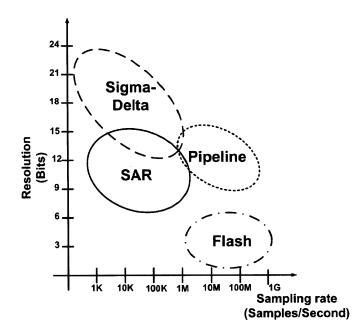

SAR, Pipeline, Sigma-Delta  $(\Sigma - \Delta)$  and Flash are fundamental architectures of analog to digital converters that cover most of the resolution-bandwidth space in energy efficient way. Figure 1-2 depicts how these architectures typically relate to the ADC resolution and sampling rate [3, 4]. Flash converters can't be utilized for the intended application as they suit low resolution requirements. Pipeline converters are energy efficient at medium-high resolution but at sampling rate in order of Mega samples per second which don't fit the speed requirements. Oversampling converters such as Sigma-Delta are commonly used at low speed applications but for high resolution requirements for 12 bits or more. SAR ADCs are frequently the architecture of choice for medium to-high-resolution applications with relatively low speed requirements under 5 Mega Samples/Sec. It allows for a FOM in order of femto-joules per conversion step while targeting the required specifications of the EEG SoC [5, 6, 7]. Thus, a SAR ADC architecture is chosen for this design.

Figure 1-2: ADC architectures comparison

## **1.3** Thesis Organization

The thesis is organized in four chapters. Chapter 1 serves as the introduction and motivation behind this work. Chapter 2 details the architecture and circuit design of the ADC building blocks. Chapter 3 presents the test-setup and measurements results while chapter 4 provides the conclusion and future work.

## Chapter 2

## Architecture and Circuit Design

This chapter presents the architecture and the circuit level implementation of the ADC designed in this work. It starts by reviewing the basic operation of conventional SAR ADC in section 2.1. The top level architecture along with the ADC conversion plan are discussed in section 2.2. Section 2.3 to 2.6 details the operation and circuit implementation of ADC building blocks including the binary capacitive DAC, dynamic comparator, charge pumps along with the methodology for sizing the switches. The SAR logic and self-resetting strategy are presented in section 2.7 while section 2.8 provides the summary of the chapter.

## 2.1 Successive Approximation Conversion Basics

Successive-approximation-register (SAR) ADCs are commonly used for medium to high resolution applications with relatively low speed requirements. It is frequently used for a wide variety of applications, such as portable/battery-powered instruments, industrial controls, and biomedical signal acquisition [8]. In this section, the basic operation principles of single-ended and differential SAR ADC are reviewed.

#### 2.1.1 Single-ended SAR ADC

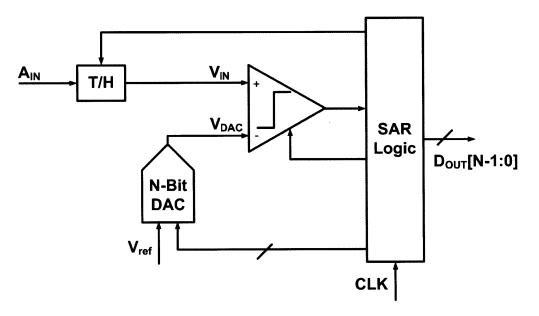

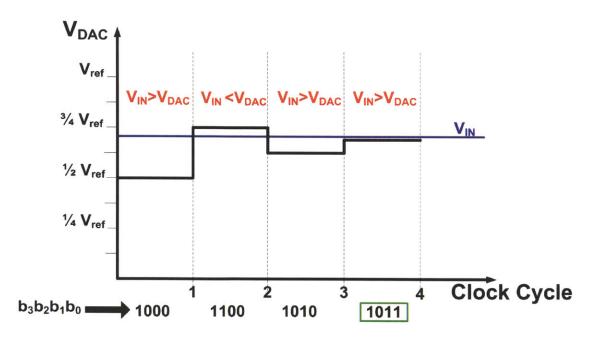

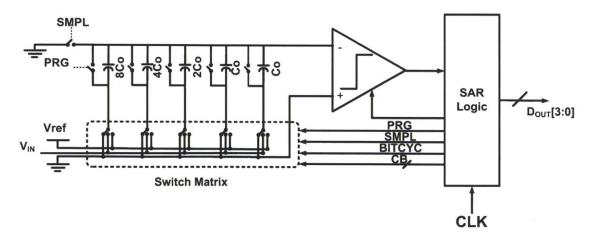

Figure 2-1 depicts the basic architecture of N-bit SAR ADC. It consists of track/hold circuitry, comparator, N-bit DAC and SAR Logic. Each conversion consists of three main phases: DAC purging (incase of using capacitive DAC), input sampling and bit-cycling. SAR ADC utilizes a binary search algorithm to generate the digital code during the bit-cycling phase. Figure 2-2 depicts a sample conversion of conventional 4 bit SAR ADC. Each bit of the digital word should be set to 1 on a cyclic basis. If input voltage is greater than the DAC voltage, the bit is permanently set to one otherwise reset back to zero [9].

Figure 2-1: Basic architecture of SAR ADC

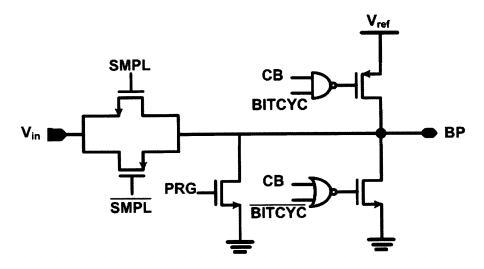

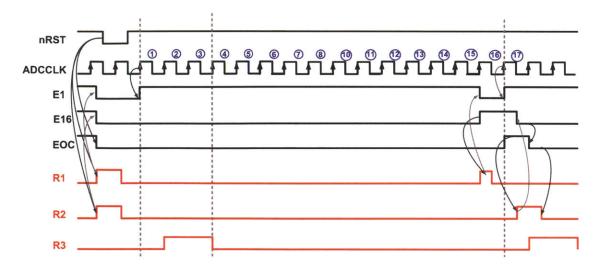

SAR ADC commonly relies on capacitive DAC that provides inherent track and hold function [8]. Figure 2-3 depicts 4-bit SAR ADC where the DAC consists of an array of 4 binary weighted capacitors plus extra LSB capacitor. The control signals of the switches for purging, sampling and bit-cycling are denoted as PRG, SMPL and BITCYC respectively. The control signal CB for each capacitor identify if it is connected to  $V_{ref}$  or ground during each cycle of the bit-cycling phase. The ADC supports input voltage from zero up to the reference voltage  $V_{ref}$ . During the purging phase (DAC resetting) the top and bottom plates of the capacitors are shorted to

Figure 2-2: Timing diagram of the bit-cycling phase of 4 bit SAR ADC

ground. During the sampling phase, the common top plate is grounded while the capacitors bottom plates are connected to the analog input. By the end of the second phase, the DAC common top plate is disconnected from ground then the bottom plates are grounded to turn the top plate voltage,  $V_{DAC}$ , to be equal to  $-V_{in}$ .

Figure 2-3: 4 bit SAR ADC utilizing binary weighted capacitive DAC

Binary search algorithm is utilized to identify the digital output code which starts by connecting the bottom plate of the MSB capacitor to  $V_{ref}$ . DAC performs charge redistribution and  $V_{DAC}$  becomes equal to  $-V_{in}+V_{ref}/2$ . As in the basic example shown before, if  $V_{in}$  is greater than  $V_{ref}/2$  i.e.  $V_{DAC}$  is less than zero, the MSB bit is set to one otherwise it is reset back to zero. The same procedure is applied to determine the rest of the output code.

#### 2.1.2 Differential SAR ADC

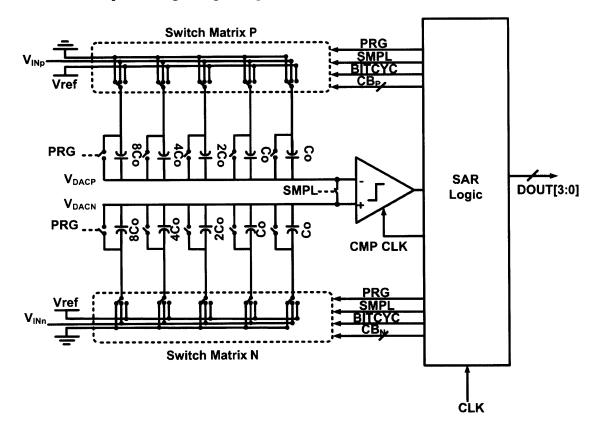

In order to increase the robustness of the whole system, the ADC should support differential analog input as discussed in chapter 1. Figure 2-4 shows an example of 4-bit differential SAR ADC that utilizes a differential capacitive DAC where the ADC differential input voltage range is equal to  $\pm V_{ref}$ .

Figure 2-4: Differential 4 bit SAR ADC utilizing binary weighted capacitive DAC

During the purging phase, all the capacitors are shorted to ground to remove stored charges from previous conversion cycles. Then, the ADC samples the differential input signal by connecting bottom plates of the capacitors of the DACp and DACn to  $V_{INp}$

and  $V_{INn}$  respectively while shorting their top plates where  $V_{DAC,P}$  and  $V_{DAC,N}$  settles to the common mode voltage of the input signal.

The bit-cycling phase starts by identifying the MSB bit which acts as the sign of the differential input. Thus, The bottom plate of the MSB capacitor of DACp array is connected to  $V_{ref}$  while the rest of the capacitors to ground and the inverse is done to DACn. The comparator generates one if  $V_{INp}$ - $V_{INn}>0$ , otherwise it generates zero. It should be noted that the positive input of the comparator is connected to  $V_{DACN}$ while the negative one is connected to  $V_{DACP}$ . If the comparator generates one, then the MSB is set to 1 and the differential input should be compared to  $V_{ref}/2$ . This is done in a similar manner to conventional single-ended SAR by connecting the bottom plate of the MSB-1 capacitor in DACp to  $V_{ref}$  while doing the inverse to DACn. If the comparator generates zero, then the MSB is set to zero and the differntial input should be compared to  $-V_{ref}/2$  and same procedure is applied for the rest of the bits during the bit-cycling phase.

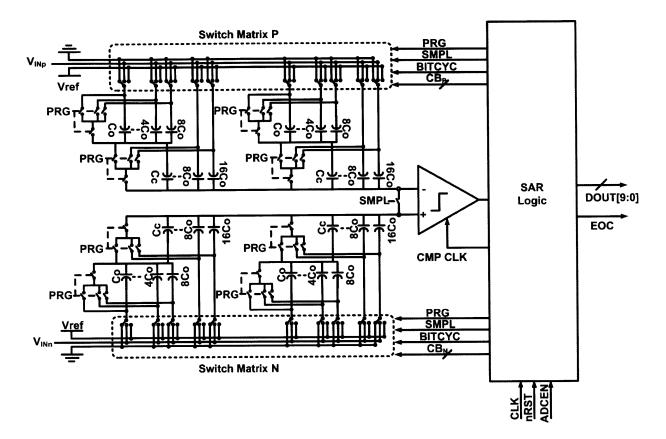

### 2.2 Global Architecture

Figure 2-5 depicts the global architecture of the 10 bit SAR ADC designed in this work. It includes differential capacitive DAC, digital comparator, SAR Logic and switches. A fully differential architecture is adopted to enhance the common mode rejection ratio as discussed in chapter 1. A binary weighted capacitive DAC is utilized in this design while combining both concepts of sptit-capacitor array and sub-DAC [10].

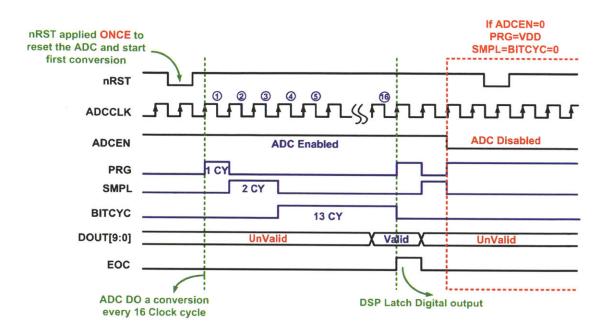

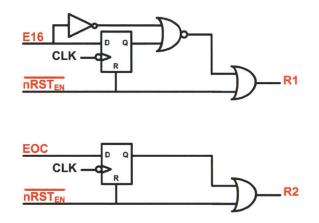

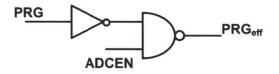

Figure 2-6 shows the ADC conversion plan where each conversion takes 16 clock cycles. A global active low reset signal (nRST) aligned with the negative clock edge is applied to initialize the registers. The conversion plan includes one clock cycle for purging, two clock cycles for sampling to relax settling time requirements of the capacitor's top plate voltage while the rest of the cycles are used for bit-cycling. The ADC provides the DBE with the End-of-Conversion (EOC) signal as a flag to latch the data at the end of the 16 clock cycles.

Figure 2-5: ADC architecture

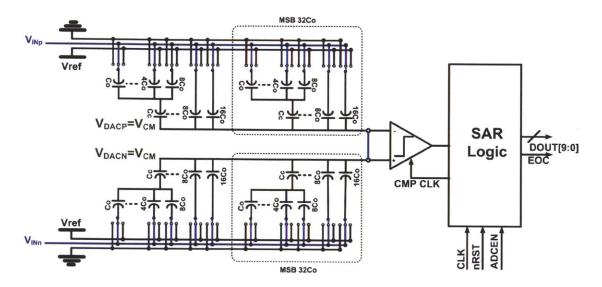

As discussed in the previous section, all the capacitors are shorted to ground during the purging phase to reset the DAC. Figure 2-7 depicts the ADC during the sampling phase where the differential input signal is connected across the bottom plates of the capacitors of the DACp and DACn where  $V_{DAC,P}$  and  $V_{DAC,N}$  settles to the common mode voltage of the input signal as discussed before.

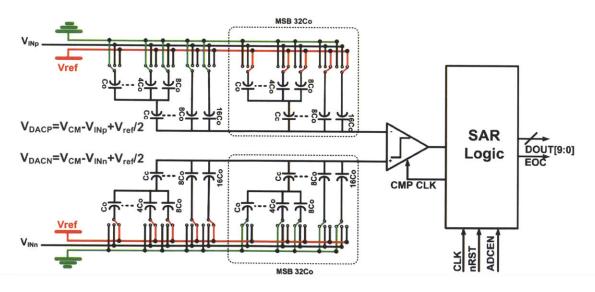

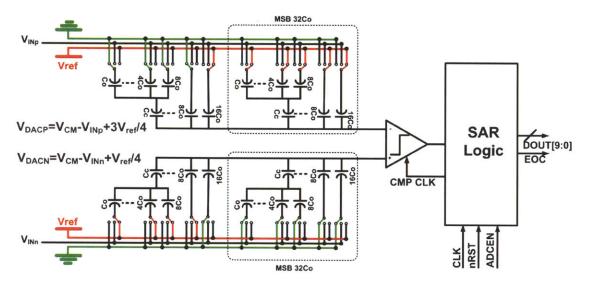

Since split capacitor array technique is utilized in the design, the operation during the bit-cycling phase slightly differs from conventional differential SAR ADC. The MSB capacitor is split into array identical to the rest of DAC capacitors. The bitcycling phase starts by identifying the MSB bit as normal by connecting the bottom plates of the capacitors of DACp MSB array to  $V_{ref}$  while the rest of the capacitors to ground and the inverse is done to DACn as shown in Figure 2-8. If the MSB is 1, the differential input should be compared to  $V_{ref}/2$  by connecting the bottom plate of the MSB-1 capacitor in DACp to  $V_{ref}$  while doing the inverse to DACn as shown

Figure 2-6: SAR ADC conversion plan

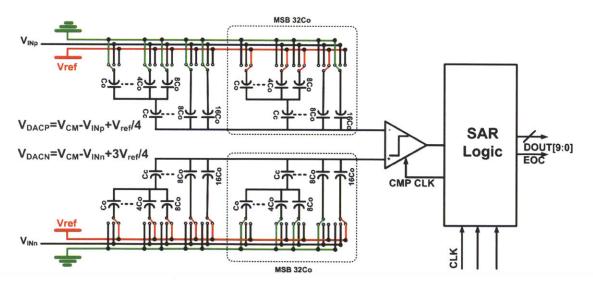

in Figure 2-9. On the other hand, if the MSB is zero, the differntial input should be compared to  $-V_{ref}/2$ . This is done using split-capacitor approach by connecting the bottom plate of the capacitor identical to MSB-1 in the DACp MSB array to ground while doing the inverse to DACn as shown in Figure 2-10.

It should be noted that as long as ADC enable (ADCEN) remains high, the ADC generates a digital word every 16 clock cycles despite the clock frequency used. It self-resets the registers at the end of each conversion to remove stored values. If ADCEN is equal to zero the capacitors bottom plates are connected to ground to disable the ADC from signal path. This feature is added to allow for individual testing of AFE in the whole system by isolating it from the ADC.

## 2.3 Capacitive DAC

The ADC designed in this work utilizes a fully differential capacitive DAC as shown in Figure 2-5. Its area and power consumption are reduced by combining both techniques of sub-DAC and split-capacitor array [10]. The DAC is composed of 6-bit main DAC and 4 bit sub-DAC where the MSB is built using capacitor array identical to the

Figure 2-7: ADC during sampling phase (purging switches are not shown for clarity)

Figure 2-8: ADC during bit-cycling phase of MSB

Figure 2-9: ADC during bit-cycling phase if MSB=1  $\,$

Figure 2-10: ADC during bit-cycling phase if MSB=0

rest of the DAC capacitors. The concepts of sub-DAC and split capacitor array are revised in the following subsections.

#### 2.3.1 Sub-DAC Interpolation

The layout area of SAR ADC employing binary weighted capacitive DAC is usually dominated by the DAC area where the ratio of MSB to LSB capacitor is equal to  $2^{N-1}$  (512 for 10 bit ADC). In order to reduce ADC area, the DAC can be divided into M-bit main-DAC and L-bit sub-DAC connected through a coupling capacitor [11], where the ADC resolution N=M+L. The net effective capacitance of the sub-DAC and coupling capacitor is equal to the unit capacitance used Co. Thus, the coupling capacitor should have a value of  $\frac{2^L}{2^L-1}C_o$ .

Figure 2-11 shows a single sided DAC split in 6 bit main-DAC and 4 bit sub-DAC. Superposition is applied to understand how each capacitor in main-DAC and sub-DAC affects the voltage  $V_{DAC}$ . Figure 2-12 depicts the effective capacitive divider while individually switching the bottom plate of each capacitor in the main-DAC to  $V_{ref}$  and the rest of capacitors to ground and assuming that  $V_{DAC}$  was initially zero. First, the bottom plate of the MSB capacitor (32Co) is connected to  $V_{ref}$ , a capacitive divider by two capacitors each is equal to 32 Co occurs and  $V_{DAC}$  is equal to half  $V_{ref}$ . If the capacitor 16Co is the one connected to  $V_{ref}$ ,  $V_{DAC}$  is equal to quarter  $V_{ref}$  and so on.

Figure 2-11: Binary weighted DAC with 6 bit main-DAC and 4 bit sub-DAC

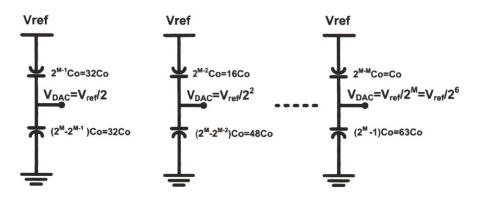

Thevenin equivalent should be utilized to apply same procedure for the sub-DAC.

Figure 2-12: The DAC effective capacitive divider while individually connecting the bottom plate of each capacitor in the main-DAC to  $V_{ref}$  and the rest of capacitors to ground

Figure 2-13 shows the effective capacitive divider while connecting the bottom plate of the MSB capacitor of the sub-DAC to  $V_{ref}$  and the rest of capacitors to ground. The voltage  $V_{DAC}$  is equal to  $V_{ref}/2$  divided by  $2^{M}$  which is the half the value yielded by the LSB of the main-DAC. The same analysis can be applied to the rest of the capacitors of the sub-DAC. It should be noted that the thevenin capacitance is the same in all cases.

Figure 2-13: Thevenin equivalent circuit for analysing passive sub-DAC

The main problem with sub-DAC interpolation is its sensitivity to the parasitic capacitance from the top plate of sub-DAC capacitors to ground. This leads to INL/DNL errors due to the compression of transition steps by the sub-DAC. However, this problem can be minimized by increasing the size of the coupling capacitor to increase the effective weight of sub-DAC interpolation [11].

#### 2.3.2 Split Capacitor Array

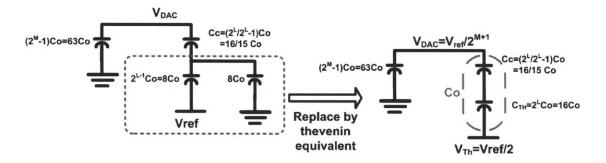

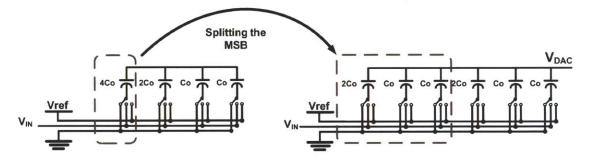

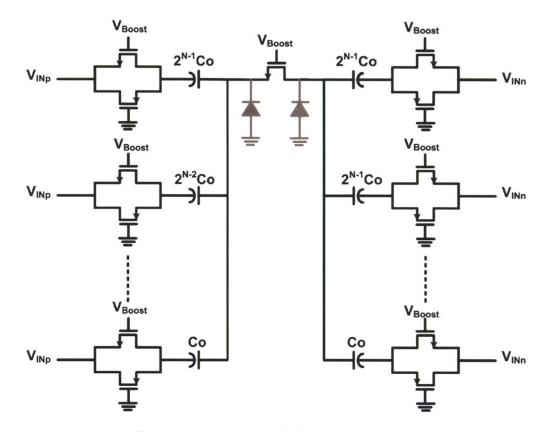

The split capacitor array provides an energy efficient charge recycling approach for the capacitive DAC. It reduces the average switching energy of the DAC by 37% compared to the conventional switching schemes [12]. Figure 2-14 shows an example of split capacitor array applied to 3 bit single-ended binary weighted capacitive DAC. The MSB capacitor  $(4C_o)$  is split into array identical to the rest of DAC capacitors.

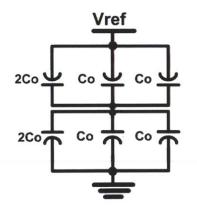

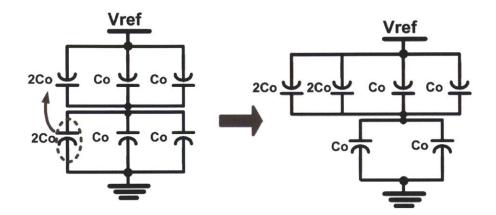

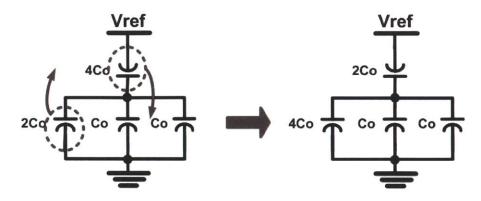

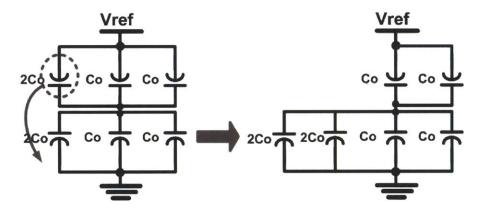

Figure 2-14: Applying split capacitor array technique to 3 bit binary weighted capacitive DAC