# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

5-2015

## Design and Verification Environment for High-Performance Video-Based Embedded Systems

Michael Mefenza Nentedem University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the <u>Computer Engineering Commons</u>, <u>Computer Sciences Commons</u>, and the <u>VLSI and</u> Circuits, Embedded and Hardware Systems Commons

#### Recommended Citation

Mefenza Nentedem, Michael, "Design and Verification Environment for High-Performance Video-Based Embedded Systems" (2015). *Theses and Dissertations.* Paper 13.

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

# Design and Verification Environment for High-Performance Video-Based Embedded Systems

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering

by

Michael Mefenza Nentedem

Ecole Nationale Superieure Polytechnique

Bachelor of Science in Telecommunication Engineering, 2009

Ecole Nationale Superieure Polytechnique

Master of Science in Telecommunication Engineering, 2010

#### May 2015 University of Arkansas

| This dissertation is approved for recommendation to the Graduate Council. |                                  |  |

|---------------------------------------------------------------------------|----------------------------------|--|

|                                                                           |                                  |  |

| Dr. Christophe Bobda Dissertation Director:                               |                                  |  |

| Dr. David Andrews<br>Committee member                                     | Dr. Scott Smith Committee member |  |

| Dr. Pat Parkerson                                                         |                                  |  |

Committee member

#### Abstract

In this dissertation, a method and a tool to enable design and verification of computation demanding embedded vision-based systems is presented. Starting with an executable specification in OpenCV, we provide subsequent refinements and verification down to a system-on-chip prototype into an FPGA-Based smart camera. At each level of abstraction, properties of image processing applications are used along with structure composition to provide a generic architecture that can be automatically verified and mapped to the lower abstraction level. The result is a framework that encapsulates the computer vision library OpenCV at the highest level, integrates Accelera's System-C/TLM with UVM and QEMU-OS for virtual prototyping and verification and mapping to a lower level, the last of which is the FPGA. This will relieve hardware designers from time-consuming and error-prone manual implementations, thus allowing them to focus on other steps of the design process. We also propose a novel streaming interface, called Component Interconnect and Data Access (CIDA), for embedded video designs, along with a formal model and a component composition mechanism to cluster components in logical and operational groups that reduce resource usage and power consumption.

This work was supported in part by the grant 1302596 from the National Science Foundation (N.S.F.)

#### Acknowledgements

I would like to extend my sincere gratitude to my advisor Dr. Christophe

Bobda. His guidance and support have been invaluable and his belief in me unfaltering. I cannot ever hope to repay the time and efforts that he devoted to my growth both academically and as a person; I can only hope that I will have the opportunity to pay this debt forward to a colleague or a student. I would like to thank Dr. David Andrews, Dr. Pat Parkerson and Dr. Scott Smith for serving as members of my dissertation committee. Their questions, comments and suggestions have helped me distill the arguments and clarify the exposition. I appreciate the time and efforts that they put in reading and evaluating my dissertation and presentations. I would also like to acknowledge that this work was supported in part by the grant 1302596 from the National Science Foundation (N.S.F.). Last but not least, I would like to thank my family for supporting me and always being there when I needed help. I would like to thank my parents Mr. Nentedem Pierre and Mme Megni Louise for their support and encouragement.

### **Table of Contents**

| Ι   | Intr         | oduction                                                                         | 1  |

|-----|--------------|----------------------------------------------------------------------------------|----|

|     | I.1          | Video and image processing                                                       | 1  |

|     |              | I.1.1 Image acquisition                                                          | 1  |

|     |              | I.1.2 Image processing algorithms                                                | 2  |

|     |              | I.1.3 Image processing implementation                                            | 3  |

|     | I.2          | FPGA                                                                             | 3  |

|     | I.3          | FPGA for rapid prototyping of embedded video applications                        | 5  |

|     |              | I.3.1 Design reuse                                                               | 5  |

|     |              | I.3.2 Design flow                                                                | 6  |

|     |              | I.3.3 Resources usage                                                            | 7  |

|     |              | I.3.4 Verification                                                               | 7  |

|     | I.4          | Objective                                                                        | 8  |

|     | I.5          | Contributions                                                                    | 8  |

|     | I.6          | Dissertation outline                                                             | 9  |

|     |              |                                                                                  |    |

| Bi  | bliogr       | aphy                                                                             | 10 |

| II  | Con          | propert Interconnect and Data Access Interface for Embedded Vi                   |    |

| 11  |              | apponent Interconnect and Data Access Interface for Embedded Vi-<br>Applications | 19 |

|     |              | Introduction                                                                     |    |

|     | II.1<br>II.2 | Motivation example                                                               |    |

|     | II.2<br>II.3 | Related Work                                                                     |    |

|     | II.4         | Interface Model                                                                  |    |

|     |              | Component Interconnect and Data Access Interface                                 |    |

|     | 11.0         | II.5.1 CIDA streaming:                                                           |    |

|     |              | II.5.2 CIDA DMA:                                                                 |    |

|     | II.6         | System Integration with CIDA                                                     |    |

|     | II.7         | Resource Optimization                                                            |    |

|     |              | Functional Verification Support                                                  |    |

|     | II.9         | Experimental Results                                                             |    |

|     | 11.0         | II.9.1 Interface comparison                                                      |    |

|     |              | II.9.2 Resource Optimization                                                     |    |

|     | II 10        | Conclusions                                                                      |    |

|     | 11.10        | Concresions                                                                      | 01 |

| Bi  | bliogr       | aphy                                                                             | 39 |

| TTT | A TA         | remover for Penid Protetyning of Embedded Vision Applications                    | 49 |

| 111 |              | ramework for Rapid Prototyping of Embedded Vision Applications  Introduction     |    |

|     |              | Related work                                                                     |    |

|     |              | Proposed Design Approach                                                         |    |

|     | 111.0        | III.3.1 Basic Hardware Modules                                                   |    |

|     | ПΙΔ          | Case Studies                                                                     |    |

|     | 111.4        | III.4.1 Driving Assistance System                                                |    |

|     |              | 111. 1.1 1/11/1115 110010/001100 D/00/0111                                       | 00 |

| III.4.2 Line Segment Detection Using Weighted Mean Shift(LSWMS)     | 57           |

|---------------------------------------------------------------------|--------------|

| III.4.3 Segmentation                                                | 58           |

| III.5 Conclusion                                                    | 59           |

| Bibliography                                                        | 61           |

| IV Automatic UVM Environment Generation for Assertion-based and Fun | ı <b>C</b> - |

| tional Verification of SystemC Designs                              | 64           |

| IV.1 Introduction                                                   | 64           |

| IV.2 Related work                                                   | 66           |

| IV.3 Proposed UVM environment for SystemC/TLM designs               | 67           |

| IV.4 Generated components                                           |              |

| IV.4.1 Packet classes                                               | 69           |

| IV.4.2 Sequencer                                                    | 71           |

| IV.4.3 Driver                                                       |              |

| IV.4.4 UVMC                                                         | 72           |

| IV.4.5 Monitor                                                      | 73           |

| IV.4.6 Coverage Checker                                             |              |

| IV.4.7 Assertions Checker                                           |              |

| IV.5 Verification Flow                                              |              |

| IV.6 Experimental Evaluation                                        | 76           |

| IV.7 Conclusion                                                     |              |

|                                                                     |              |

| Bibliography                                                        | 79           |

| V Interface Based Memory Synthesis Of Image Processing Applications | 5            |

| In FPGA                                                             |              |

| V.1 Introduction                                                    | 82           |

| V.2 Related work                                                    | 84           |

| V.3 Architectural model                                             | 84           |

| V.3.1 Image processing operations                                   | 84           |

| V.3.2 Image processing memory elements                              |              |

| V.3.3 Image processing applications                                 | 86           |

| V.3.4 Embedded Memories                                             |              |

| V.3.5 Memory synthesis problem                                      |              |

| V.4 Experimental results                                            |              |

| V.5 Conclusion                                                      |              |

| Bibliography                                                        | 97           |

| VI Complexions                                                      | 100          |

| VI Conclusions                                                      |              |

| VI.1 Summary                                                        |              |

| VI.2 Future Work                                                    | 101          |

### List of Figures

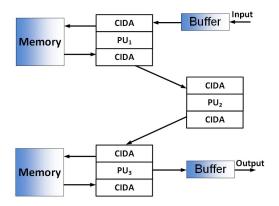

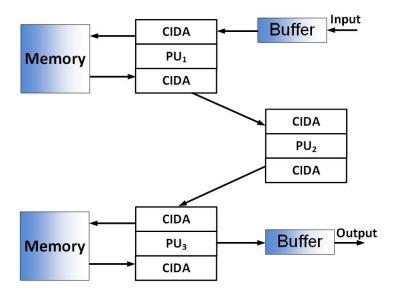

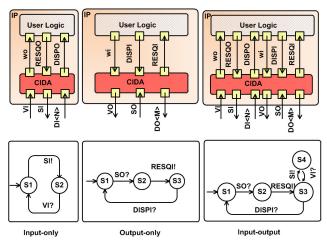

| Figure II.1:   | Motivation example. In (a) the 3 components are connected serially while in (b) and (c) they are clustered                                                                                                                                                                                                                                               | 15             |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Figure II.2:   | Interface automata. The automaton is enclosed in a box, whose ports correspond to the input and output actions. The names of the actions are appended with the symbol "?" (resp. "!", ";") to denote that the action is an input (resp. output, internal) action. An arrow without                                                                       | 18             |

| Figure II.3:   | CIDA streaming. On top, interface description; on bottom, interface                                                                                                                                                                                                                                                                                      | 21             |

| Figure II.4:   | CIDA DMA. On top, interface description; on bottom, interface automa-                                                                                                                                                                                                                                                                                    | 23             |

| Figure II.5:   | Organization of data access. Designer specify only the source and sink of data using the CIDA interface. The system coordinates the data transfer                                                                                                                                                                                                        | 26             |

| Figure II.6:   |                                                                                                                                                                                                                                                                                                                                                          | $\frac{1}{27}$ |

| _              |                                                                                                                                                                                                                                                                                                                                                          | 28             |

| 0              | UVM verification environment                                                                                                                                                                                                                                                                                                                             |                |

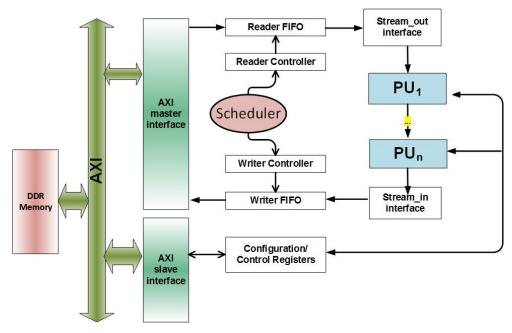

| 0              | hardware architecture                                                                                                                                                                                                                                                                                                                                    |                |

| _              |                                                                                                                                                                                                                                                                                                                                                          | 37             |

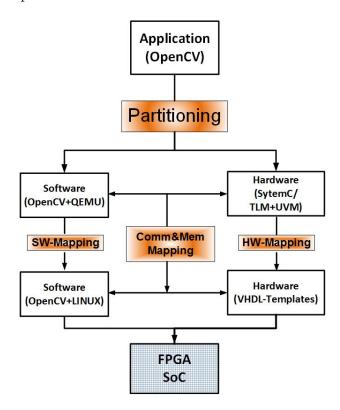

| Figure III.1:  | The Proposed Design Flow                                                                                                                                                                                                                                                                                                                                 | 47             |

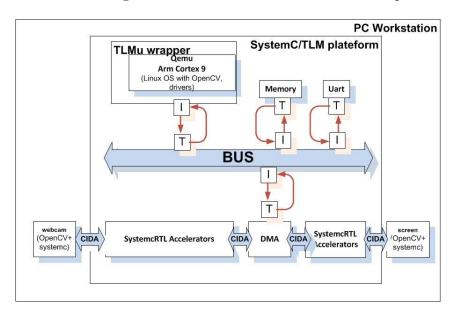

| Figure III.2:  | SystemC/TLM abstract representation of the target platform at system-level. Initiator (I) and Target (T) interfaces are automatically included at the boundary of components of an abstract system-on-chip description. CIDA is used to handle data access from hardware modules                                                                         | 48             |

| Figure III.3:  | Organization of data access. The designer specifies only the source and sink of data using the CIDA interface. The system coordinates the data transfer and access to share memories                                                                                                                                                                     | 51             |

| Figure III.4:  | System integration with CIDA; abstract representation (left) and con-                                                                                                                                                                                                                                                                                    | 52             |

| _              | Inverse perspective mapping. The Original image (left) and transformed                                                                                                                                                                                                                                                                                   | 55             |

|                | Synthesis results for each implemented module. All modules are capable of running well over 100 MHz. The Serializer and Deserializer modules are connected to a 64-bit-wide CIDA for pixel-wise data communication. This way, each intermediate module deals with single pixels on the bus, rather than having to redundantly deal with the extraction / |                |

| Figure III 7.  |                                                                                                                                                                                                                                                                                                                                                          | 56             |

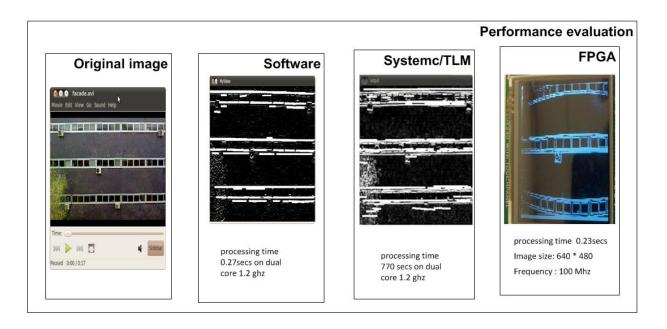

| r 1gure 111.7: | Line segment detection using weighted mean shift. From left to right we have the input image, the output of the OpenCV algorithm (initial specification) running on a workstation, the output of the SystemC SoC                                                                                                                                         |                |

|                | prototype and the output of the emulation into FPGA                                                                                                                                                                                                                                                                                                      | 59             |

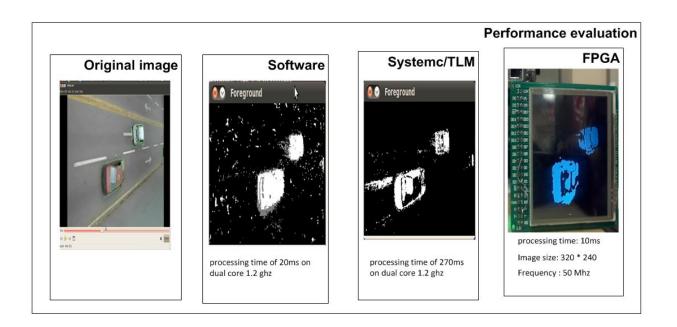

| Figure III.8: Segmentation implementation. From left to right we have the input image, the output of the OpenCV algorithm running on a PC station, the output of the SystemC SoC prototype and the output of the emulation into FPGA. | 60 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

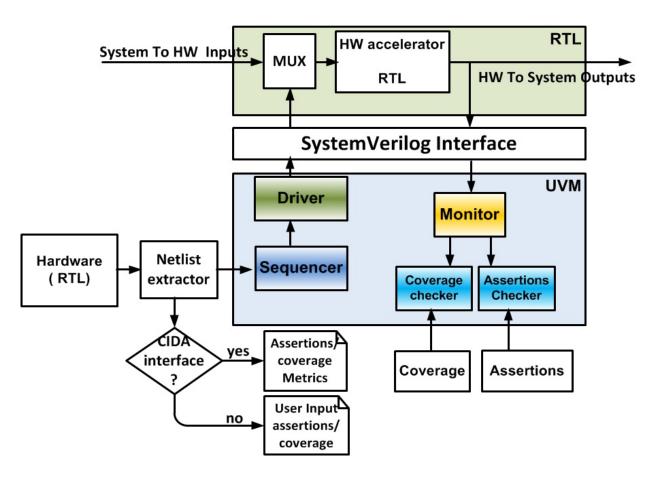

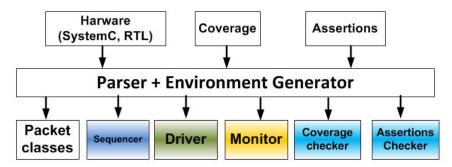

| Figure IV.1: UVM testbench generation for a SystemC design. Using a SystemC specification, coverage and assertions, we generate all the necessary components in UVM. If not specified, coverage metrics are automatically generated.  | 68 |

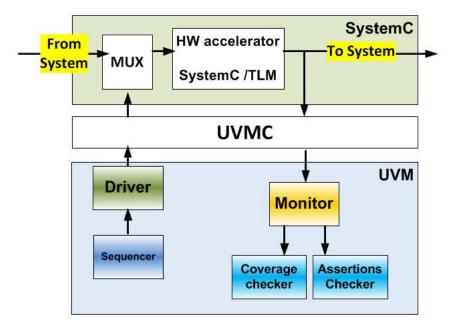

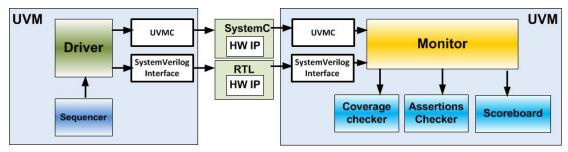

| Figure IV.2: Verification environment. It is automatically encapsulated on top of the SystemC DUT.                                                                                                                                    | 69 |

| Figure IV.3: Example of SystemC DUT. Sobel implementation with a streaming data interface                                                                                                                                             | 70 |

| Figure IV.4: Generated packet classes. On the left is the side structure of packet in SystemC for the DUT of Figure ??.On the right side is the structure of packet in UVM for the DUT of Figure ??                                   | 71 |

| Figure IV.5: Generated packet classes for a TLM DUT. On the left is the side structure of packet in SystemC, on the right side is the structure of packet in                                                                          | 71 |

| Figure IV.6: Sequences Generation. Randomize() is used to generate random values. Stream_in_data is constrained to be less than 256 for the Sobel                                                                                     | 72 |

| Figure IV.7: Coverage implementation in our environment. It shows the bins or set of values that we want to cover for each signal                                                                                                     |    |

| Figure IV.8: Assertion implementation in our environment. Rst must be set for at least 3 clock cycles. Stream_out_stop and Stream_out_valid cannot be true at the same time. These are 2 properties of the protocol imple-            |    |

| Figure IV.9: Functional consistency checking using the Proposed UVM environment                                                                                                                                                       |    |

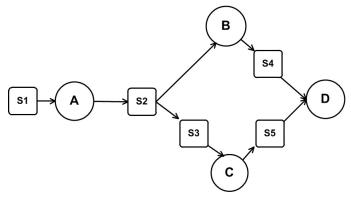

| Figure V.1: Model of an image processing application. A, B, C and D are components; S1 to S5 are memory sources                                                                                                                       | 87 |

| Figure V.2: CIDA streaming. On top, interface description; on bottom, interface automaton.                                                                                                                                            | 88 |

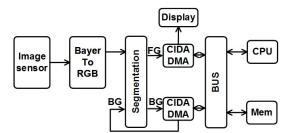

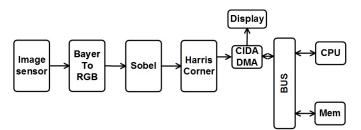

| Figure V.3: Segmentation implementation.  Figure V.4: Harris corner implementation.                                                                                                                                                   | 94 |

### List of Tables

| Table II.1:  | Interface comparison CIDA VS AXI4-stream VS Avalon-ST                                                                                                                                                                       | 34 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table II.2:  | Resource reduction on all testcases.                                                                                                                                                                                        | 38 |

| Table II.3:  | Power reduction on all testcases.                                                                                                                                                                                           | 38 |

| Table III.1: | Resources utilization of our case studies in the emulation platform. The overall percentage of utilization is less than 28% which gives enough resources for further acceleration.                                          | 58 |

| Table III.2: | Duration in seconds for processing a frame at different levels                                                                                                                                                              | 58 |

| Table IV.1:  | Experimental evaluation of the proposed environment. Size is the number of lines in the DUT, Tgen is the time (in seconds) to create the environment for the DUT, Tsim is the CPU simulation time (in seconds) for the DUT. | 77 |

| Table V.1:   | Total available emebedded memories for Zynq XC7z020CLG484-1                                                                                                                                                                 | 90 |

|              | Power estimation for RAM with different widths and depths                                                                                                                                                                   |    |

|              | Single-port RAM                                                                                                                                                                                                             |    |

|              | Dual-port RAM                                                                                                                                                                                                               |    |

|              | Experimental evaluation.                                                                                                                                                                                                    |    |

|              |                                                                                                                                                                                                                             |    |

#### List of Papers

This dissertation is based on the following four papers:

### Chapter 2 Component Interconnect and Data Access Interface for Embedded Vision Applications

Michael Mefenza, Franck Yonga and Christophe Bobda In Journal of Real-Time Image Processing. Submitted for review.

### Chapter 3 A Framework for Rapid Prototyping of Embedded Vision Applications

Michael Mefenza, Franck Yonga, Luca B Saldanha, Christophe Bobda and Senem Velipassalar

In Conference on Design & Architectures for Signal and Image Processing (DASIP), Oct 2014, Madrid, Spain. Accepted.

# Chapter 4 Automatic UVM Environment Generation for Assertion-based and Functional Verification of SystemC Designs

Michael Mefenza, Franck Yonga and Christophe Bobda In Conference on Microprocessor Test and Verification (MTV 2014), Dec 2014, Austin, Texas, USA. Accepted.

### Chapter 5 Interface Based Memory Synthesis Of Image Processing Chains In FPGA

Michael Mefenza and Christophe Bobda

In International Symposium on Highly Efficient Accelerators and Reconfigurable Technologies (HEART 2015). Submitted for review.

#### Other related papers:

# A Hardware/software Prototyping System for Driving Assistance Investigations

Jacob Anders, Michael Mefenza, Christophe Bobda, Franck Yonga,

#### Z. Aklah and Kevin Gunn.

In Journal of Real-Time Image Processing, pages 1-11, May 2013. [Online]. Available: http://dx.doi.org/10.1007/s11554-013-0351-4. Contributed to chapter 2.

# RazorCam: A Prototyping Environment for Video Communication

Michael Mefenza, Franck Yonga and Christophe Bobda In International Workshop on Mobile Computing Systems and Applications, 17(3):13-14, February 2013. [Online]. Available: http://doi.acm.org/10.1145/2542095.2542103. Contributed to chapter 3

#### I Introduction

#### I.1 Video and image processing

The use of cameras, and thus visual detection, has become a promising alternative conventional range sensors due to their advantages in size, costs and accuracy. Robotics, driving assistance systems, autonomous driving cars and unmanned aerial systems (UAS) are few examples of critical areas of application. Progress in automotive is leading to the use of cameras in high-end cars for driving assistance, lane departure warning, autonomous cruise control and occupant pose analysis [1]. UAS are increasingly used in surveillance [2], [3], precision agriculture [3], search and rescue [4], [3] and communications relay [5], [3]. Many research efforts have also been devoted to building systems for vision-aided flight control [6], tracking [7], terrain mapping [8], and navigation [9]. Image processing can be described as a task which converts an input image into a modified output image or a task that extract information from the features present in an image. A typical set-up of an image processing system includes an image acquisition device and the image processing unit.

#### I.1.1 Image acquisition

Video images are captured by CMOS or CCD (charge-coupled device) image sensors. These are semiconductor devices comprising an array of light sensitive elements which convert photon intensity into electric charge. In most cases the sensing element responds to intensity only; color images are captured by passing the light through a mosaic of red, green and blue filters before sampling, such that each element captures one primary color only. The sensor produces a frame by spatially dividing a light sensitive region into an ordered array of picture elements referred to as pixels, which are aligned to a grid or lattice, with M rows and N columns. The size (M X N) of the image is defined as the number of pixels per frame. A common size for video derived from analogue sources is 720 x 576 whereas for digitally sourced video, it is typically a minimum of 640 x 480 in most applications.

#### I.1.2 Image processing algorithms

There are several types of image processing algorithms depending on the end use of the video stream. Algorithms range from low-level processing, whereby operations are performed uniformly across a complete image or sequence, to high-level procedures such as object tracking and identification. Low-level techniques are generally highly parallel, repetitive and require high throughput, making them attractive for implementation in hardware. Moreover, operations are generally a function of a localized contiguous neighborhood of pixels from the input frame, which can be exploited in data reuse schemes. Note that the serialization of video frames using raster-scanning means that significant portions of the video stream may need to be stored, despite the data locality of a particular algorithm. Examples of image processing algorithms include image segmentation, noise elimination and morphological erosion and dilation. These operations find applications in robot vision and machine vision. Image processing algorithms can be classified in 4 categories which are applied to alter a pixel of a set of values to make an image more suitable for subsequent operations:

- Point operations

- Global operations

- Neighborhood operations

- Temporal operations

These categories cover simple algorithm operations. Many higher-level algorithms may be formed from combinations of operations from these five categories. An important requirement of video processing is the real-time i.e. the processing should be fast enough so that the result is meaningful for the user. For example, the processing in a video-based autonomous car should be fast enough in detecting pedestrians so that the car can be able to avoid them. Real-Time is the term used to describe a class of video processing system in which the video signal is processed at the rate of video capture such that the rate of generating output pixels matches the rate of receiving input pixels. Real-time video processing is computationally demanding but often highly parallelizable, making it amenable to hardware implementations.

#### I.1.3 Image processing implementation

Image processing algorithms are usually written in high level languages such as OpenCV, C++ and executed within software based processors such as General Purpose Processors (GPP) and Digital signal processors (DSP). A GPP typically has a generic instruction set that is not optimized for any particular application [10]. There are several issues limiting their applicability in real-time processing systems. The main issue is due to the fact that a GPP does not offer any type of specialized hardware support for specific or repetitive operations found in digital processing algorithms. A DSP, on the other hand, has a specialized instruction set with dedicated hardware support for operations commonly used in digital signal processing algorithms [11]. As a consequence, this type of implementation platform has a better throughput but lacks the flexibility of programmable hardware processors such as Application Specific Integrated Circuits (ASICs) and Field programmable gate arrays (FPGA). ASICs are fabricated and made for special or dedicated applications. This means that their precise functions and performance are considered and fully analyzed before fabrication. The consequence is efficiency, reliability and high performance. However, changes in system requirements which might be due to an oversight or a changing system demands results in a complete replacement of the device because the architecture in ASICs cannot be altered. An FPGA is a reconfigurable implementation platform which typically consists of logic blocks, interconnects (routing), and I/O blocks [12]. An FPGA also offers the possibility of exploiting parallelism, resulting in an increased performance compared to GPPs and DSPs. Compared to ASIC, FPGA technology offers flexibility and rapid prototyping capabilities in favor of faster time to market. A design concept can be tested and verified in hardware without going through the long fabrication process of custom ASIC design. You can then implement incremental changes and iterate on an FPGA design. For these reasons, FPGA are used as alternative for video and image processing systems.

#### I.2 FPGA

Field programmable gate arrays (FPGA) are configurable integrated circuits containing programmable logic that can be used to design digital circuits. Modern FPGAs acting as true system-on-chip (SoC) devices with integrated memory, microprocessors, digital signal processing (DSP) elements, high-speed transceivers, clock management, and

numerous other features. The basic elements of FPGAs are configurable logic blocks (CLB) connected together via a hierarchy of routing resources and programmable switch matrices. Each CLB contains a relatively small amount of memory and some logic resources that may be programmed to implement the desired function, with the memory acting as a look-up table (LUT), RAM, or a shift register. When configured as a LUT it may be used to replicate combinatorial and sequential logic, and CLBs may be chained together to implement logic functions of any size. LUTs provide the main resource for implementing logic functions. LUTs can also be configured as a Distributed RAM or as a 16-bit shift register [13]. The storage elements can be programmed as either a D-type flip-flop or a level-sensitive latch in order to provide a means of synchronizing data to a clock signal. Wide-function multiplexers effectively combine LUTs in order to permit more complex logic operations. The carry chain, together with various dedicated arithmetic logic gates, supports rapid and efficient implementations of mathematical operations. To enable connections between logic elements themselves and between logic elements and any other parts of the chip, the FPGA contains the interconnect. It is an important feature that ultimately determines device performance. It is essentially a network of interconnecting wires with switching matrices at crossover points comprised of pass-transistors and multiplexers programmable routing resources take up a large proportion [13]. Interconnects provide the mechanism for routing signals between logic cells, memory blocks, DSP blocks and I/O pins inside the FPGA. Interconnects are usually optimized for efficient signal transport based on the signal frequency and the distance between the signal source and the sink to ensure predictability, signal integrity and performance repeatability. In addition to these basic components, on-chip blocks of memory are also provided. Many of the FPGA designs require some kind of fast memory for temporary storage of intermediate results, data buffers and other. For this reason, the chip contains embedded memory blocks. These are hardened SRAM memory units, usually configurable for different memory sizes, data widths or single/dual port access. The reconfigurability feature as well as hardware parallelism of the FPGAs offers significant advantages in many applications. However, there are a number of challenges to system development particularly in the field of video and image processing.

#### I.3 FPGA for rapid prototyping of embedded video applications

Embedded video systems are usually composed of deeply integrated hardware and software components to achieve complexity and performance. Low-level repetitive computations on huge amounts of data are mapped into hardware, while complex reasoning parts are maintained in software. There are several challenges to embedded video system development in FPGAs. Some of these challenges include the design reuse, design flow, resources usage and design verification. They will be discussed in the following sections.

#### I.3.1 Design reuse

Design reuse is the use of a library of intellectual property (IP) cores to build a desired circuit. The library implement functions of high complexity (e.g., a DCT or a filter) and systems are built bottom-up by selecting designs from the library and connecting them together. Bottom-up block-based design reuse has limited scalability due to the design cost of integration. System-level interconnect and logic must be custom designed for each implementation, the complexity of which grows exponentially with block number. Functional and performance verification are difficult. These issues are addressed by using a standardized communication architecture, such as Open Core Protocol (OCP) [23], WISHBONE [8], AMBA [4]. Standardizing block interfaces precludes compatibility issues; while the communication architecture implementation is itself a parameterized circuit which can be reused. The block design process can be simplified as well by isolating the interaction between blocks from their functionality. By using pre-designed components, the main design task moves from designing components from scratch and interconnecting them to simple integration of existing IPs. Unfortunately, this process can be very difficult and integration burdens can quickly offset the benefit of IP-reuse. IPs are available with various interfaces, which limit data exchange among interface with different communication protocols and data access mechanism. Research in interface synthesis has sought to automatically generate glue-logic between components with different interfaces. The lack of formalism and standard in existing interfaces as well as the infinite number of potential protocols and communication mechanism makes it impossible for a single tool to target the general purpose case and provide a universal synthesis methodology. Standard interfaces such as Avalon-streaming [1] from Altera,

AXI4-Stream [25] from Xilinx among others, lack the formalism required to capture all facets of the interface. They often lead to a poor timing, higher resource usage and higher power consumption; the main reason being their general purpose orientation.

#### I.3.2 Design flow

Software design environments, such as OpenCV, are very popular in the software community for the design of video-based systems. While those frameworks increase the productivity by providing a rich set of library function for image and video manipulation and machine learning, they are limited to target only general purpose processors. As a consequence, there is a need to map applications captured in those framework onto dedicated hardware/software architecture while performing verification tasks. Manual translations would be time consuming, error-prone, and would require hardware design skills not available in the image processing community, the bulk of which is made upon software designers. In some systems the hardware part is fixed, but the increasing demands on performance and quality requires more and more that the hardware fulfills very special requirements and that it is precisely adjusted to the embedded software. As a consequence, it is often no longer sufficient to use prefabricated hardware components. Traditionally, hardware devices are implemented by low-level coding in hardware description language (HDL). This approach is very remote from the high level specification tool and can be a very tedious task and need special expertise for image processing algorithms. An easier path is to use high level languages (HLL). These include C/C++, Java, MATLAB [8]. many works have focused on synthesizing hardware from C. De Micheli [14] summarized the major research contribution in the use of C/C++ for hardware modeling and synthesis while Edwards [15] provided in detail, challenges to hardware synthesis from C-based languages. It was observed that the approach generates inefficient hardware due to difficulties in specifying or inferring concurrency, time, type and communication in C and its variants. To these ends, modeling languages such as System [1] have been optimized to efficiently overcome some of these shortcomings (for example, both handling concurrency through process-level parallelism) and are often employed to capture the system behavior in the form of executable specifications. The SystemC library has layers of increasing abstraction, enabling hardware to be modeled at different levels. In addition, since systems are usually composed of deeply integrated

hardware and software components to achieve complexity and performance, these components must be designed together. This leads to hardware/software co-design. An essential component of co-design methods is HW/SW co-simulation, which is necessary to evaluate and compare different design alternatives. In a HW/SW co-simulation, hardware and software parts of a system are simulated together. This provides an integrated way to simulate the interactions between hardware and software. The main challenge in HW/SW co-simulation is that hardware and software designers talk in different languages. They use different abstraction levels, different models of computation, different programming languages and different tools. These differences make it complicated to bring the design processes together and to unify them in a single co-simulation framework.

#### I.3.3 Resources usage

The essential resources on FPGAs are arithmetic and logic resources, embedded memory and logic cells. They are available in an optimized form but in limited amounts [8]. It is necessary to have a balanced usage of these resources in an application in order to avoid a shortage of one type of resource while having an excess of others. For instance, an example temporal algorithm would be to detect motion by subtracting a frame from the previous one. This would require frame buffering, and it is clear that whenever processing is required that utilizes the temporal dimension of video data the storage requirements increase rapidly. Alternatively, global operations involve high speed processing, as multiple passes through the image data will usually be required; this will increase the memory requirement and pose implementation challenges in timely processing of the data. It is clear that on-chip memory is an important resource that can quickly become scarce. This kind of temporal processing, where data sets are comprised of elements that do not arrive in sequence but are distributed in time, is common in many video applications but because of high data rates can often involve a significant requirement for memory resources.

#### I.3.4 Verification

Video-based autonomous systems are used in critical areas such as unmanned aerial systems (UAS) and autonomous vehicles with high safety standards, which can only be provided by a sound verification process. As FPGA capabilities and design

complexities increase, verification and simulation also become more complex. Verification of logic designs is at present carried out predominantly through RTL simulation, using event-driven HDL simulators. It is the responsibility of the designer to produce testbenches that correctly drive the simulation software and cover a sufficient range of test cases to ensure the original specification is being met. Due to the fact that testbenches are not synthesized the full extent of VHDL or Verilog instructions may be used, which provides a considerable number of additional capabilities over HDL that is to be synthesized, but designing the testbench and performing the simulation is still a lengthy and complicated process.

#### I.4 Objective

It is therefore imperative to provide an automatic approach for the translation process, while minimizing the resources involved and insuring correctness of design through verification. This can be addressed by exploiting:

- High-level system modeling: to define concepts necessary for modeling embedded vision-based systems through SystemC/TLM.

- Transformations: to develop necessary model to model transformation rules, in order to allow subsequent refinements down to the hardware/software implementation.

- Verification and analysis: to develop methods to verify and analyze models, in order to guarantee that the final implementation corresponds with the initial system specification.

The objective of this dissertation is: to demonstrate the feasibility of a high-level framework for the rapid design and verification of embedded vision-based systems. The approach allows capturing computer vision application at a highest abstraction-level with subsequent refinements and verification down to the hardware/software implementation.

#### I.5 Contributions

The contributions of this dissertation are as follows:

• A novel streaming interface, called Component Interconnect and Data Access (CIDA), for embedded video designs, along with a formal model and a component

composition mechanism to cluster components in logical and operational groups that reduce resource usage and power consumption.

- A design methodology for rapid prototyping of system-on-chip with emphasis of embedded video applications. It leverages existing tools and provides a means to facilitate their integration toward a semi-automatic mapping of software specification to hardware/software implementations.

- A verification flow to perform Assertion-based and coverage validation on SoC design at IP level.

These contributions will be discussed at a later stage together with the results obtained by their use. Tests on the performance of the proposed solutions and comparisons with other works are also discussed and were published.

#### I.6 Dissertation outline

The remainder of this dissertation is organized as follows. Chapter II presents an interface methodology to address design reuse problems and a comparison with other interfaces. In chapter III, our design methodology for rapid prototyping of embedded video applications is presented and the verification flow is described in chapter IV. In chapter V, memory synthesis approach is presented for resource optimization. Finally, chapter VI presents conclusions drawn from this research, as well as possible future work.

#### Bibliography

- [1] A. Wilson, "Auto cameras benefit from cmos imagers," 2009. [Online]. Available: http://www.vision-systems.com/display\_article/228883/19/none/none/Feat/Auto-cameras-benefit-from-CMOS-imagers

- [2] G. Cai, B. Chen, K. Peng, M. Dong, and T. Lee, "Modeling and control of the yaw channel of a uav helicopter," *Industrial Electronics, IEEE Transactions on*, vol. 55, no. 9, pp. 3426–3434, 2008.

- [3] O. Špinka, O. Holub, and Z. Hanzálek, "Low-cost reconfigurable control system for small uavs," *Industrial Electronics, IEEE Transactions on*, vol. 58, no. 3, pp. 880–889, 2011.

- [4] B. Ludington, E. Johnson, and G. Vachtsevanos, "Augmenting uav autonomy," *Robotics Automation Magazine*, *IEEE*, vol. 13, no. 3, pp. 63–71, 2006.

- [5] M. Campbell and W. Whitacre, "Cooperative tracking using vision measurements on seascan uavs," *Control Systems Technology, IEEE Transactions on*, vol. 15, no. 4, pp. 613–626, 2007.

- [6] N. Guenard, T. Hamel, and R. Mahony, "A practical visual servo control for an unmanned aerial vehicle," *Robotics, IEEE Transactions on*, vol. 24, no. 2, pp. 331–340, 2008.

- [7] F. Lin, K.-Y. Lum, B. Chen, and T. Lee, "Development of a vision-based ground target detection and tracking system for a small unmanned helicopter," *Science in China Series F: Information Sciences*, vol. 52, no. 11, pp. 2201–2215. [Online]. Available: http://dx.doi.org/10.1007/s11432-009-0187-5

- [8] M. Meingast, C. Geyer, and S. Sastry, "Vision based terrain recovery for landing unmanned aerial vehicles," in *Decision and Control*, 2004. CDC. 43rd IEEE Conference on, vol. 2, 2004, pp. 1670–1675 Vol.2.

- [9] J. Kim and S. Sukkarieh, "Slam aided gps/ins navigation in gps denied and unknown environments," in *The 2004 International Symposium on GNSS/GPS*, Sydney, 2004, pp. 6–8.

- [10] J. L. Hennessy and D. A. Patterson, Computer architecture: a quantitative approach. Elsevier, 2012.

- [11] P. Lapsley, J. Bier, A. Shoham, and E. Lee, "Dsp processor fundamentals," *IEEE SPECTRUM*, 1998.

- [12] W. J. MacLean, "An evaluation of the suitability of fpgas for embedded vision systems," in Computer Vision and Pattern Recognition-Workshops, 2005. CVPR Workshops. IEEE Computer Society Conference on. IEEE, 2005, pp. 131–131.

- [13] S. Mirzaei, "Design methodologies and architectures for digital signal processing on fpgas," Ph.D. dissertation, UNIVERSITY OF CALIFORNIA SANTA BARBARA, 2010.

- [14] G. De Micheli, "Hardware synthesis from c/c++ models," in *Proceedings of the conference on Design, automation and test in Europe.* ACM, 1999, p. 80.

- [15] S. A. Edwards, "The challenges of hardware synthesis from c-like languages," in *Design, Automation and Test in Europe, 2005. Proceedings.* IEEE, 2005, pp. 66–67.

# II Component Interconnect and Data Access Interface for Embedded Vision Applications

Michael Mefenza, Franck Yonga and Christophe Bobda

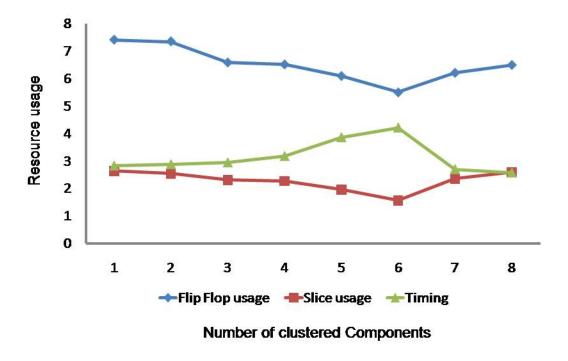

Abstract— IP-based design is used to tackle complexity and reduce time-to-market in Systems-on-Chip with high-performance requirements. Component integration, the main part in this process, is a complicated and time-consuming task, largely due to interfacing issues. Standard interfaces can help to reduce the integration efforts. However, existing implementations use more resources than necessary and lack of a formalism to capture and manipulate resource requirements and design constraints. In this paper, we propose a novel interface, the Component Interconnect and Data Access (CIDA), and its implementation, based on the interface automata formalism. CIDA can be used to capture system-on-chip architecture, with primarily focus on video-processing applications, which are mostly based on data streaming paradigm, with occasional direct memory accesses. We introduce the notion of component-interface clustering for resource reduction and provide a method to automatize this process. With real-life video processing applications implemented in FPGA, we show that our approach can reduce the resource usage (#slices) by an average of 20% and reduce power consumption by 5% compared to implementation based on vendor interfaces.

**Keywords**— Interface Formalism, Computer Vision, Functional Verification, FPGA.

#### II.1 Introduction

Embedded vision applications are increasingly complex, in part because of the huge amount of functionality required by customers, the huge amount of data delivered by high-density sensors and complex computation to apply on those data in real-time. With the well established component-based design approach, complexity can be tackled and time-to-market of embedded vision applications reduced by using pre-designed and pre-verified components to assemble large and complex systems. Using off-the-shelf components, the main design task moves from designing components from scratch and

interconnecting them to simple integration of existing IPs. Unfortunately, this process can be very difficult and integration burdens can quickly offset the benefit of IP-reuse. IPs are available with various interfaces, which limit data exchange among interface with different communication protocols and data access mechanism. One way to address this issue is to insert protocol transducers or wrappers between IPs with incompatible protocols. The result is an increase in resource usage and design effort, with a negative impact on time-to-market. Research in interface synthesis has sought to automatically generate glue-logic between components with different interfaces. The lack of formalism and standard in existing interfaces as well as the infinite number of potential protocols and communication mechanism makes it impossible for a single tool to target the general purpose case and provide a universal synthesis methodology. Standardization is the path adopted by companies to address the interfacing issue. It forces IP designers to use a well described and implemented interface, thus making the integration easier. However, standard interfaces such as Avalon-streaming[1] from Altera, AXI4-Stream[25] from Xilinx among others, lack the formalism required to capture all facets of the interface. They often lead to a poor timing, higher resource usage and higher power consumption; the main reason being their general purpose orientation.

To address these issues, we propose a novel streaming interface, called Component Interconnect and Data Access (CIDA), for embedded video designs, along with a formal model and a component composition mechanism to cluster components in logical and operational groups that reduce resource usage and power consumption. Even though CIDA can be used for the design of any Systems-on-Chip, design efforts were made for the use in video processing applications, which usually require access to image data from various sizes and various sources. Local access is performed to access local buffers, neighbor processed data, and global memory data, all of which represent part of, or entire images at different levels of the processing chain. With real-life video processing applications, our approach was able to achieve a reduction of 20% in resource consumption and 5% in power consumption with a considerable reduction in the overall design time.

The rest of the paper is organized as follows: Section II.2 introduces a motivation example for a better understanding of the problem addressed in this work. Related research regarding streaming interfaces and component-based design methodology is discussed in section II.3. We present our proposed interface formalism in section II.4, followed by its implementation in section II.5. Section II.6, section II.7 and

section II.8 respectively presents system integration, resource optimization and functional verification support, Experimental results with real-life applications implemented in FPGAs are provided in section II.9. Finally, section II.10 concludes the paper.

#### II.2 Motivation example

Generally, interfaces are separated from the core functions, so the IP core can be easily and quickly integrated into different system platforms utilizing different protocols, by simply changing the interface logic wrapper without altering the core logic function. Our main objective is to provide a formalized streaming interface with a means to minimize logic resources and the total area by appropriately composing components using that interface. The formalism is used to describe and manipulate the constraints under which independently developed components can properly operate together. Furthermore, it helps specifying resource optimization and verification objectives, thus simplifying the use of external tools for optimization.

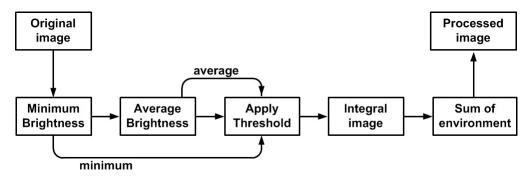

Consider the example of figure II.1 where 3 components with registered-input and output, using the same interface with different component-logic. Because component-based design sees the components as separated entities with separate interface, the 3 components can be connected serially, as in figure II.1-a, thus using three times the same interface. Clustering 2 of the 3 components (Figure II.1-b) leads to less resource usage. The main reason is that the interface of a clustered group of components usually uses less amount of resources than the separated implementation. Reducing resource usage will lead to a reduction in power consumption and sometimes to an improvement of the timing, as many of our experiments have confirmed. Figure II.1-b and figure II.1-c show different clustering possibilities, all leading to different results. We intend in this paper to study the impact of different configurations on the overall system.

#### II.3 Related Work

The bandwidth requirements of video processing applications can be achieved using a stream processing model where applications data are organized as streams of data which flow through a composition of producer/consumer components using a streaming interface. A streaming interface description concentrates on the input/output behavior abstracting it from the component's internal structure.

**Figure II.1**: Motivation example. In (a) the 3 components are connected serially while in (b) and (c) they are clustered.

There are few streaming interfaces available for FPGA. Xilinx provides AXI4-Stream [25] and Altera respectively the Avalon-streaming [1] for their FPGAs. However, those interfaces use more resources than the user usually needs. Moreover, they do not provide the formalism needed to capture interface properties and devise input for synthesis and verification tools. Interface formalism provides a means to unambiguously describe and manipulate constraints under which independently developed components can work properly together. Streaming architectures can also be organized in structures in which neighbors communicate directly through dedicated FIFOs [17] [24] [27]. The work in [20] presents the SIMPPL model that uses asynchronous FIFOs to connect different Computing Elements (CEs). FSL (Fast Simplex Link) [24] interface are implemented as 32-bit x 16-deep FIFOs, which helps to decouple the timing of the FSL master from the FSL slave. FERP (Full/Empty Register Pipe) [27] presents a similar architecture as the FSL, but with additional information to coordinate multiple streams of data. The use of FIFOs limits the model to streaming only, with no possibility of global data access as required when entire pictures are stored in the main memory. Furthermore, blind use of FIFOs increases resource usage between components that do not require intermediate storage in their communication link. Several works have focused on generating hardware/software interfaces [15] [12] [21] [11], other have provided BUS

interconnect mechanism such as Open Core Protocol (OCP) [23], WISHBONE [8], AMBA [4] for integration of customized peripherals. The goal is to convert peripheral interface operations into packets that adhere a bus-specific protocol by inserting wrappers in the peripheral. This introduces unnecessary cost in streaming-oriented architectures. In contrast, we target direct communication models and use point-to-point interconnect structure for all on-chip communications. [28] [13] propose a method to generate interface circuits. The proposed solution produces flexible micro architectures from FSM descriptions of the two interfaces to be connected. Knowledge of the protocols of both the sender and the receiver is required. With the infinite number of available protocols and communication paradigms, it is nearly impossible for a single tool to target the general purpose case and provide a universal synthesis methodology.

Different formalisms exist for modeling interfaces, among which are relational interfaces [22], Assume/Guarantee contract [18], Interface Automata [2], and I/O automata [14]. [22] presents a theory of relational interfaces, that is, interfaces that specify relations between inputs and outputs, which is not in the scope of our work, which is IP reusability by a separation of concerns between interface and user-logic. In Assume/Guarantee contracts [18], the assumptions made on the environment and the guarantees provided by the system are modeled as separate sets of behaviors, whereas in interface theories the two are merged into a single model, called an interface. I/O automata and interface automata are formalisms that provide a single model for the input and output actions of a component. The main difference between the two formalisms is that I/O automata are required to be input-enabled, meaning they must be receptive at every state to each possible input action while for interface automata, some inputs may be illegal in particular states, i.e., the component is not prepared to service these inputs in those states. We are using a formalism that bears syntactic similarities to Interface Automata but significant differences arise as we use a lower level of abstraction. While actions in Interface Automata models represent methods and procedure calls, our model uses actions to describe the behavior of hardware signals.

Component-based design techniques are important for mastering design complexity and enhancing re-usability. Components are designed independent from their context of use and may be glued together through their interfaces. This view has led some authors, e.g. [3], [16], [5] to consider a component as a black box and to concentrate on the combination of components using a syntactic interface description of the

components. However, none of these works have provided an implementation and optimization mechanism aimed at reducing metrics such as resource usage and power.

We address the limitations of the previous works with a novel data access interface that reduced IP interactions to the description of data source and destination. The proposed formal model captured the properties of our interface and allows seamless optimization through component clustering and functional verification.

#### II.4 Interface Model

In this section, we present an interface formalism based on Interface Automata(IA) [2], which is used to model interaction between system components and their environment. This interaction is performed by means of input and output actions. Input actions describe the behavior that the component expects (or assumes) from the environment. Output actions represent the behavior it communicates (or guarantees) to the environment.

**Definition 1 (Interface Automaton)** An Interface Automaton is a tuple  $S = \langle Q, q^0, Q^f, A^I, A^O, A^H, \rightarrow \rangle$  where:

- Q is a finite set of states with  $q^0 \in Q$  being the initial state and  $Q^f \subseteq Q$  being the set of final states;

- $A^I, A^O$  and  $A^H$  are pairwise disjoint finite sets of input, output, and hidden actions, respectively, A is the set of all actions i.e.  $A = A^I \cup A^O \cup A^H$ ;

- $\rightarrow \subseteq Q \times A \times Q$  is the transition relation that is required to be input deterministic (i.e.  $(q, a, q_1), (q, a, q_2) \in \rightarrow$  implies  $q_1 = q_2$  for all  $a \in A^I$  and  $q, q_1, q_2 \in Q$ ).

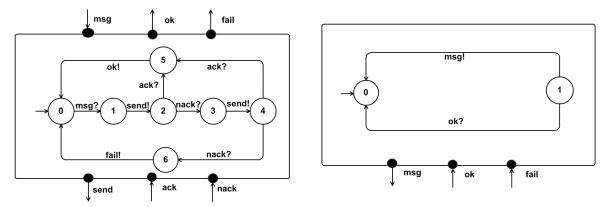

An interface is a shared boundary across which two separate components of a system exchange information. Interface automata are light-weight models that capture the temporal behavior of an interface. The following examples of interface automata are borrowed from [9]. The automaton (Fig. II.2-a) receives and transmits messages over a lossy communication channel. The input actions msg, ack, and nack (resp., send, ok, and fail) are depicted by incoming (resp., outgoing) arrows to the enclosing box, and question (resp., exclamation) marks on edge labels. For the sake of optimization in image

processing, we consider special cases of interface automata (input-only, output-only and input-output).

**Definition 2 (Input-only)** An input-only interface is an interface that can only receive streams or data information.

Input-only interfaces are used in components at the end of image processing chains such as displays, storage or image transfer.

**Definition 3 (Output-only)** An output-only interface is an interface that can only transmit streams or data information.

Output-only interfaces are used in components in front of image processing chains, including cameras, storage and image collectors. Figure II.2-b presents an example of output-only interface which can be used to generate messages for the interface of Fig. II.2-a.

**Definition 4 (Input-Output)** An input-output interface is an interface that can receive and transmit streams or data information.

Input-output interface can be used anywhere in an image processing chain, particularly between two components. Figure II.2-a presents an example of input-output interface that receives streams through its msg port and transmits them through its send port.

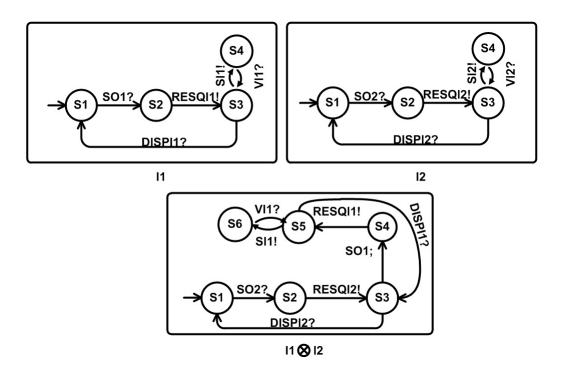

Figure II.2: Interface automata. The automaton is enclosed in a box, whose ports correspond to the input and output actions. The names of the actions are appended with the symbol "?" (resp. "!", ";") to denote that the action is an input (resp. output, internal) action. An arrow without source denotes the initial state of the automaton.

**Definition 5 (Compositionality)** Let S and T be two IA, and let  $shared(S,T) = A_S \cap A_T$  be the set of shared actions. We say that S and T are composable whenever  $shared(S,T) = (A_S^I \cap A_T^O) \cup (A_S^O \cap A_T^I)$ .

The interpretation is that variables in shared(S,T) are outputs of S which are connected to inputs of T. Note that we allow shared(S,T) to be empty, in which case serial composition reduces to parallel composition (where no connections between the two interfaces exist).

**Definition 6 (Product of interfaces)** Let S and T be composable IA. The product  $S \bigotimes T$  is the interface automata defined by:

- $Q_{S \otimes T} = Q_S X Q_T$  with  $q_{S \otimes T}^0 = (q_S^0, q_T^0)$ ;

- $A_{S \otimes T}^{I} = A_{S}^{I} \cup A_{T}^{I} shared(S, T), A_{S \otimes T}^{O} = A_{S}^{O} \cup A_{T}^{O} shared(S, T),$  and  $A_{S \otimes T}^{H} = A_{S}^{H} \cup A_{T}^{H} \cup shared(S, T)$

- $(q_S, q_T) \xrightarrow{a} S \bigotimes T(q_S', q_T')$  if any of the following holds:

- $-a \in A_S shared(S,T), q_S \xrightarrow{a} Sq_S', and q_T = q_T'$

- $-a \in A_T shared(S,T), q_T \xrightarrow{a} Tq_T', and q_S = q_S'$

- $-a \in shared(S,T), q_S \xrightarrow{a} Sq_S', and q_T \xrightarrow{a} Tq_T',$

There may be reachable states on  $S \bigotimes T$  for which one of the components, say S, may produce an output shared action that the other is not ready to accept (i.e. its corresponding input is not available at the current state). Those states are called error states. The composition of 2 IAs is defined as their product without the error states. To describe and perform resource reduction through component clustering, a formalism must be provided for the single components.

**Definition 7 (Component)** A component, C, is a tuple (U, I) where

- U is the core function of C.

- $I = \langle Q, q^0, Q^f, A^I, A^O, A^H, \rightarrow \rangle$  is an interface through which C interacts with other components, for instance, a messaging interface or a procedural interface.

Components are executable units that read data and write data to ports. They are composed of a core that represents the task's functionality and an interface that establishes data transmission on the input/output ports. The component model (Definition 7) provides a framework for representing components and composing them. The interface I of a component can be an input-only or an output-only or an input-output, depending on where it is used in a system.

**Definition 8 (Component clustering)** A component, C = (U, I), can be composed from a set of simpler components,  $C_1(U_1, I_1), ..., C_n(U_n, I_n)$ , as follows:

- U is constructed from  $U_1, ..., U_n$  by connecting  $U_1, ..., U_n$  through their interfaces.

- I is derived from the composition of  $I_1, ..., I_n$ .

The goal of component clustering it to combine a set of simpler components into a unique component with equivalent core logic and an equivalent and resource optimized interface. Using the above formalism, we propose a new streaming interface and a component-composition mechanism to cluster components.

#### II.5 Component Interconnect and Data Access Interface

The need for a new interconnect mechanism was motivated by the desire to allow designers of image processing IP to focus on the functions of their IPs and let the data supply and collection mechanism be taken care of by the interconnect implementation. Data needed by image processing IP can be local, usually small part of images stored in buffer nearby, global with entire images stored in the main memory, or direct, as computation result from neighbor modules. Furthermore, local, direct and global data can be shared by several modules, which requires a coordination. The purpose of CIDA is to provide a simple interface, which would be used by designers to specify the source and destination of their data in a very abstract manner, regardless of the implementation. The designer would then be freed from the implementation of the orchestration and dataflow mechanism, which will be entirely handled in the interface. We have therefore designed the Component Interconnect and Data Access (CIDA), that fulfills the requirement of the interface model presented in section II.4 and provides a set of common features that IP cores can use.

CIDA features include a streaming interface for exchanging data among hardware and DMA for exchanging data with global memories. CIDA can be parameterized to efficiently accommodate different peripherals. To manage local, direct and remote data access, we differentiate between the two main properties of CIDA: CIDA Streaming for streaming-based design and CIDA-DMA for streaming design that incorporate global memory access.

#### II.5.1 CIDA streaming:

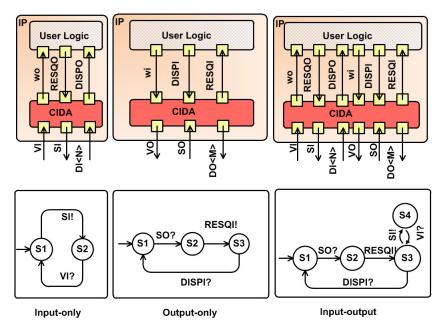

CIDA-Streaming is based on a handshaking protocol with the different configurations and the inputs, outputs and internal signals used to wrap a user logic function as shown in Figure II.3. The data signals are made generic to handle different data width during the streaming.

**Figure II.3**: CIDA streaming. On top, interface description; on bottom, interface automaton.

DI < N > represents the input data with width N, VI a valid data at the input, SI a request for data at the output. DO < M > describes the output data with width M, VO a valid data at the output, SO a request for input data, Wo data sent to User Logic with width N and RESQO a request for data to the User Logic, active low. DISPO signals valid data sent to the User Logic. WI is the data from User Logic, width N, DISPI a valid data from User Logic, RESQI a request for data from User Logic, active low. The

number of signals needed is very limited in the CIDA implementation. When used as input-only, the interface is in state S1 until the User Logic is ready to receive data. The User Logic sets RESQO low to signal it is ready to receive data, the interface sets SI low and waits for a valid data. Upon reception of a valid data, the data are transmitted to the User Logic and the interface returns to the state S1. In the output-only configuration, the interface is in state S1 until it receives a request data. The interface transmits that request to the User Logic and waits for a valid data. Upon reception of a valid data, the data is sent out and the interface returns to the state S1. When used as input-output, the interface is in state S1 until it receives a request for data. The interface transmits that request to the User Logic and waits for a valid data. In order to produce a valid data, the User Logic sets RESQO low to signal it is ready to receive data, the interface sets SI low and waits for a valid data. Upon reception of a valid data at the input, the data are transmitted to the User Logic, processed by the User Logic to produce a valid data at the output. Upon receiving a valid data from the User Logic, the data is sent out and the interface returns to the state S1. The User Logic can request as much data as it needs to produce a valid output. Figure II.3 shows the states and transitions for each configuration. To model the CIDA streaming as interface automaton  $\langle Q, q^0, Q^f, A^I, A^O, A^H, \rightarrow \rangle$  defined in section II.4, we consider the three cases input-only, output-only and input-output separately:

```

- A^{I} = \{VI, DI < N>, RESQO\},

- A^{O} = \{SI, wo, DISPO\},

- A^{H} = \{\emptyset\},

- \rightarrow = \{S1 \xrightarrow{RESQO?} S2, S2 \xrightarrow{VI?} S1\}.

• output-only : I = \langle Q, q^{0}, Q^{f}, A^{I}, A^{O}, A^{H}, \rightarrow \rangle with

- Q = \{S1, S2, S3\}, q^{0} = \{S1\}, Q^{f} = \{S3\},

- A^{I} = \{wi, DISPI, SO\},

- A^{O} = \{VO, DO < M>, RESQI\},

- A^{H} = \{\emptyset\},

- \rightarrow = \{S1 \xrightarrow{SO?} S2, S2 \xrightarrow{RESQI!} S3, S3 \xrightarrow{DISPI?} S1\}.

```

• Input-only:  $I = \langle Q, q^0, Q^f, A^I, A^O, A^H, \rightarrow \rangle$  with

$-Q=\{S1, S2\}, q^0=\{S1\}, Q^f=\{S2\},$

• Input-output :  $I=I=< Q, q^0, Q^f, A^I, A^O, A^H, \rightarrow > \textit{with}$

- $-Q=\{S1, S2, S3, S4\}, q^0=\{S1\}, Q^f=\{S3\},$

- $A^{I} = \{ VI, DI < N >, RESQO, wi, DISPI, SO \},$

- $A^O = \{SI, wo, DISPO, VO, DO < M >, RESQI\},$

- $-A^{H}=\{\emptyset\},$

- $\rightarrow = \{S1 \xrightarrow{SO?} S2, S2 \xrightarrow{a} S3, S3 \xrightarrow{b} S1, S3 \xrightarrow{c} S4, S4 \xrightarrow{VI?} S3\} \text{ where } a = \text{'RESQI!', } b = \text{'DISPI?' and } c = \text{'RESQO?'}.$

#### II.5.2 CIDA DMA:

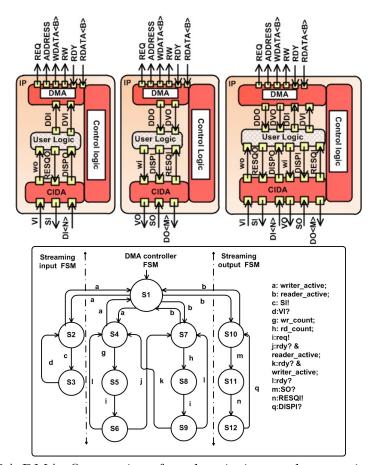

CIDA DMA is made of a streaming interface and a memory-mapped interface. CIDA DMA is used to write incoming streams into a memory frame buffer without processor intervention.

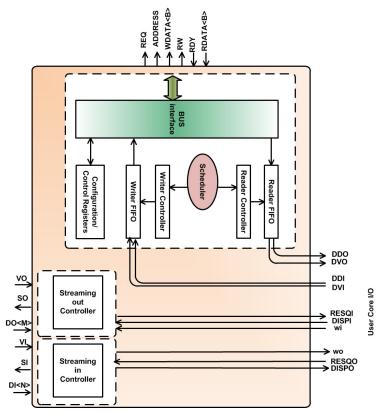

Figure II.4: CIDA DMA. On top, interface description; on bottom, interface automaton.

Reciprocally, images can be read from the frame buffer and streamed out. Figure II.6 shows an implementation of the DMA interface where incoming/outgoing streams are in FIFOs for synchronization and a scheduler is used to coordinate memory reads/writes

and prevent collisions. The scheduling policy is currently based on round robin, but more complex scheduling mechanisms will be implemented in the future. Different configurations are possible as shown in Figure II.4. The corresponding FSM of a configuration is obtained by removing the missing streaming interface from the FSM in figure II.4. DDI represents the DMA input data, DVI a valid DMA input data, DDO the DMA output data, DVO a valid DMA output data. {REQ, ADDRESS, WDATA, RW, RDY, RDATA are memory-mapped signals, which go through a BUS to allow interconnection between multiples DMA interfaces and multiple memories. DMA operations (read/write) can be done in single word or in burst mode. We used FIFOs to store streams for burst operations. Wr\_count is the number of elements in the Write FIFO (Figure II.6) and rd\_count is the number of elements in the Read FIFO. Writer\_active, respectively reader\_active, is used to initialize writing and reading frames to and from memory. Reading and writing frame buffers can be done simultaneously, in which case a scheduler is used to order single-word or burst read/write operations. Figure II.4 shows the states and transitions for each configuration. The control logic contains memory-mapped registers that can be used to reset or start/stop execution of DMA operations from the software. It also contains a set of registers for configuring and gathering the status of IPs. This relieves the designer from implementing memory-mapped registers and bus interface in each IP which needs a configuration from the software. To model the CIDA DMA as interface automaton, we use  $\langle Q, q^0, Q^f, A^I, A^O, A^H, \rightarrow \rangle$  defined in section II.4 we consider the three cases input-only, output-only and input-output separately:

```

• Input-only : I = \langle Q, q^0, Q^f, A^I, A^O, A^H, \rightarrow \rangle with

-Q = \{S1, S2, S3, S4, S5, S6, S7, S8, S9\}, q^0 = \{I\}, Q^f = \{S3\},

-A^I = \{VI, DI < N >, RESQO, DDI, DVI, RDY, RDATA\},

-A^O = \{SI, wo, DISPO, REQ, ADDRESS, WDATA, RW\},

-A^H = \{writer\_active, reader\_active, wr\_count, rd\_count\},