## University of Arkansas, Fayetteville ScholarWorks@UARK

Electrical Engineering Undergraduate Honors Theses

**Electrical Engineering**

5-2013

## Automated Behavioral Modeling of Switching Voltage Regulators

Michael Leonard University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/eleguht

#### **Recommended** Citation

Leonard, Michael, "Automated Behavioral Modeling of Switching Voltage Regulators" (2013). *Electrical Engineering Undergraduate Honors Theses.* 2. http://scholarworks.uark.edu/eleguht/2

This Thesis is brought to you for free and open access by the Electrical Engineering at ScholarWorks@UARK. It has been accepted for inclusion in Electrical Engineering Undergraduate Honors Theses by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

Automated Behavioral Modeling of Switching Voltage Regulators

# Automated Behavioral Modeling of Switching Voltage Regulators

An Undergraduate Honors College Thesis

in the

Department of Electrical Engineering College of Engineering University of Arkansas Fayetteville, AR

by

Michael Leonard

## Abstract

This work describes the development of a software tool that implements a novel method for automatically generating simulation ready behavioral models for switching circuits with an emphasis on power regulators. The work begins by examining the theory of operation of both linear and switching regulators. Then, the capability of two behavioral modeling languages (Verilog-A and PSPICE ABM) are examined in detail. Next, the languages previously discussed are used to develop and test a model of a commercial regulator (Texas Instruments TPS40305). Finally, the prospect of automating the process is discussed. This thesis is approved.

Thesis Advisor:

Dr. Alan Mantooth

Thesis Committee:

## Acknowledgements

I would like to thank the following people, without their support this work would not be possible. Dr. Alan Mantooth for providing the project, facilities, guidance, and securing funding. Dr. Matt Francis for keeping the project on track, providing guidance and reviewing an early version of this work. Rui Mao for working to hand derive models, identify necessary algorithms, and clarifying my questions. Dr. John Stewart for his excellent advising and for offering multiple revisions to this work. Drs. Julio Gea-Banacloche and William Oliver III for offering their time to read my work and serve on my advising committee.

Finally my parents, first my Mom, for keeping me sane on the many late nights I have endured over the years and always providing encouragement and for caring for me more than any other person in the world; and my Dad for his selfless efforts at helping me succeed in whatever I committed to. From the early years of T-Ball and Soccer, to the late nights of Lego League, to helping me with scholarships and then trusting me to handle my business, I can say with certainty that I wouldn't be where I am today without their love. For that, I am forever grateful.

## **Table of Contents**

| Abstract          |                                           |  |  |  |

|-------------------|-------------------------------------------|--|--|--|

| Acknowledgements  |                                           |  |  |  |

| Table of Contents |                                           |  |  |  |

| Table of Figures  | Table of Figures   6                      |  |  |  |

| 1 Introductio     | n to Voltage Regulators                   |  |  |  |

| 1.1 Compa         | rison of Regulator Types9                 |  |  |  |

| 1.2 Comm          | on Applications of Switching Regulators10 |  |  |  |

| 2 Physical Pr     | rinciples of Voltage Regulators           |  |  |  |

| 2.1 Compo         | onent Level 10                            |  |  |  |

| 2.1.1 Re          | esistor                                   |  |  |  |

| 2.1.2 Inc         | ductor                                    |  |  |  |

| 2.1.3 Ca          | apacitor 12                               |  |  |  |

| 2.1.4 Di          | lode [2]                                  |  |  |  |

| 2.1.5 Tr          | ansistor 15                               |  |  |  |

| 2.2 System        | n Level – Linear Regulator                |  |  |  |

| 3 Two Comm        | non Switching Regulator Topologies        |  |  |  |

| 3.1 Buck R        | Regulator                                 |  |  |  |

| 3.1.1 Co          | ontinuous Mode                            |  |  |  |

| 3.1.2 Di          | scontinuous Mode                          |  |  |  |

| 3.1.3 Su          | ımmary                                    |  |  |  |

| 3.2 Boost I       | Regulator                                 |  |  |  |

| 3.2.1 Co          | ontinuous Mode                            |  |  |  |

| 3.2.2 Di          | scontinuous Mode                          |  |  |  |

| 3.2.3 Su          | 11111111111111111111111111111111111111    |  |  |  |

| 4 Switching l     | Regulator Control Schemes                 |  |  |  |

|   | 4.1                                             | Pul     | se-width modulation                            | . 34 |

|---|-------------------------------------------------|---------|------------------------------------------------|------|

|   | 4.                                              | .1.1    | Voltage-mode PWM                               | . 34 |

|   | 4.                                              | .1.2    | Current-mode PWM                               | . 35 |

| 5 | Si                                              | imulat  | ion of Switching Regulators                    | . 36 |

|   | 5.1                                             | Effe    | ects of Switching on Simulation Time           | . 37 |

|   | 5.2                                             | Me      | thods of Reducing Simulation Time              | . 37 |

|   | 5.3                                             | Sele    | ected Modeling Method and Planned Improvements | . 38 |

| 6 | In                                              | ntrodu  | ction to Behavioral Modeling Software          | . 39 |

|   | 6.1                                             | Ver     | ilog-A                                         | . 39 |

|   | 6.                                              | .1.1    | Using Verilog-A and Exploring Capability       | . 40 |

|   | 6.2                                             | PSF     | PICE ABM                                       | . 41 |

|   | 6.                                              | .2.1    | Using PSPICE and Exploring Capability          | . 41 |

| 7 | Μ                                               | Iodeliı | ng a Commercial Regulator                      | . 42 |

|   | 7.1                                             | Mo      | del Development Process                        | . 42 |

|   | 7.2                                             | Aut     | omating the Process                            | . 44 |

| 8 | Se                                              | oftwar  | e Implementation of Automation                 | . 45 |

|   | 8.1                                             | Ten     | nplate Based Approach                          | . 47 |

|   | 8.2                                             | GU      | I Development Process                          | . 48 |

|   | 8.3                                             | Mo      | del Output Algorithms                          | . 51 |

|   | 8.4                                             | Ana     | alysis of Developed Model                      | . 56 |

|   | 8.                                              | .4.1    | Transient Analysis                             | . 56 |

|   | 8.                                              | .4.2    | Frequency Analysis                             | . 58 |

| 9 | С                                               | onclus  | sion                                           |      |

| A | Appendix A: Code to generate models of TPS40305 |         |                                                |      |

| А | Appendix A: PSPICE ABM Reference Sheet          |         |                                                |      |

## **Table of Figures**

| Fig. 1: Typical switching regulator circuit. This particular configuration shows a boost converter  |

|-----------------------------------------------------------------------------------------------------|

| that offers a higher voltage at the output than at the input. This circuit will be discussed more   |

| thoroughly in the following sections                                                                |

| Fig. 2: This configuration is a simple linear voltage regulator. The circuit makes use of resistive |

| losses to dissipate power combined with the voltage stability of the Zener diode to provide a       |

| highly stable output voltage at the cost of potentially high power dissipation                      |

| Fig. 3: Illustration of the difference between electron flow and conventional current               |

| Fig. 4: Capacitor structure showing the dielectric and the induced electric field                   |

| Fig. 5: Diode physical structure                                                                    |

| Fig. 6: Regions of operation of the diode [2]7                                                      |

| Fig. 7: Illustration of device construction of an NPN BJT transistor showing the operation in the   |

| active region9                                                                                      |

| Fig. 8: Regions of operation and I-V characteristics for the BJT [2] 10                             |

| Fig. 9: Illustration of MOSFET construction                                                         |

| Fig. 10: MOSFET regions of operation 12                                                             |

| Fig. 11: Simple Zener regulator with an added emitter follower for increased output current 14      |

| Fig. 12: Simple Zener voltage regulator                                                             |

| Fig. 13: Basic topology for a buck regulator. This circuit is useful for reducing the magnitude of  |

| the input voltage to the required output voltage                                                    |

| Fig. 14: Graph showing the inductor current of a buck regulator operating in the continuous         |

| mode of operation                                                                                   |

| Fig. 15: Graph showing the inductor current of a buck regulator operating in the discontinuous      |

| mode of operation                                                                                   |

| Fig. 16: Equivalent ON circuit of a buck regulator operating in the continuous mode of              |

| operation                                                                                           |

| Fig. 17: Equivalent OFF circuit of a buck regulator operating in the continuous mode of             |

| operation                                                                                           |

| Fig. 18: Equivalent circuit of buck regulator after inductor has expended all of the stored energy  |

| and the current drops to zero                                                                       |

| Fig. 19: Open loop response of the buck regulator, showing the voltage transfer ratio in relation  |

|----------------------------------------------------------------------------------------------------|

| to the duty cycle                                                                                  |

| Fig. 20: Equivalent circuit for the ON State of the boost regulator topology                       |

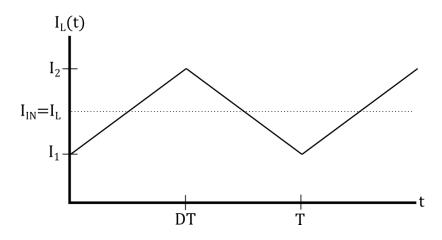

| Fig. 21: Example waveform for the inductor current of a boost regulator operating in the           |

| continuous mode of operation                                                                       |

| Fig. 22: Equivalent circuit for the OFF State of the boost regulator topology                      |

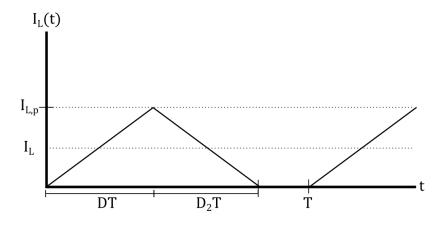

| Fig. 23: Example waveform for the inductor current of a boost regulator operating in the           |

| discontinuous mode of operation25                                                                  |

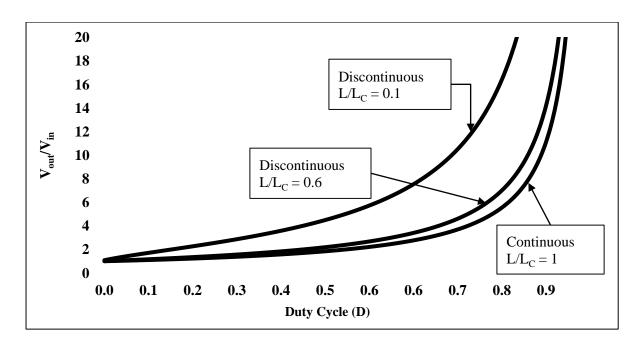

| Fig. 24: Open loop response of the boost regulator, showing the voltage transfer ratio in relation |

| to the duty cycle                                                                                  |

| Fig. 25: PWM controller attached to a buck regulator topology                                      |

| Fig. 26: Proposed new model large signal structure incorporating the diode forward drop and        |

| switch on-resistance                                                                               |

| Fig. 27: PWM switch arranged to model the buck topology [6]                                        |

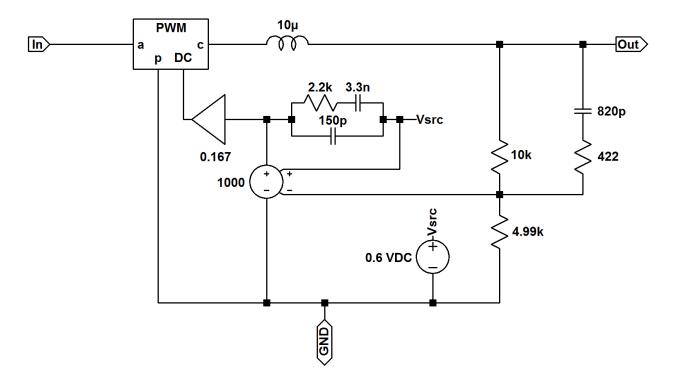

| Fig. 28: Schematic of the internal model of the TPS40305 switching regulator37                     |

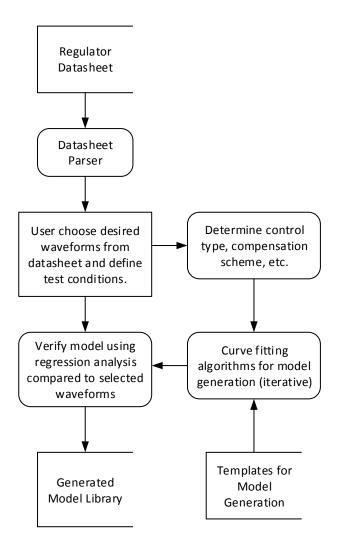

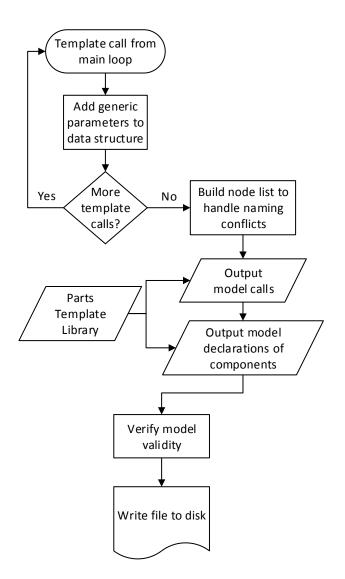

| Fig. 29: Flowchart describing the general flow of the program from the perspective of the          |

| modeler                                                                                            |

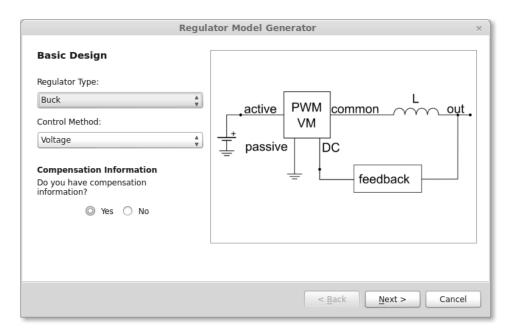

| Fig. 30: The first step in the model generation tool wizard                                        |

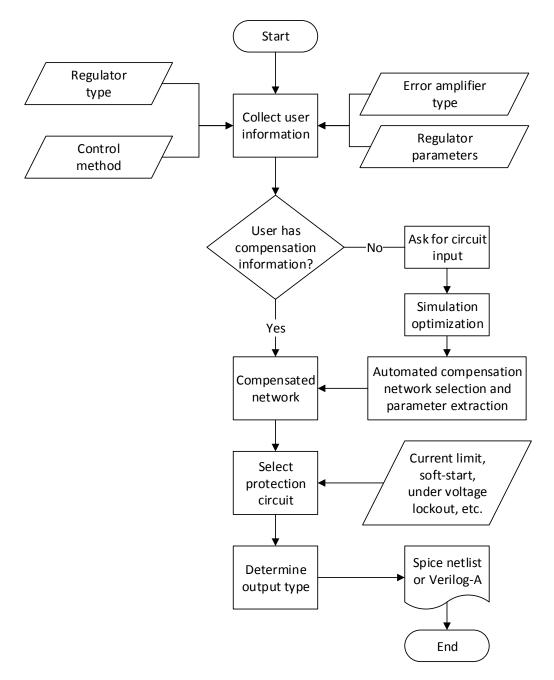

| Fig. 31: Flowchart for the graphical user interface                                                |

| Fig. 32: Categorizing the building blocks of a switching regulator model                           |

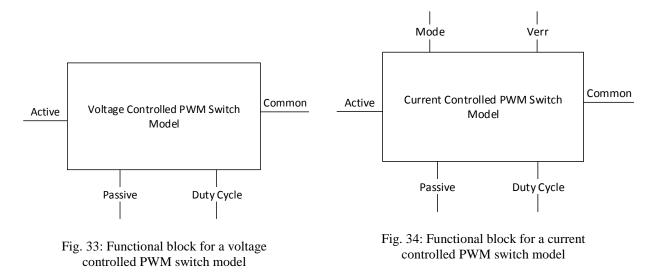

| Fig. 33: Functional block for a voltage controlled PWM switch model                                |

| Fig. 34: Functional block for a current controlled PWM switch model                                |

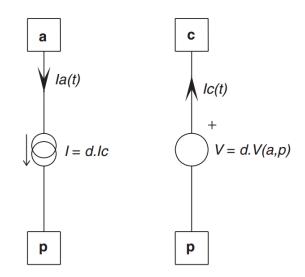

| Fig. 35: Voltage mode PWM arrangement [6]                                                          |

| Fig. 36: Current mode PWM arrangement [6]                                                          |

| Fig. 37: Flowchart showing the process for outputting a generic regulator model                    |

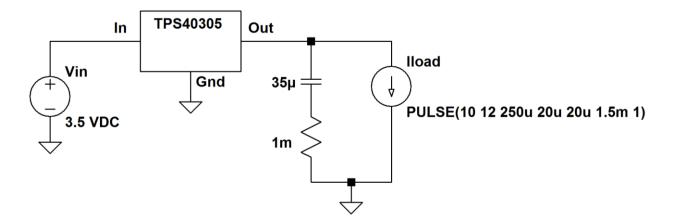

| Fig. 38: Circuit schematic for transient simulation of TPS40305                                    |

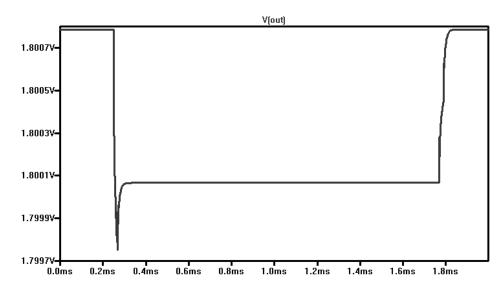

| Fig. 39: Simulation results from a 2ms transient simulation in which the output load current       |

| begins and ends at 1A and is quickly ramped up to a "full" 20A load in the middle section 50       |

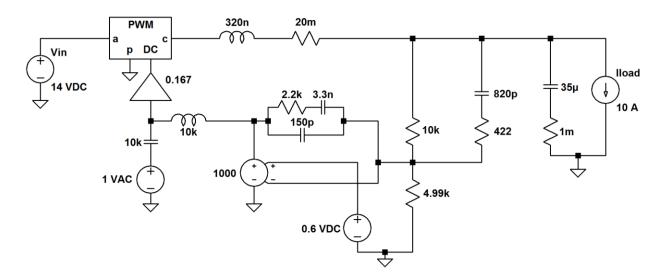

| Fig. 40: Circuit schematic for AC simulation of TPS40305                                           |

## **1** INTRODUCTION TO VOLTAGE REGULATORS

It is very common for electronic devices to require a constant voltage in order to maintain operation. Generally, these devices are designed around fairly generic voltage ranges such as 12V, 5V, or 3.3V. Unfortunately the wall outlet, or a battery, do not deliver these voltages so it is necessary to have some sort of device which will control the supply voltage to keep it in an acceptable range. These voltage regulation devices are referred to as *voltage regulators* and are a key component of nearly every electronic device in use today. There are two common types of voltage regulators. The first, known as a linear regulator, uses mostly passive elements to keep the output voltage steady and relatively independent of the input voltage. The second, known as a switching regulator, uses an active device in a switching configuration to regulate the voltage. Each type has its own advantages and disadvantages that will be discussed further in this section.

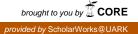

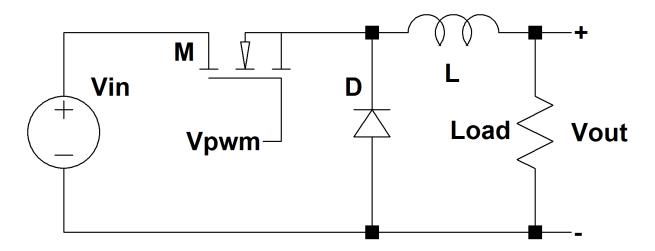

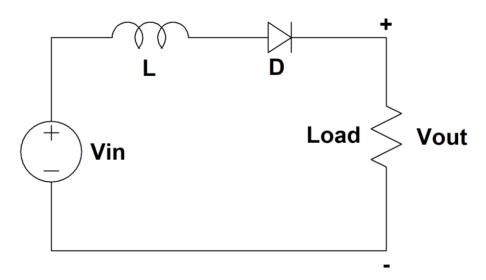

The switching regulator is a power electronics circuit with a wide usage base in modern electronic systems. The basic premise of operation of a switching regulator is to use a switching element, such as a transistor, in conjunction with an energy storage component in order to regulate the voltage and current at the terminals of the circuit.

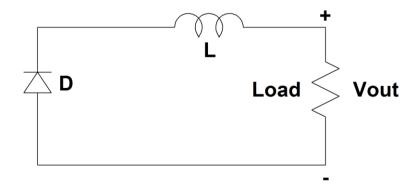

Fig. 1: Typical switching regulator circuit. This particular configuration shows a boost converter that offers a higher voltage at the output than at the input. This circuit will be discussed more thoroughly in the following sections.

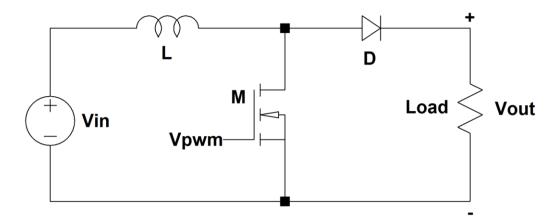

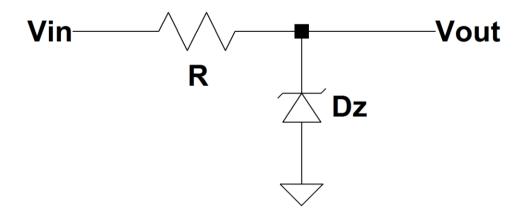

This is in contrast to the also very common, linear regulator. A linear regulator serves the same purpose as a switching regulator but performs the function using a significantly different implementation. Linear regulators utilize resistive losses to dissipate a set amount of power and control the voltage at the output terminal.

Fig. 2: This configuration is a simple linear voltage regulator. The circuit makes use of resistive losses to dissipate power combined with the voltage stability of the Zener diode to provide a highly stable output voltage at the cost of potentially high power dissipation.

#### **1.1 COMPARISON OF REGULATOR TYPES**

These two regulator types have their drawbacks as well as merits, which lend themselves to very different uses. A quick summary of benefits of the two regulator types follows [1]:

- Due to the absence of switching elements, linear regulators are very well suited for applications requiring low supply noise.

- Since current is either being delivered to the load, or not flowing at all, switching regulators are often best when power efficiency is a critical concern.

- For low power levels (< 2W) linear regulators are the superior choice since they are physically smaller circuits.

- At high power levels, switching regulators are the logical choice since they dissipate less power; they also create less thermal radiation.

- Switching regulators are the *only* choice when it comes to supplying a higher output voltage than delivered to the input.

From these generalized conclusions, one can understand possible applications for each regulator type.

## **1.2 COMMON APPLICATIONS OF SWITCHING REGULATORS**

Switching regulators enjoy a wide range of applications in modern electronics. With the combination of low cost, small size, and excellent efficiency, these devices are well suited to a wide array of uses.

| Use Case              | Description                                                                                                                                                                                                                                       |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Computer Power Supply | Nearly all computers require a range of supply voltages from $\pm 12V$ , $\pm 5V$ and others. As a result, switched mode power supplies have become the de-facto standard for use in computing.                                                   |

| Cell Phone Chargers   | Due to the high volume associated with producing cell-phone<br>chargers the circuit designs are very cost-sensitive. Switching<br>power supplies allow for cheaper components inside a smaller<br>package which leads to further cost reductions. |

| Consumer Electronics  | An increasing number of consumer devices such as televisions and<br>even audio devices are using switching regulators to supply steady<br>and reliable supply voltages over a wide range of inputs.                                               |

| Space Vehicles        | As a result of the small size and low weight of switching regulators<br>in comparison to other power supply options, most space vehicles<br>utilize these devices in order to cut down on weight and reduce fuel<br>costs.                        |

Table I: An abbreviated listing of common uses for switching regulators.

## **2** PHYSICAL PRINCIPLES OF VOLTAGE REGULATORS

Before discussing the intricacies of regulator design, an understanding of the physical properties at both the component level and the system level would prove useful.

### 2.1 COMPONENT LEVEL

Every regulator, whether switching or linear, is comprised of some or all of the basic circuit elements. These include components such as resistors, inductors, capacitors, transistors and diodes. Each of these devices will be discussed as an overview and then the system level physics will be examined.

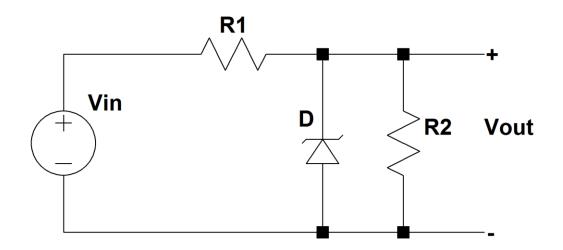

Rather than jumping right in to a discussion of components at the physical level, it should be noted that there are some electric conventions and principles that are a bit counterintuitive. Perhaps the most commonly cited of which is the discord between "conventional current" and "charge carrier current."

Fig. 3: Illustration of the difference between electron flow and conventional current.

Current is used to quantify the flow of electric charge; however, electric charge is either carried by a negative charge carrier (**electron**) or positive charge carrier (**hole**). This implies that a current comprised of negative charge carriers flowing in one direction is equal to a current comprised of an equal amount of positive charge carriers flowing in the opposite direction. For this reason, it is common practice to arbitrarily assume that current flows from an area of higher electric potential to an area with lower electric potential. This arbitrary assignment is known as **conventional current flow** and will be used throughout this work.

#### 2.1.1 Resistor

The resistor is the most fundamental of all circuit elements. It is a passive device that directly relates current flow through the device to the voltage across the device by the following relation, known as Ohm's law:

$$v(t) = i(t)R \tag{1}$$

This equation implies that as the current through the device increases, the voltage across the device increases linearly, as well as the converse.

Using electrons as an example of a charge carrier, electrons are attracted to areas of higher potential; therefore increasing the voltage differential increases the force being applied to the electrons in the resistor and causes an increased current flow.

#### 2.1.2 Inductor

Inductors work on a slightly more complex principle. An inductor is a two terminal passive device that relates to voltage across the terminals to the change in current through the terminals. This relation is given by the following equation:

$$v(t) = -L\frac{di(t)}{dt}$$

<sup>(2)</sup>

A charged particle in motion generates a magnetic field, thus by extension a current generates a magnetic field. Imagine taking a wire and wrapping it around a central axis several times. If one were to pass a current through this wire it would cause the magnetic field lines to wrap around the entire assembly in a manner that would align them with the center axis. Increasing the current intensity causes more field lines to pass through the center of the device. If a changing number of field lines pass through a coil, a voltage is induced in that wire. When the wire is wrapped in the axial configuration of an inductor this causes an opposing voltage to be induced. This effect produces the relation between voltage and changing current.

#### 2.1.3 Capacitor

A capacitor can be considered a complementary device to the inductor. Both are in the same family, utilizing electromagnetic fields to achieve the desired behavior. Like the aforementioned two devices, capacitors are two terminal passive devices. In opposition to the inductor, a capacitor relates the current through the device to the change in voltage across the terminals by the following relation:

$$i(t) = C \frac{dv(t)}{dt}$$

<sup>(3)</sup>

This has the effect of smoothing out voltage changes and is commonly used as a component in filtering circuits.

Much like an inductor, the physics behind capacitors requires a basic understanding of electromagnetics. A basic capacitor is comprised of two parallel plates separated by an electrical insulator known as a dielectric.

Fig. 4: Capacitor structure showing the dielectric and the induced electric field.

Each plate holds an equal but opposite charge that creates an electric field between the two plates. The dielectric material serves to reduce the intensity of the electric field and therefore increases the **capacitance**. Since capacitance is defined as  $\frac{dq}{dv}$  a capacitor can be thought of as a charge storage device.

#### 2.1.4 Diode [2]

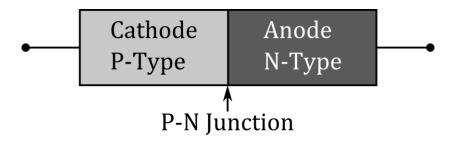

The last of the basic passive devices is the diode. A diode is a semiconductor device made of oppositely doped semiconductors. This creates a device that allows current to ideally flow in one direction but not the other. The figure below illustrates the basic composition of a diode.

Fig. 5: Diode physical structure

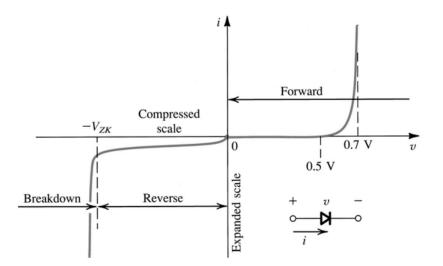

While there are many different types of diodes, the canonical form of the diode is a fairly simple device. The diode is the first device examined which has a current-voltage (I-V) relationship that is non-linear. Diodes generally operate in one of a few regions, the diode can be forward-biased, reverse-biased, or in the breakdown region. The following sections briefly discuss each region of operation.

Fig. 6: Regions of operation of the diode [2]

#### 2.1.4.1 Forward Biased Region

In the forward biased region the diode essentially acts as a short circuit and conducts in a nearly unimpeded fashion. The diode is considered to be in the forward biased region when the voltage across the terminals is greater than zero. In this region, the current through the device can be closely approximated by a diode model known as the Shockley diode equation that is given as:

$$i = I_S(e^{\nu/V_T} - 1)$$

where  $I_S$  is the **saturation current** and  $v_T$  is the **thermal voltage.** This model predicts that as the voltage across the diode increases, the current through the device increases exponentially, which explains why after a certain point the diode behaves as a short circuit.

#### 2.1.4.2 Reverse Biased Region

In the reverse biased region the diode nearly completely blocks the flow of current in the reverse direction. The diode enters the reverse bias region when the voltage difference across the terminals is less than zero and remains in this region until the voltage crosses a threshold known as the **breakdown voltage**.

The current through the device in the reverse bias region is equal to the saturation current of the diode. This arises from the behavior of the material at the boundary known as the **p-n junction**, where the two types of material (p-type and n-type) meet. Applying a voltage differential such that the voltage at the n-type terminal is higher than the voltage at the p-type terminal results in a situation in which the junction forces a **depletion region** and the device transfers only a small

amount of charge carriers between the junction. This situation is what causes the reverse bias effect.

#### 2.1.4.3 Breakdown Region

The breakdown region refers to the region of operation in which the voltage across the terminal has surpassed the breakdown voltage. This causes a complete "breakdown" of the depletion region and results in spontaneous conduction in the reverse direction.

Generally when a diode enters the breakdown region it is considered a catastrophic failure and the device must be replaced. Destruction of the device results from the relatively large voltage applied across the terminals; this large voltage causes the p-n junction to breakdown and to cease operating as a semiconductor device.

In certain cases a diode falling into the breakdown region is not catastrophic. One type of diode, known as the avalanche diode, is actually designed to survive operation in the breakdown region without permanent damage.

Some diodes, known as Zener diodes, are designed to be operated in the reverse bias region. These devices are widely used in linear regulators in order to provide a constant reference voltage and will be discussed in more detail in the following sections.

#### 2.1.5 Transistor

Transistors are perhaps the most complex and broad field of basic circuit elements. The transistor is an active three (or four) terminal device that is commonly used to control either the current through or voltage across a circuit.

A transistor can be thought of as a control station that opens, constricts, or closes to control the flow of charger carriers through two of its terminals. This operation allows for various combinations which have paved the way for nearly every electronic invention since the early 1970's, including radios, amplifiers, switches, televisions, computing, etc.

While the general field of transistors is very broad, by far the two most common types of devices in use today are **bipolar-junction transistors (BJT)** and **metal-oxide semiconductor field effect transistors (MOSFET)**. Each device has merits and will receive proper analysis in the following sections. Generally, BJT's are used when the design requires very high frequency switching while MOSFET's are used for designs that aim for lower bias power draw or higher input impedance.

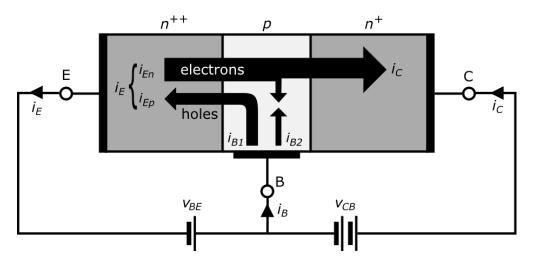

#### 2.1.5.1 BJT

A BJT is a very widely used transistor type developed only a year after the first transistor making it the oldest type of transistor still in use today. The BJT operates as a current control device and comes in one of two configurations, NPN or PNP. In the NPN construction the diode is manufactured as a layer of n-type material, another of p-type material, and another of n-type material. The PNP type is just the opposite order. These devices operate by utilizing the principle of charge injection. As a larger voltage is applied to the center material more charge carriers are injected into the device so that the entire device begins to behave more and more like a short circuit.

Fig. 7: Illustration of device construction of an NPN BJT transistor showing the operation in the active region.

As only a rough understanding of transistor operation is necessary for the following sections, the intricacies of operation will be left to more eloquent writers with fewer page constraints, however the essentials are covered as necessary [2, 3].

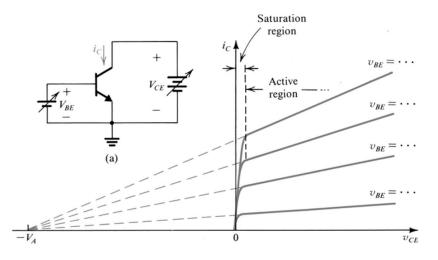

BJT's like diodes and MOSFET's are nonlinear devices with three modes of operation. The regions of operation of a BJT are the **cutoff**, **active**, and **saturation** regions and each one has a specific behavior.

Fig. 8: Regions of operation and I-V characteristics for the BJT [2]

The BJT enters the cutoff region when the base voltage is lower than the emitter voltage and the collector voltage is higher than the base. In this region, the transistor is not conducting. The saturation region is next and is entered when the base voltage is higher than the emitter voltage but the collector voltage is not higher than the base voltage. In this region the current through the device is rapidly rising to reach the maximum collector current. Upon hitting the maximum collector current limit the device enters into the active region in which the collector current is essentially flat. This is the most commonly used region of operation and has many purposes ranging from acting as a resistor to performing signal amplification.

#### 2.1.5.2 MOSFET

The MOSFET is the other most common type of transistor. MOSFET's are relatively new as compared to BJT's; though this has not slowed the adoption rate of MOSFET's and these devices are now being used in applications that were previously reserved for BJT's.

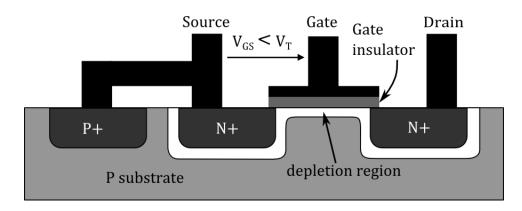

Fig. 9: Illustration of MOSFET construction

The principle of operation for a MOSFET is very different from the BJT. Whereas the BJT relies on charge carrier injection and recombination, the MOSFET utilizes a unique behavior of the semiconductors comprising the device. When a voltage is applied to the gate it causes an effect on the substrate that creates a **depletion region**. Within the depletion region a **channel** is induced between the drain and source that allows for the conduction of charge carriers. As the voltage on the gate increases the size of the channel increases and allows for more charge carrier transportation, therefore allowing more current flow.

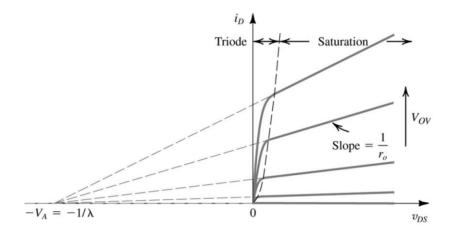

Like a BJT the MOSFET has three distinct regions of operation known as the cut-off, active, and saturation regions; however, somewhat confusingly the active region of the MOSFET is most similar to the saturation region of the BJT and the saturation region of the MOSFET is most similar to the active region of the BJT. The following figure illustrates the three regions of operation of the MOSFET.

Fig. 10: MOSFET regions of operation

Before analyzing the regions of operation it is helpful to introduce a quantity known as the **overdrive voltage**, this quantity is most responsible for determining the charge flowing through the channel and is described by the following relationship

$$v_{OV} \stackrel{\text{\tiny def}}{=} v_{gS} - V_T \tag{4}$$

where  $v_{gs}$  is the small signal voltage from the gate to source and  $V_T$  is the **threshold voltage**, which is a device parameter determined by the manufacturing process.

For all following analysis the device under consideration will be assumed to be an NMOS device in which the substrate is p-type, but by incorporating a reverse in polarity analysis is the same for PMOS devices.

The MOSFET is in the cut-off region whenever the gate-source voltage is less than the threshold voltage. In this region the channel is pinched off and the device does not conduct.

The next region of operation is entered when the drain-source voltage is greater than zero but less than the overdrive voltage as defined above. In this region the device begins conducting and an increase in drain-source voltage causes the induced channel to expand and thus results in an increased current flow. The drain current in this region can be described by:

$$i_D = k'_n \frac{W}{L} \Big[ (v_{gs} - V_T) v_{DS} - \frac{1}{2} v_{DS}^2 \Big]$$

<sup>5</sup>

where  $k'_n$  is another device parameter determined at manufacturing time and  $\frac{W}{L}$  is the width of the device divided by the length of the channel, a quantity known as the **aspect ratio**.

Finally, when the drain-source voltage is greater than the overdrive voltage the MOSFET enters the saturation region. In this region of operation the channel has expanded to its maximum limit and is conducting as much current as possible. Therefore, with an increasing drain-source voltage the drain current is relatively stable. The following relation describes this region:

$$i_D = \frac{1}{2} k'_n \left(\frac{W}{L}\right) (v_{GS} - V_T)^2 \tag{6}$$

Like the BJT, this last region in which the device current is relatively constant under increasing voltage conditions is the region in which the device is most commonly designed to operate. However, for the purposes of a switching regulator the transistor will be operated as a switch and will therefore be driven between the cut-off and saturation regions as quickly as possible. The following sections will analyze a linear and switching regulator, respectively. Each device will utilize the components described in the preceding sections and the operation will be discussed in detail.

#### 2.2 SYSTEM LEVEL – LINEAR REGULATOR

This section focuses on analysis of a linear regulator known as a simple series regulator with emitter follower. This device relies heavily on the aforementioned reverse bias operation of the Zener diode as well as the current amplification of the BJT.

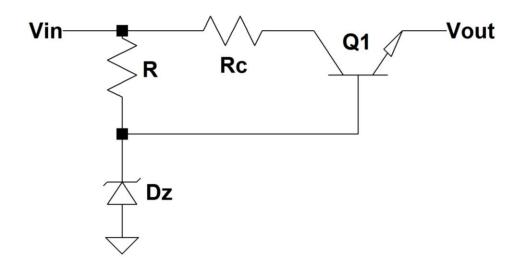

Fig. 11: Simple Zener regulator with an added emitter follower for increased output current

In order to understand the operation of this device however, let us first consider a very similar configuration that does not use the BJT. This design relies solely on the Zener diode to regulate the output.

Fig. 12: Simple Zener voltage regulator

While it was mentioned previously, the Zener diode was not discussed in great detail. The reason for the Zener diode's unusual behavior of holding a steady voltage under reverse-bias results from a physical effect known as the **Zener effect** [4]. The Zener effect occurs as a result of an expansion in the depletion region at the p-n junction, this expansion creates a high strength electric field across the junction that allows for highly stable voltage regulation.

Returning to the regulator shown in Fig. 11, a configuration known as an emitter-follower allows for higher current at the output but otherwise operates on the same principle as the simple Zener regulator.

## **3 TWO COMMON SWITCHING REGULATOR TOPOLOGIES**

There are a myriad of topologies that can be used to implement a switching regulator. As a general introduction, this work focuses only on the two most common; however, the developed tool and method for modeling these circuits allows for the modeling of any generic pulse width modulated switching regulator. Specifically, this section focuses on Buck and Boost regulators that serve as the building block of most modern voltage regulation circuits [5]. Throughout analysis, there will be a number of important assumptions and definitions that will be used unless otherwise noted:

- 1. The transistor is driven by a periodic signal.

- 2. The duty cycle of the converter is defined as the ratio of the time the transistor is on to the time the transistor is off, this is assumed to be a variable quantity.

- 3.  $t_{on}$  refers to the time in which the transistor is on and current flows through the device

- 4.  $t_{off}$  refers to the time in which the transistor is off and current is not flowing through the device

- 5. The switching period, *T*, is the inverse of the switching frequency, or the sum of  $t_{on}$  and  $t_{off}$ .  $T = \frac{1}{f_s} = t_{on} + t_{off}$

- 6.  $t_{on}$  and  $t_{off}$  can be related to the duty cycle by  $t_{on} = DT$  and  $t_{off} = (1 D)T$ .

- 7. While the load is depicted as a resistor, the load on a voltage regulator is rarely, if ever, purely resistive.

- 8. The regulator has already completed the startup process and has reached steady state operation.

#### **3.1 BUCK REGULATOR**

The buck regulator topology is a step-down regulator in that the voltage at the output is smaller than the voltage at the input, and is of the same polarity. Additionally the output voltage is directly proportional to the input voltage multiplied by the duty cycle of the switching element; therefore, the following relations describe most basic features of the buck regulator [5].

$$0 \le V_{out} \le V_{in} \tag{7}$$

$$V_{out} = V_{in}D \tag{8}$$

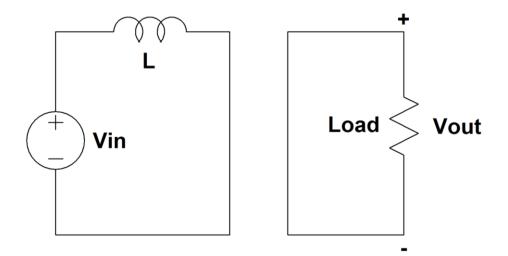

While it is important to understand the basic operation of the buck regulator topology, it is much more useful to understand the theory of operation so that a simulation model can be derived. In order to develop such an understanding, it is instructive to examine the canonical circuit topology that is shown in Fig. 13.

Fig. 13: Basic topology for a buck regulator. This circuit is useful for reducing the magnitude of the input voltage to the required output voltage.

A full treatment of the buck topology, as well as the other common topologies, can be found in [5]. For the purpose of developing a behavioral model, a basic understanding of the principles of operation will be sufficient.

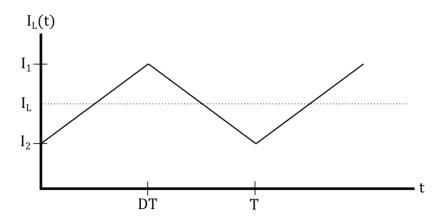

Analysis of the buck regulator is conceptually simplified by dividing the operation into two modes, continuous and discontinuous operation. In **continuous mode** the current through the inductor ( $I_L$ ) either never becomes zero as shown in Fig. 14, or only becomes zero at a singular point.

Fig. 14: Graph showing the inductor current of a buck regulator operating in the continuous mode of operation.

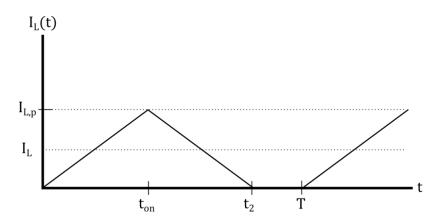

Conversely, in **discontinuous mode** the inductor current may drop to zero for an indefinite period as shown in Fig. 15.

Fig. 15: Graph showing the inductor current of a buck regulator operating in the discontinuous mode of operation.

#### 3.1.1 Continuous Mode

Consider a buck regulator topology that is guaranteed to be in the continuous mode of operation. The circuit can be in one of two states; either the transistor is ON, or the transistor is OFF. These two states will be referred to as the **ON State** and **OFF State**.

In the ON State the equivalent circuit for the regulator is shown in Fig. 16:

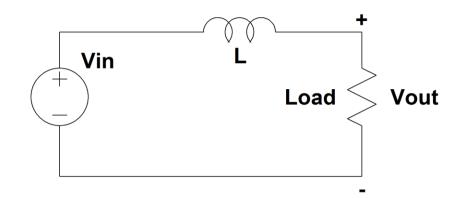

Fig. 16: Equivalent ON circuit of a buck regulator operating in the continuous mode of operation.

From this equivalent circuit, the difference between  $V_{in}$  and  $V_{out}$  is the voltage drop across the inductor ( $V_L$ ):

$$V_{in} - V_{out} = V_L = L \frac{di}{dt}$$

<sup>(9)</sup>

In the case where the current is continuous the current has the form:

$$\frac{di}{dt} = \frac{l_2 - l_1}{t_{on}} \tag{10}$$

Substituting this into the preceding equation and solving for  $t_{on}$  yields:

$$t_{on} = L \frac{I_2 - I_1}{V_{in} - V_{out}}$$

11)

In the OFF State the equivalent circuit for the regulator is shown in Fig. 17:

Fig. 17: Equivalent OFF circuit of a buck regulator operating in the continuous mode of operation.

Since it is impossible to instantaneously change the current flowing through an inductor, a phenomenon known as "inductive kick" causes the voltage polarity across the inductor to immediately reverse. [3] This reversal forces  $V_L = -V_{out}$  therefore:

$$-V_{out} = L \frac{I_1 - I_2}{t_{off}}$$

(12)

solving this equation for  $t_{off}$  yields:

$$t_{off} = L \frac{I_2 - I_1}{V_{out}}$$

13)

In steady state operation the term  $I_2 - I_1$  is the same during the ON State and the OFF State, therefore:

$$\frac{V_{in} - V_{out}}{L} t_{on} = \frac{V_{out}}{L} t_{off}$$

(14)

Simplifying and substituting the known values for  $t_{on}$  and  $t_{off}$  gives:

$$V_{out} = DV_{in} \tag{15}$$

The buck regulator multiplies the input voltage by the duty cycle of the switching signal. Since D < 1, the output voltage will always be less than the input voltage.

#### **3.1.2 Discontinuous Mode**

Many regulators enter the discontinuous mode while operating light loads, so it is also important to analyze the buck regulator while it operates in this mode. The regulator enters discontinuous mode when the inductor current drops to zero for longer than an instant. As before, analysis is simplified by considering the regulator in the On State and the Off State separately and then combining the derivations to encompass the overall circuit behavior.

To mathematically determine if the regulator is in the discontinuous mode, the inductance value must be compared to the **critical inductance** of the switching regulator. The critical inductance is purely a design parameter for the regulator and is used as a check so that the designer can know whether the device will enter discontinuous mode or not. This value can be calculated by:

$$L_C = \frac{R(1-D)}{2f_S} \tag{16}$$

where *R* is the resistive load, *D* is the duty cycle, and  $f_s$  is the switching frequency. Using this term the regulator is defined as operating in the discontinuous conduction mode if  $L < L_c$ . One other important consideration is that, like the analysis of the continuous conduction mode, the discontinuous conduction mode can be considered to be in a certain state. However, due to the

fact that the inductor current can remain at zero for a period of time, it is important to consider this in analysis. Therefore the regulator can be considered to be in one of three states:

State 1. ON StateState 2. OFF State (Discharging)State 3. OFF State (Discharged)

The behavior in states 1 and 2 are the same as derived previously for the continuous mode; however, state 3 describes a new behavior that did not previously need to be considered.

Fig. 18: Equivalent circuit of buck regulator after inductor has expended all of the stored energy and the current drops to zero.

In this state, the inductor has expended all of its stored energy and current is no longer flowing to the load as a result of the regulator. It is important to remember though that since the load can be, and usually is, a reactive load this loss of current does not necessarily mean that the output voltage drops to zero. As has been derived in other works [5, 6, 7] the input/output voltage relationship is given by:

$$\frac{V_{out}}{V_{in}} = \frac{2}{1 + \sqrt{1 + \frac{4L(1-D)}{L_C}}}$$

17)

#### 3.1.3 Summary

The buck regulator is a useful topology for producing a lower output voltage than is supplied to the input. This characteristic occurs as a result of the topological configuration of the switching element that causes the inductor to only store enough energy to deliver a reduced voltage to the output. In the boost configuration, the switching element will be repositioned so that it is topologically positioned "after" the inductor. The effect of this change will be developed in the next section. Table II shows a few useful references that will be utilized in the following sections in order to derive and verify a behavioral model for the buck regulator.

| Mode          | Requirement | Voltage Ratio Function                                              |

|---------------|-------------|---------------------------------------------------------------------|

| Continuous    | $L > L_C$   | $V_{out}/V_{in} = D$                                                |

| Discontinuous | $L < L_C$   | $V_{out}/V_{in} = \frac{2}{1 + \sqrt{1 + \frac{4L(1-D)}{D^2 L_C}}}$ |

Table II: Summary of voltage transfer equations for the various modes of operation for a buck regulator

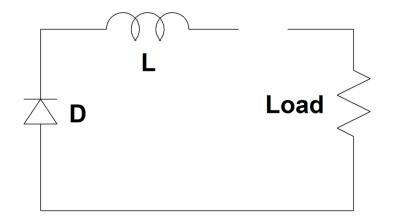

Fig. 19: Open loop response of the buck regulator, showing the voltage transfer ratio in relation to the duty cycle.

#### **3.2 BOOST REGULATOR**

The boost regulator (Fig. 1) is another building block of switched-mode power supplies. This particular topology is used to supply a higher voltage at the output than at the input. Analysis for the boost topology will proceed in a similar manner to the previous section in which the buck topology was analyzed. As before, for the purposes of behavioral modeling the intricate details of operation are not of great concern. Thus the topology will only be developed so far as to offer an appreciation for the principles of operation.

#### **3.2.1** Continuous Mode

Much like the analysis of the buck regulator, the boost regulator is most easily analyzed by dividing operation into two functional states. These states will be referred to by the previously established convention of ON and OFF.

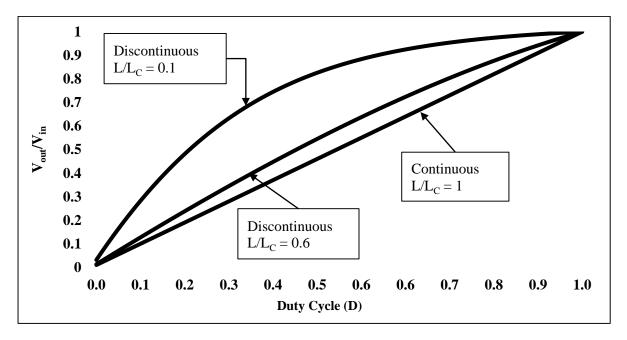

Fig. 20: Equivalent circuit for the ON State of the boost regulator topology.

In the ON state, the switching element creates a short circuit so that the supply voltage and the inductor form a closed loop while the load is its own loop as well. In this state the input is supplying a voltage that induces a constantly increasing inductor current from  $I_1$  to  $I_2$ , this is described by the following:

$$I_2 - I_1 = \Delta I = t_{on} \frac{v_{in}}{L} \tag{18}$$

While the transistor is on, the input is essentially disconnected from the output and the output current is being supplied from the output capacitor. The output capacitor has already reached steady state operation and has enough built up charge to keep the voltage relatively constant.

Fig. 21: Example waveform for the inductor current of a boost regulator operating in the continuous mode of operation.

In the OFF state, the transistor ceases to conduct and the input voltage is connected to the rest of the circuit. When this happens, the voltage across the inductor reverses polarity in order to maintain a constant current. During this time the inductor is transferring its stored energy into the output capacitor, this transfer of energy causes the voltage at the output to rise above the input voltage and hence gives the "boost" regulator its namesake behavior.

Fig. 22: Equivalent circuit for the OFF State of the boost regulator topology.

The change in current during this period is when the inductor current drops from  $I_2$  to  $I_1$ . This can be characterized by:

$$I_2 - I_1 = \Delta I = t_{off} \frac{v_{out} - v_{in}}{L}$$

19)

Since  $\Delta I$  is the same in both equations we can combine Eqs. 18) and 19) to see that:

$$\Delta I = t_{on} \frac{v_{in}}{L} = t_{off} \frac{v_{out} - v_{in}}{L}$$

and substituting the definitions for  $t_{on}$  and  $t_{off}$  gives:

$$V_{in}DT = V_{out}(1-D)T - V_{in}T + V_{in}DT$$

which simplifies to:

$$V_{out} = \frac{V_{in}}{1 - D}$$

20)

#### 3.2.2 Discontinuous Mode

As with the buck regulator, if the current flowing through the inductor falls to zero before the transistor switches back on the boost regulator is considered to be operating in the discontinuous mode. As mentioned in the derivation of the behavior of a buck regulator, the regulator operates in the discontinuous mode if the value of the load inductance is below the critical inductance. The critical inductance for the boost regulator is given by:

$$L_{C} = \frac{RD(1-D)^{2}}{2f_{s}}$$

21)

In addition to the critical inductance, the boost regulator relies on a value known as the **critical resistance** that is of equal importance in determining whether the regulator is in continuous or discontinuous mode. The critical resistance is given by:

$$R_C = \frac{2f_s L}{D(1-D)^2} \tag{22}$$

Fig. 23: Example waveform for the inductor current of a boost regulator operating in the discontinuous mode of operation.

Referring to the figures above it is possible to derive a transfer function describing this topology in the discontinuous mode. Analysis begins by noting the average voltages across the inductor during each part of the switching are  $V_{in}$  during the *DT* period and  $V_{out} - V_{in}$  during the  $D_2T$ period. Since the voltages change by equal but opposite amounts during these two periods it can be written that

$$V_{in}D - (V_{out} - V_{in})D_2 = 0$$

23)

where  $D_2$  is the period in which the inductor current is falling and is defined by  $(t_2 - t_{on})/T$ .

After analyzing the inductor current during each period it is possible to find equations relating D and  $D_2$  to physical circuit parameters, substituting these values into Eq. 23 yields a quadratic equation that can be solved to find that the voltage conversion ratio in the discontinuous mode is given by:

$$\frac{V_{out}}{V_{in}} = \frac{1}{2} + \frac{1}{2}\sqrt{1 + \frac{4DL_c}{L(1-D)^2}}$$

#### 3.2.3 Summary

The boost regulator is a useful topology for producing a higher output voltage than is supplied to the input. This characteristic occurs as a result of the topological configuration of the switching element that causes the inductor to store enough energy to deliver an increased voltage to the output capacitor. Below are a few useful references that will be utilized in the following sections in order to derive and verify a behavioral model for the boost regulator.

| Mode          | Requirement | Voltage Ratio Function                                                        |

|---------------|-------------|-------------------------------------------------------------------------------|

| Continuous    | $L > L_C$   | $V_{out}/V_{in} = \frac{1}{1-D}$                                              |

| Discontinuous | $L < L_C$   | $V_{out}/V_{in} = \frac{1}{2} + \frac{1}{2}\sqrt{1 + \frac{4DL_c}{L(1-D)^2}}$ |

Table III: Summary of voltage transfer equations for the various modes of operation for a boost regulator

Fig. 24: Open loop response of the boost regulator, showing the voltage transfer ratio in relation to the duty cycle.

# **4** SWITCHING REGULATOR CONTROL SCHEMES

Thus far, the topologies examined have all been analyzed as an open loop network, but in reality all switching regulators perform as a closed loop system and are used with some sort of feedback network. This aids the stability of the circuit and keeps the regulator working correctly over a much wider range than would be possible without the feedback. While there are many different types of control schemes that can be designed, the vast majority of switching regulators use one of a small number of templates to implement the control. The most widely used control schemes are **pulse-width modulation** and **hysteresis control**. As hysteresis control is not used in any of the regulators modeled by this group so far, it will not be discussed in further detail, but the

various types of pulse-width modulation are used quite frequently and receive a more in depth treatment.

#### 4.1 PULSE-WIDTH MODULATION

Pulse width modulation (PWM) is a fairly simple control scheme. Operating on the principle of modulating the on/off time of the switching signal this control scheme allows for precise optimization of the output voltage. There are two general methods of implementing a PWM scheme; the designer can choose to use a **variable-frequency PWM** or **fixed-frequency PWM**.

In the variable-frequency PWM implementation, the on and off times are free to be changed so as to cause an unpredictable switching period. This can cause great difficulty in filtering the unpredictable electromagnetic interference (EMI) introduced as a result of the switching effect.

As an alternative to variable-frequency, many switching regulators utilize a fixed-frequency approach that greatly simplifies the EMI filtering. This implementation is realized by varying the on time and off time in a complementary fashion that ensures that the switching period remains constant.

In addition to choosing a variable-frequency vs. fixed-frequency approach, it is also necessary to choose between a voltage-mode PWM and a current-mode PWM. The essential difference between the two is that a voltage-mode scheme samples the voltage at the output and adjusts the duty cycle accordingly, while a current-mode scheme samples the current through the inductor. Each scheme has its own advantages and disadvantages that will be discussed in the upcoming sections.

#### 4.1.1 Voltage-mode PWM

The voltage-mode control scheme samples the voltage at the output by using a voltage divider circuit and adjusts the duty cycle accordingly. Due to the relative simplicity of implementation this is the more widely used control method. A typical voltage-mode control scheme is shown below.

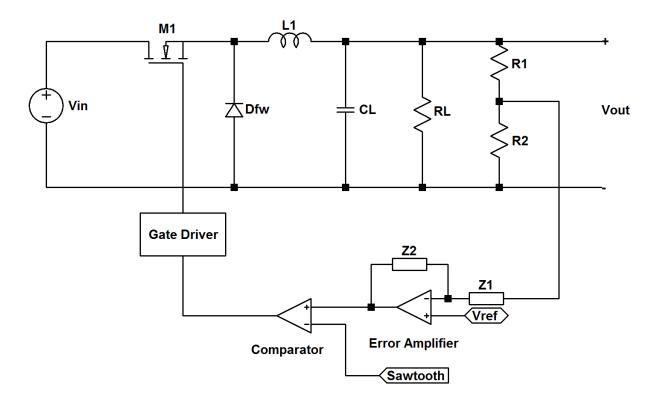

Fig. 25: PWM controller attached to a buck regulator topology

The following algorithm describes the basic principle of operation:

- 1. Sense the difference between the output voltage and reference voltage; this is known as the error voltage.

- 2. Compare the error voltage to a periodic sawtooth signal

- a. If the error voltage is greater than the sawtooth, then the switch should be on.

- b. Otherwise the switch should be off

The simplicity of this method is attractive and is a major reason for its popularity.

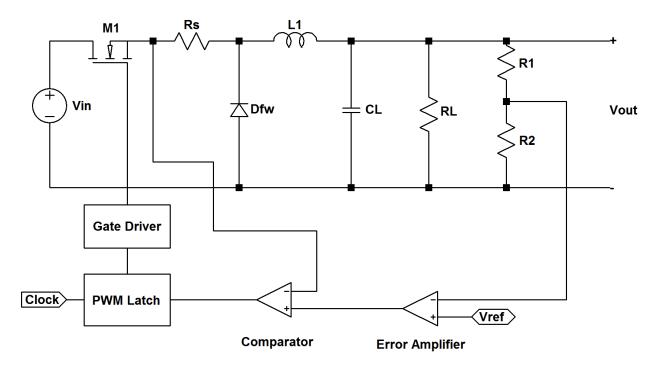

#### 4.1.2 Current-mode PWM

The other type of PWM control scheme proves to be a bit more complex, but not without reason. Current-mode PWM operates by sensing the current through the inductor, which is an inherently difficult task to accomplish without altering the output. One major advantage of a current controlled PWM would be the natural limits placed on the inductor current. This doesn't come without drawbacks though; the current controlled PWM tends to suffer from more stability issues than the voltage controlled PWM. Specifically, when the duty cycle is greater than 50% the inductor generates sub-harmonic oscillations that can cause the system to lose stability. There are

proven methods of compensating for this instability, though that further increases system complexity.

The general algorithm used by the current-mode PWM scheme is described below:

- 1. Sense current flowing through the inductor.

- 2. If inductor current has exceeded control signal level, then close the transistor.

This system works well after compensating for the instability.

# **5** SIMULATION OF SWITCHING REGULATORS

Simulation has become an essential step in the circuit design process. It is highly unlikely for a commercial circuit to be built before being verified through some sort of simulation package. For most circuits, simulation is actually an integrated part of the design flow, such that the circuit designer may iteratively simulate the design hundreds of times before determining the proper implementation.

Most circuit simulation packages in use today are based off of a SPICE (Simulation Program with Integrated Circuit Emphasis) like simulator [1]. These simulators use an iterative numerical method to calculate the voltages at every node in the circuit, as well as the current through every

branch. Due to the computational power of modern computers these techniques generally work quickly enough to require a negligible amount of time; however, in special cases the simulation can take hours or even days. The simulation of switching regulators happens to be one such case.

#### 5.1 EFFECTS OF SWITCHING ON SIMULATION TIME

The cause for this significant increase in simulation time is a direct consequence of the iterative nature of the SPICE engine. In a normal circuit, with an absence of switching elements, most circuit quantities change in a relatively predictable pattern. This predictability allows the simulation engine to take larger steps in between calculations. This means that there will be a relatively small amount of required simulation points, with a minimal amount of iterations at each point.

In contrast, a circuit containing switching elements will experience somewhat "violent" transitions at each switching event. These rapid transitions break the predictability of the circuit behavior which means that the simulator is required to solve the nodal matrix at many more points, and coincidentally, the solution will often take longer at each time step because the simulator will have increased difficulty in selecting initial conditions.

This non-trivial increase in computational complexity leads to drastically extended simulation times and an extremely large data set on the order of several gigabytes. Such a resource intensive process is not something to be taken lightly and serious commercial vendors do not allow this to slow their design times down. Other methods must be utilized to make the design/verification process more efficient and economically viable.

## 5.2 METHODS OF REDUCING SIMULATION TIME

Fortunately, there are methods for reducing the effect of switching on simulation time. The most common methods involve some sort of behavioral modeling that attempts to remove the rapid changes associated with a switching event while maintaining an acceptable level of model fidelity. By far the most widely used method is **State-Space Averaging**; however when modeling switching regulators, two additional modeling methods that deserve mention are **Discrete-Time Modeling** [8] and **Black-Box Two Port Networks** [9]. All of these modeling methods have advantages. For example, State Space models tend to be fairly accurate and are

very general models; however, they each have their drawbacks as well. State-space averaging can become very difficult as the circuit increases in size, discrete-time modeling suffers from the same fate, and black-box modeling requires some knowledge about the system under test.

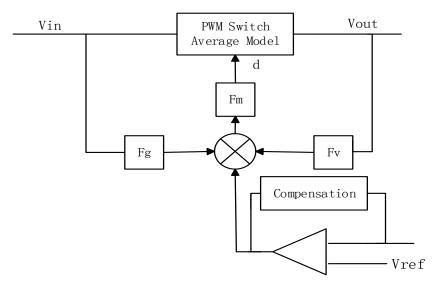

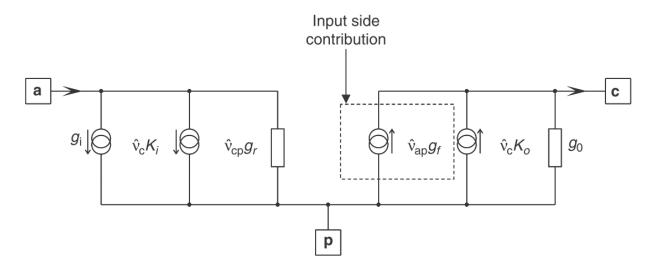

In response to the shortcomings of these modeling methods, this research group chose to utilize a modeling method described in [6] which focuses on averaging the switching element of the regulator and leaving the remaining devices as realistic models. This approach is simple, easily automated, and highly flexible.

### 5.3 SELECTED MODELING METHOD AND PLANNED IMPROVEMENTS

After careful investigation of previous work [10, 11, 12, 9], a combination of a template based approach and the time averaged PWM model described in [6] was determined to be the most robust and simplest to implement method for the purposes of developing an automated process. Having decided on this method though, it is worth noting that the selected method has room for improvement, which will be addressed in work currently under development. Planned improvements are:

- Describe operation in continuous conduction mode *and* discontinuous conduction mode.

- Extend PWM model to accurately describe large signal behavior, which is not currently offered by this model.

- Implement into the model nonlinearities that may be important such as switch onresistance and diode forward voltage drop.

Fig. 26: Proposed new model large signal structure incorporating the diode forward drop and switch on-resistance.

# 6 INTRODUCTION TO BEHAVIORAL MODELING SOFTWARE

In the modern workflow, Verilog-A has become the de-facto standard of analog behavioral modeling languages, and so will be examined more closely. In addition to Verilog-A, most circuit designers and modelers alike have become familiar with SPICE or some derivative of it as a program that excels in circuit analysis and verification. It is then natural to extend the verification process even further and allow for behavioral modeling within SPICE.

Since SPICE was developed as a circuit simulation package it was not given any native behavioral modeling capability. Fortunately, the electronic design automation company Cadence has implemented a library of behavioral modeling tools into their proprietary version of SPICE that allows for the same general capabilities as Verilog-A [13]. In the spirit of providing a fully integrated design/verification flow PSPICE ABM is explored as well.

#### 6.1 VERILOG-A

Verilog-A is the standard for behavioral modeling and the reason for this is fairly clear. Verilog-A was developed as a standardized branch off of the hardware description language (HDL) Verilog. With development beginning in 1985 and officially becoming an IEEE standard 10 years later, Verilog is considered a mature language [14, 15]. Originally developed to aid digital circuit designers with circuit design, and later synthesis, the original standard did not allow for very robust analog behavioral models.

Realizing the need for analog extensions, development of the Verilog-A language extension began soon after development of Verilog and as a result developed proceeded rapidly and was quickly integrated into the Verilog HDL standard.

## 6.1.1 Using Verilog-A and Exploring Capability

Since Verilog-A was developed solely to provide capability for analog modeling and is by nature a behavioral modeling language, it is an excellent choice for use in automatically generating models. The capability of Verilog-A is nearly limitless; as long as the modeler has an adequate understanding of the subject matter the language can be used to model any analog system. For example while it is often used within the Electrical Engineering discipline to model complex circuit behavior, Verilog-A can also be used in other fields such as fluid dynamics, economic modeling, or any general situation in which a **through variable** or **across variable** make sense.

| Capability                            | Description                                                                                                                   |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Arithmetic Operations                 | Addition, subtraction, multiplication, etc.                                                                                   |

| Relational Operations                 | Less than, equal to, greater than, etc.                                                                                       |

| Logical Operations                    | Provides an implementation for the basic Boolean logical operations, both at the bit-wise level and at a more abstract level. |

| Standard Mathematical Functions       | Natural and Base 10 logarithm, exponential, square root, etc.                                                                 |

| Transcendental Mathematical Functions | Implements the trigonometric functions. (sin, cos, tan, atan, sinh, etc.)                                                     |

| Time Based Calculus                   | Time derivative and integral.                                                                                                 |

| Transforms                            | Laplace and Z transforms are built into the simulator                                                                         |

Table IV: A summary table describing some of the advanced capabilities defined in the Verilog-A language.

The above table only scratches the surface of what Verilog-A is capable of but provides a clear picture of the capability and shows that it is indeed powerful enough for modeling of switching regulators.

# 6.2 PSPICE ABM

SPICE was not developed as a behavioral modeling tool, so the amount of functionality provided by PSPICE is not nearly as comprehensive as that which is offered by Verilog-A. Fortunately, the functionality that is provided is sufficient to cover most modeling requirements of an analog system. The actual capability will be discussed further in the proceeding section. The important consideration though is that PSPICE ABM provides all of the necessary functionality to generate switching regulator models.

# 6.2.1 Using PSPICE and Exploring Capability

While nearly every circuit designer is familiar with the graphical interface of SPICE simulators, a generally less familiar concept is the **circuit netlist**. The netlist is what is parsed by SPICE and describes the connections and parameters of the various models involved in the simulation. As a reference, **Appendix A: PSPICE ABM Reference Sheet** provides a nearly extensive list of the capabilities offered by the PSPICE ABM extension.

The table below shows a summary of the analog modeling functions supported by PSPICE ABM that can be compared to the summary given above for Verilog-A.

| Capability                                 | Description                                                                        |

|--------------------------------------------|------------------------------------------------------------------------------------|

| Arithmetic Operations                      | Addition, subtraction, multiplication, etc.                                        |

| Relational Operations                      | Less than, equal to, greater than, etc.                                            |

| Logical Operations                         | In contrast to Verilog-A, ABM only provides<br>an implementation for IF statements |

| Standard and Transcendental Math Functions | The same functions implemented in Verilog-A                                        |

| Time Based Calculus                        | Integration and differentiation in the time domain                                 |

| Transforms                                 | In contrast to Verilog, ABM provides a Laplace transform only                      |

Table V: A summary table describing most of the capabilities defined in PSPICE ABM.

| Look-up-tables                    | A feature often used for modeling off of<br>measured data, allowing for a certain input<br>value to correspond to another defined output |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Filters and Limiters <sup>1</sup> | Implements high, low, band-pass, and band-<br>reject Chebyshev filters as well as various<br>limiting functions                          |

While ABM capability is not nearly as extensive as Verilog-A, any functionality that would be required in a model of a switching regulator can be implemented using the behavioral modeling capabilities of PSPICE. Thus the tool is capable of outputting models in both Verilog-A and PSPICE ABM.

# 7 MODELING A COMMERCIAL REGULATOR

Before even considering automating any process, it is first necessary to understand how that process works. The most straightforward way to develop such an understanding is to create a model by hand. Doing so allows the CAD developer to see what steps in the process are most time consuming, which steps are most critical, and which are most likely to be able to be left out without loss of fidelity in the model.

The logical starting point for developing and testing a model would be to recreate the behavior of a commercially available regulator. The first candidate for generation by hand was the TPS40305 [16], which is described as a "high efficiency wide input synchronous buck controller." The process involved in developing this model is described below, results from simulating this model are discussed in a later section.

# 7.1 MODEL DEVELOPMENT PROCESS

The first step in developing a simulation ready model for a switching regulator based off of datasheet [16] information is to refer to the datasheet and obtain as much information as possible about the device. For the TPS40305 some of the more interesting information is listed below:

- Buck regulator core

- 1.2 MHz switching frequency

<sup>&</sup>lt;sup>1</sup> These features are only supported by the Cadence OrCAD package of PSPICE

- Soft-start circuit protection

- Over-current protection

- Required operating voltages are all listed

- Maximum duty cycle is 85%

This is only a short list of the information contained in the datasheet; in addition to the above listed parameters the datasheet includes suggested use configurations, packaging information, several pages of testing results, and an extensive amount of other information.

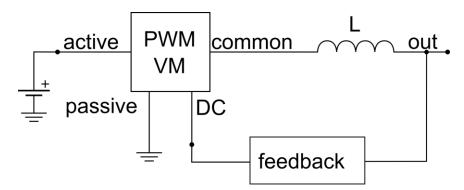

After identifying these important details the modeler can begin to create the model while considering the important figures of merit to capture. As this particular circuit is listed as a buck regulator, the modeler can begin by arranging the PWM switch into the buck configuration as shown below.

Fig. 27: PWM switch arranged to model the buck topology [6]

After that, the modeler can consider adding circuit protection features and begin the highly repetitive parameter tuning process in which the various regulator parameters can be adjusted to meet the optimal performance. Fortunately, the datasheet provides some guidance on selecting an appropriate inductance value and suggests an optimal configuration for the compensation network.

At the end of this process, the modeler is left with a model of the regulator IC itself but to actually test the behavior the model must be placed into a properly developed circuit. These circuits and their corresponding simulations are discussed in the following sections.

Fig. 28: Schematic of the internal model of the TPS40305 switching regulator.

## 7.2 AUTOMATING THE PROCESS

After creating the first and second models by hand, the process was well enough defined that the algorithms required to automate this time consuming and seemingly complex process could come under consideration.

In developing an algorithm, one of the first steps is always to determine which portions of a process are repetitive, for these are often the steps that are most appropriate for automation. In fact, this repetition is evident in the very definition of the word. From Merriam-Webster [17]:

#### **Al-go-rithm** – *noun* $\ |\ al-g\partial - ri-th\partial m |$

A procedure for solving a mathematical problem (as of finding the greatest common divisor) in a finite number of steps that frequently involves repetition of an operation; *broadly* : a step-by-step procedure for solving a problem or accomplishing some end especially by a computer

Thus, switching regulator model generation is a field that is prepared for automation. The next step is simply to identify which portions of the design loop can be automated, and then to do so.

The listing below provides a summary of some of a few parts of the model generation flow that need to be automated.

- 1. **Determine control type**: Every practical switching regulator has some sort of control scheme to keep the output voltage stable over a wide range. This control scheme is either voltage controlled or current controlled, a distinction that must be determined by the modeler. This is the type of information that could be determined from the datasheet.

- 2. Determine regulator topology: As the vast majority of switching regulators are implemented through a buck, boost, or buck-boost topology it is straightforward to identify the core of the regulator model. Therefore this is a task that should be built into the automation process.

- **3. Parameter Fitting:** This is perhaps the portion most fit for automation. After determining the basics of the regulator's composition, it then becomes necessary to tune the parameters of the chosen topology to show the desired behavior. This process can be tedious and very time consuming. Generally the modeler performs some calculations to get a rough estimate for what parameters to use and then goes into an iterative process to fine-tune the parameters. This type of iteration is a process that computers naturally perform well.

## 8 SOFTWARE IMPLEMENTATION OF AUTOMATION

In order to automate the model generation process it is necessary to remove the modeler from the details of model generation as much as possible. Ideally, the software should be simple enough to use that no modeling experience would be required and that anyone with an understanding of the desired results should be able to produce a simulation ready model. It is however no easy task to generalize such a complex field and make it so easy to use. That is the challenge faced by this project and that is the final goal.

After examining various software design approaches, as well as considering the general process involved with creating a regulator model, it became apparent that a template-based approach would be the best method for generating the output files desired. The idea behind a templatebased approach is to identify by hand the reusable parts of regulator models then to generalize these reusable parts into a parameterized template. The reasons for this decision and details of operation are described in the following section.

The following is a sample of the languages and libraries used thus far in the development process with a short description:

- **Python** Powerful and easy to use scripting language providing the backend processing

- **Qt** Well established and actively developed multi-platform user interface framework, used for the GUI

- **Pyside** Python language bindings to interface python with the Qt framework, used for the GUI

- **Doxygen** Documentation generation tool which creates documentation from source code comments, used to generate developer documentation

- ElementTree A python library developed with the purpose of parsing and operating on various XML formatted objects, used to store the developed models for later use and manipulation

Fig. 29: Flowchart describing the general flow of the program from the perspective of the modeler.

### 8.1 TEMPLATE BASED APPROACH

The template-based approach of output generation was chosen for a very simple reason. Upon observing hand created models, it was clear that they all had quite a bit in common. In fact it often occurs that the only differences between regulator models of the same family are relatively minor parameter adjustments. This is the type of situation in which a template based approach excels and will fit make it a simple matter of utilizing curve fitting algorithms to find the proper parameters. The details of this approach are explained farther down in section 8.3.

## 8.2 GUI DEVELOPMENT PROCESS

In developing the user interface it is important to consider the way in which the final user will interact with the program. In CAD software, the end user is generally technically proficient with subject matter experience. This however is no excuse for an overly confusing and frustrating interface. In order to provide the simplest and most straightforward modeling process, the tool uses a wizard interface to walk the modeler through the necessary steps.

Fig. 30: The first step in the model generation tool wizard.

The process of determining in what order to present options to the user was much that same as solving any Engineering or Physics problem.

The first step began with identifying all of the variables under consideration such as regulator core type, error amplifier type (for compensation), control method (voltage, current, etc.), regulator parameters, and circuit protection features.

The next step was to determine which of these variables were dependent on each other. For example, it is impossible to know which regulator parameters will need to be gathered before asking the user what type of regulator core and control method is being modeled.

Finally, after considering all constraints, it was essential to present the information in a logical manner. Within the program the user is first greeted with a screen asking for basic information about the regulator core such as the type, and control method. The next screen then presents

parameters for the user to provide, which are necessary for simulation. The next screen gathers all information related to compensation information. This includes choosing a compensation template and selecting an error amplifier type. In the near future, this tool will provide functionality to automatically determine compensation information based off of datasheet information or a circuit netlist.

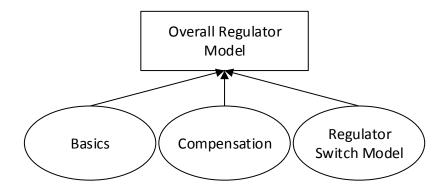

Fig. 31: Flowchart for the graphical user interface