#### University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

10-19-2015

# High Level Synthesis and Evaluation of the Secure Hash Standard for FPGAs

Ian Spencer Janik University of Windsor

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### **Recommended** Citation

Janik, Ian Spencer, "High Level Synthesis and Evaluation of the Secure Hash Standard for FPGAs" (2015). *Electronic Theses and Dissertations*. Paper 5470.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

#### High Level Synthesis and Evaluation of the Secure Hash Standard for

**FPGAs**

By

Ian Janik

A Thesis Submitted to the Faculty of Graduate Studies through the Department of Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada

2015

© 2015 Ian Janik

## High Level Synthesis and Evaluation of the Secure Hash Standard for FPGAs

By

Ian Janik

APPROVED BY:

R. Seth Department of Civil and Environmental Engineering

E. Abdel-Raheem Department of Electrical and Computer Engineering

M. Khalid, Advisor Department of Electrical and Computer Engineering

September 16, 2015

#### **Declaration of Co-Authorship**

#### I. Co-Authorship Declaration

This thesis also incorporates the outcome of a joint research undertaken in collaboration with Qing Tang under the supervision of Dr. Mohammed Khalid. The collaboration is covered in Chapter 2 of the thesis. In all cases, the key ideas, primary contributions, experimental designs, data analysis and interpretation, were performed by the author, and the contribution of coauthor was primarily through the help in evaluation of the Altera SDK for OpenCL that comprises the paper "An overview of Altera SDK for OpenCL: A user perspective" that was published at the Electrical and Computer Engineering (CCECE), 2015 conference. Ideas of that paper are used in this thesis.

I am aware of the University of Windsor Senate Policy on Authorship and I certify that I have properly acknowledged the contribution of other researchers to my thesis, and have obtained written permission from each of the co-author(s) to include the above material(s) in my thesis.

I certify that, with the above qualification, this thesis, and the research to which it refers, is the product of my own work.

#### II. Declaration of Previous Publication

| This                                                                       | thesis | includes | 2 | original | papers | that | have | been | previously |

|----------------------------------------------------------------------------|--------|----------|---|----------|--------|------|------|------|------------|

| published/submitted for publication in peer reviewed journals, as follows: |        |          |   |          |        |      |      |      |            |

| Thesis Chapter   | Publication title/full citation                                                                                                                                                                             | Publication status* |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Chapter 2        | I. Janik, Q. Tang, and M. Khalid, "An overview of Altera SDK for OpenCL: A user perspective," <i>Electrical and Computer Engineering (CCECE), 2015 IEEE 28th Canadian Conference on.</i> pp. 559–564, 2015. | published           |

| Chapters 2 and 3 | I. Janik and M. Khalid "FPGA<br>Synthesis and Evaluation of<br>SHA-2 and SHA-3 Algorithms<br>Using the Altera SDK for<br>OpenCL"                                                                            | In preparation      |

I certify that I have obtained a written permission from the copyright owner(s) to include the above published material(s) in my thesis. I certify that the above material describes work completed during my registration as graduate student at the University of Windsor.

I declare that, to the best of my knowledge, my thesis does not infringe upon anyone's copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material from the work of other people included in my thesis, published or otherwise, are fully acknowledged in accordance with the standard referencing practices. Furthermore, to the extent that I have included copyrighted material that surpasses the bounds of fair dealing within the meaning of the Canada Copyright Act, I certify that I have obtained a written permission from the copyright owner(s) to include such material(s) in my thesis.

I declare that this is a true copy of my thesis, including any final revisions, as approved by my thesis committee and the Graduate Studies office, and that this thesis has not been submitted for a higher degree to any other University or Institution.

#### Abstract

Secure hash algorithms (SHAs) are important components of cryptographic applications. SHA performance on central processing units (CPUs) is slow, therefore, acceleration must be done using hardware such as Field Programmable Gate Arrays (FPGAs). Considerable work has been done in academia using FPGAs to accelerate SHAs. These designs were implemented using Hardware Description Language (HDL) based design methodologies, which are tedious and time consuming. High Level Synthesis (HLS) enables designers to synthesize optimized FPGA hardware from algorithm specifications in programming languages such as C/C++. This substantially reduces the design cost and time. In this thesis, the Altera SDK for OpenCL (AOCL) HLS tool was used to synthesize the SHAs on FPGAs and to explore the design space of the algorithms. The results were evaluated against the previous HDL based designs. Synthesized FPGA hardware performance was comparable to the HDL based designs despite the simpler and faster design process.

#### Acknowledgements

First and foremost I would like to thank my supervisor Dr. Khalid for giving me the opportunity to work with him to obtain my degree. I need to thank him for all of the guidance, advice, support, and encouragement he has given over the past two years.

I would like to thank Dr. Abdel-Raheem and Dr. Seth for agreeing to be a part of my committee and contributing their time from their busy schedules to provide insight on this project.

I'd also like to thank Ryan Tang for helping me when I needed it. Without his help learning and problem solving, this work would have not gone as smoothly.

I need to thank my mom for her continued support and encouragement throughout my university career that has allowed me to pursue my interests.

Lastly, I would like to thank my girlfriend, Jen. She motivates me to try my hardest and is always there to listen and help whenever I need it. I would not be where I am today without her.

## **Table of Contents**

| Declaration of Co-Authorship          | iii  |

|---------------------------------------|------|

| Abstract                              | v    |

| Acknowledgements                      | vi   |

| List of Tables                        | xii  |

| List of Figures                       | xiv  |

| List of Abbreviations                 | xvii |

| Chapter 1 Introduction                | 1    |

| 1.1 Thesis Goals                      | 3    |

| 1.1.1 General Objectives              |      |

| 1.2 Thesis Outline                    | 4    |

| Chapter 2 Background and Related Work | 5    |

| 2.1 Field Programmable Gate Arrays    | 5    |

| 2.2 High Level Synthesis              | 6    |

| 2.3 Heterogeneous Computing           | 7    |

| 2.3.1 Open Computing Language         | 8    |

| 2.3.1.1 Host Program                  | 9    |

| 2.3.1.2 OpenCL Kernel                 | 11   |

| 2.3.1.3 OpenCL Extensions             |      |

| 2.3.2 Th | e Alte | ra SDK for OpenCL                  | 13   |

|----------|--------|------------------------------------|------|

| 2.3.2.   | 1 H    | Iost Program                       | .13  |

| 2.3.2.2  | 2 K    | Kernel                             | .14  |

| 2.3.2.   | 3 E    | Extensions                         | . 14 |

| 2.3.2.4  | 4 F    | PGA Accelerator Cards              | . 15 |

| 2.3.2.   | 5 T    | The Tools                          | 16   |

| 2.4 The  | e Secu | re Hash Standard                   | . 18 |

| 2.4.1 SH | IA-1   |                                    | . 20 |

| 2.4.1.   | 1 Iı   | nitialization                      | . 22 |

| 2.4.1.2  | 2 N    | Message Padding                    | . 22 |

| 2.4.1.   | 3 S    | step 1. – Message Schedule         | . 23 |

| 2.4.1.4  | 4 S    | step 2. – Update Working Variables | . 23 |

| 2.4.1.   | 5 S    | Step 3. – Rounds of Hashing        | . 24 |

| 2.4.1.   | 6 S    | tep 4. – Update Intermediate Hash  | . 25 |

| 2.4.2 SH | IA-2   |                                    | . 26 |

| 2.4.2.   | 1 S    | SHA-256                            | . 27 |

| 2.4      | .2.1.1 | Initialization                     | . 27 |

| 2.4      | .2.1.2 | Message Padding                    | . 28 |

| 2.4      | .2.1.3 | Step 1. – Message Schedule         | . 28 |

| 2.4      | .2.1.4 | Step 2. – Update Working Variables | . 29 |

| 2.4.2.1     | .5 Step 3. – Rounds of Hashing        | 30 |

|-------------|---------------------------------------|----|

| 2.4.2.1     | .6 Step 4. – Update Intermediate Hash | 31 |

| 2.4.2.2     | SHA-512                               | 32 |

| 2.4.2.2     | .1 Initialization                     | 33 |

| 2.4.2.2     | .2 Message Padding                    | 34 |

| 2.4.2.2     | .3 Step 1. – Message Schedule         | 35 |

| 2.4.2.2     | .4 Step 2. – Update Working Variables | 36 |

| 2.4.2.2     | .5 Step 3. – Rounds of Hashing        | 36 |

| 2.4.2.2     | .6 Step 4. – Update Intermediate Hash | 37 |

| 2.4.3 SHA-3 | 3                                     | 38 |

| 2.4.3.1     | Theta Step Mapping                    | 43 |

| 2.4.3.2     | Rho Step Mapping                      | 44 |

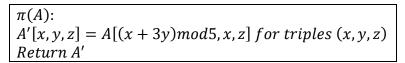

| 2.4.3.3     | Pi Step Mapping                       | 45 |

| 2.4.3.4     | Chi Step Mapping                      | 46 |

| 2.4.3.5     | Iota Step Mapping                     | 47 |

| 2.5 Related | l Work                                | 48 |

| 2.5.1 SHA-1 | 1                                     | 48 |

| 2.5.2 SHA-2 | 2                                     | 49 |

| 2.5.3 SHA-3 | 3                                     | 51 |

| 2.6 Summa   | ary                                   | 52 |

| Chapter 3 | 3 Synthesis and Evaluation | 53 |

|-----------|----------------------------|----|

| 3.1       | Overview                   | 53 |

| 3.2       | SHA-1                      | 54 |

| 3.2.1     | 1 Host Program             | 54 |

| 3.2.2     | 2 Kernel                   | 55 |

| 3.2       | 2.2.1 Optimization         | 59 |

| 3.2.3     | 3 Results                  | 60 |

| 3.3       | SHA-2                      | 66 |

| 3.3.1     | 1 SHA-256                  | 66 |

| 3.3       | 3.1.1 Host Program         | 66 |

| 3.3       | 3.1.2 Kernel               | 67 |

|           | 3.3.1.2.1 Optimization     | 71 |

| 3.3       | 3.1.3 Results              | 71 |

| 3.3.2     | 2 SHA-512                  | 75 |

| 3.3       | 3.2.1 Host Program         | 75 |

| 3.3       | 3.2.2 Kernel               | 75 |

|           | 3.3.2.2.1 Optimization     | 80 |

| 3.3       | 3.2.3 Results              | 80 |

| 3.4       | SHA-3                      | 82 |

| 3.4.1     | 1 Host Program             |    |

| 3.4.2 Kernel                         |

|--------------------------------------|

| 3.4.2.1 Optimization                 |

| 3.4.3 Results                        |

| 3.5 Comparison                       |

| 3.6 Summary                          |

| Chapter 4 Conclusion and Future Work |

| 4.1 Future Work 104                  |

| Appendix A: SHA-1 Kernel Code 105    |

| Appendix B: SHA-256 Kernel Code 107  |

| Appendix C: SHA-512 Kernel Code 109  |

| Appendix D: SHA-3 Kernel Code 111    |

| References                           |

| Vita Auctoris                        |

### List of Tables

| Table 2.1: SHA-1 Initial Hash Values                          | 22 |

|---------------------------------------------------------------|----|

| Table 2.2: SHA-1 Step 1 - Message Schedule                    | 23 |

| Table 2.3: SHA-1 Step 2 - Update Working Variables            | 24 |

| Table 2.4: SHA-1 Step 3 - Rounds of Hashing                   | 25 |

| Table 2.5: SHA-1 Step 4 - Update Intermediate Hash            | 26 |

| Table 2.6: Characteristics of SHA-2 Functions                 | 26 |

| Table 2.7: SHA-256 Initial Hash Values                        | 28 |

| Table 2.8: SHA-256 Step 1- Messasge Schedule                  | 29 |

| Table 2.9: SHA-256 Step 2 - Update Working Variables          | 29 |

| Table 2.10: SHA-256 Step 3 - Rounds of Hashing                | 31 |

| Table 2.11: SHA-256 Step 4 - Update Intermediate Hash         | 32 |

| Table 2.12: SHA-512 Initial Hash Values                       | 34 |

| Table 2.13: SHA-512 Step 1- Message Schedule                  | 36 |

| Table 2.14: SHA-512 Step 3 - Rounds of Hashing                | 37 |

| Table 2.15: Characteristics of SHA-3 Functions                | 39 |

| Table 2.16: SHA-3 Function Definitions                        | 43 |

| Table 2.17: SHA-3 Theta Step Mapping                          | 44 |

| Table 2.18: SHA-3 Rho Step Mapping and Calculated Offsets     | 45 |

| Table 2.19: SHA-3 Pi Step Mapping                             | 46 |

| Table 2.20: SHA-3 Chi Step Mapping                            | 46 |

| Table 2.21: SHA-3 Iota Step Mapping and Round Constant Values | 47 |

| Table 3.1: SHA-1 Kernel Comparison                            | 62 |

| Table 3.2: SHA-1 Performance Comparison to Related Work   | 66 |

|-----------------------------------------------------------|----|

| Table 3.3: SHA-256 Performance Comparison to Related Work | 74 |

| Table 3.4: SHA-512 Performance Comparison to Related Work | 82 |

| Table 3.5: SHA-3 Kernel Comparison                        | 90 |

| Table 3.6: SHA-3 Performance Comparison to Related Work   | 97 |

## List of Figures

| Figure 2.1: Logic Element Architecture [9]                                      |

|---------------------------------------------------------------------------------|

| Figure 2.2: Organization of OpenCL Work-Groups and Work-Items with NDRange of 2 |

| [7]10                                                                           |

| Figure 2.3: Altera SDK for OpenCL Programming Flowchart 17                      |

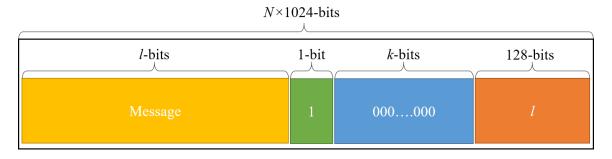

| Figure 2.4: Representation of SHA-1 Padding Rule                                |

| Figure 2.5: Representation of SHA-512 Padding Rule                              |

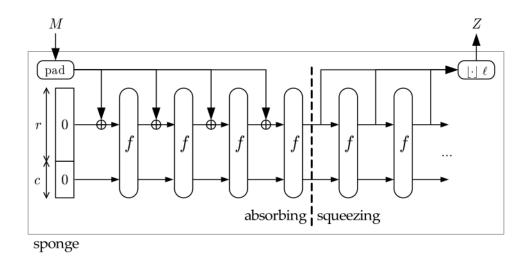

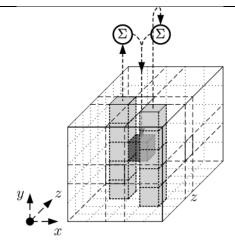

| Figure 2.6: Sponge Function Construction [26]                                   |

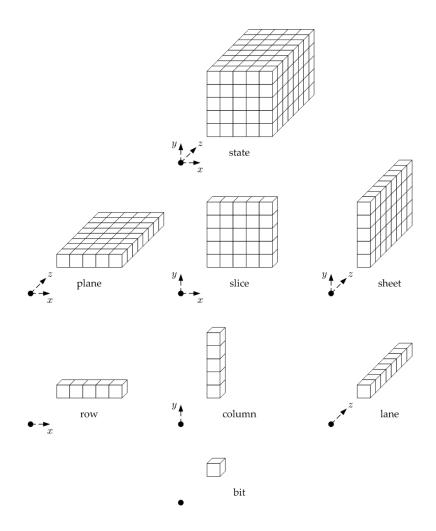

| Figure 2.7: SHA-3 State and Its Components [25] 40                              |

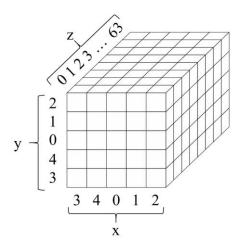

| Figure 2.8: Coordinate Convention of State. Adapted from [20] 41                |

| Figure 2.9: Representation of SHA-3 Padding Rule                                |

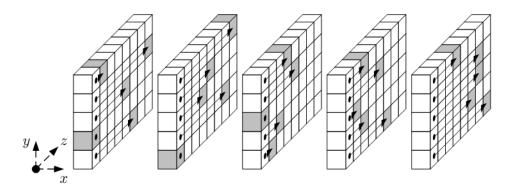

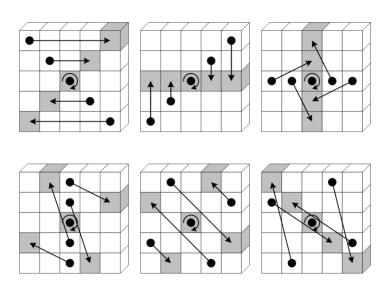

| Figure 2.10: SHA-3 Theta Step Mapping [25] 44                                   |

| Figure 2.11: SHA-3 Rho Step Mapping [25]45                                      |

| Figure 2.12: SHA-3 Pi Step Mapping [25]                                         |

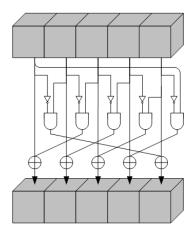

| Figure 2.13: SHA-3 Chi Step Mapping [25]                                        |

| Figure 3.1: Custom Functions of the SHA-1 Kernel                                |

| Figure 3.2: Declaration of Variables in the SHA-1 Kernel                        |

| Figure 3.3: Message Schedule Derivation in the SHA-1 Kernel                     |

| Figure 3.4: Steps 2 and 3 of the SHA-1 Kernel                                   |

| Figure 3.5: Step 4 and Processing Final Hash Variables of SHA-1 Kernel          |

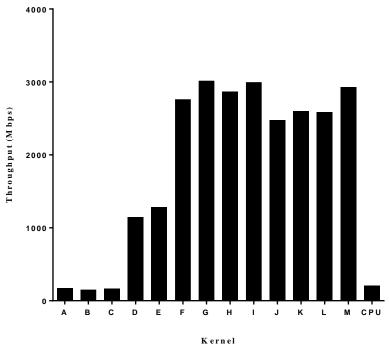

| Figure 3.6: SHA-1 Test Kernel Throughput                                        |

| Figure 3.7: SHA-1 Test Kernel Throughput divided by PRU of Target FPGA          |

| Figure 3.8: SHA-1 Throughput vs. Message Size 64                                |

| Figure 3.9: Custom Functions of the SHA-256 Kernel                                   | . 67 |

|--------------------------------------------------------------------------------------|------|

| Figure 3.10: Variable Declaration and Initialization of the SHA-256 Kernel           | . 68 |

| Figure 3.11: Message Block Caching and Message Schedule Derivation of the SHA-       | 256  |

| Kernel                                                                               | . 69 |

| Figure 3.12: Steps 2 and 3 of the SHA-256 Kernel                                     | . 70 |

| Figure 3.13: Step 4 and Processing Final Hash Variables of SHA-256 Kernel            | . 71 |

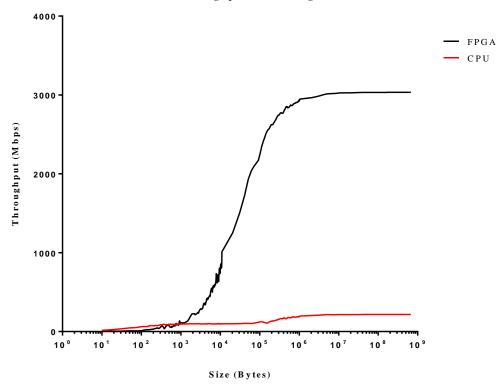

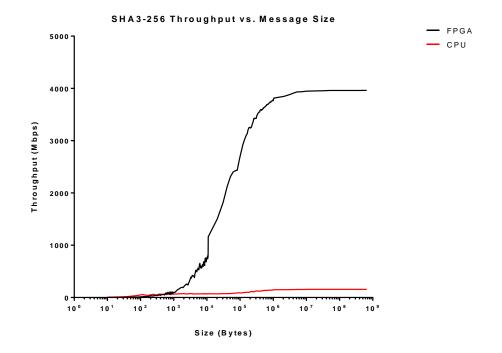

| Figure 3.14: SHA-256 Throughput vs. Message Size                                     | . 73 |

| Figure 3.15: Custom Functions of the SHA-512 Kernel                                  | . 76 |

| Figure 3.16: Variable Declaration and Initialization of the SHA-512 Kernel           | . 77 |

| Figure 3.17: Message Block Caching and Message Schedule Derivation of the SHA-       | 512  |

| Kernel                                                                               | . 78 |

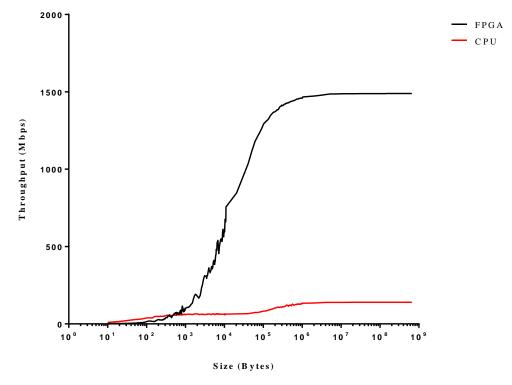

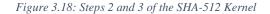

| Figure 3.18: Steps 2 and 3 of the SHA-512 Kernel                                     | . 79 |

| Figure 3.19: Step 4 and Processing Final Hash Variables of SHA-512 Kernel            | . 79 |

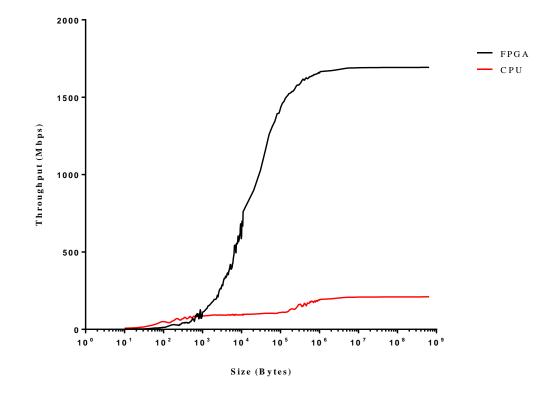

| Figure 3.20: SHA-512 Throughput vs. Message Size                                     | . 81 |

| Figure 3.21: Custom Functions of the SHA-3 Kernel                                    | . 83 |

| Figure 3.22: Declaration and Initialization of the Variables of the SHA-3 Kernel     | . 84 |

| Figure 3.23: Absorbing the Message Block into the State of SHA-3 Kernel              | . 85 |

| Figure 3.24: Theta Step Mapping of the SHA-3 Kernel                                  | . 85 |

| Figure 3.25: Rho and Pi Step Mappings of the SHA-3 Kernel                            | . 86 |

| Figure 3.26: Chi Step Mapping of the SHA-3 Kernel                                    | . 87 |

| Figure 3.27: Iota Step Mapping and Final Processing of the State in the SHA-3 Kernel | 87   |

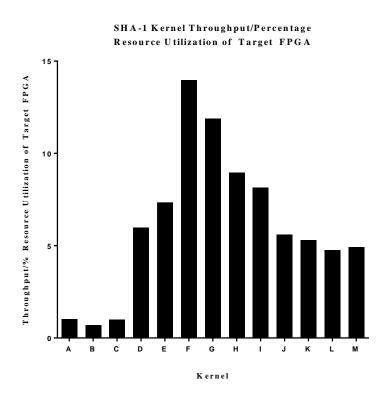

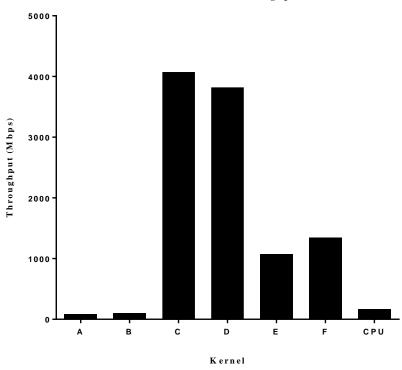

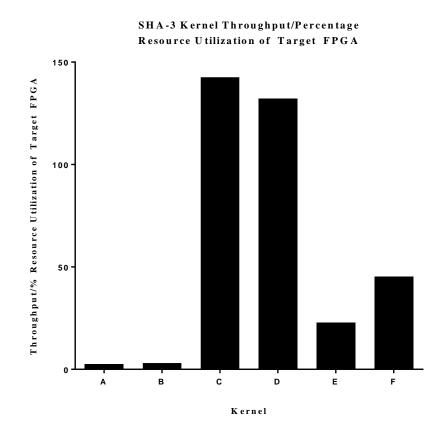

| Figure 3.28: Comparison of SHA-3 Test Kernel Throughput                              | . 90 |

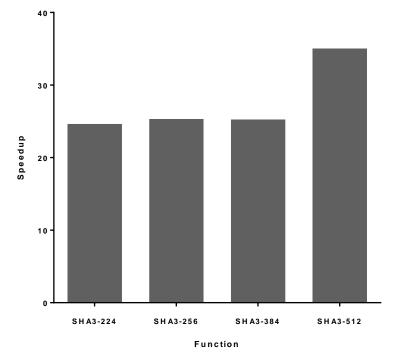

| Figure 3.29: SHA-3 Test Kernel Throughput divided by PRU of Target FPGA              | . 91 |

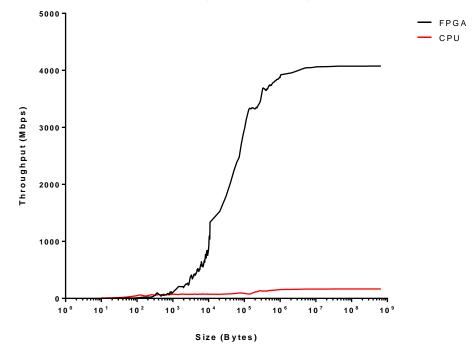

| Figure 3.30: SHA3-224 Throughput vs. Message Size | . 93 |

|---------------------------------------------------|------|

| Figure 3.31: SHA3-256 Throughput vs. Message Size | . 93 |

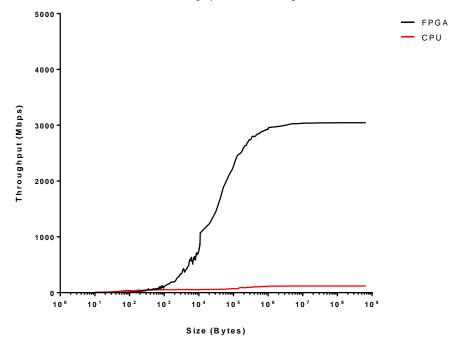

| Figure 3.32: SHA3-384 Throughput vs. Message Size | . 94 |

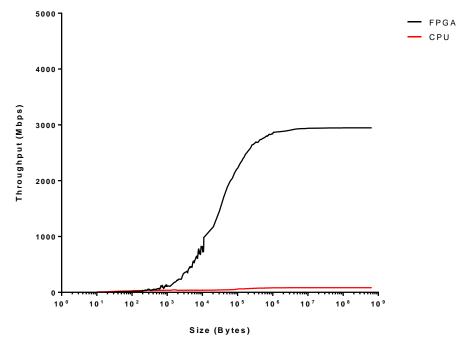

| Figure 3.33: SHA3-512 Throughput vs. Message Size | . 94 |

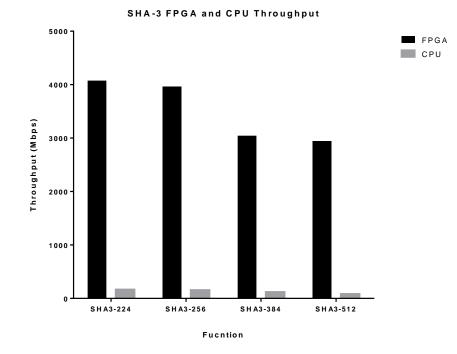

| Figure 3.34: SHA-3 FPGA and CPU Throughput        | . 95 |

| Figure 3.35: Comparison of SHA-3 Kernel Speedup   | . 95 |

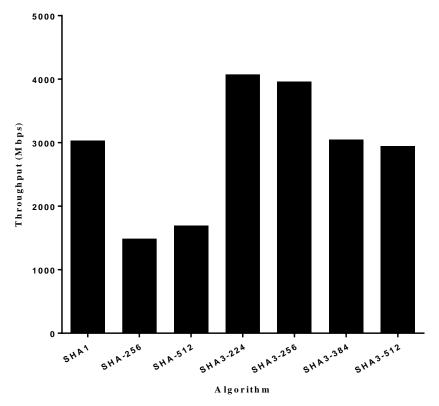

| Figure 3.36: Throughput Comparison of All SHAs    | . 99 |

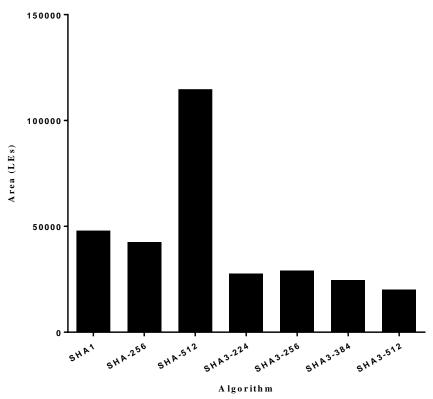

| Figure 3.37: Area Comparison of All SHAs          | 101  |

## List of Abbreviations

| AOCL    | Altera SDK for OpenCL                          |

|---------|------------------------------------------------|

| API     | Application Program Interface                  |

| ASIC    | Application Specific Integrated Circuit        |

| BSP     | Board Support Package                          |

| CAD     | Computer Aided Design                          |

| CPU     | Central Processing Unit                        |

| DDR3    | Double Date Rate 3                             |

| DSE     | Design Space Exploration                       |

| DSP     | Digital Signal Processor                       |

| FIFO    | First-In First-Out                             |

| FPGA    | Field Programmable Gate Array                  |

| GPU     | Graphical Processing Unit                      |

| HDL     | Hardware Description Language                  |

| HLL     | High Level Language                            |

| HLS     | High Level Synthesis                           |

| ΙΟ      | Input-Output                                   |

| LE      | Logic Element                                  |

| LUT     | Look Up Table                                  |

| NDRange | N-Dimensional Range                            |

| NIST    | National Institute of Standards and Technology |

| OpenCL | Open Computing Language                   |

|--------|-------------------------------------------|

| PRU    | Percentage Resource Utilization           |

| PCIe   | Peripheral Component Interconnect Express |

| ROTL   | Rotate Left                               |

| ROTR   | Rotate Right                              |

| SDK    | Software Development Kit                  |

| SHA    | Secure Hash Algorithm                     |

| SHR    | Shift Right                               |

| SoC    | System on Chip                            |

| XOF    | Extendable-Output Function                |

#### **Chapter 1 Introduction**

In today's world, electronic communication has become a necessity in both work and personal lives, especially since the advent of the Internet. There are online communication applications focusing on everything from commerce to the military that must be secure to ensure privacy is achieved.

Cryptography deals with securing electronic communication. A major part of cryptography is hash functions. They take an input message of any length and produce an output of a fixed length. Hash functions can only be used one way, meaning an input message cannot be derived from an output. Furthermore, the design of these functions cause a drastic change in the output when an input is even slightly changed. Applications of hash functions include file integrity, password verification, file identification, pseudorandom number generation, as well as key derivation [1], [2].

Due to the algorithms used in their computation, hash functions have poor speed performance on general purpose processors, such as central processing units (CPUs) in computers [3]. In order to achieve high speed and secure communication, hash functions must be accelerated using application specific processors. These processors can be implemented in dedicated hardware, such as application specific integrated circuits (ASICs), or they can be designed with reconfigurable hardware, with field programmable gate arrays (FPGAs). ASICs require the longest design time, but provide the best in performance and power efficiency. The development cost can only be overcome with the production of a high volume of circuits. If the time to market must be short, or the volume needed is too small, ASIC design can be unacceptable for a certain application. FPGAs can be reconfigured to implement any hardware design. This makes them useful in prototyping of systems, or even in final products when the cost of using ASICs is too high. Another advantage of FPGAs is that their reprogrammable hardware can be changed to suit different applications at runtime.

Traditional FPGA design is done using hardware description languages (HDLs). This process is very tedious and time consuming compared to software development programming languages. HDL programming in FPGA designs can be compared to using assembly code for CPU programs. The ability to specify hardware designs in a high level and abstract way is needed to substantially expand the user base for FPGA technologies. The process of designing FPGA hardware using high level languages (HLLs) is called high level synthesis (HLS). This takes abstract designs and synthesizes them down to an HDL model. Existing tools can then compile it into FPGA hardware. HLS allows programmers that do not have the strong background needed in hardware design to easily utilize FPGAs in their applications. There have been many attempts to produce HLS tools, such as Xilinx Vivado, University of Toronto's LegUp, and the Altera Software Development Kit (SDK) for OpenCL (AOCL) [4]–[6]. These tools take different approaches to implementing HLS designs. The Altera SDK for OpenCL uses a heterogeneous computing approach to HLS.

Heterogeneous computing systems contain additional computational hardware besides CPUs. These systems are used for demanding applications that have poor performance on CPUs. The most popular heterogeneous computing components are graphical processing units (GPUs), also known as video cards. They are used to enable very fast rendering of graphics that will be displayed to the user and allow for greater

2

complexity in user interfaces. A separate GPU is a necessity to play modern games on computers due to the amount of computation needed to simulate the physics and image aspects of the display. The clock frequency of a GPU is much slower than that of the CPU, but it contains multiple computational units that can all work in parallel, allowing a much higher throughput than a CPU. GPUs can be used for more than just graphics. By taking control of the processing power of the hardware, it is possible to use them in high throughput and parallel computational tasks. To allow programs to utilize GPUs and other hardware, the Open Computing Language (OpenCL) was developed [7]. This has become a popular standard for heterogeneous computing using CPUs, GPUs, digital signal processors (DSPs), and even FPGAs.

The AOCL uses the heterogeneous computing standard to allow programs to take advantage and utilize FGPA hardware installed in a computer. Rather than just converting high level designs to FPGA implementation, it focuses on utilizing FPGA hardware to accelerate computationally intensive parts of programs.

#### **1.1** Thesis Goals

Cryptographic hash functions have many applications on computers and servers, but their speed performance is poor on CPU hardware. In a heterogeneous computing system with reconfigurable FPGA hardware available, the computation of the hash functions can be accelerated to increase speed performance of these applications.

#### **1.1.1 General Objectives**

• Develop an understanding of the OpenCL programming ecosystem and its relationship to HLS for FPGAs

- Explore the Secure Hash Algorithms (SHAs) defined by the National Institute of Standards and Technology (NIST).

- Develop C++ implementations of the SHAs to run on CPU.

- Use the AOCL to accelerate the OpenCL versions of the SHAs (functionally equivalent to C++ implementations) using an FPGA.

- Evaluate the speedup of the HLS model compared to CPU speed and other FPGA implementations in published literature.

- Test the viability of the Altera SDK for OpenCL platform in the acceleration with this common and computationally intensive task.

#### **1.2** Thesis Outline

The goal of this thesis is to accelerate the secure cryptographic functions specified in the secure hash standard using the AOCL HLS tool for FPGAs. In Chapter 2, background information is presented on FPGAs, HLS, heterogeneous computing, OpenCL, SHAs, as well as a review of relevant work in literature. Chapter 3 presents the synthesis and evaluation of the SHAs. This includes a detailed description of the design process and final outcomes. Chapter 3 also includes the experimental results and discussion comparing them to previous related research work. Finally, in Chapter 4, the thesis concludes with a summary and discussion of possible future work in this area.

#### **Chapter 2 Background and Related Work**

There has been much research done in the area of accelerating cryptographic hash functions using FPGAs. This chapter focuses on the giving an overview of FPGAs, as well as HLS. It then goes on to describe heterogeneous computing systems, OpenCL, and the AOCL CAD tool that is used in this work. The secure hash standard and its functions are outlined in detail. The chapter ends with a literature review of published research using FPGAs to accelerate the functions of the secure hash standard.

#### 2.1 Field Programmable Gate Arrays

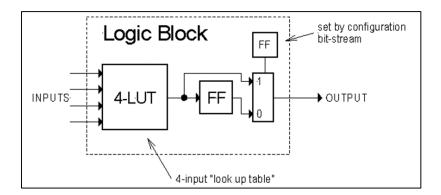

FPGAs are prefabricated chips that contain reconfigurable hardware. They can be programmed and reprogrammed to implement different applications. FPGAs consist of memory blocks, input-output (IO) blocks, logic elements (LEs), as well as embedded hardware such as DSP blocks. All of these elements are attached with programmable interconnects [8]. Configuring these interconnects and LEs will implement a hardware design. Each LE is composed of a look-up table and a flip-flop. The architecture is shown in Figure 2.1. The function of the 4-input look-up table (4-LUT) is to implement any binary function of 4 inputs. For more complex functions, such as multiplication or division, the integrated DSP blocks are used to reduce the number of LEs needed, and increase speed of computation.

Figure 2.1: Logic Element Architecture [9]

Traditional FPGA design is done with hardware description languages (HDLs), such as Verilog or VHDL. Using mature computer aided design (CAD) tools, very fast and efficient FPGA hardware is generated from the HDL specifications.

#### 2.2 High Level Synthesis

Design using HDLs for FPGAs is a tedious and time consuming process. The complexity of the programming limits the utilization of FPGA technology to developers with a good understanding of hardware design. The time needed to complete HDL designs is much longer than comparable applications in software. This is due to the high level and abstract specification possible in software development. To advance adoption and utilization, FPGA design needs to become as simple as software development. The process of high level synthesis (HLS) aims to allow FPGA models be specified in high level software languages such as C or C++. The way that HLS CAD tools work is to take algorithms written in high level languages (HLLs) and generate optimized HDL models that can then be synthesized to FPGA hardware using existing tools. These HLS tools allow people without the complex hardware design knowledge to use FPGAs in their

applications. HLS tools can also speed up FPGA design to similar timeframes as software development.

Some currently available HLS tools include Xilinx Vivado, University of Toronto's Legup, and the Altera SDK for OpenCL [4]–[6]. These tools take different approaches in imagining the future of HLS. Vivado and Legup both take an algorithm that is specified in a HLL and create a functionally equivalent HDL model. The Altera SDK for OpenCL targets the acceleration of computationally intensive programs by utilizing an FPGA board installed in a computer. The FPGA is used to offload high intensive calculation from the CPU.

#### 2.3 Heterogeneous Computing

Traditional computing systems contain only one type of processor, the CPU. When applications exist that have inherently poor performance on CPUs, there is no way to accelerate them on the available hardware. To increase computation speed, specialized hardware is added to the system. These systems that contain multiple types of processors are referred to as heterogeneous computing systems [10]. These specialized processors can be multicore CPUs, GPUs, DSPs, FPGAs, or other devices. The most common, GPUs, were designed to process complex graphics for displays, however, their hardware can be exploited to do other computational tasks. The different architecture of the GPU allows for high throughput parallel processing. Other types of heterogeneous components can run certain applications faster or more efficiently.

#### 2.3.1 Open Computing Language

The most challenging aspect of using heterogeneous computing systems is creating programs that can take advantage of the installed hardware. Open computing language (OpenCL) was developed to be the standard programming language for heterogeneous systems [7]. Having one language that can accommodate all types of added devices allows for maximum portability of programs.

OpenCL was first developed by Apple Inc. in 2008, but has since been taken over by the Khronos Group [7]. This is a group of companies that work together to create royalty-free open standards for various computational applications. Some other popular standards they are responsible for maintaining, besides OpenCL, are OpenGL, WebGL, and Vulkan [11]. With multiple companies working together on the application program interface (API) of the OpenCL standard, compatibility between vendors is guaranteed. That doesn't mean that all the hardware is identical, but each implementation must provide the specified characteristics to be OpenCL certified.

The OpenCL model operates with two required components. The first is the host processor that is used to execute standard sequential program code. This host processor is usually the CPU in a workstation or server. The second component is the OpenCL device, which is used to run the parallel component of the code. There can be multiple OpenCL devices in a single system used together to achieve the highest possible throughput. The program code is broken into two parts as well, the host program and the OpenCL kernel. The host program, unsurprisingly, runs on the host processor, and is used to initialize the OpenCL device and data. The OpenCL kernel is the code that runs on the OpenCL device. Multiple instances of the kernel can be executed simultaneously depending on the capabilities of the OpenCL device targeted.

#### 2.3.1.1 Host Program

The host program is no different from any other traditional CPU program. The OpenCL API is used to find, setup, and initialize the OpenCL devices. The API exists for C and C++ programming languages. The host program is needed to organize and send the proper data to the OpenCL implementation. The API includes many functions that make the application very portable between different systems. An example of this is the querying functions that are available. The host program can scan for installed OpenCL compatible hardware. Then, it can be programmed to use any configuration of hardware available. This allows the creation of OpenCL applications that can adapt to any system with the best possible results. For this to be practical, the kernel code must be compiled at runtime, which means a compiler must be included in the OpenCL software development kit (SDK) for that device. The kernel code can be compiled pre-runtime as well, but that limits the OpenCL devices that the program can utilize.

Another aspect of the host program is initialization and setup of the kernel. The OpenCL kernel can be thought of as a regular function in programming. The kernel has arguments that need to be set and it must be launched by the host. When an argument to a kernel contains a large amount of data it is best to use an OpenCL buffer object. The API contains functions for creating, reading, and writing to buffers.

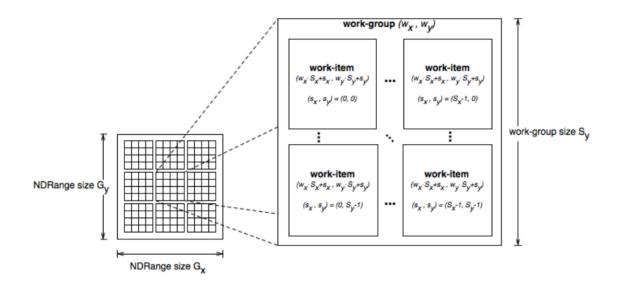

Kernels can be launched in multiple instances. Each instance is defined as a workitem. These work-items can be organized into multiple work-groups, and can be identified in one, two, or three dimensions, called the N-Dimensional Range (NDRange). The NDRange is specified depending on the application to make indexing more intuitive. The work-group size is then specified in each dimension. The number of work-groups will be determined by the total number of work-items and the work-group size. Proper organization of work-items can significantly improve performance of certain algorithms. Figure 2.2 shows the organization of the work-items and work-groups with an NDRange set to 2. This visualization can be expanded into 1 or 3 dimensions to understand the effect of setting the NDRange.

Figure 2.2: Organization of OpenCL Work-Groups and Work-Items with NDRange of 2 [7]

Some OpenCL API commands are executed by adding them to a created command queue, which is another type of OpenCL object. A command queue exists for each OpenCL device and executes the appropriate commands in a sequential fashion. The commands that are executed from the queue include reading or writing from OpenCL buffers, and launching the kernel. These operations can be blocking or non-blocking. Blocking operations force the host program to stall until the command has finished execution. This is needed to ensure data integrity when reading/writing to buffers. Without blocking the host could change the data in the middle of processing the memory transfer. Non-blocking commands allow the host program to continue. Then the CPU is able to keep executing commands while the OpenCL device executes the kernel.

The host program can be compiled with any standard C or C++ compiler. There is no requirement to the compilation, other than linking to the appropriate OpenCL SDK libraries for the used devices.

#### 2.3.1.2 OpenCL Kernel

The OpenCL kernel is the second component of an OpenCL application. This is the code that runs on the OpenCL device. Its execution is invoked by the host program. The kernel is written in a language that is a subset of the C-99 programming language [7]. The kernel function is of type *void* and does not return any value. In order to send data back to the host, an OpenCL buffer must be used that is given as an argument to the function. Other arguments can exist of single variables, just like other programming functions.

There are four memory types available in OpenCL implementations. The first is global memory. This is usually the RAM attached to the OpenCL device. It can be accessed by both the host program and the kernel. This is where the OpenCL buffers exist and it is used to transfer data between the host program and the kernel. It has the slowest access time of all the OpenCL memories. The second type of memory is constant memory. This is a subset of global memory that is only writable from the host. The kernel can only read this memory. It is used to transfer constant variables from the host to the kernel. The next type of memory is local memory. It is only accessible to the kernel. It is embedded in the OpenCL device and has very fast access time compared to that of global memory. Work-items in the same work-group access the same block of local memory but work-items in different work-groups cannot. This limitation keeps the memory access very fast and can impact the organization of the work-groups. The size of the local memory is also very small compared to global memory. The last type of memory is private memory which is independent for each work-item. The use of private memory is to hold the internal variables of the work-item. These memory types may be implemented differently in separate OpenCL devices, but they must have those characteristics. Proper utilization of the memory architectures available in OpenCL is the key to achieving good performance.

The OpenCL API has many functions built in that the kernel can execute such as math and print functions. A very important set of functions are the work-item functions. They are used to get the identifier of the current work-item in the work-group or globally. They can also be used to determine the NDRange, the number of work-groups, or number of work-items. These functions are important as they permit an easy way to specify which portion of a data set that specific work-item will operate on. It also allows for the creation of dynamic kernels that can adjust automatically for a different number or size of work-groups, without the need of redesign.

The kernel can be compiled in two different ways. The first is at runtime with the compiler built into the SDK for the target OpenCL device. This provides the greatest portability of the code, and allows the most systems to be supported. However, different types of OpenCL devices can be optimized in different ways to achieve the best performance. If a certain OpenCL device is the known target of the application, the

proper optimization can be done and the kernel can be compiled before runtime. This makes the application restricted to certain systems, but with increased performance. It also takes away the need to compile at runtime, making it run slightly faster. This is also the only practical solution for some OpenCL devices as compilation can take much longer than the acceptable amount of time to complete at runtime, such as FPGAs that can take hours to days to compile complex kernels.

#### 2.3.1.3 **OpenCL Extensions**

Devices must conform to the OpenCL standard to achieve the certification. It is still possible for certain devices to provide more functionality than specified in OpenCL. This is done through OpenCL extensions, which extend the functionality of the API for a certain device. It can be used to provide higher performance that what is offered in the standard, or enable features that are just not possible on different architectures.

#### 2.3.2 The Altera SDK for OpenCL

The AOCL is a HLS tool that focuses on combining reconfigurable hardware and heterogeneous computing by integrating FPGA peripherals into computers. It uses the OpenCL standard to target FPGA accelerator cards as the OpenCL device, with custom hardware that is optimized for each application.

#### 2.3.2.1 Host Program

The host program of an OpenCL application that targets Altera FPGAs is very similar to other OpenCL devices. The one caveat is that the kernel must be constructed in the host from the compiled binary image and not the OpenCL kernel source code. It cannot be compiled at runtime like other OpenCL devices. Other than that limitation, all that needs to be done is to link the host program to the OpenCL libraries included in the

SDK. Once that is completed, the program can be compiled by any C or C++ compiler and then executed.

#### 2.3.2.2 Kernel

As stated previously, the major difference when using the AOCL compared to other OpenCL devices is that compilation of the kernel is not possible at runtime. In order to execute a kernel, it must be first compiled into the FPGA binary for the specific FPGA installed on the system. The reason this needs to be done before runtime is that it can take multiple hours to compile the kernel as FPGA synthesis is a slow process. The AOCL is compliant with version 1.0 of the standard, but the current version is 2.1 [6], [12]. This means that only the features and functions available in the 1.0 specification are available to use. Some components, like the print function, which was added in 1.2, have been added into the AOCL [13].

#### 2.3.2.3 Extensions

As earlier described, it is possible for vendors to add more functionality to their OpenCL SDKs than that specified in the standard. These additions are called extensions. Due to the reconfigurable nature of FPGAs, some features have been added that are not possible to do on other OpenCL device architectures. One of these extensions is channels, which allows two concurrently running kernels to exchange data directly, without the need of global memory. This creates a first-in first-out (FIFO) buffer in the hardware that is responsible for data transfer. In other architectures, like a GPU, something like this is not possible with its static hardware. Depending on the application, this could be a huge performance boost when using FPGA. Other extensions are available that can allow direct input-output (IO) to the FPGA itself. Not needing to access data through RAM can allow for much faster operation.

#### 2.3.2.4 FPGA Accelerator Cards

The FPGA targets of the AOCL are attached to accelerator cards. These cards are peripheral component interconnect express (PCIe) devices that can be installed on most modern computer motherboards. They can be bought off the shelf from manufacturers such as Nallatech, Terasic, and BittWare [14]–[16], or they can designed and built from scratch. Board support packages (BSPs) are available from each vendor for each board. This is required to map the AOCL to the hardware architecture of the board. There is also a blank BSP available to easily create a package for custom made boards. The main components of the FPGA accelerator cards are an Altera Statix V or Arria 10 FPGA, double date rate 3 (DDR3) RAM, interfacing hardware, and cooling components. Some of the cards can also include high speed network interfaces, or other communication ports to direct IO directly into the accelerator. Nallatech has just released an accelerator card featuring dual Arria 10 FPGAs, opening multi-FPGA possibilities on a single peripheral [17]. Other cards differ slightly by the exact FPGA chip installed, having varying amounts of speed and area available.

The other target device of the AOCL is a system on chip (SoC) platform [18]. This system uses an Altera Cyclone V SoC which contains an FPGA and ARM host processor inside a single chip. The ARM processor can execute the host program to execute OpenCL kernels on the FPGA portion of the chip. This opens the HLS aspect of the AOCL to the word of embedded applications, which is more traditional application of FPGAs. In this thesis, the accelerator card that was used is the Terasic DE5-Net FPGA Developer board. It contains an Altera Stratix V GX FPGA, containing 622,000 LEs, and 4 GB of 1066 MHz DDR3 RAM.

#### 2.3.2.5 The Tools

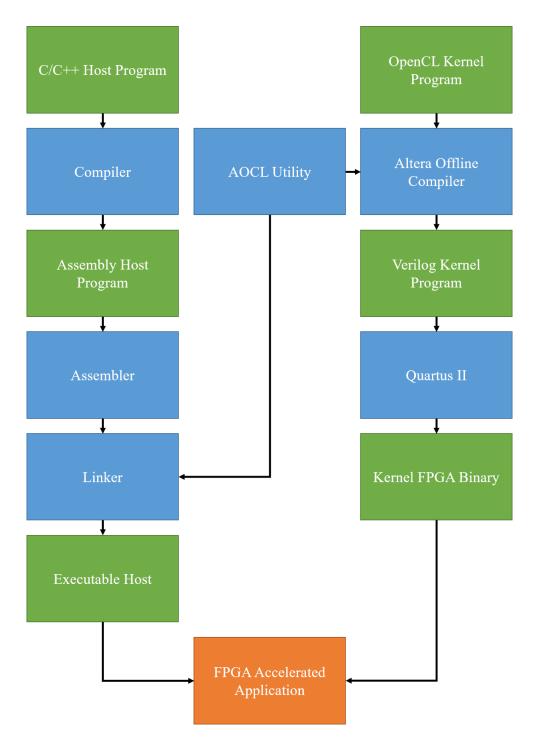

In order to program using the AOCL, there are three main software components needed. The first is the AOCL itself. Next is the BSP for the accelerator card. The last piece of software needed is the Quartus II CAD tool, which is Altera's tool for FPGA synthesis. Typically used for HDL design, it is very mature and efficient in the generation of FPGA hardware from HDL models. The AOCL contains two important programs. The first is the Altera Offline Compiler (AOC) which is responsible for compiling the kernel. The main function of AOC is to synthesize the OpenCL kernel to an intermediate Verilog form. It then calls Quartus II to compile that intermediate Verilog model into FPGA hardware. The second program included in the AOCL is the AOCL utility command, which is used to install the BSP, link the AOCL to the host program, as well as programming the FPGA device. The combination of these tools provides an intuitive and smooth HLS solution using the OpenCL standard.

Figure 2.3: Altera SDK for OpenCL Programming Flowchart

## **2.4** The Secure Hash Standard

The secure hash standard specifies three families of secure cryptographic hash functions [19], [20]. The purpose of these functions is to take an input of any arbitrary length and provide a fixed size output, called the digest. The operation of the hash functions only work in one direction meaning there is no way to generate the input back from the output. They are also designed in such a way that even a small change in the input should produce a drastic change in the output. These secure hash algorithms (SHAs) have many cryptographic applications, such as file integrity, password storage, file identification, pseudorandom number generation, and key derivation [1], [2].

File integrity is a very important aspect of digital communication. When transferring a file from one system to another, it is necessary to ensure that the file has not been changed or corrupted in any way. When the transfer median is the Internet, it becomes even more important as attackers can try to modify or spoof files to execute malicious programs. If firmware files become corrupted in transfer and are then programmed to device, the hardware can fault and become unrepairable. Using SHAs, the file can be examined on both ends of communication and if the outputs match, then the file integrity has been kept and it is identical to the original. If the output is different, than some problem has occurred, such as modification, corruption, or spoofing, and the file can be retransferred before execution.

Another important application of SHAs is password storage. When dealing with password authentication, the ability to safely store that information is vital, as users tend to use the same passwords for multiple applications. If a system is compromised and the passwords are stored as plaintext, then the attacker has access to the users other applications as well. SHAs can be used to securely store password information. When a password is created or changed, it will first be concatenated with another string, called the salt. Then the salt and password will be set as the input of a secure hash function. The output generated can then safely be stored. When the user needs to be authenticated, the same process is done. If the hash matches the stored value, then the password was correct. The purpose of the salt is added security to augment the output hash from other applications using the same SHA and password. Since the input cannot be derived from the stored hash, when the system is compromised there is no way to get the users plaintext password. Furthermore, the salt can then be changed and the user can still safely use the old password again.

SHAs can also be useful for file identification. Files are usually identified by their name, but names can be easily changed. A SHA can produce a fixed size identifier of any size input. Using the SHA output of a file to identify it means that the file is identified by its data only. If the name is changed, the SHA will be the same as the actual data of the file that has not changed. A SHA digest is like a fingerprint of a file. This system is commonly used in peer-to-peer file sharing applications. If a user changes the name, the application can still understand which file it is. If the file is modified, then the digest will change and appropriate measures can be taken to prevent the sharing of that file. This also provides protection against attackers masquerading malicious files as desired files.

Pseudorandom number generation can be accomplished through the use of SHAs. Taking a sequential series of numbers and computing the SHA digest of each will produce a pseudorandom number sequence. Truncating the hash to a certain number of bits can limit the size of the numbers that can be generated.

In public key cryptography there exists two keys needed for secure communication [21]. The first key is called the public key, which is known. The second key is the private key, which is unknown. The relationship between these keys defines asymmetric encryption. When a public key is used to encrypt data, only the private key is able to decrypt it. The reverse is also true, as public key is the only way to decrypt private key encrypted data. There are many advantages to the public key cryptography scheme, such as inherent authentication. Data is known to come from a certain source if the public key is able to decrypt it, as the private key was used to encrypt it. In symmetric key cryptography, there is only a single key that is used for both encryption and decryption. For both symmetric and asymmetric cryptography, some applications require the derivation of the public or shared keys. An example application of this is WPA and WPA2 security for wireless networks [22]. The key is derived by using a password-based key derivation function, which uses a SHA along with the password and wireless network name to generate the key. In a public key setting, using key derivation to generate the public key adds another layer of security to the system.

## 2.4.1 SHA-1

The SHA-1 variant is the first family of hash functions specified by NIST in the secure hash standard [19]. It was introduced in 1995 as a replacement for SHA-0, which had security flaws. The family only contains a single function that is used to produce a 160-bit digest. The input message must be less than  $2^{64}$  bits in length. The SHA-1 family has been deprecated [23], meaning that it is not to be used in new secure applications, however there are many legacy systems still rely on this 20 year old standard, keeping it relevant.

The algorithm of SHA-1 based on the Merkle–Damgård construction [24]. It takes an input message, M, which has a length, l, that is less than 2<sup>64</sup> bits. The algorithm operates with a word size of 32-bits. This means that all numbers are represented using 32-bits, and that any addition operations will be complete modulo 2<sup>32</sup>, as there is no storage for carry bits. The basic operation takes place on 512-bit blocks of the message, with eighty rounds of hashing done per block. This will repeat until all the blocks of the original message have been hashed.

The computation of SHA-1 function requires the following:

- Eighty 32-bit words, known has the message schedule, represented as  $W_0$  through  $W_{79}$ . Each word will be used in a single round of hashing.

- Five 32-bit working variables, *a*, *b*, *c*, *d*, and *e*. Another temporary 32-bit variable, *T*, is also needed. They will be used to hold intermediate values of the hash during the computation.

- Sixteen 32-bit words to represent the 512-bit message block. They are denoted as  $M_0^{(i)}$  through  $M_{15}^{(i)}$  where *i* is used to represent the number of the current message block.

- Five 32-bit words used to represent the 160-bit digest. In between message blocks they will hold the intermediate hash value. Similar to the message block, it is represented as  $H_0^{(i)}$  through  $H_4^{(i)}$ , where *i* is the current message block.

## 2.4.1.1 Initialization

Before hashing can begin, the initialization of the intermediate hashing variables must be completed. This is setting the initial values for  $H_0^{(0)}$  through  $H_4^{(0)}$  to the ones specified in the standard. The hexadecimal values can be found in Table 2.1.

Table 2.1: SHA-1 Initial Hash Values

$H_0^{(0)} = 67452301$   $H_1^{(0)} = \text{efcdab89}$   $H_2^{(0)} = 98\text{badcfe}$   $H_3^{(0)} = 10325476$  $H_4^{(0)} = \text{c3d2e1f0}$

## 2.4.1.2 Message Padding

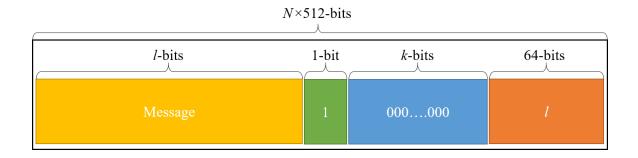

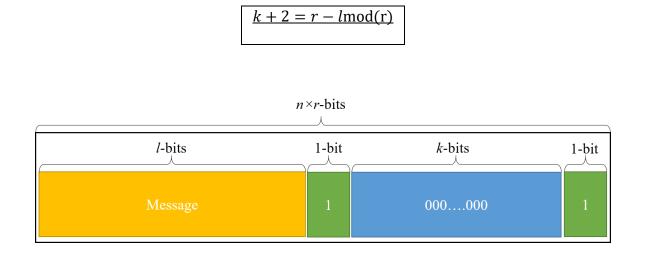

Another important step to be done before hashing occurs is padding the message. It has already been stated that the hash calculation takes place on a single 512-bit block of the message. For this to work out properly in the final block, the message must be padded to a length that is even multiple of 512-bits. The padding scheme is shown in Figure 2.4. The original message first has a single '1' bit appended to it, then many '0' bits, followed by the 64-bit binary representation of the message length, *l*. The number of '0' bits needed can be found by solving the following equation for *k*.

$$l + 1 + k = 448 \text{mod} 512$$

Once determined, the single '1' bit, the k '0' bits, and the 64-bit value of l, all appended to the original message will result in a new input that is a multiple of the 512-bit block size.

Figure 2.4: Representation of SHA-1 Padding Rule

#### 2.4.1.3 Step 1. – Message Schedule

The first step of the SHA-1 function is to determine the message schedule. The message schedule consists of eighty words, one that will be used in each round of hashing. The first sixteen are directly input from the current message block. The next sixty-four values are a function of previous message schedule values. This function incorporates a *bitwise rotate left (ROTL)* by 1 bit and *exclusive-ors (XORs)*. The formula is shown in Table 2.2.

Table 2.2: SHA-1 Step 1 - Message Schedule

$$W_{t} = \begin{cases} M_{t}^{(i)} & 0 \le t \le 15\\ ROTL^{1}(W_{t-3} \bigoplus W_{t-8} \bigoplus W_{t-14} \bigoplus W_{t-16}) & 16 \le t \le 79 \end{cases}$$

## 2.4.1.4 Step 2. – Update Working Variables

The second step of the algorithm is to simply update the working variables. They are updated to the value of the intermediate hash from the previous message block. In the case of the first message block, the values that were set in the initialization stage will be used. The details of this step is given in Table 2.3.

Г

$$a = H_0^{(i-1)}$$

$$b = H_1^{(i-1)}$$

$$c = H_2^{(i-1)}$$

$$d = H_3^{(i-1)}$$

$$e = H_4^{(i-1)}$$

## 2.4.1.5 Step 3. – Rounds of Hashing

The third step of SHA-1 is where all the computation actually occurs. In this step the eighty rounds of hashing are completed. The formula is given in Table 2.4. The process starts by setting the temporary variable T to the modular addition of five components. The first is a *ROTL* by 5 bits of the working variable a. The next is a round dependent function of the variables b, c, and d. Depending on the current round, the function will be either a *choose*, *parity*, or *majority* of the three variables. The third operand of the addition is the working variable e, followed by a round constant K which is a round dependent constant specified in the standard. The last component is the message schedule of the round. The other parts of each round shift the working variables by 1 word with the exception of c, which gets the variable b *ROTL* by 30 bits. Finally, each round is concluded by setting variable a to the value stored in temporary variable T. The process is completed until all rounds of hashing are done.

| Table 2.4: SHA | -1 Step 3 - Round | s of Hashing |

|----------------|-------------------|--------------|

|----------------|-------------------|--------------|

| for $t = 0$ to 79<br>{<br>$T = ROTL^5(a) + f_t(b, c, d)$<br>e = d<br>d = c<br>$c = ROTL^{30}(b)$<br>b = a<br>a = T<br>}                                                                                                               | $) + e + K^t + W^t$                                                             |                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| $f_t(x, y, z) = \begin{cases} Ch(x, y, z) = (x \land y) \oplus (\overline{x} \land x) \\ Parity(x, y, z) = x \oplus y \oplus z \\ Maj(x, y, z) = (x \land y) \oplus (x \land y) \\ Parity(x, y, z) = x \oplus y \oplus z \end{cases}$ | $z) \\ \land z) \oplus (y \land z)$                                             | $0 \le t \le 19$<br>$20 \le t \le 39$<br>$40 \le t \le 59$<br>$50 \le t \le 79$ |

| $K_{t} = \begin{cases} 5a827999 \\ 6ed9eba1 \\ 8f1bbcdc \\ ca62c1d6 \end{cases}$                                                                                                                                                      | $0 \le t \le 19$<br>$20 \le t \le 39$<br>$40 \le t \le 59$<br>$60 \le t \le 79$ |                                                                                 |

# 2.4.1.6 Step 4. – Update Intermediate Hash

The last step of the SHA-1 algorithm is to update the intermediate hash. This is done by performing modular addition between the previous message block's intermediate hash and the five working variables of the current message block, as shown in Table 2.5. If another message block has yet to be hashed, the entire process from step 1 to 4 will be repeated. If the last message block has been hashed, then the 160-bit digest is available by concatenating the five 32-bit hash variables together.

Table 2.5: SHA-1 Step 4 - Update Intermediate Hash

| $H_0^{(i)} = a + H_0^{(i-1)}$ |

|-------------------------------|

| $H_1^{(i)} = b + H_1^{(i-1)}$ |

| $H_2^{(i)} = c + H_2^{(i-1)}$ |

| $H_3^{(i)} = d + H_3^{(i-1)}$ |

| $H_4^{(i)} = e + H_4^{(i-1)}$ |

|                               |

## 2.4.2 SHA-2

SHA-2 is the second family of hash functions defined by NIST in the secure hash standard, and was published in 2001 [19]. The SHA-2 family contains six functions that provide differing digest sizes and security. The overall function process is very similar to that of SHA-1, and is also based on the Merkle–Damgård construction [24]. The characteristics of the different functions are shown in Table 2.6. The number in the algorithm name specifies the digest length. These six functions are made of only two different algorithms with slight modifications in initialization, and truncation of the output. SHA-224 and SHA-256 follow the exact same process, except the initial hash values that are set. The 256-bit output digest is simply truncated to the first 224-bits to achieve SHA-224. The other functions are the same as the SHA-512 variant, with similar changes made in initial values and truncation of the output.

| Function    | Message Size        | Block Size | Word Size | Digest Size |

|-------------|---------------------|------------|-----------|-------------|

| SHA-224     | $<2^{64}$ bits      | 512 bits   | 32 bits   | 224 bits    |

| SHA-256     | $<2^{64}$ bits      | 512 bits   | 32 bits   | 256 bits    |

| SHA-384     | $<\!\!2^{128}$ bits | 1024 bits  | 64 bits   | 384 bits    |

| SHA-512     | $<\!\!2^{128}$ bits | 1024 bits  | 64 bits   | 512 bits    |

| SHA-512/224 | $<\!\!2^{128}$ bits | 1024 bits  | 64 bits   | 224 bits    |

| SHA-512/256 | $<\!\!2^{128}$ bits | 1024 bits  | 64 bits   | 256 bits    |

Table 2.6: Characteristics of SHA-2 Functions

#### 2.4.2.1 SHA-256

SHA-256 will produce a 256-bit output digest from any input message with a length smaller than 2<sup>64</sup> bits. It has a word size of 32-bits and a block size of 512-bits. The number of hashing rounds in this algorithm is sixty-four per message block. This algorithm is identical to SHA-224 with slight changes that are detailed in the appropriate locations.

The following components are required for SHA-256:

- Sixty-four 32-bit words for the message schedule, denoted as  $W_0$  through  $W_{63}$ . One word is needed for each round of hashing.

- Eight 32-bit working variables, *a*, *b*, *c*, *d*, *e*, *f*, *g*, and *h*. Two temporary variables,

*T*<sub>1</sub> and *T*<sub>2</sub>, are also needed. These will hold intermediate values during each round of the hash computation.

- Sixteen 32-bit words to hold the 512-bit message block. They are defined as  $M_0^{(i)}$  through  $M_{15}^{(i)}$ , using *i* is to represent the number of the current message block.

- Eight 32-bit variables to represent the 256-bit intermediate and final hash values,  $H_0^{(i)}$  through  $H_7^{(i)}$ , where *i* is the current message block.

## 2.4.2.1.1 Initialization

Before the hash calculation can begin, initialization of the intermediate hashing variables must be completed. This is setting the initial values for  $H_0^{(0)}$  through  $H_7^{(0)}$  to the ones specified in the standard. The values that are set depend on the function used. If implementing SHA-224, this is the first change to the algorithm. The hexadecimal values for both functions can be found in Table 2.7.

| SHA-256                          | SHA-224                         |

|----------------------------------|---------------------------------|

| (-)                              |                                 |

| $H_0^{(0)} = 6a09e667$           | $H_0^{(0)} = c1059ed8$          |

| $H_1^{(0)} = bb67ae85$           | $H_1^{(0)} = 367 \text{cd} 507$ |

| $H_2^{(0)} = 3c6ef372$           | $H_2^{(0)} = 3070 dd 17$        |

| $H_3^{(0)} = a54 \text{ff} 53 a$ | $H_3^{(0)} = f70e5939$          |

| $H_4^{(0)} = 510e527f$           | $H_4^{(0)} = \text{ffc00b31}$   |

| $H_5^{(0)} = 9b05688c$           | $H_5^{(0)} = 68581511$          |

| $H_6^{(0)} = 1$ f83d9ab          | $H_6^{(0)} = 64f98fa7$          |

| $H_7^{(0)} = 5$ be0cd19          | $H_7^{(0)} = befa4fa4$          |

|                                  |                                 |

Table 2.7: SHA-256 Initial Hash Values

## 2.4.2.1.2 Message Padding

The block size and word size of the SHA-256 algorithm are the same as SHA-1. The padding scheme is also identical to the previous hash family. This means that the entire message padding process is equivalent to that of SHA-1. See section 2.4.1.2 for the detailed description.

#### 2.4.2.1.3 Step 1. – Message Schedule

Once again, deriving the message schedule is the first step of the algorithm. In SHA-256, this consists of sixty-four words. The first sixteen are directly input from the message block. The next forty-eight are calculated using a function of four previous message schedule words. This function incorporates modular addition and two other functions, denoted as  $\sigma_0$  and  $\sigma_1$ . Each of these functions include *bitwise rotate rights* (*ROTRs*), *bitwise right shifts* (*SHR*), and *XORs*. The number of shift and rotate bits differ between the functions. The step outline is shown in Table 2.8.

#### Table 2.8: SHA-256 Step 1- Messasge Schedule

$$W_{t} = \begin{cases} M_{t}^{(i)} & 0 \le t \le 15\\ \sigma_{1}^{\{256\}}(W_{t-2}) + W_{t-7} + \sigma_{0}^{\{256\}}(W_{t-15}) + W_{t-16} & 16 \le t \le 63 \end{cases}$$

$$\sigma_{0}^{\{256\}}(x) = ROTR^{7}(x) \oplus ROTR^{18}(x) \oplus SHR^{3}(x)$$

$$\sigma_{1}^{\{256\}}(x) = ROTR^{17}(x) \oplus ROTR^{19}(x) \oplus SHR^{10}(x)$$

# 2.4.2.1.4 Step 2. – Update Working Variables

Step two of SHA-256 is updating the working variables. They are set to the value of the intermediate hash from the previous message block. In the case of the first message block, the values that were set in the initialization stage will be used. Again, these values will differ between the SHA-256 and SHA-224 functions. The step is detailed in Table 2.9.

| Table 2.9: | SHA-256 | Step 2 - | Update | Working | Variables |

|------------|---------|----------|--------|---------|-----------|

|------------|---------|----------|--------|---------|-----------|

$$a = H_0^{(i-1)}$$

$$b = H_1^{(i-1)}$$

$$c = H_2^{(i-1)}$$

$$d = H_3^{(i-1)}$$

$$e = H_4^{(i-1)}$$

$$f = H_5^{(i-1)}$$

$$g = H_6^{(i-1)}$$

$$h = H_7^{(i-1)}$$

## 2.4.2.1.5 Step 3. – Rounds of Hashing

The third step in the algorithm is the sixty-four rounds of hashing. This step contains the majority of computation required to calculate a message digest. The first step is calculating the two temporary variables,  $T_1$  and  $T_2$ . The value of  $T_1$  is a modular addition of variable h, the message schedule for that round,  $W_t$ , and the round constant,  $K_t$ . There is also two operands to the sum that are the result of different functions, one being a *choose* function with inputs e, f, and g, while the other is the function  $\sum_1$  with input e.  $\sum_1$  returns the result of *XORing* together three *ROTRs* of the input. The rotate factors are 6-bits, 11-bits, and 25-bits, respectively. To calculate  $T_2$ , it is the sum of a *majority* function with the inputs a, b, and c, and  $\sum_0$  with the input a.  $\sum_0$  is the same as  $\sum_1$  but with rotate factors of 2-bits, 13-bits, and 22-bits instead. The rest of the round shifts the working variables by one word, with the exception of variable e, which gets the addition of d and  $T_1$ , and variable a, which gets the value of summing  $T_1$  and  $T_2$ . This step repeats until all sixty-four rounds are completed.

for

$$t = 0$$

to 63 by 1

{

$T_1 = h + \sum_{1}^{\{256\}} (e) + Ch(e, f, g) + K_t^{\{256\}} + W_t$

$T_2 = \sum_{0}^{\{256\}} (a) + Maj(a, b, c)$

$h = g$

$g = f$

$f = e$

$e = d + T_1$

$d = c$

$c = b$

$b = a$

$a = T_1 + T_2$

}

$Ch(x, y, z) = (x \land y) \oplus (\overline{x} \land z)$

$Maj(x, y, z) = (x \land y) \oplus (x \land z) \oplus (y \land z)$

$\sum_{0}^{\{256\}} (x) = ROTR^2(x) \oplus ROTR^{13}(x) \oplus ROTR^{22}(x)$

$\sum_{1}^{\{256\}} (x) = ROTR^6(x) \oplus ROTR^{11}(x) \oplus ROTR^{25}(x)$

Values for  $K_t^{\{256\}}$  can be found in the secure has standard documentation [19].

# 2.4.2.1.6 Step 4. – Update Intermediate Hash

Finally, the intermediate hash variables are updated to the sum of their previous value and the corresponding working variable, as shown in Table 2.11. The entire algorithm is repeated until all the message blocks have been processed. Once that has

happened, the 256-bit output is given by concatenating all eight intermediate hash variables together. If the function is SHA-224, that 256-bit digest is truncated to 224-bits.

| $H_0^{(i)} = a + H_0^{(i-1)}$ |

|-------------------------------|

| $H_1^{(i)} = b + H_1^{(i-1)}$ |

| $H_2^{(i)} = c + H_2^{(i-1)}$ |

| $H_3^{(i)} = d + H_3^{(i-1)}$ |

| $H_4^{(i)} = e + H_4^{(i-1)}$ |

| $H_5^{(i)} = f + H_5^{(i-1)}$ |

| $H_6^{(i)} = g + H_6^{(i-1)}$ |

| $H_7^{(i)} = h + H_7^{(i-1)}$ |

|                               |

Table 2.11: SHA-256 Step 4 - Update Intermediate Hash

## 2.4.2.2 SHA-512

The SHA-512 function produces a 512-bit digest of the input message. In this case the size of the file must be less than 2<sup>128</sup> bits. The algorithm uses a word size of 64 bits with a block size of 1024 bits. SHA-512 computes eighty rounds of hashing on each message block. Other functions of the SHA-2 family use the same algorithm as SHA-512, with slight modifications. These functions are SHA-384, SHA-512/224, and SHA-512/256. The changes needed to implement these functions are descripted where required.

The computation of the SHA-512 function needs the following components:

• Eighty 64-bit words for the message schedule, one for each round of hashing, represented as  $W_0$  through  $W_{79}$ .

- Eight 64-bit working variables, *a*, *b*, *c*, *d*, *e*, *f*, *g*, and *h*. Two temporary variables,

*T*<sub>1</sub> and *T*<sub>2</sub>, are also needed. They will be used to hold intermediate values during each round of the hash computation.

- Sixteen 64-bit words to hold the 1024-bit message block. They are denoted as  $M_0^{(i)}$  through  $M_{15}^{(i)}$ , using *i* is to represent the number of the current message block.

- Eight 64-bit variables to represent the 512-bit intermediate and final hash values,  $H_0^{(i)}$  through  $H_7^{(i)}$ , where *i* is the current message block.

## 2.4.2.2.1 Initialization

In a similar fashion to SHA-256, the intermediate hash variables must be initialized to values specified in the standard before the computation can begin. These values are different for each variant that follows the same algorithm. There are defined values for SHA-512, SHA-384, SHA-512/224, as well as SHA-512/256. The values in hexadecimal form for  $H_0^{(0)}$  through  $H_7^{(0)}$  are shown in Table 2.12.

| SHA-512                                                                                                                                                                                                  | SHA-384                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5111-512                                                                                                                                                                                                 | 5111-304                                                                                                                                                                                                                            |

| $H_0^{(0)} = 6a09e667f3bcc908$                                                                                                                                                                           | $H_0^{(0)} = \text{cbbb9d5dc1059ed8}$                                                                                                                                                                                               |

| $H_1^{(0)} = bb67ae8584caa73b$                                                                                                                                                                           | $H_1^{(0)} = 629a292a367cd507$                                                                                                                                                                                                      |

| $H_2^{(0)} = 3c6ef372fe94f82b$                                                                                                                                                                           | $H_2^{(0)} = 9159015a3070dd17$                                                                                                                                                                                                      |

| $H_3^{(0)} = a54 ff 53 a 5 f1 d36 f1$                                                                                                                                                                    | $H_3^{(0)} = 152$ fecd8f70e5939                                                                                                                                                                                                     |

| $H_4^{(0)} = 510e527$ fade682d1                                                                                                                                                                          | $H_4^{(0)} = 67332667 \text{ffc} 00b31$                                                                                                                                                                                             |

| $H_5^{(0)} = 9b05688c2b3e6c1f$                                                                                                                                                                           | $H_5^{(0)} = 8eb44a8768581511$                                                                                                                                                                                                      |

| $H_6^{(0)} = 1$ f83d9abfb41bd6b                                                                                                                                                                          | $H_6^{(0)} = db0c2e0d64f98fa7$                                                                                                                                                                                                      |

| $H_7^{(0)} = 5$ be0cd19137e2179                                                                                                                                                                          | $H_7^{(0)} = 47b5481dbefa4fa4$                                                                                                                                                                                                      |

|                                                                                                                                                                                                          |                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                          |                                                                                                                                                                                                                                     |

| SHA-512/224                                                                                                                                                                                              | SHA-512/256                                                                                                                                                                                                                         |