#### University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

2013

# Hardware JPEG Decompression

Dan MacDonald University of Windsor

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### **Recommended** Citation

MacDonald, Dan, "Hardware JPEG Decompression" (2013). Electronic Theses and Dissertations. Paper 4889.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

### Hardware JPEG Decompression

by

Dan MacDonald

A Thesis

Submitted to the Faculty of Graduate Studies through the Department of Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada 2013

#### $\bigodot$ 2013 Dan MacDonald

All Rights Reserved. No Part of this document may be reproduced, stored or otherwise retained in a retreival system or transmitted in any form, on any medium by any means without prior written permission of the author. Hardware JPEG Decompression by Dan MacDonald

APPROVED BY:

Boubakeur Boufama Computer Science

Huapeng Wu Electrical and Computer Engineering

Roberto Muscedere, Advisor Electrical and Computer Engineering

May 15, 2013

# **Declaration of Originality**

I hereby certify that I am the sole author of this thesis and that no part of this thesis has been published or submitted for publication.

I certify that, to the best of my knowledge, my thesis does not infringe upon anyones copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material from the work of other people included in my thesis, published or otherwise, are fully acknowledged in accordance with the standard referencing practices. Furthermore, to the extent that I have included copyrighted material that surpasses the bounds of fair dealing within the meaning of the Canada Copyright Act, I certify that I have obtained a written permission from the copyright owner(s) to include such material(s) in my thesis and have included copies of such copyright clearances to my appendix.

I declare that this is a true copy of my thesis, including any final revisions, as approved by my thesis committee and the Graduate Studies office, and that this thesis has not been submitted for a higher degree to any other University or Institution.

### Abstract

Due to the ever increasing popularity of mobile devices, and the growing number of pixels in digital photography, there becomes a strain on viewing one's own photos. Similar to Desktop PCs, a common trend occurring in the mobile market to compensate for the increased computational requirements is faster and multi-processor systems. The observation that the number of transistors in integrated circuits doubles approximately every 18-24 months is known as Moore's law. Some believe that this trend, Moore's law, is plateauing which enforces alternate methods to aid in computation.

This thesis explores supplementing the processor with a dedicated hardware module to reduce its workload. This provides a software-hardware combination that can be utilized when large and long computations are needed, such as in the decompression of high pixel count JPEG images. The results show that this proposed architecture decreases the viewing time of JPEG images significantly. I would like to dedicate this work to my family and friends. I thank you for the support and motivation to tinker and find this path.

## A cknowledgments

I will always be grateful to my supervisor, Dr. Muscedere, for his vast knowledge, advice, and for bringing this challenging project to my attention.

I'd also like to thank my other committee members, Dr. H. Wu and Dr. B. Boufama, for their support in this research. Lastly, I'd like to thank my dog Maxx for posing in a test image.

# Contents

| De       | eclara | ation of Originality             | iv  |

|----------|--------|----------------------------------|-----|

| A        | bstra  | $\mathbf{ct}$                    | v   |

| De       | edica  | tion                             | vi  |

| A        | cknov  | wledgments                       | vii |

| Li       | st of  | Figures                          | xii |

| Li       | st of  | Tables                           | xiv |

| Li       | st of  | Abbreviations                    | xvi |

| 1        | Intr   | oduction                         | 1   |

|          | 1.1    | History of JPEG Images           | 2   |

|          | 1.2    | Overview of Research, Motivation | 3   |

|          | 1.3    | Organization of Thesis           | 4   |

| <b>2</b> | The    | JPEG Standard                    | 6   |

|          | 2.1    | Discrete Cosine Transform        | 7   |

#### CONTENTS

|   | 2.2                                                                                                | Quantization                                   | 10 |  |

|---|----------------------------------------------------------------------------------------------------|------------------------------------------------|----|--|

|   | 2.3                                                                                                | Huffman Encoding and Decoding                  | 11 |  |

|   | 2.4                                                                                                | Field Programmable Gate Array                  | 14 |  |

|   |                                                                                                    | 2.4.1 Soft Processor                           | 14 |  |

|   | 2.5                                                                                                | Summary                                        | 15 |  |

| 3 | Exis                                                                                               | sting Work in Hardware JPEG Algorithms         | 16 |  |

|   | 3.1                                                                                                | libjpeg                                        | 17 |  |

|   | 3.2                                                                                                | Inverse Discrete Cosine Transform (IDCT)       | 18 |  |

|   |                                                                                                    | 3.2.1 Distributed Arithmetic DCT               | 19 |  |

|   |                                                                                                    | 3.2.2 Loeffler Algorithm                       | 20 |  |

|   | 3.3                                                                                                | YCC to RGB Colour Space Conversion             | 22 |  |

|   |                                                                                                    | 3.3.1 Look Up Table                            | 24 |  |

|   |                                                                                                    | 3.3.2 Shift and Add                            | 25 |  |

|   |                                                                                                    | 3.3.3 Integer Based Transform                  | 26 |  |

|   | 3.4                                                                                                | Summary                                        | 27 |  |

| 4 | Pro                                                                                                | posed Hybrid Architecture                      | 28 |  |

|   | 4.1                                                                                                | Development Board Specs                        | 29 |  |

|   | 4.2                                                                                                | Hardware Software Communication                | 30 |  |

|   |                                                                                                    | 4.2.1 Communication through DDR2 RAM           | 31 |  |

|   |                                                                                                    | 4.2.2 Communication through Hardware Registers | 32 |  |

|   | 4.3                                                                                                | Hardware Design                                | 33 |  |

|   |                                                                                                    | 4.3.1 IDCT                                     | 33 |  |

|   |                                                                                                    | 4.3.2 Colour Conversion                        | 36 |  |

|   | $4.3.2  \text{Colour Conversion}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |                                                |    |  |

|              | 4.4                  | Software Design             | 38 |

|--------------|----------------------|-----------------------------|----|

|              |                      | 4.4.1 IDCT                  | 38 |

|              |                      | 4.4.2 Colour Conversion     | 40 |

|              | 4.5                  | Summary                     | 41 |

| <b>5</b>     | $\operatorname{Res}$ | ults                        | 43 |

|              | 5.1                  | Testing Setup and Procedure | 43 |

|              | 5.2                  | Timing Results              | 46 |

|              |                      | 5.2.1 Hardware Timing       | 49 |

|              | 5.3                  | Image Verification          | 50 |

|              | 5.4                  | Summary                     | 55 |

| 6            | Cor                  | clusion and Recommendations | 56 |

|              | 6.1                  | Recommendations             | 57 |

| R            | efere                | nces                        | 59 |

| A            | Sou                  | rce Images                  | 61 |

| В            | Tes                  | ting Scripts                | 63 |

| $\mathbf{C}$ | СС                   | Zode                        | 66 |

|              | C.1                  | libjpeg modifications       | 66 |

|              | C.2                  | ReadImage.c                 | 74 |

| D            | $\mathbf{VH}$        | DL Code                     | 80 |

|              | D.1                  | 2D IDCT                     | 80 |

#### CONTENTS

|              | D.2 | Colour Converter            | 95  |

|--------------|-----|-----------------------------|-----|

| $\mathbf{E}$ | Huf | fman Decoding Example       | 105 |

|              | E.1 | Source Image                | 105 |

|              | E.2 | Huffman Table Extraction    | 108 |

|              | E.3 | Image Decoding              | 109 |

|              |     | E.3.1 Block 1 - Luminance   | 109 |

|              |     | E.3.2 Block 1 - Chrominance | 110 |

|              |     | E.3.3 Block 2 - Luminance   | 111 |

|              |     | E.3.4 Block 2 - Chrominance | 112 |

|              | E.4 | Finalizing                  | 113 |

|              | E.5 | Huffman Tables              | 114 |

|              |     |                             |     |

#### Vita Auctoris

# List of Figures

| 2.1 | JPEG Compression Process [13]                    | 7  |

|-----|--------------------------------------------------|----|

| 2.2 | JPEG Decompression Process [13]                  | 7  |

| 2.3 | Energy Compaction of the DCT                     | 9  |

| 2.4 | Zig Zag order of a DCT block [13]                | 9  |

| 2.5 | Huffman Tree                                     | 13 |

| 3.1 | Desktop JPEG Profiling                           | 18 |

| 3.2 | Loeffler Algorithm for 1D DCT                    | 21 |

| 3.3 | Loeffler Algorithm for 1D IDCT                   | 22 |

| 3.4 | Cb-Cr colour plane at a constant luma value      | 23 |

| 4.1 | Layers of a GNU/Linux based embedded system      | 31 |

| 4.2 | Dequantization and 2D-IDCT Hardware Design       | 35 |

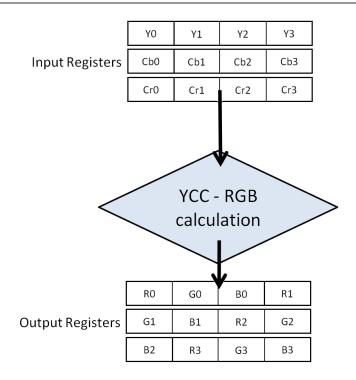

| 4.3 | YCC to RGB Hardware Design                       | 38 |

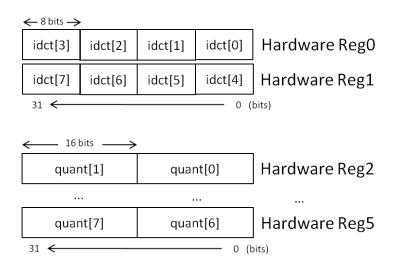

| 4.4 | IDCT array-register data compaction              | 39 |

| 4.5 | 3D image array                                   | 40 |

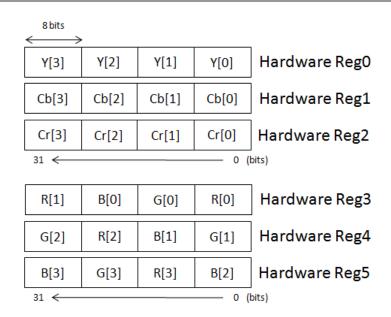

| 4.6 | Colour Conversion array-register data compaction | 41 |

#### LIST OF FIGURES

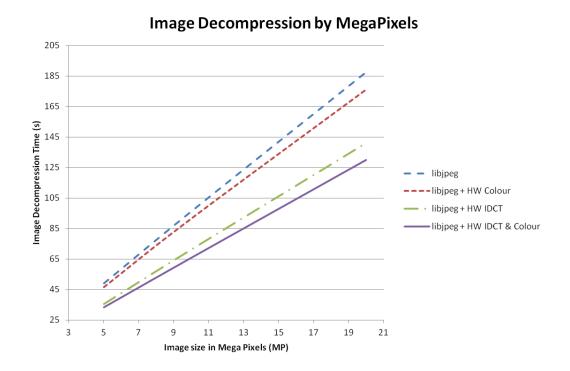

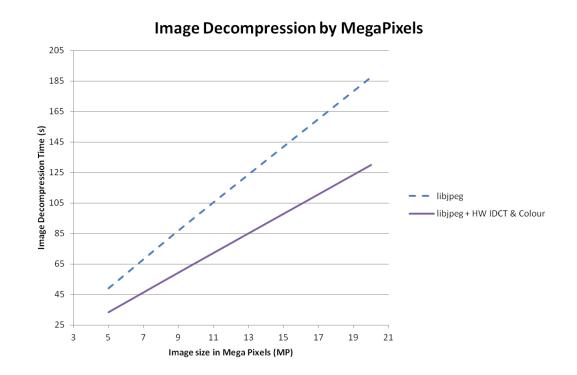

| 5.1 | Image Decompression Timing                | 48  |

|-----|-------------------------------------------|-----|

| 5.2 | Image Decompression Timing                | 49  |

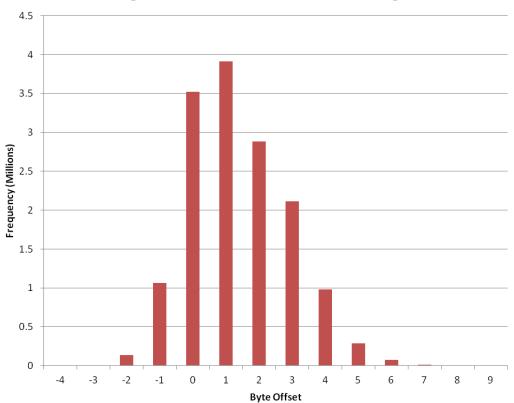

| 5.3 | Bookstore image byte offset histogram     | 51  |

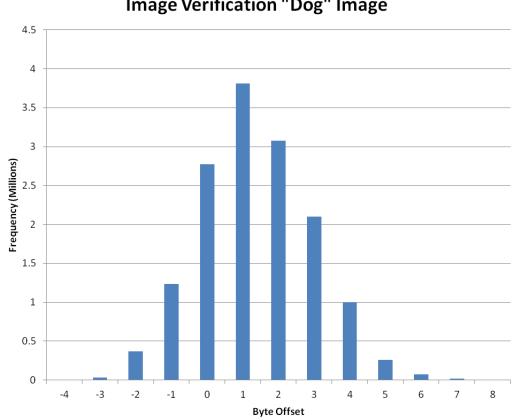

| 5.4 | Dog image byte offset histogram           | 52  |

| 5.5 | beach image byte offset histogram         | 53  |

| A.1 | Sample 20MP images                        | 62  |

| E.1 | Sample image                              | 106 |

| E.2 | HEX dump from sample image                | 106 |

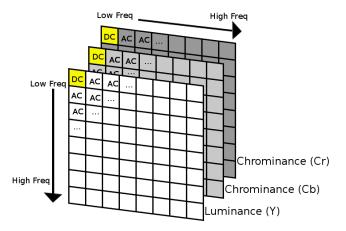

| E.3 | DCT Frequency domain of an 8x8 JPEG block | 107 |

# List of Tables

| 2.1 | Example Huffman data                                                   | 12  |

|-----|------------------------------------------------------------------------|-----|

| 3.1 | Butterfly[B], Rotator[R], and constant Multiplication Blocks for Loef- |     |

|     | fler's Algorithm                                                       | 21  |

| 3.2 | Colour Space Look Up Table example                                     | 24  |

| 4.1 | YCC - RGB constants                                                    | 37  |

| 5.1 | Test Image Dimensions                                                  | 46  |

| 5.2 | Bookstore Image Results                                                | 47  |

| 5.3 | Dog Image Results                                                      | 47  |

| 5.4 | Beach Image Results                                                    | 47  |

| 5.5 | Hardware Only Timing per test image                                    | 50  |

| 5.6 | Test Image Verification                                                | 54  |

| E.1 | Huffman Decoding Results                                               | 113 |

| E.2 | Huffman Luminance (Y) DC table                                         | 114 |

| E.3 | Huffman Luminance (Y) AC table                                         | 115 |

| E.4 | Huffman Chrominance (Cb and Cr) DC table                               | 116 |

| E.5 | Huffman Chrominance (Cb and Cr) AC table | 117 |

|-----|------------------------------------------|-----|

| E.6 | Huffman DC Value Encoding                | 118 |

List of Abbreviations

1D 1 Dimensional 2D2 Dimensional ASIC Application Specific Integrated Circuit CPU Central Processing Unit Discrete Cosine Transform DCT DSP Digital Signal Processing FDCT Forward Discrete Cosine Transform FPGA Field Programmable Gate Array HDL Hardware Description Language HWHardware IDCT Inverse Discrete Cosine Transform JPEG Joint Photographic Experts Group LUT Lookup Table MP Megapixel  $\mathbf{p}\mathbf{x}$ pixels RAM Random Access Memory RISC **Reduced Instruction Set Computer** SOC System On Chip SW Software RGB Red Green Blue VHDL VHSIC Hardware Description Language VHSIC Very High Speed Integrated Circuit YCC Luminance Chrominance(Cb) Chrominance(Cr)

# Chapter 1

### Introduction

In recent years digital photography has taken leaps and bounds in the consumer market. Along with improved sensors, functions, and touch screens, the pixel count of the images are steadily increasing. At the time of writing this thesis, a consumer can purchase a digital camera capable of taking a JPEG image of, 20 million pixels (20 MP). Additionally there has been an explosion with mobile devices such as smart phones and tablets. The trend that the number of transistors in integrated circuits doubles approximately every 18-24 months is known as Moore's law [9]. Following this trend, mobile processors are approaching the speed and multi-core architectures of their desktop counterparts. A pocket sized computer has its advantages, but it does face challenges when viewing the growing size of multi-media, especially digital images. By far the most popular form digital image in computing today is the JPEG (Joint Photographic Experts Group) image. JPEG images are found in every digital camera, photo editing suites, MPEG video, internet browsers, and video games to name a few. As all of the photo albums, and every photo taken become digitized into JPEGs, being able to comfortably view the images becomes necessary.

### 1.1 History of JPEG Images

Early in computing history a need for viewing digital images arose. However, with limited memory and storage space, raw image data was not a feasible solution. In 1986 a committee, the Joint Photographic Experts Group (JPEG) [4], was formed to create a standard for digitized images. The JPEG group worked to standardize a method of coding still pictures, known as JPEGs. The JPEG standard outlines a codec that defines how an image is compressed into a stream of bytes and decompressed back into an image.

The JPEG standard was first publicly released in 1992, which was approved as ITU-T Recommendation T.81 and in 1994 as ISO/IEC 10918-1. Two years later the standard was updated to include rules and checks for software conformance. Several parts of the standard have been added in the years since, which introduce features such as the JPEG File Interchange Format(JFIF), that outlines the structure of the raw data in the file.

The focus of the JPEG codec is to preserve as much data as possible while compressing it into a much smaller file size. Due to this fact, JPEG images are considered a lossy compression. By default they have a high degree of compression, with minimal perceptible loss in image quality but this can be adjusted. Adjustment of the compressions ratio results in a tradeoff between data losses and file size. Higher compression ratio have smaller file size, and vice versa. The JPEG standard provides a framework for image compression and decompression, but depending on the algorithms used determines the different types of JPEGs. A few types are progressive sequential, lossless and baseline sequential. By far the most common type is Baseline Sequential. The standard provides a simple and efficient algorithm which makes it suitable for all digital cameras.

### 1.2 Overview of Research, Motivation

The accelerating popularity of mobile devices, and exploding pixel counts found in consumer grade digital cameras have lead to an issue when attempting to view ones own images. Many software applications have employed techniques when displaying larger images, such as pre-computing display sized thumbnails. However precomputation of a digital photo album does not resolve the problem, nor are these techniques future proof against large device screen sizes, resolution, and increasing pixel count. The focus of this thesis is to present an alternative architecture to relieve computations from the CPU and therefore improve upon the delay mobile devices undergo when accessing large JPEG images. Currently there are dedicated hardware modules for audio and video playback, but nothing has been done for still images. This work is implemented on an embedded FPGA Linux platform using a JPEG decoding software library found in the majority of mobile devices.

This thesis demonstrates the capability of dedicated hardware to assist the CPU in computational workloads. It primarily focuses on reducing delays from the mathematically challenging two-dimensional inverse discrete cosine transform (IDCT), and the colour conversion from the luminance, and chrominance channels to the red, green, blue colour system frequently used in digital displays. It achieves improvements from hardware and software optimizations.

#### **1.3** Organization of Thesis

Chapter 1 begins with an introduction to JPEG images and the JPEG ISO Standard, then continues with a brief introduction to digital photography and trends in the mobile market. Chapter 2 elaborates on the JPEG standard, describing the necessary steps used to compress and decompress raw data to and from a viewable image. Chapter 3 discusses previous works which aid in specific algorithms used by the JPEG standard. Chapter 4 proposes a new software-hardware hybrid architecture used to improve upon the JPEG decoding time. Chapter 5 presents the testing methodology, timing results, and verification of the hybrid architecture. Chapter 6 concludes this thesis by making recommendations on future improvements for this work.

## Chapter 2

### The JPEG Standard

The JPEG standard for compression of still images [13], outlines the processes which must be utilized to complete the JPEG compression or decompression. The standard is comprised of 3 primary transformations which are reversible. In this chapter, the methods and guidelines of the JPEG standard are reviewed, followed by a brief introduction to Field Programmable Gate Arrays (FPGAs) and embedded systems.

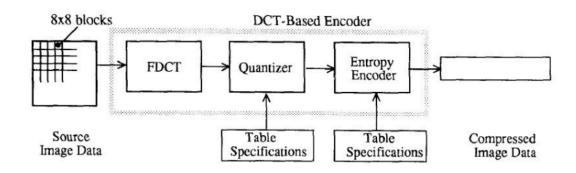

The JPEG compression process consists of the Forward Discrete Cosine Transform(FDCT), quantization of the DCT coefficients, and encoding the remaining values into binary representations as shown in Figure 2.1.

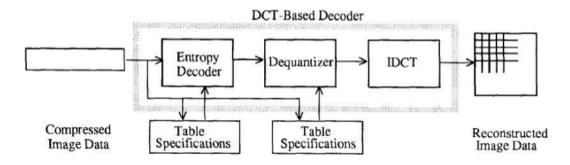

The JPEG decompression process consists of the same components as compres-

Figure 2.1: JPEG Compression Process [13]

Figure 2.2: JPEG Decompression Process [13]

sion in the reverse and inverse order. Decoding the binary values, dequantization, and the Inverse Discrete Cosine Transform(IDCT) to obtain the original image content as shown in Figure 2.2.

### 2.1 Discrete Cosine Transform

The Forward Discrete Cosine Transform(FDCT) is commonly referred to as the Discrete Cosine Transform (DCT). It is a mathematical transform that achieves a high

degree of compression with minimal losses. Equation 2.1 shows the 1 dimensional DCT (1D-DCT) of length 8. In JPEG image processing, Figure 2.1, the DCT is performed 2 dimensionally (2D-DCT) on 8x8 blocks as shown in Equation 2.2, in which the 1D-DCT is applied to each row, followed by each column.

$$F(k) = \alpha(k) \sum_{x=0}^{7} f(x) \cos\left(\frac{(2x+1)k\pi}{16}\right)$$

$$\alpha(k) = \sqrt{\frac{1}{8}} \text{ for } k = 0$$

$$\alpha(k) = \frac{1}{2} \text{ otherwise}$$

(2.1)

$$F(u,v) = \frac{1}{4}C(u)C(v)\sum_{x=0}^{7}\sum_{y=0}^{7}f(x,y)\cos(\frac{(2x+1)u\pi}{16})\cos(\frac{(2y+1)v\pi}{16})$$

$$C(u),C(v) = \frac{1}{\sqrt{2}} \text{ for } u,v = 0$$

$$C(u),C(v) = 1 \text{ otherwise}$$

(2.2)

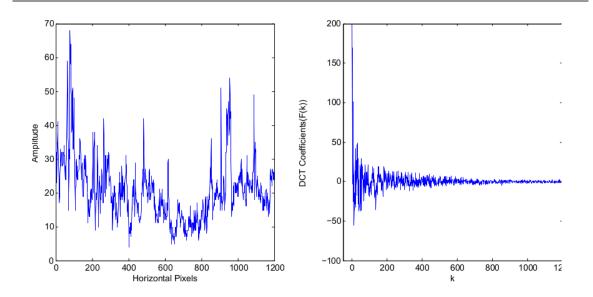

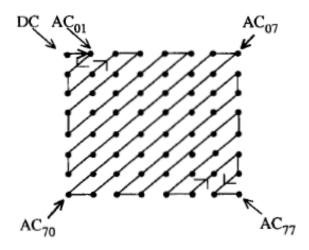

As a result the output of the 2D-DCT focuses its energy in the upper left corner of the 8x8 block, causing most of the 8x8 block to be zero. Figure 2.3 illustrates the energy compaction of one row of pixels. Encoding of the DCT block can then be optimized with the zig-zag pattern in Figure 2.4. Thus the trailing zeros can further assist in the high compression in JPEG images.

Figure 2.3: Energy Compaction of the DCT

Figure 2.4: Zig Zag order of a DCT block [13]

In the JPEG decompression, Figure 2.2, process the Inverse Discrete Cosine Transform (IDCT) is utilized to transform the dequantized Huffman coefficients back into useable image data. Equation 2.3 shows the 2D-IDCT, which is the inverse of the 2D-DCT. Similar to the DCT, the IDCT is a row-column transformation.

$$f(x,y) = \frac{1}{4} \sum_{u=0}^{7} \sum_{v=0}^{7} C(u)C(v)F(u,v)\cos(\frac{(2x+1)u\pi}{16})\cos(\frac{(2y+1)v\pi}{16})$$

$$C(u), C(v) = \frac{1}{\sqrt{2}} \text{ for } u, v = 0$$

$$C(u), C(v) = 1 \text{ otherwise}$$

(2.3)

### 2.2 Quantization

The quantization transformation shifts the output of the DCT down with integer rounded division to increase the compression shown in Equation 2.4. Smaller numbers use fewer bits which achieves higher compression. The factor at which the DCT coefficients are divided is determined by the quantization matrix. The quantization matrix is a statistically determined matrix where the higher valued coefficients at the top left of the matrix receive more scaling than the rest. This is due to the fact that the output of the DCT focuses its energy at this corner. In most JPEGs the quantization matrices are not statistically determined for that particular image, instead a generic set of tables based on the human vision system and trends from the DCT are used.

$$F^{Q}(u,v) = IntegerRound(\frac{F(u,v)}{Q(u,v)})$$

(2.4)

Dequantization is the reverse of quantization where the inputs to the IDCT are multiplied by the same quantization matrix to scale up the coefficients to the original intended value as shown in Equation 2.5.

$$F^{Q'}(u,v) = F^{Q}(u,v) * Q(u,v)$$

(2.5)

### 2.3 Huffman Encoding and Decoding

The final component of the JPEG compression/decompression process is entropy encoding/decoding. Encoding is the process of converting data from one format to another for the purposes of speed, security or space saving. The purpose of entropy encoding/decoding used in JPEG images is to compress the data without any losses. The most common type of JPEG image is baseline sequential, which use Huffman encoding/decoding [6]. Huffman encoding achieves lossless compression by allocating the most frequently used symbols with the fewest number of bits. The example data set in Table 2.1 illustrates how this process functions.

#### 2. THE JPEG STANDARD

| Symbol | Frequency | Code | Code Length |

|--------|-----------|------|-------------|

| А      | 24        | 0    | 1           |

| В      | 12        | 100  | 3           |

| С      | 10        | 101  | 3           |

| D      | 8         | 110  | 3           |

| Е      | 8         | 111  | 3           |

Table 2.1: Example Huffman data

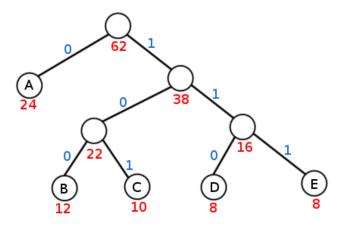

Based on the frequency of the symbol, a Huffman tree in Figure 2.5 is constructed. Most frequently used symbols are near the top of the tree, and the less frequent are at the bottom. A "move" down the right branch of the tree represents a "1", and a "move" down the left branch represents a "0"

Eg: Symbol 'C' is allocated the bits "101", while the most common symbol 'A' uses only 2 bits.

Figure 2.5: Huffman Tree

Using this method the Huffman encoding creates a much smaller encoded bit stream. Instead of building a Huffman tree each time, the JPEG image includes a set of tables giving the bit to number translations. For decoding a set of 4 tables are created. The tables are categorized by the colour channel, and frequency type: Luminance DC, Luminance AC, Chrominance DC, and Chrominance AC. The two Chrominance channels(Cb, Cr) share the AC and DC tables.

Huffman decoding is the reverse process of encoding. With the provided tables and compressed bitstream the values can be perfectly reconstructed during JPEG decompression. In many digital imaging devices such as digital cameras, the Huffman symbol calculations for that image are not calculated and a set of statistically determined tables are used instead. Utilizing the default set of tables allows for faster image compression, but can create a larger file size. In programs such as image editors, these settings can be changed to calculate the Huffman tables for a given image, which result in a smaller file size, but more computation time.

#### 2.4 Field Programmable Gate Array

A Field Programmable Gate Array (FPGA) is an integrated circuit designed to be configurable after manufacture. Using design tools, an FPGA can be programmed to generate the logic for virtually any hardware configuration. Unlike common CPU architectures, since FPGAs are effectively programmable hardware it has the capability to perform computations in parallel. This attribute greatly enhances speed over the conventional methodology.

Many embedded systems, specifically those in mobile devices consist of a complete system on chip (SOC). Additional hardware such as peripherals, are added either internally or externally. The use of FPGAs provide a flexible development platform without the cost of a conventional SOC design. This work utilizes an FPGA which models a SOC and its peripherals. The FPGA platform makes this work a suitable platform and allows testing in real time.

#### 2.4.1 Soft Processor

A soft processor is a microprocessor core that can be entirely implemented in using logic synthesis. For FPGAs a soft processor design can mimic the Reduced Instruction Set Computer(RISC) architectures found in many embedded systems. The MicroB- laze processor [1] used in this work is a soft processor designed for Xilinx FPGAs. The MicroBlaze is implemented entirely in the general-purpose memory and logic fabric of Xilinx FPGAs.

### 2.5 Summary

This chapter discussed the methods outlined in the JPEG standard used to compress and decompress JPEG image data, as well as gave an introduction to FPGAs in embedded systems.

Due to the fact that the JPEG is highly complex, this research focuses on optimizing individual components of the JPEG decompression process rather than the entire algorithm. Utilizing the configurability of FPGAs a hardware architecture can be designed to improve the software functions. This hybrid software-hardware architecture will be a beneficial replacement for the conventional software only approach.

### Chapter 3

# Existing Work in Hardware JPEG Algorithms

The JPEG ISO standard, described in Chapter 2, outlines the transforms that are needed in order to compress and decompress JPEG images. It does not describe the specific algorithms that need to be used to achieve the end product. There hasn't been much publicized work on the complete decompression of a JPEG, but there has been some work in the individual algorithms used to decompress a JPEG image. This chapter will begin with an introduction to libjpeg, the most commonly used JPEG software library used in mobile systems, followed by the state of the art in the algorithms applicable to JPEG images, as well as their advantages and disadvantages.

### 3.1 libjpeg

There has been much work done in the software compression and decompression of JPEG images. In 1986, shortly after the JPEG standard was created a group called the Independent JPEG Group [7] (IJG) created the free open-source C library called "libjpeg". The library is multi-platform configurable, and follows all of the JPEG ISO standards, and as such libjpeg is credited by the JPEG group to being a reliable source to use in software applications. Due to its longevity and popularity libjpeg has found itself as the primary JPEG encoder/decoder in mobile device applications, as well as desktop applications. For this reason, this work uses the libjpeg ported for the Xilinx MicroBlaze architecture as the starting point and control for testing.

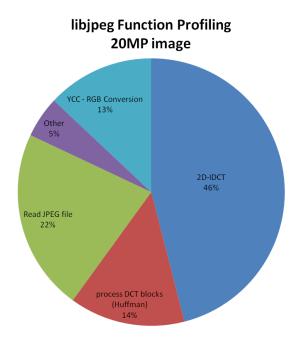

Chapter 2 outlined the three primary steps used in compression and decompression, however these algorithms are not necessarily the most costly functions in the digital domain. Therefore, the libjpeg library was profiled (a process of timing the functions in software to find where the most significant bottlenecks reside) and examined.

To acquire an approximate function benchmark a 20 MP image was profiled on a desktop PC running a Pentium-4 3GHz processor, 32-bit GNU/Linux operating system, and 2GB of RAM. The image was profiled 100 times and averaged to achieve statistical accuracy. Figure 3.1 displays the profiling results.

The profiling results show that the most expensive functions are the IDCT, the

3. EXISTING WORK IN HARDWARE JPEG ALGORITHMS

Figure 3.1: Desktop JPEG Profiling

colour space conversion, and the Huffman transform with 46%, 13%, and 14% respectively. The focus of this work centres on optimizing the IDCT and colour conversion to enhance the JPEG decompression time.

### 3.2 Inverse Discrete Cosine Transform (IDCT)

First introduced in Section 2.1 the IDCT is the Inverse of the Discrete Cosine Transform which used to transform the output of raw dequantized Huffman coefficients. For JPEG images the pixels are split into 8x8 blocks prior to applying the DCT. The 2D-IDCT consists of 16 1D-IDCTs over the 8 rows and 8 columns of the DCT blocks. Equation 3.1 demonstrates the formal definition of the 2D-IDCT as it applies to the 8x8 JPEG blocks.

$$f(x,y) = \frac{1}{4} \sum_{u=0}^{7} \sum_{v=0}^{7} C(u)C(v)F(u,v)\cos(\frac{(2x+1)u\pi}{16})\cos(\frac{(2y+1)v\pi}{16})$$

$$C(u), C(v) = \frac{1}{\sqrt{2}} \text{ for } u, v = 0$$

$$C(u), C(v) = 1 \text{ otherwise}$$

(3.1)

The traditional IDCT in equation 3.1 shows the iterative multiplication process.

#### 3.2.1 Distributed Arithmetic DCT

The Distributed Arithmetic DCT (DA-DCT) proposed by Pan [10] attempts to reduce the complexity of the DCT by exploiting the binary representations of the 2D-DCT matrix. The number of additions in this transform are reduced by a factor of 22. On average 1 multiplication, 40 additions, and 16 binary shifts are required for each DCT coefficient. Equations 3.2 - 3.6 illustrate how the transform is performed.

$$Y = A * X = \begin{pmatrix} A_1 & A_2 & \cdots & A_L \end{pmatrix} \begin{pmatrix} X_1 \\ X_2 \\ \vdots \\ X_L \end{pmatrix}$$

(3.2)

$$A_k = -A_k^M 2^M + \sum_{i=N}^{M-1} A_k^i 2^i$$

(3.3)

where  $A_k^i$  is 0 or 1

$$Y = \underbrace{2^{N} * \left(-2^{M-N} \ 2^{M-N-1} \ \cdots \ 2 \ 1\right)}_{S} * \underbrace{\begin{pmatrix} A_{1}^{M} & A_{2}^{M} \ \cdots \ A_{L}^{M} \\ A_{1}^{M-1} & A_{2}^{M-1} \ \cdots \ A_{L}^{M-1} \\ \vdots \ \vdots \ \cdots \ \vdots \\ A_{1}^{N} & A_{2}^{N} \ \cdots \ A_{L}^{N} \end{pmatrix}}_{B} * \underbrace{\begin{pmatrix} X_{1} \\ X_{2} \\ \vdots \\ X_{L} \end{pmatrix}}_{X}$$

Let

$$C = B * X = \begin{pmatrix} C_M & C_{M-1} & \cdots & C_N \end{pmatrix}^T$$

(3.5)

$$Y = S * C \tag{3.6}$$

The multiplicative complexity is significantly reduced at the cost of additions and shift operations, however; the DA-DCT word length must be  $\geq 9$  in order to be considered indistinguishable from floating point, and it must be  $\geq 16$  to be numerically equivalent.

#### 3.2.2 Loeffler Algorithm

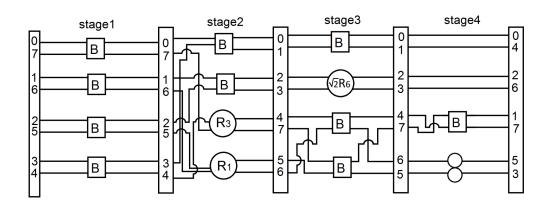

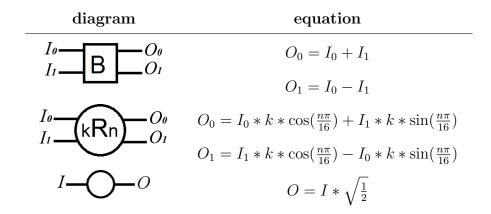

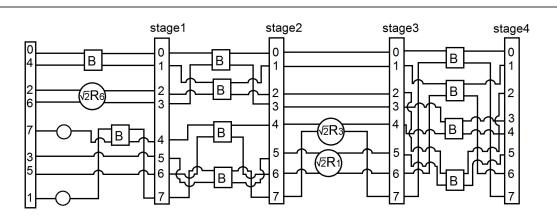

By far the most popular algorithm for the DCT is the The Loeffler Algorithm [8] used in [12]. The Loeffler Algorithm takes a similar approach to the DCT as the Fast Fourier Transform (FFT) takes to the Discrete Fourier Transform(DFT). The Algorithm is mapped to a set of "Butterfly" and "Rotator" blocks. It reduces the DCT down to 29 additions and 11 multiplications, shown in Figure 3.2 and Table 3.1.

3. EXISTING WORK IN HARDWARE JPEG ALGORITHMS

Figure 3.2: Loeffler Algorithm for 1D DCT

where

Table 3.1: Butterfly[B], Rotator[R], and constant Multiplication Blocks for Loeffler's Algorithm

Due to the reversibility of the DCT, the IDCT Loeffler algorithm is mapped out as in Figure 3.3.

3. EXISTING WORK IN HARDWARE JPEG ALGORITHMS

Figure 3.3: Loeffler Algorithm for 1D IDCT

Since the complexity of the algorithm significantly reduces the complexity of the IDCT to fewer multiplications and additions, it makes this algorithm the most suitable method for the JPEG process. Consequently, this is the current IDCT algorithm implemented in the libjpeg library.

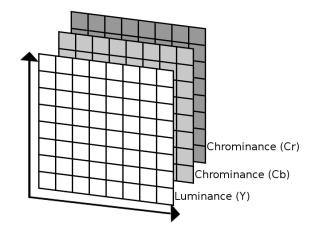

### 3.3 YCC to RGB Colour Space Conversion

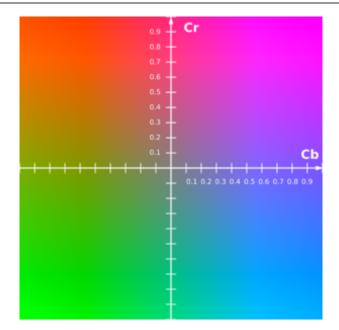

The colour scheme of the JPEG standard is based on the Luminance and Chrominance channels (YCC). The YCC colour scheme has minimal redundancy, unlike RGB, which makes it suitable for JPEG images. "Y" is the Luminance component and "Cb" and "Cr" are the blue-difference, and red-difference chroma components. Figure 3.4 illustrates the chroma colour plane at a constant luma value.

Most displays use the Red-Green-Blue (RGB) colour scheme, so conversion between the two colour schemes is necessary. The colour space conversion is a simple process, Equation 3.7, but is an intensive operation due to the fact that each pixel

3. EXISTING WORK IN HARDWARE JPEG ALGORITHMS

Figure 3.4: Cb-Cr colour plane at a constant luma value

has 3 colour channels, which have 4 multiplications and 4 additions. For example, a 20MP image has 60 million individual colour channels, which possibly has 80 million multiplications, and 80 million additions.

$$R = Y + 1.402 * (Cr - 128) \tag{3.7a}$$

$$B = Y + 1.772 * (Cb - 128) \tag{3.7b}$$

$$G = Y - 0.34414 * (Cb - 128) - 0.71414 * (Cr - 128)$$

(3.7c)

#### 3.3.1 Look Up Table

The Look-up Table (LUT) method is one of the most efficient methods, especially for embedded systems, for computing a large number of calculations for limited multiplications. Since the colour conversion utilizes constant multiplications, and the chrominance colour channels are limited to 256 values many systems pre-compute every possible value. These values are stored in a table to be referenced when needed. Typical YCbCr LUT implementation calculates the 4 base multiplications, Cr \* 1.402, Cr \* 0.71414, Cb \* 1.772 and Cb \* 0.34414, and stores the values in tables. When calculation is needed the Cr and Cb values are used as indices in these tables, and additions are the only operation to calculate.

|       | Cr-Red       | Cr-Green       | Cb-Blue      | Cb-Green       |

|-------|--------------|----------------|--------------|----------------|

| index | (Cr * 1.402) | (Cr * 0.71414) | (Cb * 1.772) | (Cb * 0.34414) |

| 1     | 1.402        | 0.714          | 1.772        | 0.344          |

| 2     | 2.804        | 1.428          | 3.544        | 0.688          |

| :     | :            | :              | :            | :              |

| 255   | 357.51       | 182.106        | 451.86       | 87.756         |

Table 3.2: Colour Space Look Up Table example

libjpeg uses LUTs for the YCC to RGB conversion. The LUTs are computed once and stored upon startup. This allows a table look up and addition to calculate the colour conversion. The advantage of this method is speed, but the disadvantage is accuracy. Indexing and accessing large tables occupies time, but the amount of time isn't necessarily consistent. Data caching problems, such as cache misses can arise with these large data sets. Most CPU caches use an n-way associative cache, which can cause replacement issues with using many table lookups, found in JPEG colour conversion. This can result in more cache misses and slower time, which is not ideal for this work.

#### 3.3.2 Shift and Add

To reduce on the cumbersome floating point multiplications needed for colour space conversion Yang et al [14] proposed a Fast Algorithm for YCbCr to RGB. On Digital Signal Processors (DSPs), floating point multiplications, multiplications by a decimal number, are simplified with multiple shift and add operations. The more unique the decimal value of the multiplicand, the more shifts and adds are required, consuming processor resources and time. Colour conversion algorithms contain unique decimal values, and are typically carried out thousands to millions of times. Yang et al proposed to reduce the complexity of the multiplications in colour conversion with minimal quantification error while maintaining the image quality.

Their algorithm selects the most significant fixed-point shift and add operations to take place of the floating point multiplication. As such, the processor has fewer operations to compute and thus time consumption is reduced.

$$R = Y + Cr + Cr \gg 2 + Cr \gg 3 + Cr \gg 5$$

$$(3.8a)$$

$$B = Y + Cb \gg 1 + Cb \gg 2 + Cb \gg 6 \tag{3.8b}$$

$$G = Y - (Cb \gg 2 + Cb \gg 4 + Cb \gg 5) - (Cr \gg 1 + Cr \gg 3 + Cr \gg 4 + Cr \gg 5) \quad (3.8c)$$

The YCC to RGB conversion in Equation 3.8 proposed were tested with video sequences comparing against floating point method. The maximum error observed was 0.02% of all the images in the video. This method is ideal for YCC to RGB approximation in JPEG applications, but the error in the colour may increase when data propagates through the DCT.

#### 3.3.3 Integer Based Transform

Pei et al [11] proposed a Reversible Integer Color Transform With Bit-Constraints to optimize colour transforms. This method looks at redesigning the input coefficients to floating point calculations completely. As a result the colour conversion transform will be lossless, and can be implemented with only fixed-point operations.

The transformation process relies on the basis that most colour transformations consist of 3x3 matrices. YCbCr, RGB, Karhunen-Loeve Average (KLA), and Intensity Hue Saturation (IHS) are all examples of 3x3 matrix colour schemes. The process to generate the integer based transform involves normalizing the input matrix and extracting the binary valued matrix which depends on 8 fixed point-values that approximate floating-point values. After the transformation is generated, using the integer transform in forward and reverse applications becomes a simple set of matrix operations.

Pei et al, tested this transform for RGB to YCbCr achieving 0.288% normalized root mean square error. The advantage of this method eliminates all floating-point operations, but the pre-computation and encoding of the colours this way is necessary, and not applicable for JPEG applications.

### 3.4 Summary

This chapter presented several existing techniques that were developed to optimize and accelerate the individual components of the JPEG process. As discussed some of these techniques are more applicable to JPEG decompression than others. The Loeffler algorithm, colour conversion LUTs, and the shift and add methods for YCC to RGB conversion are the most advantageous procedures for JPEG implementation.

In the work presented herein, a novel hybrid architecture between software and hardware was designed to provide hardware acceleration of large JPEG images.

# Chapter 4

# Proposed Hybrid Architecture

This chapter illustrates the proposed hybrid software-hardware architecture used to accelerate the time it takes to decompress a JPEG image with libjpeg. This hybrid approach is applied to the IDCT and the colour conversion components of the JPEG decompression scheme. This chapter describes the architecture and the reasoning in each domain; hardware and software.

In the proposed design, the IDCT and colour conversion were implemented in hardware to aid the software library in its most expensive operations. This novel design incorporates the advantages of using parallelism in hardware along with a few software memory techniques to expedite the JPEG decompression time.

# 4.1 Development Board Specs

In order to emulate the conditions of a real world mobile device this work used an embedded GNU/Linux variant on an FPGA. The FPGA development board used was a Xilinx XUPV5-LX110T development board [3], which has the following specifications:

- Xilinx Vertex<sup>®</sup>-5 XC5VLX110T FPGA

- 64-bit wide 256MB DDR2 small outline DIMM(SODIMM) module

- On-board 32-bit ZBT synchronous SRAM and Intel P30 StrataFlash

- 10/100/1000 tri-speed Ethernet PHY

- Programmable system clock generator

- RS-232 port

- JTAG programming interface

For this proposed architecture the development board is programmed with a 125 MHz MicroBlaze soft-core processor. The operating system is the GNU/Linux variant, Petalinux [2], which is targeted at FPGA-based embedded MicroBlaze and PowerPC systems. Petalinux allows C /C++ application development and debugging using its provided compilers. Included in the Petalinux kernel is a host of standard libraries and applications, one of which is a recent version of libjpeg.

## 4.2 Hardware Software Communication

The desired goal of the hybrid architecture is to optimize software by moving the expensive operations to dedicated hardware, but the communication link between hardware and software is a vital component in and of itself. There are a few methods available for interaction between the software and the hardware, each with their own pros and cons.

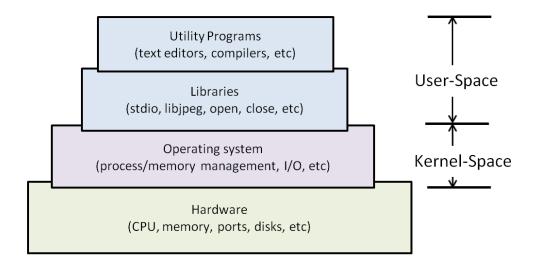

With respect to memory in a memory managed Linux kernel, the privileges can be envisioned as a set of layers as in Figure 4.1. The top most layer is the user-space. This layer is what the typical user interacts with, here the compiled applications are executed, and present the input and output. In this layer there exists a dynamic amount of memory available, which are virtually indexed by the kernel. This protection prevents the user from corrupting any valuable memory locations. The next layer down is the kernel. The kernel is the memory limited control centre. Device drivers exist in the kernel which communicate between the user-space and kernel, and between kernel and the physical memory or hardware. The bottom-most layer is the hardware. The hardware is the physical aspect such as DDR2 RAM, hardware registers, ports, and logic elements.

The kernel protection layer becomes an added bottleneck for the hardware acceleration of software, especially for multiple transactions. As a result the careful consideration of this communication is taken into account. There are two primary methods of inter-system interaction; through DDR2 RAM, or through hardware mapped registers, each of which utilize a memory controller driver found in "/dev/mem".

Figure 4.1: Layers of a GNU/Linux based embedded system

#### 4.2.1 Communication through DDR2 RAM

The first method for software-hardware communication can be done through the system's available DDR2 RAM. The user-space application requests access to a sector of RAM from the memory driver, and receives a pointer that can be used to read and write to the RAM.

On the hardware side, the logic must provide the control signals at the correct timing to read and write to the RAM module. The control signals must be accurate to transmit the data correctly. Unlike software, the hardware has full control over how much data can be transmitted in one transaction. This advantage is through what is called Burst reading and writing. For this transaction a multi-port memory controller(MPMC) is available to the MicroBlaze processor. The MPMC supports Burst reads and writes up to 32 32-bit words per transaction. This greatly speeds up memory access time. Utilizing Burst reading and writing in a design is beneficial, however there is too much data copying, which is too costly. Data is copied from software to RAM, from RAM to hardware logic elements to operate on, and then back.

#### 4.2.2 Communication through Hardware Registers

The alternative method for communication is directly through the hardwares memory mapped registers, eliminating the need for additional RAM accesses. For software, the data transfer is similar to the process with RAM. The software reads and writes to a pointer allocated to it by the /dev/mem driver.

On the hardware side, the register which has been written to by software can be directly operated on without needing any additional copying. Additionally, the hardware has the ability to react immediately after a register has been written. This provides an "interrupt on change" type of interface eliminating the need for a "start" command.

Utilizing direct communication through registers is limited by the resources and the property that these software accessible registers cannot be bidirectional, however there is far less data copying than communication through RAM.

There are pros and cons for each method, but direct communication through registers provides faster throughput. The register only process is simpler to use for the hardware, faster, less copying of data, and it allows for concurrent processing between software and hardware. Concurrent processing is achieved when the software is writing to register "n" while the hardware operates on registers "n-1", "n-2", ..., etc.

# 4.3 Hardware Design

In this work the software layout must be considered when designing the hardware for the 2D-IDCT and colour conversion. The most optimal hardware designs relieve as much processing from the Software as possible. The input and output data structures on the software level must remain the same, and any data manipulation must be done on the hardware level.

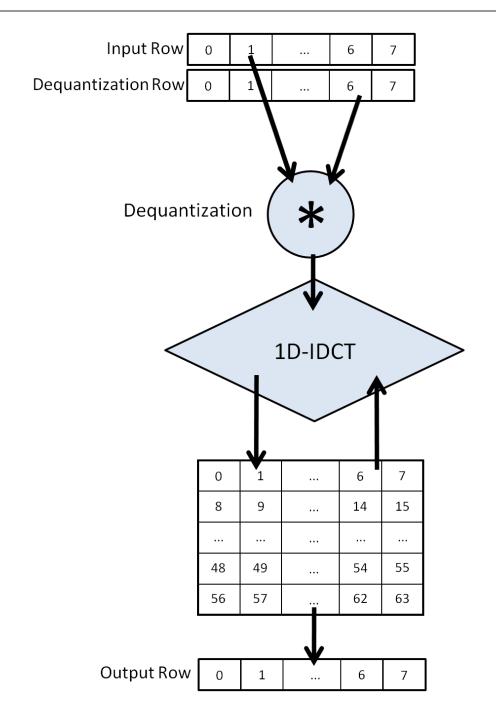

#### 4.3.1 IDCT

The 2D-IDCT hardware design relieves the software from three operations found in libjpeg; dequantization, the 2D-IDCT, and range-limiting. Dequantization is the multiplication of the IDCT input coefficients by the quantization matrix, scaling up the coefficients back to the original post-DCT value. After dequantization, the 2D-IDCT is carried out. As mentioned in Chapter 2 and 3, the 2D-IDCT transform is separable into its rows and columns. In the JPEG architecture DCT blocks of 8x8 are used. Eight row 1D-IDCTs followed by eight column 1D-IDCTs are needed to complete a full 2D-IDCT. The last step, range-limiting is a simple process to suppress out of range corrupt values.

The separability of the rows and columns allows the hardware design of the 2D-IDCT to accept the input matrices, IDCT and quantization matrix, coefficients rowby-row. Upon receipt of an input and quantization row, the hardware IDCT module immediately computes the simple multiplication for the dequantization. The dequantized values are the input to the row 1D-IDCTs. The most efficient IDCT algorithm to date is the modified Loefler Algorithm [8], and is the most suitable for hardware implementation. Since this algorithm not only uses fewer multiplications than the standard IDCT algorithm, the multiplications are also in parallel which is ideal for hardware implementation. Natively libjpeg uses integer based multiplication for its IDCT. Floating point is possible, but is costly. To keep the accuracy found with floating point the integer based IDCT shifts all of its multiplication factors up, performs the calculation, and shifts the product back down. This process truncates its less significant digits, but retains accuracy and speed in integer form. The 1D-IDCT implementation in this hardware design utilizes the shift and multiply technique carried through the entire 1D-IDCT.

Once a complete row has been written by software to the hardware registers, the 1D-IDCTs compute the row IDCTs. After all of the 8 rows have been written to the hardware registers, the hardware module transposes the rows and computes the 8 column IDCTs for a full 2D-IDCT. The final step is range limiting the output. Range limiting shifts and truncates the output to an 8 bit range of 0 to 255, and is the data type libjpeg uses for these values. Data corruption in JPEG compression is possible, so range limiting prevents out of range pixel values from wrapping around to an invalid number. The design layout is illustrated in Figure 4.2.

Figure 4.2: Dequantization and 2D-IDCT Hardware Design

#### 4.3.2 Colour Conversion

The colour conversion hardware design in this work relieves the software from three operations found in libjpeg; YCC to RGB table pre-computation, YCC to RGB conversion, and range limiting.

The majority of digital displays use the RGB colour scheme. As mentioned in Chapter 3, libjpeg uses the YCC colour scheme to optimize storage capacity. The conversion from YCC to RGB libjpeg utilizes a set of lookup tables for the Chrominance components; Cr-red, Cb-blue, Cr-green, Cb-green, of each colour channel. LUTs are the most efficient method, but the access speed can be inconsistent due to the possibility of cache misses. As the data set increases, the probability of a cache miss increases as well. As a result, this is not a suitable method for this work.

The hardware design of the colour conversion in this work performs a straight YCC to RGB calculation, eliminating the need for pre-computed table. This is possible because the number of cycles hardware uses to perform a multiplication by the Cr-red, Cb-blue, Cr-green, and Cb-green constants is fewer than the number of cycles used in software to reference the look up tables. The multiplications by the constants in Table 4.1 are performed using fixed point multiplication while retaining the accuracy of floating point multiplication with decimal truncation.

#### 4. PROPOSED HYBRID ARCHITECTURE

| Colour Channel | Decimal Value | Binary Representation |

|----------------|---------------|-----------------------|

| Cr-red         | 1.402         | 10110011011101001     |

| Cr-green       | 0.71414       | 01011011011010010     |

| Cb-green       | 0.34414       | 00101100000011010     |

| Cb-blue        | 1.772         | 11100010110100010     |

Table 4.1: YCC - RGB constants

The last optimization the hardware colour conversion makes is multi pixel conversion. Since each colour channel, Y, Cb, Cr, R, G, and B, are 8 bits each and the software accessible registers are 32 bits the hardware converts 4 pixels at once, filling each register with 4 colour channels. The RGB output range-limited to 8 bit values of 0 to 255 and is rearranged to match the order in libjpeg as shown in Figure 4.3.

Figure 4.3: YCC to RGB Hardware Design

# 4.4 Software Design

In this work, libjpeg was modified to utilize the hardware components. Since most of the workload is being transferred into the hardware domain, all data copying was carefully thought out and minimized. Minimizations are performed by maintaining the layout of arrays, pointer manipulation and word size consistency.

### 4.4.1 IDCT

Libjpeg computes the IDCT using the Modified Loeffler algorithm. Pointers to the input coefficients are passed to the function along with a reference to the quantization

matrix. The function dequantizes the coefficients by multiplication, performs the IDCT, and range limits the output to 8 bits. These three processes were moved to hardware.

For this architecture the software IDCT component's functions are limited to writing rows to the hardware registers, and reading rows from the registers. The software writes in the quantization matrix and IDCT coefficients into the hardware registers row by row. The same registers are used because the hardware can manipulate the data faster than the software can change it. To maximize the data transfer from software to hardware the rows are moved into the fewest amount of 32 bit registers as possible. Casting the rows into integer pointers permits using 2 hardware register for 8 entries of the IDCT input, and 4 registers for 8 entries of the quantization matrix. After computation in hardware, the software reads in the output registers row by row from 2 hardware registers. Figure 4.4 illustrates the data compaction.

Figure 4.4: IDCT array-register data compaction

#### 4.4.2 Colour Conversion

Upon starting, libjpeg calculates all the possible chrominance combinations for the conversion from YCC to RGB colour space. These calculations are stored in 4 tables: Cr-red, Cb-blue, Cr-green, Cb-green. When called, the YCC-RGB colour conversion function gets passed a 3 dimensional array which represents the deconstructed image in the YCC colour channels. Figure 4.5 shows a visual representation of this image. the x-y coordinates of the image represent the x-y coordinates of the source image, where each layer represents the different colour channels of each pixel.

Figure 4.5: 3D image array

Each array of colour channels are passed in as 8 bit unsigned values. Natively, 32bit CPU architectures function optimally with 32-bit words, additionally the software accessible hardware registers are 32 bits. As a result in this architecture for the colour conversion, a technique is used to cast a 32 bit integer pointer to the array of 8 bit bytes. This allows the software to access 4 values of Y, Cb, or Cr with one variable, and one write to the hardware register. Figure 4.6 illustrates this technique.

Figure 4.6: Colour Conversion array-register data compaction

Similarly, after conversion the RGB registers are read in the same manner. This data compaction utilizes 3 registers for input, and 3 registers for output to transmit 24 colour channels. Using this technique the software loops through all the pixels in the image, in 4 pixel increments, writing YCC and reading RGB without any need for control registers. No control registers are required, due to the fact that this conversion is very simple, and the hardware computes the conversion on 4 pixels before the software can read it.

## 4.5 Summary

This chapter presents the techniques, and structure of the proposed software-hardware hybrid architecture for the decompression of JPEG images. The JPEG software library is accelerated with hardware components for the 2D-IDCT and YCC to RGB colour conversion. Huffman decoding, the next logical step in JPEG decompression acceleration, is outlined in Appendix E.

In the following chapter, this work is timed, and tested. The results show how fast the decompression time has increased as well as the accuracy of the decompression with respect to a software only decompressed image.

# Chapter 5

# Results

This chapter presents the testing setup and procedures used to test the proposed hardware accelerated components of libjpeg, as well as the timing analysis. The conclusions that may be derived from the results are described, and then compared to the widely used software library, libjpeg.

## 5.1 Testing Setup and Procedure

Testing for this work was carried out on the Xilinx XUPV5-LX110T FPGA development board. The board was loaded with the GNU/Linux variant, Petalinux. The base design, hardware and software only included the most basic and crucial components. The hardware designed for the system includes the IDCT and colour conversion modules. These modules are linked into the MicroBlaze design, and accessed through input and output registers.

Petalinux includes the libjpeg source files which can be cross-compiled to run on the target. This library is the base in which this work is built on. The Petalinux kernel was configured for the Xilinx target hardware, MicroBlaze processor, and built for a Memory Management Unit (MMU) system. Once the Hardware is downloaded to the board, it is loaded with the Petalinux image. User built binaries can be loaded into the image, but for the purposes of this work the binaries and test JPEG images were executed through the network due to their size. Utilizing the network permits for faster development, testing, and eliminates the need to build the large test JPEG images from being built into the Petalinux flash image.

For this work, the necessary libjpeg files were modified and cross-compiled into a static library. Shared library compilation is possible, however it requires the Petalinux to be rebuilt and downloaded to the target which is not a productive solution. Upon generation of the static JPEG libray the main program files are cross-compiled with the library into a binary suitable for the target.

On the FPGA target, the binary is run by providing the path to JPEG image. Timing of the images is a difficult task. The work done in the areas of timing and profiling software applications on a soft processor, is underdeveloped and not readily available. As a result, this work depends on using the Petalinux "time" function. The time function provides the real, user, and system time execution of a binary with a resolution of 10 milliseconds. This work uses the user time which is presented in 5.2.

To verify the decompression of the images were accurate, a subjective test and objective test were performed. After decompression, the raw RGB data was written to the system's frame-buffer, which is displayed on an attached monitor. Visual, subjective inspection for artifacts, and similarity to the original was carried out on the image. Objective verification was implemented by comparing the decompressed and converted raw RGB values output from this work compared to the software only output. The verification results are presented in 5.3.

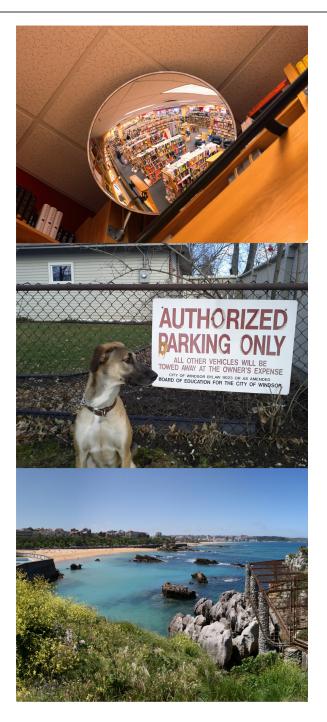

Not all images are the same, but will posses the same decompression scheme. For this work, 3 separate images with varying image metrics at 3 different pixel densities, 5 MP, 10 MP, and 20 MP were tested. To maintain statistical accuracy each image was tested 100 times and averaged using the scripts in Appendix B and a spreadsheet program. The three images, found in Appendix A, hereby referred to as the *bookstore, dog, and beach* images were the test images used in this work. The images began at an approximate 20MP, and were scaled down to 10MP, and 5MP to observe the versatility of this work. Each image was saved with no colour sub-sampling, and no Huffman optimizations to emulate the ideal settings observed in digital cameras. Table 5.1 gives the dimensional details of each image used.

#### 5. RESULTS

| Image     | Width(px) | Height(px) | Size(MP) | Size(MB) |

|-----------|-----------|------------|----------|----------|

|           | 2686      | 1862       | 5.0      | 1.5      |

| bookstore | 3799      | 2634       | 10.0     | 2.6      |

|           | 5400      | 3744       | 20.2     | 4.1      |

|           | 2560      | 1920       | 4.9      | 1.8      |

| dog       | 3653      | 2740       | 10.01    | 3        |

|           | 5164      | 3873       | 20.0     | 4.8      |

|           | 2503      | 1998       | 5.0      | 1.8      |

| beach     | 3540      | 2826       | 10.0     | 3.1      |

|           | 5040      | 4024       | 20.2     | 4.9      |

Table 5.1: Test Image Dimensions

# 5.2 Timing Results

After each image was tested and timed, it was compared to the software only benchmark. Comparing to the benchmark, the timing improvement ( $\Delta t$ ), and percentage of the benchmark was calculated (% SW) as shown in Tables 5.2, 5.3, and 5.4.

% of Software =

$$\frac{\text{Hardware time}(s)}{\text{Software time}(s)} * 100$$

(5.1)

5. RESULTS

|                  |         | 5MP           |       |                          | 10MP          |       |                          | 20MP          |       |

|------------------|---------|---------------|-------|--------------------------|---------------|-------|--------------------------|---------------|-------|

|                  | Time(s) | $\Delta t(s)$ | % SW  | $\operatorname{Time}(s)$ | $\Delta t(s)$ | % SW  | $\operatorname{Time}(s)$ | $\Delta t(s)$ | % SW  |

| Software Only    | 49.18   | -             | -     | 96.71                    | -             | -     | 184.54                   | -             | -     |

| Colour HW        | 46.66   | 2.52          | 94.87 | 91.87                    | 4.84          | 94.99 | 174.08                   | 10.46         | 94.33 |

| IDCT HW          | 35.97   | 13.21         | 73.14 | 71.16                    | 25.55         | 73.58 | 139.78                   | 44.76         | 75.75 |

| IDCT + Colour HW | 33.28   | 15.91         | 67.66 | 65.73                    | 30.98         | 67.97 | 128.72                   | 55.82         | 69.75 |

Table 5.2: Bookstore Image Results

| 5MP              |         |               | 10MP  |                          |               | 20MP  |         |               |       |

|------------------|---------|---------------|-------|--------------------------|---------------|-------|---------|---------------|-------|

|                  | Time(s) | $\Delta t(s)$ | % SW  | $\operatorname{Time}(s)$ | $\Delta t(s)$ | % SW  | Time(s) | $\Delta t(s)$ | % SW  |

| Software Only    | 48.44   | -             | -     | 95.88                    | -             | -     | 188.86  | -             | -     |

| Colour HW        | 45.84   | 2.60          | 94.62 | 90.64                    | 5.24          | 94.54 | 176.91  | 11.95         | 93.67 |

| IDCT HW          | 33.95   | 14.49         | 70.08 | 71.16                    | 24.72         | 74.22 | 141.29  | 47.57         | 74.81 |

| IDCT + Colour HW | 32.93   | 15.52         | 67.97 | 65.63                    | 30.25         | 68.45 | 130.31  | 58.55         | 69    |

Table 5.3: Dog Image Results

|                  |         | 5MP           |       |         | 10MP          |       |         | 20MP          |       |

|------------------|---------|---------------|-------|---------|---------------|-------|---------|---------------|-------|

|                  | Time(s) | $\Delta t(s)$ | % SW  | Time(s) | $\Delta t(s)$ | % SW  | Time(s) | $\Delta t(s)$ | % SW  |

| Software Only    | 49.73   | -             | -     | 96.30   | -             | -     | 189.40  | -             | -     |

| Colour HW        | 46.85   | 2.87          | 94.22 | 91.72   | 4.58          | 95.24 | 177.02  | 12.37         | 93.47 |

| IDCT HW          | 36.84   | 12.88         | 74.1  | 71.58   | 24.73         | 74.33 | 142.21  | 47.18         | 75.09 |

| IDCT + Colour HW | 33.89   | 15.83         | 68.16 | 66.22   | 30.08         | 68.76 | 131.19  | 58.21         | 69.27 |

Table 5.4: Beach Image Results

Tables 5.2, 5.3, and 5.4 illustrate that the hardware accelerated colour conversion provided an approximate 4% increase in timing, hardware accelerated 2D-IDCT provided an approximate 25% increase in timing, and the combined hardware components provided an approximate 31% increase in the timing over the software only approach for decompression. Furthermore, the individual as well as combined hardware acceleration of these components exhibits a near linear timing improvement as image size grows as shown in Figure 5.1 and 5.2.

Figure 5.1: Image Decompression Timing

Figure 5.2: Image Decompression Timing

#### 5.2.1 Hardware Timing

The primary source of improvement in this work is due to the speed of the hardware modules. Hardware has little to no overhead. Analyzing the hardware performance without the software overhead; the 2D-IDCT Hardware takes 186 clocks to achieve a full 8x8 transformation, and the YCC to RGB colour conversion takes 9 clocks to transform 4 pixels with 3 colour components. At 125 MHz, the IDCT takes 1.44  $\mu$ s for one 8x8 block, and the colour conversion transforms 4 pixels in 7 2ns. Applying these calculations to each 20 MP test image can be found in Table 5.5.

| Image     | # 8x8 Blocks | # pixels/4 | IDCT HW(s) | Colour HW(s) | % HW Time |

|-----------|--------------|------------|------------|--------------|-----------|

| bookstore | 947700       | 15163200   | 1.36       | 1.09         | 1.90      |

| dog       | 937509       | 15000129   | 1.35       | 1.08         | 1.86      |

| beach     | 950670       | 15210720   | 1.37       | 1.10         | 1.88      |

Table 5.5: Hardware Only Timing per test image

# 5.3 Image Verification

Since both of the IDCT and Colour Conversion algorithms use fixed point arithmetic, some error will be introduced. This work aims to improve the timing of the entire JPEG decompression process while maintaining a valid output with minimal error. As a result the output of the image needs to be verified. The accuracy for this work was verified using subjective and objective comparisons against the original, software only, decompression.

For the subjective verification, the images were written to the system's frame buffer, a reserved region of memory that is processed with a video controller to be displayed on an attached monitor. The displayed images were then visually inspected for any image artifacts, and any differences in colour, shade, and orientation compared to the original.

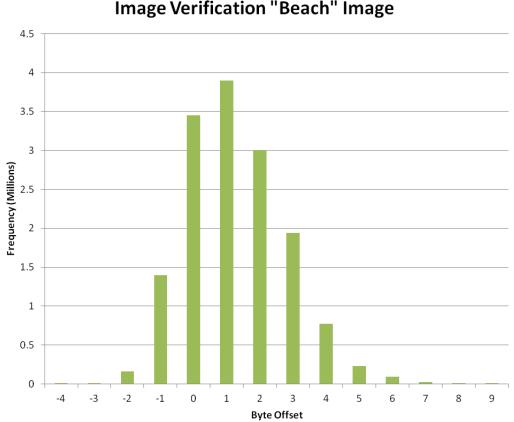

For the objective verification the 5MP images were tested. The raw RGB bytes from the software only and software-hardware methods were saved to files. The approximate 15 million bytes of each image were then compared side by side to find the offsets. The byte offsets were calculated and plotted in the histograms in Figures 5.3, 5.4, and 5.5.

# Image Verification "Bookstore" Image

Figure 5.3: Bookstore image byte offset histogram

Image Verification "Dog" Image

Figure 5.4: Dog image byte offset histogram

Image Verification "Beach" Image

Figure 5.5: beach image byte offset histogram

A zero byte offset is ideal, meaning the decompressed version matches the software decompressed image perfectly. In the Figures 5.3, 5.4, and 5.5 the highest frequencies occur at the lowest offsets, and lowest frequencies occur at the highest offsets. Interestingly the highest frequency peaks exist at the offset of 1, likely from a rounding that appears during integer truncation. The worst case scenario in all cases is a byte offset of 9 at an extremely low frequency of 111. Quantifying the image data of the histograms can be performed using equations 5.2 and 5.3, which will find the similarity between the software decompressed image versus the proposed method.

Byte Accuracy (%) =

$$\left(1 - \left|\frac{\text{byte offset}}{255}\right|\right) * 100$$

(5.2)

Image Accuracy(%) =

$$\frac{\sum_{i=N}^{M} \left(1 - \left|\frac{\text{byte offset}_{i}}{255}\right|\right) * \text{byte offset frequency}_{i}}{\text{total } \# \text{ of bytes}} * 100$$

$$where:$$

$$N = \text{minimum byte offset}$$

$$M = \text{maximum byte offset}$$

(5.3)

Table 5.6 shows that the hardware decompressed test images are nearly 100% of their software decompressed counterpart.

| Image     | Percentage of SW Image (%) |

|-----------|----------------------------|

| bookstore | 99.3914                    |

| dog       | 99.357                     |

| beach     | 99.4129                    |

Table 5.6: Test Image Verification

#### 5.4 Summary

This chapter presents the results of the proposed design. The hybrid softwarehardware architecture was timed against a software only method providing 31% increase in timing in the decompression of a 20MP image, while maintaining over 99% accuracy. The timing was analyzed with 5MP, 10MP and 20MP images to observe that this design is superior to that of software as image size increases.

The following chapter concludes this work, and proposes design improvements for future work.

## Chapter 6

### Conclusion and Recommendations

The evolution of technology has greatly affected everyday consumers in the areas of mobile computing, and digital multimedia. The size of an image in digital photography, in terms of pixels, is constantly increasing as sensors, processors, and memory are improved. Mobile devices are approaching and meeting the processor speeds and architectures of their desktop counterparts. However, the methodology and algorithms used to decompress digital JPEG images on these powerful embedded systems is outdated and ineffective with the growing image sizes.

Since the invention of the JPEG image, software methods have been the sole answer for decompression. The JPEG decompression process contains many computations which increase with the image size. As computations increase so will the decompression time. To assist the software it is imperative to consider hardware acceleration in the mobile system to improve the decompression time of these images.

The research presented in this thesis focuses on the most cumbersome processing found in the software decompression of JPEG images. Hardware acceleration of the 2D-IDCT, YCC to RGB colour space conversion, and Huffman decoding processes were examined. The proposed solution to expedite slow JPEG decompression is hardware acceleration proven with the use of an FPGA. This novel design proves to combine the flexibility of software with the speed of hardware, resulting in a hybrid approach which accelerates the JPEG decompression significantly, while maintaining more than 99% of the original image.

The novelty of this architecture is the hybridization of the hardware and software to calculate the 2D-IDCT, and the YCC to RGB colour conversion. Multiplications in both components are calculated in parallel to optimize the throughput from software to hardware, preventing the need for the software to wait for the hardware to complete. The optimizations produced an average of 31% decrease in decompression time of a 20MP colour image, with no chroma-subsampling and no Huffman optimizations.

#### 6.1 Recommendations

This design has greatly improved the JPEG decompression process, but bottlenecks in the system do remain. The JPEG process is natively sequential, which limits some parallelization optimizations from being possible. The most significant bottleneck in this design, proved to be the software design and layout. Specifically the linearity of the library as well as memory management and data transfer from software to hardware. A memory managed GNU/Linux kernel, which many embedded systems are based off, has limitations on the user-space from accessing its own physical memory addresses. This requires the need for kernel involvement, at the cost of time. Memory management is a concern in a typical software implementation to avoid lagging or crashing the system. Hardware would have the ability to act like a co-processor, but in this implementation the memory access is limited by the library layout. For these reasons, my recommendation for future improvement involves rewriting the libjpeg library with these considerations in mind. The library would need to implement a shared memory pool between software and hardware for direct access to the raw JPEG as well as the output buffer. This would allow less data copying, permit the hardware to relieve more workload from software, as well as access raw data for the Huffman decoding process.

#### References

- [1] Microblaze soft processor core @ONLINE, January 2011. http://www.xilinx.com/tools/microblaze.htm.

- [2] Petalinux software development kit @ONLINE, January 2011. http://www.xilinx.com/tools/petalinux-sdk.htm.

- [3] Xilinx university program xupv-lx110t development platform @ONLINE, January 2011. http://www.xilinx.com/products/boards-and-kits/XUPV5-LX110T.htm.

- [4] Joint photographic experts group @ONLINE, January 2012. http://www.jpeg.org.

- [5] Calvin Hass. Impulse adventure jpeg huffman coding tutorial @ONLINE, March 2011. http://www.impulseadventure.com/photo/jpeg-huffman-coding.html.

- [6] D.A. Huffman. A method for the construction of minimum-redundancy codes. Proceedings of the IRE, 40(9):1098–1101, 1952.

- [7] Tom Lane. Independent jpeg group @ONLINE, October 2010. http://www.ijg.org/.

- [8] C. Loeffler, A. Ligtenberg, and G.S. Moschytz. Practical fast 1-d dct algorithms with 11 multiplications. In Acoustics, Speech, and Signal Processing, 1989. ICASSP-89., 1989 International Conference on, pages 988–991 vol.2, may 1989.

- [9] G.E. Moore. Cramming more components onto integrated circuits. Proceedings of the IEEE, 86(1):82–85, 1998.

- [10] Wendi Pan. A fast 2-d dct algorithm via distributed arithmetic optimization. In *Image Processing*, 2000. Proceedings. 2000 International Conference on, volume 3, pages 114 –117 vol.3, 2000.

- [11] Soo-Chang Pei and Jian-Jiun Ding. Reversible integer color transform with bit-constraint. In *Image Processing*, 2005. ICIP 2005. IEEE International Conference on, volume 3, pages III – 964–7, sept. 2005.

- [12] R. Swamy, M. Khorasani, Yongjie Liu, D. Elliott, and S. Bates. A fast, pipelined implementation of a two-dimensional inverse discrete cosine transform. In *Electri*cal and Computer Engineering, 2005. Canadian Conference on, pages 665–668, may 2005.

- [13] G.K. Wallace. The jpeg still picture compression standard. Consumer Electronics, IEEE Transactions on, 38(1):18–19, feb 1992.

- [14] Yang Yang, Peng Yuhua, and Liu Zhaoguang. A fast algorithm for ycbcr to rgb conversion. Consumer Electronics, IEEE Transactions on, 53(4):1490 –1493, nov. 2007.

# Appendix A

Source Images

#### A. SOURCE IMAGES

Figure A.1: Sample 20MP images

### Appendix B

## Testing Scripts

```

#!/bin/bash

# This script times and runs the Secondary scripts with the given parameters

# COUNT = The number of times to run the secondary script

# RESULT_FILE = the files to store the timing results in

# PROG = precompiled program name

0 = Software only

#

1 = IDCT HW accelerated

2 = Colour Conversion HW accelerated

#

3 = IDCT + Colour Conversion HW accelerated

#

# ARG1 = the path to the image to be decoded

Available images:

5MP_1.jpg, 5MP_2.jpg, 5MP_3.jpg,

10MP_1.jpg, 10MP_2.jpg, 10MP_3.jpg,

#

# 20MP_1.jpg, 20MP_2.jpg, 20MP_3.jpg

# ARG2 = boolean to write the resultant image to the system's framebuffer

# ARG3 = factor to scale the image down

# Variables

COUNT=20 # user-defined

RESULT_FILE0=results_SW_timing.txt

RESULT_FILE1=results_idct_timing.txt

RESULT_FILE2=results_colour_timing.txt

RESULT_FILE3=results_total_timing.txt

PROGO=./Image_SW_control

PROG1=./ImageHw_idct

PROG2=./ImageHw_colour

PROG3=./ImageHw_total

ARG2=0

# fb: 0 = no, 1 = yes

ARG3 = 1

# scale factor: 1-8

ARG1=pics/pic.jpg  # path to image file

```