## University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

1991

# An architecture for multi-layer feed-forward neural networks.

Aria. Nosratinia University of Windsor

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### **Recommended** Citation

Nosratinia, Aria., "An architecture for multi-layer feed-forward neural networks." (1991). Electronic Theses and Dissertations. Paper 980.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A ON4

## NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

## AN ARCHITECTURE FOR MULTI-LAYER FEED-FORWARD NEURAL NETWORKS

by

Aria Nosratinia

A Thesis Submitted to the Faculty of Graduate Studies through the Department of Electrical Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

> Windsor, Ontario, Canada August 1991

National Library of Canada Bibliothèque nationale du Canada

Canadian Theses Service

Ottawa, Canada K1A 0N4 Service des thèses canadiennes

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-69905-1

© Aria Nosratinia 1991

All Rights Reserved

### ABSTRACT

Feed-forward neural networks can perform classifications and generalizations that are difficult to achieve with any other known method, and their performance matches or surpasses that of the conventional methods. To utilize the potential of these networks to the fullest, however, an efficient hardware implementation is needed. In this thesis, an architecture for efficient implementation of feed-forward multi-layer neural networks is introduced. The interconnection congestion problem is addressed by a multiplexing scheme, which reduces the number of physical interconnections without any loss of generality. The building blocks are mostly in current mode analog CMOS, and the connection strengths of the network are stored in a digital memory. Also included in this thesis is a performance analysis of the architecture and a study of the effects of quantization and truncation of connection strengths on network performance.

To my parents

#### ACKNOWLEDGEMENTS

I would like to express my sincere thanks and appreciation to my supervisors, Dr. M. Ahmadi and Dr. M. Shridhar, for their support and guidance throughout the progress of this thesis. I would also like to thank Mr. Jun Cao for his help in running the simulations of chapter 5. Thanks must also go to the Mostafapour family for their unfailing support and encouragement during my stay in Windsor.

## TABLE OF CONTENTS

| ABSTRACT             | •      | •     | •     | ٠     | •     | •     | •    | •     | •    | •    | •    | •   |     | • | • | • | • | iv  |

|----------------------|--------|-------|-------|-------|-------|-------|------|-------|------|------|------|-----|-----|---|---|---|---|-----|

| DEDICATION .         |        | •     |       |       | •     |       |      |       |      |      |      |     |     | • | • | • | • | v   |

| ACKNOWLEDGEN         | MEN    | ГS    | •     | •     | •     | •     | •    |       |      |      | •    |     | •   |   |   | • | • | vi  |

| LIST OF FIGURES      | ; .    | •     | •     |       |       |       |      | •     |      |      |      | •   |     |   |   |   |   | ix  |

| LIST OF TABLES       | •      | •     | •     | •     | •     | •     | •    | •     | •    | •    | •    | •   | •   | • | • | • | ٠ | xii |

| 1. Introduction .    |        | •     | •     | •     | •     | •     |      |       |      | •    |      |     | •   | • | • | • | • | 1   |

| 1.1 Goals, objec     | tives  | and   | org   | gani  | zatio | on o  | f th | is th | esis | •    |      | •   | •   | • | • | ٠ | • | 2   |

| 1.2 A brief histo    | ry of  | rese  | earc  | h in  | nei   | ral   | moo  | iels  | •    | •    | •    | ٠   | •   | • | • | • | ٠ | 4   |

| 1.3 Some major       | poin   | ts oi | n ne  | rvo   | us sj | yste  | m a  | nd r  | ieur | al n | node | ls  |     | • | • |   | • | 6   |

| 1.4 Implementat      | tion c | of ne | ura   | l ne  | twoi  | rks   | •    | •     | •    | •    | •    | •   | •   |   |   |   | • | 7   |

| 1.5 VLSI implei      | menta  | itior | ns –  |       | •     | •     | •    | •     | •    |      | •    |     |     | • | • | • |   | 9   |

| 1.6 Handwritten      | i char | acte  | er re | cog   | nitic | on a  | nd f | eed-  | for  | wara | i ne | two | rks |   |   | • |   | 12  |

| 1.7 Summary .        | •      | •     | •     | •     |       | •     | •    | ٠     | ٠    | •    | •    | •   | •   | • | • | • |   | 14  |

| 2. An Architecture f | for M  | ulti- | -Lay  | yer l | Neu   | ral N | letv | vork  | .s   | •    |      |     | •   |   |   |   |   | 15  |

| 2.1 The archited     | ture   | •     |       |       |       |       | •    | •     |      |      | •    |     |     | • | • |   | • | 18  |

| 2.2 Operation .      | •      | •     |       |       |       |       |      |       | •    | •    |      | •   |     |   | • | • |   | 20  |

| 2.3 Modification     | ns.    | •     |       |       |       | •     |      |       |      |      | •    | •   | •   | • |   | • |   | 23  |

| 2.4 Units and so     | cales  |       |       | •     |       |       |      |       | •    |      |      |     | •   | • |   |   | • | 25  |

| 2.5 Input/output     | t con  | side  | ratio | ons   |       |       |      | •     |      |      |      | •   |     | • |   |   |   | 27  |

| 2.6 Performance      |        |       |       |       |       |       |      |       |      |      |      |     |     |   |   |   |   |     |

| 2.7 Summary          |        | -     |       |       |       | -     |      |       |      |      |      |     |     |   |   |   |   |     |

| 3.Neuron and Syna    | ipse   | •     |       |       |       |       |      | •     | ٠    |      |      | •   | •   |   |   |   |   | 42  |

| 3.1 Neuron           | -      |       |       |       |       |       |      |       |      |      |      |     |     |   |   |   |   | 42  |

| 3.1.1 Curre          | ent m  | ode   | neı   | ıron  | ıs.   |       |      |       |      |      |      | •   |     |   | • |   |   | 43  |

| 3.1.2 Volta          | ge m   | ode   | neu   | rons  | s.    |       |      |       |      |      |      |     |     |   |   |   |   | 48  |

| 3.2 Synapse          | -      |       |       |       |       |       |      |       |      |      |      |     |     | • |   |   |   | 50  |

| 3.2.1 Multi          |        |       |       |       |       |       |      |       |      |      |      |     |     | • |   | • |   | 50  |

| 3.2.2 ROM            | •      |       |       |       |       |       |      |       |      |      |      | •   |     | • | • |   |   | 53  |

| 3.3 Summary          |        |       |       |       |       |       |      |       |      |      |      |     | *   |   |   |   | • | 56  |

| Ju Juning            | · ·    | •     | •     | •     | •     | •     | •    | -     | •    | -    |      |     |     |   |   |   |   |     |

| 4. Support Circuitry | ,        |         |        | •          | •     | •      | •     | •     | •     | •   |   | • | • | ٠ | • | 57  |

|----------------------|----------|---------|--------|------------|-------|--------|-------|-------|-------|-----|---|---|---|---|---|-----|

| 4.1 Trans-imped      | lance ai | nplifie | r.     |            | •     | •      |       | •     | •     | •   |   | • |   | • | • | 57  |

| 4.2 Voltage to c     | urrent c | convert | er .   |            | •     | •      | •     | •     | •     |     | • |   | ٠ | • |   | 60  |

| 4.3 Address ger      | eration  | •       | • •    |            | •     |        | •     | •     |       | •   | • | • | • | • | • | 62  |

| 4.4 Analog buff      | ers and  | outpu   | t pad  | driv       | ers   | •      | •     | •     |       |     | • | ٠ |   | • | • | 63  |

| 4.4.1 A buff         | er with  | high c  | apac   | itive      | driv  | e.     | •     | •     | •     | •   | • | • | • | • | • | 64  |

| 4.4.2 A rail-        | to-rail  | buffer  | for re | esisti     | ive a | nd ca  | apac  | itive | e loa | ıds | • | • | • | • | • | 69  |

| 4.5 Summary .        | •        | • •     | •      |            | •     | •      | •     | •     | •     | •   | • | • | • | • | • | 75  |

| 5. Quantization and  | Trunca   | tion Ef | ffects | <b>.</b> . | •     | •      | •     |       |       | •   |   | • |   | • |   | 76  |

| 5.1 A simple ex      |          |         |        |            |       |        |       |       |       |     |   |   |   |   |   | 76  |

| 5.2 A complex of     | example  | e;hand  | writte | en cł      | narac | ter re | ecog  | gniti | on    |     | • |   |   |   |   | 77  |

| 5.3 Summary          | •        |         | •      | •          |       | •      | •     | •     | •     | •   | • | • | • | • | ٠ | 81  |

| 6. Conclusion .      |          |         |        | •          |       | •      | •     | •     | •     | •   | ٠ | ٠ | ٠ | ٠ | • | 82  |

| Appendix A A B       | rief Ov  | erview  | of th  | ne N       | ervo  | us S   | ystei | m     | •     | •   | • | • | • | • |   | 86  |

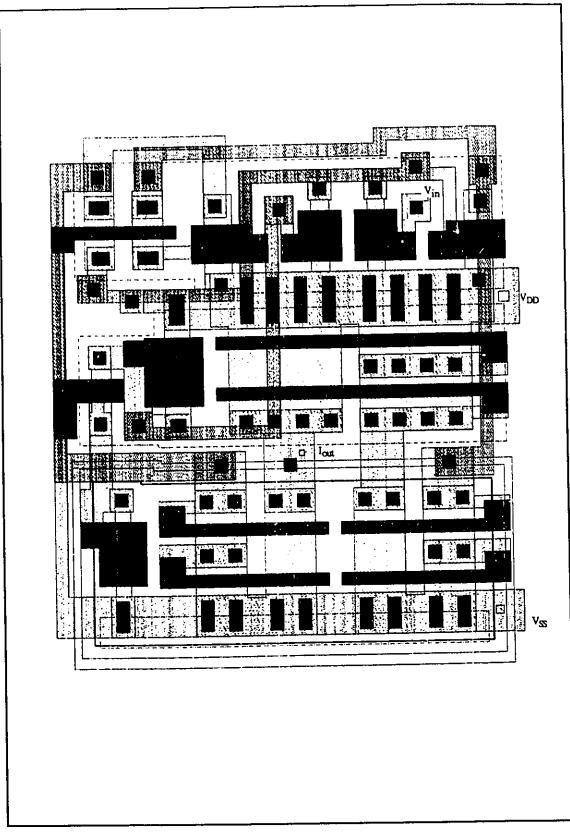

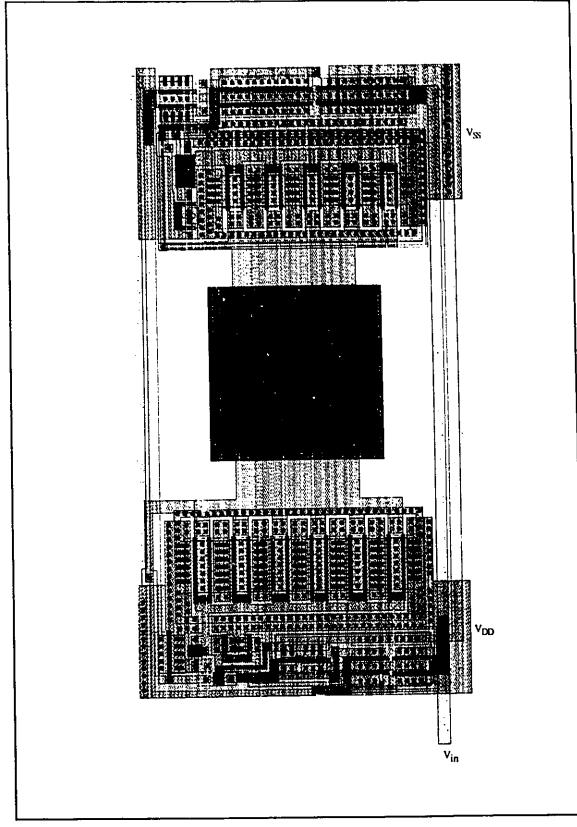

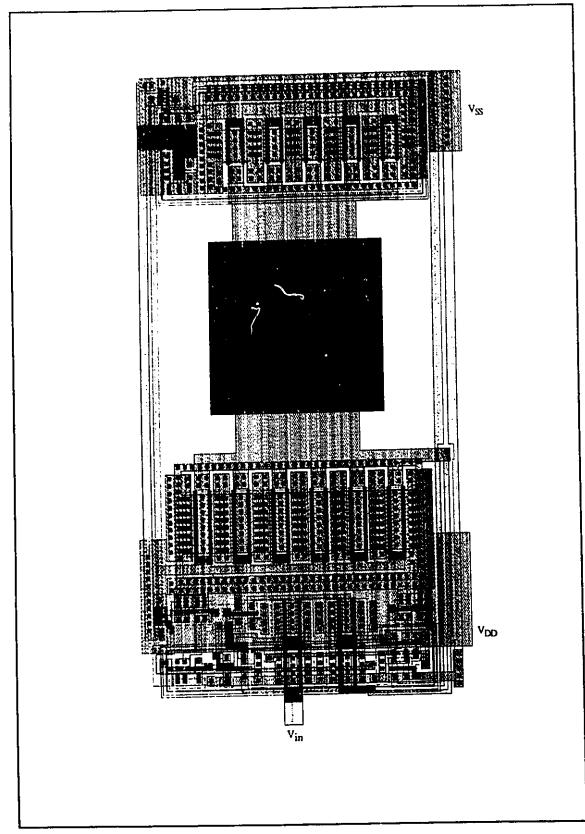

| Appendix B Lay       | out Dia  | grams   |        | •          | • •   | •      |       | •     | •     | •   | • |   | • | • | • | 95  |

| Appendix C Har       | dware a  | ind Sol | ftwar  | e To       | ools  | ٠      | ٠     | •     | •     | •   | • | • | • | • | • | 106 |

| REFERENCES           |          | • •     |        | •          |       | •      | •     | •     | •     | •   | • | • | • | • |   | 109 |

| VITA AUCTORIS        |          |         |        |            |       | •      |       | •     |       | •   | • | • | • | • |   | 118 |

## LIST OF FIGURES

| Figure 1.1:  | Character Recognition                                          | 13    |

|--------------|----------------------------------------------------------------|-------|

| Figure 2.1:  | Multi-layer feed-forward network                               | 16    |

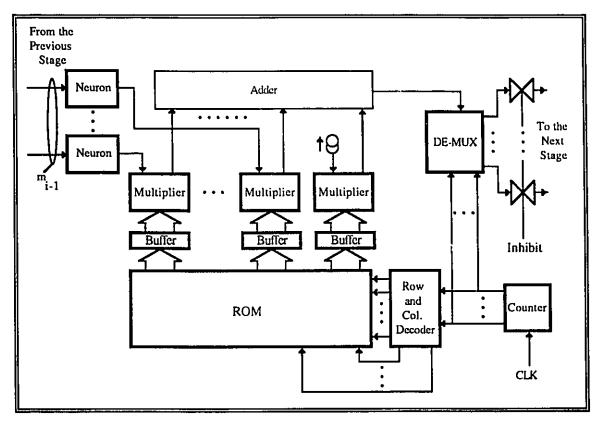

| Figure 2.2:  | Layers and stages in the architecture                          | 18    |

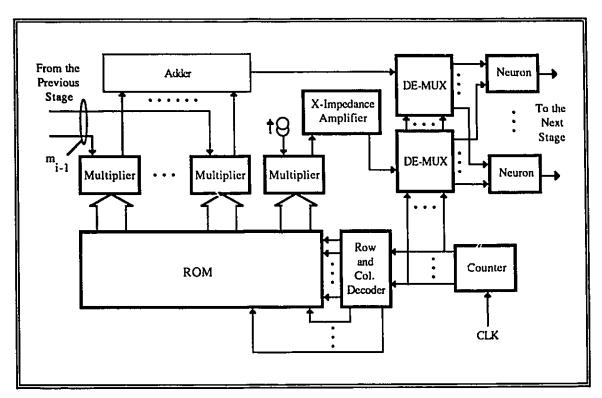

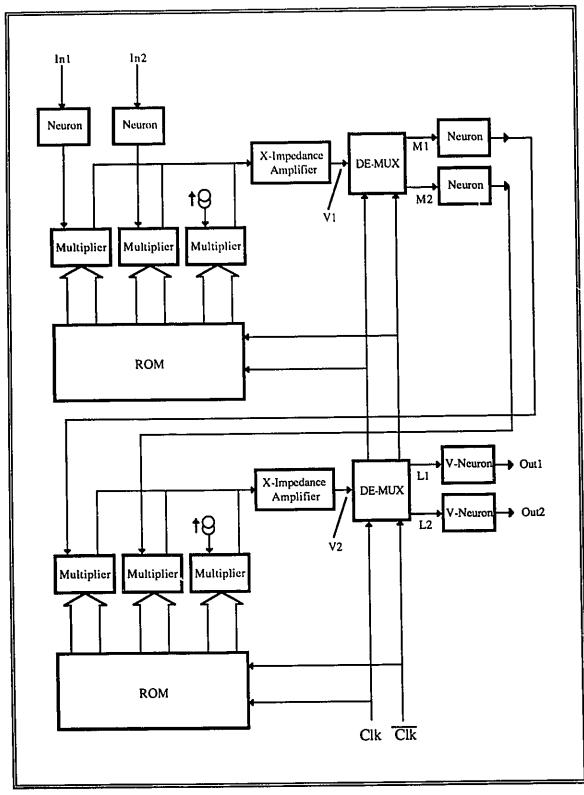

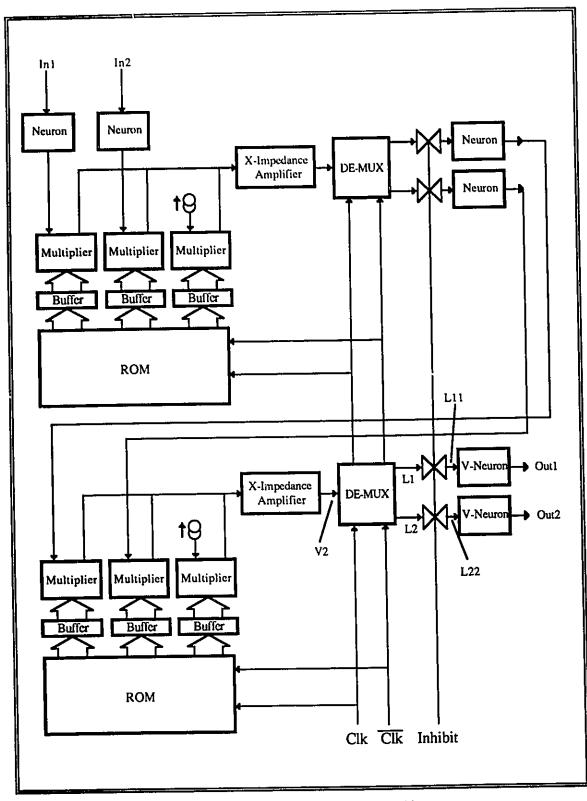

| Figure 2.3:  | Internal structure of one stage                                | 19    |

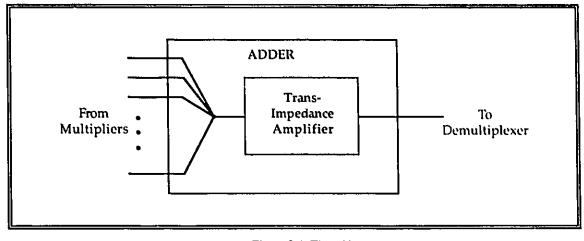

| Figure 2.4:  | The adder                                                      | 21    |

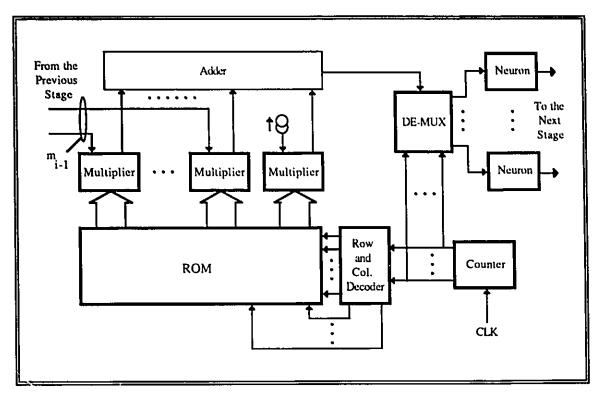

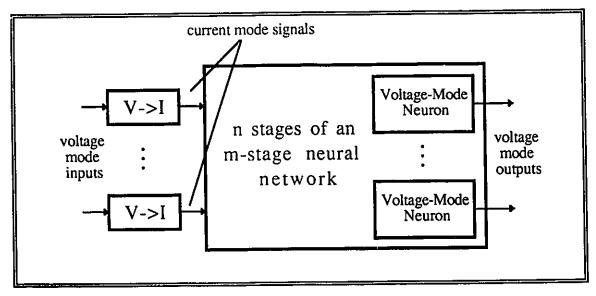

| Figure 2.5:  | Modified architecture                                          | 23    |

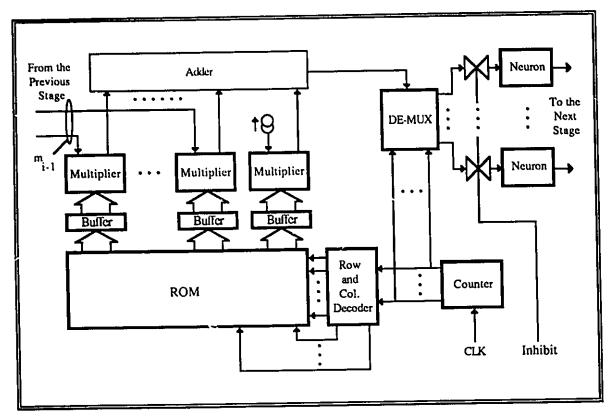

| Figure 2.6:  | Second modification for further improvement                    | 24    |

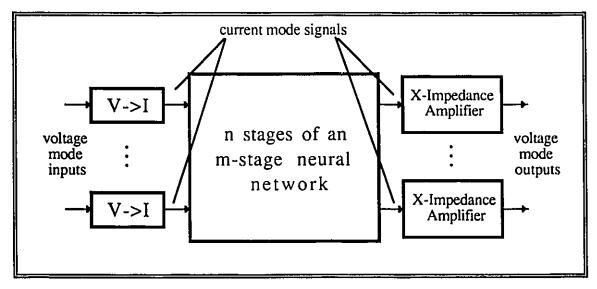

| Figure 2.7:  | Conversion of the signal mode at input and output              | 28    |

| Figure 2.8:  | Second solution to the I/O problem                             | 29    |

| Figure 2.9:  | Changing the I/O mode by displacing the neurons                | 30    |

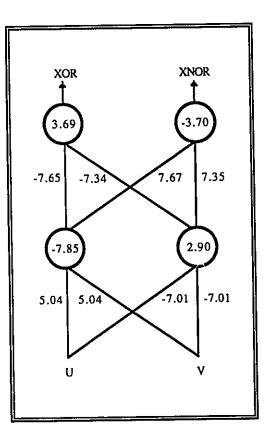

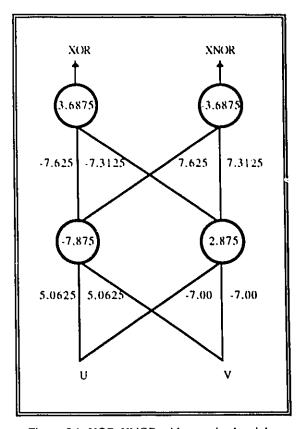

| Figure 2.10: | XOR and XNOR                                                   | 31    |

| Figure 2.11: | XOR-XNOR using the original architecture                       | 32    |

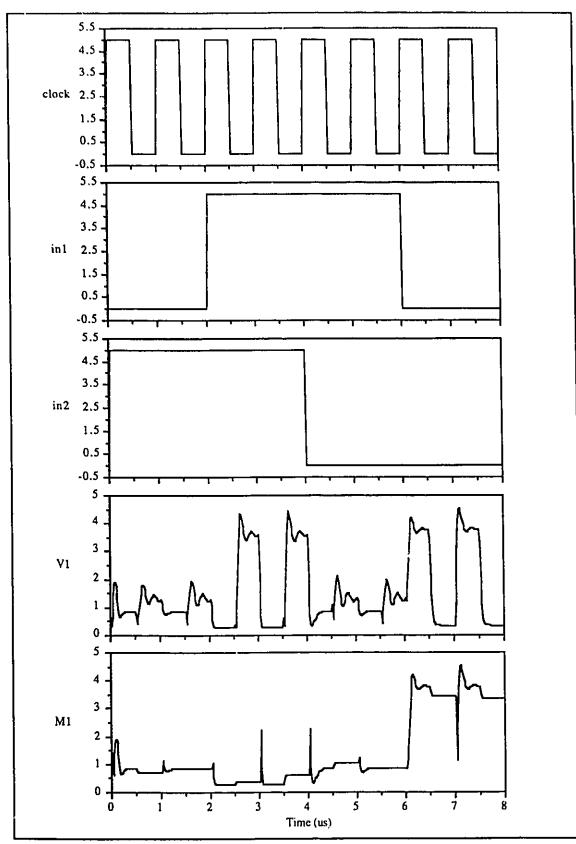

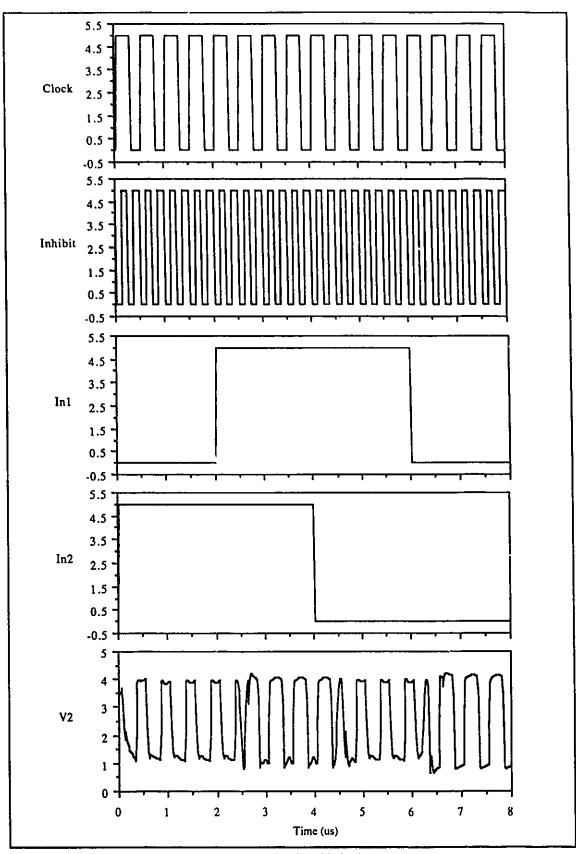

| Figure 2.12: | Waveforms of the original architecture                         | 33-35 |

| Figure 2.13: | XOR-XNOR with the modified architecture                        | 37    |

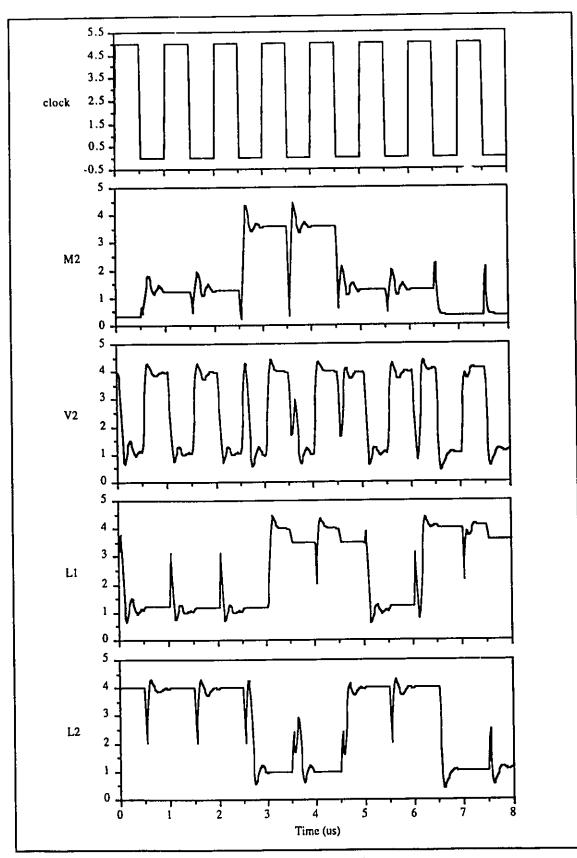

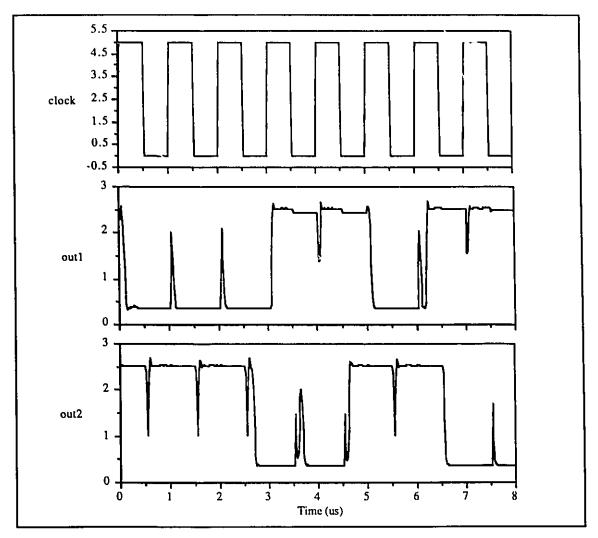

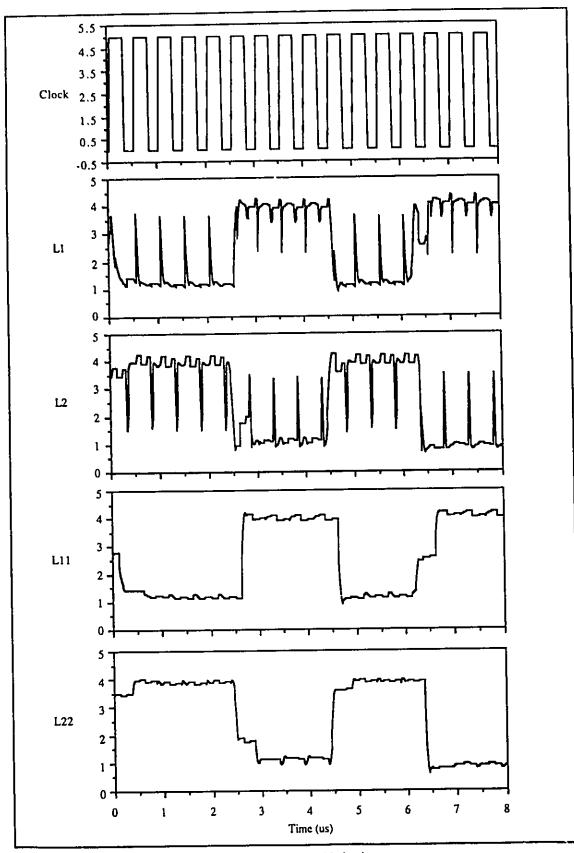

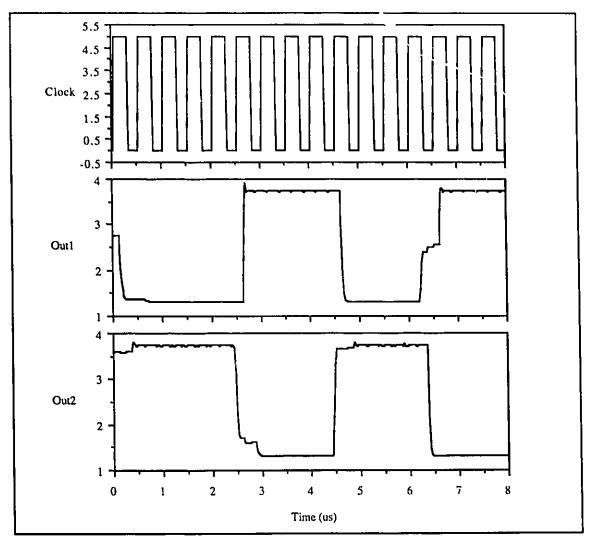

| Figure 2.14: | Waveforms of the modified architecture                         | 38-40 |

|              |                                                                |       |

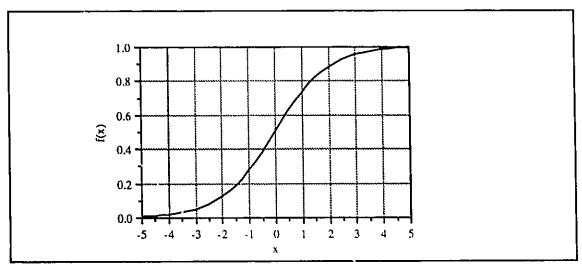

| Figure 3.1:  | The sigmoidal logistics function                               | 43    |

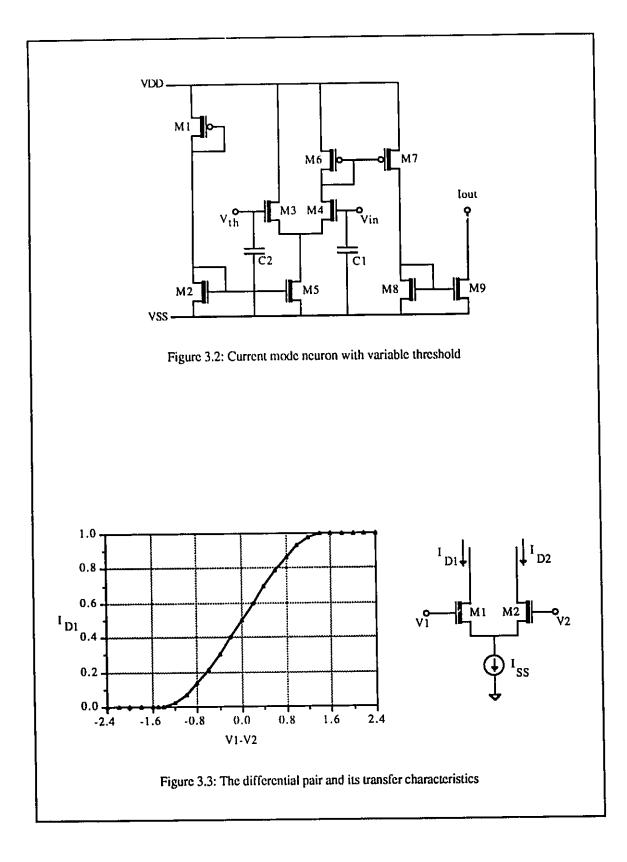

| Figure 3.2:  | Current mode neuron with variable threshold                    | 44    |

| Figure 3.3:  | The differential pair and its transfer characteristics         | 44    |

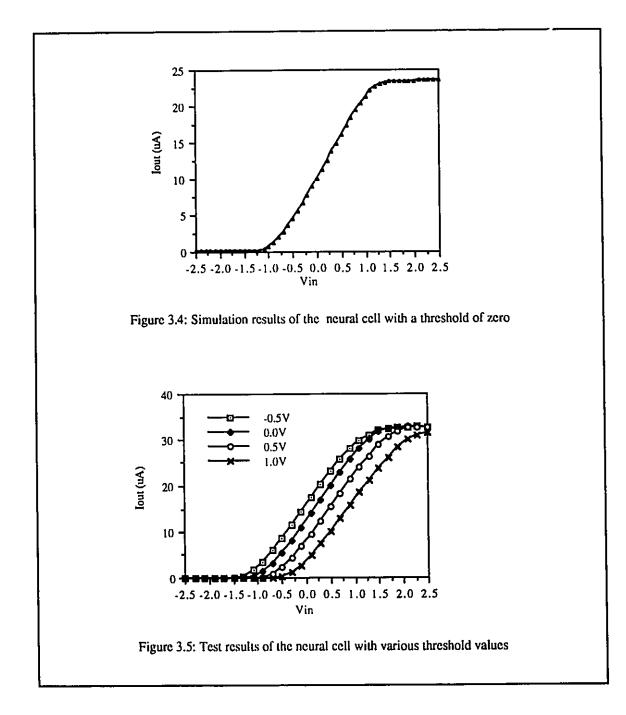

| Figure 3.4:  | Simulation results of the neural cell with a threshold of zero | 46    |

| Figure 3.5:  | Test results of the neural cell with various threshold values  | 46    |

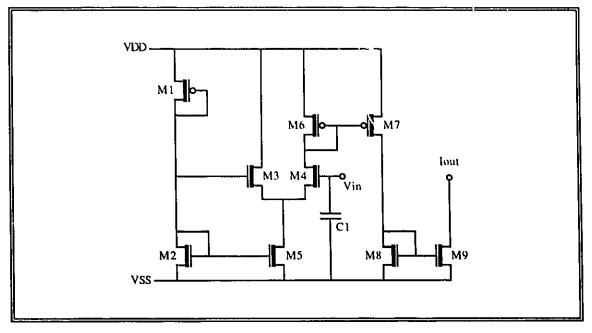

| Figure 3.6:  | Current mode neural cell with fixed threshold                  | 47    |

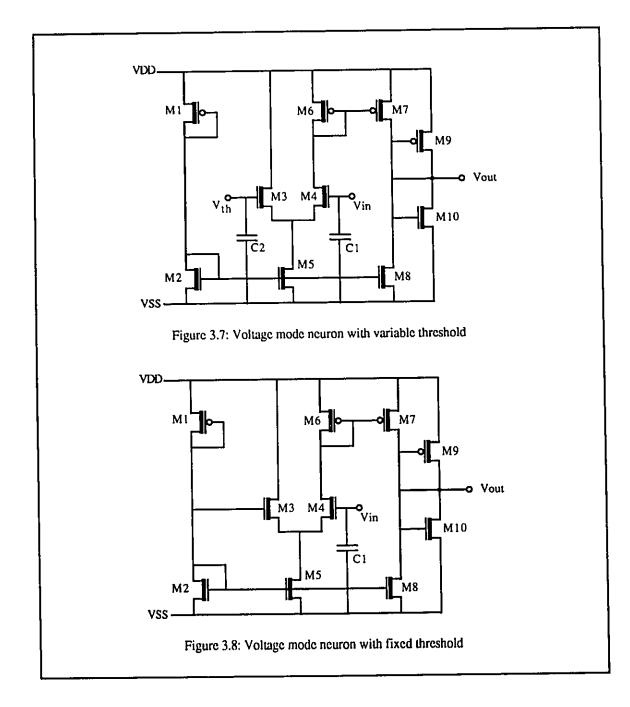

| Figure 3.7:  | Voltage mode neuron with variable threshold                    | 48    |

| Figure 3.8:                 | Voltage mode neuron with fixed threshold                                               |   |

|-----------------------------|----------------------------------------------------------------------------------------|---|

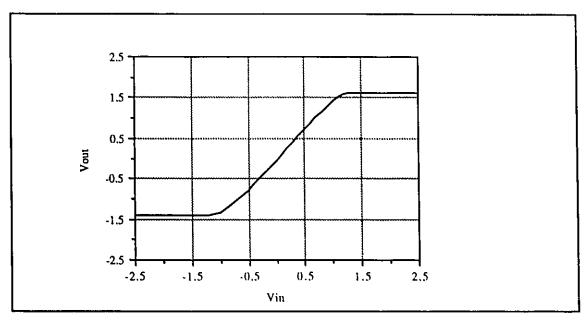

| Figure 3.9:                 | Transfer characteristics of the voltage mode neuron                                    |   |

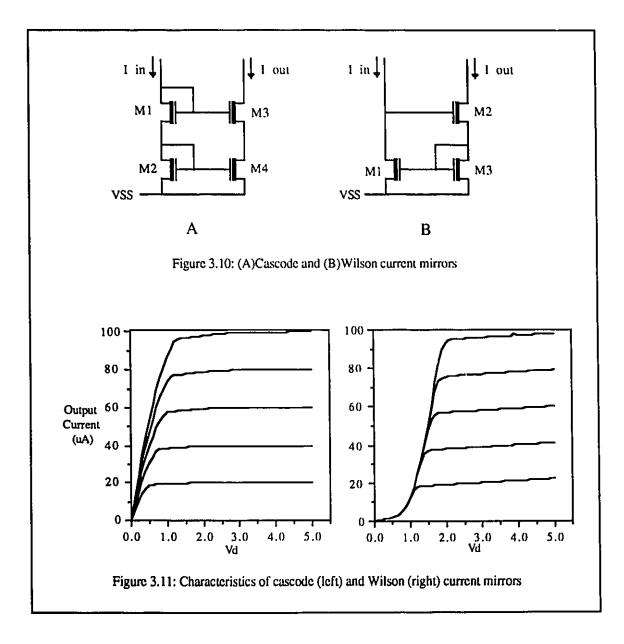

| Figure 3.10:                | Cascode and Wilson current mirrors                                                     |   |

| Figure 3.11:                | Characteristics of cascode and Wilson current mirrors 51                               |   |

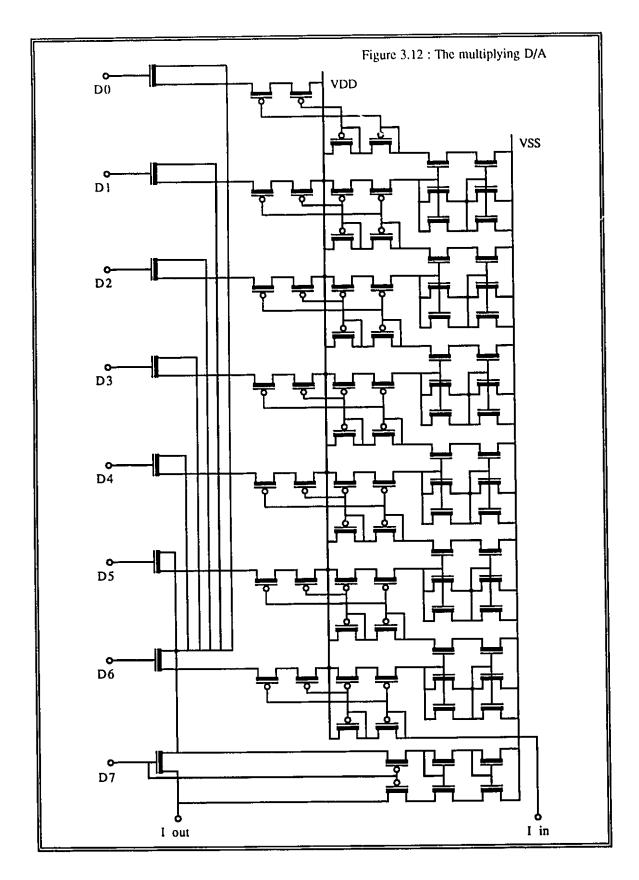

| Figure 3.12:                | The multiplying D/A                                                                    |   |

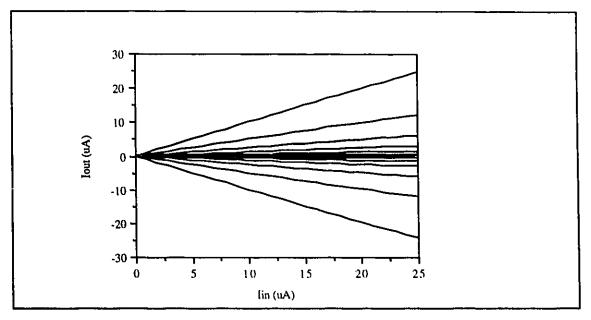

| Figure 3.13:                | Output of the D/A vs. input current                                                    |   |

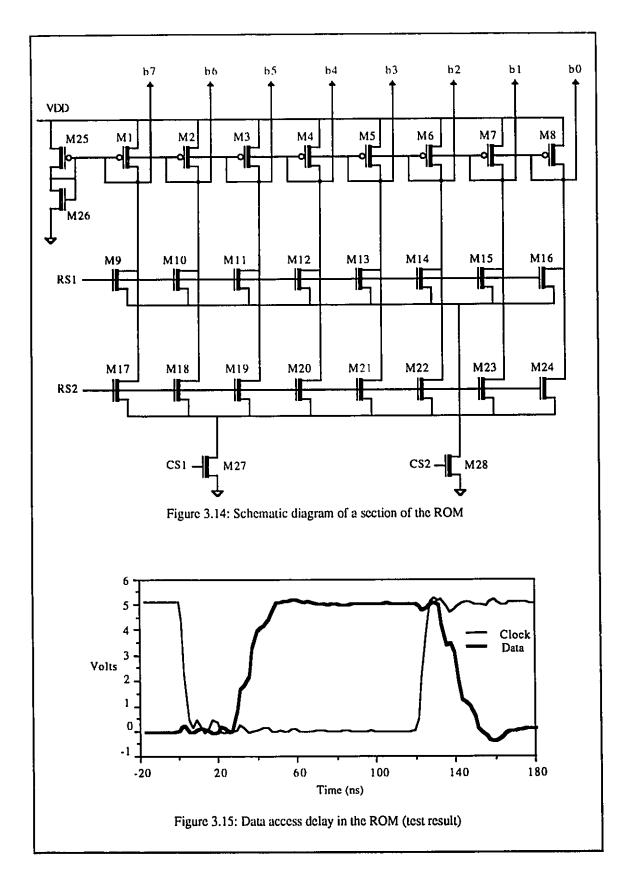

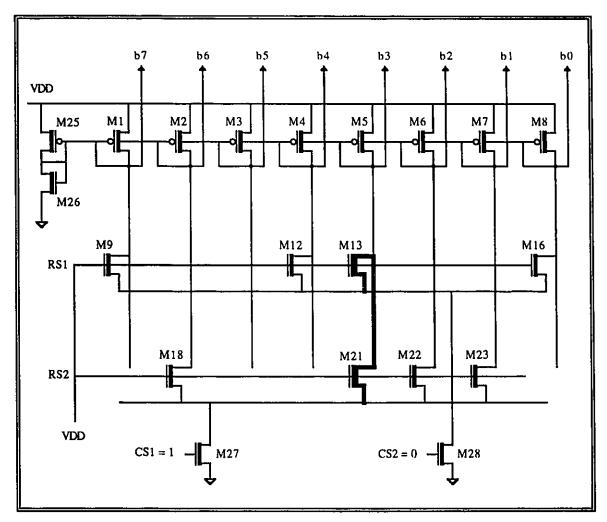

| Figure 3.14:                | Schematic diagram of a section of the ROM                                              |   |

| Figure 3.15:                | Data access delay in the ROM                                                           |   |

| Figure 3.16:                | A possible source of error in the ROM circuit                                          |   |

|                             |                                                                                        |   |

| Figure 4.1:                 | Trans-impedance amplifier                                                              |   |

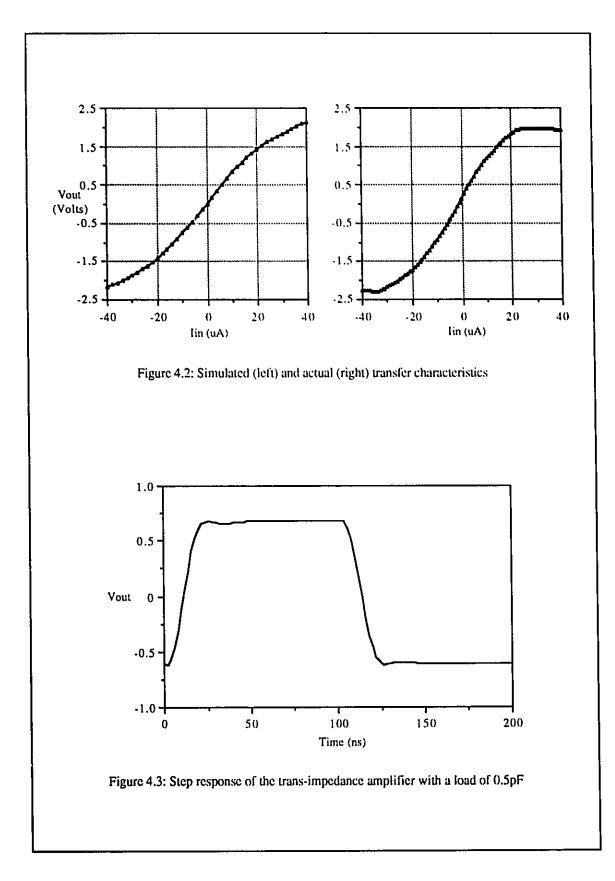

| Figure 4.2:                 | Simulated and actual transfer characteristics                                          | ) |

| Figure 4.3:                 | Step response of the X-impedance amplifier with a load of 0.5pF 59                     | ) |

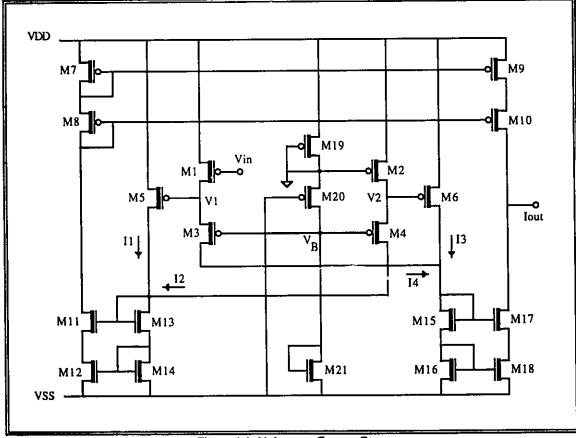

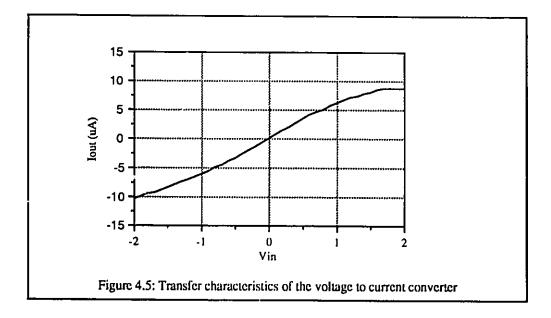

| Figure 4.4:                 | Voltage to current converter                                                           | ) |

| Figure 4.5:                 | Transfer characteristics of the voltage to current converter 61                        | l |

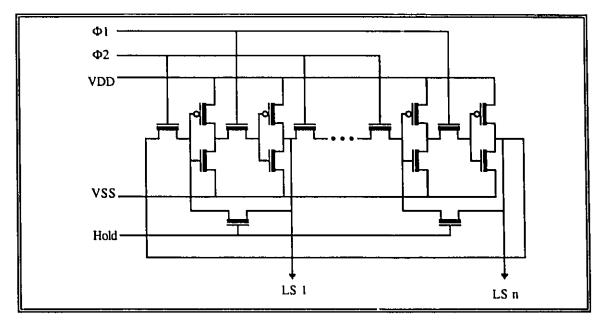

| Figure 4.6:                 | A suggested circuit for the ring counter                                               | 3 |

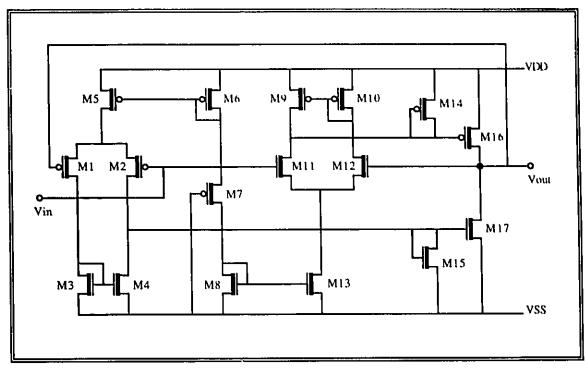

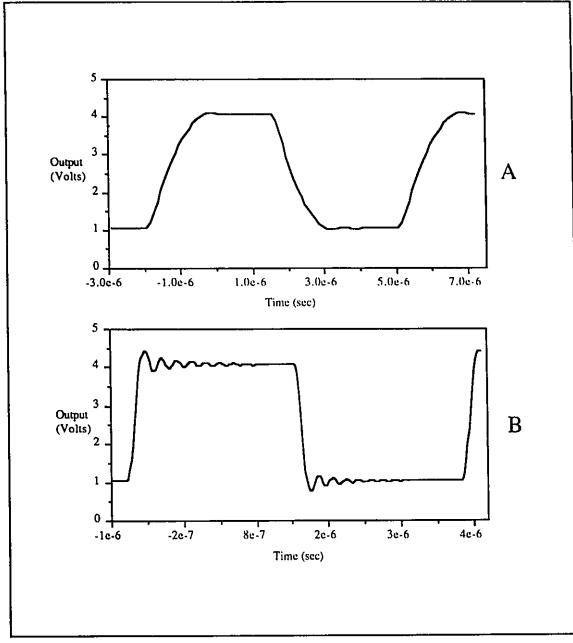

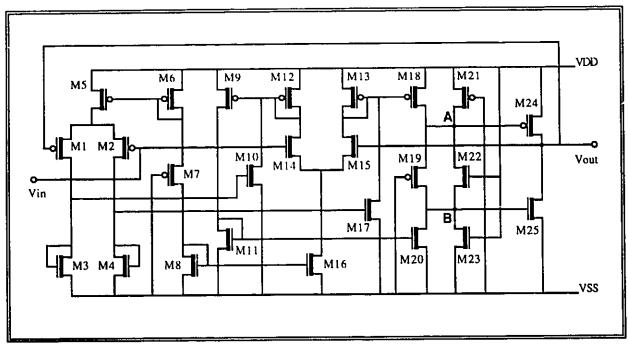

| Figure 4.7:                 | Schematic diagram of the buffer with high capacitive drive 65                          | 5 |

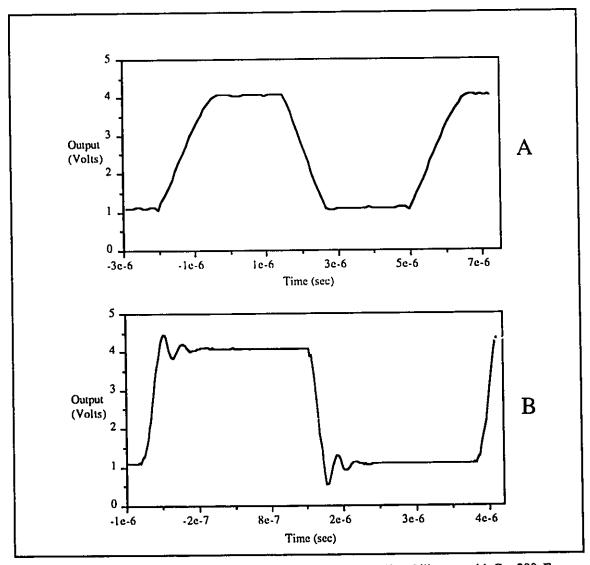

| Figure 4.8:                 | Test results: A) Step response with $C_L=5000pF$                                       |   |

|                             | B) Stability test with $C_L=200pF$ 65                                                  |   |

| Figure 4.9:                 | Transfer characteristics with various loads (test results) 68                          | 3 |

| Figure 4.10:                | Normalized harmonics of the output at 20kHz with Vin=2V(p-p) 6                         | 8 |

| Figure 4.11:                | Frequency response of the buffer with CL=5000pF RL=10k $\Omega$ . 65                   | 8 |

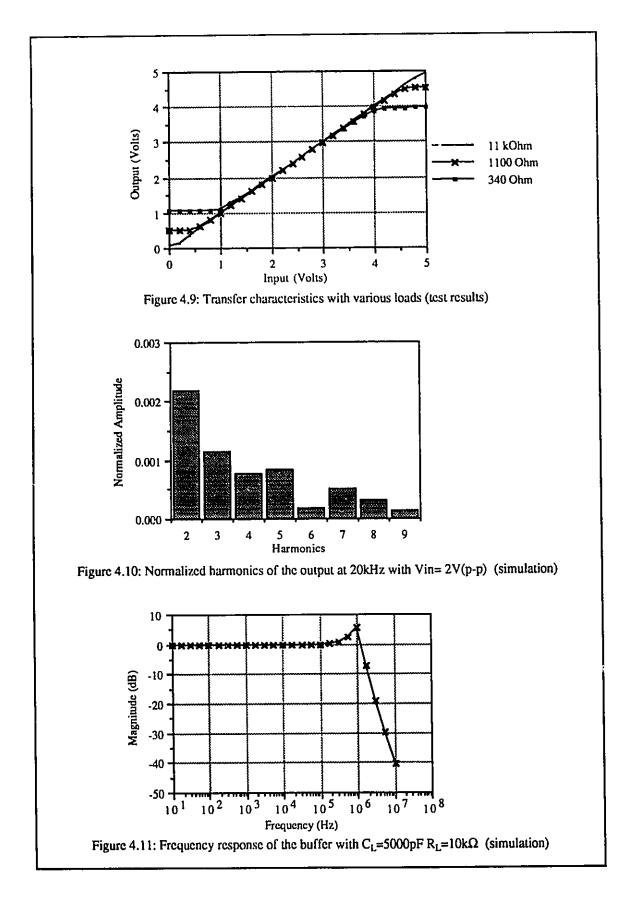

| Figure 4.12:                | Schematic diagram of the buffer for resistive and capacitive load 70                   | 0 |

| Figure 4.13:                | Test results: A) step response with $C_L=5000pF$<br>B) Stability test with $C_L=200pF$ | 2 |

| <b>E</b> laura: <b>4</b> 14 | _)j                                                                                    |   |

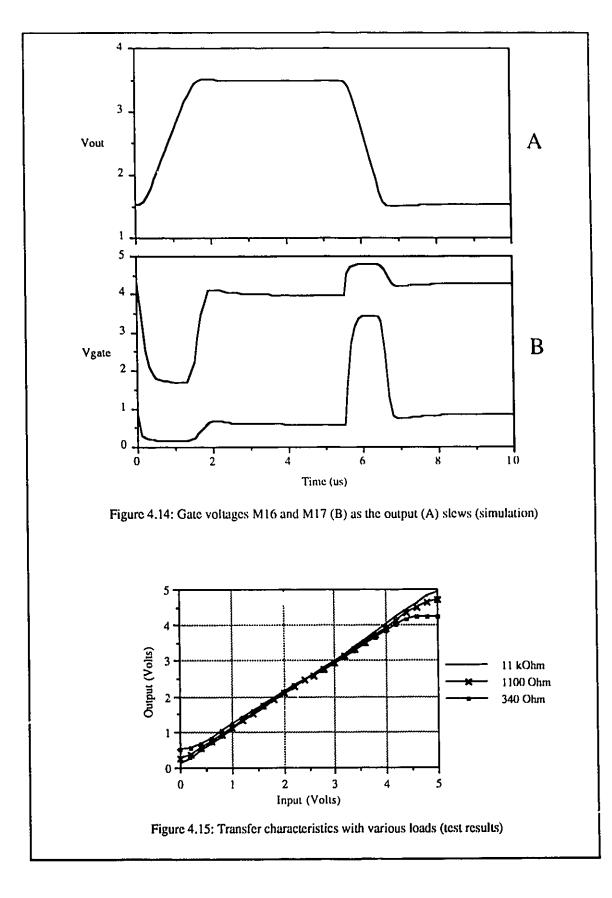

| Figure 4.14:                |                                                                                        |   |

| Figure 4.15:                | Transfer characteristics with various loads (test results) 7                           | 2 |

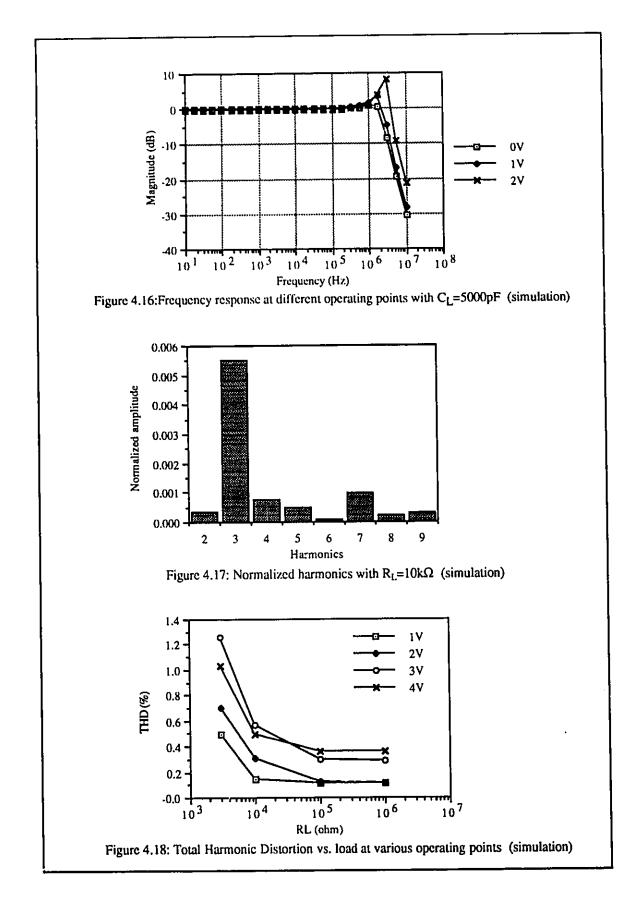

| Figure 4.16: | Frequency response at different operating points with C <sub>L</sub> =5000pF | 74  |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------|-----|--|--|--|--|--|

| Figure 4.17: | Normalized harmonics at 20kHz with Vin=2V(p-p) and $R_L=10k\Omega$ 74        |     |  |  |  |  |  |

| Figure 4.18: | Total harmonic distortion vs. load at various operating points .             | 74  |  |  |  |  |  |

| Figure 5.1:  | XOR-XNOR with quantized weights                                              | 77  |  |  |  |  |  |

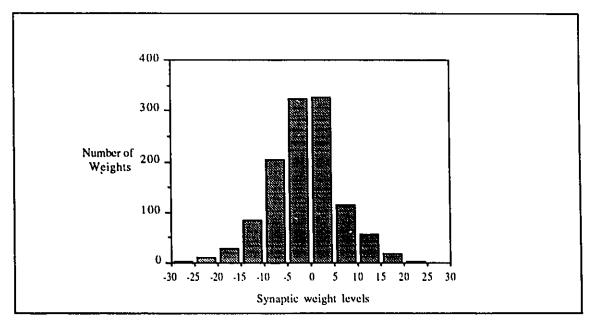

| Figure 5.2:  | Distribution of the synaptic weights in Example 2                            | 79  |  |  |  |  |  |

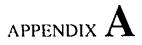

| Figure A.1:  | Neuron and its different sections                                            | 89  |  |  |  |  |  |

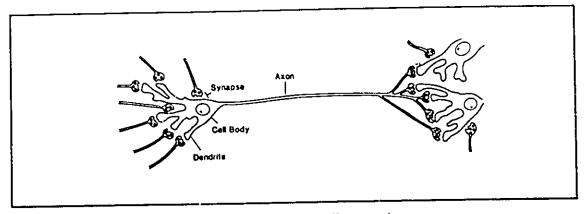

| Figure A.2:  | Different neuron types                                                       | 90  |  |  |  |  |  |

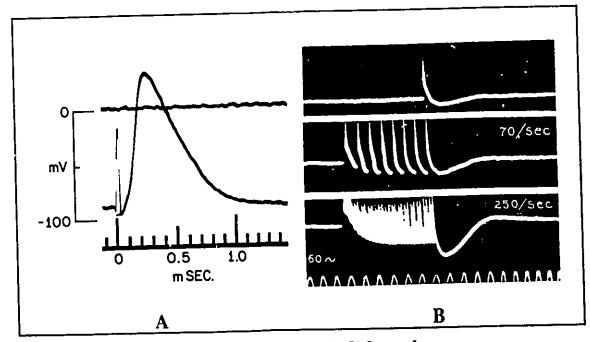

| Figure A.3:  | A) A typical nerve impulse B) Output of a neuron                             | 93  |  |  |  |  |  |

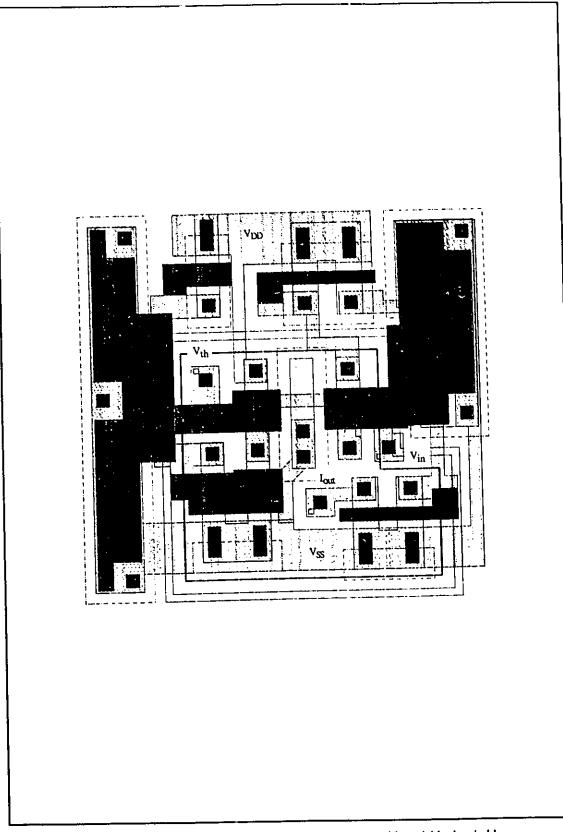

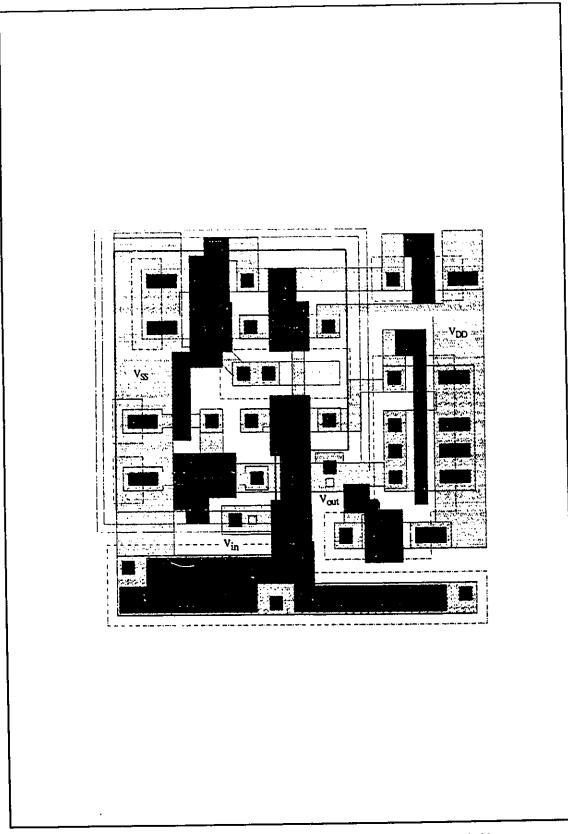

| Figure B.1:  | Layout diagram of the current mode neuron with variable threshold            | 96  |  |  |  |  |  |

| Figure B.2:  | Layout diagram of the current mode neuron with fixed threshold               | 97  |  |  |  |  |  |

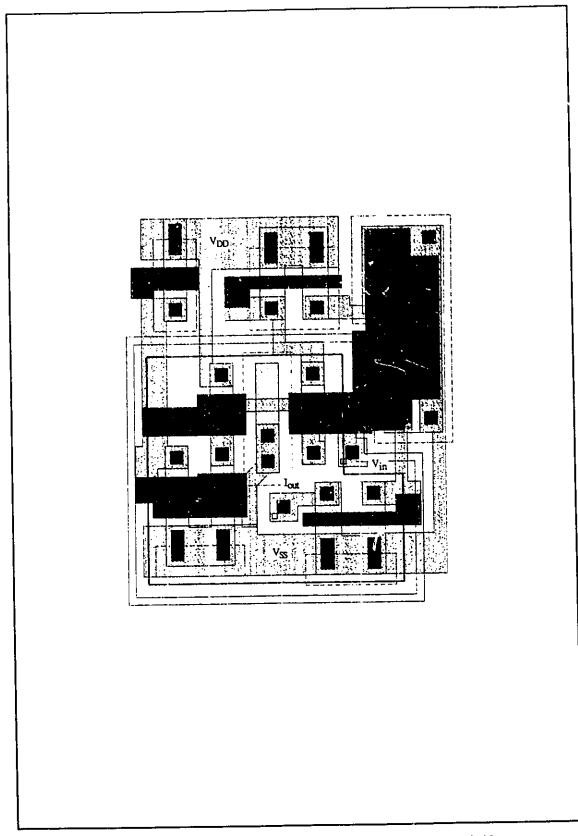

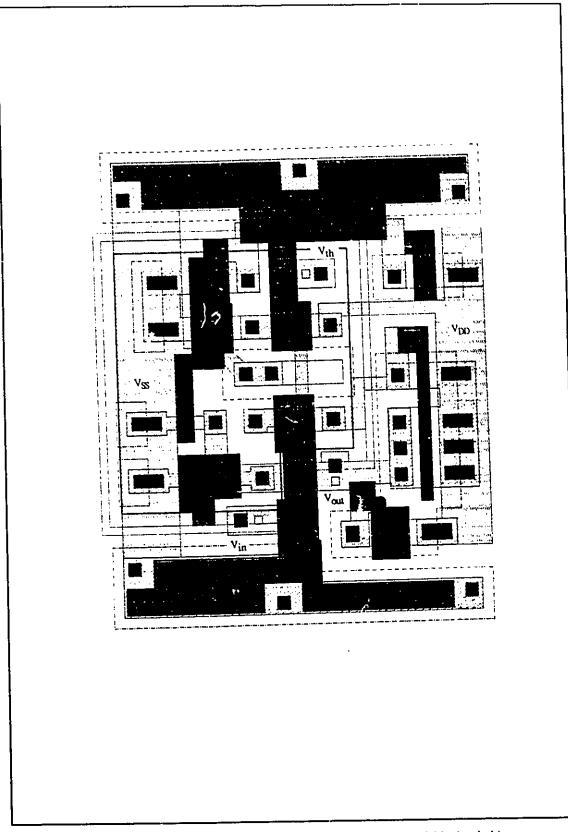

| Figure B.3:  | Layout diagram of the voltage mode neuron with variable threshold            | 98  |  |  |  |  |  |

| Figure B.4:  | Layout diagram of the voltage mode neuron with fixed threshold               | 99  |  |  |  |  |  |

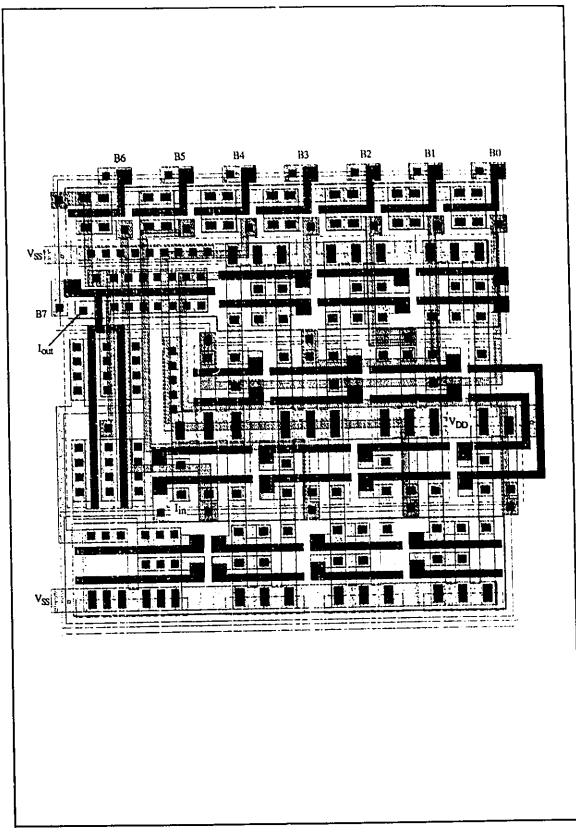

| Figure B.5:  | The multiplying D/A                                                          | 100 |  |  |  |  |  |

| Figure B.6:  | ROM with buffers                                                             | 101 |  |  |  |  |  |

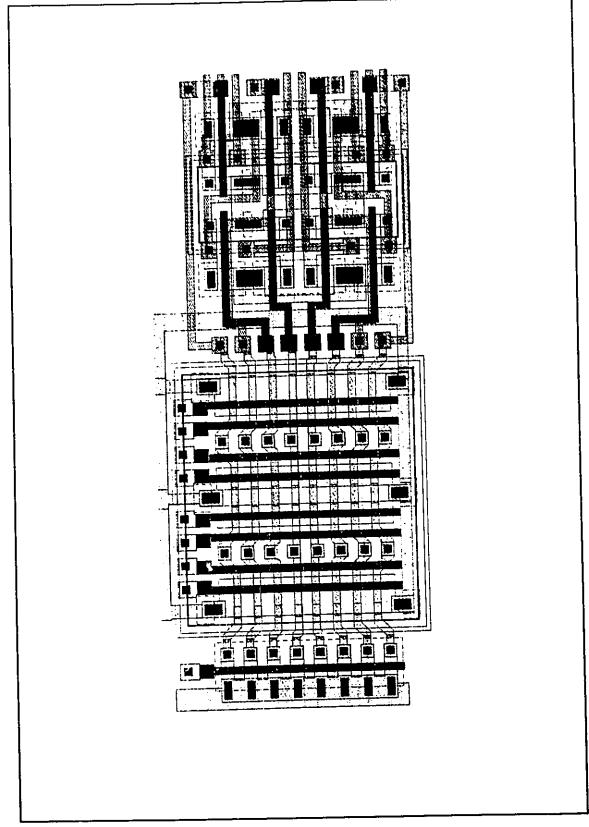

| Figure B.7:  | Trans-impedance amplifier                                                    | 102 |  |  |  |  |  |

| Figure B.8:  | Voltage to current converter                                                 | 103 |  |  |  |  |  |

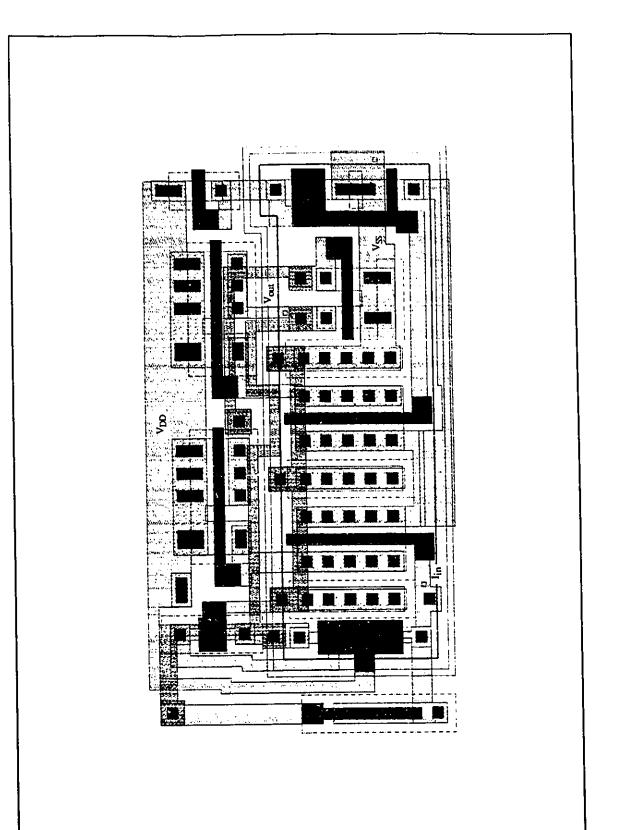

| Figure B.9:  | Output buffer for high capacitive loads                                      | 104 |  |  |  |  |  |

| Figure B.10: | Output buffer for high capacitive and resistive loads                        | 105 |  |  |  |  |  |

## LIST OF TABLES

| Table 3.1:       | Transistor geometries of the neural cells                    | • | • | • | 49 |

|------------------|--------------------------------------------------------------|---|---|---|----|

| <b>m</b> 11 4 1. | Device geometries for the trans-impedance amplifier          |   |   |   | 58 |

|                  | Device geometries for the voltage to current converter .     |   |   |   |    |

|                  | Device geometries for the buffer for capacitive loads        |   |   |   |    |

|                  | Worst case pole-zero configurations at Vin=4V (simulation)   |   |   |   |    |

|                  | Device geometries for the second buffer                      |   |   |   |    |

|                  | Pole-zero configu: ations (simulation)                       |   |   |   |    |

| 14010 1101       |                                                              |   |   |   |    |

| Table 5.1:       | Recall accuracy with the original connection strengths .     |   | • | • | 78 |

| Table 5.2:       | Recall accuracy with the weights quantized but not truncated |   |   |   | 80 |

| 14010 5.2. | Recard accuracy what are weights quantized to              |   |   |    |

|------------|------------------------------------------------------------|---|---|----|

| Table 5.3: | Recall accuracy with weights truncated at 20 and quantized | • | • | 80 |

| Table 5.4: | Recall accuracy with weights truncated at 14 and quantized | • | • | 80 |

## CHAPTER 1

## Introduction

Even in the age of supercomputers with processing powers in the range of tens to hundreds of megaflops, there are many tasks at which the human brain surpasses the computer. These tasks fall mainly in the area of associative memory, generalization, perception and classification. The brain itself is an amazingly complex machine, a systematic study and understanding of which started only a century ago. A brief overview of the structure and biology of the nervous system is presented in appendix A.

Ever since the mid-twentieth century, the capabilities of the brain in the areas of associative memory and robust decision making has drawn the interest of cognitive and physiological psychologists, as well as computer scientists. A variety of models to describe different behavioral aspects of the brain have been proposed since then. Each of these models, at best, reflects only a few of the properties of the nervous system.

In most of the cases where the brain holds the edge over the computer, a number of different pieces of information have to be processed at the same time. Examples include perception of written words, where one or more of the letters are partially or completely obscured [1-3], and spoken word or phrases where a part of the phonemes are removed [4]. These examples suggest a mechanism in which a number of processes occur simultaneously, influencing and being influenced by each other. This leads to a class of models that have most appropriately been called Parallel Distributed Processing (PDP) [3].

In these models, the processing of information is performed by a large number of relatively simple, highly interconnected elements. Psychologists usually consider these elements as certain hypotheses about such things as the letters in a particular display, and the activities would stand for the relative strengths of these hypotheses. In other cases, they may consider them as possible goals, objectives or actions. Electrical Engineers and others involved in physical sciences, however, prefer to consider these units as physical cells with measurable, quantitative inputs and outputs. From the viewpoint of the engineer, a neural network in the most general case consists of a number of nonlinear, highly interconnected elements, each of which acts on the weighted sum of its inputs. This view is particularly attractive because of its biological plausibility. In either case, the PDP models have radically changed our perceptions of the mechanisms of learning and recall.

## 1.1 Goals, objectives and organization of this thesis:

This work concerns itself with the development of architectures and circuits for feedforward multi-layer neural networks. A hybrid architecture for this type of network will be presented. It will be shown that this architecture results in a decrease in the number of physical interconnections on the chip without any loss of generality. The multiplexing scheme used will also make possible multi-chip systems without a great number of connections. A complete set of cells for this architecture has been designed in a full custom CMOS VLSI technology.

The motivation for this work was a desire for a real-time solution for handwritten character recognition. However, all architectures and circuits presented in this thesis can be applied to any feed-forward network regardless of application. Multi-layer feed-forward networks have shown a great deal of promise as robust and reliable classifiers and it is in this capacity that they are used in the solution of the character recognition problem. A brief description of the character recognition problem is presented later as a typical application.

In chapter 1, the objectives of the thesis are defined, a brief overview of the history of research in neural models and implementation methods is presented, and some important points about neural networks are reviewed. The original form of the architecture is proposed and analyzed in chapter 2. In this scheme, the number of interconnections and multipliers is reduced considerably from a full implementation. Also, the problem of matching the units and scales in the network, and the I/O mode of the network and related issues, are discussed. A number of solutions to these problems and the advantages and drawbacks of each of them are presented.

In chapter 3, realizations of the two main building blocks, neuron and synapse, are introduced. Several variations of the neuron and also the issues pertinent in the design of the synapse will be discussed. In chapter 4, the other building blocks needed in the architecture are presented. These include a trans-impedance amplifier, a voltage to current converter, and a series of high-power output buffers with low silicon area consumption. A suggestion for efficient address generation for the ROM and demultiplexers is given in section 4.3.

In chapter 5, the effects of quantization and truncation of the weights on two examples are investigated. Finally, in chapter 6, conclusions about this work of research are presented and some areas of promise for future work are pointed out.

## 1.2 A Brief history of research in neural models:

The history of research on nervous systems goes as far back as the discovery of the electrical nature of nervous transmission by Galvani, and the early experiments of Helmholz. Significant advances in the area of nervous modeling, however, had to wait until late nineteenth century. At this time, cognitive psychologists like James [5] outlined the fundamental concepts of nervous activity that are still in use today.

The famous paper of McCulloch and Pitts [6] in 1943 is usually cited as the beginning of serious work on neural modeling. They showed that a neural-like network of linear threshold elements can compute any logical function. Actually, the impact of this paper on computer science was much more pronounced than on neural networks [7-8]. In 1949, Donald Hebb published his epoch making work [9], explicitly stating the correlation update law that James had only hinted at half a century ago. Frank Rosenblatt [10] proposed the first computationally oriented network and also devised the perceptron convergence procedure. Widrow and Hoff [11] with their ADALINE (1960) helped bring adaptive systems and neural networks together; and also attracted the interest of electrical engineers to this relatively young subject.

At this time, it was clear that a dichotomy in the understanding of the brain function was forming. One group, inspired by Rosenblatt, believed in the power of the perceptron and in general considered a connectionist architecture essential to the types of behavior observed in human learning and recall processes. In other words, this group regarded as important not only *what* the brain does, but also *how* it is done. The other group attached no great importance to the internal mechanisms of the nervous system; they were mostly in favour of serial symbol processing. The area of artificial intelligence as we know it today is a reflection of the beliefs of this second group.

In 1960, Minsky and Papert published their famous book, *Perceptrons* [12]. This book is a brilliant mathematical analysis of the limitations of networks consisting of a single layer of linear threshold units. The only mistake of the authors, if it may be called so, is that they went a step further and surmised that these limitations extend to the general multi-layer and non-linear case. A thing that most people accepted at the time - and just happens not to be true. This misconception resulted in a considerable slackening of the pace of research in neural networks for the next two decades.

Between this time and the late 1970's, when a new interest in neural networks was aroused, the works of Kohonen in correlation matrix memories [13] and Grossberg in mathematical modeling [14] were most prominent.

The 1980's saw a renaissance of neural networks. Some of the interesting developments in this period include; studies in letter perception [1-2], Hopfield networks [15-16], Self-organized networks [17-19], Neocognitron [20-23], Bolzmann machines [24], and last but far from least, the back error propagation learning algorithm [25-28]. The topic continues to be of great interest and has attracted researchers from various areas of science and engineering.

## 1.3 Some major points on nervous system and neural models:

There are a number of characteristics of the brain [29] that are best taken into account when either forming models for cognitive processes or pursuing the engineering design of a hardware implementation of these models. Most of these points have had a deciding influence on the way the architectures and circuits in this thesis were developed.

- Neurons are slow: Much slower than conventional computing components. The speed of most operations in modern computers is in the order of nanoseconds, whereas in the neurons it is four orders of magnitude slower. This is the basis of the so-called "100-step program" [30], meaning that most useful operations in the brain have to be performed in less than 100 serial steps. Evidently, this points to massive parallelism in the brain.

- 2. There are a large number of neurons: The number of neurons in the brain is estimated at 10<sup>10</sup> to 10<sup>11</sup>.

- 3. Neurons receive inputs from a large number of neurons: The number of inputs to each neuron can be between 1000 to 100,000.

- 4. Neurons communicate by activation and inhibition: The information flowing in the nervous system is quantitative, i.e. signed numbers of limited precision and range.

- 5. Information is continuously available: There is no appreciable decision phase during which a unit provides no response. Alternatively, it can be said that the system is asynchronous.

- 6. Graceful degradation with damage and information overload: Partial damage to the nervous system, in the form of disconnection of a few neurons, does not cause a

breakdown of the whole system or even the specific function. Neither does information overflow result in irreparable loss of information.

7. *Distributed control:* All processes are local. There is no central executive overseeing the general flow of information.

#### **1.4 Implementation of neural networks:**

Mathematical modeling and the work of such people as Grossberg and Hebb was fundamental in the development of neural networks. It was only after the advent of the digital computer and availability of numerical simulation, however, that investigators of nervous system and behavioral psychology could actually evaluate the performance of their models in any accuracy or detail. One of the first attempts in this direction was made by Farley and Clark in 1954 [31]. Others soon followed.

Among the more sophisticated software implementations is the Neocognitron by Fukushima [20-23]. This was a multi-layer neural network with 9 layers. Four different types of neural units were used and the learning was supervised. The network was trained to recognize handwritten characters regardless of size and position.

Another successful example in software implementation of neural networks was the NETTALK, a network that learned how to read. This feed-forward, 3-layer network was developed in 1986 by Sejnowsky and Rosenberg [32]. Bolzmann machine and back propagation learning rules were both applied with comparable results, the difference being that back propagation was faster in learning. After 12 CPU hours on a DEC VAX, it was able to produce phonemes from the training set which were correct 95% of the time.

It is generally not very difficult to simulate a known network on a digital computer. The amount of time needed to run such a program, however, can be immense. This stems from modeling a highly interconnected parallel system with serial hardware. Implementation of neural networks with special purpose hardware has been addressed many times during the past 3 decades. Probably the first attempt at making a learning machine was made by Marvin Minsky in 1951. This machine, made at Harvard, had a memory consisting of 40 control knobs, which were moved by a single motor through electric clutches. It had some 300 tubes and in Minskey's own words [33] was never thoroughly debugged, but worked nonetheless (robustness).

Rosenblatt established himself as one of the pioneers of this area in early 1960's when he and his colleagues in Cornell University built a "Mark I" perceptron with 400 photoreceptive sensors on a 20x20 array. This perceptron had 152 associative units and 8 binary response units for the final classification. Each sensory unit had up to 40 random connections to the associator units. Some importan: results from this machine appeared in a later paper by Block [34].

The major problem in the realization of neural networks is the sheer amount of hardware necessary to implement even the simplest of functions. In recent years, a great deal of interest has been aroused in optoelectronic hardware as a means of implementing neural networks. The Hopfield network and the linear associator are among the networks successfully implemented using this method [35-36]. Optoelectronics is well suited to neural networks. Optical systems are fully parallel and allow a high degree of interconnection, because crossing light beams do not interfere. Also, a large number of active elements can be implemented with comparative ease, since optical devices like lenses and gratings can operate on a number of light beams simultaneously, without increasing the complexity. Mixing optics with electronics combines the best of two worlds: massive

parallelism of optics and flexibility, high gain and decision making properties of electronics. It seems more attractive to form analog neural hardware by completely optical means. However, in the absence of fully optical decision making devices (e.g. sensitive optical bistable devices) the capabilities of the optoelectronic approach remain very attractive [37].

#### **1.5 VLSI implementations:**

VLSI is also a suitable medium for the implementation of neural networks. Neural networks typically contain a large number of similar, relatively simple units, which goes very well with VLSI. At the present time, the most successful semiconductor technology for computer logic and memory is digital CMOS. Other technologies cannot match the outstanding integration scale and low power dissipation of CMOS. Its only weakness is speed, and that is improving steadily. Because of the maturity of this technology, some attempts have been made to use it for the implementation of neural networks [38-39]. Among these are wafer scale designs [40], and those trying to achieve a similar mode of transmission as biological neural networks by using pulse stream arithmetic [41]. The advantages of the digital approach are:

- A) Design techniques are advanced, automated, and well understood.

- B) Programming of weights can be managed easily.

- C) Interchip communication and possible exchange of information with a host computer can be readily performed.

- D) Digital memories are relatively easy to build and the weight storage problem, from which analog implementations suffer, does not appear in the digital case.

On the other hand, neural networks are analog in nature and, intuitively, it seems that an analog implementation would be more suitable and elegant. One of the properties of neural networks is that they use signals that have limited precision and range, and their environment can be very noisy. Therefore, precision of variables and noise immunity, the most powerful aspects of digital systems, do not seem essential.

Also, many of the functions needed in the network may be approximated by a combination of a few semiconductor devices on a chip, making use of their characteristic curves. In a digital system, the implementation of a non-binary function usually necessitates a cumbersome lookup table approach. The number of interconnection wirings will also be much smaller in an analog system than in a parallel-bus digital version. Finally, digital multipliers occupy larger silicon areas than comparable analog multipliers.

Carver Mead [42-44] and others [45] have tried to apply analog CMOS to the simulation of biological neural networks, especially sensory organs and early processing elements. Some other works [46-47] have been directed to the development of networks and algorithms that are more compatible with the strengths and limitations of CMOS VLSI.

Before any practical engineering application of analog neural networks can be realized, the problem of weight storage has to be addressed. Almost all of the information in a neural network is stored in the connection weights, and to store these analog values is by no means trivial. At present, no reliable nonvolatile analog memory is available, and the choices are more or less limited to the following:

A) Programmable threshold devices, i.e. floating gate and metal-nitride-oxidesemiconductor (MNOS) devices [48]. The attractiveness of nonvolatile storage on these devices is reduced by the difficulty in making small weight changes [49], limitation to a finite number of WRITE cycles, and inaccessibility of the technology [50]. In neural networks, unlike conventional EEPROMs, a large number of bits have to be written at the same time. This makes the WRITE circuitry even more complex. Also, the aging problems of floating gate and especially MNOS devices have yet to be resolved.

- B) Dynamic analog storage on a node or a MOS capacitor. Storage on a node can be useful for the purpose of demonstrating the feasibility of an algorithm, or when the system is adapting constantly. Experiments on this method [51] have shown that by cooling the chip down to cryogenic temperature, weights can be maintained for hours. Dynamic storage on MOS capacitors can be attractive once some compromises are made in terms of layout area and environmental requirements of the circuit [50] (to reduce the effect of leakage mechanisms). If the capacitors are large enough, and a reasonable control over the temperature is maintained, leakage can be reduced to a level low enough so that analog refresh from digital memory using conventional D/A techniques will be possible.

- C) Multi-level storage on a capacitor [52]. In this method, the capacitor holding the analog value is allowed to take any of a set of U discrete voltages, which are usually equally spaced. If  $U_{i-1}$  and  $U_i$  are the elements of U, such that  $U_{i-1} < V_{C0} < U_i$ , then the system sets the voltage  $V_C$  to  $U_i$ . Once  $V_C=U_i$ , it remains locked at that value by regular refreshes.

- D) Hybrid solutions by digital storage of weights. In this method, multiplying digital to analog converters (MDAC) are used to perform synaptic multiplications. This has the advantage of reliability and permanent preservation of weights without any great compromise. The drawback of this approach is the limited number of bits in dynamic range, which stems from mismatching of the devices on the chip. This will have an adverse effect on the convergence of most of the learning algorithms.

This method is ideal for applications where constant adaption is unnecessary. It will be shown later that fairly complex recall problems can be solved with as little as 8 bits of precision (including the sign bit).

## 1.6 Handwritten character recognition and feed-forward networks:

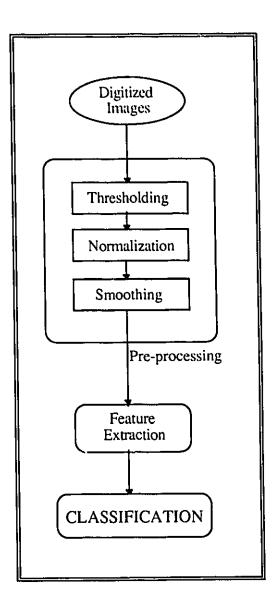

Handwritten character recognition is an engineering problem with applications in such diverse areas as postal services and banking. Most of the character recognition problems follow the solution flow as described below [53]. Each of these steps may be performed in a number of different ways.

The raw data is usually in the form of digitized images, with multiple gray levels. This image goes through a preprocessing stage which consists of thresholding, normalization, and smoothing, not necessarily in that order. Thresholding reduces the multiple gray level image to a binary image, easier to handle for the later stages of the process. Normalization brings all the data samples to the same size so that differences in size will not affect the final decision on character type. Smoothing will add or subtract some dark pixels in the image so as to remove the roughness of the edges of the characters. This is actually analogous to a form of integration and serves to reduce spurious, useless data in the image.

The next step is feature extraction. The binary image at this point still contains a huge amount of information. In a typical 512x512 binary image, this amounts to 262,144 bits. If all this information is used, it will lead to over-classification. Insignificant and/or unimportant differences in bit patterns may cause two different images of the same character to be recognized as different characters, or result in other undesirable effects. Extraction of

features reduces the data to a manageable size and retains only those fragments of information that are most necessary and helpful in classification.

In the last stage, the features of the particular image are compared to the features of one or more known images from a "training set", and a decision is arrived at as to the type of the character. In the statistical classifiers like nnearest-neighbor and its variants, a number of distance measures from the present features to the features of the training set are computed and used as a criterion in decision making. In feedforward neural networks, the features fed at the input are changed to an internal representation [54] at the hidden layer(s) and the answer appears at the output. The information content of the training set is distributed throughout the network in the form of connection strengths and no explicit comparison takes place. Neural networks can compete very well with the traditional classifiers.

Figure 1.1: Character Recognition

Although it would be very attractive and elegant to perform the recognition without feature extraction, i.e. directly from the visual data, attempts in this direction have been unable to produce recognition rates acceptable for practical applications [55]. Also, it is worth mentioning that the feature extraction approach has some merit in the way of being nearer to what happens in nature. It has been shown that many preprocessing actions take place in the early vision system, including, for instance, edge extraction [56].

#### 1.7 Summary:

The objective of this thesis, in the next few chapters, is to introduce an architecture for feed-forward neural networks. This type of network is very suitable for classification and can be used in applications such as pattern recognition. In this architecture, the synaptic weights are stored in a digital memory structure and a multiplexing scheme is used to reduce the number of physical interconnections. In this chapter, a general overview of neural networks and some historically significant research efforts in modelling and implementation of these networks were presented. Some important points about neural models were given and, as the context of this work, a general flow of the solution to character recognition problem was outlined.

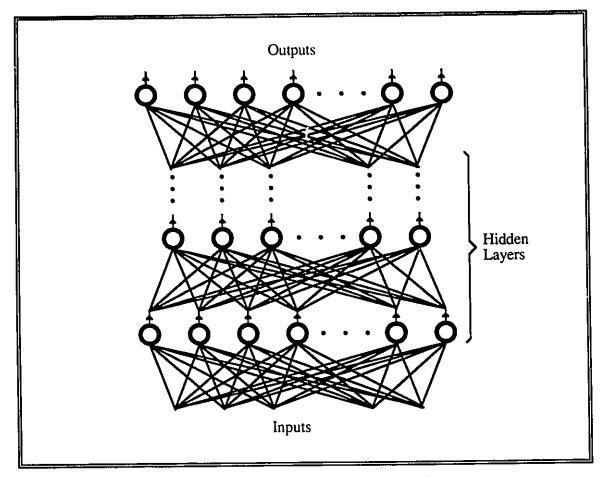

## An Architecture for Multi-layer Neural Networks

Multi-layer networks are a popular and important subclass of neural networks. Because of their simple dynamics, which stems from a lack of feedback paths, these networks are inherently stable. Also, the existence of powerful learning and adaptation algorithms for these networks makes them even more attractive from an engineering point of view. Supervised learning schemes on feed-forward multi-layer networks, such as back error propagation, are particularly attractive for applications such as pattern and speech recognition, waveform classification, etc.

Analog VLSI is a promising vehicle for the implementation of these networks. Large scale integration makes it possible to put many electronic elements on a semiconductor chip with better reliability and lower cost. VLSI fabrication is particularly compatible with designs with a large number of similar and simple elements; a central characteristic of neural networks. However, another inherent property of neural networks, high interconnectivity, has proven to be one of the major obstacles in the way of hardware implementation of large networks. It has been known for some time that the interconnections limit the size of

neural networks on chips. Analog technology has the advantage that the maximum information capacity of a single line is only limited by noise and other uncertainties<sup>1</sup>. When the signals are represented digitally and transmitted in parallel, each activation or node value needs several wires for interconnection, whereas one wire suffices in an analog system.

Figure 2.1: Multi-layer feed-forward network

In the design of analog neural networks, one of the most difficult issues is the storage of synaptic weights. Although some studies have been made in this area, a reliable, compact analog memory in CMOS technology, that can preserve data with acceptable accuracy for

<sup>1</sup> In the strict sense, the bandwidth should be included in any information analysis. Here, however, we only refer to the information content at a given point in time based on the allowable levels on a line.

long periods of time, is not available. As indicated in chapter 1, a number of analog memory designs have been presented in the literature. Furman and Abidi [51] presented a design for a feed forward network with back error propagation. The weights are stored as charges on small capacitors on the nodes, and can be preserved for hours by keeping the chip at cryogenic temperatures. Borgstrom, Ismail and Bibyk [48] presented a circuit technique involving floating gate MOS transistors. The weights are stored as charges in the floating gates. Schwartz, Howard and Hubbard [50] introduced a circuit utilizing dynamic charge storage on MOS capacitors. The weights can be preserved on the order of seconds. Some other designs [57-60] are also present in the literature.

All these methods present problems that make the design of a practical network, with suitable size for solving practical problems, very difficult. A realistic engineering design has to have at least tens of neurons on a chip, work in normal temperatures, and preserve connection strengths during the operation of the system. This necessitates a certain degree of efficiency in the utilization of chip real estate. The designs that use dynamic charge storage on capacitors have to use up large areas for the capacitive elements to ensure a reliable preservation of weights at different temperatures. Multilevel storage on capacitors involves a considerable amount of overhead in circuitry to keep the capacitors at the locked voltages. Floating gate memories show large variations in transistor characteristics and need large voltages on the chip for programming.

Digital weight storage has been addressed by Raffel et al. [61] and others. This is the method chosen for the architecture presented in this thesis. The most general form of multilayer networks, without feedback, is implemented (figure 2.1). Most of the functions are realized in analog current mode circuitry, which eliminates the need for adder hardware.

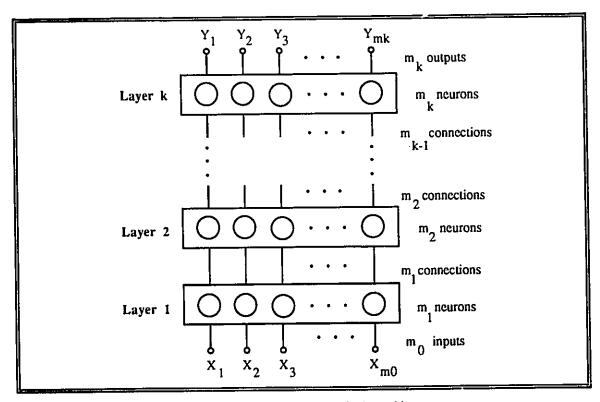

#### 2.1 The architecture:

The general form of the architecture is shown in figure 2.2. Each of the layers has a structure similar to that shown in figure 2.3. Here, we define a stage as a layer of neurons and their corresponding connection strengths. Each set of connection strengths is associated with the neurons of the next layer, instead of those of the preceding layer. Therefore, each of these stages consists of the neurons at that layer plus all the connection strengths from the previous layer. In this way, the number of physical interconnections between any two stages i and i+1 are reduced to the number of neurons in stage i (figure 2.2). This possibility should be apparent intuitively: once the weights are fixed, the amount of information passed to a layer does not exceed the information present at the output of the preceding layer, and the minimum number of lines needed to carry this information is no more than m<sub>i</sub>.

Figure 2.2: Layers and stages in the architecture

With this setup, a multi-chip system can also be considered. In such a system, each of the stages would be implemented on a separate chip. In other schemes, this has to be avoided because of the high number of interconnections. In this architecture, interstage wiring has been dramatically reduced and much larger systems can be designed using a number of chips, each of which constitutes one stage of the network. This can also lead to a semicustom approach to the design of these networks, where only one generic chip containing one stage is designed. This chip will contain the maximum number of neurons possible in the technology in use (e.g.  $3 \mu$  or  $1.2 \mu$  CMOS). It will also provide the maximum number of interconnections to another stage with the same number of neurons. The user can order these chips and program his/her own network. If the number of neurons in any stage is greater than needed, they can be masked out by assigning zero to the incoming weights.

Figure 2.3: Internal structure of one stage

The central idea in this scheme (figure 2.3) is an imbedded multiplexing of the connection strengths. This is possible because the bandwidth of the analog signals in the network is, or can be made, much smaller than the clocking frequencies available in digital CMOS. The feed-forward networks that we consider do not have feedback. Therefore, the delays introduced by multiplexing do not disrupt the network dynamics and only increase the time latency. The most important constraint is that the analog nodes should be refreshed in time so that the output of the neurons are kept valid at all times. The minimum clocking speed depends on the leakage of the nodes, itself dependent on temperature, and is no more than a few hundred KHz; quite practical.

Currently, the value of the weights is stored in a mask-programmed static ROM. Eventually, this can be changed to a PROM or EPROM for field programmability and easy customizing. They can also be stored in a RAM for a programmable version.

#### 2.2 Operation:

The ROM storage, at the logical level, can be considered as an  $(m_{i-1} + 1) \times m_i$  two dimensional array. The counter is reset after each  $m_i$  clock cycles. Suppose that at an arbitrary point in time, the output of the counter is equal to j,  $0 \le j \le m_i - 1$ . The jth column of the ROM is fed to the digital inputs of the multiplier array. The multipliers are current mode multiplying digital to analog converters with the multiplier in digital form and the multiplicand in analog (current mode) form.

At the same time, the output node values of stage i-1, in the form of current, are available at the analog inputs of the multipliers. The weighted current mode outputs are added on a node, and the result of this addition is converted to voltage by a trans-impedance amplifier (figure 2.4). This value is then passed to the jth neuron by a demultiplexer, and the activity of this neuron forms one element of the input of the next stage. The input nodes of the neurons have capacitances that hold the value of their input until the next demultiplexing cycle.

Figure 2.4: The adder

Each of the neurons has two inputs: post-synaptic activation and threshold value. The threshold of the neurons can be considered as a negative signal coming from a source with a strength of unity and a weight equal to the threshold value. One row of the storage is allocated to the threshold values and the signal is distributed using the same demultiplexing method described above. The input of the first  $m_{i-1}$  multipliers are summed and fed to a demultiplexer. The output of the multiplier  $(m_{i-1}+1)$ , which represents the threshold, is input to the other demultiplexer. At each clock cycle, the two demultiplexers forward these signals to the inputs of one neuron, providing the refresh of both the activation and threshold at the same time. In order to avoid mismatching, the current source shown in figure 2.3 is actually another neuron with signal and bias inputs connected to  $V_{DD}$  and ground respectively.

This multiplexing scheme enables the reduction of the number of multipliers in each stage from  $(m_{i-1} + 1) \times m_i$  to  $m_{i-1}+1$ . The same reduction factor holds for the interconnections between layers.

As always, there is a price to be paid for convenience. The settling time of the network is the factor that is adversely affected when going from a full implementation to one with multiplexing. In the worst case, where all connection strengths are non-zero and all inputs to all neurons change at a point in time, the settling time will be:

$$\Gamma = \sum_{i=1}^{K} \frac{n_i}{f}$$

(2.1)

Where:

T = Total settling time

K = Number of layers

$n_i =$ Number of neurons in stage i

f = Clocking frequency

In a typical application for handwritten character recognition, a network with the following specifications was designed and trained with the back error propagation algorithm:

| Number of active layers | 3          |

|-------------------------|------------|

| Number of inputs        | 36         |

| Number of neurons       | 20, 15, 10 |

Setting the clocking frequency to 6MHz, the settling time will be equal to 7.5 microseconds. During this time, 3195 multiplications are performed, which translates to  $426 \times 10^6$  multiplications per second.

### 2.3 Modifications:

In the original form, the neurons have two inputs each; post-synaptic activation and threshold. This is similar to the structure of the nervous system, where the threshold is the property of individual neurons and is applied locally. A more effective and accurate approach, however, is also possible, as shown in figure 2.5.

Figure 2.5: Modified architecture

The variable threshold neuron of the original structure makes use of a differential pair of MOS transistors at its input stage; this will be discussed in greater detail in later chapters. The transfer characteristics of this neuron, as a function of (v1-v2), is not the same over a large range of v2 (figures 3.3 through 3.5). In other words, the characteristics of the neuron changes at different threshold values. This undesirable effect can be prevented by transferring the subtraction performed in thresholding back to the adder node. In this

approach, neurons will have only one input each, and the threshold values will be internally fixed to zero. The thresholds are added, with a negative sign, to the post-synaptic activations. This modification not only results in uniform transfer characteristics and a linear subtraction by current mode circuits on a node, but also saves some hardware. By a comparison of figures 2.3 and 2.5, it is seen that a trans-impedance amplifier, a demultiplexer, and a considerable amount of wiring at the input of the neurons have been eliminated.

Figure 2.6: Second modification for further improvement

Another set of changes that would improve the performance are shown in figure 2.6. At the output of the ROM array, a series of static buffers are added. The objective is to reduce the length of bit lines to a minimum so that cell and pullup transistors in the ROM have a smaller load capacitance to charge and discharge, hence an acceleration of the response of the ROM. This will allow greater settling time for the rest of the circuit.

An inhibit signal and a switching circuit are also added before the neurons. Because of the finite settling time of the multipliers and specifically the trans-impedance amplifier inside the adder block, the signals at the output of the demultiplexer are not stable at the time the address becomes available. If this inhibition circuitry is not provided, the capacitors at the input nodes of the neurons will receive erroneous charging voltages at the beginning of each refresh cycle. The corresponding voltage spikes in the signals effectively increase the settling time. This will be discussed in greater detail later in the thesis.

### 2.4 Units and scales:

The transfer characteristic generally preferred for the neuron is sigmoidal (S-like). The feed-forward model for the back-error propagation learning algorithm is usually associated with a version of the sigmoid; the so-called logistics function:

$$f(net) = \frac{1}{1 + e^{-net}}$$

(2.2)

The transfer characteristic of the physical circuit representing the neuron can be approximated with:

$$I_{out} = \frac{A}{1 + e^{-net/B}}$$

(2.3)

The range of the connection weights also has to be fixed. This range clearly depends on the application. Suppose that the choice is made and the largest weight to be represented is W. Also, suppose that the designed multiplying D/A will deliver an output current of K times its input current when all the bits are set to 1, i.e. the largest connection strength W will result in a multiplication by K. The transfer characteristic of the trans-impedance amplifier can be expressed in terms of the amplification factor R, i.e. the slope of the transfer characteristic at the linear region.

Having the four parameters A, B, W, K and R, the mapping relation can be expressed as follows: The unit value of the post-synaptic activation is clearly B volts. The other parameters have to be adjusted so that an activation of strength unity at the output of a stage, namely A amps, multiplied by a connection strength of unity and passed through the trans-impedance amplifier will result in a post-synaptic activity of B. This means:

. .

$$A \frac{K}{W} R = B$$

(2.4)

The choice of B is limited by the power supply voltages and the desire to have as much resolution within this potential difference as possible. K is determined by VLSI layout considerations (in our case is 2), and W is determined by the application. A and R can be used to balance the equation.

### 2.5 Input/Output considerations:

In each of the stages defined above, the input and output signals are in current mode (figures 2.3, 2.5 and 2.6). Although this does not create any problems inside the chip, it is preferable that the I/O communication is performed in voltage mode. The current levels are in the microamp range and would be severely affected by the noise that can be coupled to the relatively long connection wires to the chip package. A possible remedy to this problem

is the use of current mode output buffers, but the design of these buffers is very difficult<sup>1</sup>. Also, current mode circuits have high input and output impedances. High impedance nodes, especially outside the chip, are susceptible to voltage noise spikes of large amplitude, which will take the current mode circuits to saturation if the voltage of the node goes beyond the power supply voltage.

To change the signals at the I/O of the chip to voltage mode, a trans-impedance amplifier at the input and a voltage to current converter at the output may be used (figure 2.7). The voltage to current converter and the trans-impedance amplifier are designed so that their combined transfer characteristic has a slope of unity. The magnitude of the current mode outputs should also be taken into account when these two blocks are designed, so that none of them will be driven into a nonlinear zone in the normal course of the operation of the network.

Figure 2.7: Conversion of the signal mode at input and output

<sup>&</sup>lt;sup>1</sup> Generally, feedback is needed to insure the linearity of a buffer. In this case, the appropriate feed back would be current-parallel, which needs linear resistors, almost impossible to make in CMOS. Stability would also be a problem.

At the output, another variation is possible which saves some silicon area. Voltage mode neural blocks <sup>1</sup> can replace the current mode neurons and the trans-impedance amplifiers at the last stage. This approach has an additional advantage: Feedback is used in trans-impedance amplifiers to achieve linear, stabilized I-V characteristics. Feedback, however, also results in performance degradation in the network dynamics. Most of the propagation delay of the network is due to the settling time of the trans-impedance amplifiers. By eliminating these extra amplifiers, the total network delay can be reduced.

There is a disadvantage associated with the incorporation of the voltage mode neuron into the network. The transfer characteristic of the voltage mode neuron is slightly different from the current mode neuron and is almost linear <sup>1</sup>. This small error may sometimes not be acceptable and the choice of one solution or another will depend on the particular application.

Figure 2.8: Second solution to the I/O problem

<sup>1</sup> Ref. to chapters 3 and 4 for complete description of this and other circuit blocks

In large multi-chip networks and in applications where absolute economy in silicon usage is necessary, another approach becomes attractive: Consider a case where the neurons of each stage are transferred to the next layer, i.e. neurons are located before the synaptic multipliers instead of after (figure 2.9). Since the input of the neurons are voltage mode, and the demultiplexer switches voltage signals, this new stage will have voltage mode inputs and outputs.

This end is achieved without using any extra blocks. The regularity of the architecture, however, is disrupted. In this modification, the first and last stages will be different from the structure of figure 2.9, because there are no neurons at the input of the overall network and there should be a layer of neurons at the output of the last stage. This scheme is therefore incompatible with the idea of a generic programmable chip for all stages, for at least three types of stages are now necessary: first, last and intermediate.

Figure 2.9: Changing the I/O mode by displacing the neurons

### 2.6 Performance analysis on an example:

It is well known that the XOR logic function and its generalized form, the parity function, are among the more difficult functions to implement on neural networks. This difficulty arises from the non-connected regions in the domain of these functions, which necessitate a separate internal representation of the data set. This function was implemented using the proposed architecture to show the validity and workability of the concepts.

The network consists of inputs, a hidden layer and an output layer. The 8 connection strengths and 4 threshold values are to be determined in the learning process. These values were iteratively computed using the back error propagation learning algorithm with the following vectors:

| <u> </u> | v | XOR | XNOR |

|----------|---|-----|------|

| 0        | 0 | 0   | 1    |

| 0        | I | 1   | 0    |

| 1        | 0 | 1   | 0    |

| 1        | 1 | 0   | 1    |

and the result of this training is shown in figure 2.10.

Figure 2.10: XOR and XNOR

The scales in the circuit can be determined in the following manner: The maximum level of synaptic strength and threshold value is set at W=8, and as mentioned before, K=2. The neurons have the following characteristics<sup>1</sup>:

Therefore:

$$A \frac{K}{W} R = B$$

$$R = \frac{B}{A}\frac{W}{K} = 60 \ K\Omega$$

To have voltage mode output, voltage mode neurons were used in the second stage (figures 2.11 and 2.13). Instead of voltage to current converters, two current mode neurons are used at the input. This is permissible because the test vectors are digital and the behavior of this block is unimportant between 0 and 1.

The circuit shown in figure 2.11 is the original architecture, i.e. without inhibition circuitry. Waveforms of the signals named in figure 2.11 are given in figure 2.12. Note the ringing on V1 and V2, the outputs of the trans-impedance amplifiers. There are also large spikes on M1, M2, L1, and L2, as explained in section 2.3. Despite spikes on the output signals, XOR and XNOR functions are clearly visible. Output transitions happen at most 4 data cycles - or, alternatively, 2 clock cycles<sup>2</sup> - after each input transition. The data is presented to the circuit with a frequency of 2MHz. This is a maximum, since even at this frequency, the outputs of the trans-impedance amplifiers are barely stable when the next data cycle arrives (fig 2.12).

<sup>&</sup>lt;sup>1</sup> Ref. chapter 3

<sup>&</sup>lt;sup>2</sup> Since there are only two memory addresses in each ROM section in this design, the Clock signal and its complement were used for selection and address decoders were avoided.

Figure 2.11: XOR-XNOR using the original architecture

Figure 2.12: (Continued below)

Figure 2.12: (Continued below)

Figure 2.12: Waveforms of the original architecture

Figure 2.13 shows the same example in the modified architecture of section 2.3. A modified circuit for the trans-impedance amplifier, with lower settling time, is used in this version. In order to show the improvements, the waveforms of the last stage are presented in figure 2.14. The clocking frequency is 2MHz, twice the previous case, and the Inhibit signal disconnects the switches around the transition of the clock.

Figure 2.13: XOR-XNOR with the modified architecture

Figure 2.14: (Continued below)

Figure 2.14: (Continued below)

Figure 2.14: Waveforms of the modified architecture

The spikes are still seen in the signals L1 and L2, but L11 and L22, the inputs of the voltage mode neurons, are smooth. Notice that V2 is settled down well before the next transition of the clock. The speed of the circuit can therefore be easily increased to 8 mega refreshes per second.

The waveforms presented in this section are the result of full-scale transistor level SPICE simulations. They serve to show the validity of concepts and to insure that the circuit

blocks work well when put together. The simulation and test results of the individual blocks will be presented in later chapters.

#### 2.7 Summary:

Analog CMOS, a promising technology for the implementation of neural networks, has been used as the basis of the architecture presented in this chapter. The main object in this design is to trade-off computation time for circuit complexity. The multiplexing scheme imbedded in the architecture allows the reduction of the number of synaptic multipliers and physical interconnections. This trade-off can be justified by the fact that biological neural networks are generally much slower than CMOS circuitry (point #1 in section 1.3), and yet have remarkable performance unparalleled by digital computers. It seems reasonable to trade the speed of CMOS for interconnection complexity, which is a major hindrance.

By making the architecture as regular as it is, and by reducing the wiring between stages, it becomes possible to have multi-chip networks. In this way, one of the constraints on the size of network is relaxed. These chips can all be similar and differ only in the ROM contents. A generic programmable chip containing one stage can be developed to facilitate the design of feed-forward networks and reduce the turn-around time in the development process.

The original architecture of figure 2.3 was composed with the assistance of ideas from biological neural networks. Some modifications were made afterwards to improve the overall performance and save silicon area. In all these versions, a relationship between the scales of the building blocks is necessary for the correct operation of the system. This relationship is summarized in the equation:

$$A \frac{K}{W} R = B$$

(2.7)

Examples with two versions of the introduced structure were presented in this chapter and the analysis of the waveforms demonstrated the necessity of the changes in the original version.

## Neuron and Synapse

### 3.1 Neuron:

In many neural net models, the transfer characteristic of the neuron is in the form of a sigmoidal (S-like) function. Beside being well behaved and continuously differentiable, it is a good approximation to the activation function of the biological neural cells. In feed-forward networks that rely on a variant of the steepest descent algorithm for learning, e.g. back error propagation, a specific type of sigmoid becomes very attractive:

$$f(x) = \frac{1}{1 + e^{-x}}$$

(3.1)

This function, sometimes called the logistics function, has the advantage that its derivative can be expressed in terms of itself and its shifted version. This is useful, since the derivative is used in the update law and is not always easy to compute.

$$f'(x) = f(x) f(1-x)$$

(3.2)

The transfer characteristics of the VLS1 neuron cells presented in this chapter are approximations to this function.

Figure 3.1: The sigmoidal logistics function

### 3.1.1 Current mode neurons:

The basic current mode neuron is shown in figure 3.2. This is a cell designed for the original architecture of figure 2.3. This cell has two inputs: activation and threshold. The S-like transfer characteristic is obtained through a MOS differential pair, as explained below. The node I<sub>out</sub> will be coupled to the input of the synapse.

The large signal characteristics of this circuit can be obtained analytically using a simplified model for the differential pair. Assume M5 to be an ideal current source, and M3 and M4 always to be in saturation. These assumptions are reasonable for the larger part of the operating region and illustrate the behavior even when the assumptions are not exactly valid. The simplified circuit is shown in figure 3.3.

The relationships describing the large signal behavior are [62]:

$$V_{\rm ID} = V_{\rm I} - V_{\rm 2} = \left(\frac{2I_{\rm D1}}{\beta}\right)^{0.5} - \left(\frac{2I_{\rm D2}}{\beta}\right)^{0.5}$$

(3.3)

and

$$l_{SS} = l_{D1} + l_{D2} \tag{3.4}$$

Where it has been assumed that M1 and M2 are matched. The solution for  $l_{D1}$  and  $l_{D2}$  is obtained by substituting (3.4) in (3.3) and forming a quadratic equation. There are four regions of operation. For  $V_{ID}^2 < -\frac{2I_{SS}}{\beta}$ :

$$I_{D1} = 0$$

$I_{D2} = I_{SS}$  (3.5)

For

$$-\frac{2I_{SS}}{\beta} < V_{ID}^2 < 0$$

:

$I_{D1} = \frac{I_{SS}}{2} - \frac{I_{SS}}{2} \left( \frac{\beta V_{ID}^2}{I_{SS}} - \frac{\beta^2 V_{ID}^4}{4I_{SS}^2} \right)^{0.5}$  (3.6)

$$I_{D2} = \frac{I_{SS}}{2} + \frac{I_{SS}}{2} \left( \frac{\beta V_{ID}^2}{I_{SS}} - \frac{\beta^2 V_{ID}^4}{4 I_{SS}^2} \right)^{0.5}$$

(3.7)

For

$$0 < V_{ID}^2 < \frac{2I_{SS}}{\beta}$$

:

$I_{D1} = \frac{I_{SS}}{2} + \frac{I_{SS}}{2} \left( \frac{\beta V_{ID}^2}{I_{SS}} - \frac{\beta^2 V_{ID}^4}{4I_{SS}^2} \right)^{0.5}$  (3.8)

$$I_{D2} = \frac{I_{SS}}{2} - \frac{I_{SS}}{2} \left( \frac{\beta V_{ID}^2}{I_{SS}} - \frac{\beta^2 V_{ID}^4}{4I_{SS}^2} \right)^{0.5}$$

(3.9)

And for

$$\frac{2I_{SS}}{\beta} < V_{ID}^2$$

:

$I_{D1} = I_{SS}$   $I_{D2} = 0$  (3.10)

The transfer characteristic of the differential pair in the normalized form  $(I_{SS}=1, \beta=1)$  is given in figure 3.3. The shape of this curve is a good approximation to the sigmoid function of figure 3.1. Simulation of the neuron cell with SPICE results in the characteristic given in figure 3.4. Test results of the same cell fabricated with the Northerm Telecom<sup>TM</sup> 3µm double-metal single-polysilicon technology are presented in figure 3.5.

Figure 3.6: Current mode neural cell with fixed threshold

For the modified form of the architecture as shown in figure 2.5 and 2.6, a neural cell with only an activation input and no threshold input is needed. This cell is given in figure 3.6. The transistors M1 and M2 have W/L ratios so that the drain of these two transistors is at 0V. This cell is the same as that of figure 3.2 with the difference that the gate of M3 is connected to the gates of M1, M2 and M5, and the capacitor C2 is eliminated.

The capacitors in both of the cells serve to reduce the voltage drop of the input nodes of these cells in the time between two refresh cycles. Charge leakage in capacitive nodes has two main components: through capacitive oxide and through the reverse biased junction of the transistor(s) charging the node. The first component is proportional to the oxide area and cannot be reduced by increasing the capacitance. The second mode depends only on the voltage of the node and the width of the charging transistor. Since the second mode is dominant in normal temperatures, an increase in the capacitance of the node will result in a lower voltage drop between refresh cycles.

### 3.1.2: Voltage mode neurons:

Voltage mode neurons (figures 3.7 and 3.8) are designed by subtracting a constant current from the drain current of M4 and feeding the result to a resistive MOS pair (M9 and M10). The transfer characteristics of this neuron is given in figure 3.9.

Figure 3.9: Transfer Characteristics of the voltage mode neuron (Simulation)

| Current Mode | Current Mode Neurons (µm) |       | Voltage Mode Neurons (µm) |  |  |

|--------------|---------------------------|-------|---------------------------|--|--|

| M1           | 5.4/5.4                   | MI    | 5.4/5.4                   |  |  |

| M2           | 5.4/9.6                   | M2    | 5.4/9.6                   |  |  |

| M3-M4        | 5.4/9.6                   | M3-M4 | 5.4/9.6                   |  |  |

| M5           | 5.4/10.2                  | M5    | 5.4/10.2                  |  |  |

| M6-M7        | 6/3                       | M6    | 6/3                       |  |  |

| M8-M9        | 6/3                       | M7    | 18.6/3                    |  |  |

| Capa         | Capacitors                |       | 3/4.2                     |  |  |

| C1           | 0.433 pF                  | м9    | 6/9                       |  |  |

| C2           | 0.519 pF                  | M10   | 3/15                      |  |  |

Table 3.1: Transistor geometries of the neural cells

Note that in the present form, the voltage mode neuron is only suitable for a final stage in the network. To be used in the intermediate stages, as proposed in section 2.5 and shown in figure 2.8, the cell has to be modified to have a minimum output activation of zero. Removal of transistor M8 would result in a minimum output of zero, since the M9-M10 pair is matched. The transistor geometries for the 4 neural cells presented so far are given in table 3.1.

### 3.2 Synapse:

By definition, the synapse is a junction between two neurons. Almost all of the information in a neural system is stored in the synapses. Some methods of designing a synapse in analog CMOS were described in section 1.5. Below we present a hybrid realization with current mode multiplying D/A converters and digital ROM for storage of pre-trained connection weights.

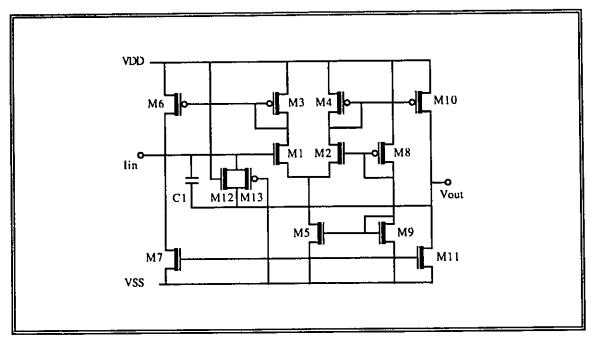

### 3.2.1 Multiplier:

Current mode digital to analog converters are constructed with a series of current mirrors, each dividing the current in half, and a series of switches that forward these currents to an addition node. The main criteria in the choice of the current mirrors are:

- a) High small signal output resistance

- b) Low minimum operating voltage for wider operational range