#### University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

1991

## The development and application of high-speed digital switching trees for regular arithmetic arrays.

Lino. Del Pup University of Windsor

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### Recommended Citation

Del Pup, Lino., "The development and application of high-speed digital switching trees for regular arithmetic arrays." (1991). *Electronic Theses and Dissertations*. Paper 3824.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

#### THE DEVELOPMENT AND APPLICATION OF HIGH-SPEED DIGITAL SWITCHING TREES FOR REGULAR ARITHMETIC ARRAYS

by

Lino Del Pup

# Submitted to the Faculty of Graduate Studies through the Department of Electrical Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the

A Thesis

University of Windsor

Windsor, Ontario August, 1991

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Oltawa, Canada K1A 0N4

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-69891-8

Lino Del Pup 1991

© All Rights Reserved

#### ABSTRACT

This work represents the author's contributions to a joint effort into the development of switching tree architectures. The work concentrates on concepts of CMOS design and lay-out stressing the optimization of parasitic and interconnect capacitance to increase circuit performance. Practical design techniques are discussed with regards to constructing pad frames and power distribution networks. These concepts are then applied to a set of three cells which trace the development of the switching tree cell. The clocking schemes, ROM architectures and general structure of each cell are discussed in detail. Finally, a set of standard cells is constructed using the switching tree structure, in 3µ CMOS technology. SPICE simulations indicate that cells performing 3-bit binary addition in one clock cycle are capable of functioning at clock speeds of up to 50 Mhz. Test results confirm the functionality of the cells up to the maximum speed of the Input/Output (I/O) pads, which is approximately 40 Mhz. Due to current I/O pad speed limitations, a set of ECL Compatible I/O pads is developed for use as part of the standard cell library. Simulation results indicate that the pads are capable of operating at speeds above 100 Mhz. Test results confirm the pads operation up to 65 Mhz, which is the maximum speed available from the test equipment. Based on the test results, it is estimated that the maximum speed of the  $3\mu$  ECL Compatible I/O pads is approximately 80 Mhz.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere thanks and appreciation to Dr. G. A. Jullien and Dr. W. C. Miller for their tremendous support and guidance throughout the progress of this thesis. Much thanks must also be given to my good friend and working partner Roger Grondin. In addition, I would also like to thank Mr. J. Novosad and Mr. A. Johns for many favours rendered. Thanks must also go to Jane Bailey for her support and patience during the writing process. Last but far from least, I would like to thank my parents, Mr. & Mrs. Achille and Edda Del Pup, for without them none of this would be possible.

#### TABLE OF CONTENTS

| ABSTRACT   | •          |                                     | iv    |

|------------|------------|-------------------------------------|-------|

| ACKNOWL    | EDGEME     | ENTS                                | v     |

| LIST OF FI | GURES      |                                     | x     |

| LIST OF TA | BLES       |                                     | xviii |

| CHAPTER    | 1          |                                     |       |

| Intro      | duction    |                                     | 1     |

| 1.1        | Introduct  | ion                                 | 1     |

| 1.2        | Thesis O   | rganization                         | 8     |

| CHAPTER    | 2          |                                     |       |

| The        | Art of Des | sign                                | 10    |

| 2.1        | Introduc   | tion                                | 10    |

| 2.2        | Dealing    | with Circuit Capacitance            | 11    |

|            | 2.2.1      | Circuit Modelling for Proper Design | 13    |

|            | 2.2.2      | Parameterizing a Circuit Block      | 15    |

|            | 2.2.3      | Summary of Modelling                | 25    |

| 2.3        | Differen   | t Transistor Configurations         | 26    |

|            | 2.3.1      | The Basic Transistor Layout         | 26    |

|            | 2.3.2      | Parallel Devices with Merged Drains | 27    |

|            | 2.3.3      | Doughnut Devices                    | 30    |

| 2.4        | Practica   | l Layout Considerations             | 31    |

|            | 2.4.1      | Generating Pad Frames               | 31    |

|         | 2.4.2      | Power Distribution                        | 33 |

|---------|------------|-------------------------------------------|----|

|         | 2.4.3      | Routing                                   | 36 |

| 2.5     | Summar     | у                                         | 37 |

| CHAPTER | .3         |                                           |    |

| The     | : Developn | nent of Switching Trees                   | 39 |

| 3.1     | Introduc   | tion                                      | 39 |

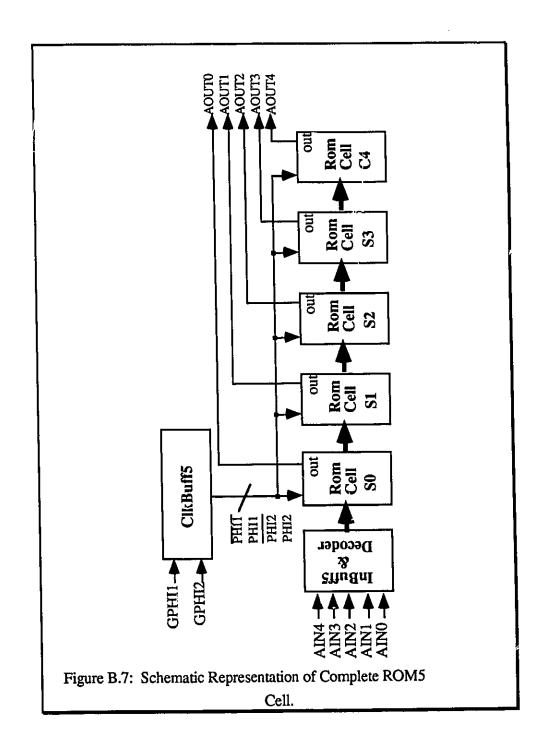

| 3.2     | The ROI    | M5 Cell                                   | 40 |

|         | 3.2.1      | The Clocking Strategy                     | 41 |

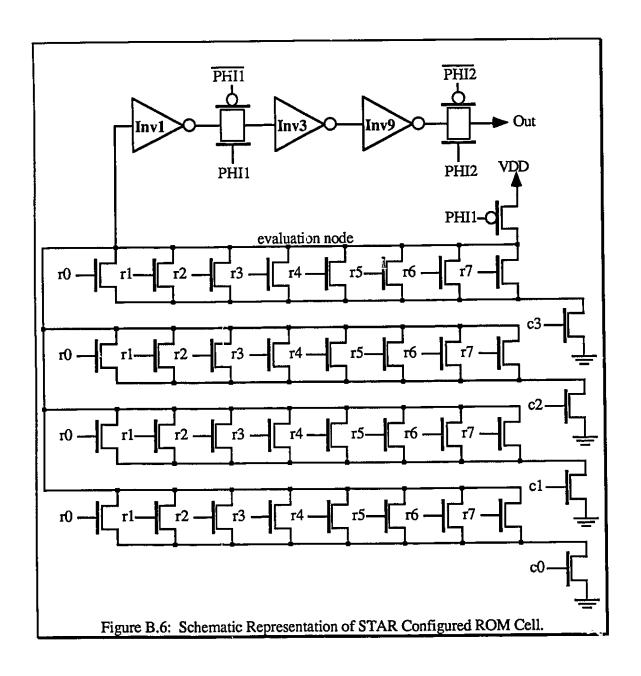

|         | 3.2.2      | The Star Configured ROM                   | 42 |

|         | 3.2.3      | Test Results of The IC3WROMB Chip         | 48 |

|         | 3.2.4      | Summary of ROM5 Design                    | 49 |

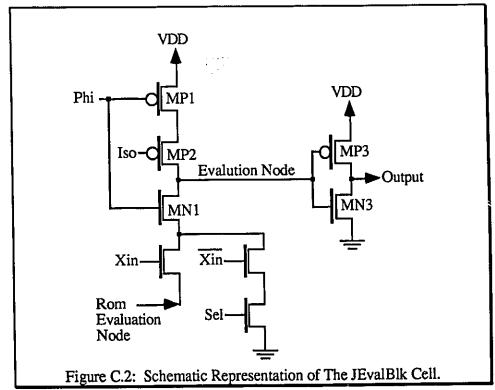

| 3.3     | The JRC    | OM Celi                                   | 50 |

|         | 3.3.1      | The Binary ROM Cell                       | 50 |

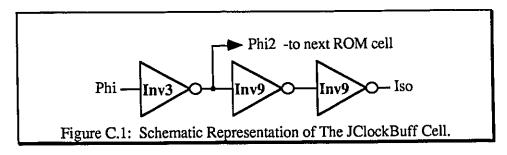

|         | 3.3.2      | The New Clocking Strategy, JClock         | 54 |

|         | 3.3.3      | Test Results of IC3WRRJT, WRXLT, WRJET    | 57 |

|         | 3.3.4      | Summary of The JROM Design                | 60 |

| 3.4     | 4 The Sw   | itching Tree Cell                         | 60 |

|         | 3.4.1      | True Single-Phase Clocking (TSPC)         | 61 |

|         | 3.4.2      | Svensson's True Single Phase Clocking     | 62 |

|         | 3.4.3      | Negative Transition TSPC-1 D-Latch        | 66 |

|         | 3.4.4      | Input / Output Buffering                  | 67 |

|         | 3.4.5      | The Complete Switching Tree Cell          | 69 |

|         | 3.4.6      | Determination of Maximum ROM Height       | 71 |

|         | 3.4.7      | Summary of The Switching Tree Cell Design | 74 |

| 3.      | 5 Heurist  | ic ROM Cell Layout Techniques             | 74 |

| 3.      | 6 Summa    | ary of The Development Work               | 82 |

#### CHAPTER 4

|      | Stand | dard Cells                                       | 83  |

|------|-------|--------------------------------------------------|-----|

|      | 4.1   | Introduction                                     | 83  |

|      | 4.2   | Standard Sub-Cells                               | 84  |

|      | 4.3   | The 3-Bit Adder Cell                             | 86  |

|      |       | 4.3.1 3-Bit Adder Simulation Results             | 88  |

|      | 4.4   | The 3-Bit Multiplier Cell                        | 91  |

|      |       | 4.4.1 3-Bit Multiplier Simulation Results        | 92  |

|      |       | 4.4.2 Test Results on The 3 Bit Multiplier Cell  | 94  |

|      | 4.5   | The 4-Bit Adder Cell                             | 95  |

|      |       | 4.5.1 4-Bit Adder Simulation Results             | 95  |

|      |       | 4.5.2 Test Results on The 4-Bit Adder Cell       | 98  |

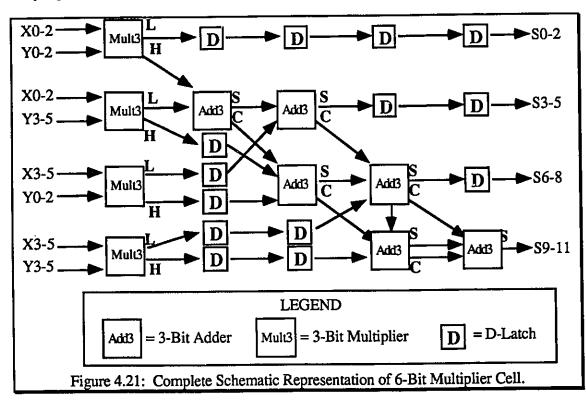

|      | 4.6   | The 6 Bit Multiplier Chip                        | 98  |

|      | 4.7   | The Development of 3µ ECL Compatible Pads        | 99  |

|      |       | 4.7.1 Defining ECL and ECL Compatible Technology | 101 |

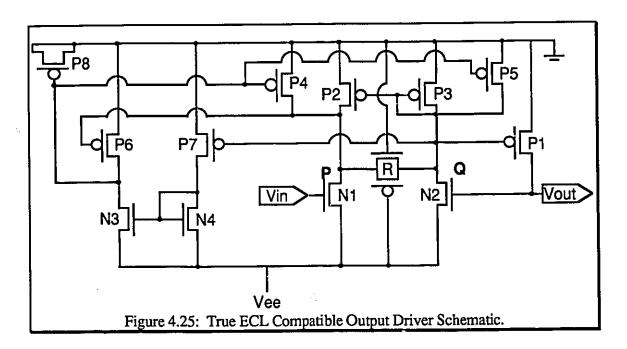

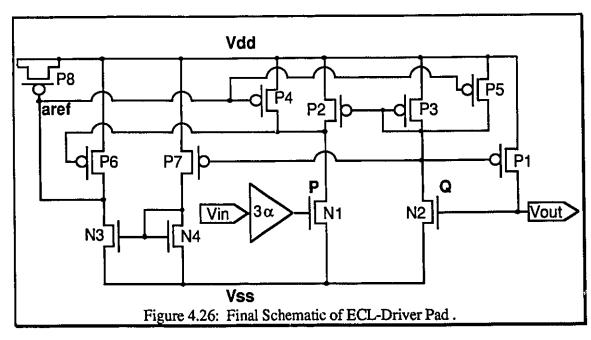

|      |       | 4.7.2 Designing The ECL-Driver Pad               | 102 |

|      |       | 4.7.3 Designing The ECL-Reciever Pad             | 105 |

|      |       | 4.7.4 ECL Simulation Results                     | 106 |

|      |       | 4.7.5 The Test Chip IC3WRECL                     | 107 |

|      |       | 4.7.6 Test Results of IC3WRECL                   | 108 |

|      | 4.8   | Summary of Standard Cells                        | 111 |

| СНАЯ | PTER  | 5                                                |     |

|      | Sun   | nmary and Future Directives                      | 112 |

|      | 5.1   | Summary and Conclusions                          | 112 |

|      | 5.2   | Future Directives                                | 115 |

| REFERENCES    |                                              | 117 |

|---------------|----------------------------------------------|-----|

| APPENDIX A,   | A Summary on Dynamic Domino CMOS Logic       | 119 |

| APPENDIX B    | Complete Schematic Diagram of ROM5 Cell      | 123 |

| APPENDIX C    | Complete Schematic Diagram of JROM Cell      | 129 |

| APPENDIX D    | Schematic Diagram of 4-Bit Comparator Cell   | 133 |

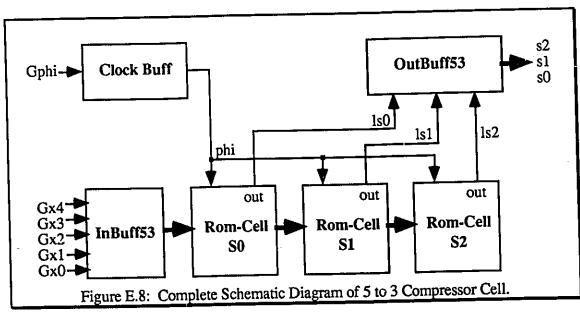

| APPENDIX E    | Schematic Diagram of 5 to 3 Compressor Cell  | 136 |

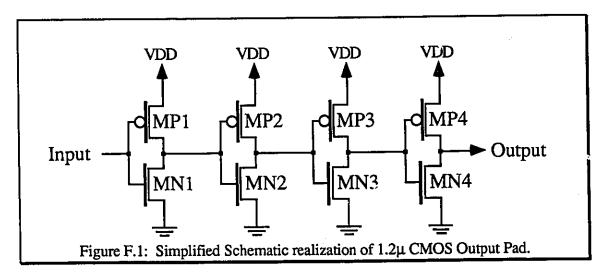

| APPENDIX F    | Summary of Development of 1.2µ CMOS I/O Pads | 142 |

| APPENDIX G    | Schematic Diagram of 3-Bit Adder Cell        | 153 |

| APPENDIX H    | SPICE-Deck for 3-Bit Adder Cell              | 158 |

| APPENDIX I    | Schematic Diagram of 3-Bit Multiplier Cell   | 179 |

| APPENDIX J    | Schematic Diagram of 4-Bit Adder Cell        | 188 |

| APPENDIX K    | Basic Transmission Line Theory               | 196 |

| APPENDIX L    | ECL Receiver and Driver Spice-Decks          | 201 |

| Vita Auctoris |                                              | 206 |

#### LIST OF FIGURES

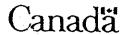

| 1.1  | A) Surface and, B) Cross-Sectional View of a Basic NMOS Transistor | 1  |

|------|--------------------------------------------------------------------|----|

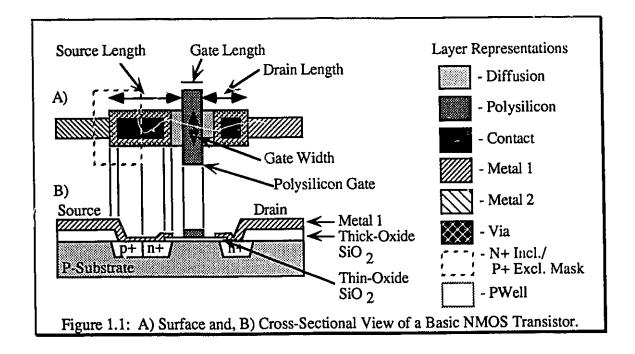

| 1.2  | Standard NMOS Circuit Design Technique                             | 2  |

| 1.3  | Localized Complimentary Well Construction of CMOS Process          | 3  |

| 1.4  | Standard CMOS Logic Construction                                   | 3  |

| 1.5  | A) Basic Clocking Scheme for Evaluating Dynamic Logic, and         |    |

|      | B) Pseudo Two-Phase Clocking Scheme                                | 5  |

| 1.6  | A) Nora Logic Block Illustrating Floating Circuit Nodes, and       |    |

|      | B) Domino Logic Block showing Single-Phase Clocking and            |    |

|      | Use of Signal Buffering                                            | 6  |

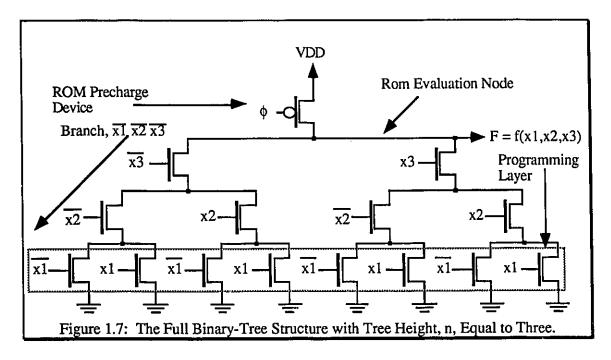

| 1.7  | The Full Binary-Tree Structure with Tree Height, n, Equal to Three | 7  |

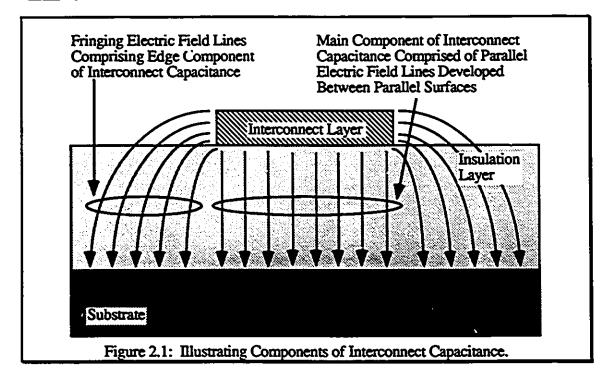

| 2.1  | Illustrating Components of Interconnect Capacitance                | 12 |

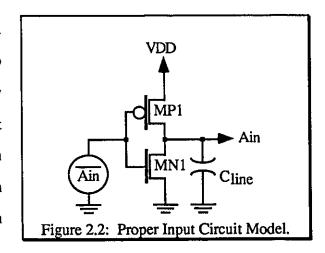

| 2.2  | Proper Input Circuit Model                                         | 13 |

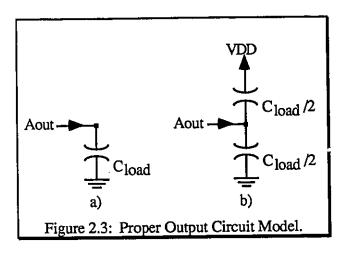

| 2.3  | Proper Output Circuit Model                                        | 14 |

| 2.4  | Schematic Diagram of a 2 Input Nand Gate                           | 15 |

| 2.5  | Layout of 2 Input Nand Gate                                        | 16 |

| 2.6  | Mask-Extracted SPICE-Deck of 2 Input Nand Gate                     | 17 |

| 2.7  | Complete Schematic for Simulating the Nand Gate                    | 16 |

| 2.8  | Additional Devices Added to the Original SPICE-Deck                | 18 |

| 2.9  | Input/Output Waveforms from Nand Gate Simulation                   | 19 |

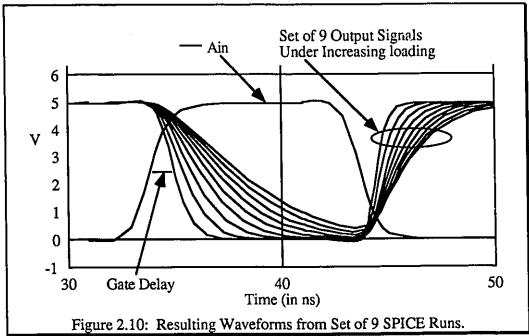

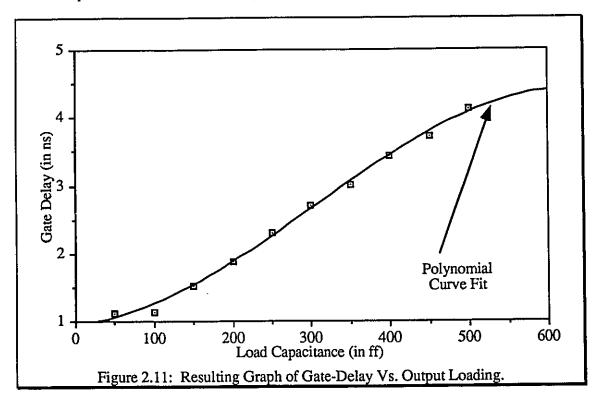

| 2.10 | Resulting Waveforms from Set of 9 SPICE Runs                       | 19 |

| 2.11 | Resulting Graph of Gate-Delay Vs. Output Loading                   | 20 |

| 2.12 | Current Waveforms from SPICE Simulations.                          | 21 |

| 2.13 | Schematic of Domino 2 Input OR Gate                                | 21 |

| 2 14 | Schematic of Input Delay Circuitry                                 | 22 |

| 2.15 | Three Micron CMOS Layout of Domino 2 Input OR Gate                    | 22 |

|------|-----------------------------------------------------------------------|----|

| 2.16 | Illustration of Setup and Hold Time Definitions                       | 23 |

| 2.17 | Simulation Results with Setup-Time of 1.0ns                           | 24 |

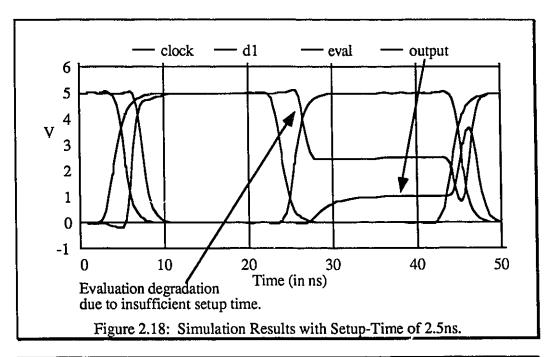

| 2.18 | Simulation Results with Setup-Time of 2.5ns                           | 25 |

| 2.19 | Simulation Results with Setup-Time of 3.0ns                           | 25 |

| 2.20 | CMOS Layer Representations in Grey-Scale Patterns                     | 26 |

| 2.21 | A) Surface and B) Cross-Sectional View of a Basic NMOS Transistor     | 27 |

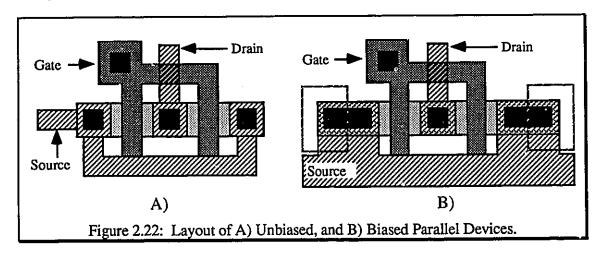

| 2.22 | Layout of A) Unbiased, and B) Biased Parallel Devices                 | 28 |

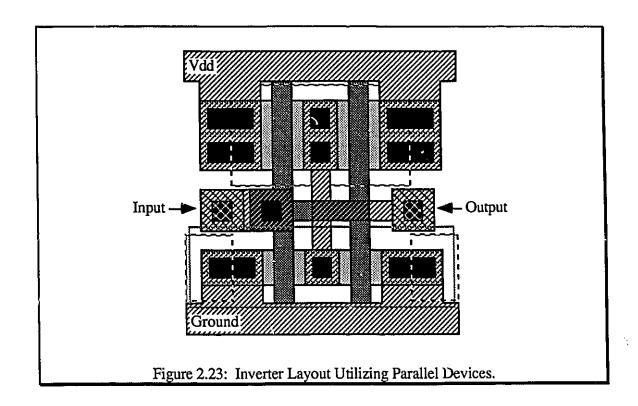

| 2.23 | Inverter Layout Utilizing Parallel Devices                            | 29 |

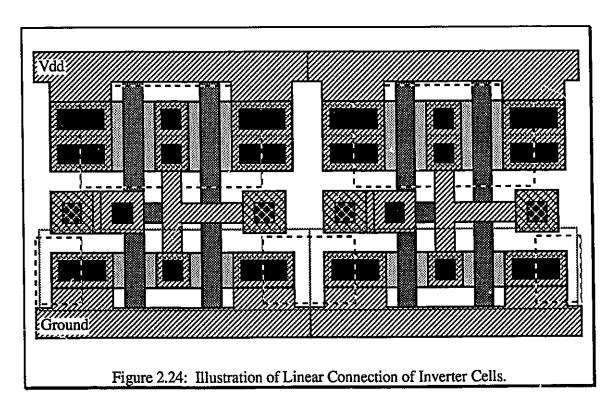

| 2.24 | Illustration of Linear Connection of Inverter Cells                   | 29 |

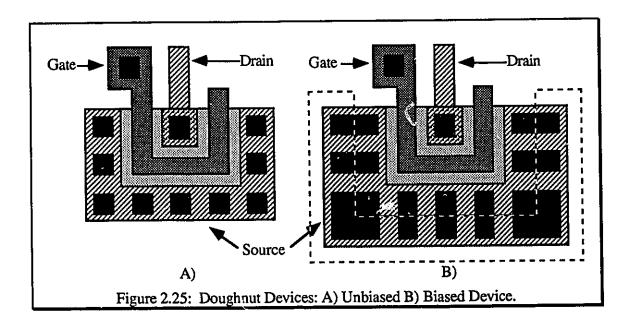

| 2.25 | Doughnut Devices: A) Unbiased B) Biased Device                        | 30 |

| 2.26 | Proper Power Distribution Network within a Circuit                    | 34 |

| 2.27 | Illustration of Current Flow in Via Connection                        | 35 |

| 2.28 | Illustration of Proper Large Current Via Connection                   | 36 |

| 2.29 | Illustration of Interlaced S-Pattern Routing                          | 36 |

| 2.30 | Illustration Showing: A) Area Efficient Design Vs. B) Inefficient     |    |

|      | Design for Metal 2 Routing                                            | 37 |

| 2.31 | Metal 2 Routing Layer Over 3-Bit Adder Cell                           | 38 |

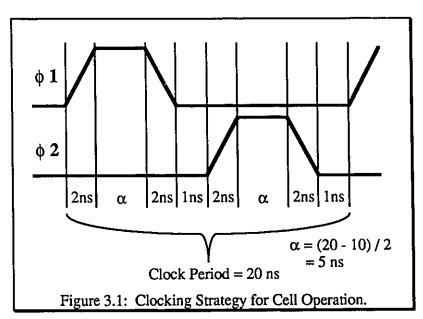

| 3.1  | Clocking Strategy for Cell Operation                                  | 41 |

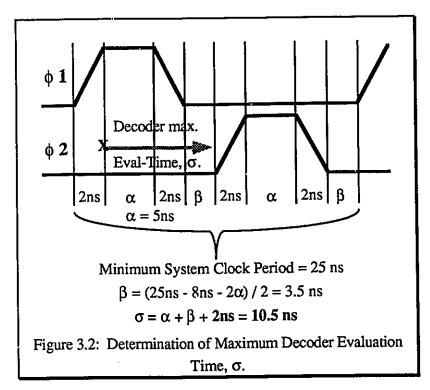

| 3.2  | Determination of Maximum Decoder Evaluation Time, $\sigma$            | 42 |

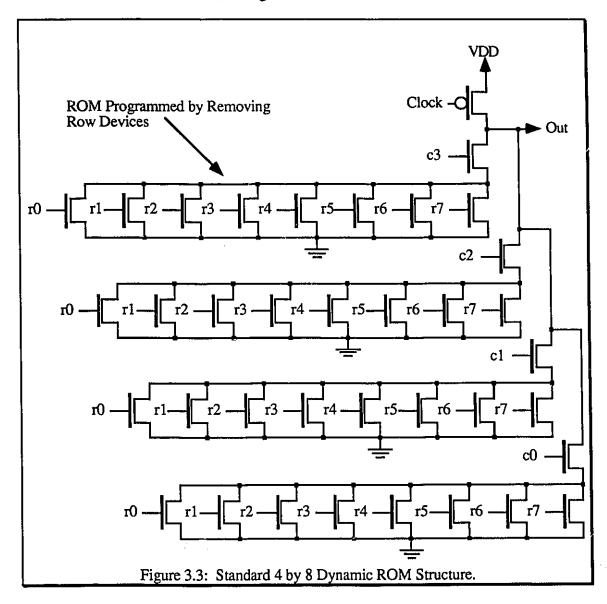

| 3.3  | Standard 4 by 8 Dynamic ROM Structure                                 | 43 |

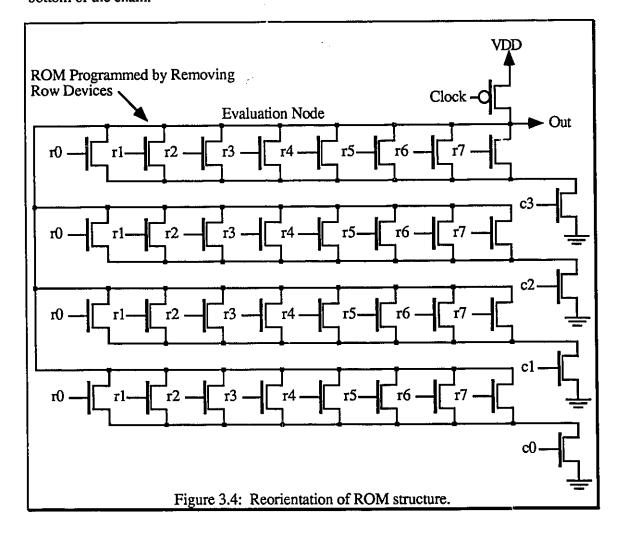

| 3.4  | Reorientation of ROM structure                                        | 44 |

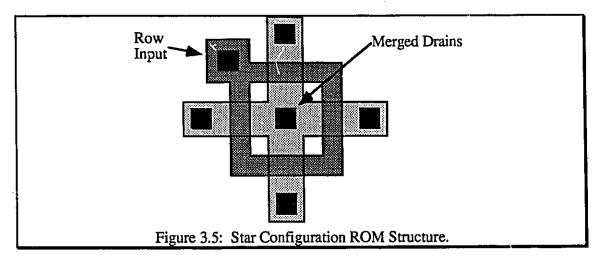

| .3.5 | Star Configuration ROM Structure                                      | 45 |

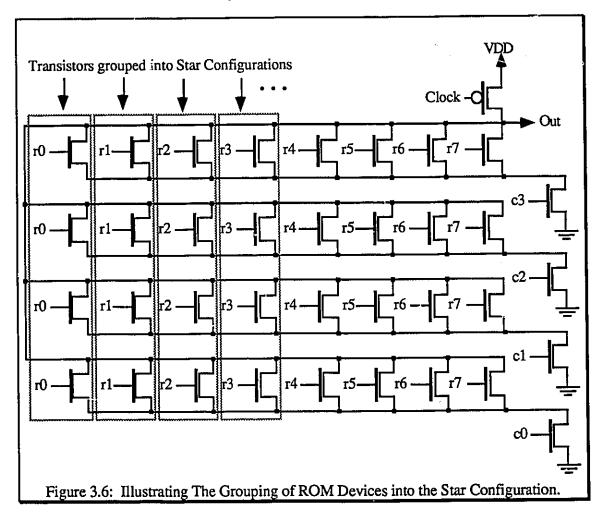

| 3.6  | Illustrating The Grouping of ROM Devices into the Star Configuration  | 46 |

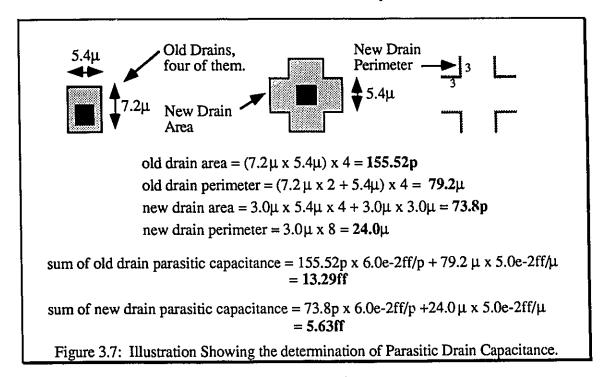

| 3.7  | Illustration Showing the determination of Parasitic Drain Capacitance | 47 |

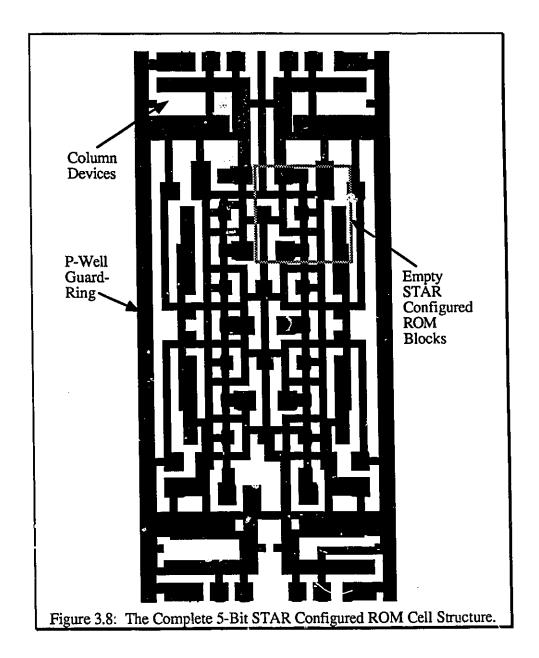

| 3.8  | The Complete 5-Bit STAR Configured ROM Cell Structure                 | 49 |

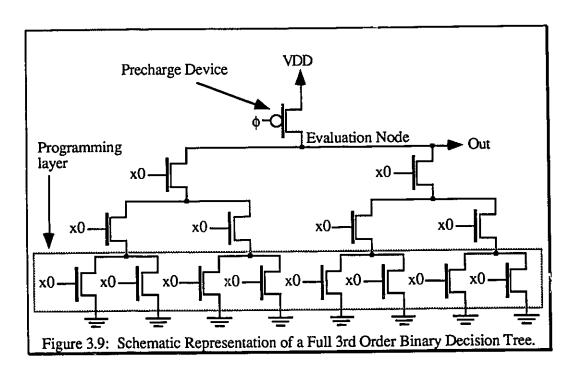

| 3.9  | Schematic Representation of a Full 3rd Order Binary Decision Tree  | 52 |

|------|--------------------------------------------------------------------|----|

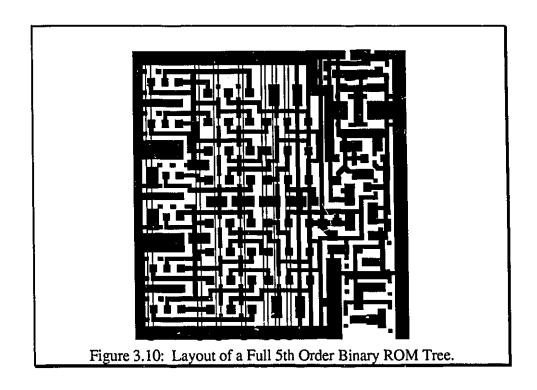

| 3.10 | Layout of a Full 5th Order Binary ROM Tree                         | 53 |

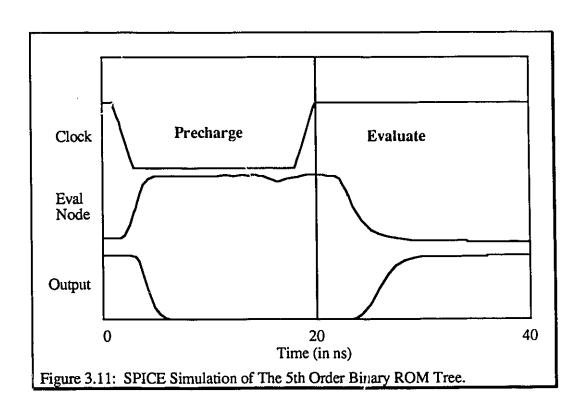

| 3.11 | SPICE Simulation of The 5th Order Binary ROM Tree                  | 53 |

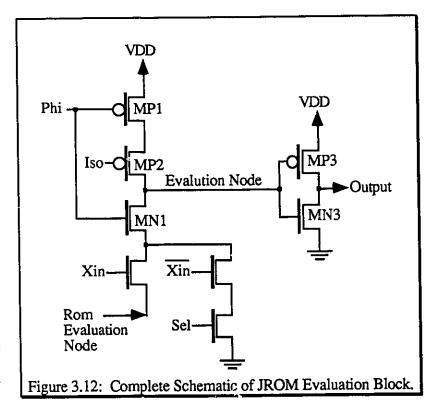

| 3.12 | Complete Schematic of JROM Evaluation Block                        | 54 |

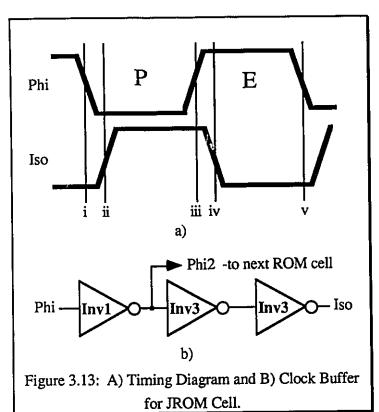

| 3.13 | A) Timing Diagram and B) Clock Buffer for JROM Cell                | 56 |

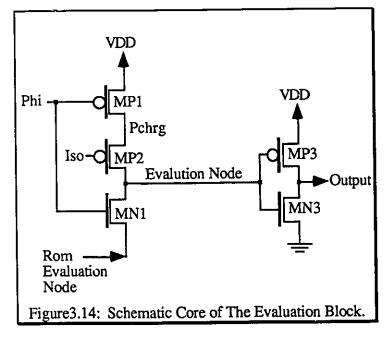

| 3.14 | Schematic Core of The Evaluation Block                             | 56 |

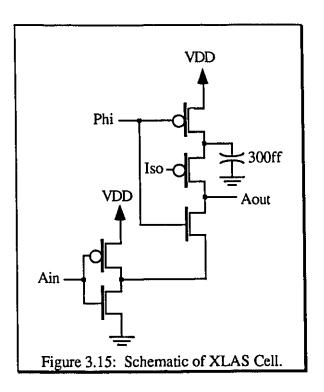

| 3.15 | Schematic of XLAS Cell                                             | 57 |

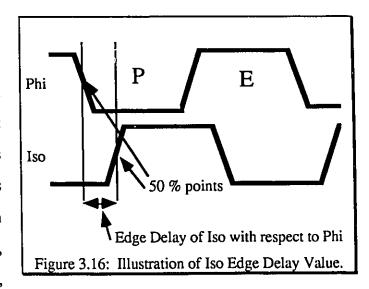

| 3.16 | Illustration of Iso Edge Delay Value                               | 59 |

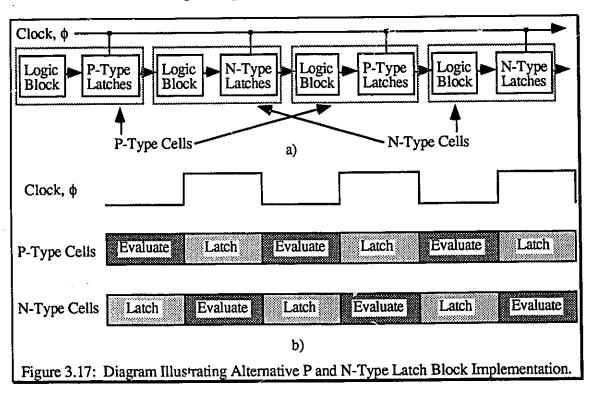

| 3.17 | Diagram Illustrating Alternative P and N-Type Latch Block          |    |

|      | Implementation                                                     | 62 |

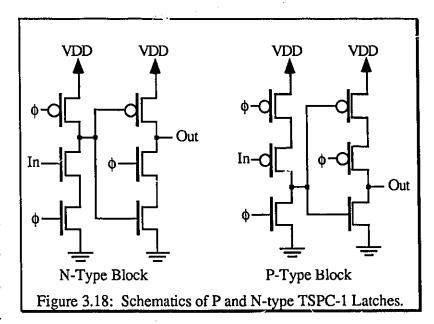

| 3.18 | Schematics of P and N-type TSPC-1 Latches                          | 63 |

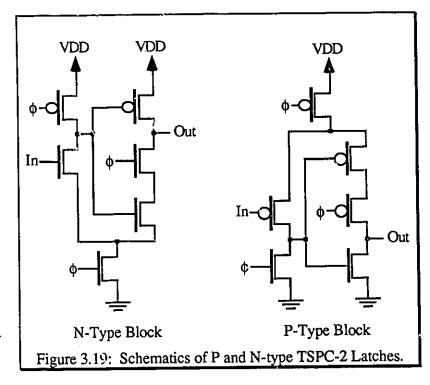

| 3.19 | Schematics of P and N-type TSPC-2 Latches                          | 64 |

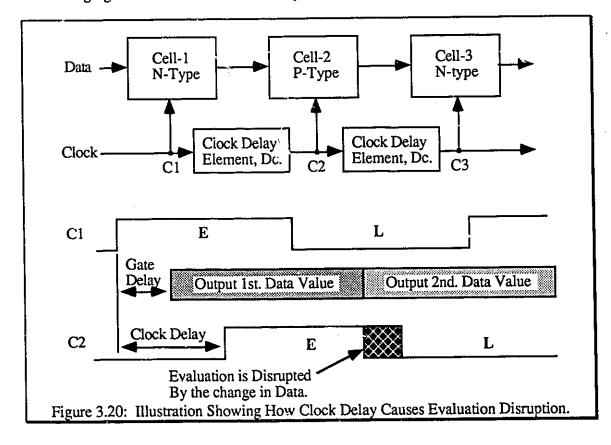

| 3.20 | Illustration Showing How Clock Delay Causes Evaluation Disruption  | 64 |

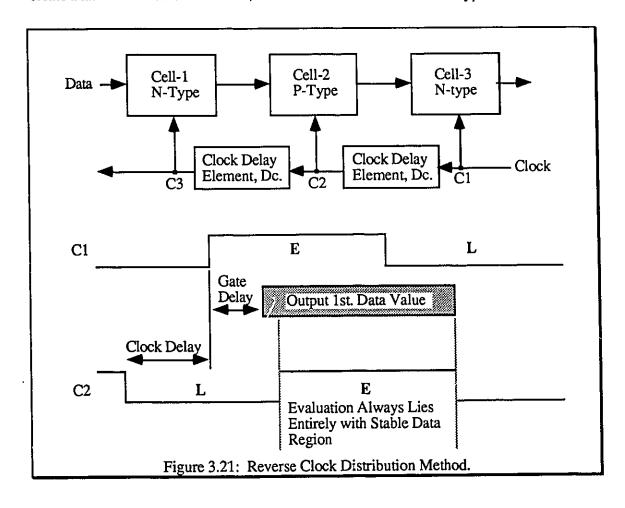

| 3.21 | Reverse Clock Distribution Method                                  | 65 |

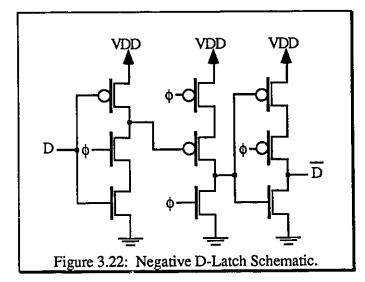

| 3.22 | Negative D-Latch Schematic                                         | 66 |

| 3.23 | The Scaled Negative Transition D-Type Latch                        | 66 |

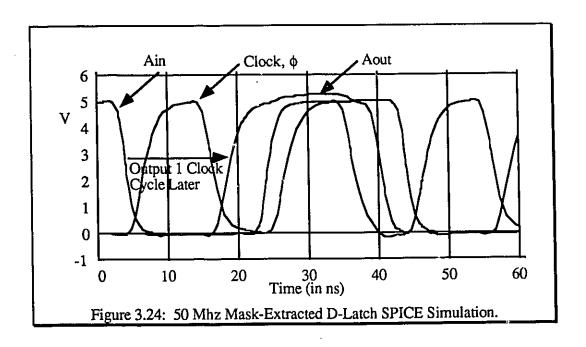

| 3.24 | 50 Mhz Mask-Extracted D-Latch SPICE Simulation                     | 67 |

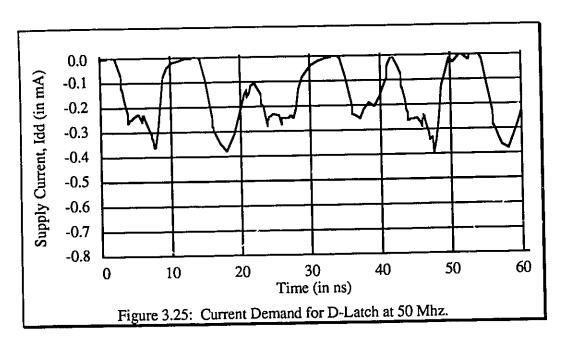

| 3.25 | Current Demand for D-Latch at 50 Mhz                               | 68 |

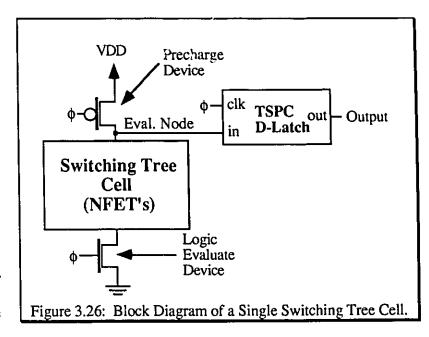

| 3.26 | Block Diagram of a Single Switching Tree Cell                      | 69 |

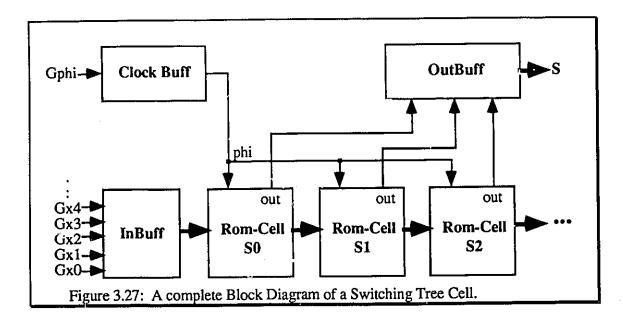

| 3.27 | A complete Block Diagram of a Switching Tree Cell                  | 70 |

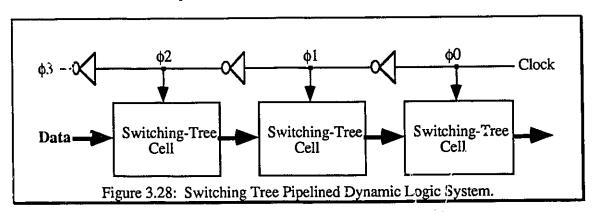

| 3.28 | Switching Tree Pipelined Dynamic Logic System                      | 70 |

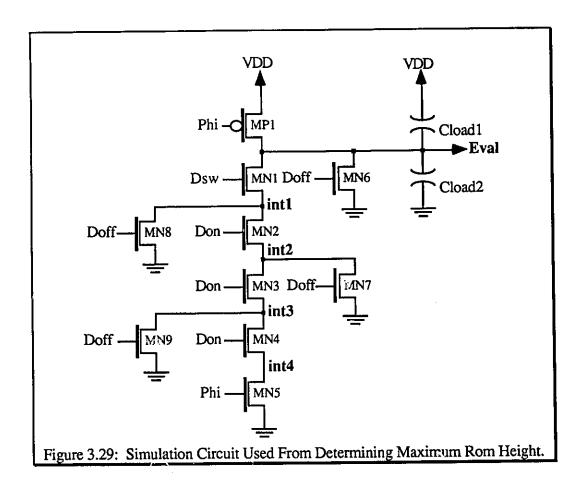

| 3.29 | Simulation Circuit Used From Determining Maximum Rom Height        | 72 |

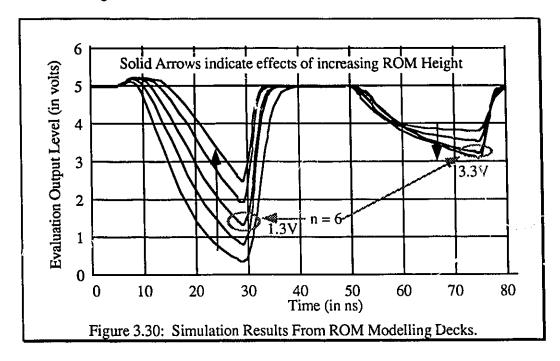

| 3.30 | Simulation Results From ROM Modelling Decks                        | 73 |

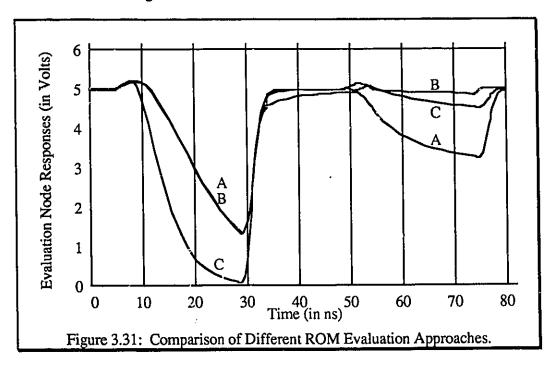

| 3.31 | Comparison of Different ROM Evaluation Approaches                  | 73 |

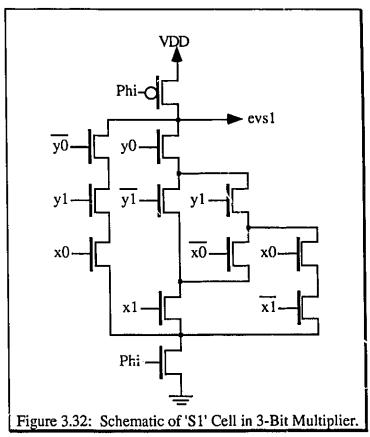

| 3.32 | Schematic of 'S1' Cell in 3-Bit Multiplier                         | 75 |

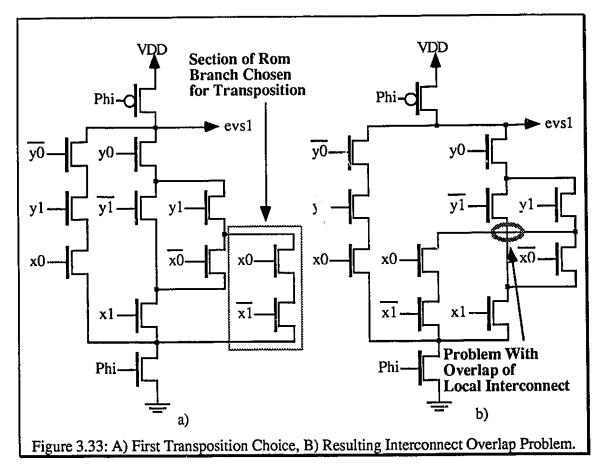

| 3.33 | A) First Transposition Choice, B) Resulting Interconnect Overlap   | 76 |

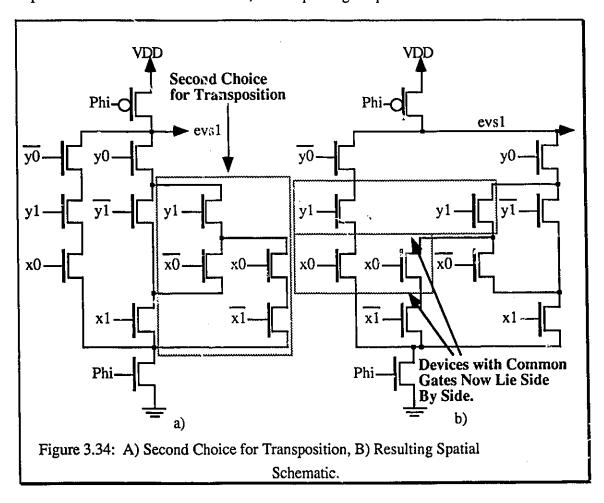

| 3.34 | A) Second Choice for Transposition, B) Resulting Spatial Schematic | 77 |

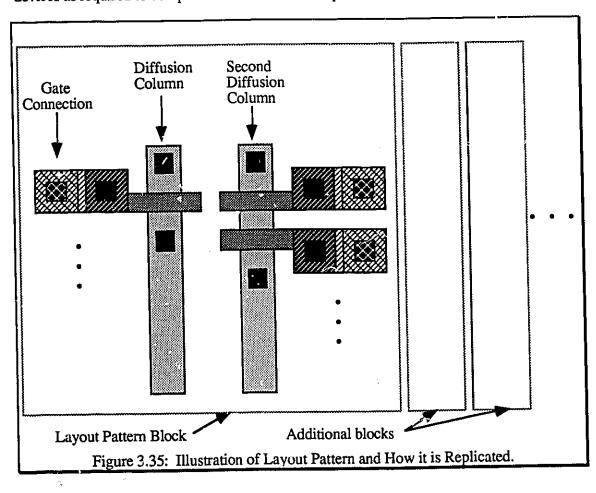

| 3.35 | Illustration of Layout Pattern and How it is Replicated                  | 78 |

|------|--------------------------------------------------------------------------|----|

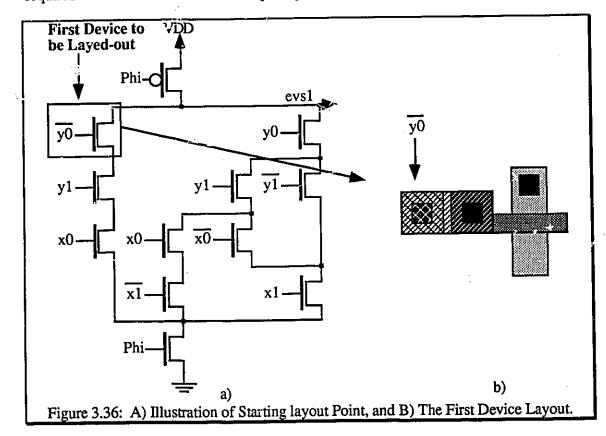

| 3.36 | A) Illustration of Starting layout Point, and B) The First Device Layout | 79 |

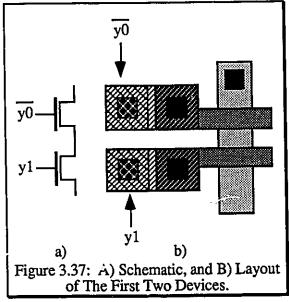

| 3.37 | A) Schematic, and B) Layout of The First Two Devices                     | 79 |

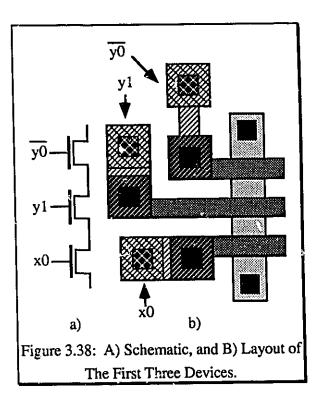

| 3.38 | A) Schematic, and B) Layout of The First Three Devices                   | 80 |

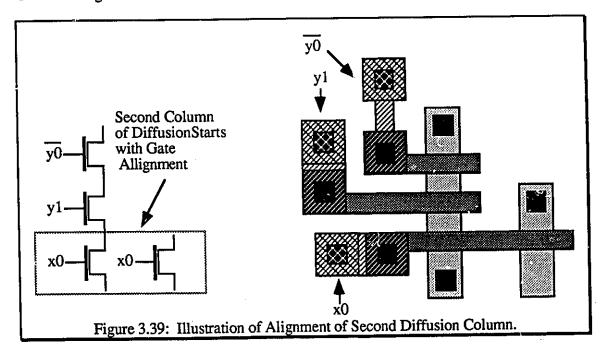

| 3.39 | Illustration of Alignment of Second Diffusion Column                     | 80 |

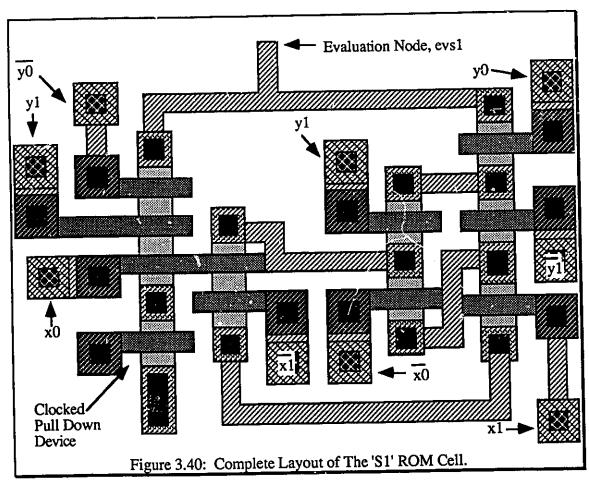

| 3.40 | Complete Layout of The 'S1' ROM Cell                                     | 81 |

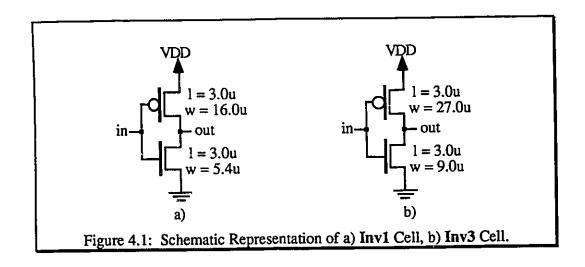

| 4.1  | Schematic Representation of a) Inv1 Cell, b) Inv3 Cell                   | 85 |

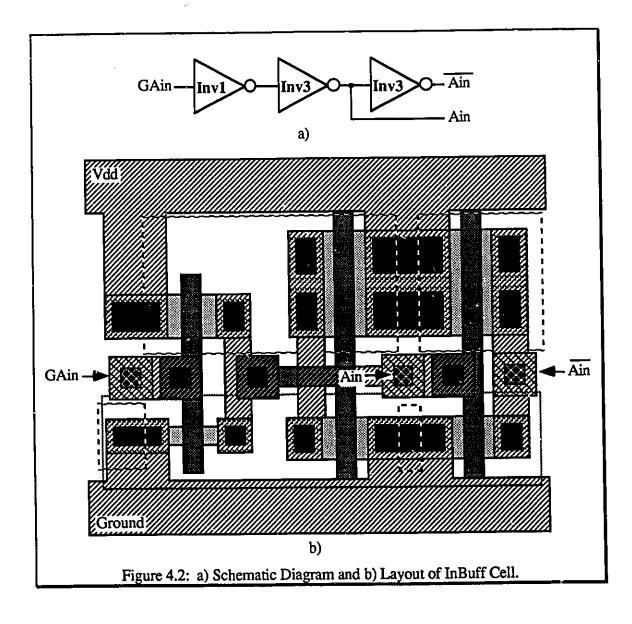

| 4.2  | A) Schematic Diagram and B) Layout of InBuff Cell                        | 85 |

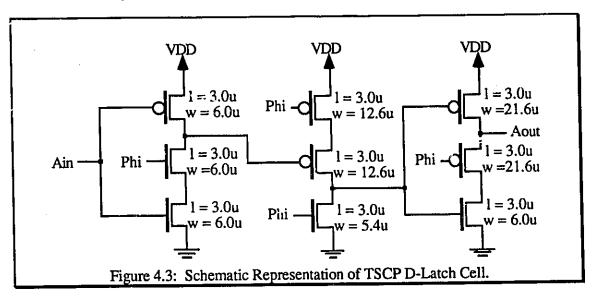

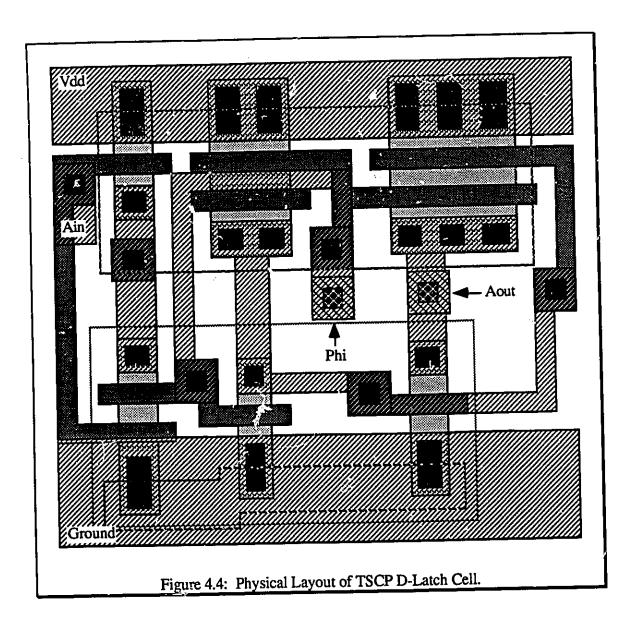

| 4.3  | Schematic Representation of TSCP D-Latch Cell                            | 86 |

| 4.4  | Physical Layout of TSCP D-Latch Cell                                     | 87 |

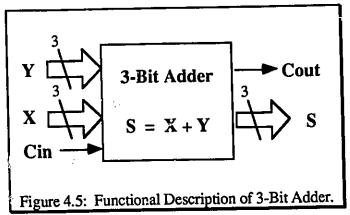

| 4.5  | Functional Description of 3-Bit Adder                                    | 87 |

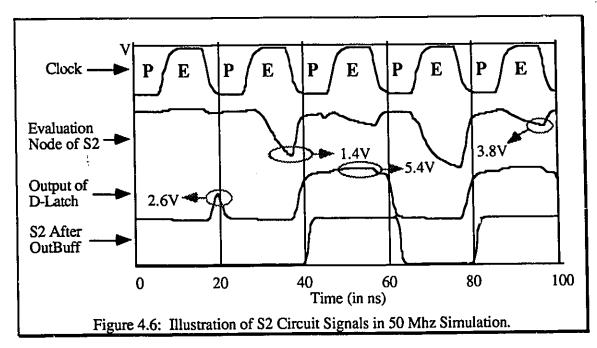

| 4.6  | Illustration of S2 Circuit Signals in 50 Mhz Simulation                  | 88 |

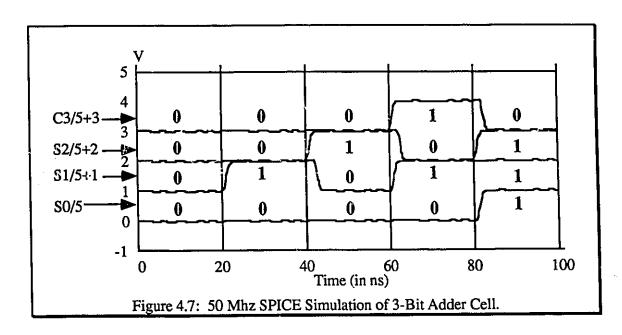

| 4.7  | 50 Mhz SPICE Simulation of 3-Bit Adder Cell                              | 90 |

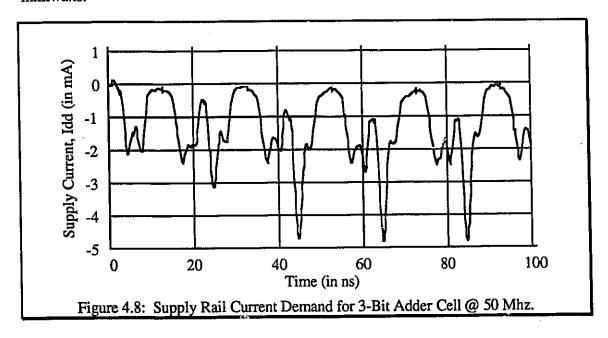

| 4.8  | Supply Rail Current Demand for 3-Bit Adder Cell @ 50 Mhz                 | 90 |

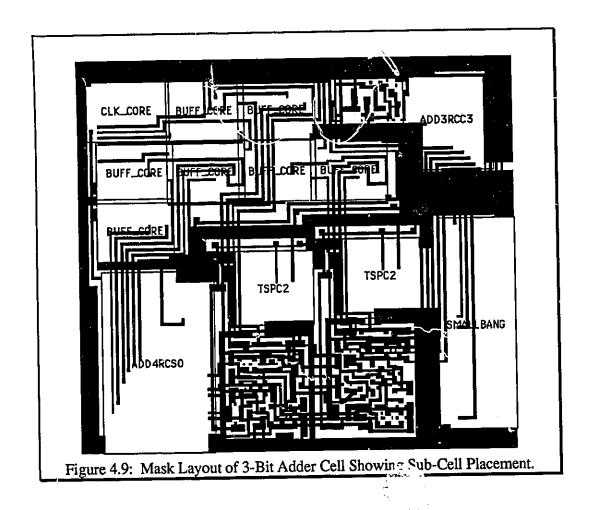

| 4.9  | Mask Layout of 3-Bit Adder Cell Showing Sub-Cell Placement               | 91 |

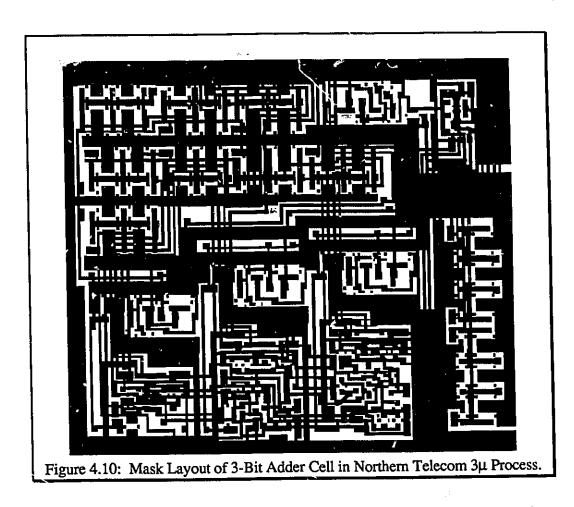

| 4.10 | Mask Layout of 3-Bit Adder Cell in Northern Telecom 3μ Process           | 92 |

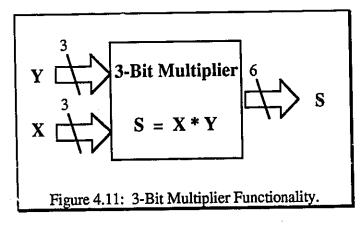

| 4.11 | 3-Bit Multiplier Functionality                                           | 91 |

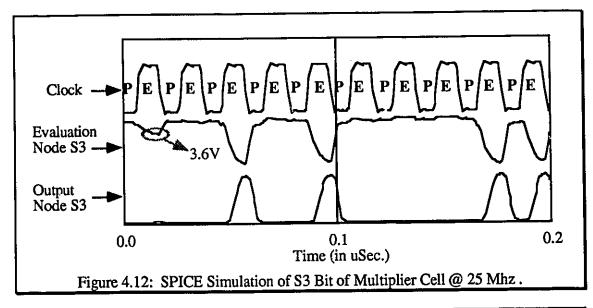

| 4.12 | SPICE Simulation of S3 Bit of Multiplier Cell @ 25 Mhz                   | 93 |

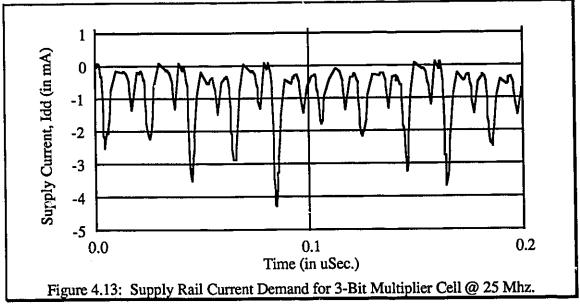

| 4.13 | Supply Rail Current Demand for 3-Bit Multiplier Cell @ 25 Mhz            | 93 |

| 4.14 | Mask Layout of 3-Bit Multiplier Cell in 3 $\mu$ CMOS Technology          | 94 |

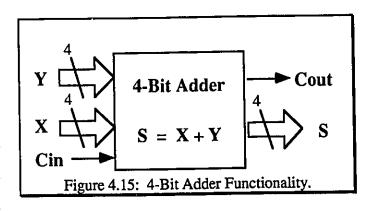

| 4.15 | 4-Bit Adder Functionality                                                | 95 |

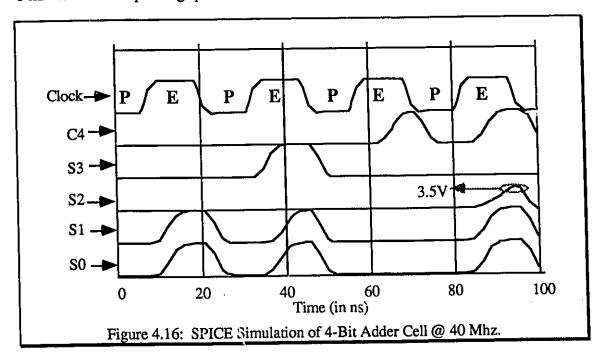

| 4.16 | SPICE Simulation of 4-Bit Adder Cell @ 40 Mhz                            | 96 |

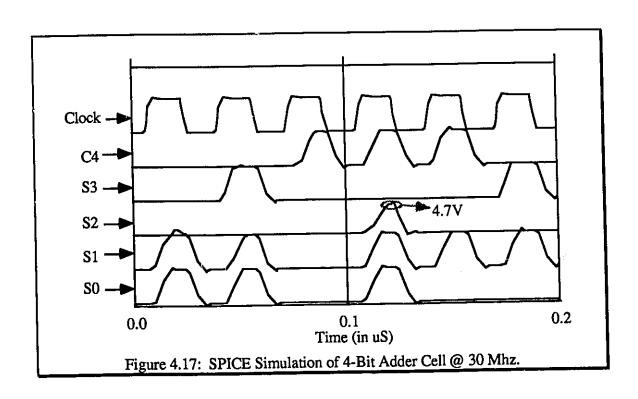

| 4.17 | SPICE Simulation of 4-Bit Adder Cell @ 30 Mhz                            | 96 |

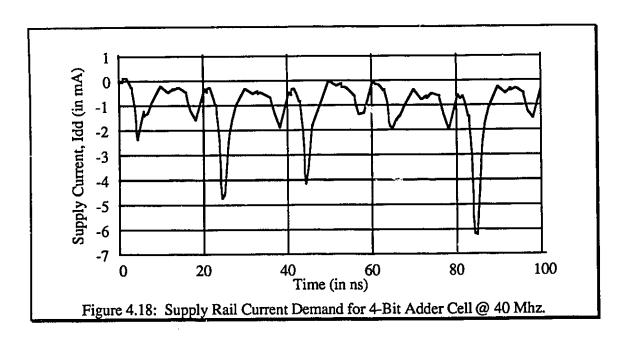

| 4.18 | Supply Rail Current Demand for 4-Bit Adder Cell @ 40 Mhz                 | 97 |

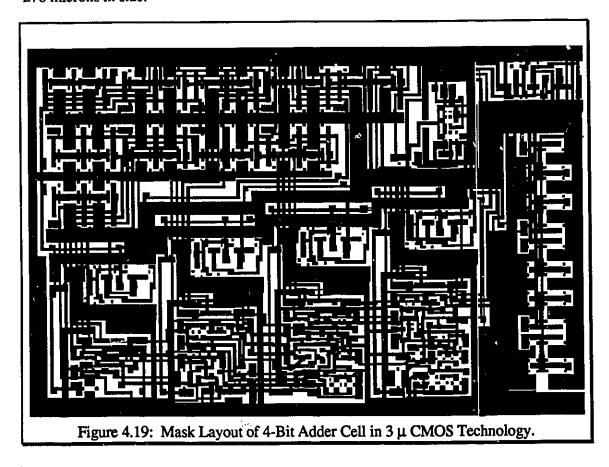

| 4.19 | Mask Layout of 4-Bit Adder Cell in 3 $\mu$ CMOS Technology               | 97 |

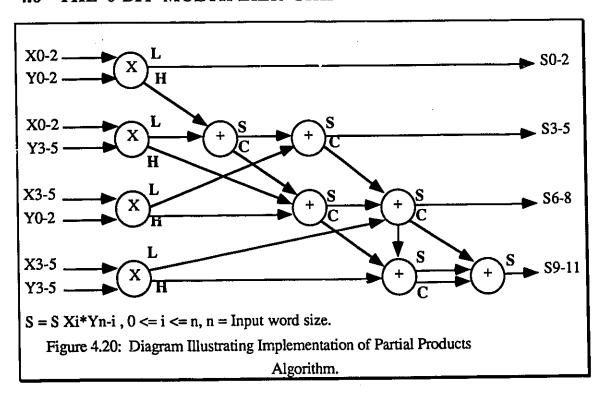

| 4.20 | Diagram Illustrating Implementation of Partial Products Algorithm        | 98 |

| 4.21        | Complete Schematic Representation of 6-Bit Multiplier Cell        | 99     |

|-------------|-------------------------------------------------------------------|--------|

| 4.22        | Physical Mask Layout of 6-Bit Multiplier Cell in 3µ CMOS Technolo | gy 100 |

| 4.23        | ECL 10K Series Specifications                                     | 101    |

| 4.24        | Specifications for ECL Compatible I/O Pads                        | 102    |

| 4.25        | True ECL Compatible Output Driver Schematic                       | 103    |

| 4.26        | Final Schematic of ECL-Driver Pad                                 | 103    |

| 4.27        | Mask Layout of ECL-Driver Pad                                     | 104    |

| 4.28        | Mask Layout of ECL-Receiver Pad                                   | 105    |

| 4.29        | Schematic Diagram of Two Stage ECL Receiver Pad                   | 106    |

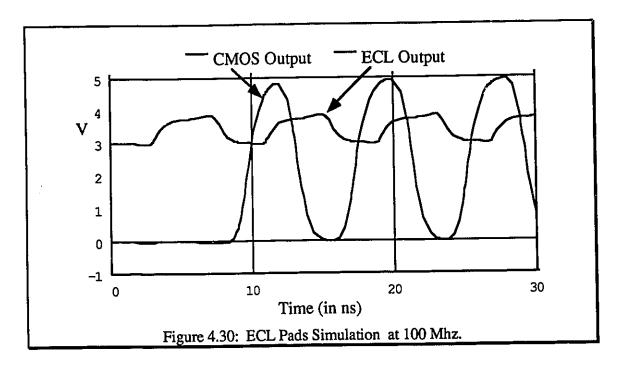

| 4.30        | ECL Pads Simulation at 100 Mhz                                    | 107    |

| 4.31        | The Layout of IC3WRECL                                            | 108    |

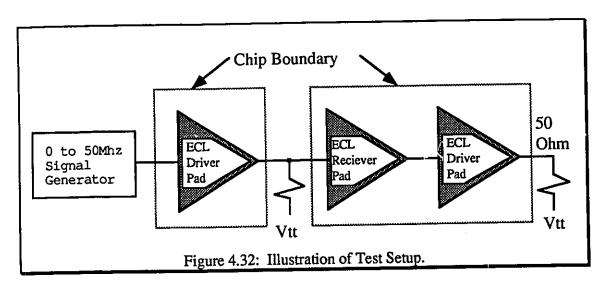

| 4.32        | Illustration of Test Setup                                        | 109    |

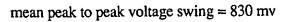

| 4.33        | Scope plots taken from ECL Compatible Board Test                  | 110    |

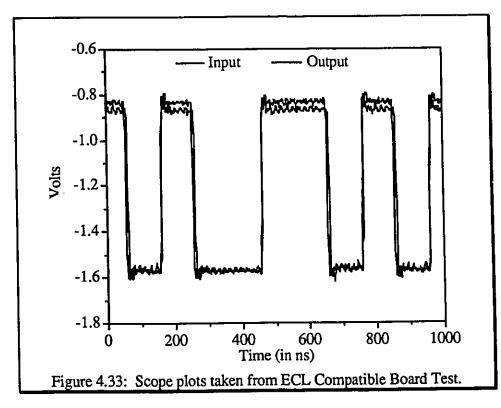

| 4.34        | ECL-Driver at 65 Mhz with Sinusoidal Excitation                   | 111    |

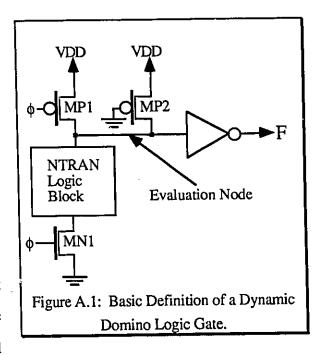

| A.1         | Basic Definition of a Dynamic Domino Logic Gate                   | 120    |

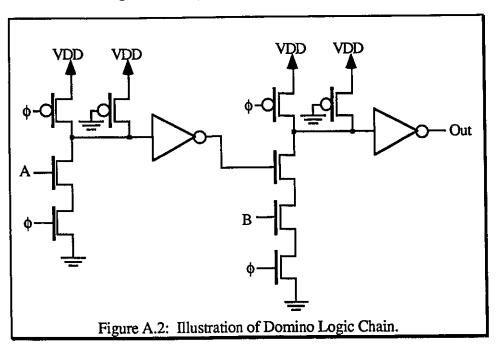

| A.2         | Illustration of Domino Logic Chain                                | 121    |

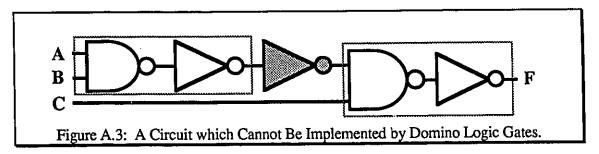

| A.3         | A Circuit which Cannot Be Implemented by Domino Logic Gates       | 122    |

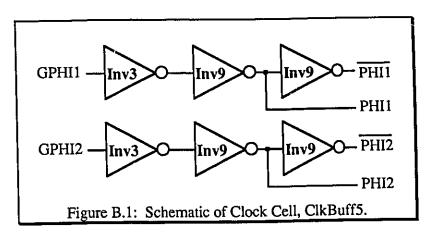

| B.1         | Schematic of Clock Cell, ClkBuff5                                 | 124    |

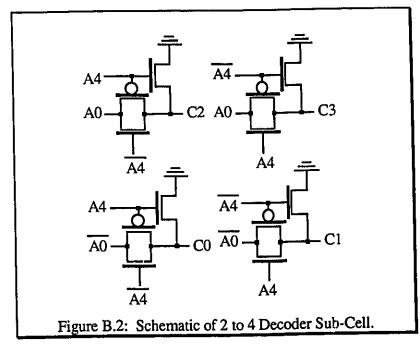

| B.2         | Schematic of 2 to 4 Decoder Sub-Cell                              | 124    |

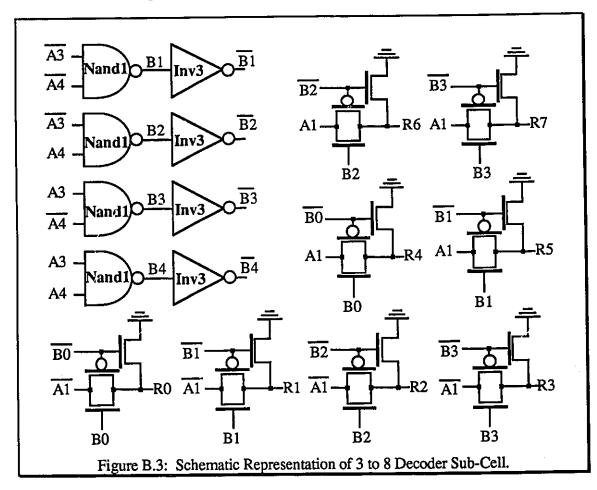

| B.3         | Schematic Representation of 3 to 8 Decoder Sub-Cell               | 125    |

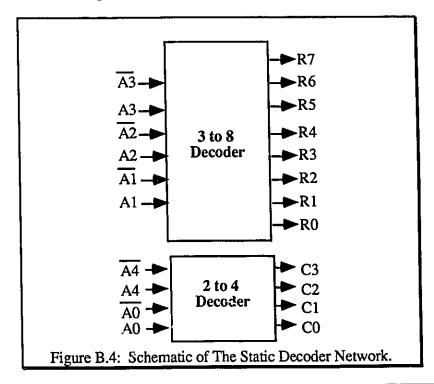

| B.4         | Schematic of The Static Decoder Network                           | 126    |

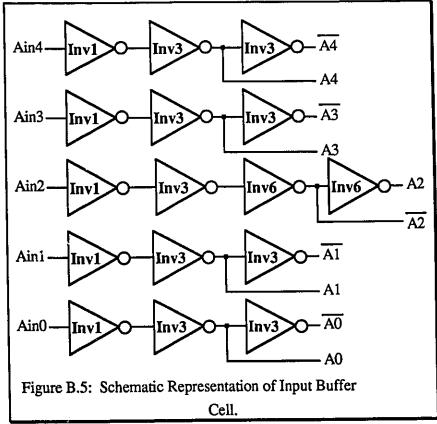

| B.5         | Schematic Representation of Input Buffer Cell                     | 126    |

| B.6         | Schematic Representation of STAR Configured ROM Cell              | 127    |

| B.7         | Schematic Representation of Complete ROM5 Cell                    | 128    |

| <b>C</b> .1 | Schematic Representation of The JClockBuff Cell                   | 130    |

| C 2         | Schematic Representation of The JEvalBlk Cell                     | 130    |

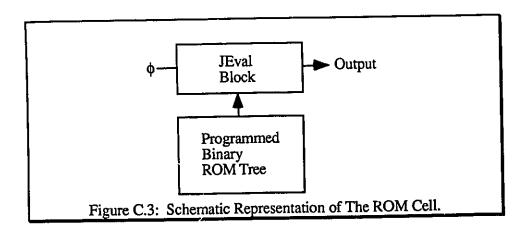

| C.3  | Schematic Representation of The ROM Cell                                     | 131   |

|------|------------------------------------------------------------------------------|-------|

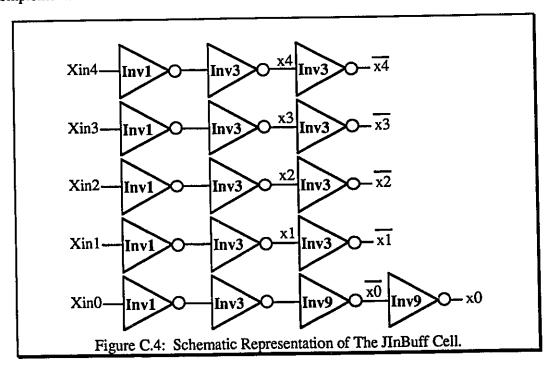

| C.4  | Schematic Representation of The JInBuff Cell                                 | 131   |

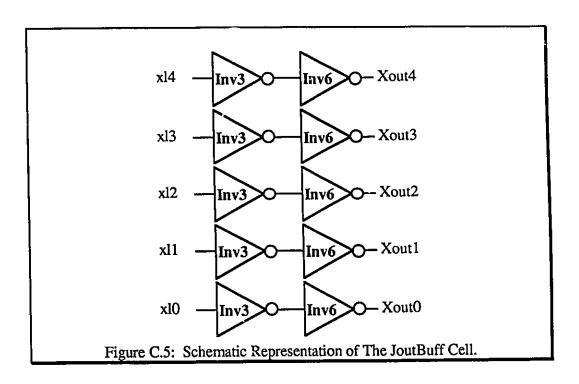

| C.5  | Schematic Representation of The JoutBuff Cell                                | 132   |

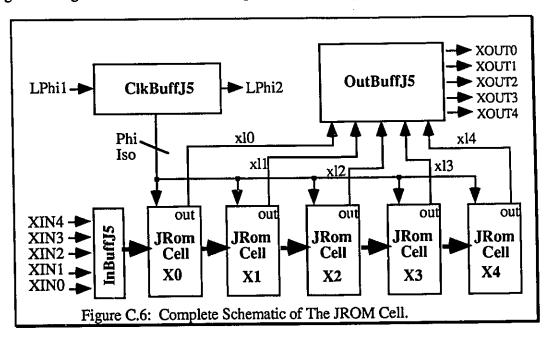

| C.6  | Complete Schematic of The JROM Cell                                          | 132   |

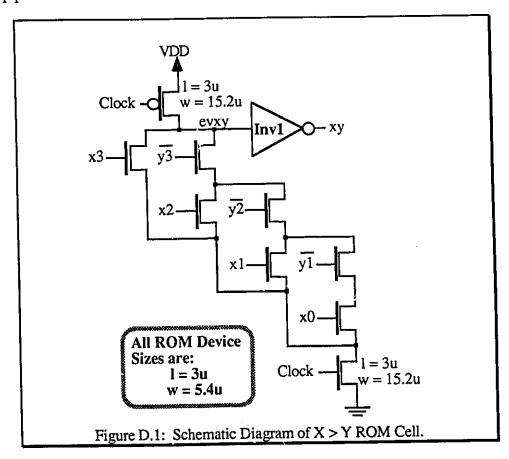

| D.1  | Schematic Diagram of X > Y ROM Cell                                          | 134   |

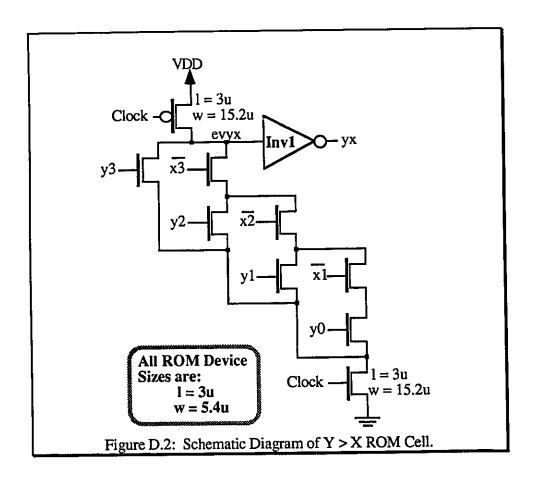

| D.2  | Schematic Diagram of Y > X ROM Cell                                          | 135   |

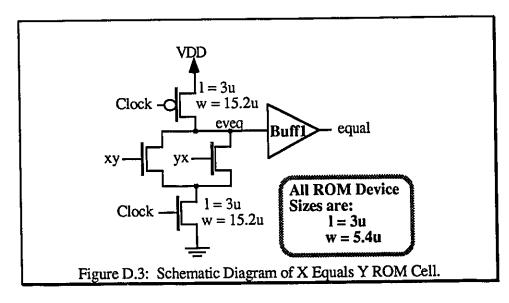

| D.3  | Schematic Diagram of X Equals Y ROM Cell                                     | 135   |

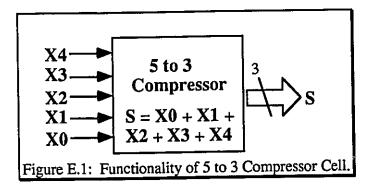

| E.1  | Functionality of 5 to 3 Compressor Cell                                      | 137   |

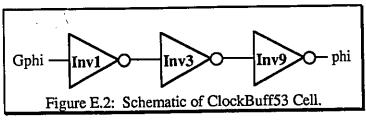

| E.2  | Schematic of ClockBuff53 Cell                                                | 137   |

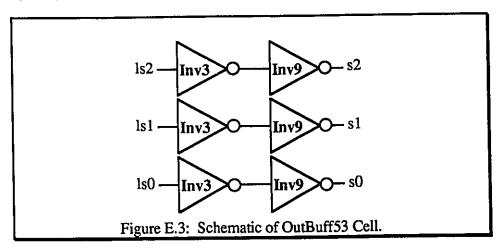

| E.3  | Schematic of OutBuff53 Cell                                                  | 137   |

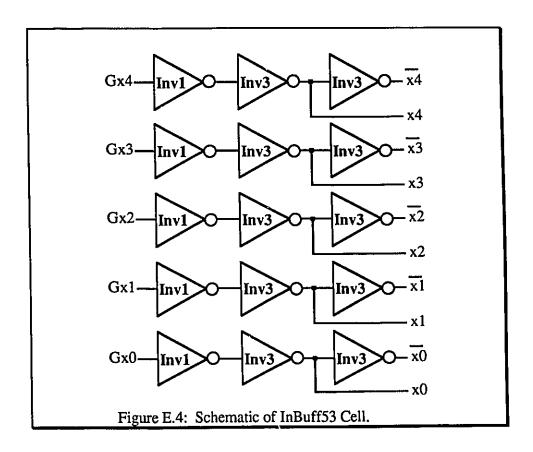

| E.4  | Schematic of InBuff53 Cell                                                   | 138   |

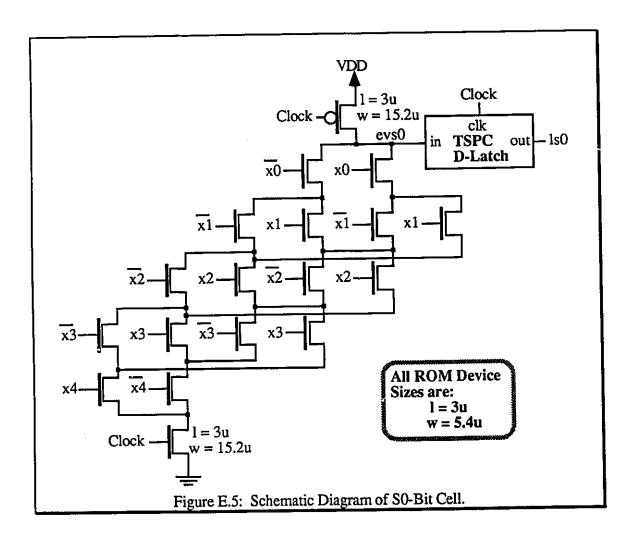

| E.5  | Schematic Diagram of S0-Bit Cell                                             | 139   |

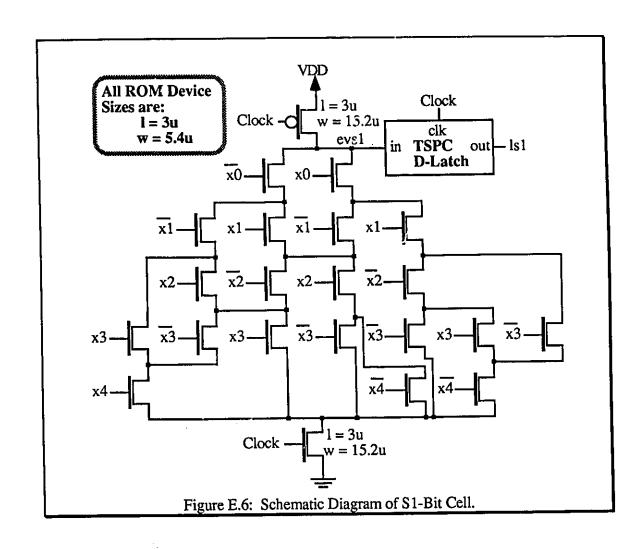

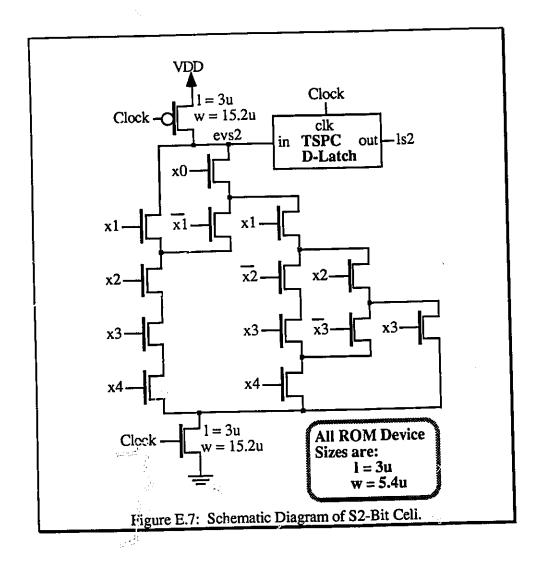

| E.6  | Schematic Diagram of S1-Bit Cell                                             | 140   |

| E.7  | Schematic Diagram of S2-Bit Cell                                             | 141   |

| E.8  | Complete Schematic Diagram of 5 to 3 Compressor Cell                         | 141   |

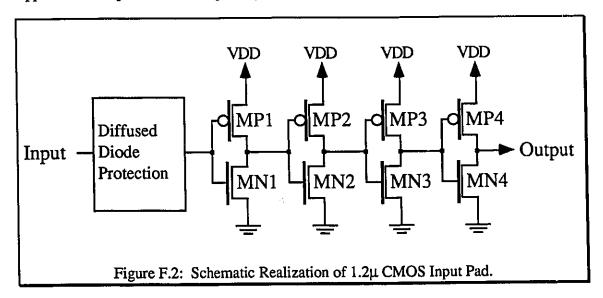

| F.1  | Simplified Schematic realization of 1.2µ CMOS Output Pad                     | 143   |

| F.2  | Schematic Realization of 1.2µ CMOS Input Pad                                 | 144   |

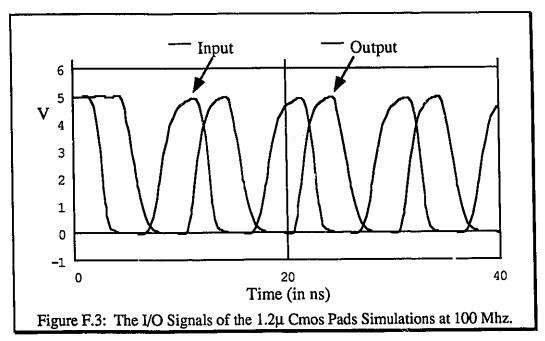

| F.3  | The I/O Signals of the 1.2µ Cmos Pads Simulations at 100 Mhz                 | 146   |

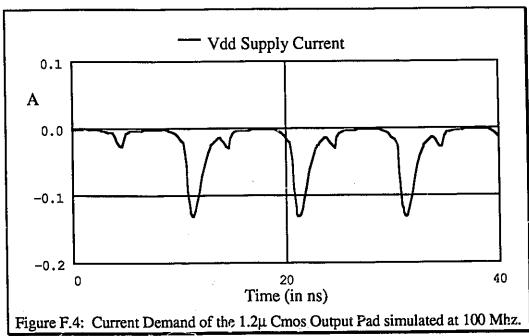

| F.4  | Current Demand of the $1.2\mu$ Cmos Output Pad simulated at $100~\text{Mhz}$ | 146   |

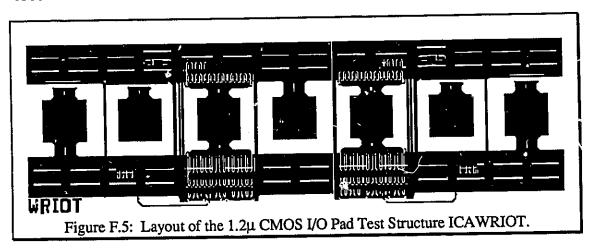

| F.5  | Layout of the 1.2µ CMOS I/O Pad Test Structure ICAWRIOT                      | 147   |

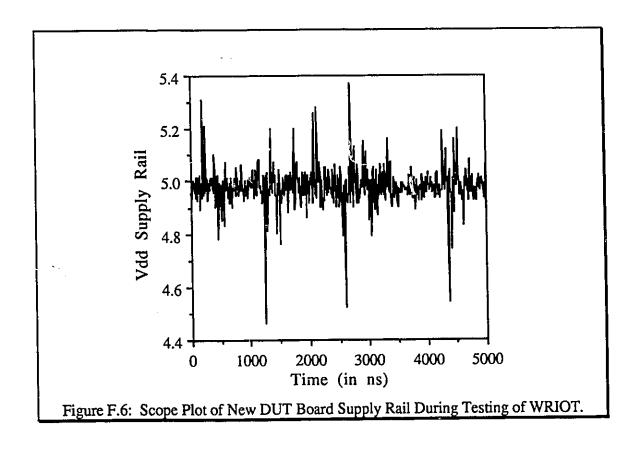

| F.6  | Scope Plot of New DUT Board Supply Rail During Testing of WRIO               | T 148 |

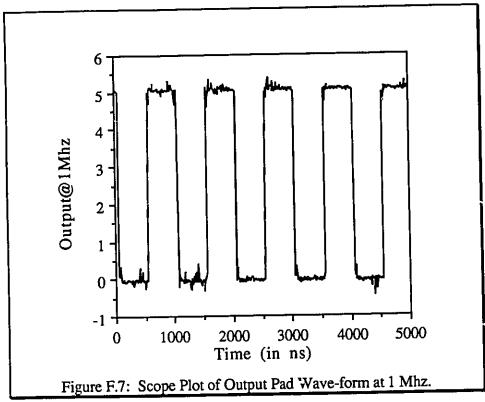

| F.7  | Scope Plot of Output Pad Wave-form at 1 Mhz                                  | 149   |

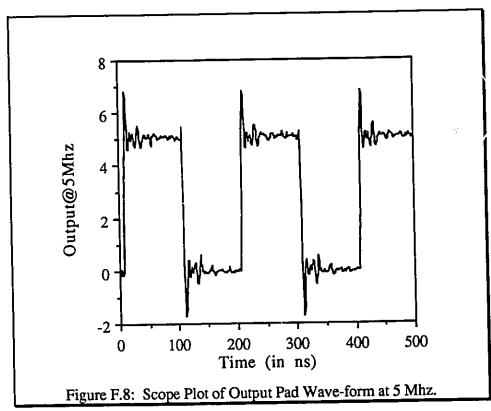

| F.8  | Scope Plot of Output Pad Wave-form at 5 Mhz                                  | 149   |

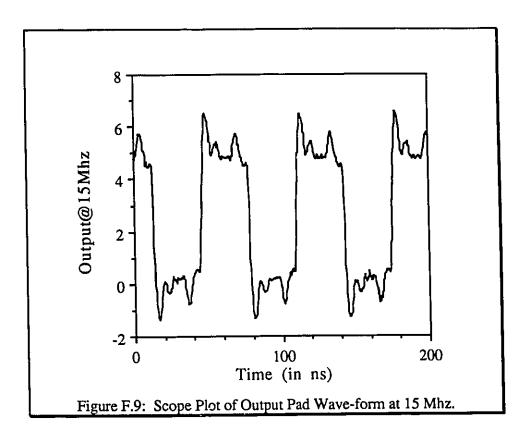

| F.9  | Scope Plot of Output Pad Wave-form at 15 Mhz                                 | 150   |

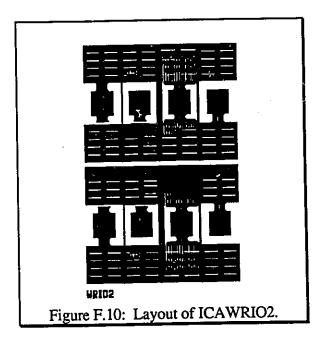

| F.10 | Layout of ICAWRIO2                                                           | 151   |

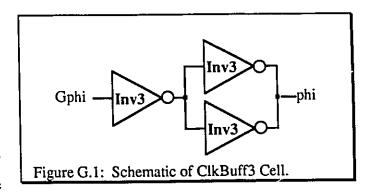

| G.1         | Schematic of ClkBuff3 Cell                                 | 154 |

|-------------|------------------------------------------------------------|-----|

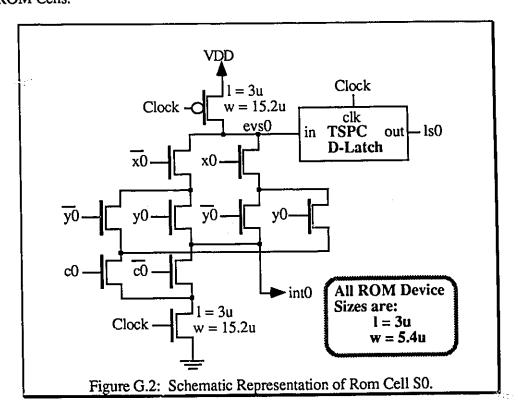

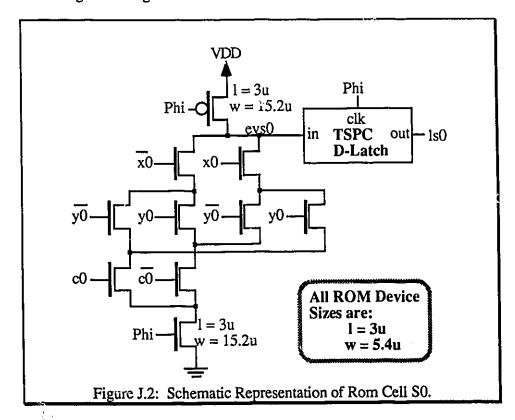

| <b>G</b> .2 | Schematic Representation of Rom Cell S0                    | 154 |

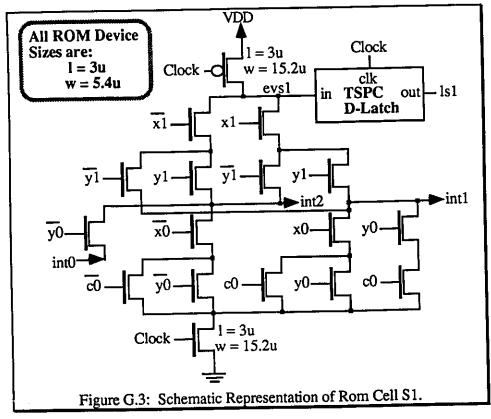

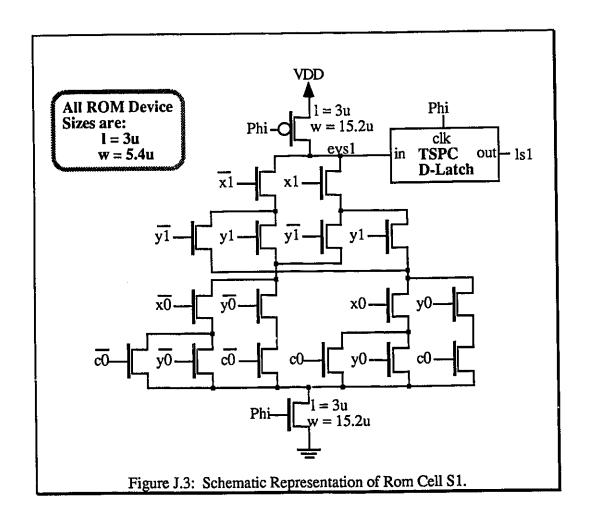

| G.3         | Schematic Representation of Rom Cell S1                    | 155 |

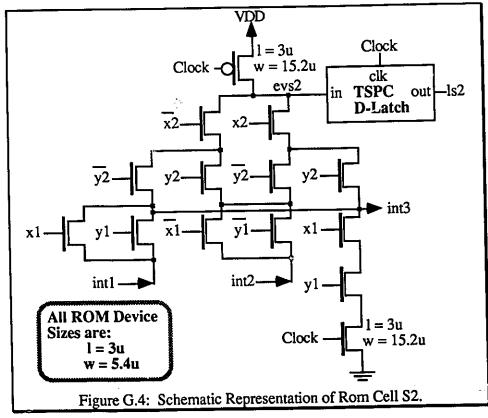

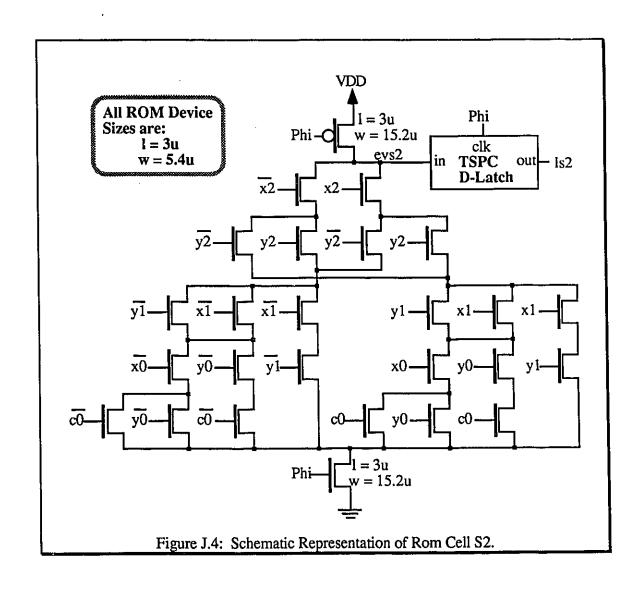

| G.4         | Schematic Representation of Rom Cell S2                    | 155 |

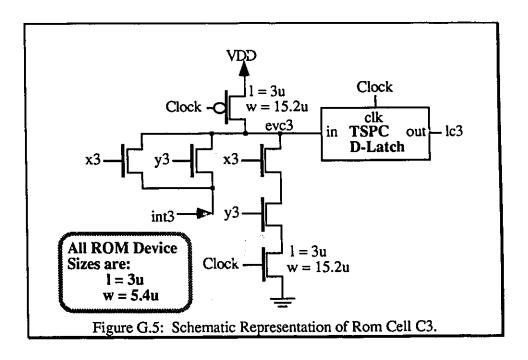

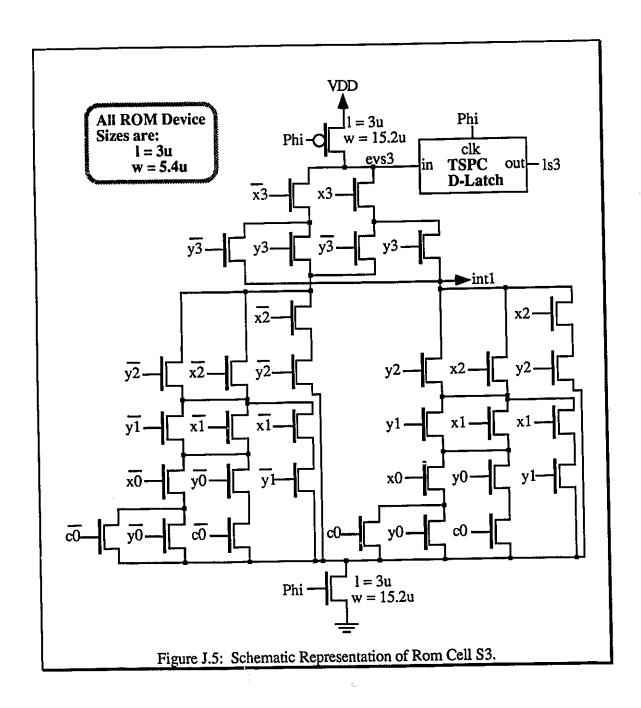

| G.5         | Schematic Representation of Rom Cell C3                    | 156 |

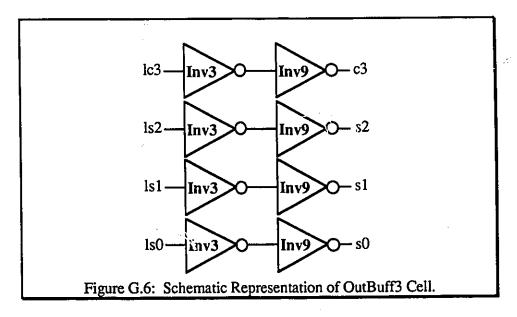

| G.6         | Schematic Representation of OutBuff3 Cell                  | 156 |

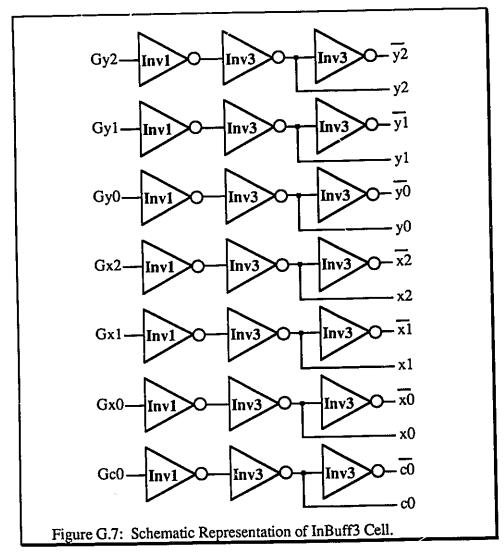

| G.7         | Schematic Representation of InBuff3 Cell                   | 157 |

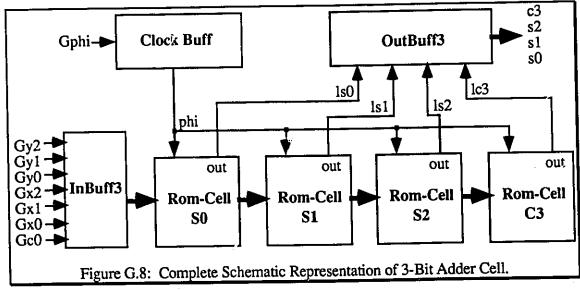

| G.8         | Complete Schematic Representation of 3-Bit Adder Cell      | 157 |

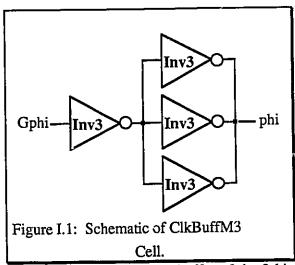

| 1.1         | Schematic of CLkBuffM3 Cell                                | 180 |

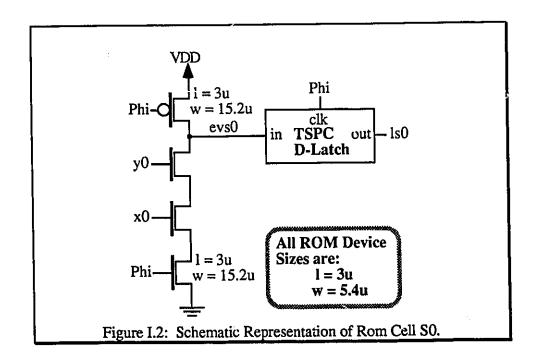

| I.2         | Schematic Representation of Rom Cell S0                    | 180 |

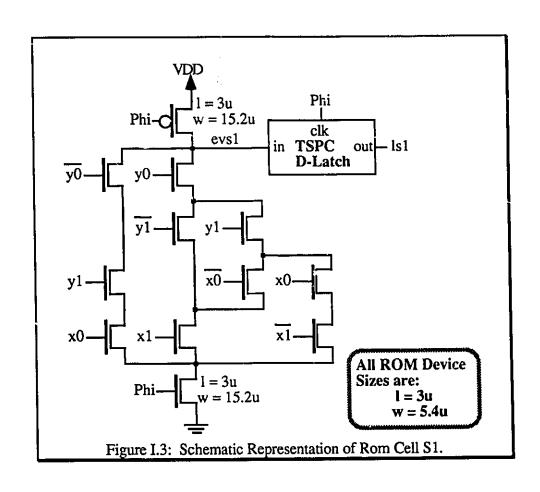

| I.3         | Schematic Representation of Rom Cell S1                    | 181 |

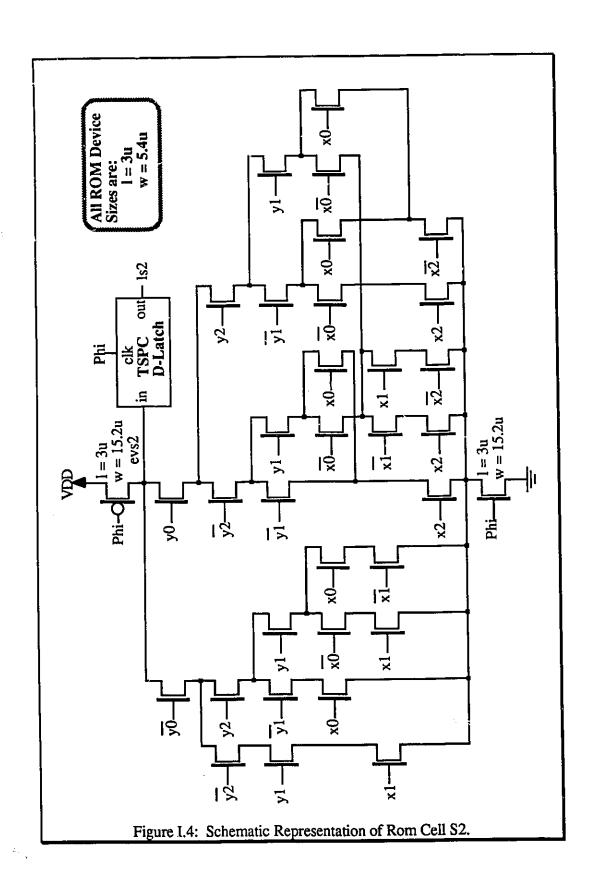

| I.4         | Schematic Representation of Rom Cell S2                    | 182 |

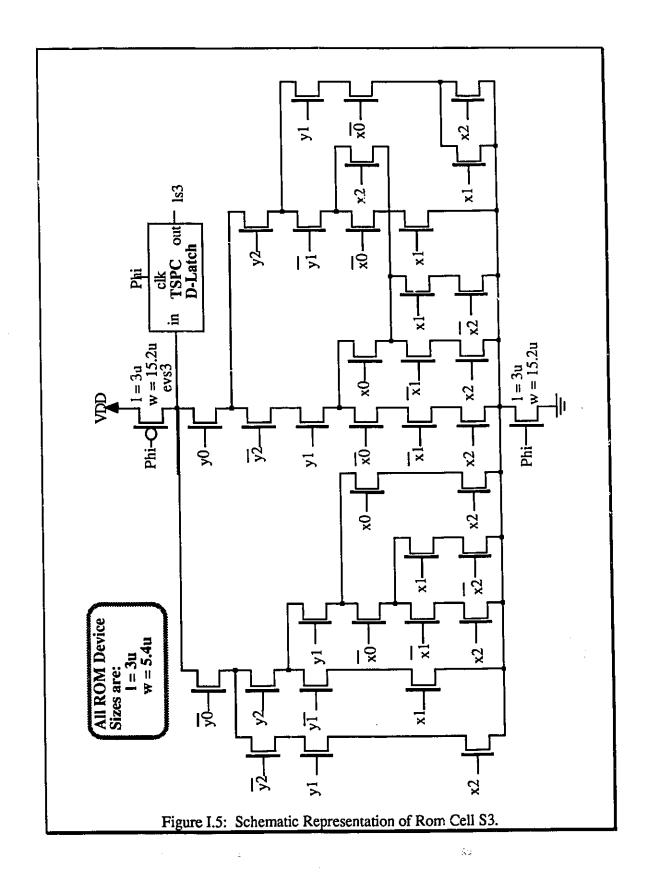

| I.5         | Schematic Representation of Rom Cell S3                    | 183 |

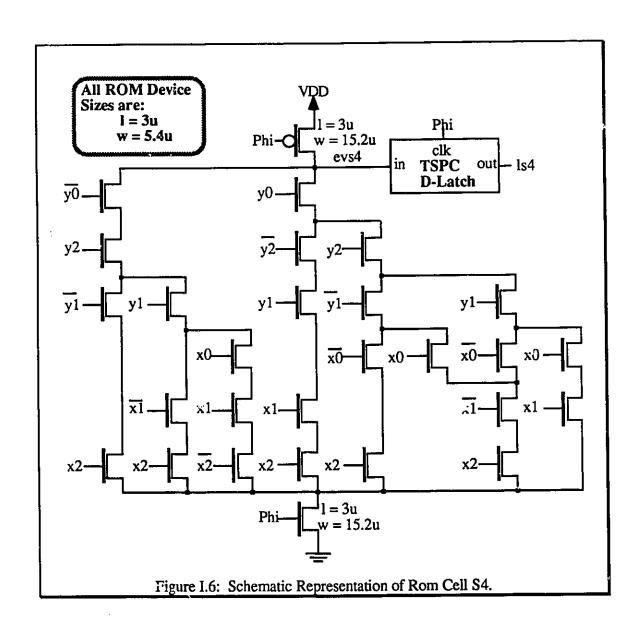

| I.6         | Schematic Representation of Rom Cell S4                    | 184 |

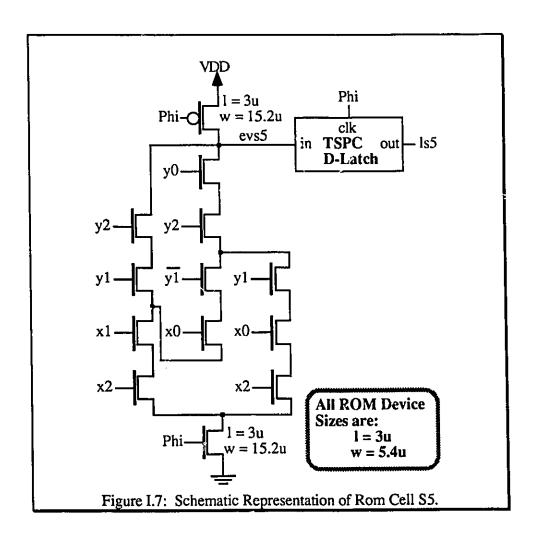

| I.7         | Schematic Representation of Rom Cell S5                    | 185 |

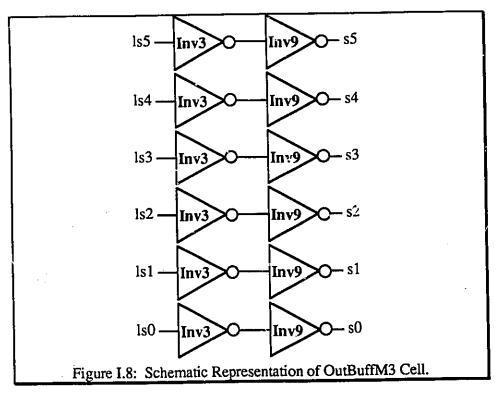

| 1.8         | Schematic Representation of OutBuffM3 Cell                 | 186 |

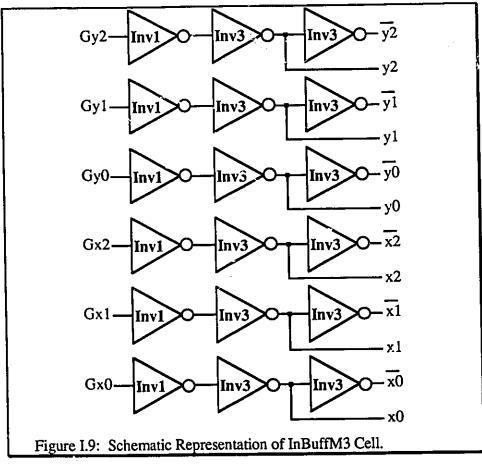

| 1.9         | Schematic Representation of InBuffM3 Cell                  | 186 |

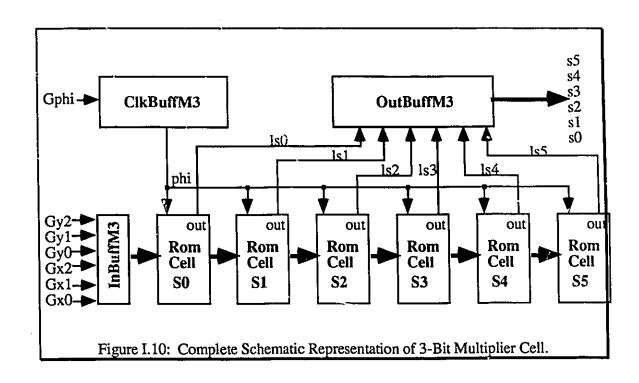

| 1.10        | Complete Schematic Representation of 3-Bit Multiplier Cell | 187 |

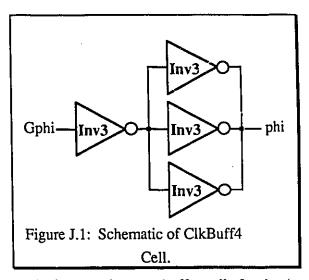

| J.1         | Schematic of ClkBuff4 Cell                                 | 189 |

| J.2         | Schematic Representation of Rom Cell S0                    | 189 |

| J.3         | Schematic Representation of Rom Cell S1                    | 190 |

| J.4         | Schematic Representation of Rom Cell S2                    | 191 |

| J.5         | Schematic Representation of Rom Cell S3                    | 192 |

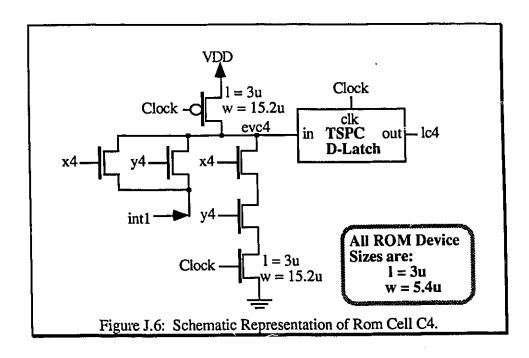

| J.6         | Schematic Representation of Rom Cell C4                    | 193 |

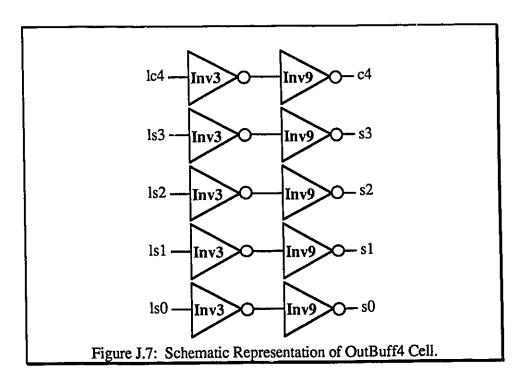

| J.7         | Schematic Representation of OutBuff4 Cell                  | 193 |

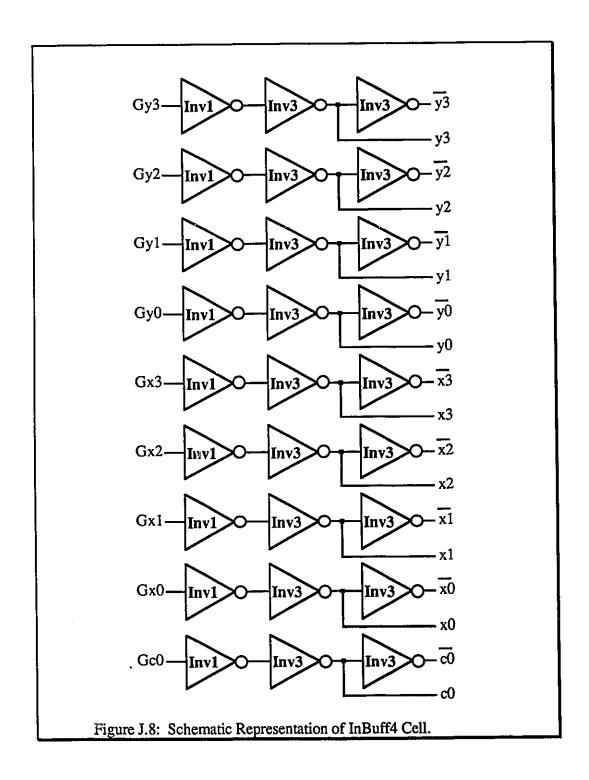

| J.8         | Schematic Representation of InBuff4 Cell                   | 194 |

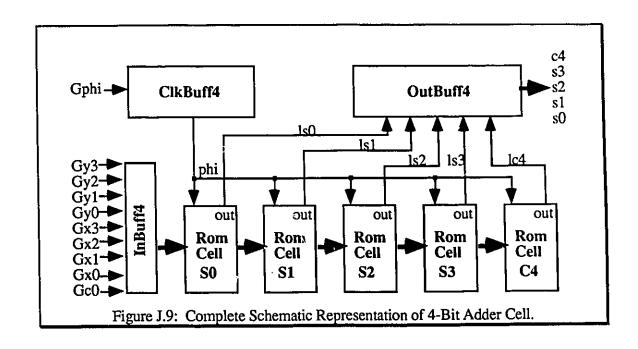

| 19          | Complete Schematic Representation of 4-Bit Adder Cell      | 195 |

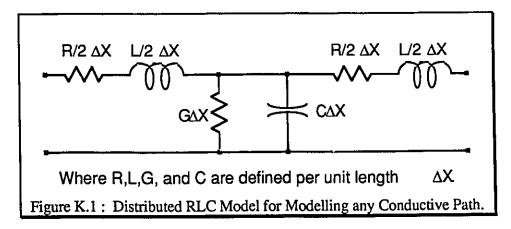

| K.1 | Distributed RLC Model for Modelling any Conductive Path | 197 |

|-----|---------------------------------------------------------|-----|

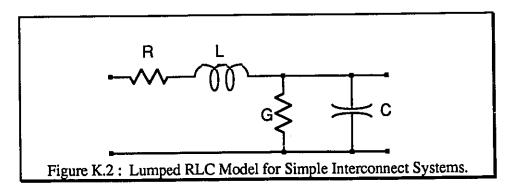

| K.2 | Lumped RLC Model for Simple Interconnect Systems        | 198 |

#### LIST OF TABLES

| 2.1 | Interconnect Capacitance Values of Bell Northern 3µ CMOS Process | 12  |

|-----|------------------------------------------------------------------|-----|

| 3.1 | Summary of Test Results on IC3WROMB                              | 48  |

| 3.2 | Possible Two Dimensional ROM Arrangement                         | 51  |

| 3.3 | Possible N Dimensional ROM Decomposition                         | 51  |

| 3.4 | Summary of Test Results on Test Chip IC3WRRJT                    | 58  |

| 3.5 | Summary of Test Results on Test Chip IC3WRXLT                    | 58  |

| 3.6 | Summary of Test Results on Test Chip IC3WRJET                    | 58  |

| F.1 | Summary of Test Data from Testing of ICAWRIOT                    | 148 |

# CHAPTER 1 INTRODUCTION

#### 1.1 INTRODUCTION

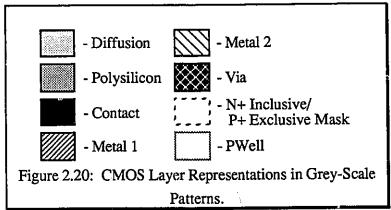

Over the past decade or so, semiconductor research has made significant advancements in the development of smaller and faster technologies. The development of Metal Oxide Semiconductor(MOS) technology, particularly the n-channel or NMOS technology, has revolutionalized the semiconductor industry and spawned a new era with the advent of the micro-computer chip. The main building block of NMOS is the n-channel field effect transistor (NFET) device. The basic structure of the NFET is illustrated in Figure 1.1.

NFET devices can be classed into two types; enhancement(E)-mode and depletion(D)-mode. Both devices have a conducting channel which varies its conductance with applied gate voltage; the depletion-mode device has a conducting channel present with zero gate to source potential, the enhancement-mode requires a threshold voltage to be applied before a channel is present. In NMOS technology, the depletion-mode device is used as a load. The presence of a conducting channel at all times, guarantees that the output of the gate will reach the supply voltage for a logic '1' output [1]. Figure 1.2 shows the standard NMOS circuit design technique which utilizes the depletion-mode active pull-up device.

Using this NMOS technology, it is possible to pack thousands of NFET transistors onto a single chip and perform complicated logic functions. The complexity of the logic functions is limited due to the large static power

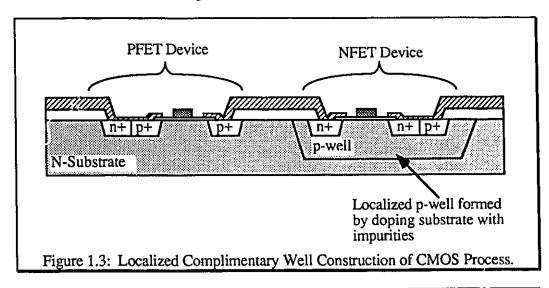

dissipation associated with large numbers of NMOS logic circuits; this limits the number of devices that can be adequately fabricated on a single chip using this technology. An alternate technology, CMOS (Complimentary Metal Oxide Semiconductor) uses, for example, p-type wells as 'surrogate' substrates diffused into an n-type substrate, allowing for the construction of both n-channel and p-channel devices on a single silicon substrate, as illustrated in Figure 1.3. Having both types of transistor allows the design of a logic family, commonly referred to as standard CMOS logic, which dissipates almost no static

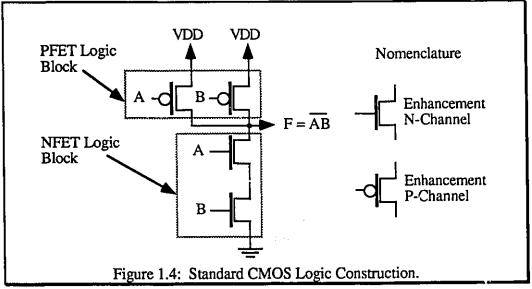

power. Standard CMOS logic is constructed out of two logic blocks, one built from NFET devices and the other from PFET devices, as shown in Figure 1.4. The two blocks perform complementary logic switch functions, and hence, for any given input, only one block will provide a path between the output node and one of the power supply rails. This reduced power dissipation and also improvements in state-of-the-art denser technologies allowed devices to be packed closer together and increased the level of functional complexity that could be placed on a single chip. Standard CMOS logic construction, however, has several disadvantages.

The mobility of holes, the majority carriers in the conducting channels of p-channel devices, is about 1/3 that of electrons, the carrier in n-channel devices. In order to provide channels with approximately the same conductance in both the n-channel and p-channel devices, the widths of the PFETs have to be increased. This increases the size of each logic gate and also increases the dynamic switching current due to the increased parasitic capacitance associated with the larger devices. It is possible to replace the PFET block with a single p-channel transistor, if special dynamic logic circuits are used. These logic circuits use temporary memory (stored charge on parasitic node capacitances) to replace the pull-up PFET logic block, thus reducing the size; the speed of dynamic logic circuits is also usually higher than that for static logic circuits because of the reduced load capacitance.

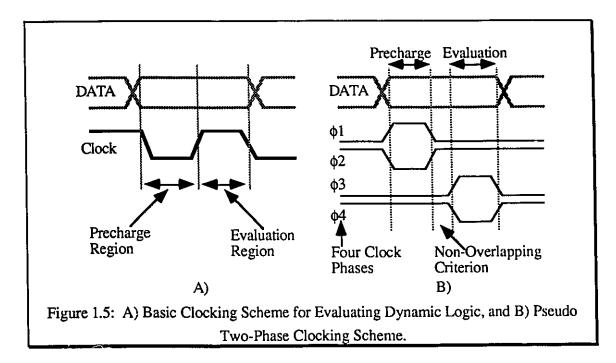

Dynamic logic families require the use of clocking schemes to first precharge the logic block and then allow it to evaluate, as shown in Fig. 1.5(a). A popular clocking technique is the pseudo two-phase clocking scheme which requires the routing of four non-overlapping clock signals, as illustrated in Fig. 1.5(b). This technique suffers from clock skew problems brought about by process deviations across the surface of large chips. Clock skew is associated with the delay experienced by clock signals as they are distributed along metal conductors across large chips. Since clocks are meant to synchronize logic circuits, synchronizing delays between one part of the circuit and another can often cause soft failures; this is particularly critical if several clocks are required for the synchronizing process (often a requirement in dynamic logic circuits). As chip areas increase, it is necessary to decrease the maximum clock rate so that the skew delays can be kept within timing tolerances. Dynamic circuits that use single phase clocks are clearly to be preferred. DOMINO [2][3][4] logic and NORA [5][6] logic are two dynamic logic families that operate with reduced numbers of clock lines. Recent results have produced, in dynamic logic, the equivalent of the edge triggered latch in static logic [7]. Thus dynamic circuits can

be synchronized with single phase clocks, reducing the clock skew problem to manageable proportions.

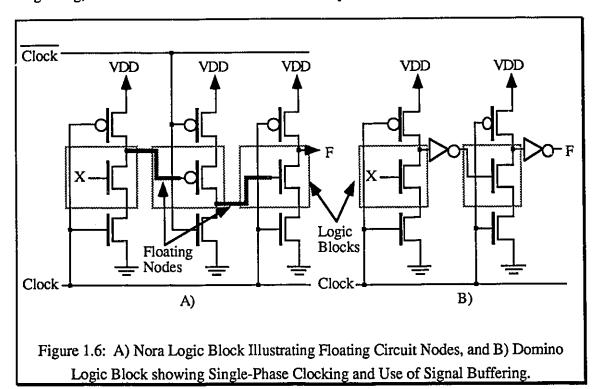

NORA logic utilizes a true two-phase clocking scheme; however, the logic suffers from noise margin degradation due to the lack of signal buffering. It is also very susceptible to capacitively coupled noise injection due to floating nodes found in the circuit path, as is illustrated in Fig. 1.6(a). The logic can be used to form a natural pipeline, since stages alternate precharge and evaluate, and so has been seriously considered for digital signal processing circuits, where throughput is more important than computational time.

Domino logic, as illustrated in Fig 1.6(b), utilizes a single-phase clock; every dynamic evaluation node, which is buffered with an inverter to prevent race conditions, maintains good noise margins. Domino logic cannot perform logic inversion, therefore complementary function Domino circuits are often required, which place large penalties on the overall area requirements. Domino logic forms a dynamic combinational chain that requires the placement of a static latch, at the end of the chain, to capture the output result.

Since inversion can easily be performed along with the static latch function, we can sometimes design the Domino chain to not require inversion; rather we perform it at the beginning, or wait until the end. This does not always work, however.

One thing that all dynamic logic families have in common is that they implement a logic function through the use of a single logic block per stage, usually in the form of NFET devices which are arranged to implement a truth-table and can be thought of as a ROM (Read Only Memory) block, since the functionality is fixed at fabrication. This concept has led to much research and development in the area of ROM and programmable ROM structures. All ROM structures possess an area of devices which defines the programming of the ROM by the placement and absence of devices. The general shape of the ROM is dictated by the input signal decoding method which places conformal restrictions on the ROM's construction. Some ROM structures utilize a decoder network which produces two fields of output corresponding to cross-point information. This type of decoder network requires the ROM to be in the form of a two dimensional structure and

programing is done by placement of devices at the intersection of row and column signals. Though two dimensional decoding is the most obvious and popular method of decoding ROM structures it is possible to create multi-dimensional ROM structures. As the dimensionality of the ROM structure increases, the complexity of the decoder network decreases. Thus if the ROM dimensionality is taken to the extreme, meaning the ROM is addressed as an 'n' dimensional structure, where 'n' is defined as the number of input bits addressable by the ROM. The resulting ROM structure is known as a Binary-Tree or Switching-Tree illustrated in Fig. 1.7, and the decoder network resolves down to 'n' inverters.

The complexity of the logic function which can be implemented using Switching-Trees is directly related to the height of the Switching-Tree, 'n'. In looking at the full Switching-Tree, Fig. 1.7, programming is done by leaving or removing the last device in each branch of the tree, which effectively creates or removes a path to ground for that particular branch. Once certain devices are removed this makes other devices in the tree no longer necessary or redundant. Thus the ROM requires to be minimized which removes

the redundant devices and increases the packing density of the ROM. This procedure though upsets the capacitive balance of the ROM's internal nodes, which can lead to charge sharing and charge redistribution problems. These issues need to be resolved in order to achieve a suitable and reliable logic block. Thus Switching-Trees are dynamic logic blocks which implement arithmetic functions which can be expressed in truth-table, or minterm fashion. Switching-Trees attempt to increase the functional density of logic circuit techniques as well as increasing operating speeds of standard CMOS technologies.

#### 1.2 THESIS ORGANIZATION

This thesis deals with the physical development of digital switching tree structures, which were implemented using dynamic logic blocks utilizing true single phase clocking techniques as well as true single-phase latches developed by Yaun & Svensson [7]. The body of this work represents the authors contribution in the team effort look into the automated design, of on the fly development, of standard switching tree cells for the implementation of random truth table, or minterm description of digital logic. This work consists of generating a library consisting of dynamic logic blocks designed using heuristic layout techniques for constructing the ROM portion of the switching tree's cells. The cells were generated by software known as 'WOODCHUCK' developed by Roger Grondin[8]. As part of the fixed cells in the library, I/O(Input/Output) pad drivers were developed to handle the increased speeds of the switching-tree structures.

Chapter II deals with practical design and layout considerations attained through years of layout experience. The chapter covers methods of improving pre-layout SPICE simulations, different device layout techniques, as well as summary of helpful hints.

Chapter III will document the development of digital switching trees, tracing through the three iterations of ROM cells. A close examination of dynamic logic as well as clocking techniques for fully pipelined bit serial architectures will be covered.

Determination of ROM-tree limitations with respect to tree heights and evaluation speed will be discussed. The evaluation of ROM-tree efficiency will also be examined using a speed, area, and power product for comparison purposes, and a heuristic rule set for performing personalized layouts of ROM-tree structures will be given.

Chapter IV presents a set of cells developed in the Bell Northern  $3\mu$  CMOS technology which represents the switching tree standard cell library. The standard cell designs were developed as proof of concept designs. Included in the library is a set of ECL compatible I/O pads developed to handle the increased speed of the switching tree cells.

Chapter V offers a summary and conclusions of the work done as well as outlining future work direction.

### CHAPTER 2

THE ART OF DESIGN

#### 2.1 INTRODUCTION

As the title suggests, designing and laying out integrated circuits is as much an art as it is a science. How the designer chooses to assemble a circuit can dramatically influence the circuit's performance. Often the success or failure of a novel architecture may very well rest on the ability of the designer to fully utilize the technology which is being used for implementation. Thus this chapter will be devoted to discussing practical design and layout considerations attained through experience. It is the author's intention to impart some practical knowledge of VLSI design to new designers.

This chapter will be divided into two main sections. The first section will discuss dealing with circuit capacitance and capacitive loading effects, which are major issues in the design of high speed circuitry. The discussion will examine the origins of parasitic device capacitance and interconnect capacitance. Methods for estimating, and improving initial SPICE circuit simulations will be discussed through the use of examples. The second section of this chapter will deal with developing practical design experience. Very often the novice designer may develop a design which may meet all the design specifications but, due to poor judgement or lack of experience, the designer may construct the design in such a manner as to severely limit the design's capabilities.

#### 2.2 DEALING WITH CIRCUIT CAPACITANCE

There are two main sources of circuit capacitance in CMOS circuits. The first source is known as parasitic device capacitance which is, most often, unwanted capacitance associated with the physical construction of a MOS device. Parasitic device capacitance exists between the three terminals of the MOSFET device and the bulk substrate connection. The local substrate or well of a MOSFET device lies directly under the device and comprises one combined plate of three parallel plate capacitors. The other plates are the drain, source, and gate region of the MOSFET device. For an in-depth discussion of the device physics with respect to capacitance refer to reference [9].

The second form of circuit capacitance exists between the interconnect layers of the CMOS technology and the substrate. As mentioned previously, all circuit components in a CMOS technology are designed on a silicon substrate, with layers of insulation between each layer. Thus all layers in the CMOS process will exhibit capacitance to the substrate; the magnitude is dependent on the position of that layer with respect to the substrate. This is why polysilicon, which is closer to the substrate than the metal interconnect layers, exhibits the highest capacitance per square. This value is even greater for the gate area where the polysilicon is separated from the substrate by only thin-oxide. The greater the thickness of total oxide between the layer and the substrate the lower the capacitance. Thus metal two, which is the top layer, has less per square capacitance than metal one, and metal one has less per square capacitance than polysilicon.

The capacitance associated with the interconnect layers is comprised of two components. The first component is the value of capacitance which exists between the two surfaces that comprise a parallel plate capacitor, neglecting any fringing effects of the electric field. This value of capacitance is defined in terms of area, and is derived from the microstrip-line capacitor model[10]. The second component which makes up the

interconnect capacitance is the edge component, which is due to the fringing effect of the electric field at the edges of the conductor. The edge component arises from the fact that the conductor has a relatively large thickness, which means that a vertical surface exists on the conductor which will produce arched electric field lines to the flat substrate surface below. The edge component is defined in terms of units of edge length. In comparing the relative lengths of the electric field lines, illustrated in Fig. 2.1, one can see that the edge component value will be smaller in size. The values of capacitance for the interconnect layers in the Northern Telecom  $3\mu$  CMOS process are listed in Table 2.1, along with values for a  $100\mu$  run of minimum width interconnect [11]. These values can be used to estimate interconnect capacitance of circuitry.

| Table 2.1: Interco | Table 2.1: Interconnect Capacitance Values of Bell Northern 3µ CMOS Process. |                          |                                |  |  |

|--------------------|------------------------------------------------------------------------------|--------------------------|--------------------------------|--|--|

| Layer to<br>Field  | Capacitance (in ff/µ <sup>2</sup> )                                          | Edge Component (in ff/μ) | Total Capacitance (in ff/100μ) |  |  |

| Polysilicon        | 6.0e-2                                                                       | 5.0e-2                   | 28.0                           |  |  |

| Metal 1            | 2.7e-2                                                                       | 4.0e-2                   | 16.1                           |  |  |

| Metal 2            | 1.4e-2                                                                       | 2.0e-2                   | 8.2                            |  |  |

#### 2.2.1 CIRCUIT MODELLING FOR PROPER DESIGN

In order to create a preliminary SPICE simulation of new circuitry which will accurately reflect the performance of the design once it has been laid out, great care must be taken to provide the simulation package with the appropriate circuit models. All SPICE device models require a model-card which lists important device parameters. Often the model is over specified in that some of the parameters can be calculated from a subset of the others. A choice is available to substitute the calculation with a single parameter value. Many of the parameters have default values; since errors are not generated if parameters are not provided (defaults substituted) it is important to examine the model parameters carefully if the defaults are not acceptable. In addition to the device models, device sizes are required. Since accurate values of perimeter and area of the source and drain nodes are required for each device, these values are most often generated from mask extractions; for preliminary designs good estimates must be obtained. Reasonable estimates of interconnect capacitance should also be added to preliminary simulation descriptions (accurate values are usually obtained from a good extraction utility for final simulations). Designers must therefore have an idea for the method in which each device will be laid out prior to constructing the SPICE-deck, and section 2.3 will discuss different transistor arrangements and how to determine their relative geometric measurements.

The first step to producing an accurate simulation description is to carefully parameterize the circuitry driving the circuit under consideration. It is essential to provide input signals with limited driving capability which accurately reflects the environment in

which the circuit will have to function. Proper placement of all input signals in time, with relationship to control signals arriving at the cell boundary, is important for guaranteeing realistic time dependent behavior. This can be done very simply by using an inverter, a capacitor, and an ideal source to accurately model the input circuit behavior, as illustrated in Fig. 2.2. The sizes of MN1 and MP1 can be taken from the last stage of the preceding input circuitry, if it is known, or a best guess will do. The input loading capacitance is critical as it dictates the general shape and relative signal delay of the input signal. The time placement of each input signal can be adjusted in the ideal input source signal description.

Accurate estimates of the loading effect of the driven circuit at the output of the circuit under simulation, have to be provided for the initial simulation. The load takes the form of lumped capacitance representing the interconnect and gate capacitance of the following stage, as

in Fig. 2.3. The value of the output capacitance can be varied through a number of SPICE simulations and the resulting data can be compiled to determine the performance of the circuit with respect to variations in output loading. An example of this will be carried out in the following section. Note that if SPICE has trouble converging in the initial DC analysis, or develops TIME-STEP-TOO-SMALL errors, then splitting the single load capacitor, as indicated in Fig. 2.3b, often corrects the problem. If this does not help, increasing the size of the capacitors by a factor of 2 or more can help. This can also be performed on internal circuit nodes which are highly isolated and have only a single capacitance value between that node and a power rail. In these cases, during high-impedance conditions, the SPICE

software may not converge in the initial DC analysis due to mathematical limitations associated with the finite precision representation of data. By replacing the capacitor by an equivalent voltage divider structure and slightly increasing its value, can sometimes eliminate the convergence problem without totally upsetting the circuits behavior.

#### 2.2.2 PARAMETERING A CIRCUIT BLOCK

To simulate large circuit designs comprised of thousands of devices, which would create too many variables for SPICE type packages, will require the use of a Digital Simulation package. Digital simulation packages require well parameterized models of the small building block or sub-circuits, in order to accurately perform an accurate timing analysis of the complete circuit. In this section we will take take two standard cells as examples and fully parameterize them, listing all necessary information required for digital circuit simulation.

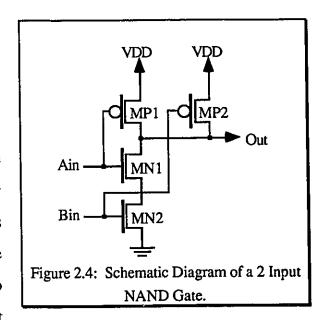

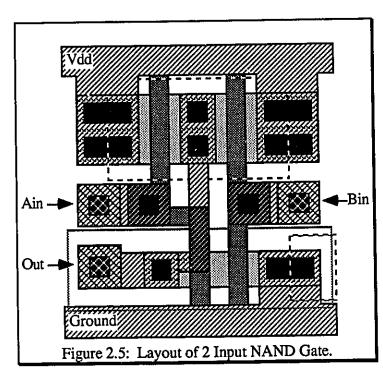

The first circuit to be considered will be a simple NAND gate. The circuit diagram for the standard cell is shown in Figure 2.4 and the layout of the cell is shown in Figure 2.5. Looking at the circuit diagram it is obvious that the only path to ground for the output node is through two series NMOS devices, while two paths to VDD exist through two single PMOS devices. Since the current

mobility is approximately three times greater for the NFETs than the PFETs, the normal scaling of device widths will be three to one in order to achieve equal pull-up and pull-down times (switching times). But since the NMOS devices are in series, it is necessary to

increase the size of the two series NMOS devices by a factor of two in order to maintain equal switching times. Thus the PMOS devices will require to be only 1.5 times larger then the NMOS devices to achieve equal switching times.

The NMOS devices used to construct the gate have widths approximately twice those of a minimum size device, or simply, 2 α (alpha) devices, where α implies the minimum device size for the technology. The PMOS devices are then appropriately scaled. The mask-extracted SPICE deck is given in Fig. 2.6.

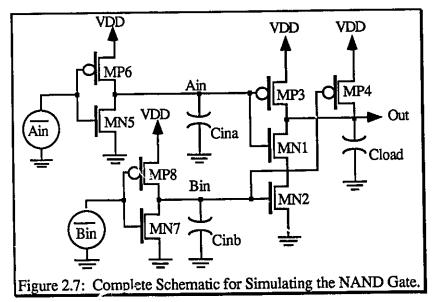

To finish

the SPICE-deck, we

add the input and

output circuitry

descriptions, as

discussed in section

2.2.1. The resulting

circuit to be simulated

is illustrated in Figure

2.7, and the additional

circuit information is given in Figure 2.8. The input signals that will be used to drive the cell are chosen so to always exercise the critical path in the cell. Since all paths in this cell

have the same delay, it will suffice to have the cell switch from a high to low output and then back. Ain and Bin signals will be defined to perform this input switch.

```

***************

* n-channel enhancement mosfets extracted from*

*mask layout follow.*

mn1 out ain 3 0 ntran w = 0.54e-05 l = 0.3e-05

+ad= 0.3888e-10 as= 0.81e-11 ps= 0.84e-05 pd= 0.252e-04

+nrd= 0.13333e+01 nrs= 0.27778

0 bin 3 0 ntran w = 0.54e-05 l = 0.3e-05

+ad = 0.3564e-10 as = 0.81e-11 ps = 0.84e-05 pd = 0.24e-04

+nrd= 0.12222e+01 nrs= 0.27778

***************

* p-channel enhancement mosfets extracted from*

*mask layout follow.*

****************

mp3 vdd ain out vdd ptran w = 0.162e-04 = 0.3e-05

+\bar{a}d = 0.10692e-09 as= 0.729e-10 ps= 0.252e-04 pd= 0.456e-04

+nrd= 0.40741 nrs= 0.27778

mp4 vdd bin out vdd ptran w=0.162e-04 l=0.3e-05

+ad= 0.10692e-09 as= 0.729e-10 ps= 0.252e-04 pd= 0.456e-04

+nrd= 0.40741 nrs= 0.27778

**********

* parasitic node capacitors follow*

**********

cn1 ain vdd 0.83956e-14

0 vdd 0.12475e-13

cn2

cn3 out vdd 0.18296e-14

cn4 bin vdd 0.70756e-14

cp1 ain 0 0.1644e-14

0 out 0.22552e-14

cp2

0 bin 0.1644e-14

cp3

**************

* parasitic coupling capacitors follow*

cc1 ain out 0.162e-14

Figure 2.6: Mask-Extracted SPICE-Deck of 2 Input NAND Gate.

```

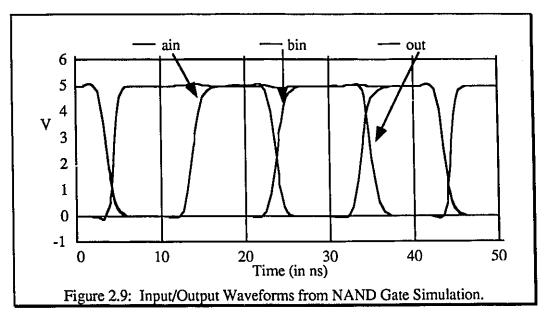

A set of nine SPICE runs will now be performed varying the load capacitance, Cload, from 50 to 500ff in 50ff increments. A set of input and output waveforms are illustrated in Fig. 2.9 showing the cell's functionality. A close-up view of the entire set of outputs for the nine runs is shown in Fig. 2.10 illustrating the variation in the gate-delay as a function of load capacitance. The gate delay for the cell is defined here by measuring the time between the 50% edge points of the input and output signals. Taking the acquired data and using a polynomial curve fitting program, as illustrated in Fig. 2.11, it is possible to produce an equation for the gate delay of the circuit with respect to load capacitance. This equation can then be used in a gate level simulator to perform switch level simulations of an entire chip composed of parameterized sub-cells. The resulting gate delay is given by eqn. (2.0).

Gate-Delay =

$$0.94727 + 9.3196e-4*C_{load} + 2.3683e-5*C_{load}^2 - 2.6154e-8*C_{load}^3$$

(2.0)

```

***************

Input Circuitry '

pulse(0.05 4.95 1ns 3ns 3ns 7ns 20ns)

ainb

pulse(0.05 4.95 1ns 3ns 3ns 17ns 40ns)

vbin

ntran 1=3u w= 5.4u pd=19.8u ad=38.88p

mn 1001

ain

ainb

ptran 1=3u w=16.2u pd=30.6u ad=116.6p

vdd

ainb

vdd

mp1002

ain

ntran 1=3u w= 5.4u pd=19.8u ad=38.88p

O

bin

binb

mn1003

ptran 1=3u w=16.2u pd=30.6u ad=116.6p

mp1004

bin

binb

vdd

vdd

0

100ff

cain

ain

100ff

cbin

bin

0

Output Load

0

100ff

cload

out

*******************

Figure 2.8: Additional Devices Added to the Original SPICE-Deck.

```

The power consumption of complex circuitry can also be determined through similar SPICE simulations, where both speed and load conditions need to be varied. For this static CMOS logic circuit the power consumption will be linearly dependant on the output load capacitance times the frequency to which that load capacitance is charged and discharged [12]. Thus running a large set of SPICE simulations would be a waste of time.

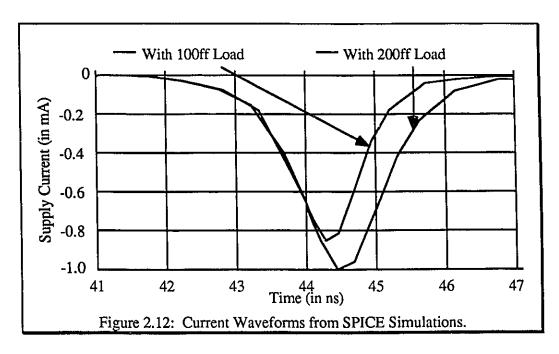

Instead if the switching current of the circuit is examined for two known load capacitances, then an equation can be determined to predict the power consumption of the circuit under

small variations in load conditions. In order to do this properly, the circuit under analysis must have its supply source isolated from the rest of the circuitry. The current waveforms in Figure 2.12 represent the supply current demanded by the NAND gate when driving a 100ff and 200ff load. By determining the energy drawn from the supply during switching, which is the area under the current 'spike' multiplied by the voltage of the power rail, then an equation can be determined for the power consumption as a function of load capacitance. The two values for power dissipation were determined to be 5.5 and 8.5mW/cycle. The equation for the power dissipation for the static CMOS NAND gate will take the form:

Pdiss=

$$(p_0 + p_1*C_{load}/100)*freq_{out}$$

mW

The determined power dissipation equation is given in eqn. (2.1).

$$P_{diss} = (2.5^{c-12} + 3.0e^{-12} * C_{load} / 100ff) * freq_{out} mW$$

(2.1)

The next issue that will be examined is that of determining proper signal placement for cells that require clock synchronization.

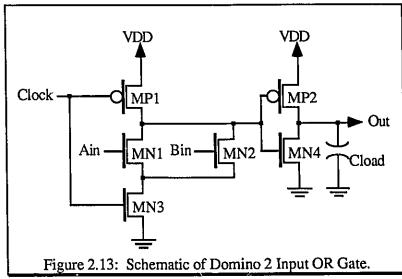

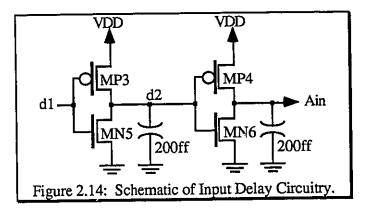

The cell that will be examined will be composed of a Domino

style 2 input OR gate, illustrated in Figure 2.13, and two inverters. See Appendix A for a summary of the domino logic family. For the purpose of this discussion, the cell in question will represent a complex logic block that has some static logic connected to the inputs, possibly comprising a decoder network with outputs having different critical path delays. To accomplish this the inverters will be placed in series with the 'Ain' input as illustrated in Figure 2.14. The other portion of the cell represents a functional block, namely the 2 input OR gate, which has clocking signals associated with it.

This portion of the cell may represent a complicated function designed in a non-race logic family like Domino Logic, or it may be a RAM or ROM based lookup table. The following discussion will explain the need

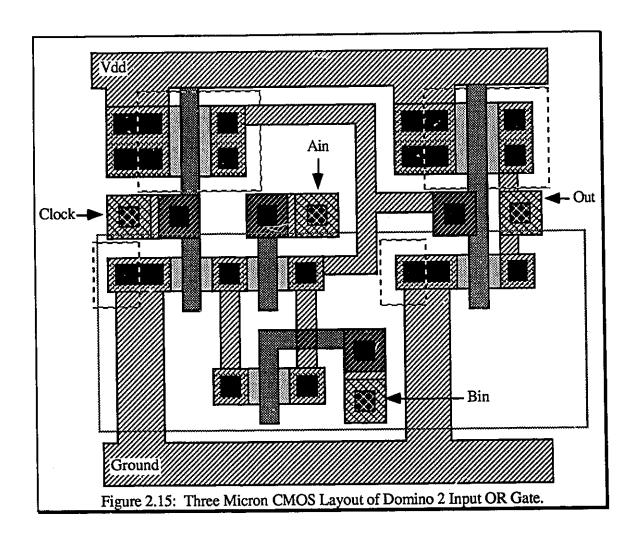

for determining proper setup and hold times as well as how to determine maximum clock speed. The layout of the Domino 2 input OR gate is shown in Figure 2.15.

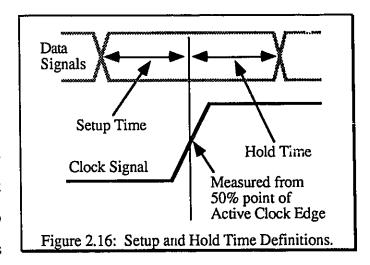

The term setup-time implies the time that the input signals must be stable before clocking of the cell can take place in order to guarantee correct results. The term hold-time implies the time that the input signal must be maintained after the clocking edge to insure correct functionality. These concepts are illustrated in Figure 2.16. Both of these terms are defined as minimum values since larger setup and hold times will always ensure functionality provided the data edges do not fall outside the window of the clock cycle. The setup and hold times for a circuit can be found by performing iterative SPICE runs and decreasing one of the values while holding the other constant. In order to do this, a complete SPICE-deck must be created which contains all input and output modelling circuitry. After experimenting with the signal edge placements with respect to the clock edge, to ensure functional simulations results, the iterative process can begin.

Since the cell being examined has only a single Domino logic block, there is no need to determine input signal hold time, as that is fixed to the width of the evaluation clock pulse as defined by the Domino logic family. So the only values

which the designer is concerned with are the input signal setup times, and the maximum evaluation time of the cell, which will determine the maximum clocking speed of the cell. This can be performed by a set of iterative SPICE runs to determine the minimum setup time. Each SPICE run will increase the delay of the clock signal hence increasing the setup time of the input signals. It is important to point out that if the SPICE software fails to run properly and sites an inability to attain DC convergence or a time-step-to-small error, this has no implication on the maximum performance of the circuit under test. It is merely an

inability of the software to produce results. Thus unless a SPICE run completes and indicates a functional failure, then no presumptions should be concluded about the circuit performance.

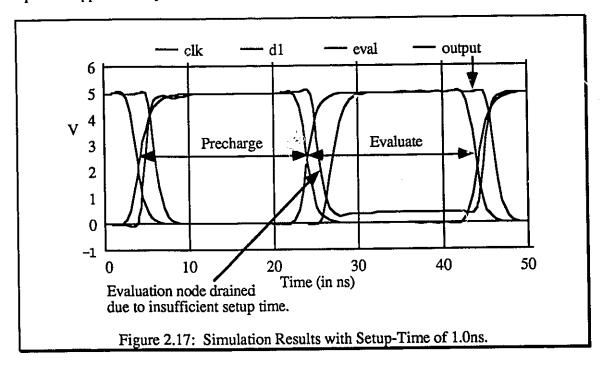

A complete SPICE-deck for the domino circuit can be found in Appendix II. The circuit is loaded down with a 200 ff load capacitance. Several initial SPICE simulations were performed to setup the initial input signals for proper functionality. The clock frequency for the simulations was chosen at a mid-range operating frequency of the technology; 25 Mhz. Moderate input signal edge times of 3 nanoseconds were chosen to ensure a realistic simulation of these signals at the gate inputs. The results of the iterative simulations, to determine the minimum value of setup-time, are illustrated in Figures 2.17 through 2.19. From these simulations it is determined that the minimum setup time required is 3ns. It can also be determined that, under the specified output load conditions, the maximum evaluation time for the cell is 5.3ns. Thus, assuming that the clock signal has a 50% duty cycle, then the minimum clock period is 11ns indicating a maximum clocking speed of approximately 90 Mhz.

# 2.2.3 SUMMARY OF MODELLING

The last few sections have indicated the need for accurate assessment and modelling of I/O specifications. This can be done through the use of simple circuitry and the application of some common sense. Furthermore, the modelling process requires the need

to predetermine how devices are to be designed, which has a large bearing on the intercircuit parasitic capacitance associated with the devices. Lastly, the simulations are necessary for determining gate-delay and cell evaluation times in order to accurately parameterize sub-cells for the use of digital simulation packages in order to accurately simulate large networks.

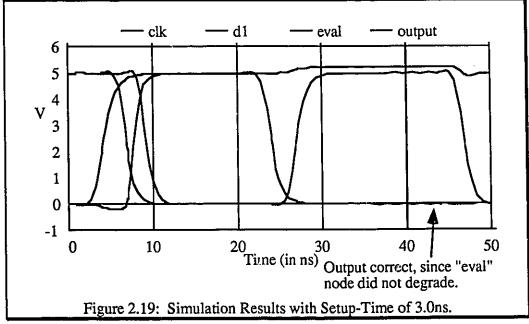

# 2.3 DIFFERENT TRANSISTOR CONFIGURATIONS

The following section will examine device lay-out configurations. To simplify the figures, some layers may be purposely left out. Figure 2.20 illustrates the standard

CMOS layer representations using simple gray-scale patterns.

### 2.3.1 THE BASIC TRANSISTOR LAYOUT

A simplified view of an NMOS transistor is illustrated in Fig. 2.21. The device illustrated has its well biased through the use of the split-contact on the source node. The split-contact in effect biases the local substrate to the ground potential. If the split-contact is replaced with a normal contact, then the two terminals would become interchangeable and their designation of source or drain terminal would be dependent on the respective terminal voltages. Note that each device well on a silicon substrate requires biasing, so that if a device is constructed without the split-contact on the source node, than a well plug will have to be placed somewhere in the local well.

This Figure also illustrates how to properly determine the length and width of the gate, drain, and source regions of the device.

In determining the area and perimeter of device nodes, the following equations are used:

Area(drain, gate, and source) = Length x Width

$$(2.2)$$

Perimeter(drain or source) =

$$2 \times Length + Width$$

(2.3)

Note that the perimeter of the drain and source regions consists of only three sides of the rectangular region. This is because the side adjacent to the gate region does not contribute any parasitic capacitance to the circuit because no real edge is formed with the substrate.

# 2.3.2 PARALLEL DEVICES WITH MERGED DRAINS

. .

The devices illustrated in Fig. 2.22 are comprised of two similar devices merged at the drain node, so as to share only one drain contact and a single polygon of diffusion. The two sources are tied together with metall. The resulting device will have the same effective gate width equal to the sum of the two devices gate widths, 2W. The main component of the drain capacitance has been reduced by a factor of 1.6, while the edge

component has been reduced by a factor of (24 + gatelength)/15, where gatelength is in design scale microns.

Thus a minimum gatelength of 9 design scale microns results in a parasitic drain capacitance to gate length ratio of approximately 1.87:1, normalized to a standard device. This ratio increases to a value of 3.12:1 when the device width is increased to 50 design scale microns. This merged design substantially reduces the loading of the output of the device by reducing the overall capacitance found at the drain node. The driving capability of the device is also enhanced since the parallel device has an overall lower 'on' resistance compared to a standard device with the same total gate length. The parallel device also provides an efficient method of creating large devices. This is illustrated in Figure 2.23 with the parallel design of a large inverter. Note the convenient routing of the power and ground rails in metal1. This allows for multiple cells to be connected in a linear array, as shown in Figure 2.24. Also note the placement of input and output connections with vias connecting to metal2. This allows the use of metal2 for the global routing of input and output signals. It is important to note that the vias in the cell are also aligned which allows for greater use of cell space for routing metal2 interconnect, since if the vias were randomly placed in the cell they would tend to block a large portion of the cell area against routing of metal2 signals.

## 2.3.3 DOUGHNUT DEVICES

The doughnut device is a logical extension of the parallel merged device. It offers an even higher parasitic drain capacitance to gate length ratio of 0.393 + 0.0781\*X, where X equals the length of the main straight section of gate measured from the diffusion edge to the inside corner of the polysilicon, and X must be greater than or equal to 12 design scale microns in order to be constructed. This gives a minimum dimension doughnut device a ratio of 1.33:1, when normalized with a standard device, which is poorer than a parallel merged device with an equivalent gate length, but a device of X equal to 50 design scale microns has a ratio of 4.75:1, which improves upon the parallel merged value of approximately 3.2:1. The doughnut device thus can offer a more efficient device which has less effective drain capacitance per unit of gate length when the required gate length is quite large. Figure 2.25 illustrates a) an unbiased, and b) a well-biased doughnut device. These devices, though offering better drive capability, tend to create less efficient layouts and hence should only be used where they are absolutely required.

### 2.4 PRACTICAL LAYOUT CONSIDERATIONS

The following is a collection of design techniques attained through several years of experience in chip designing and testing by the author.

## 2.4.1 GENERATING PAD FRAMES

The following points should be noted when determining the numbers of pads (pin count) required for a given test design:

- 1/ Bring all output signals to individual pins. Do not multiplex output pads unless it is absolutely necessary; if the output signals connected to that pad fail, there will be no way of absolutely determining what caused the failure.

- 2/ Use individual clock signals for each test structure on the chip, which are brought in on individual pins. This will allow for individual structures to be clocked while all others remain stopped. This will reduce the amount of noise during testing and will allow for the measurement of dynamic and static currents of the individual structures.

- 3/ If the test structures consist of a set of pipelined cells, where the clock signals are buffered through the pipeline, than the clock signals at the end of the pipeline should be buffered and placed on output pads so that the integrity and shape of the final clock signals can be 'scoped to determine if failure of a structure could be contributed to poor clock signals due to lack of sufficient buffering of degradation of signals due to noise or signal jitter.

- 4/ Separate power and ground rails should be used to separate internal circuitry rails from the noisy pad driver rails, since the large switching spikes generated by output pad drivers can disrupt the functionality of sensitive internal circuitry. This concept can be taken one step further, if the chip has internal analog and digital circuitry along with I/O pad

driver circuitry, then three separate rails should be used to ensure the greatest decoupling of the different circuit components. These separate rails will obviously be connected to separate pins to allow for the decoupling of those rails to be performed off-chip through the use of ceramic filter capacitors.

- 5/ Use enough power and ground pins. Do not restrict the amount of power that can be drawn by the circuitry by not using enough power and ground pins. There should be a power and ground pin between every three to five output pad driver pins depending on the amount of current that the output pads require. Unless you are absolutely sure, do not assume that one power pin can supply all the power to your circuitry and the output pads.

- 6/ When laying out the pad frame do not create ground loops with the metal conductors. Ground loops are any circular or annular pieces of metal which are connected to the same node. Thus the main I/O pad power and ground rails should be cut so that they do not form a complete circle. These metal loops constitute a single loop transformer which can produce loop currents in the conductor due to magnetic interference and can degrade the performance of the circuitry.

- 7/ If pin limitations require the multiplexing of pins, then **input pins can be** multiplexed to different test structures provided that the input signals only drive device gates. Do not connect input pins from different circuitry which are connected to drains or sources of devices because they can cause clipping of input signals. This can only be determined if the complete setup can be simulated using an analog simulator.

- 8/ Consider tapping out critical circuit signals through buffering circuitry, which will place a minimal amount of load on the circuit under test, to drive an output pin. This extra observability is often useful when determining circuit failure mechanisms. If it is felt that tapping out the signal may disrupt the circuitry, then duplicate the structure on the chip and keep the integrity of one while tapping out the second.

After these considerations in determining the number of pins that will be required, the next step is to look at the circuitry in order to place the pads close to the circuitry that they will be connected too. When wiring signals from the I/O pads, the use of metal2 for routing the long signal connections to the circuitry is a better choice over the metal1 routing layer, since the metal2 layer has a lower capacitance per square value than that of metal1.

Following these tips will ensure that the pad frame will provide the best performance and observability of the circuitry under test.

## 2.4.2 POWER DISTRIBUTION

Power distribution in circuitry is an important issue. The most important thing to remember is that the power flowing into your circuitry is the life blood of your design. If you severely restrict the flow of power to your circuitry, then it will most likely fail or will be unable to perform to its peak ability. The following points should be observed:

1/ Metal is more suitable for power rail distribution since it offers a higher per square caracitance over the metal 2 routing layer. The high capacitance is advantageous on power rails as the increased energy stored in this extra capacitance will help support the power rails when current demand is high and help filter out high frequency noise components that exist on the power rail.

2/ Make the power rails large enough. Excessively thin or narrow power rails lead to dips in supply voltage at critical switching periods when the demand for current exceeds the power rail's ability to provide it. Secondly, an excessively thin or narrow ground rail will lead to a floating ground reference as excessive charge is dumped onto the ground rail at a level which is above the ability of the rail to instantly carry it away. Hence both rails must be of an adequate size. The normal procedure for sizing of the rails is to determine the maximum peak current demand which may be imposed by the circuitry at that point.

Then multiply that value by a safety margin value, say 1.2, and then divide that result by the current density per square of conductor value, which can usually be found in the design rule guide book for the technology. This will give the effective width of the power rail conductor. The ground rail conductor is then oversized slightly, say by 5% to 10% to ensure that a solid ground reference voltage is maintained. If the exact size of the power rail can not be determined, then make it large, use any empty space on the chip to increase the size of the power rails.

- 3/ For circuits which switch large amounts of current remember to make the ground rail larger than the power rail because CMOS circuitry is more susceptible to floating ground rails than to a drooping power rail.

- 4/ Do not use polysilicon or large numbers of via jumpers between metal1 and metal2 in the power rail construction. Both polysilicon and vias produce high resistance connections which will create larger voltage drops on the power rails during peak current demands.

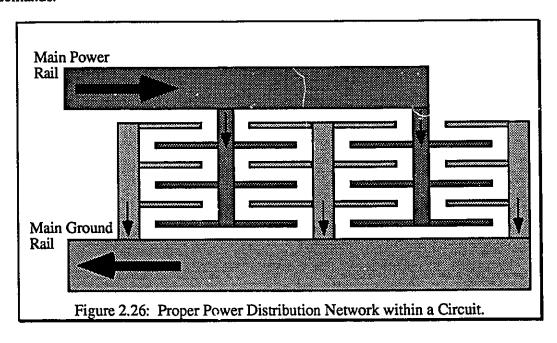

5/ Treat the conductors' width along the power rail like a water pluming system. Thus the main power rail is the widest and gets progressively smaller as it reaches the ends of the feed lines; this is illustrated in Figure 2.26. Also note in Figure 2.26 that no ground loops are formed in the power distribution network. The rails branch-out and terminate in the device circuitry, secondly the ground rails are slightly larger then the power rails.

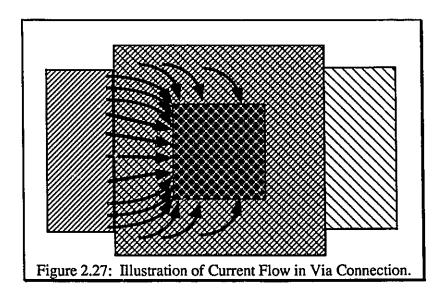

6/ When vias must be placed in the power rail, realize the current carrying limitations of the vias. Vias have a higher per square resistivity than that of the metal interconnect, which means during peak current demands a substantial voltage drop may occur at these points. Secondly, the vias have a lower current carrying capability due to the physical construction of a via connection. A close-up view of a Via connection is illustrated in Figure 2.27.

The small arrows in the diagram indicate current movement, and their relative spacing indicates the relative current density in the Via connection. From this diagram you will note that the majority of the current tends to travel through the leading edge of the Via structure leading to higher current densities at the edges of the structure which may not be possible if the value of the per square current density for the conductor is exceeded. The resulting effect is a current bottle-neck at the via location.

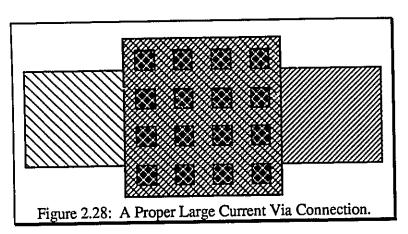

The problem can obviously be alleviated by using more vias with an overall leading edge length larger then the conductors' width, as illustrated in Figure 2.28.

## 2.4.3 ROUTING

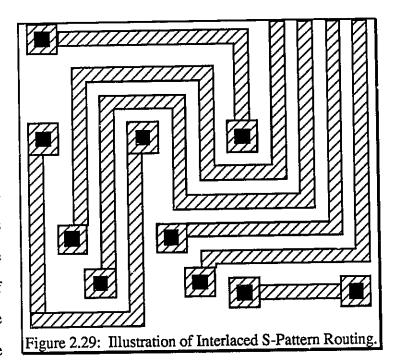

When designing large cells, routing is very important. The problem of routing congestion is often due to poor pre-layout considerations. During the placement of sub-cell circuits into a larger cell, care must be taken to determine the paths of all interconnect and to leave adequate space for them. One

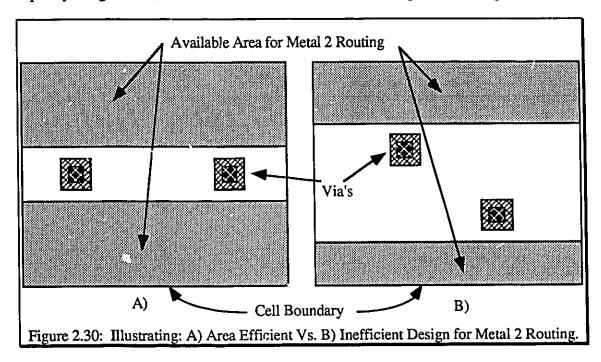

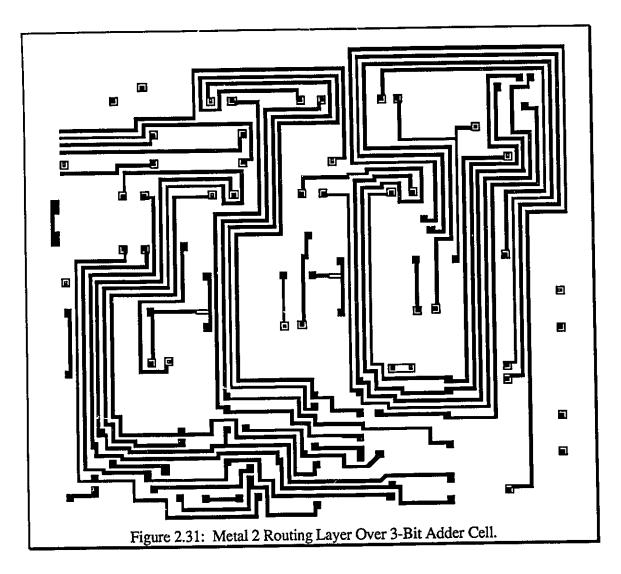

helpful method for getting metal2 routing into and out of large cells is to use continuous interlaced 'S' patterns as illustrated in Figure 2.29. In order to do this the via locations within the cell must be placed for maximum efficiency. When vias in the cell are aligned they allow for greater use of cell space for routing metal2 interconnect. If the vias are randomly placed in the cell they tend to block a large portion of the cell area against routing of metal2 signals. This concept is more clearly seen in Figure 2.30. Fig. 2.30a) illustrates

a cell which has a large area for routing signals over it in metal2, while Fig. 2.30b) shows a poorly designed cell, which has almost no area free for routing of metal 2 signals.