#### **University of Windsor**

## Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2007

# An embedded tester core for mixed-signal System-on-Chip circuits

Rashid Rashidzadeh University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Rashidzadeh, Rashid, "An embedded tester core for mixed-signal System-on-Chip circuits" (2007). *Electronic Theses and Dissertations*. 4622.

https://scholar.uwindsor.ca/etd/4622

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# AN EMBEDDED TESTER CORE FOR MIXED-SIGNAL SYSTEM-ON-CHIP CIRCUITS

by

Rashid Rashidzadeh

A Dissertation

Submitted to the Faculty of Graduate Studies

through Electrical and Computer Engineering Department

in Partial Fulfillment of the Requirements for

the Degree of Doctor of Philosophy at the

University of Windsor

Windsor, Ontario, Canada 2007 ©2007 Rashid Rashidzadeh

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-35096-6 Our file Notre référence ISBN: 978-0-494-35096-6

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## **ABSTRACT**

A new methodology for testing high frequency analog/RF cores in a mixed-signal System-on-Chip (SoC) environment using an embedded tester core is presented. The proposed test method provides a solution to the problem of bandwidth limitation associated with I/O transmission paths and eliminates the need for an advanced external Automatic Test Equipment (ATE) to interact with the embedded tester. The design of the tester is based primarily on a digital level solution, except for a Track and Hold (T/H) circuit and a few CMOS switches, so as to offer the scalability advantages of a soft core description.

In the proposed test method, low frequency waveforms are generated by an external Arbitrary Waveform Generator (AWG) and then upconverted from low to high frequency through an on-chip modulator to excite fast analog circuits. The high frequency response waveforms on the other hand, are down converted from high to low frequency via subsampling techniques and then sent to an external controller for test result evaluation. In this method all high speed operations are performed onboard the chip and only low frequency signals are transmitted between the embedded tester core and the external environment.

A coupled Phase-Locked-Loop (PLL) and Delay-Locked-Loop (DLL) module is employed to generate a carrier signal in the 2.7 GHz range and to synchronize sampling operations to achieve an effective 10 ps interval between sampling points. Coherent subsampling is achieved using a track and hold circuit that is synchronized

with the embedded tester's internal voltage controlled oscillator. The circuits have been designed so that to minimize oscillator jitter and the nonlinear effects associated with the sampling circuit. Simulation studies using an RF oscillator and a Low Noise Amplifier (LNA) as circuits under test verified the measurement capabilities of the proposed tester architecture.

A prototype of the tester core with a chip area of 1  $mm^2$  has been fabricated in 0.18  $\mu m$  CMOS process. Experimental measurements performed on the embedded tester have determined that the bandwidth of the T/H circuit is approximately 4.8 GHz. The overall coherent sub-sampling path accuracy was measured and found to have less than 5.3 % error in amplitude. The simulation and measurement results show that the proposed test methodology can successfully be employed to measure the performance of very fast analog/RF circuits via a low speed transmission path.

To the memory of my mother

ACKNOWLEDGEMENTS

I wish to express my gratitude to people whose supervision, guidance, advice and

encouragement were helpful to this research. First, I would like to extend my sincere

gratitude to my supervisor, Dr. W. C. Miller, who provided support and assistance

for this research. I also wish to thank the committee members Dr. M. Ahmadi and

Dr. S. Chowdhury of Electrical and Computer Engineering, and Dr. D. Northwood

of Mechanical Engineering for the assistance they have provided and their patience

in reading and commenting on my thesis.

I also thank Engineering Faculty Members and Faculty of Engineering Staff to

whom I am very grateful over my years of study at the University of Windsor. In

addition, I would like to give my special thanks to Mr. Frank Cicchello for his com-

puting and experimental infrastructure support throughout my graduate program.

I would also like to acknowledge the financial support provided by Natural Sci-

ences and Engineering Research Council of Canada (NSERC) 1, Micronet Network

of Centres of Excellence<sup>2</sup> and Gennum Corp.<sup>3</sup> which formed the basis for developing

this research project.

I owe a great debt to my family. I thank them most sincerely for their patience,

understanding, encouragement and unfailing moral support over the long period of

time spent on this research.

$^{1}$ www.nserc-crsng.gc.ca

$^2$ www.micronetrd.ca

$^3$ www.gennum.ca

vi

# TABLE OF CONTENTS

| ΑE              | ABSTRACT         |         |                                              | iii        |

|-----------------|------------------|---------|----------------------------------------------|------------|

| DE              | DIC              | ATION   | 1                                            | v          |

| AC              | ACKNOWLEDGEMENTS |         |                                              |            |

| LIST OF FIGURES |                  |         |                                              | x          |

| I               | INT              | RODU    | JCTION                                       | 1          |

|                 | 1.1              | Statem  | nent of the Problem                          | 1          |

|                 | 1.2              | Propos  | sed Test Solution                            | 2          |

|                 | 1.3              | Outline | e of the Thesis                              | 3          |

| II              | DE               | SIGN I  | FOR TEST METHODOLOGIES                       | 5          |

|                 | 2.1              | Digital | Circuit Testing                              | 5          |

|                 |                  | 2.1.1   | IEEE 1149.1 Standard Boundary Scan           | 5          |

|                 |                  | 2.1.2   | IEEE P1500 Standard for Embedded Core Test   | 6          |

|                 | 2.2              | Analog  | Circuit Testing                              | 7          |

|                 |                  | 2.2.1   | Analog DFT Methods                           | 10         |

|                 |                  | 2.2.2   | State of the Art                             | 16         |

|                 | 2.3              | Summa   | ary                                          | 20         |

| III             | PR               | OPOSE   | ED TEST METHOD                               | <b>2</b> 1 |

|                 | 3.1              | Modul   | ation Based Test Stimuli Generation          | 22         |

|                 | 3.2              | Sampli  | ng Techniques                                | 24         |

|                 |                  | 3.2.1   | Coherent Sampling                            | <b>2</b> 5 |

|                 |                  | 3.2.2   | Subsampling Method                           | 26         |

|                 | 3.3              | System  | Level Simulation of the Proposed Test Method | 28         |

|                 | 3.4              | Archite | ecture of the Proposed Embedded Tester       | 32         |

|                 | 3.5              | Test P  | rotocol                                      | 33         |

|                 | 3.6              | Summa   | arv                                          | 37         |

| IV           | TO  | POLO   | GY SELECTION AND SYSTEM LEVEL SIMULATION                        | 39  |

|--------------|-----|--------|-----------------------------------------------------------------|-----|

|              | 4.1 | High l | Frequency Stimulus Generator                                    | 39  |

|              |     | 4.1.1  | Mixer                                                           | 40  |

|              |     | 4.1.2  | Carrier Signal Generator                                        | 43  |

|              |     |        | 4.1.2.1 Linear Model and Stability Analysis of the Employed PLL | 50  |

|              |     |        | 4.1.2.2 Frequency Synthesizer                                   | 53  |

|              |     | 4.1.3  | Block Diagram of the Carrier Signal Generator in Matlab         | 56  |

|              | 4.2 | Respo  | nse Capturing Circuitry                                         | 58  |

|              |     | 4.2.1  | Sampling Clock Generator                                        | 58  |

|              |     | 4.2.2  | Track and Hold                                                  | 66  |

|              | 4.3 | Packa  | ging Selection                                                  | 66  |

|              | 4.4 | Summ   | ary                                                             | 66  |

| $\mathbf{V}$ | PH  | YSICA  | AL LEVEL DESIGN OF BUILDING BLOCKS                              | 68  |

|              | 5.1 | Analo  | g Circuits                                                      | 68  |

|              |     | 5.1.1  | Phase Locked Loop                                               | 68  |

|              |     |        | 5.1.1.1 Delay Cell                                              | 69  |

|              |     |        | 5.1.1.2 Voltage Controlled Oscillator                           | 77  |

|              |     |        | 5.1.1.3 Phase and Frequency Detector                            | 81  |

|              |     |        | 5.1.1.4 Charge Pump                                             | 82  |

|              |     | 5.1.2  | Delay Locked Loop                                               | 88  |

|              |     | 5.1.3  | Mixer                                                           | 92  |

|              |     | 5.1.4  | Track and Hold                                                  | 96  |

|              | 5.2 | Digita | l Circuits                                                      | 102 |

|              |     | 5.2.1  | Multiplexer                                                     | 102 |

|              |     | 5.2.2  | Counter                                                         | 104 |

|              |     | 5.2.3  | Comparator                                                      | 105 |

|              |     | 5.2.4  | Serial-to-Parallel Converter                                    | 106 |

|              | 5.3 | Measu  | rement Accuracy                                                 | 106 |

|                              | 5.4  | Mixed Signal Interconnect and Packaging                 | 108 |

|------------------------------|------|---------------------------------------------------------|-----|

|                              | 5.5  | Summary                                                 | 111 |

| $\mathbf{VI}$                | CA   | LIBRATION PROCEDURE AND SIMULATION RESULTS              | 112 |

|                              | 6.1  | RF Oscillator Performance Metric Measurement            | 113 |

|                              | 6.2  | Performance Metric Measurement of a Low Noise Amplifier | 115 |

|                              | 6.3  | Summary                                                 | 118 |

| VII EXPERIMENTAL RESULTS 119 |      |                                                         |     |

|                              | 7.1  | Low Frequency Sampling Accuracy Test                    | 119 |

|                              | 7.2  | High Frequency Sampling Accuracy Test                   | 123 |

|                              | 7.3  | Step Response Testing                                   | 124 |

|                              | 7.4  | Summary                                                 | 127 |

| VII                          | ICC  | ONCLUSIONS AND FUTURE WORK                              | 128 |

|                              | 8.1  | Conclusions                                             | 128 |

|                              | 8.2  | Future Work                                             | 129 |

| VT                           | ΓΔ Δ | JUCTORIS                                                | 155 |

# LIST OF FIGURES

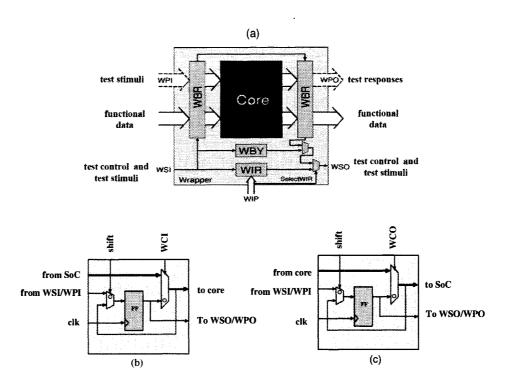

| 1  | IEEE P1500 (a) wrapper architecture. (b) wrapper boundary input cell. (c) wrapper boundary output cell                                                                                                                    | 7  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

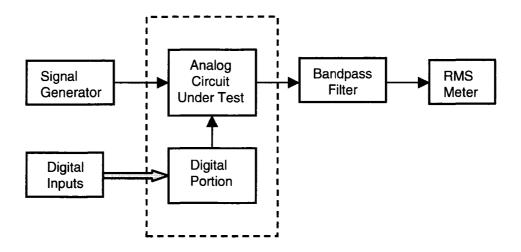

| 2  | Traditional test setup for mixed-signal devices                                                                                                                                                                           | 8  |

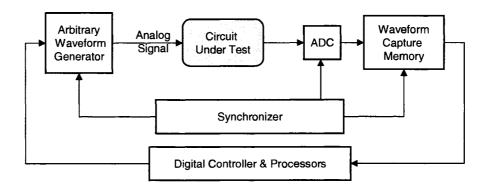

| 3  | DSP based analog tester scheme.                                                                                                                                                                                           | 9  |

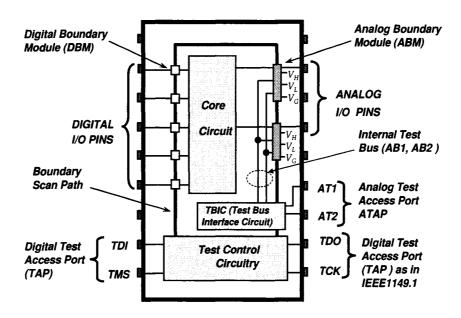

| 4  | Mixed signal boundary scan architecture                                                                                                                                                                                   | 11 |

| 5  | Analog boundary module in the 1149.4 standard                                                                                                                                                                             | 12 |

| 6  | A typical analog test bus.                                                                                                                                                                                                | 13 |

| 7  | Mixed-signal BIST architecture using on-chip ADC and DAC modules.                                                                                                                                                         | 14 |

| 8  | Signature test configuration for RF circuits [28]                                                                                                                                                                         | 16 |

| 9  | (a) Functional diagram and (b) detailed view of the proposed on-chip test system in [29]                                                                                                                                  | 17 |

| 10 | Block diagram of the test wrapper proposed in [32] for mixed-signal SOCs testing.                                                                                                                                         | 18 |

| 11 | Block diagram of an open architecture ATE                                                                                                                                                                                 | 19 |

| 12 | Block diagram of a typical programmable AWG                                                                                                                                                                               | 22 |

| 13 | Bipolar chopper modulator                                                                                                                                                                                                 | 23 |

| 14 | (a) Non coherent samples of a sinusoidal waveform used for FFT calculation. (b) the waveform represented by the FFT spectrum                                                                                              | 25 |

| 15 | (a) Coherent samples of a sinusoidal waveform used for FFT calculation. (b) the waveform represented by the FFT spectrum                                                                                                  | 26 |

| 16 | Subsampling a periodic waveform                                                                                                                                                                                           | 27 |

| 17 | Subsampling spectrum.                                                                                                                                                                                                     | 28 |

| 18 | Simulation setup to verify the proposed test technique                                                                                                                                                                    | 29 |

| 19 | Modulation and subsampling techniques (a) low frequency test generated by the AWG. (b) high frequency test signal applied to a hypothetical CUT. (c) CUT's output signal. (d) samples of the CUT obtained by subsampling. | 30 |

| 20 | <ul><li>(a) Spectrum of the input waveform applied to the hypothetical CUT.</li><li>(b) spectrum of the CUT's response waveform.</li><li>(c) spectrum of the</li></ul>                                                    |    |

|    | CUT's response after downconversion                                                                                                                                                                                       | 31 |

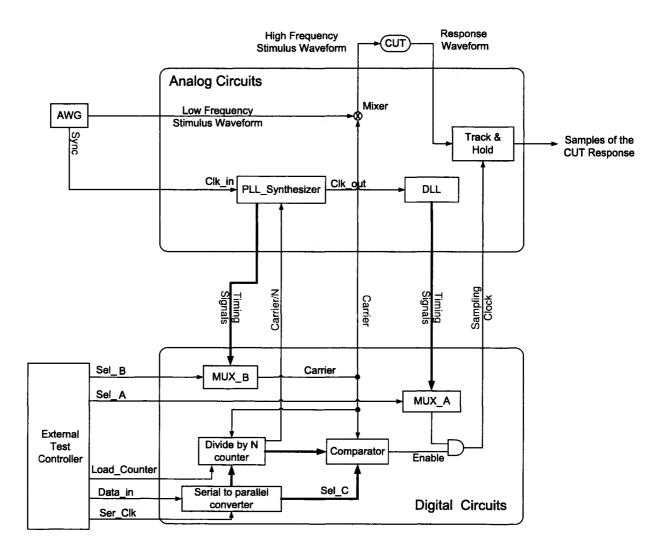

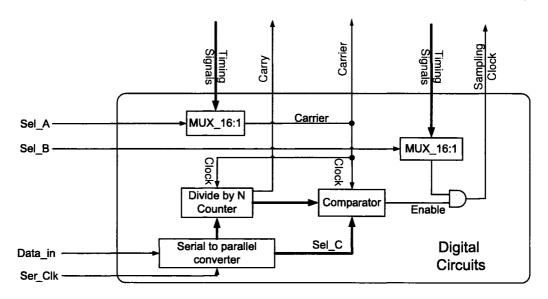

| 21 | Block diagram of the proposed tester core                                                                              | 32 |

|----|------------------------------------------------------------------------------------------------------------------------|----|

| 22 | Detailed block diagram of the proposed tester core                                                                     | 34 |

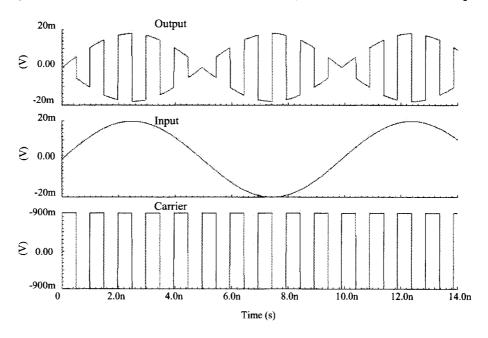

| 23 | Typical input and carrier signals applied to the mixer and the corresponding output.                                   | 35 |

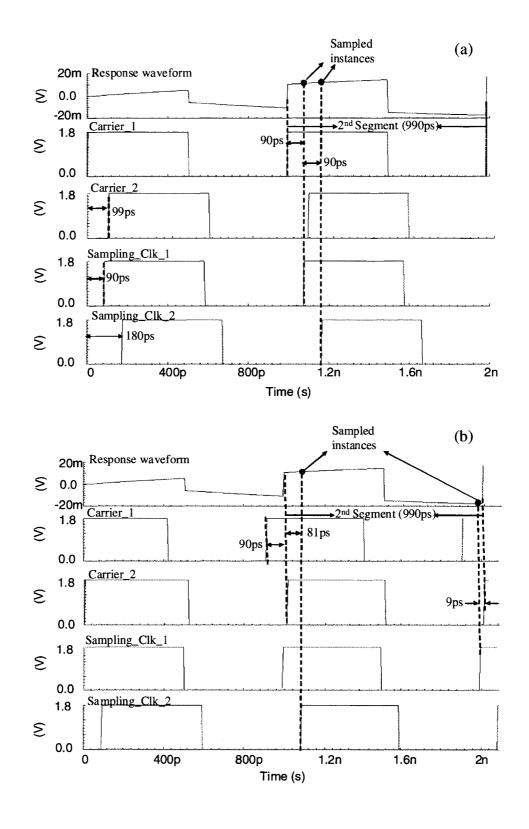

| 24 | Shift and sample process. (a) when carrier-1 is in phase with the input. (b) when carrier-2 is in phase with the input | 38 |

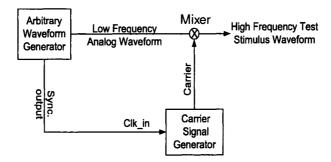

| 25 | Block diagram of the employed high frequency stimulus generator                                                        | 40 |

| 26 | Block diagram of a passive chopper modulator                                                                           | 41 |

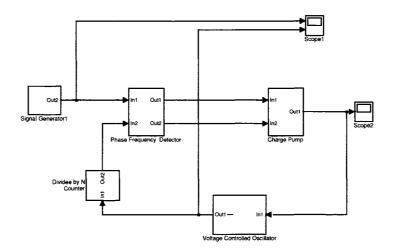

| 27 | Simulation setup in Matlab/Simulink to test the mixer                                                                  | 41 |

| 28 | Simulated spectrum of the input and output waveforms                                                                   | 42 |

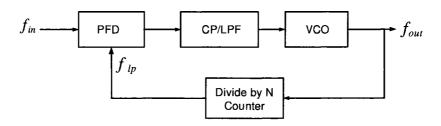

| 29 | Block diagram of type II PLL                                                                                           | 43 |

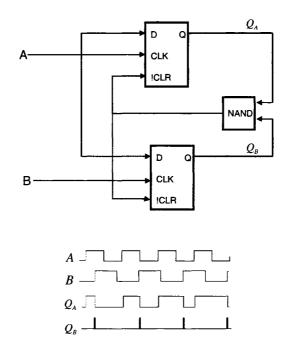

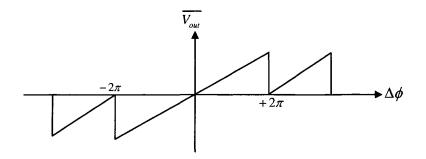

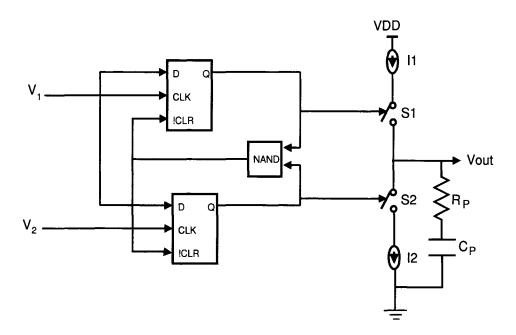

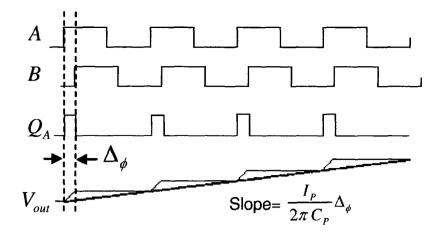

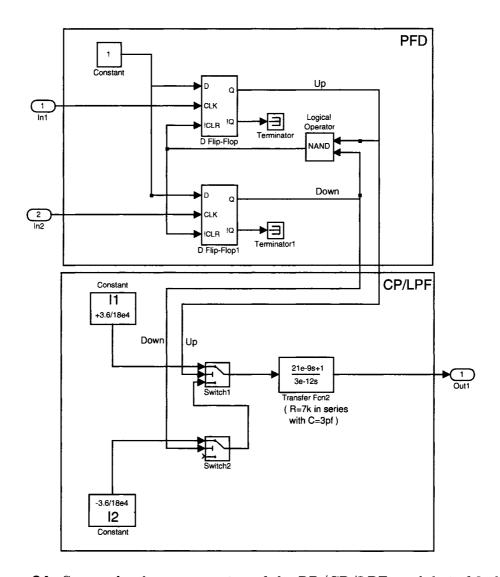

| 30 | Selected PFD architecture and its typical input and output signals waveforms                                           | 44 |

| 31 | Characteristic of the PFD                                                                                              | 45 |

| 32 | PFD followed by a charge pump.                                                                                         | 45 |

| 33 | Step response of the employed PFD/CP/LPF module                                                                        | 46 |

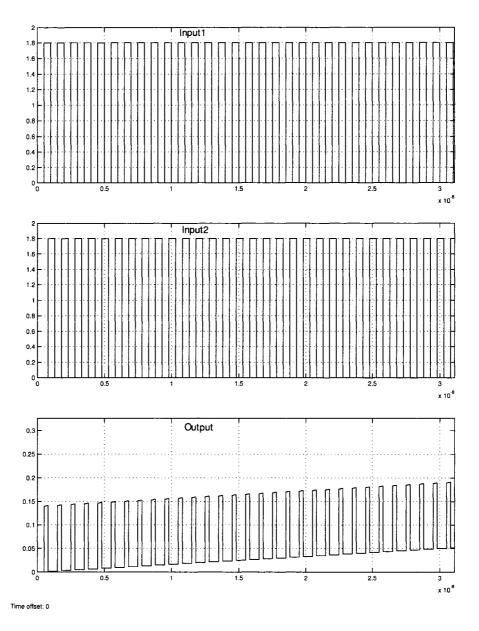

| 34 | System level representation of the PD/CP/LPF module in Matlab. $$ .                                                    | 47 |

| 35 | Input and output of the PFD/CP/LPF                                                                                     | 48 |

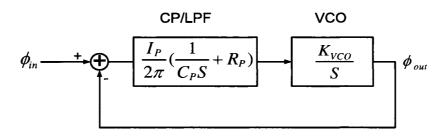

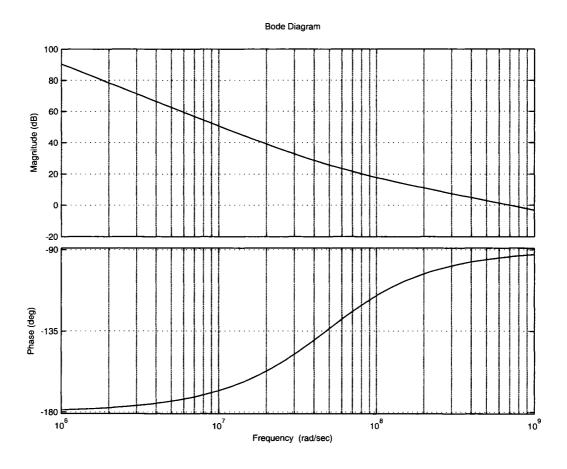

| 36 | Linear model of the employed PLL                                                                                       | 50 |

| 37 | Bode diagram of the open loop transfer function of the PLL                                                             | 52 |

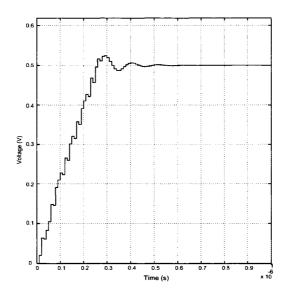

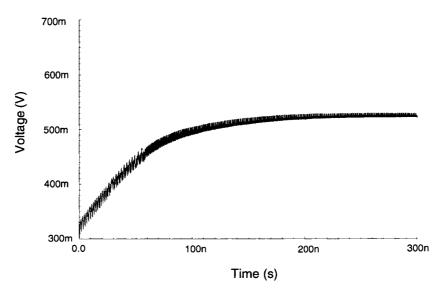

| 38 | The simulated control voltage of the PLL                                                                               | 53 |

| 39 | Block diagram of the employed PLL synthesizer                                                                          | 54 |

| 40 | Matlab/Simulink setup for the synthesizer                                                                              | 55 |

| 41 | Synthesizer simulation results for $N=8$ . (a) input and (b)output                                                     | 55 |

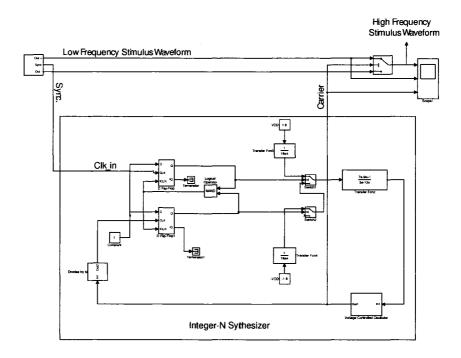

| 42 | Simulink test setup for the high frequency stimulus generator                                                          | 56 |

| 43 | Simulation results for the high frequency stimulus generator                                                           | 57 |

| 44 | Block diagram of the response capturing module                                                                         | 58 |

| 45 | Timing signal generator using a VCO                                                                                    | 59 |

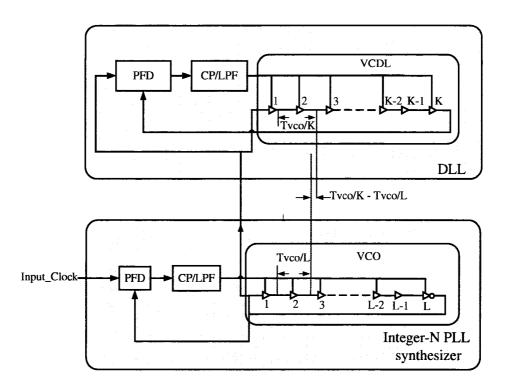

| 46 | DLL building blocks                                                                                                    | 60 |

| 47 | DLL linear model.                                                                                                      | 61 |

| 48 | Precision timing signal generator using a coupled PLL and DLL module.                                                                         | 62 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 49 | Employed precision timing signal generator                                                                                                    | 63 |

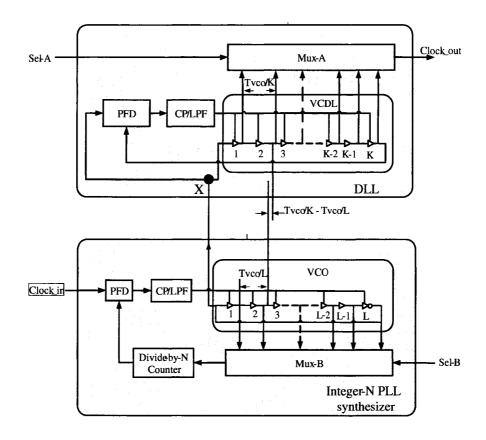

| 50 | Input waveform chopped into eight segments and the samples of the 2nd segment taken by subsampling                                            | 65 |

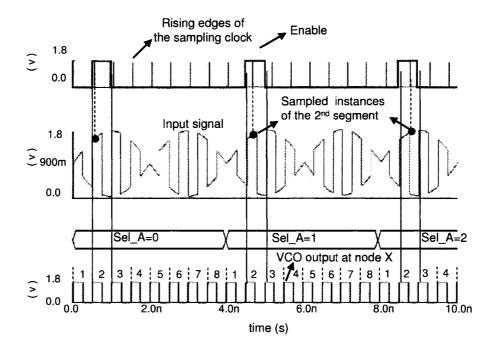

| 51 | The employed cross-coupled differential delay cell. (a) schematic diagram. (b) layout.                                                        | 70 |

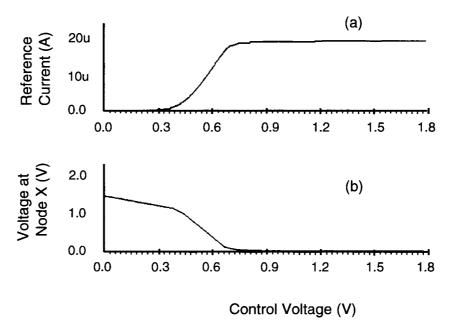

| 52 | Simulation result of DC analysis performed on the control circuit                                                                             | 73 |

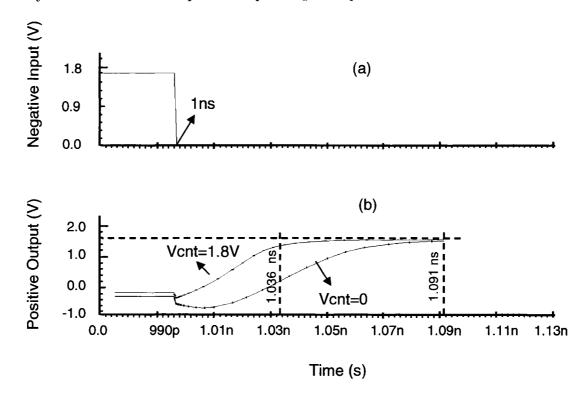

| 53 | The AC response of the delay cell. (a) applied input signal. (b) output response for Vcnt=0 and Vcnt=1.8 V                                    | 75 |

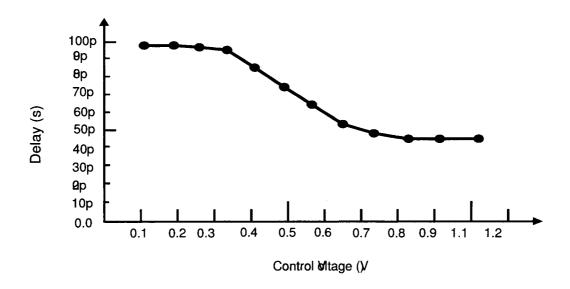

| 54 | Delay characteristic of the employed delay cell                                                                                               | 76 |

| 55 | Linear model of oscillator circuits.                                                                                                          | 77 |

| 56 | Simulation result from transient analysis of the delay cell                                                                                   | 78 |

| 57 | Ten delay elements employed to build a ring oscillator                                                                                        | 79 |

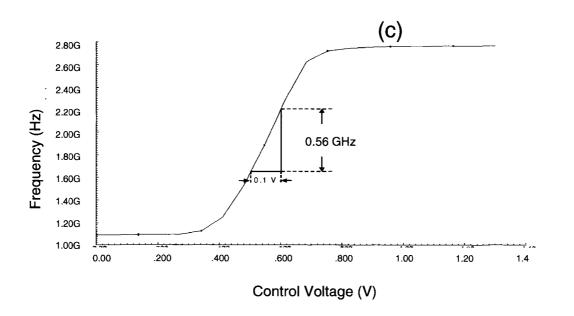

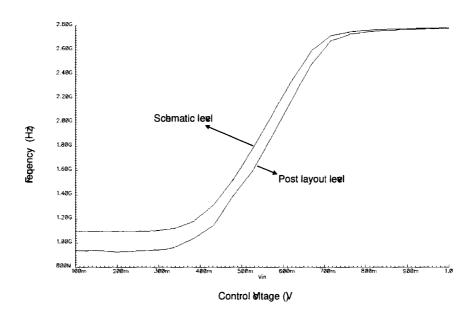

| 58 | Implemented voltage controlled oscillator. (a) block diagram. (b) physical implementation. (c) post layout tuning range simulation            | 80 |

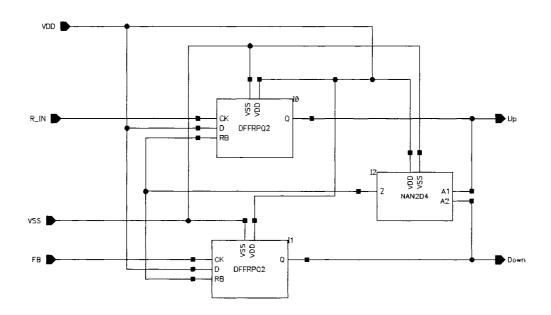

| 59 | PFD implementation using CMOS 0.18 $\mu m$ standard library cells                                                                             | 81 |

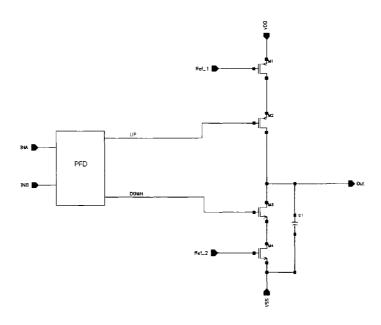

| 60 | Basic charge pump                                                                                                                             | 82 |

| 61 | Skew effect on control voltage                                                                                                                | 83 |

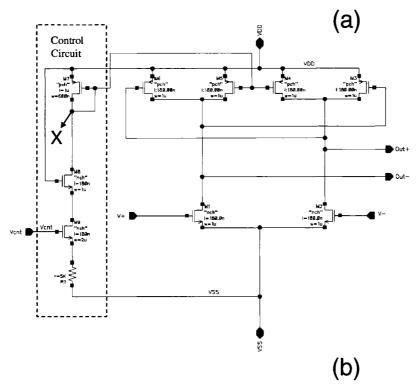

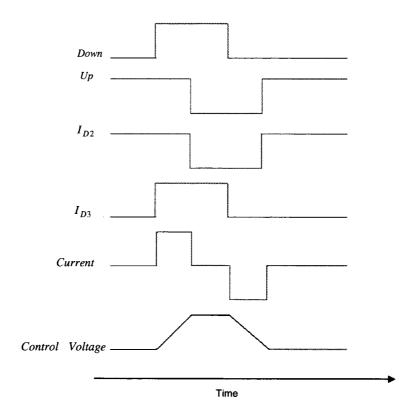

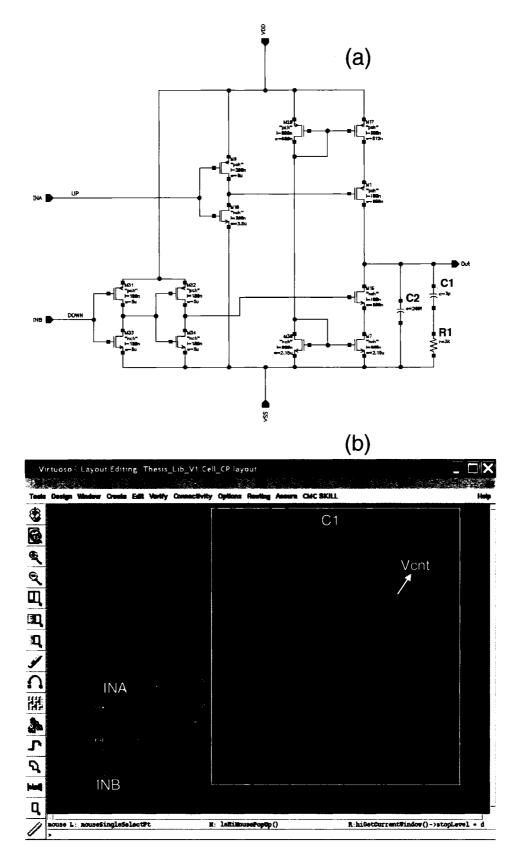

| 62 | Implemented charge pump (a) schematic diagram. (b) layout                                                                                     | 84 |

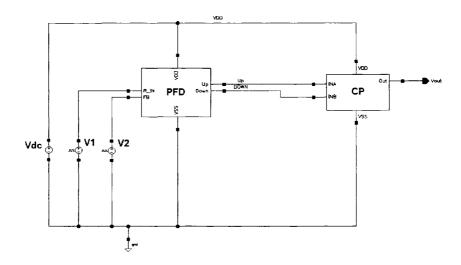

| 63 | Test setup for the charge pump gain measurement                                                                                               | 85 |

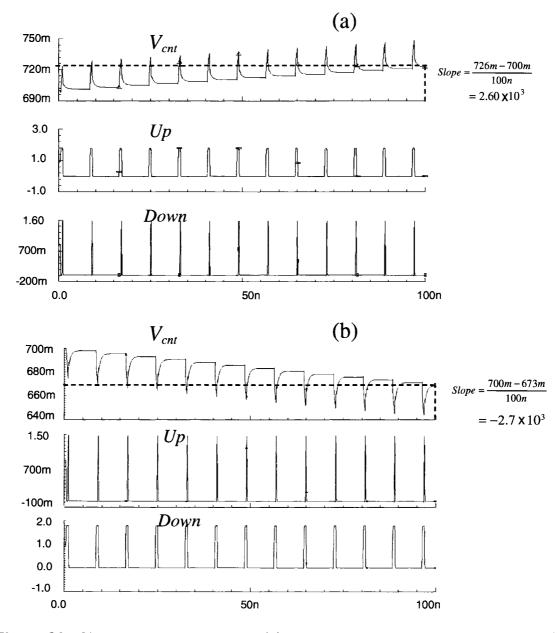

| 64 | Charge pump response for (a) inputs with positive phase difference.<br>(b) the same inputs but switched to present negative phase difference. | 86 |

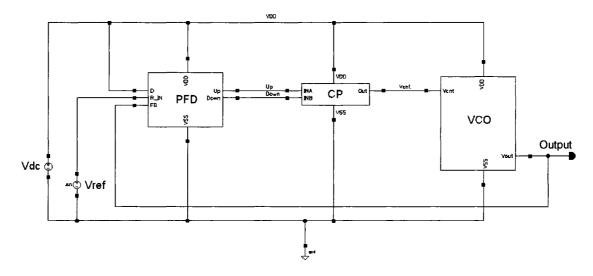

| 65 | The PLL test setup.                                                                                                                           | 87 |

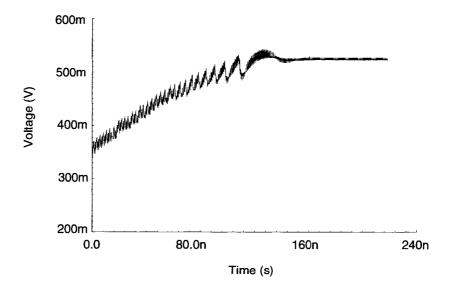

| 66 | The PLL control voltage during lock acquisition.                                                                                              | 87 |

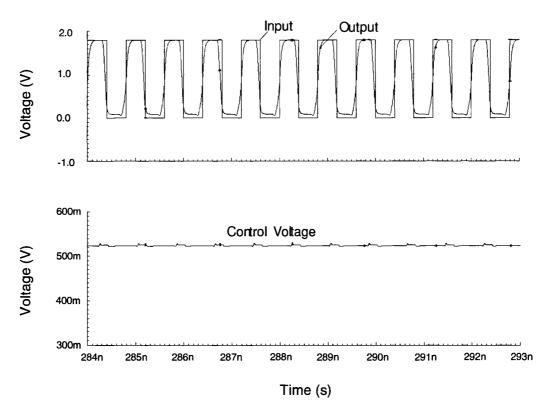

| 67 | Input, output and control voltage of the PLL at the locked condition.                                                                         | 88 |

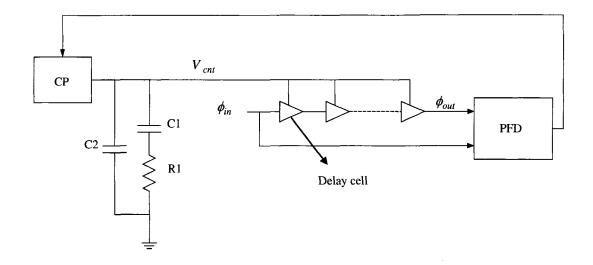

| 68 | DLL with a second order closed loop transfer function                                                                                         | 89 |

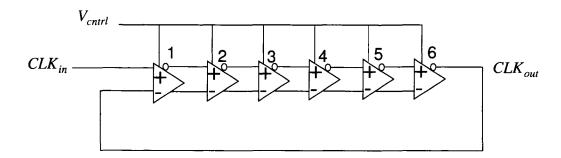

| 69 | Differential delay cells configured as a voltage controlled delay line                                                                        | 89 |

| 70 | Control voltage variation of the DLL indicating how the lock is acquired.                                                                     | 90 |

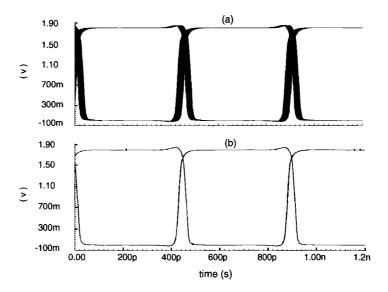

| 71 | Simulated eye diagram for the sampling clock of 1.1 GHz. (a) before attaining the phase lock. (b) after attaining the phase lock              | 91 |

| 72 | Peak-to-peak jitter of the sampling clock at 1.1 GHz. (a) before attaining the phase lock. (b) after attaining the phase lock                                                               | 91   |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 73 | Schematic level implementation of the mixer                                                                                                                                                 | 92   |

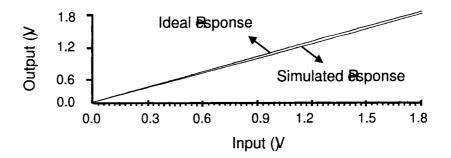

| 74 | Simulated DC characteristic of the employed CMOS switches for mixer realization                                                                                                             | 93   |

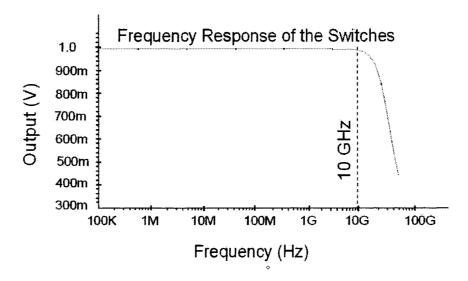

| 75 | Frequency Response of the Analog Switches Used in the Mixer                                                                                                                                 | 93   |

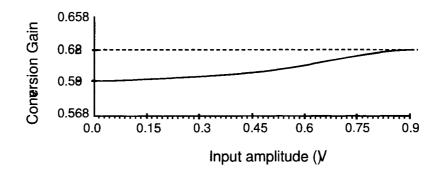

| 76 | Mixer's voltage conversion gain versus input voltage amplitude                                                                                                                              | 94   |

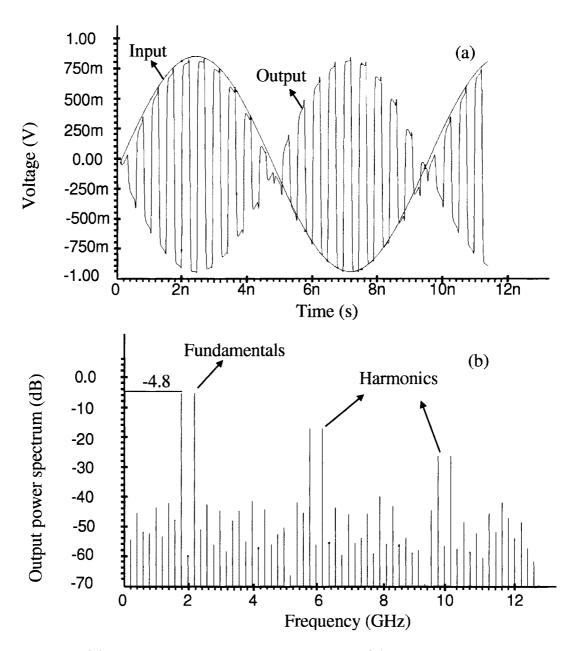

| 77 | (a) Mixers input and output waveforms. (b) spectrum of the output.                                                                                                                          | 95   |

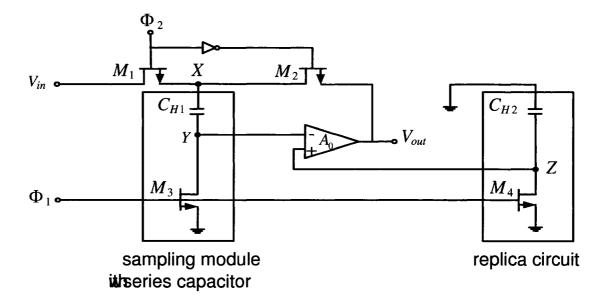

| 78 | Track and hold circuit with a replica circuit.                                                                                                                                              | 96   |

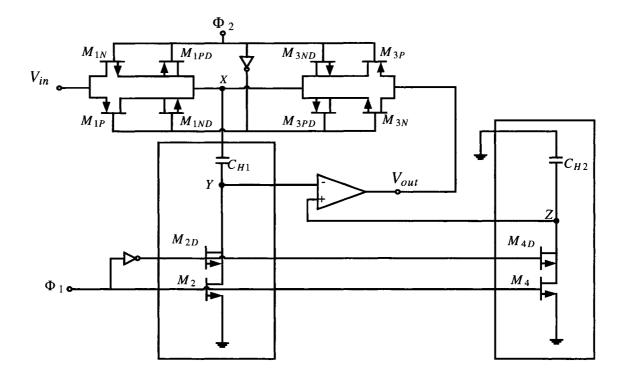

| 79 | T/H circuit with complementary and dummy transistors                                                                                                                                        | 99   |

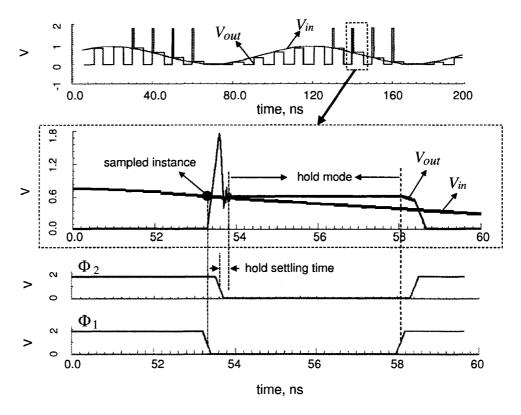

| 80 | The input and output waveforms of the T/H circuit for a sinusoidal input of 1.8 $V_{PP}$ at 10 MHz with a 100 MHz sampling clock                                                            | 101  |

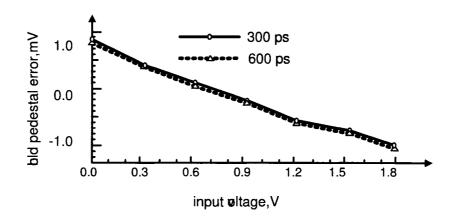

| 81 | Simulated hold pedestal error as a function of DC input voltage for two different clock transitions of 300 ps and 600 ps                                                                    | 101  |

| 82 | Block diagram of digital circuits.                                                                                                                                                          | 102  |

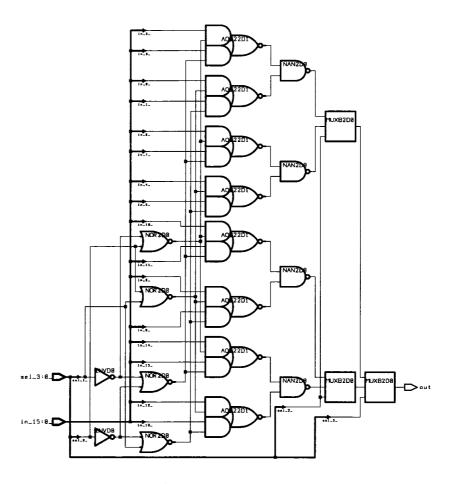

| 83 | Circuit diagram of the multiplexer generated by synopsys design analyzer                                                                                                                    | .103 |

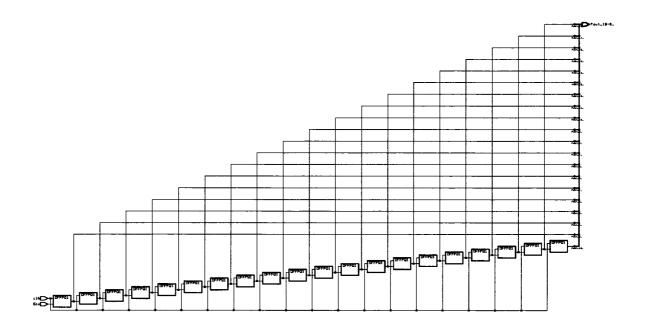

| 84 | Circuit diagram of the counter generated by synopsys design analyzer.                                                                                                                       | 104  |

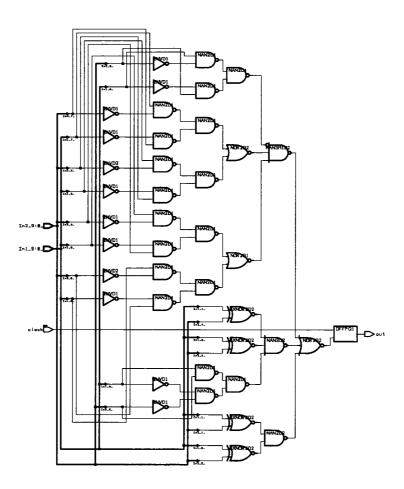

| 85 | Circuit diagram of the comparator                                                                                                                                                           | 105  |

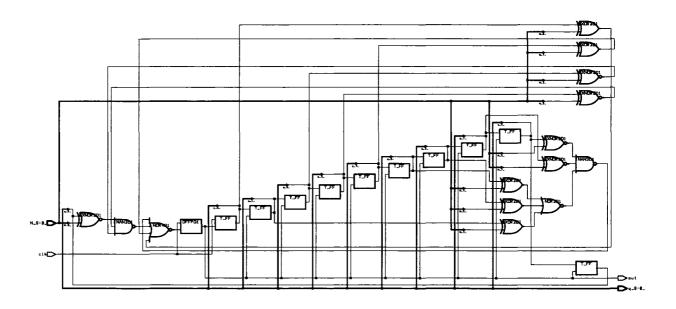

| 86 | Circuit diagram of the serial to parallel converter module                                                                                                                                  | 106  |

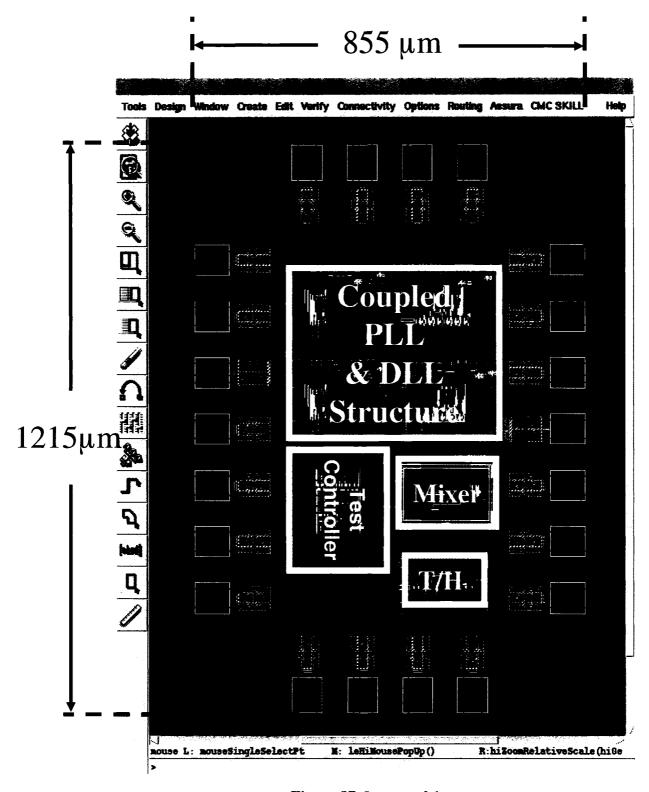

| 87 | Layout of the tester core                                                                                                                                                                   | 109  |

| 88 | Designed tester core (a) chip layout. (b) chip photo. (c) bonding diagram                                                                                                                   | 110  |

| 89 | Simulation of VCO tuning range before and after physical implementation                                                                                                                     | 111  |

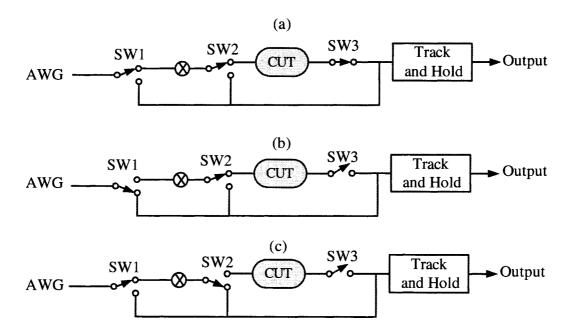

| 90 | (a) Normal operation mode. (b) calibration and self-test mode to measure the sampling module performance. (c) calibration and self-test mode to measure the performance of the mixer module | 112  |

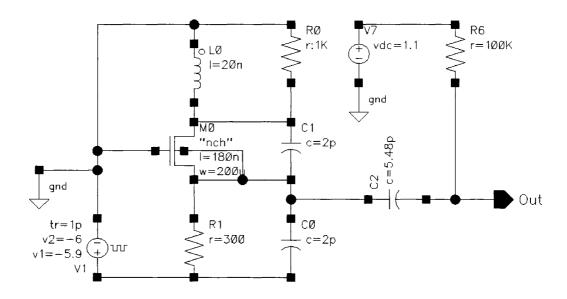

| 91 | Schematic diagram of the RF oscillator used a CUT                                                                                                                                           | 114  |

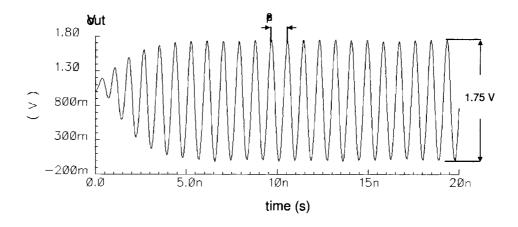

| 92 | RF oscillator output waveform                                                                                                                                                               | 114  |

| 93 | Simulated power spectrum of the oscillator output                                                                                                                                           | 115  |

| 94 | Simulated two-sided power spectrum of (a) CUT's response. (b) applied stimulus                                                                                                              | 116  |

| Simulated (a) gain and (b) IP3 against the power of the fundamental tone at the input                                                                                                                                         | 117               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

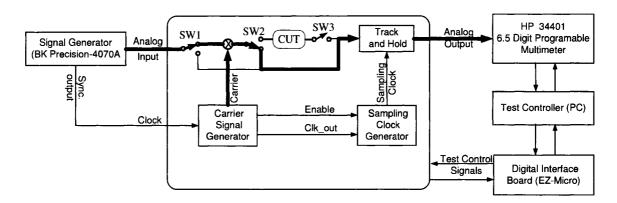

| (a) Setup for sine wave testing                                                                                                                                                                                               | 119               |

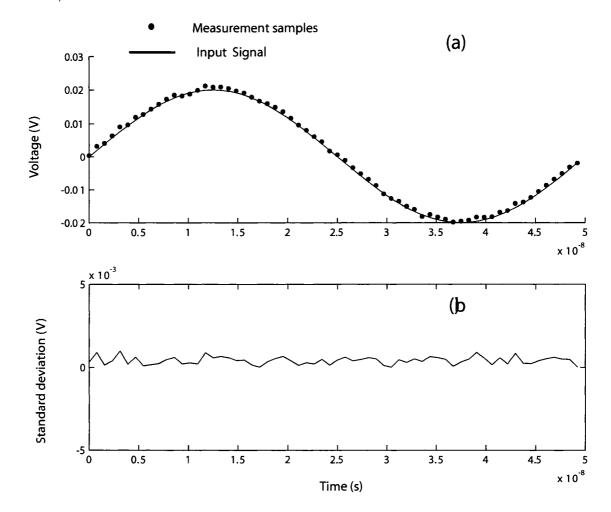

| (a) Measured samples of the applied sinusoidal input. (b) Standard deviations of the samples                                                                                                                                  | 121               |

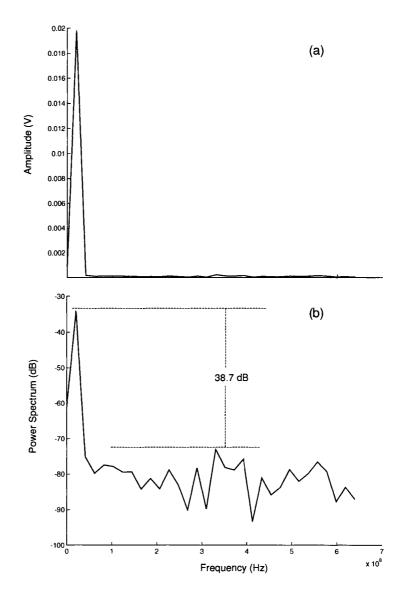

| Single-sided spectrum(a) Amplitude. (b) Power                                                                                                                                                                                 | 122               |

| (a) Test setup for SNDR measurement                                                                                                                                                                                           | 123               |

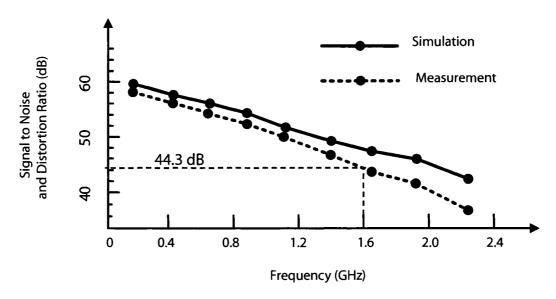

| Simulated and measured SNDR versus input signal frequency                                                                                                                                                                     | 124               |

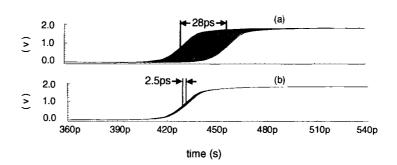

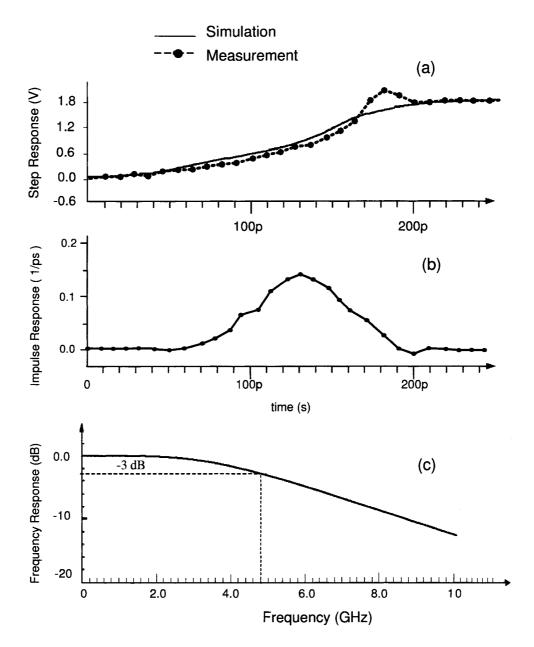

| (a) Measured and simulated samples of T/H the step response. (b) Impulse response of the sampling scheme determined from the measured step response. (c) Frequency response of the sampler obtained from the impulse response | 126               |

|                                                                                                                                                                                                                               | tone at the input |

## CHAPTER I

## INTRODUCTION

# 1.1 Statement of the Problem

It is possible to design and fabricate an incredibly dense integrated circuits comprised of interconnected modules or cores. These cores can be reused in many other different systems. This type of architecture is called a System-on Chip (SoC). A typical SoC can contain various digital, analog and mixed signal cores fabricated all together on a single chip. While SoC technology presents new opportunities, it also poses some significant challenges. Testing the emerging generation of SoCs poses unique challenges and risks. According to the International Technology Roadmap for Semiconductors (ITRS), "the ability to deliver high frequency signals to external Automatic Test Equipment (ATE) without much loss and distortion becomes a monumental task in test engineering". The problem of integrated circuit testing becomes even more complicated to solve when high-speed analog circuits are involved. High-frequency analog signals are difficult to measure and challenging to route to ATE pin electronics due to the continuous nature of analog signals and their sensitivity to signal integrity degradation. Advanced ATEs with customized interface circuits and matching impedances are required to perform test on high-speed analog/RF circuits. These test requirements contribute to a substantial increase in the cost and complexity of test setup for high-speed mixed-signal devices. Given the cost curve that ATE has followed over the last decade, a machine that could test a complex SoC, if it were at all technically feasible, would carry a huge price tag on the order of 50-100 million US dollars. Even if the semiconductor industry were willing to pay such costs, few believe that any ATE machine of a presently known architecture would be able to test tomorrow's SoCs as accurately and reliability as would be required. A fresh approach is needed to explore new solutions to the problems of mixed-signal IC testing in a SoC environment.

## 1.2 Proposed Test Solution

There is a general consensus that some form of on-chip measurement is needed to relieve the critical bottlenecks in testing analog/RF circuits. An on-chip ATE that is located within a microscopic distance of the Circuit-Under-Test (CUT) and has a down frequency conversion capability can perform high-speed tests without the limitations imposed by the I/O transmission paths. Moreover, in very high frequency ranges this approach can eliminate the need for matching impedances owing to negligible signal reflection at lower frequencies. However, embedding all the functions of an ATE inside a chip increases the area overhead, power consumption and complexity to a level that may not be practical. A viable solution is to embed only the high frequency analog measurement functions of an ATE inside the SoC and generate low frequency signals to communicate the measurements to an external low performance, low price external ATE or even a laptop computer. In the proposed test method, all high frequency test operations are performed inside an embedded tester core and the results are communicated at low frequencies with an external controller. To generate test stimulus waveform, an on-chip high frequency digital level signal is mixed with an off-chip low frequency analog. Using a digital carrier in this method reduces the need for analog circuits to a significant degree. The proposed test method advances the state-of-the-art by providing an almost entirely digital solution for the problem of RF/Analog circuit testing (except for T/H circuit and a few switches). Using an all digital PLL and DLL to implement the test method, an RF/analog tester can be offered as a synthesizable RTL code that is scalable and not technology dependent. The need to transmit lower frequency signals over the I/O transmission paths is realized using a coherent sub-sampling technique. The proposed embedded tester core offers a solution for embedded SoC testing that provides several major advantages as follows:

## Provides a solution to generating very high frequency stimulus signals for testing purposes

The use of a squarewave carrier that can be modulated by an external waveform offers the ability to generate very high order harmonics that can be used as a test stimulus for the mixed-signal circuits under test. The high frequency test signals generated in this manner have the same stability and controllability as the modulated carrier itself.

# Provides a solution to the problem of bandwidth limitation of SoC I/O paths

An embedded tester can be located very close to the internal cores that comprise the SoC implementation. The bandwidth limitations of the connectivity between the embedded tester core and the CUT are relatively minor. However, the bandwidth limitations associated with the I/O transmission path to an external device are significant. The physical length of the transmission path and the physical nature of the I/O pads impose severe limitations on attempts to measure very high speed internal core performance. In the proposed tester architecture coherent sub-sampling is used to measure very high frequencies and communicate the values at low frequencies. Therefore, the embedded tester core can transmit test results without the speed limitations normally imposed by the overall transmission paths.

#### 3. Soft Core Advantages

The architecture of the embedded tester employs an all digital realization wherever possible. This allows for the major part of the tester circuitry to be described in terms of a soft core. This in turn allows the design to be more readily

scalable and migrated to other process technologies. Only the track and hold circuit and a few switches have an analog realization.

#### 4. Reduces the Cost and the Complexity of Testing

The embedded tester core employs coherent sub-sampling to generate and transmit low frequency test result signals externally from the SoC. The lower frequency range simplifies the requirements of the ATE, the fixture and the transmission lines used to connect the SoC to the ATE. This can significantly reduce the cost and complexity of test procedure.

## 1.3 Outline of the Thesis

The rest of this dissertation is organized as follows. Chapter 2 introduces the basic concepts of mixed signal device testing, starting with a short overview of digital circuit testing followed by descriptions of the test methods developed in the context of analog/RF device testing over the years. The most recent studies in this field and the latest mixed signal ATE architecture employed by semiconductor industry are also covered in this chapter. Chapter 3 begins with the description of the proposed test method for fast RF/Analog circuits. Mathematical foundations of the employed enabling techniques, system level representation of the proposed test scheme and the architecture of the embedded tester are also presented in this chapter. Chapter 4 discusses topology selections and high level simulations of the building blocks of the tester. Schematic and layout level implementation of the analog and digital circuits are described in chapter 5. This chapter also includes the results of simulations performed on various modules of the tester. Chapter 6 presents simulation results for two test cases in which an RF oscillator and a Low Noise Amplifier (LNA) are used as CUTs. The experimental results are presented in chapter 7 and finally, in chapter 8 conclusions are drawn and recommendations are made for future work in this field.

### CHAPTER II

## DESIGN FOR TEST METHODOLOGIES

In general, testing a mixed signal chip is performed in two different domains of digital and analog electronics with different methods of testing. The interactions between analog and digital circuits are also tested in a separate phase. Digital circuit testing has been under intense research for a long time resulting in accurate fault models and powerful automatic test generation methods [6, 7, 8, 9]. While digital circuit testing is a mature subject, design for test methodologies for analog circuits [10] is still in its early stages and fundamental research is needed to address numerous challenges in this area. In this chapter first IEEE 1149.1 standard [11] for digital circuit testing is briefly discussed and then various test methods developed for analog circuits are covered and finally the state of the art in this field is presented.

# 2.1 Digital Circuit Testing

Generally, any circuit or methodology used to utilize the process of testing a product is called Design For Test (DFT). DFT, if properly implemented, has the potential to offer higher product quality at lower production cost. The DFT methods in the digital domain has reached to a satisfactory level and now it is considered as an inseparable part of digital IC design. IEEE 1149.1 standard boundary scan, also called JTAG, is among the most successful DFT methods developed for digital circuits.

#### 2.1.1 IEEE 1149.1 Standard Boundary Scan

Boundary scan has been successfully incorporated into digital designs and has considerably simplified the test or even diagnosis of advanced electronic devices. The IEEE 1149.1 standard can be divided into two parts: 1149.1a, or the digital boundary scan

standard [12], and 1149.1b, or the Boundary Scan Description Language (BSDL). The IEEE 1149.1a standard defines the chip level test architecture for digital circuits, and 1149.1b defines the boundary scan description language.

#### 2.1.2 IEEE P1500 Standard for Embedded Core Test

There is a close relationship between the structure of IEEE P1500 [13, 14] and the standard for boundary scan (IEEE 1149.1). IEEE 1149.1 architecture has been developed to facilitate board-level interconnect testing through chip-level wrappers. The same idea has been utilized to design a wrapper based test structure at the chip level for SoC devices containing embedded cores. Although the basic idea beyond these two methods is the same, they have important differences due to the significant flexibility required for embedded core testing. The wrapper in P1500 standard is used as a shell around a core under test. It allows the core to be isolated from its environment and tested independently. Figure 1 gives an overview of the main elements of the P1500 wrapper architecture. The wrapper in P1500 has three main types of modes:

#### 1. Functional Operation

In this mode the wrapper is transparent and operates as if it does not exist.

#### 2. Inward-facing

The test access to the embedded core is provided in this mode.

#### 3. Outward-facing

This mode provides test access to the circuitry outside the core.

As shown in Figure 1a, the P1500 wrapper has functional input and output ports. It also includes a Wrapper Interface Port (WIP) and an internal Wrapper Instruction Register (WIR) to control the test process. The operation of the wrapper is controlled by both the WIP signal and the instruction loaded into the WIR.

**Figure 1:** IEEE P1500 (a) wrapper architecture. (b) wrapper boundary input cell. (c) wrapper boundary output cell.

## 2.2 Analog Circuit Testing

Testing analog circuits is proven to be more challenging as compared to digital circuit testing due to the continues nature of analog signals and their sensitivity to signal degradation. Although just a small portion of most of the modern ICs is analog, the cost of analog circuit testing exceeds the cost of digital circuit testing in mixed signal environments due to the complexity of analog test generation and required equipment for test execution [15]. In a typical test scenario, a stimulus waveform is applied to the CUT and then the CUT's response is captured to evaluate the test result either in the time or frequency domain. Basic analog testers evaluate the test results in the time domain while advanced ATEs employ Fast Fourier Transform (FFT) as an effective tool for test-result analysis in the frequency domain.

#### 1. Traditional Analog Tester

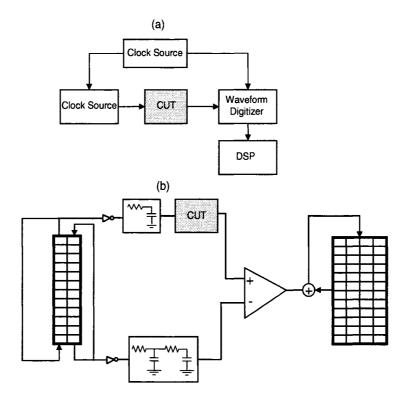

A basic test setup in the time domain as shown in Figure 2 involves applying a stimulus input to the analog circuit under test to excite the CUT with a dc, sinusoidal, squarewave, or some random signals and to measure the response with a power meter [10].

Figure 2: Traditional test setup for mixed-signal devices.

The traditional method of testing suffers from many factors limiting the application of such an approach. First, all defects in this method are assumed to have a detectable effect on the rms value at the output which in a general case of testing is not a valid assumption leading to a considerable number of undetected faults. Moreover, complete testing of some analog circuit specifications can take a significant amount of time. Consider, for example, measuring the integral nonlinearity of an ADC [16]. For a 12-bit ADC, this would require locating 4096 input voltages. Such a large number of tests can limit throughput during the device production phase and can significantly add to the cost of production.

#### 2. Digital Signal Processing (DSP) Based Analog Tester

DSP based testing of analog circuits [17] has been widely employed by ATE industry due to the flexibility and test reliability that this method provides. DSP is a powerful methodology that allows faster, more reliable and more accurate analog testing as compared to the traditional rms measurement method. A typical DSP based test setup for analog circuits as shown in Figure 3, involves applying analog stimulus to the CUT and sampling the output waveform to evaluate the response. The advantages of DSP based testing over traditional

**Figure 3:** DSP based analog tester scheme.

measurement techniques are summarized as follow:

#### • Reduced Test Time

In this method several sinusoidal waveforms with different frequencies and amplitudes can be added together to generate a multiple tone stimulus waveform. When the CUT response to such a stimulus waveform is captured, the responses to the different components of the applied multi-tone waveform are simultaneously determined. For example to test a filter, a multi-tone waveform can be applied and a serious of magnitude and phase responses can be measured at several frequencies at the same time. This capability eliminates the need for separate tests at different frequencies and significantly reduces the time required to carry out a complete test on

a typical CUT.

#### • Spectrum Analysis

The FFT analysis in the DSP based measurement provides a spectrum of the sampled signal, indicating the strength of each component in the frequency domain. This capability is a major advantage over non-DSP test methods. Using FFT analysis, the noise and distortion components can easily be separated from the CUT response to the fundamental component enabling an accurate and repeatable measurement.

#### Advanced Signal Processing

Since in this method the test results are evaluated in the digital domain, various DSP methods can be employed to improve the results. For example, the output resolution can be enhanced by interpolation between the samples or zero padding.

#### 2.2.1 Analog DFT Methods

There are many types of mixed signal DFT techniques, some of them are summarized as follows:

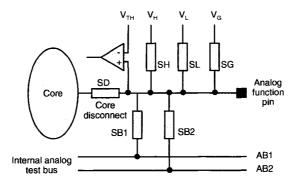

#### 1. Mixed signal boundary scan (IEEE Standard 1149.4)

IEEE 1149.4 is regarded as a mixed signal counterpart of the 1149.1 boundary scan for digital circuits. The 1149.4 standard [18] specifies the same signal pins that are associated with the 1149.1 standard. It is compliant with the digital Test Access Port (TAP) and boundary architecture. The main difference is that the 1149.4 includes new pins and analog switches to support analog signals. Figure 4 shows the 1141.4 architecture in which Digital-Boundary Modules (DBMs) are the boundary-scan cells defined in 1149.1 and Analog Boundary Modules (ABM) are the cells introduced in 1149.4 for mixed-signal devices. The IEEE

1141.4 standard employs two Analog-Test (AT) pins one to apply test signals and the other to route the response waveforms to the measurement equipment. The external analog-test bus, which connects to AT1 and AT2, accesses the internal bus under the control of the Test Bus Interface Circuit TBIC. The TBIC allows the internal test-bus lines to connect to either or both AT pins, isolates the internal test bus when it is not in use to eliminate unwanted noise interference, or connects the bus to one of two dc voltages (VH and VL). Interconnects between ICs can be tested by applying either  $V_H$  or  $V_L$  through an AT pin in one side and check the status of the signal at the other side.

**Figure 4:** Mixed signal boundary scan architecture.

The 1149.4 standard primary target is to perform a simple chip-to-chip interconnect testing similar to that used in traditional digital boundary scan. however, it can also be utilized to perform internal analog circuit testing [19]. Figure 5 shows the details of an ABM module which provides access to analog input and output signals via external pins.

#### 2. Ad-Hoc Mixed-Signal DFT

Figure 5: Analog boundary module in the 1149.4 standard.

Other than IEEE 1149.4 and IEEE P1500 standard there are a few generally accepted methods in the area of mixed-signal testing. Most of the mixed signal DFT methods are based on ad-hoc techniques that are developed for particular applications. Many companies deploy their own application-specific ways to improve testability, such as adding special function modes, increasing the number of output and input pins, and providing internal loops.

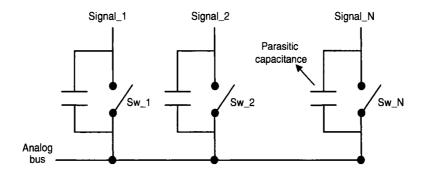

For a large analog circuit, applying the test signal to an input pin and capturing the response from the output provides a limited observability. Therefore, it is desirable to divide the CUT into several parts and add some test pins between them so that each part of the circuit can be tested separately. One of the popular methods to provide access to the internal nodes of a CUT is through analog test buses (Figure 6). This method can increase the testability and the observability of integrated circuits significantly. However, it suffers from several drawbacks. First, the switches are commonly implemented using complementary CMOS P and N transistors that introduce a parasitic capacitance in parallel with the switch. The parasitic capacitances provide an AC path between the analog nodes in the CUT that may cause instability and oscillation. Moreover, the crosstalk and clock feed through [20] between the observed nodes may become a serious problem undermining the accuracy of the measurement.

**Figure 6:** A typical analog test bus.

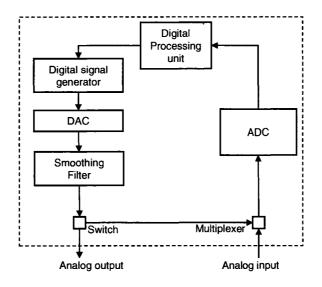

#### 3. Mixed-Signal Built-in-Self Test (BIST)

BIST is the most promising approach to improving mixed-signal DFT. One of the main advantages of BIST method is the protection of analog signals against distortion. BIST techniques employ on-chip signal generators and analysis circuitry, which results in less distortion and greater measurement accuracy. If BIST is fully implemented, the only signal that needs to be routed off chip is a pass/fail bit indicating the test results. The main problem faced by BIST is the fact that the BIST circuitry is exposed to the same process and temperature variations as the CUT. Therefore, it is critical for any BIST scheme to support self test and calibration. To reduce the BIST area overhead, existing on-chip hardware can be used. On-chip DACs and ADCs can effectively be employed to build a BIST structure for low speed mixed-signal devices.

A typical on-chip test architecture for a mixed-signal circuit is shown in Figure 7. Digital input data for the DAC can be provided by a linear feedback shift register (LFSR) or a Read Only Memory (ROM) and a built-in logic block observers (BILBO) [7] can be utilized to capture the ADC output. The data stored in the BILBO registers can be compared against a known response stored in a on-chip memory or it can be analyzed using a Multiple Input Signature Register

Figure 7: Mixed-signal BIST architecture using on-chip ADC and DAC modules.

(MISR). In [21], a BIST scheme is introduced to detect faults based on the autocorrelation and cross-correlation of the impulse responses for a pseudorandom piecewise-constant input signal. In [22], a BIST circuit is proposed to observe changes in the power supply current as an indicator for detecting faults. The main idea behind this approach is that faults will either increase or decrease the power supply current compared to the fault-free circuit. In [23] a BIST circuit has been designed to test DACs. The samples of the response waveforms in this scheme are captured with a sample-and-hold circuit to measure offset, gain, integral linearity, and differential linearity of DACs. A modified version of this circuit has also been proposed for testing successive approximation ADCs. [24, 25] a vectorless BIST technique called Oscillation Built in Self Test (OBIST) is proposed. In this method the CUT is converted to an oscillator. Then the oscillation frequency and the amplitude of the output are used as indicators for test result evaluation. The deviation of the oscillation frequency and the output amplitude from their nominal values indicate a faulty circuit. Most of the test methods developed for analog circuits are based on functional tests

while the OBIST can be implemented for structural tests. This is a significant advantage over the other methods since it opens the way for development of CAD tools for analog circuit testing. The oscillation-test method can provide a test solution to low frequency analog and mixed-signal circuits such as active filters and operational amplifiers [26, 27]. The only complication is how to add analog switches to establish feedback paths and meanwhile reduce the effect of test circuitry on normal CUT operation. Achieving this goal at the RF frequency range poses a formidable challenge where the loading effect of switches can undermine the performance of the CUT.

Due to various problems such as impact on performance, area overhead or implementation difficulties most of the analog BIST methods have not been used in industry. For an analog BIST to be successful at least to main condition should be satisfied: First, it must be accurate in the presence of normal noise and process variation to achieve test repeatability, and second it has to be easily implemented and if possible offered as a digitally synthesizable module.

#### 4. Separation of Analog and Digital Circuits

The separation of analog and digital circuits provides better control over analog circuits. Scan cells known as scan collars can be employed to break a mixed-signal circuit to analog and digital parts. Once the circuit is broken into digital and analog parts, digital circuits can be tested using the efficient CAD based test methods developed for digital circuits. The analog portion can be analyzed separately and proper test method can be developed accordingly. This divide and conquer methodology is particularly useful when a small analog circuit is integrated with a large digital circuit on a chip.

#### 2.2.2 State of the Art

Some of the analog test methods developed over the years to lower the burden of analog circuit testing in mixed-signal environment were presented in the previous section. In this section the state of the art research works in the area of on-chip analog/RF circuit testing and their advantages and limitations are presented.

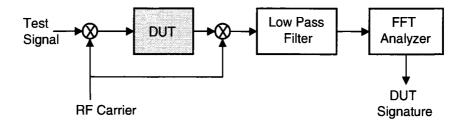

In [28] a test method for high frequency analog circuit is presented. The test scheme as indicated in Figure 8 employs two on-chip mixers. The first mixer is used to

Figure 8: Signature test configuration for RF circuits [28].

up convert a low frequency test waveform to a high frequency test stimulus signal. The second mixer is employed to down convert the CUT response from high to low frequency. The demodulated signal is used to evaluate the performance metric of the CUT. This method has potential to enable a low performance external tester to carry out test on high speed embedded circuits. The main disadvantage of this method is that it does not take into account the nonlinearity effects of the on-chip mixers. Moreover since the mixers are exposed to the same process variation as the embedded circuits, the scheme can not provide reliable measurement results without calibration.

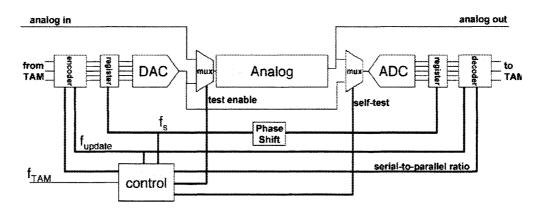

In [29, 30, 31] a compact DSP tester has been developed for analog circuit testing. It is a general purpose mini-ATE with an on-chip arbitrary waveform generator an a compact ADC for result evaluation. The functional diagram and detail view of this tester is shown in Figure 9. The tester retains all the advantages of the DSP-based

test method moreover it provides an easy implementation solution. The proposed test scheme has been almost entirely implemented in digital domain using standard CMOS gates expect for an op-amp and a basic low pass filter. Although this tester

**Figure 9:** (a) Functional diagram and (b) detailed view of the proposed on-chip test system in [29]

can be employed to perform test on numerous analog circuits, it can not be used for high frequency analog/RF cores due to the frequency limits of the employed signal generator .

In [32] a modular test approach for mixed signal SoCs has been proposed. A unified test access architecture has been developed for both digital and analog cores. Each analog core in this method is wrapped by a pair of digital-to-analog converter and analog-to-digital data converters as shown in Figure 10. The proposed method provides a solution for low speed analog circuits in mixed signal environments. However, due to a limited speed of the employed ADC and DAC converters, this method also

cannot be utilized for high speed analog circuits testing.

**Figure 10:** Block diagram of the test wrapper proposed in [32] for mixed-signal SOCs testing.

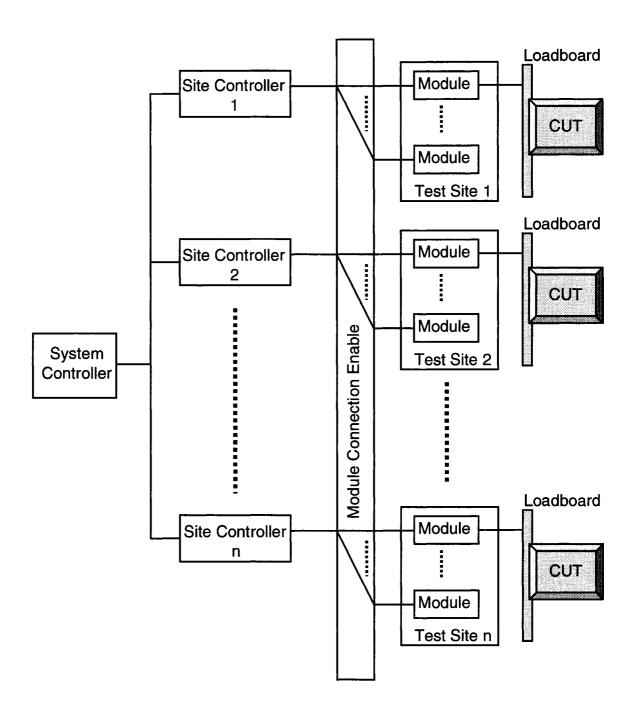

Leading companies in the ATE industry such as Advantest [33] and Teradyne [34] have also intensified efforts to provide a test solution for the next generation of mixed signal devices. The ATE industry is moving toward an open architecture automatic test equipment to integrate software and instruments of different vendors into ATEs. The use of modules in this framework is based on plug-and-play to achieve the optimal test configuration. Each modular unit can be removed, replaced with another unit from a different vendor, or reconfigured to map the test resources according to the requirements of device-under-test (DUT). Open architecture tester eliminates fixed configuration and provides a considerable flexibility to meet various chip test requirements resulting in an optimized and cost effective ATE. Figure 11 shows a typical open architecture ATE.

Figure 11: Block diagram of an open architecture ATE.

## 2.3 Summary

This chapter presented introductory material that relates to DFT for mixed signal devices. IEEE 1149.1 and P1500 standards which are the most successful DFT methods in the field of digital and analog circuits were briefly covered. Dominant test techniques developed over years to address the problem of analog circuit testing were introduced. The last part of the chapter focused on the state of the art in the field of Analog/RF circuit testing in both academia and industry.

### CHAPTER III

### PROPOSED TEST METHOD

Previous research works in the area of mixed-signal IC design have considered the integration of some test functionality to lower the burden of analog circuit testing; however they have been mainly aimed at providing test solutions for low frequency mixed-signal ICs [35]- [38] or developing customized test methods [39]- [47] for specific high-speed analog/RF circuits or applications. In this work a new test methodology based on an on-chip tester for high speed analog/RF circuits is presented. The proposed test method utilizes DSP techniques due to significant advantages of DSP based test methods over traditional approaches. To test fast analog/RF circuits, high-speed stimulus waveforms are required to excite the CUTs. Response waveforms are also needed to be captured at high speed to prevent the loss of information. These requirements can not be met by generic DSP based test scheme in which the stimulus generation and response measurement can hardly exceed maximum frequency of a few tens of MHz due to the speed limitation of DAC and ADC converters.

In the proposed test solution, modulation and subsampling methods have been employed as enabling techniques to overcome the limitations of the DSP based test approach. In this method a low frequency stimulus waveform is generated by an external Arbitrary Waveform Generator (AWG). This waveform is then mixed with a high frequency on-chip signal and upconverted from low to high frequency. The resultant waveform is used as a high-speed test stimulus signal to excite a CUT. On the other hands, the high frequency response of the CUT is down converted from high to low frequency through subsampling techniques. This test method eliminates the need for high speed interactions between the CUT and the external environment

since all high speed tests are carried out inside the chip.

It is highly desirable to implement on-chip testers in the digital domain due to various reasons such as scalability, ease of implementation, and lower noise sensitivity. Therefore, to design an embedded tester for analog/RF circuits, it is essential to choose proper modulation method among numerous modulation techniques to reduce the complexity of the tester and minimize the number of analog circuits. In this chapter first the enabling techniques are described and then a system level simulation in Matlab/Simulink is performed to validate the proposed test method and in the end the conceptual block diagram of the tester is presented.

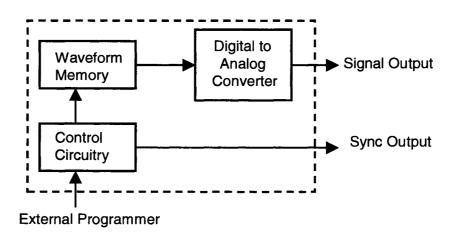

### 3.1 Modulation Based Test Stimuli Generation

The stimulus waveform in the DSP test method is generated by an Arbitrary Waveform Generator (AWG). The basic idea behind AWG is to digitally store the samples of the desired signal in a memory and convert them to an analog signal through a digital to analog converter. Figure 12 shows a typical AWG in which a waveform memory is employed to provide data for a DAC. This method of test waveform gen-

**Figure 12:** Block diagram of a typical programmable AWG.

eration offers several advantages such as a very low phase noise and direct mixing of signals in digital domain. Moreover, since the waveform is digitally stored in a memory it can readily be modified to generate any desired waveform without the limitations imposed by hardware in basic waveform generators. However, the maximum frequency of the signal supplied by a generic AWG is limited by the speed of the employed DAC.

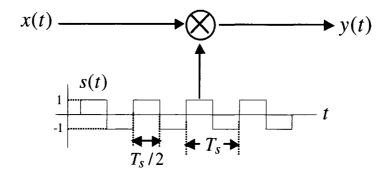

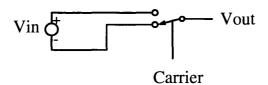

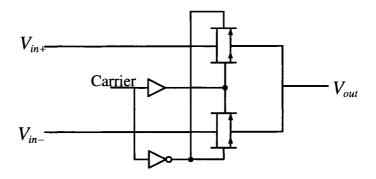

Modulation techniques can be utilized to overcome that barrier. There are numerous methods of modulation developed over years for different applications, however for the purpose of fast analog circuit testing, a balanced modulator based on a bipolar chopper modulator (Figure 13) offers attractive properties that can be summarized as: (a) It can be implemented using a simple passive mixer which presents a higher linearity compared to active mixers. (b) Its carrier signal is a squarewave that can be generated and controlled by digital circuits. The Fourier series expansion representing

**Figure 13:** Bipolar chopper modulator.

the output waveform y(t) of a bipolar chopper modulator is given by:

$$y(t) = \frac{4}{\pi}x(t)\cos w_s t - \frac{4}{3\pi}x(t)\cos 3w_s t + \frac{4}{5\pi}x(t)\cos 5w_s t - \dots$$

(1)

Where x(t) is a modulating signal and  $\omega_s$  is the circular frequency of the carrier. If x(t) is sinusoidal, the spectrum of y(t) will have two tones that are repeated at odd harmonics of the carrier signal enabling the tester to perform two-tone tests and measure intermodulation distortion of RF components. The use of a square wave carrier instead of a sine waveform introduces higher frequency harmonics, adding to the computational complexity of the response measurement. However, as outlined below, using a digital level squarewave carrier offers a number of advantages that justify its use for on-chip high-speed stimuli generation.

### 1. Wide tuning range

For a sinusoidal oscillator, once the design is completed, the test frequency range is fixed by the oscillator's tuning range and cannot be easily expanded. However, with a squarewave digital level oscillator, the range can simply be expanded by adding a divide by N counter to the output of the oscillator and using the counter's output as a new lower frequency carrier.

### 2. Lower sensitivity

Digital level signals are generally more immune to noise and distortion than analog signals.

### 3. Lower nonlinearity effect of the mixer

A passive CMOS mixer driven by a squarewave instead of a sinusoidal signal exhibits less nonlinearity due to a relatively high overdrive voltage [49].

## 3.2 Sampling Techniques

To perform DSP based measurement, samples of the desired waveform have to be obtained via sampling techniques [50]. In a general case of DSP based measurement, samples of the desired waveforms are captured through a sampler and converted to digital data via an ADC. The outputs of the ADC are stored in a memory and supplied to an FFT analyzer as a set of data representing the captured waveform. Finally, the spectrum of the captured signal is determined by FFT techniques from the test result evaluation. However, FFT analysis can produce misleading results if it is not

implemented properly.

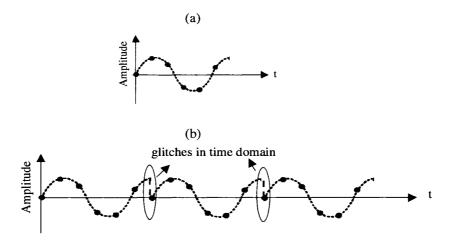

The FFT method essentially assumes that each given set of samples represent a periodic signal. This periodicity assumption introduces error if the given set of samples does not contain an integer number of cycles of the sampled waveform. Figure 14 shows a non-coherent [17] set of samples of a sinusoidal waveform used for an FFT calculation and the actual waveform represented by the computed FFT. It can be

**Figure 14:** (a) Non coherent samples of a sinusoidal waveform used for FFT calculation. (b) the waveform represented by the FFT spectrum.

observed that the periodicity assumption translates into glitches in the time domain. As a result, the spectrum obtained by the FFT shows frequency leakage distortion. To deal with this problem various windowing techniques (e.g. Kaiser, Hamming, Han, etc.) have been developed. However, none of them can entirely eliminate the effect of the frequency leakage.

### 3.2.1 Coherent Sampling

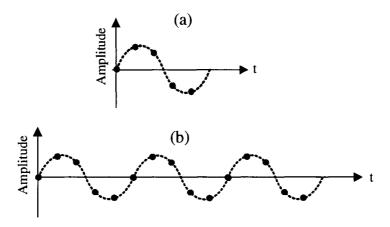

In a general case of sampling, spectral leakage is unavoidable. However, if the period of the desired signal is known, then by obtaining a proper set of samples the frequency leakage can be avoided.

For the purpose of testing where the tester has full control over the signals and

samples frequency leakage can be avoided by coherent sampling which is widely used by ATE industry for FFT calculation. The following equation has to be satisfied to successfully obtain a coherent set of samples.

$$F_s/N = F_t/M \tag{2}$$

Where  $F_s$ ,  $F_t$ , N and M represent sampling clock frequency, test signal frequency, total number of samples taken and total number of cycles respectively. Figure 15 shows a coherent set of samples used for the FFT calculation and the associated periodic waveform represented by the computed FFT. Coherent sampling not only eliminates

**Figure 15:** (a) Coherent samples of a sinusoidal waveform used for FFT calculation. (b) the waveform represented by the FFT spectrum.

the frequency leakage problem but leads to faster test time and less computation. The only complication is that a timing synchronization between the test signal and the sampling clock is required. In the proposed embedded tester scheme in this work, the AWG and the sampling clock generator have been synchronized through a coupled DLL and PLL structure to satisfy the coherent sampling requirement.

### 3.2.2 Subsampling Method

The basic DSP test setup can not properly test high speed devices even if the problem of high speed test stimulus generation by the AWG is solved. In order to successfully

26

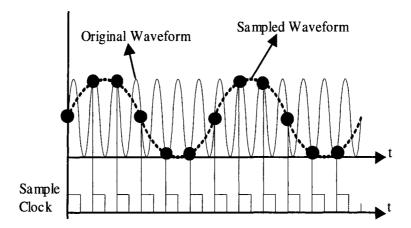

convert high-speed analog waveforms into digital data, a fast ADC is required. However, due to the limited speed of ADC devices a direct conversion method can hardly be applied to digitize signals running faster than a few tens of MHz. The subsampling method is proven to be an efficient technique to enable low speed ADCs to digitize high speed waveforms. To illustrate the technique, consider a periodic signal x(t) with frequency equal to  $f_s$  that is sampled with frequency  $f_s + \Delta f$  where  $\Delta f$  is a small increment. As indicated in Figure 16, the sampling points walk along the waveform

**Figure 16:** Subsampling a periodic waveform.

x(t) at a rate equal to  $\Delta f$  capturing an expanded version of the original waveform. The sampled waveform y(t) is expressed as  $y(t) = x(\alpha t)$  where  $\alpha = \frac{\Delta f}{fx}$ . Thus, a low-speed ADC can be employed to digitize the expanded waveform. The original high-speed signal can later be reconstructed from the samples of the expanded waveform by digital signal processing methods. To illustrate the operation of subsampling technique in frequency domain, consider a typical periodic waveform characterized by a discrete spectrum in frequency domain, ideally sampled by a train of impulses; the result can be expressed as:

$$y_1(t) = x(t) \sum_{i=-\infty}^{+\infty} \delta(t - KT_s)$$

(3)

Where  $T_S$  is the sampling period and  $\delta()$  represents the delta function. The corresponding spectrum is represented by:

$$Y_1(f) = f_s \sum_{i=-\infty}^{+\infty} X(f - Kf_s)$$

(4)

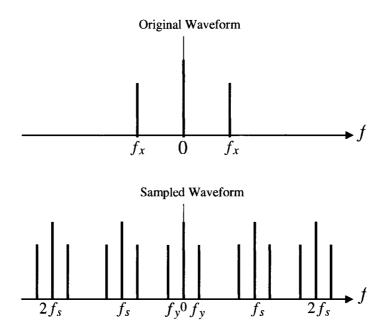

As a result the fundamental appears at the beat frequency  $f_y = f_s - f_x = \Delta f$  and compressed images of the spectrum centered at  $Kf_s$  are created as indicated in Figure 17. To reconstruct the high frequency signal, a low pass filter can be used to separate

**Figure 17:** Subsampling spectrum.

the fundamental from the spectrum of the sampled waveform.

# 3.3 System Level Simulation of the Proposed Test Method

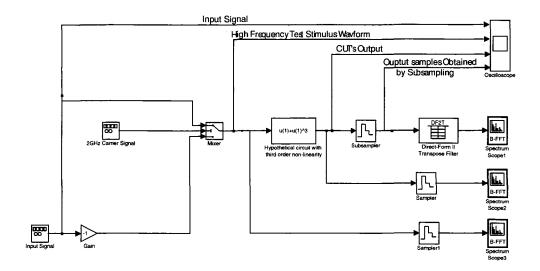

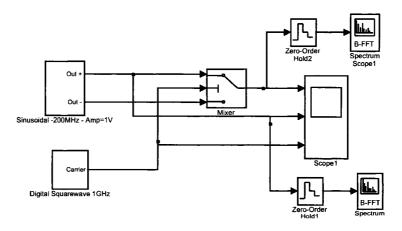

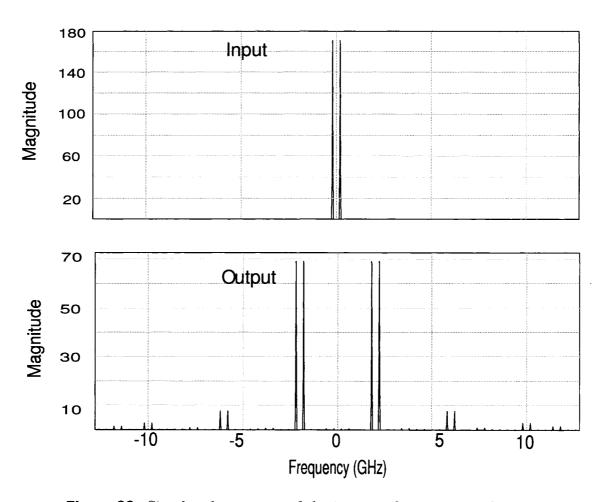

To verify the application of the proposed enabling techniques a Matlab/Simulink simulation is conducted. The simulation setup is shown in Figure 18. A sinusoidal signal with a period of 5ns represented by  $x(t) = 1.5\sin(2\pi \times 200 \times 10^6 t)$  is applied to a bipolar mixer to modulate a 2 GHz square carrier. The output of the mixer is

**Figure 18:** Simulation setup to verify the proposed test technique.

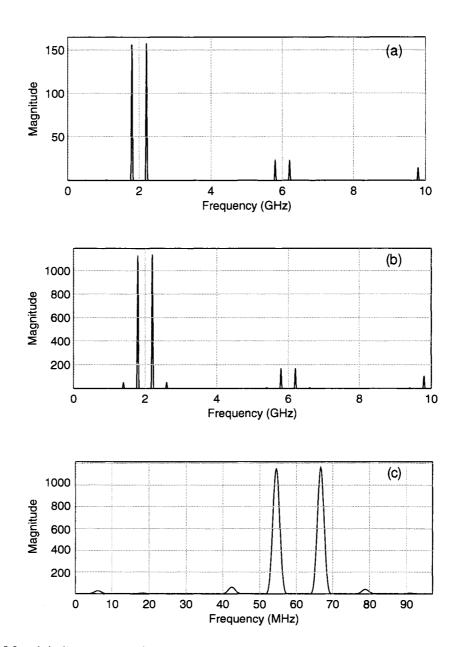

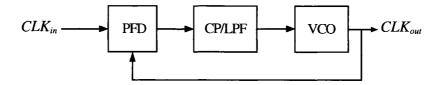

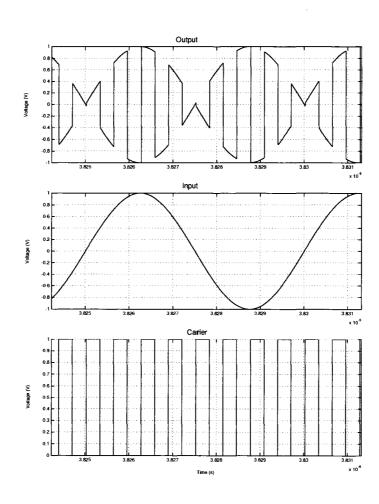

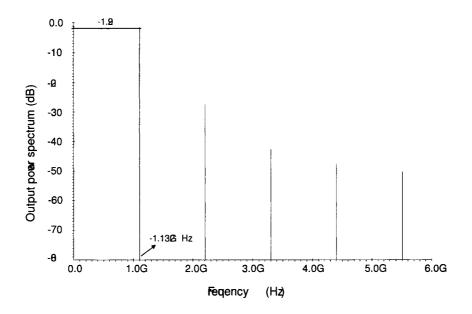

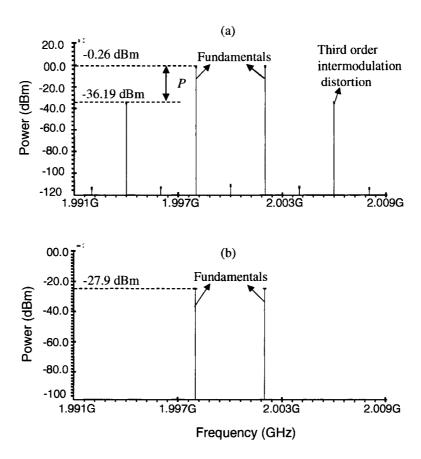

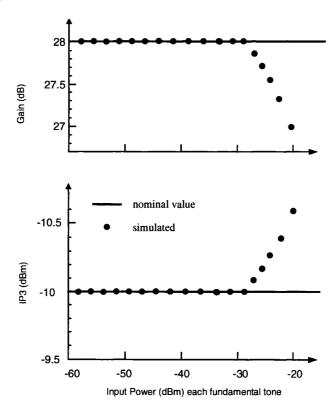

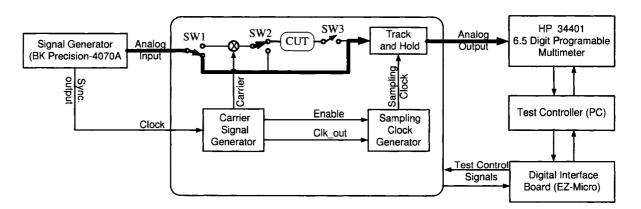

applied to a hypothetical CUT with third order non-linearity which is represented by  $y = u(1) + u(1)^3$  where u(1) is the input variable. The response waveform is subsampled with the speed of 5 ns + 5 ns/32. The samples are processed via a digital filter and then applied to a spectrum scope for FFT analysis. A four-channel oscilloscope is used to display signals before and after subsampling in the time domain. The signals obtained by the oscilloscope are shown in Figure 19. Three FFT analyzer modules are used to determine the spectrum of the stimulus signal applied to the CUT, the spectrum of the CUT response and the spectrum of the output after subsapling respectively. The spectrum of the output as shown in Figure 20 indicates that the response of the CUT at 2 GHz is downconverted to 2 GHz/32=62.5 MHz. The effect of the third harmonic distortion is also shown in the simulation results. The conducted simulation shows that if the mixing and subsampling techniques are properly employed a high speed circuit can effectively be tested with low speed measurement instruments.

**Figure 19:** Modulation and subsampling techniques (a) low frequency test generated by the AWG. (b) high frequency test signal applied to a hypothetical CUT. (c) CUT's output signal. (d) samples of the CUT obtained by subsampling.

**Figure 20:** (a) Spectrum of the input waveform applied to the hypothetical CUT. (b) spectrum of the CUT's response waveform. (c) spectrum of the CUT's response after downconversion.

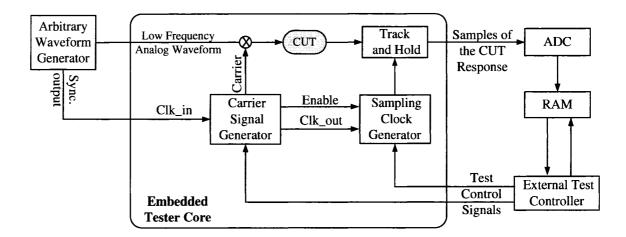

# 3.4 Architecture of the Proposed Embedded Tester

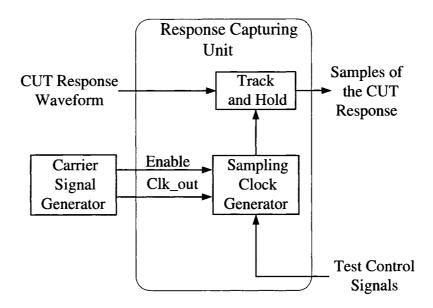

Figure 21 shows the conceptual block diagram of the tester core. The high frequency

**Figure 21:** Block diagram of the proposed tester core.

portion of the tester is embedded inside the chip as part of the DFT implementation while the low frequency part that includes AWG, ADC, RAM and Test Controller are externally configured. The tester operates as described below:

The AWG provides a low frequency periodic waveform that modulates the carrier through the mixer. It also provides a sync output which is a digital version of the supplied analog waveform. The sync signal is applied to a PLL driven carrier signal generator to synchronize the carrier with the low frequency waveform supplied by the AWG. This synchronization is required to support coherent subsampling. The mixer's output, which is a high frequency waveform, is applied to the CUT as a test stimulus. The samples of the CUT response waveform are captured through a track and hold circuit. The sampling clock generator provides the T/H with a synchronized clock to obtain proper samples of the CUT's output through subsampling. The captured samples are then transferred to an external controller for test result evaluation.

The proposed test scheme requires precise timing edges to sample the CUT's output at the right moment otherwise the captured samples do not represent the original high frequency waveform. In the proposed tester a coupled PLL and DLL module has been employed for the purpose of synchronization. The external stimulus waveform, the internal carrier and the sampling clock are all synchronized together through this module. This multi-level synchronization enables the tester to chop the AWG waveform to integer-N slices and at the meantime provide a sampling clock to obtain coherent samples of the CUT response through subsampling.

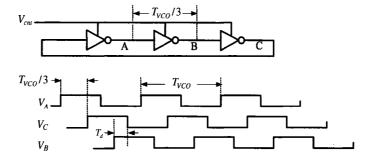

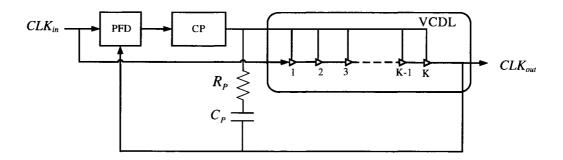

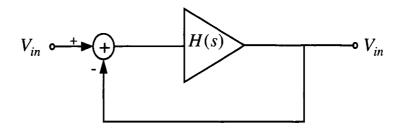

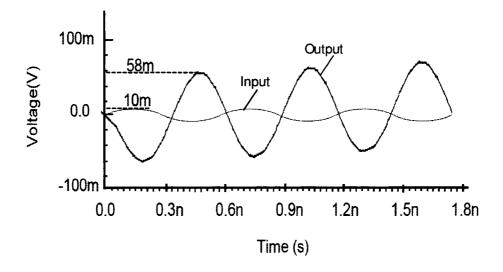

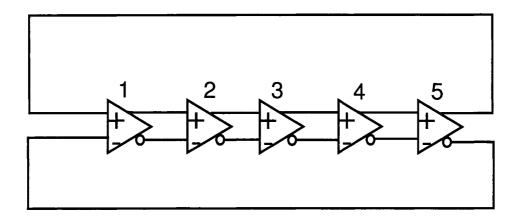

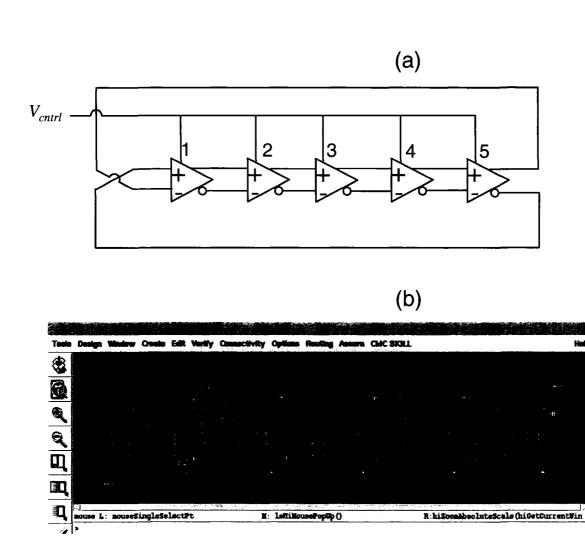

### 3.5 Test Protocol