#### **University of Windsor**

## Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2004

## New VLSI design of a MAP/BCJR decoder.

Leila Sabeti University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Sabeti, Leila, "New VLSI design of a MAP/BCJR decoder." (2004). *Electronic Theses and Dissertations*. 2850.

https://scholar.uwindsor.ca/etd/2850

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# New VLSI Design of a MAP/BCJR Decoder

by

#### Leila Sabeti

#### A Thesis

Submitted to the Faculty of Graduate Studies and Research through the Department of Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at The University of Windsor

Windsor, Ontario, Canada 2004

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-494-00161-5 Our file Notre référence ISBN: 0-494-00161-5

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## © 2004 Leila Sabeti

All Rights Reserved. No part of this document may be produced, stored or otherwise retained in retrieval system of transmitted in any form, on any medium or by any means without the prior written permission of the author.

## New VLSI Design of a MAP/BCJR Decoder

by

Leila Sabeti

| APPROVED BY:                                  |  |

|-----------------------------------------------|--|

|                                               |  |

| R. Lashkari<br>IMSE Department                |  |

| M.A. Sid-Ahmed ECE Department                 |  |

| M. Ahmadi, Advisor<br>ECE Department          |  |

|                                               |  |

| B. Shahrava, Chair of Defense  ECE Department |  |

September 29, 2004

# Abstract

Any communication channel suffers from different kinds of noises. By employing forward error correction (FEC) techniques, the reliability of the communication channel can be increased. One of the emerging FEC methods is turbo coding (iterative coding), which employs soft input soft output (SISO) decoding algorithms like maximum a posteriori (MAP) algorithm in its constituent decoders. Owing to their outstanding performances, turbo codes have already been adopted by recent communication systems such as Consultative Committee for Space Data systems (CCSDS), telemetry channel coding and the 3rd Generation Partnership Project. A major difficulty of applying turbo codes in many applications is the decoding complexity of SISO decoders.

Efficient implementations of these decoders can significantly increase the employment of turbo codes in different communication applications. Because Max-Log-MAP algorithm is the best compromise among other algorithms in terms of performance and implementation complexity, our implementation is based on this algorithm.

In this thesis we introduce a design with lower complexity and less than 0.1dB performance loss compare to the best performance observed in Max-Log-MAP algorithm. A parallel and pipeline design of a MAP decoder suitable for ASIC (Application Specific Integrated Circuits) is used to increase the throughput of the chip. The branch metric calculation unit is studied in detail and a new design with lower complexity is proposed. The design is also flexible to communication block sizes, which makes it ideal for variable frame length communication systems. A new even-spaced quantization technique for the proposed MAP decoder is utilized. Normalization techniques are studied and a suitable technique for the Max-Log-MAP decoder is explained. The decoder chip is synthesized and implemented in a  $0.18 \,\mu$  m six-layer metal CMOS technology.

# Acknowledgments

I would like to extend my sincere gratitude and appreciation to people who have contributed to the completion of this thesis.

First and foremost, I would like to thank my supervisor, Dr. Majid Ahmadi, for whom I have the utmost respect and admiration. He had a tremendous impact on me academically, socially and personally, and for this I am forever in his debt.

I am also grateful to Dr. Kemal Tepe for his knowledge suggestions and his enthusiasm towards my research. I would also like to thank my committee members, Dr. M. A. Sid-Ahmed and Dr. R. Lashkari for their patience and support.

Additionally, I would like to thank my husband, Shahram Talakoub for his patience, his confidence in my ability and his guidance and assistance toward my research. Finally, I would like to acknowledge my parents for their constant support, encouragement and motivation.

# Table of Contents

| Abstract                            | iv  |

|-------------------------------------|-----|

| Acknowledgements                    | v   |

| List of Figures                     | ix  |

| Chapter 1: Introduction             |     |

| 1.1 Digital Communication Systems   | 1   |

| 1.1.2 Information Source            | 2   |

| 1.1.3 Source Encoder                | 2 3 |

| 1.1.4 Channel                       | 4   |

| 1.1.5 Noise                         | 5   |

| 1.1.6 Channel Coding                | 6   |

| 1.1.7 Modulation                    | 6   |

| 1.1.8 Source Decoder                | 6   |

| 1.1.9 Output Information            | 6   |

| 1.2 History of Coding               | 7   |

| 1.3 Number Systems                  | 8   |

| 1.3.1 Signed Fixed Point Numbers    | 8   |

| 1.3.2 Redundant Number Systems      | 9   |

| 1.3.3 Residue Number Systems        | 10  |

| 1.3.4 Logarithmic Number Systems    | 11  |

| 1.3.5 Floating point Number Systems | 11  |

| 1.4 Thesis Overview                 | 12  |

| 1.4.1 Thesis Highlights             | 12  |

| 1.4.2 Thesis Overview               | 13  |

| Chapter 2: Turbo Coding             | 14  |

| 2.1 Turbo Encoder                   | 14  |

|                                     |     |

| 2.2 RSC Encoder                     | 16  |

| 2.3 Interleavers                    | 20  |

| 2.3.1 Pseudo-Random Interleavers    | 20  |

| 2.3.2 Convolutional Interleavers    | 20  |

| 2.4 Turbo Decoder                                              | 21       |

|----------------------------------------------------------------|----------|

| 2.5 Turbo Coding Algorithms                                    | 23       |

| 2.5.1 Viterbi Algorithm (VA)                                   | 24       |

| 2.5.2 MAP/BCJR Algorithm                                       | 26       |

| 2.5.3 Results of the MAP Algorithm                             | 31       |

| 2.5.4 Max-Log-MAP Algorithm 2.5.5 Log-MAP Algorithm            | 32<br>34 |

| 2.5.6 Sliding MAP                                              | 35       |

| 2.6 Improving the Max-Log-MAP Turbo Decoder                    | 35       |

| 2.7 Algorithm Comparison                                       | 37       |

| 2.8 System Specification Summary                               | 38       |

| Chapter 3: System Design and Modeling                          | 39       |

| 3.1 Max-Log-MAP Decoder Block Diagram                          | 40       |

| 3.2 New Branch metric Calculation Unit                         | 41       |

| 3.3 Proposed Node Metric Calculation Unit                      | 43       |

| •                                                              | 45       |

| 3.4 Log-likelihood Ratio (LLR)                                 | 45       |

| 3.5 Soft Output Calculation Unit                               | 46       |

| 3.6 Quantization                                               |          |

| 3.7 Normalization                                              | 50       |

| Chapter 4: RTL Simulation and Synthesis                        | 53       |

| 4.1 Verilog History                                            | 53       |

| 4.2 RTL Coding                                                 | 55       |

| 4.3 Synthesis                                                  | 65       |

|                                                                |          |

| Chapter 5: VLSI Implementation                                 | 68       |

| 5.1 Hardware and Software Trade-offs                           | 69       |

| 5.1.1 16-bit Fixed-point DSPs                                  | 71       |

| 5.1.2 Modern VLSI DSPs 5.1.3 application-Customized RISC Cores | 71<br>72 |

| 5.2 Floorplanning and Power Planning                           | 73       |

| 5.2.1 Ring Power Pads                                          | 74       |

| 5.2.2 Core Power Pads                                          | 75       |

| 5.3 Placement                                                  | 75       |

| 5.4 clock Tree Generation              | 76  |  |

|----------------------------------------|-----|--|

| 5.5 Routing                            | 76  |  |

| 5.5.1 Sroute                           | 76  |  |

| 5.5.2 Trial Routing                    | 77  |  |

| 5.5.3 Nano Route                       | 77  |  |

| 5.5.4 Wroute                           | 77  |  |

| 5.6 Filler Cells                       | 78  |  |

| 5.7 Metal Fill                         | 78  |  |

|                                        |     |  |

| Chapter 6: Results and Conclusion      | 79  |  |

| 6.1 results and comparison             | 80  |  |

| 6.2 Summary of Contributions           | 80  |  |

| 6.2.1 Algorithmic Contribution         | 82  |  |

| 6.2.2 Architectural Contribution       | 82  |  |

| 6.2.3 System Level Design Contribution | 82  |  |

| 6.3 Conclusions                        | 83  |  |

| References                             | 84  |  |

| Appendix A                             | 92  |  |

| Appendix B                             | 94  |  |

| Appendix C                             | 109 |  |

| Appendix D                             | 113 |  |

| VITA ALICTORIS                         | 120 |  |

# List of Figures

| Figure 1.1 A typical digital communication system                                        | 2     |

|------------------------------------------------------------------------------------------|-------|

| Figure 1.2 A channel model                                                               | 5     |

| Figure 2.1 Turbo encoder                                                                 | 15    |

| Figure 2.2 RSC Encoder                                                                   | 16    |

| Figure 2.3 State diagram of RSC encoder                                                  | 18    |

| Figure 2.4 Trellis diagram of the RSC decoder                                            | 18    |

| Figure 2.5 A middle section of the trellis diagram                                       | 19    |

| Figure 2.6 Code tree representation                                                      |       |

| Figure 2.7 Comparison of block, convolutional, and random interleaving                   | 21    |

| Figure 2.8 Turbo decoder                                                                 | 22    |

| Figure 2.9 Turbo decoding algorithms                                                     | 23    |

| Figure 2.10 Viterbi algorithm with generator (7, 5) for BSC                              | 26    |

| Figure 2.11 Turbo code with different scaling factors, block length 5114 bit, 8iteration |       |

| AWGN, rate 1/3 and generators (13, 15) <sub>oct</sub>                                    | 36    |

| Figure 2.12 Comparison between performances of turbo coding algorithms, block length     | gth   |

| 668bit, 4 iterations, AWGN, rate 1/3 and generators (7, 5)                               | 37    |

| Figure 3.1 Block diagram of the proposed Max-Log-MAP decoder                             |       |

| Figure 3.2 Branch metric calculation unit                                                | 43    |

| Figure 3.3 Parallel architecture of the $\alpha$ calculation unit                        |       |

| Figure 3.4 Log-likelihood calculation                                                    |       |

| Figure 3.5 Pipeline calculation of LLR for 4 state Max-Log-MAP decoder                   | 46    |

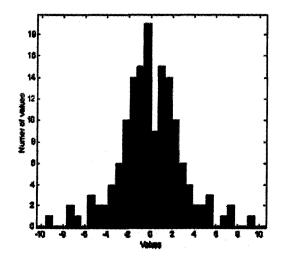

| Figure 3.7 Histogram for the a Priori Probability values (LUT input)                     | 48    |

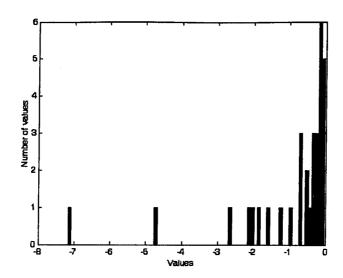

| Figure 3.8 Logarithm of the AP(-1) or AP(+1) (LUT output)                                | 49    |

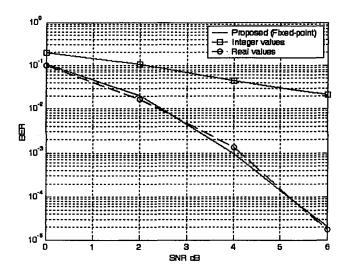

| Figure 3.9 Comparison between proposed quantization, using integer values for            |       |

| quantization and the best possible performance (AWGN, 400 bits frame, no itera           | tion, |

| Max-Log-MAP decoder)                                                                     | 49    |

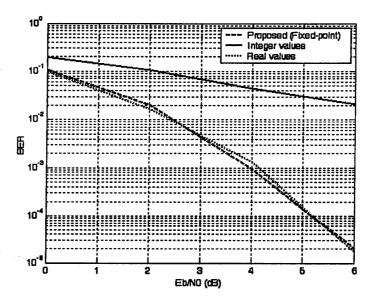

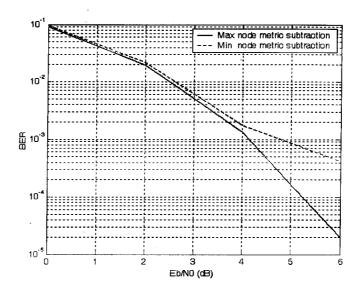

| Figure 3.10 Comparison between two normalization methods, block length 400               | 52    |

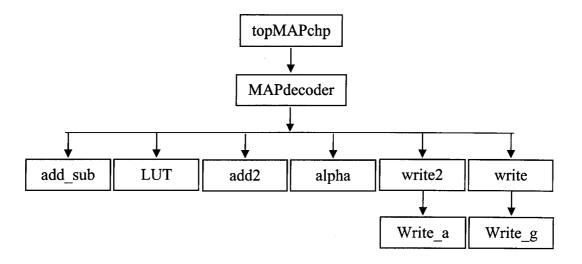

| Figure 4.1 hierarchical levels of the modules written in Verilog                         | 56    |

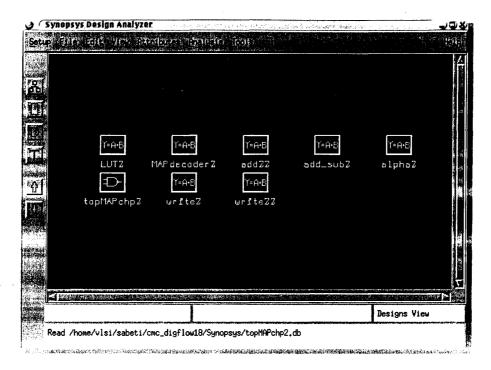

| Figure 4.2 Modules in Synopsys, Design analyzer                                          | 57    |

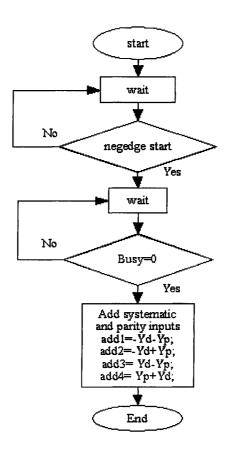

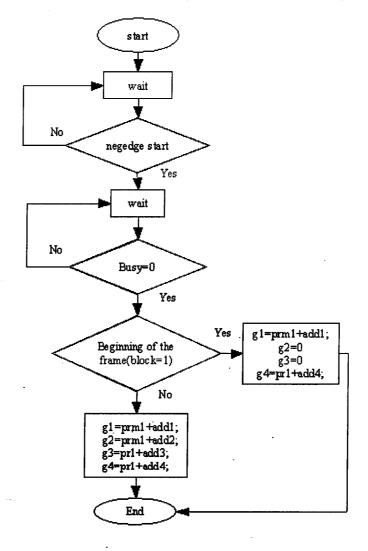

| Figure 4.3 add_sub module flowchart                                                      |       |

| Figure 4.4 add module                                                                    |       |

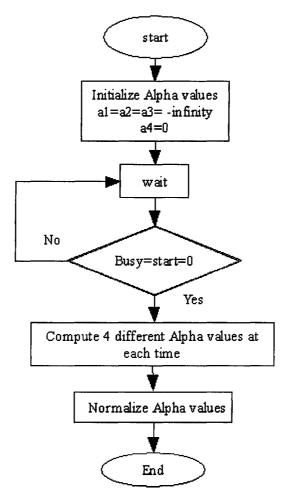

| Figure 4.5 Alpha module                                                                  |       |

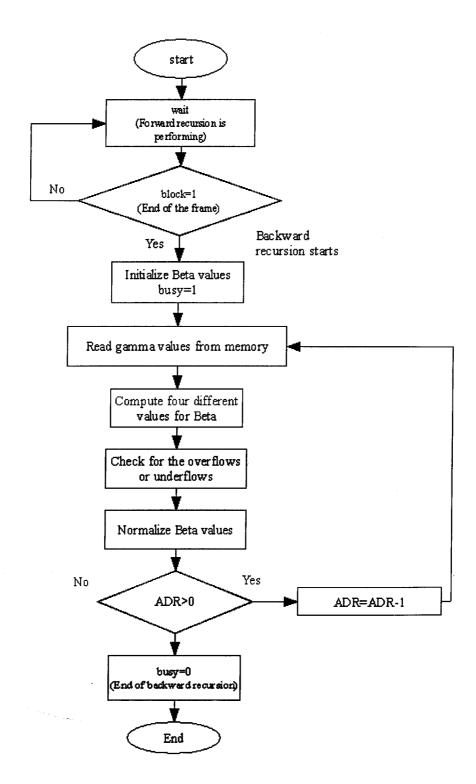

| Figure 4.6 write module (computation of Beta values)                                     | 62    |

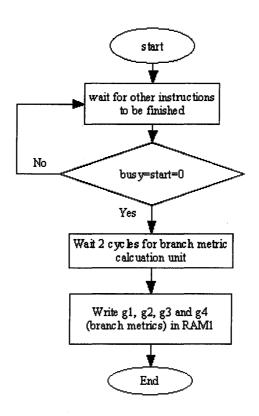

| Figure 4.7 write module (writing branch metric values into RAM1)                         | 63    |

| Figure 4.8 writ2a module (LLR computation)                                               |       |

| Figure 4.9 writ2e module (writing Alpha values into RAM2)                                | 64    |

| Figure 4.10 Wave forms status in Simvision                             | 64         |

|------------------------------------------------------------------------|------------|

| Figure 4.11 Waveform status in Simvision                               | 65         |

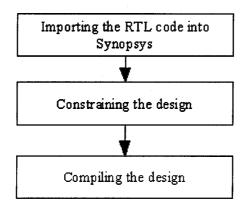

| Figure 4.12 Synthesis steps                                            | 65         |

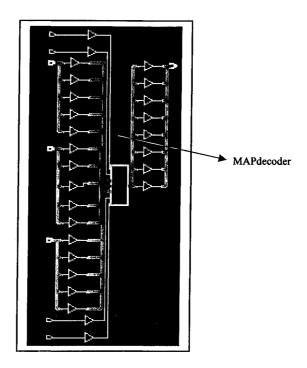

| Figure 4.13 shows the synthesis level of the main module or MAPdecoder |            |

| Figure 4.14 Inside the main module after synthesis level               | 66         |

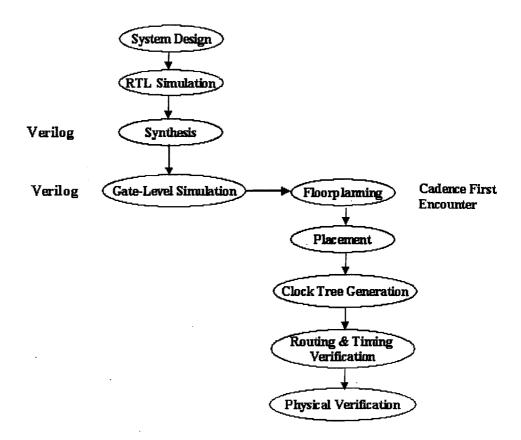

| Figure 5.2 Digital design flow                                         | 69         |

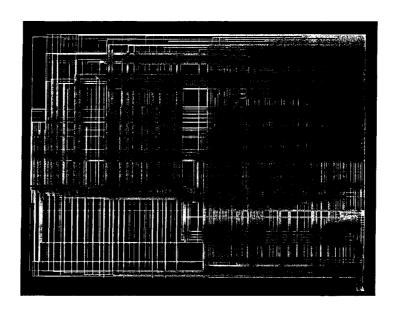

| Figure 5.3 Floorplanned design                                         | <b>7</b> 4 |

| Figure 5.4 Power planned design                                        | 74         |

| Figure 5.5 Placed design                                               | 75         |

| Figure 5.6 Chip after Clock Tree Generation                            |            |

| Figure 5.7 Routed design                                               | 77         |

# Chapter 1

## Introduction

The purpose of a communication system is to transport information from a source to one or more user destinations via a communication channel. There are two types of communication systems, analog communication systems and digital communication systems. In analogue systems the information varies continuously in both amplitude and time, and is used to modify some characteristic of a sinusoidal carrier wave (e.g. amplitude, phase, frequency), however in digital systems the information is processed so that it can be represented by a sequence of discrete messages.

## 1.1 Digital Communication Systems

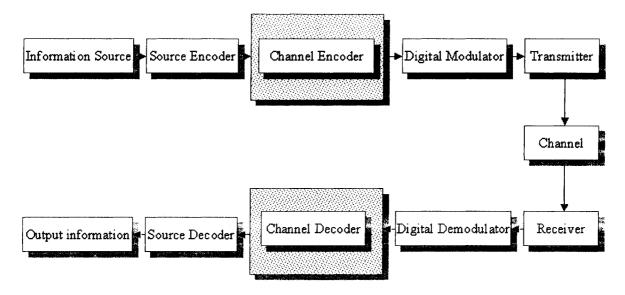

A digital communication system conveys information in digital form from a source to one or more destinations through a communication channel. Figure 1.1 gives the block diagram of a typical digital communication system.

Figure 1.1 A typical digital communication system

#### 1.1.2 Information Source

The input is source signal. It might be a sequence of symbols such as letters from the English or Chinese alphabet, binary symbols from a computer file, etc. Alternatively, the input might be a waveform, such as a voice signal from a microphone, the output of a sensor, a video waveform, or, it might be a sequence of images such as X-rays or photographs.

Whatever the source signal is, we will model it as a sample function of a random process. This is one of the reasons why probability is an essential prerequisite for communication theory. It is not obvious why inputs to communication systems should be modeled as random, and in fact this was not appreciated before Shannon developed information theory in 1948. The study of communication before that time (and well after that time) was based on Fourier analysis, which basically studies the effect of passing sine waves through various kinds of systems and components. This kind of analysis often called Nyquist theory in the context of digital communication.

However, Shannon's view was that if the recipient knows that a sine wave of a given frequency is to be communicated, why not simply regenerate it at the output rather than send it over a long distance? Or, if the recipient knows that a sine wave of unknown frequency is to be communicated, why not simply send the frequency rather than the entire waveform?

The essence of Shannon's viewpoint is that we should focus on the set of possible inputs from the source rather than any particular input. The objective then is to transform each possible input into a transmitted signal in such a way that each possible transmitted signal can be distinguished from the others at the output. A probability measure is needed on this set of possible inputs to distinguish typical inputs from abnormal inputs. It will be explained later how this point of view drives the processing of the inputs as they pass through a communication system.

#### 1.1.3 Source Encoder

The source encoder has the function of converting the input from its original form into a sequence of bits. The simplest source coding techniques involve representing the source signal by a sequence of symbols from some finite alphabet, and then coding the alphabet symbols into fixed-length blocks of bits. For example, letters from the 27-symbol English alphabet (including a space symbol) may be encoded into 5-bit blocks. Or, upper-case letters, lower-case letters, and a great many other special symbols may be converted into 8-bit blocks (bytes) using the 7-bit standard ASCII code.

The most straightforward approach to converting an analog waveform to a bit sequence, called analog to digital (A/D) conversion, is first sampling the source at a sufficiently high rate (called the "Nyquist rate"), and then quantizing it properly for adequate reproduction. For example, in standard voice telephony, the voice waveform is filtered to a bandwidth of less than 4 KHz and sampled 8000 times per second; each sample is then quantized into one of 256 levels and represented by an 8-bit byte. This yields a source coding bit rate of 64 kb/s.

Beyond the basic objective of conversion to bits, the source encoder often has the further objective of transmitting as few bits as possible, subject to the need to reconstruct the input adequately at the output. In this case source encoding is often called data compression. For example, modern speech coders can encode telephone-quality speech at bit rates of the order of 6-16 kb/s rather than 64 kb/s.

#### 1.1.4 Channel

Here, the channel in a generic digital communication system is discussed before considering channel coding.

In general, the channel is that part of the communication medium that is given and not under the control of the designer. Thus, to a source code designer, the channel might be a digital channel with bits as input and output; to a telephone-line modem designer, it might be a 4 KHz voice channel; to a cable modem designer, it also might be a physical coaxial cable of up to a certain length, with certain bandwidth restrictions.

For a channel code designer, the channel is often a physical channel; e.g., a pair of wires, a coaxial cable, or an optical fiber going from the source location to the destination. It also might be the open space between source and destination over which, electromagnetic radiation can carry signals, underwater acoustic channel or storage channel.

If a channel was simply a linear time-invariant system (e.g., a filter), then it could be completely characterized by its impulse response or frequency response. However, the channels that we look at here (and channels in practice) always have an extra ingredient noise. Suppose that there were no noise and a single input voltage level could be communicated exactly. Then, representing that voltage level by its infinite binary expansion, we would in principle be able to transmit an infinite number of binary digits by transmitting a single real number. This is absurd in practice, of course, precisely because noise limits the number of bits that can be reliably distinguished. Again, it was

Shannon in 1948 who, realized that noise provides the fundamental limitation to performance in communication systems.

### 1.1.5 Noise

The major characteristic of a communication channel in is how the channel distorts the information. We start by listing out some common channel defects:

- 1. Thermal noise in electronic devices

- 2. Signal attenuation

- 3. Amplitude and phase distortion

- 4. Multipath distortion

- 5. Finite-bandwidth (low-pass filter) distortion

- 6. Impulsive noise

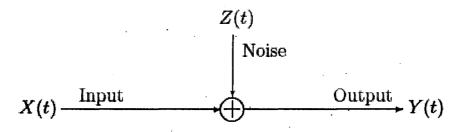

Based on a knowledge of these channel defects, we construct the generic channel model. The most common channel model involves a waveform input X(t), an added noise waveform Z(t), and a waveform output Y(t) that is the sum of the input and the noise, Y(t) = X(t) + Z(t), as shown in Figure 1.2.

Figure 1.2 A channel model

Each of these waveforms is viewed as a stochastic process. For any channel with input X(t) and output Y(t), we could define the noise to be Z(t) = Y(t) - X(t), which is essential to be statistically independent of the input. The noise Z(t) is often modeled as white

Gaussian noise (in this case it is called Additive White Gaussian Noise), which is the most common and most studied model among the various models.

## 1.1.6 Channel Coding

The objective of channel coding is to map the signal to a form where reliable communication can be achieved over a noisy channel. This may be achieved by introducing controlled redundancy into the signal. The channel decoder attempts to reconstruct the original encoder input as accurately as possible. The choice of channel coding depends considerably on the channel over which the data will be transmitted. Block codes, convolutional codes, and more recently block turbo codes are examples of channel encoding techniques.

#### 1.1.7 Modulation

Modulation is performed to provide for efficient transmission of the signal over the channel. It operates by keying shifts in the amplitude, frequency, or phase of a sinusoidal carrier wave to the channel encoder output. The detector performs demodulation, attempting to produce a signal that follows the time variations in the channel encoder output. Modulation is required for transmitting over a band-pass channel.

#### 1.1.8 Source Decoder

The source decoder performs the inverse mapping of the source encoder. Usually, it can be realized with low complexity.

## 1.1.9 Output Information

Output information is the sink of the transmitted information and should be similar to the original information of the source before they are sent trough the channel.

## 1.2 History of Coding

Unlike analog communication, digital communication has the ability to detect and correct errors produced by the noise of the channel. Forward error correction plays an important role in the system design process, which attempts to balance the tradeoffs of power, bandwidth, and data reliability.

Digital communication is a field in which theoretical ideas have had an unusually powerful impact on actual system design. The basis of the theory was developed in 1948 by Claude Shannon, and is called Information Theory. For the first 25 years or so of its existence, information theory served as a rich source of academic research problems and as a tantalizing suggestion that communication systems could be made more efficient and more reliable by using these approaches. By the mid 1970's, mainstream systems using information theoretic ideas began to be widely implemented for two reasons. First, by that time there were a sizable number of engineers who understood both information theory and communication system development. Second, implementation of the sophisticated algorithms was possible because of the low cost and increasing processing ability of digital hardware.

Shannon's major accomplishments include the development of the noiseless source coding theorem, the rate distortion theorem, and the channel coding theorem [gallager]. In 1948, Shannon published a groundbreaking paper and showed that reliable communication trough a noisy channel is possible. What Shannon showed was fact that more sophisticated coding schemes can achieve arbitrarily low error probabilities without lowering the data rate below a certain data rate that depends on the channel being used, called the channel capacity.

Channel capacity can be calculated from the following equation:

$$C = W \log_2 (1+S/N)$$

where W is the bandwidth in Hz, S is the signal power in watts and N is the total noise power.

Now, after explanation about the digital communication systems there is an overview of different number systems, which is part of any digital system computation.

## 1.3 Number Systems

In this design, we are working with fixed-point values that can be either positive or negative and one of the underlying considerations that must be made when carrying out digital arithmetic is the number representation. Therefore, in this section different number systems are discussed with their advantages and shortfalls.

### 1.3.1 Signed Fixed Point Numbers

The natural number system (also known as unsigned integer), although simple to put into practice, limits the potential of the overall design. To realize sophisticated arithmetic computation, the number system of choice must be capable of signed representation. There are several means by which signed representation may be achieved.

The earliest form of signed numbers representation is known as signed magnitude (or sign-and-magnitude), where a sign bit is included as part of the value. Similar to the manual representation of negative numbers, a number will have a numeric value, and a sign bit in front identifying negation. Thus a k-bit system will have a (k-1)-bit magnitude description. Although conceptually signed values will require supplementary circuitry (such as magnitude comparator, or subtractor) for proper addition.

An encoding scheme may also be used to eliminate negative values during computation. Biased representations, for example, will convert everything to positive numbers by adding a fixed bias value. Also referred to as excess-biased encoding, this type of representation is the difficulty in multiplication and division, and the additional computation that is required to unbiased values

Complement formats are the third major representation of signed numbers. A large complementation constant is added to all negative values, satisfying the condition that there is no overlap in the representation of the positive values. In binary systems, 2's complement representation obtained by taking the ones complement (bit-wise negation) and adding 1, is used to describe negative values. The ease of negation and computation using complement formats leads to their attractiveness as a signed digit representation.

## 1.3.2 Redundant Number Systems

A number system with radix-R maybe fully described using R distinct digits. For example the binary system (radix-2), can define any value using the 2-digit set [0, 1]. In general a positional radix-R number system representations a k-digit value as a string of digits:

$$(d_{k-1}, d_{k-2}, \dots d_0)$$

$$\sum_{i=0}^{k-1} d_i R^i$$

A system is referred to as redundant if more than *R* digits are used to define a radix-R representation. Redundant number systems are primarily used in digital systems for arithmetic speed-up techniques. By over defining a system using redundant values, the cost of computation of certain operations may be appreciably reduced. Addition is one such application, where use of redundant representation allows for constant time addition, since the value of the carry bit may be obtained by examining a fixed number of previous bits [pillai].

A simple case of redundant number systems that has already been represented is the carry save representation of a number. By describing a K-bit value using two k-bit numbers in the carry save format, [0, 1, 2], the necessary for carry propagation is alleviated. The description of a value using what are essentially twice as many bits may be clearly justified when considering the array multiplier. By maintaining the partial product

summation in carry save form, the latency of each stage is reduced to only one full adder delay, since carry propagation is postponed until the final stage.

Other redundant number systems have also proven to be favorable alternative to conventional systems. The signed digit number system, first classified in 1961, has demonstrated 33% savings in adders required for multiplication over standard binary notation [parhami].

The disadvantage of using redundant number representation is need for re-conversion back into conventional notation.

### 1.3.3 Residue Number Systems

In a residue number system representation (RNS), a umber x, is represented by the set of its residues with respect to modulo m:

$$x_i = \operatorname{xmod} m_i = \langle x \rangle_{mi}$$

Since a value is uniquely represented using smaller residues, the mathematical operations that are carried out will inevitably be fast and simple. Addition, multiplication and subtraction are the primary vantage points in residue number systems. This is due to the fact that these functions may be carried out by directly performing the given operation on the smaller residues. Frenking and Parhi [frenking] present an application of RNS arithmetic in public-key cryptography scheme, which inherent use of modular exponentiation and multiplication.

One disadvantage of such number systems is reduction of representation efficiency over binary notation. A k-bit representation, yielding 2<sup>k</sup> unique values, may only produce half as many in RNS format. Also, any gains in performance achieved by implementing addition, subtraction and multiplication may be eclipsed by the severe complexity of other mathematical and logical operations.

### 1.3.4 Logarithmic Number Systems

In pure mathematics, the multiplication and division of logarithms are easily performed by addition and subtraction respectively. Since the hardware implementation of addition/subtraction circuits is substantially more straightforward than that of multipliers and dividers, logarithmic number systems (LNS) may be employed to carry out these operations. As in other non-conventional representations, LNS in only directed towards the enhancement of certain operations, and presents restrictions on most other standard numeric tasks, such as addition and subtraction.

Recently the Double Base Number System (DBNS) has been proposed at yet another class of redundant number representation [dimitrov]. Simple arithmetic operations are made possible by simple geometric interpretation of the orthogonal bases. DBNS provides logarithmic like computation with reduced look-up table dimensions. This representation provides yet another alternative for application specific computation enhancement.

## 1.3.5 Floating Point Number Systems

In order to achieve the levels of precision demanded by modern systems, it becomes imperative to have a number representation capable of describing real numbers. The limited range and/or precision of fixed-point values alleviated through the use of the floating-point number system. Unlike fixed-point representations where the location of the decimal point is predefined, floating point values allow extremely large or small numbers to be represented with the same high degree of precision by defining a value using a dynamic range.

As defined in IEEE standard for binary floating-point arithmetic [IEEE], a floating-point value is defined as:

$$x = \pm f \times b^e$$

where x is the floating point value f is the fraction of mantissa, b is the base (fixed at 2 for precision) and e in the exponent.

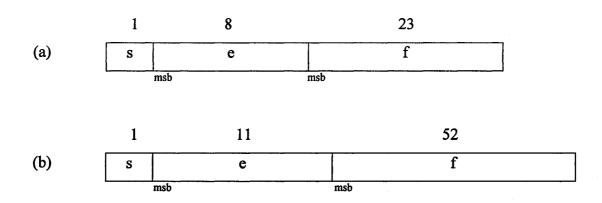

Floating-point numbers have two distinct representations according to the standard, depending on word size. Figure 1.3 outlines the difference in the structure of the words of the 32-bit single precision and the 64-bit double precision formats. The sign (s), exponent (e) and fraction or mantissa (f), form the 32 and 64 bit precision formats. The mantissa is normalized to lie within the set [1, 2), such that the MSB is a 1. In this manner the leading 1 is removed and understood; this is referred to as the "hidden one", saving one bit in representation. The signed integer exponent is biased accordingly, such that the value will always be a positive number; the exponent biased for 127 and for single and 1023 for double precision formats.

Figure 1.3 IEEE floating-point standard word widths for

(a) single precision (b) double precision

#### 1.4 Thesis Overview

## 1.4.1 Thesis Highlights

This thesis will present the design and implementation of a new Maximum a Posteriori (MAP) Decoder, which is a Soft-Input Soft-Output (SISO) decoder. The Max-Log-MAP algorithm is found to be the best compromise between performance and

complexity for implementation of this decoder. The architecture is parallel and pipeline and therefore, makes the design work at a high throughput rate. A new quantization is introduced that best fits the performance requirements. Also a new branch metric calculation unit is proposed, which is less complex and smaller in terms of area size.

The RTL code of the design is written in Verilog and the decoder is synthesized and implemented in CMOS  $0.18 \mu$  m technology.

The system specifications are as follows:

■ Encoder: Recursive Systematic Convolutional (RSC)

Channel: Additive White Gaussian Noise (AWGN)

Considered Modulation: Binary Phase Shift Keying (BPSK)

Block size: 10-1024

#### 1.4.2 Thesis Overview

This thesis has begun with a general overview of the digital communication systems in this chapter. Turbo coding and its algorithms are discussed in chapter 2. System level design including the decoder architecture and the MATLAB simulation results of quantization and normalization techniques are explained in chapter 3. Chapter 4 will focus on RTL simulation and synthesis level of the design, and VLSI implementation steps are presented in chapter 5. The thesis will end with the results, comparisons and conclusions in chapter 6.

# Chapter 2

# Turbo coding

Although Shannon proved the theoretical limit at which error-free communications could take place using error-correcting codes, all previous coding schemes have fallen far short of this limit. In 1993 a group of French researchers devised a new class of error-correcting codes, which achieved near-Shannon limit performance. Turbo codes were developed in 1993 by C. Berrou, A. Glavieux and P. Thitimajshima [berrou] at the "Ecole Nationale Superieure des Telecommunications de Bretagne" in Brest, France, as an exercise in VLSI design and claimed to achieve performance near Shannon limit in the AWGN channels. The modified BAHL et al. algorithm [bahl] was used for decoding. The original turbo code's performance came within 0.7 dB of Shannon's theoretical limit after 18 decoding iterations. This chapter presents the development of turbo codes and discusses the theoretical background necessary to understand their application.

### 2.1 Turbo Encoder

The focus of coding theory since Shannon's initial work has been to find a constructive way to place  $2^k$  codewords in an n-dimensional space without overlapping the decoding spheres. The code rate r is defined as the ratio of k, the number of information symbols transmitted per codeword, to n, the total number of symbols

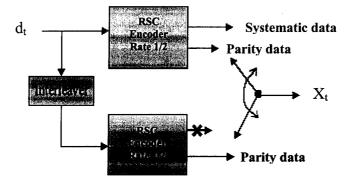

with 7 symbols and has a rate equal to 4/7. This code, the first error correcting code, was able to correct a single error in a block of seven encoded bits. Other attempts to solve the problem presented by coding theory have included block codes (such as Golay, BCH, and Reed-Solomon codes) and convolutional codes, but prior to the early 1990's, no practical techniques achieved the full promise of Shannon's predictions. Turbo coding is a unique approach to the old coding problem. Turbo codes are able to integrate structured codes in a pseudo-random manner, which approximates Shannon's capacity limit; this constitutes a significant increase in power efficiency compared to previous block and convolutional coding schemes. The original turbo code employed two recursive systematic convolutional (RSC) encoders concatenated in parallel and separated by a pseudo-random interleaver.

Figure 2.1 Turbo encoder

Each rate 1/2 RSC encoder produces a set of systematic and parity bits. The systematic bits are identical to the input bits; the parity bits are determined from the input bits, the state of the encoder, and the generator matrix. Because transmitting two sets of systematic bits is redundant, the interleaved systematic bits from the second RSC encoder are punctured, or removed, before transmission. The overall rate of the turbo code can be increased from 1/3 to 1/2 by alternately puncturing the parity bits from each of the constituent encoders. As the code rate increases, bandwidth efficiency improves; however, performance is degraded since the decoder has less information to use in making a decision.

The resulting code has a complex structure and appears quite random. This characteristic of the code results in good performance, particularly at low signal-to-noise ratios (SNRs). The overall code, however, is broken down into its constituent parts at decoder.

## 2.2 RSC Encoder

As previously mentioned, the original turbo code was a parallel-concatenated convolutional code. Concatenated codes can be classified as either parallel-concatenated convolutional codes (PCCCs), in which two encoders operate on the same information bits, or serial concatenated convolutional codes (SCCCs), in which one encoder encodes the output of another encoder. The term "turbo code" is often associated with PCCCs and will be used to refer to PCCCs throughout the rest of this thesis. PCCCs employ two or more recursive systematic convolutional (RSC) encoders joined in parallel by one or more pseudo-random interleavers. Although the encoders need not be identical, they often are, in practice. An example of a RSC encoder is shown in Figure 2.2.

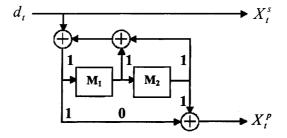

Figure 2.2 RSC Encoder

The data bits  $d_t$  are fed into the encoder, which generates a set of systematic and parity bits. There are two memories in this encoder, which are shift registers. The size of the memory defines how many symbols in the input sequence will affect the output sequence at a time. The rate of the convolutional code is the ratio between the number of inputs and the corresponding number of outputs at a time. For example if the rate is  $R_C = 1/2$ , then each bit of the binary input sequence  $(d_t)$  is mapped into two bits in binary output sequence  $(X_t^s)$  and  $X_t^p$  as shown in Figure 2.2. The modulation used is binary phase shift keying (BPSK), which map 1 to 1 and 0 to -1. The generator sequence defines how the

output will be obtained by the inputs in the memories and the most recent one. The generator is (7, 5) or (111, 101), which is shown in Figure 2.2. Each connection in the Figure 2.2 is shown by 1 and otherwise by 0.

Another parameter is the constraint length of the code, K, which is equal to the number of memories plus one. Figure 2.2 shows a RSC encoder with code rate ½, generators (7, 5) and constraint length 3. Table 1.1 shows how encoder outputs are obtained by the inputs in the memories.

Table 1.1 RSC encoder values

| $d_{t}$ | M1 | M2 | S | $X_t^s$ | $X_{\iota}^{p}$ |

|---------|----|----|---|---------|-----------------|

| 0       | 0  | 0  | 0 | 0       | 0               |

| 0       | 0  | 1  | 1 | 0       | 0               |

| 0       | 1  | 0  | 1 | 0       | 1               |

| 0       | 1  | 1  | 0 | 0       | 1               |

| 1       | 0  | 0  | 1 | 1       | 1               |

| 1       | 0  | 1  | 0 | 1       | 1               |

| 1       | 1  | 0  | 0 | 1       | 0               |

| 1       | 1  | 1  | 1 | 1       | 0               |

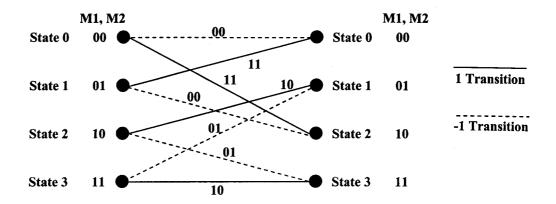

The convolutional code's properties are usually presented in graphical form by using one of the three equivalent diagrams: code trellis, state diagram and code tree.

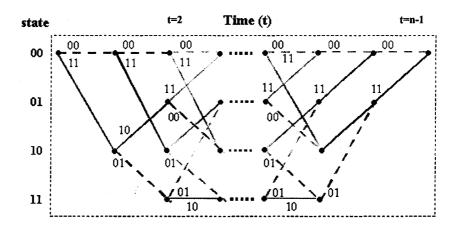

The state diagram of the RSC encoder with inputs and outputs shown in above table is presented in Figure 2.3.

Figure 2.3 State diagram of RSC encoder

Figure 2.3 is a finite state machine that changes its state when an input symbol enters to the machine and produces two output symbols during the transition (since the code rate is ½). Although we obtain the state relationships from the state diagram, we cannot obtain the time information from it. Usually the convolutional encoders are forced to the zero state at the end of the coding, a process called trellis termination, in order to make the decoding process easier. It is done by placing the M zero bits at the end of the information sequence. This causes rate loss. For long blocklengths, the rate loss is acceptable, but for short blocklengths, the termination causes severe degradation in the system performance because, those additional zero bits carry no information. The trellis diagram created by the encoder (7, 5) is shown in Figure 2.4.

Figure 2.4 Trellis diagram of the RSC decoder

It starts from state 0 and ends again to state 0. State numbers show the values inside the encoder memories.

The middle section of the code trellis created by encoder (7, 5) is shown in Figure 2.5. The dashed lines indicate zero-transition (-1 in BPSK modulation) and the solid lines indicate one-transition branches. The branch labels are also shown in this Figure.

Figure 2.5 A middle section of the trellis diagram

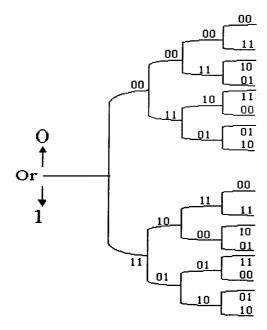

The code tree of the code (7, 5) is shown in Figure [tree]. The output sequence follows the upper branch when zero enters to the encoder and lower branch when one enters to the encoder as an input. The code tree for code (7, 5) starts repeating itself after the third branch because it is a memory 2 code and after the third branch, the first input bit has no affect on the output sequence. The number of possible branches in the code tree doubles itself at each time unit. For an L-bit input sequence, there are 2<sup>L</sup> distinct possible paths that the code can follow on the tree.

Figure 2.6 Code tree representation

### 2.3 Interleavers

An interleaver changes the order of the information sequence for the second and other encoders in pseudo-random fashion. Intereavers are widely used to improve code performance for channels, which introduce burst errors, but the place and function of an interleaver in the turbo codes are different from those of previously employed interleavers. The turbo interleaver reorders the uncoded information sequence for the second and other encoders so that the correlation between encoded sequences is arbitrarily low. In this way each generated code can be treated as independent. A good interleaver can significantly increase the performance of turbo coding by increasing the separation between sequences.

#### 2.3.1 Pseudo-Random Interleavers

One of the fundamental components of turbo codes is the pseudo-random interleaver. This design technique generates an overall code, which appears random but is actually composed of two or more structured codes. The random characteristics of the code result in good performance, yet the overall code is easily decoded at the receiver by breaking it down into its structured, constituent components. Choosing a good interleaver design is important for obtaining good turbo code performance, but the most significant parameter relating to the interleaver is its size. As the interleaver size increases, performance improves. There is a tradeoff, however, between performance and latency.

#### 2.3.2 Convolutional Interleavers

There are a number of interleavers to choose from when designing PCCCs. Block interleavers tend to give poor performance because they do not adequately break apart certain input sequences which result in low weight codewords. Convolutional interleaving also results in an interleaving pattern where low weight codewords are likely to degrade performance. Simulation results have shown that convolutional interleaving between constituent RSC encoders yields poor performance for these reasons [refthes14]. A

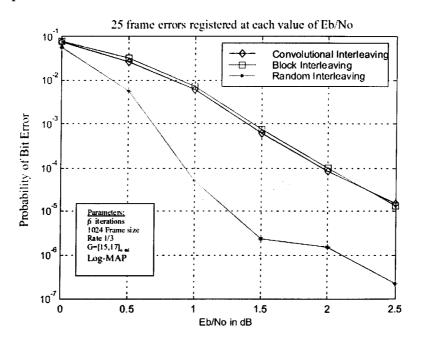

comparison of block, convolutional, and random interleaving is shown in Figure 2.7. A rate 1/3, constraint-length 4, turbo code with generator matrices  $G = (13, 15)_{octal}$  was used to encode 1024-bit data frames. The Log-MAP algorithm was used for decoding, and plots are shown for six decoding iterations. Twenty-five errors were logged at each value of Eb/No. In general, when structure is introduced to the interleaver design, turbo code performance suffers. With a few exceptions, random interleavers provide good performance. Slightly improved performance can be obtained with a spread interleaver. A spread interleaver is a pseudo-random interleaver designed according to an algorithm, which guarantees that a specified distance always separates consecutive input symbols in the output sequence.

Figure 2.7 Comparison of block, convolutional, and random interleaving

## 2.4 Turbo Decoder

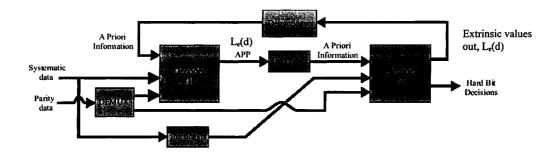

The whole decoder consists of two constituent decoders, deinterleavers and interleavers. Each decoder operates on the systematic and parity bits (channel outputs) associated with its constituent encoder and produces soft outputs of the original data bits in the form of extrinsic values. Soft output gives the probability of each received bit from the channel to be 0 or 1 (-1 or 1 in BPSK modulation). The decoders then share their

respective soft information in an iterative fashion. The goal of this project is implementation of these two decoders or soft input soft output (SISO) modules and if MAP algorithm runs through these decoders, they are called maximum a posteriori (MAP) decoders. The extrinsic output of each decoder is interleaved (or deinterleaved) and passed to the next decoding module as a priori information. Decoding continues in an iterative fashion for a fixed number of iterations or until a given convergence criteria is met. Because iterative decoding is subject to diminishing returns, the coding gains realized with each additional iteration are less than for the previous iteration. This principle is illustrated in Figure 2.8.

Although turbo codes integrate the two desirable qualities of pseudo-randomness and ease of decoding, the important contribution to communication theory lies in the iterative decoding method used to decode them. This iterative strategy has been employed in other communications areas such as iterative multiuser detection, turbo equalization, and turbo code assisted synchronization with good results.

Figure 2.8 Turbo decoder

Turbo decoder is a soft input soft output (SISO) decoder and for a systematic code, it can be shown [turbo] that the soft output of the decoder L(d) is equal to:

$$L(d) = L'(d) + L_a(d)$$

where L'(d) is a priori log likelihood ratio and  $L_e(d)$  is extrinsic log likelihood ratio.

$$L'(d) = \log \left[ \frac{p(x \mid d = +1)}{p(x \mid d = -1)} \right]$$

$$L_e(d) = \log \left[ \frac{p(d = +1)}{p(d = -1)} \right]$$

The soft output or log-likelihood ratio (LLR) provides the probability of the channel output bits and decides if the channel output bits have been originally 1 or -1. The soft decision L(d) is a real number that provides a hard decision as well as the reliability of that decision. The sign of L(d) denotes the hard decision; that is, for a positive value of L(d) decides that the channel output bit has been originally +1 and for negative values decides that the bit has been -1. The magnitude of L(d) denotes the reliability of that decision.

## 2.5 Turbo Coding Algorithms

Having outlined the iterative decoding process, the specific decoding algorithms used by the SISO modules will now be described. This section highlights two classes of trellis-based algorithms, which are typically used to decode turbo codes. Figure 2.9 lists the two classes of trellis-based algorithms.

Figure 2.9 Turbo decoding algorithms

In 1967 the VA was presented in [viterbil] as a practical procedure for maximum-likelihood decoding of convolutional codes. The VA is optimal for estimating the state sequence of a finite-state Markov process observed over a discrete memoryless channel (DMC)[forney]. The VA minimizes the frame error rate by finding the most likely path

through the trellis. The VA is unsuitable for turbo decoding because it is a soft-input, hard-output algorithm. A soft-output VA (SOVA), introduced by Hagenauer and Hoeher in [hagenauer1], is a SISO algorithm, which retains information related to the pruned, competing paths. This information determines the reliability of the bits, which differ from those in the surviving path.

In 1996 the Improved SOVA was developed in [papke] to combat an inherent bias with SOVA. The bias is removed by multiplying the SOVA output by a normalizing constant derived from the estimated mean and variance of the output. A small performance increase mitigates the slight increase in computational complexity.

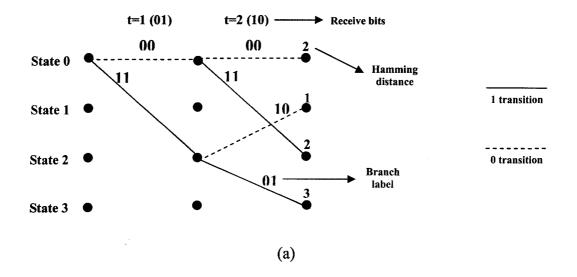

## 2.5.1 Viterbi Algorithm (VA)

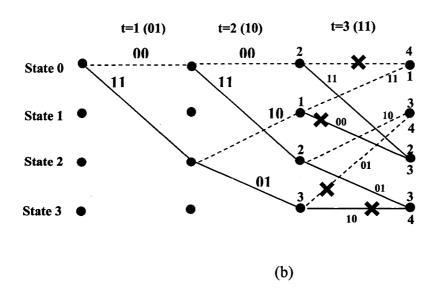

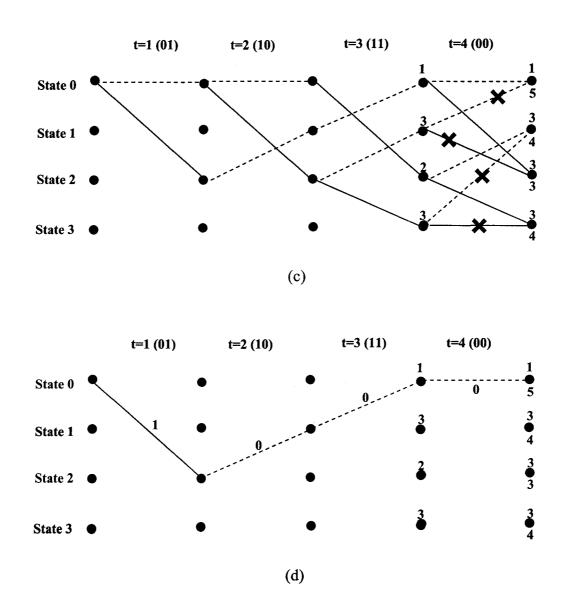

VA starts with a known initial state and the metric of the path originating starting from this state is zero. Then the received sequence at each time instant is compared stage by stage with branch labels of the code and the distances between these two are measured by a metric. These metrics are added to the paths' previous metrics. For the binary symmetric channel (BSC), the Hamming distance between the branch labels and received sequence is a good choice for the metric. When the paths merge at a particular state, the paths with the bigger metrics are dropped and the path with the smaller metric survives for next step. If the merging paths have the same metric, then the surviving path will be chosen randomly among them. The procedure is repeated until the end of the trellis is reached and the path whose metric is the smallest is hopefully the correct path and the bit sequence, which creates this path, is hopefully the error free decoded sequence. Figure 2.10 shows the trellis diagram for the VA algorithm with the generator (7, 5). Suppose that we receive the sequence (01, 10, 11, 00). The algorithm starts decoding from the zero state at time t=1. Figure 2.10(a) shows the paths after decoding for received bits (01) and (10) and each path metric is shown above the paths. The next received sequence is (11). Figure 2.10(b) shows the path's new metrics after decoding for that sequence. The X marked paths are dropped paths. Paths with larger Hamming distances drop and the path with the least distance remains. Figure 2.10(c) shows the

<sup>&</sup>lt;sup>1</sup> The Hamming distance is the number of bits which differ between two binary strings

paths after decoding the last received sequence (00). At that stage, the entire path's metrics of the state 2 are the same and we drop one of them randomly. Figure 2.10(d) shows the final survivor paths. According to Figure 2.10(d), the most likely decoded sequence will be (1000).

As we can see from Figure 2.10, we have always 4 survivor paths for t>=2. In general, we have always  $2^{k-1}$  survivor paths after t>=k-1 for a constraint length K convolutional code, because only one paths will survive among the paths entering to a state. Due to the exponential increase on the number of survivor paths,  $2^{k-1}$ , with respect to the constraint length, K, the utilization of the VA is practical for relatively short constraint length codes.

Figure 2.10 Viterbi algorithm with generator (7, 5) for BSC

## 2.5.2 MAP/BCJR Algorithm

Based on an algorithm developed by Chang and Hancock for removing intersymbol interference, the MAP algorithm was introduced in 1974 as an optimal means for estimating the a posteriori probabilities (APPs) for a finite-state Markov process observed over a DMC [bahl]. The MAP algorithm, also known as the BCJR algorithm for the four researchers who developed it, is a forward-backwards recursion algorithm, which minimizes the probability of bit error rate. Therefore, the path that the MAP algorithm traces through the trellis need not be connected, as is the case for the VA. In the 1970's the MAP algorithm fell out of favor for decoding convolutional codes because of its computational complexity in comparison to VA. When SISO decoding of turbo codes became an important issue, the Max-Log-MAP and Log-MAP algorithms were introduced to solve the instability problem; they are now the preferred SISO algorithms used to decode turbo codes. In the following thesis, these algorithms are explained and MAP algorithm is described first.

Transition probabilities and output probabilities in MAP algorithm are represented by the following equations [bahl],

$$p_{t}(m \mid m') = \Pr\{S_{t} = m \mid S_{t-1} = m'\}$$

$$q_{t}(X \mid m', m) = \Pr\{X_{t} = X \mid S_{t-1} = m'; S_{t} = m\}$$

where m and m' are transitions and X is the encoder output. The source starts in the initial state  $S_t = 0$ , and produces an output sequence  $X_I^t$  ending in the terminal state  $S_t = 0$ .  $X_I^t$  is the input to a noisy discrete memoryless channel (DMC), whose output is the sequence  $Y_I^t = Y_I$ ,  $Y_2$ , ...  $Y_t$ . The transition probabilities of the channel are defined by R(.|.) so that

$$\Pr\{Y_1^t \mid X_1^t\} = \prod_{j=1}^t R(Y_j \mid X_j)$$

The objective of the decoder is to examine Y<sub>1</sub><sup>t</sup> and estimate the a priori probability (APP) of the states and transitions of the source or encoder, i.e., the conditional probabilities

$$\Pr\{S_t = m \mid Y_1^{\tau}\} = \Pr\{S_t = m; Y_1^{\tau}\} / \Pr\{Y_1^{\tau}\}$$

(1)

and

$$\Pr\{S_{t-1} = m'; S_t = m \mid Y_1^{\tau}\} = \Pr\{S_{t-1} = m'; S_t = m; Y_1^{\tau}\} / \Pr\{Y_1^{\tau}\}$$

(2)

A graphical interpretation of the problem is shown in Figure 2.3. The nodes are the states and the branches represent the transitions having nonzero probabilities. If we index the states with both the time index t and state index m, we get the "trellis" diagram of Figure 2.4. The trellis diagram shows the time progression of the state sequences. For every state sequence  $S_I^t$  there is a unique path through the trellis diagram, and vice versa.

If the source is time variant, then we can no longer represent it by a state-transition diagram; however, it is obvious that we can construct a trellis for its state sequences.

Associated with each node in the trellis is the corresponding APP Pr  $\{S_t = m \mid Y_1^r\}$  and associated with each branch in the trellis is the corresponding APP Pr  $\{S_{t-1} = m'; S_t = m \mid Y_1^r\}$ . The objective of the decoder is to examine  $Y_I^t$  and compute these APPs.

For ease of exposition, it is simpler to derive the joint probabilities

$$\lambda_{\iota}(m) = \Pr\{S_{\iota} = m; Y_{\iota}^{\tau}\}$$

and

$$\sigma_t(m', m) = \Pr\{S_{t-1} = m'; S_t = m; Y_1^{\tau}\}\$$

Since, for a given  $Y_1^{\tau}$ ,  $\Pr\{Y_1^{\tau}\}$  is a constant, we can divide  $\lambda_{t}(m)$  and  $\sigma_{t}(m',m)$  by  $\Pr\{Y_1^{\tau}\}$  (= $\lambda_{t}(0)$ , which is available from the decoder) to obtain the conditional probabilities of (1) and (2). Alternatively, we can normalize  $\lambda_{t}(m)$  and  $\sigma_{t}(m',m)$  to add up to 1 to obtain the same result. We now derive a method for obtaining the probabilities  $\lambda_{t}(m)$  and  $\sigma_{t}(m',m)$ . Let us define the probability functions:

$$\alpha_{t}(m) = \Pr\{S_{t} = m; Y_{1}^{t}\}$$

$$\beta_{t}(m) = \Pr\{Y_{t+1}^{\tau} \mid S_{t} = m\}$$

$$\gamma_{t}(m', m) = \Pr\{S_{t} = m; Y_{t} \mid S_{t-1} = m'\}$$

Now

$$\lambda_{t}(m) = \Pr\{S_{t} = m; Y_{1}^{t}\}. \Pr\{Y_{t+1}^{\tau} \mid S_{t} = m; Y_{1}^{t}\}$$

$$= \alpha_{t}(m). \Pr\{Y_{t+1}^{\tau} \mid S_{t} = m\}$$

$$= \alpha_{t}(m). \beta_{t}(m)$$

(3)

The middle equality follows from the Markov property that if  $S_t$  is known, events after time t in not depend on  $Y_I^t$ .

Similarly,

$$\sigma_{t}(m', m) = \Pr\{S_{t-1} = m'; Y_{1}^{t-1}\}. \Pr\{S_{t} = m; Y_{t} \mid S_{t-1} = m'\}. \Pr\{Y_{t+1}^{\tau} \mid S_{t} = m\}$$

$$= \alpha_{t-1}(m'). \gamma_{t}(m', m). \beta_{t}(m)$$

(4)

Now for  $t = 1, 2, ..., \tau$

$$\alpha_{t}(m) = \sum_{m'=0}^{M-1} \Pr\{S_{t-1} = m'; S_{t} = m; Y_{t}^{t}\}\$$

$$= \sum_{m'} \Pr\{S_{t-1} = m'; Y_{t}^{t-1}\}. \Pr\{S_{t} = m; Y_{t} \mid S_{t-1} = m'\}\$$

$$= \sum_{m'} \alpha_{t-1}(m'). \gamma_{t}(m', m)$$

(5)

Again, the middle equality follows from the fact that events after time t-1 are not influenced by  $Y_1^{t-1}$  if  $S_{t-1}$  is known.

For t = 0 we have the boundary conditions

$$\alpha_0(0) = 1$$

, and  $\alpha_0(m) = 0$ , for  $m \neq 0$ . (6)

Similarly, for  $t = 1, 2, ..., \tau - 1$

$$\beta_{t}(m) = \sum_{m'=0}^{M-1} \Pr\{S_{t+1} = m'; Y_{t+1}^{\tau} \mid S_{t} = m\}$$

$$= \sum_{m'} \Pr\{S_{t+1} = m'; Y_{t+1} \mid S_{t} = m\} . \Pr\{Y_{t+2}^{\tau} \mid S_{t+1} = m'\}$$

$$= \sum_{m'} \beta_{t+1}(m') . \gamma_{t+1}(m, m')$$

(7)

The appropriate boundary conditions are

$$\beta_{\tau}(0) = 1$$

, and  $\beta_{\tau}(m) = 0$ , for  $m \neq 0$ . (8)

Relations (5) and (7) show that  $\alpha_{\iota}(m)$  and  $\beta_{\tau}(m)$  are recursively obtainable. Now

$$\gamma_{t}(m', m) = \sum_{X} \Pr\{S_{t} = m \mid S_{t-1} = m'\}. \Pr\{X_{t} = X \mid S_{t-1} = m', S_{t} = m\}. \Pr\{Y_{t} \mid X\}$$

$$= \sum_{X} p_{t}(m \mid m').q_{t}(X \mid m', m).R(Y_{t} \mid X)$$

(9)

where the summation in (9) is over all possible output symbols X.

In the equation (9),  $p_t(m|m')$  is the transition probability and the output X, is a deterministic function of the transition so that, for each transition, there is a 0 - 1 probability distribution  $q_t(X|m',m)$ . For time invariant codes  $q_t(.|.)$  is independent of t. If the output sequence is sent over a DMC with symbol transition probabilities  $r_t(.|.)$ , the derived block transition probabilities are

$$R(Y_t | X_t) = \prod_{j=1}^{n_0} r(y^{(j)} | x_t^{(j)})$$

where  $Y_t = (y_t^{(1)}, ..., y_t^{(n_0)})$  is the block received by the receiver at time t. For instance, in a BSC with crossover probability  $p_c$ :

$$R(Y_t | X_t) = (p_c)^d (1 - p_c)^{n-d}$$

where d is the Hamming distance between  $X_t$ , and  $Y_t$ .

### 2.5.3 Results of the MAP Algorithm

The ultimate result of the MAP algorithm is the logarithm of the ratio of the a posteriori probability (APP) of each information bit being 1 to the APP of it being 0.

$$\Lambda(X_{t+1}) = \log \frac{\sum_{(m',m),X=1} \gamma_{t+1}(m',m).\beta_{t+1}(m).\alpha_t(m')}{\sum_{(m',m),X=-1} \gamma_{t+1}(m',m).\beta_{t+1}(m).\alpha_t(m')}$$

(10)

In this design binary phase shift-keying (BPSK) modulation is considered so that, bits with the value of 0 and 1 are mapped to -1 and 1 respectively. Forward node metric at time t is calculated from the computed forward node metric at time t-1 and the branch metric at time t:

$$\alpha_t(m) = \sum_{m'} \alpha_{t-1}(m').\gamma_t(m',m)$$

Backward node metric at time t is calculated from the computed forward node metric and the branch metric at the current time t+1:

$$\beta_t(m') = \sum_m \beta_{t+1}(m) \cdot \gamma_{t+1}(m', m)$$

Transition metric or Gamma is the symbol transition probability and for a 1/2 code rate encoder can be computed as:

$$\gamma_{t}(m',m) = \sum_{x} p_{t}(m \mid m') \cdot q_{t}(X_{t} \mid m',m) \cdot R(Y_{t_{d}} \mid X_{t}) \cdot R(Y_{t_{p}} \mid X_{t})$$

(11)

where,  $X_t$  is the channel input symbol at time t and  $Y_d$  and  $Y_p$  are channel outputs for Systematic data and Parity data respectively  $q_t$  and R are probability functions that mentioned before.

### 2.5.4 Max-Log-MAP Algorithm[robertson2]

The complexity of the MAP algorithm is high in terms of number of operations, especially number of multiplications. Max-Log-MAP algorithm is the logarithmic approximation of MAP algorithm therefore; we work with the logarithms of the values mentioned in MAP algorithm using the following approximation:

$$\ln(e^{\gamma_1} + \dots + e^{\gamma_n}) \approx \max_{i \in \{1\dots n\}} \gamma_i \tag{12}$$

In AWGN, the maximum likelihood probability function,  $R(Y_t \mid X_t)$ , is equal to:

$$R(Y_t \mid X_t) = \frac{1}{\sqrt{\pi N_0}} e^{-\frac{1}{N_0}(Y_t - X_t)^2}$$

(13)

By taking the logarithm of equation (11) and substituting for R from the equation (13) we obtain the following equation for branch metric:

$$\ln \gamma_{t}(m', m) = \frac{2Y_{t_{d}}X_{t}}{N_{0}} + \frac{2Y_{t_{p}}X_{t}}{N_{0}} + \ln AP_{t} + K$$

(14)

where  $N_0/2$  is the variance of the noise in Additive White Gaussian Noise (AWGN) channel and K is a constant which can be ignored since it cancels out during the recursive calculations. Equation (14) is a less complex algorithm in comparison to (11); however there are still some multiplications and divisions in (14) that can be removed and changed to an equation with only additions and comparisons without using any approximation. This fact is explained in section 3.2.

Forward and backward node metrics in MAP algorithm can be shown by the following equations:

$$\alpha_{t}(m) = \frac{\sum_{m'} \alpha_{t-1}(m').\gamma_{t}(m',m)}{\sum_{m} \sum_{m'} \alpha_{t-1}(m').\gamma_{t}(m',m)}$$

(15)

$$\beta_{t}(m') = \frac{\sum_{m} \beta_{t+1}(m).\gamma_{t+1}(m',m)}{\sum_{m'} \sum_{m} \beta_{t+1}(m).\gamma_{t+1}(m',m)}$$

(16)

By taking the logarithm of  $\alpha$  and  $\beta$  in equations (15) and (16) and using approximation (12), we get:

$$\ln \alpha_{t}(m) = \ln(\sum_{m'} e^{\ln(\alpha_{t-1}(m').\gamma_{t}(m',m))}) - \ln(\sum_{m} \sum_{m'} e^{\ln(\alpha_{t-1}(m').\gamma_{t}(m',m))})$$

and

$$\ln \beta_{t}(m') = \ln \left(\sum_{m} e^{\ln(\beta_{t+1}(m).\gamma_{t+1}(m',m))}\right) - \ln \left(\sum_{m'} \sum_{m} e^{\ln(\beta_{t+1}(m).\gamma_{t+1}(m',m))}\right)$$

to get:

$$\ln \alpha_{t}(m) = \max_{m'} [\ln \alpha_{t-1}(m') + \ln \gamma_{t}(m', m)] - \max_{(m', m)} [\ln \alpha_{t-1}(m') + \ln \gamma_{t}(m', m)]$$

$$\ln \beta_{t}(m') = \max_{m} [\ln \beta_{t+1}(m') + \ln \gamma_{t+1}(m', m)] - \max_{(m,m')} [\ln \beta_{t+1}(m') + \ln \gamma_{t+1}(m', m)]$$

The second terms are a result of the derivation from (15) and (16) and because these normalization terms will cancel out in (17), omitting them has no effects on the output of the Max-Log-MAP algorithm and the final equation will be:

$$\ln \alpha_t(m) = \max_{m'} [\ln \alpha_{t-1}(m') + \ln \gamma_t(m', m)]$$

$$\ln \beta_{t}(m') = \max_{m} [\ln \beta_{t+1}(m') + \ln \gamma_{t+1}(m', m)]$$

There are no multiplications exist in the above equation and it is only includes additions and comparisons. Therefore, this is obvious that the above equations are less complex and need smaller area size for implementation.

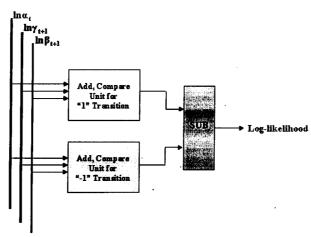

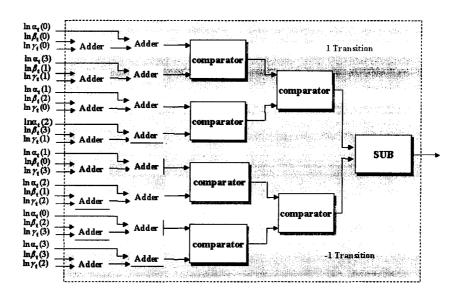

The Log-likelihood reliability is also computed from branch and node metrics as follow:

$$\ln \Lambda_{t+1} \approx \max_{(m,m'),X=1} [\ln \gamma_{t+1}(m',m) + \ln \beta_{t+1}(m) + \ln \alpha_{t}(m',m)] - \max_{(m,m'),X=-1} [\ln \gamma_{t+1}(m',m) + \ln \beta_{t+1}(m) + \ln \alpha_{t}(m',m)]$$

Again by looking at the above equation and compare it to the same equation in MAP algorithm (equation (10)), we can conclude that LLR obtained in Max-Log-MAP algorithm is less complex.

The Max-Log-MAP algorithm has a performance loss of about 0.5dB that can be improved ~0.4dB more by using a scaling factor within the extrinsic information in turbo decoders [vogt1]. This concept will be explained later.

### 2.5.5 Log-MAP Algorithm [robertson2]

Applying a correction term to the Max-Log-MAP algorithm forms the Log-MAP algorithm:

$$\ln(e^{\delta_1} + e^{\delta_2}) = \max(\delta_1, \delta_2) + \ln(1 + e^{-|\delta_1 - \delta_2|})$$

$$= \max(\delta_1, \delta_2) + f_c(|\delta_1 - \delta_2|)$$

where  $f_c(.)$  is a correction function and by considering  $\delta = \ln(e^{\delta_1} + ... + e^{\delta_{n-1}})$  we can show that:

$$\ln(e^{\delta_1} + \dots + e^{\delta_n})$$

$$= \ln(\Delta + e^{\delta_n}) \text{ with } \Delta = e^{\delta_1} + \dots + e^{\delta_{n-1}} = e^{\delta}$$

$$= \max(\ln \Delta, \delta_n) + f_c(|\ln \Delta - \delta_n|)$$

$$= \max(\delta, \delta_n) + f_c(|\delta - \delta_n|)$$

as a result, by correcting the approximation made in Max-Log-MAP at each step, the performance of Log-MAP algorithm will be almost the same as MAP algorithm.

Term " $f_c(|\delta-\delta_n|)$ " compensates the approximation error in equation (12). But correction is done using look-up tables in practical implementations and multiple look up tables are required for a wide range of operating signal-to-noise ratios (SNRs), thus it increases the hardware cost [cheng].

### 2.5.6 Sliding MAP

Sliding window MAP [chass] performs the calculations on the sub block instead of recursive calculation on the whole received block.

The size of the sub block is in the order of the survivor length of the Viterbi algorithm, SMAP reduces the demand on memory. A disadvantage is increase in the complexity, since for each sub block a reliable start vector for the backward recursion has to be provided. That means, instead of one forward and one backward recursion now one forward and two backward recursions are necessary.

## 2.6 Improving the Max-log-MAP Turbo Decoder

Remember from section 2.4 that:

$$L(d) = L'(d) + L_e(d)$$

where L(d) is a posteriori probability, L'(d) is soft output of the decoder and  $L_e(d)$  is extrinsic probability. By applying an additional scaling factor, R, to the extrinsic information the result will be:

$$L(d) = L'(d) + R.L_{\rho}(d)$$

The scaling factor R allows us to change the amount of information exchanged between two constituent decoders. Larger R makes the previous decoder outcome dominate the current decoding result, whereas the smaller R makes one decoder less dependent on the other decoder's result. In [Wu1], the scaling factor R=0.6, and in [vogt1], the scaling factor R=0.7 have given the best BER performance for AWGN. A properly selected scaling factor could improve the Max-Log-MAP by ~0.4 dB, yielding a near optimal (Log-MAP) BER performance.

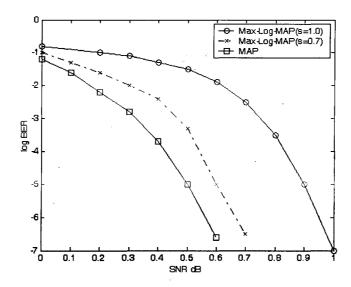

Figure 2.11 Turbo code with different scaling factors, block length 5114 bit, 8iterations, AWGN, rate 1/3 and generators (13, 15)<sub>oct</sub>

The BER improvement is due to the fact that the scaling factor R can effectively mitigate error propagation through iterations. Normally in Max-Log-MAP, when a cluster of extrinsic values of the first decoder are in error, they would dominate the branch metrics in the second decoder, and in turn causes more decoding errors in the second decoder. Because the decoding is iterative, more errors would be produced in the end. However, with the scaling factor the effect of erroneous a-priori values on branch metrics is reduced, allowing the decoder to upset the previous incorrect decoding results.

Figure 2.11 shows the performance of the best-evaluated scaling factor compare to the standard algorithm (s=1.0) for block length 5114 and AWGN channel. For a bit error rate of 10<sup>6</sup> the improvement of the Max-Log-MAP is ~0.3dB and the difference between Max-Log-MAP and MAP is now only 0.1dB.

### 2.7 Algorithm Comparison

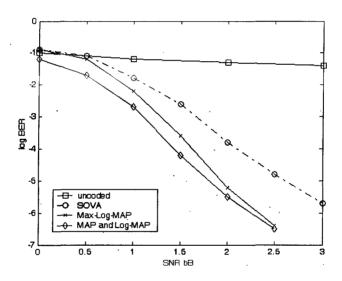

Figure 2.12 shows the comparison between different algorithm's performances [vogt2]. SOVA has the maximum performance loss and Log-MAP and MAP, which are optimum algorithms, have the best performance. The Max-Log-MAP algorithm has a performance loss of about 0.4dB and as it mentioned in previous section, it can be improved up to ~0.3dB more by using a scaling factor within the extrinsic information in turbo decoders.

Figure 2.12 Comparison between performances of turbo coding algorithms, block length 668bit, 4 iterations, AWGN, rate 1/3 and generators (7, 5)

Comparison between computational complexity shows that the MAP algorithm is the most complex algorithm and not suitable for implementation. This fact is observable from the MAP algorithm equations. Moreover, for implementation of the additional of the Log-MAP algorithm, multiple look up tables are required for varies signal to noise ratios and, which makes the design larger and increases the cost. Therefore, Max-Log-MAP

algorithm is chosen for the purpose of implementation of MAP decoder, which is the best compromise between performance and complexity.

## 2.8 System Specification Summary

The proposed decoder specifications are as follows:

• Encoder: Recursive Systematic Convolutional (RSC)

• Channel: Additive White Gaussian Noise (AWGN)

• Modulation: Binary Phase Shift Keying (BPSK)

• Number Of Memories: 2

• Code Rate: 1/2

• Frame size: variable up to 1024 bits

# Chapter 3

# System Design and Modeling

A major difficulty of applying turbo codes in many applications is the decoding complexity of SISO decoders. Efficient implementations of those decoders can significantly increase employment of turbo codes in different communication applications.

After introducing turbo coding and its related algorithms and choosing Max-Log-MAP algorithm for implementation, we discuss the system design and the proposed architecture for the implementation of MAP decoder. In this chapter an efficient design of a MAP Decoder suitable for ASIC, with lower complexity and smaller area size is introduced. The performance loss of the proposed design is less than 0.1dB in comparison with the best performance observed in Max-Log-MAP algorithm.

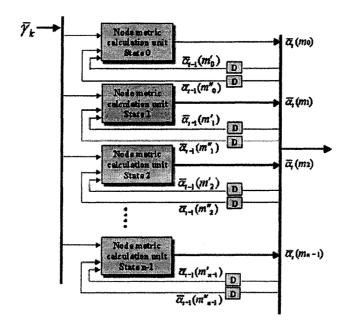

At the beginning, quantization and normalization techniques are studied and those that best fit the proposed MAP decoder are described. Furthermore, a new design with lower complexity is introduced for transition probability ( $\gamma$ ) calculation unit. The architecture used for this design is parallel and pipeline, which explained in this chapter.

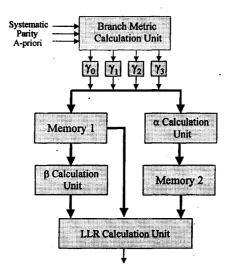

## 3.1 Max-Log-MAP Decoder Block Diagram

It was mentioned in chapter 2 that four parameters are calculated in Max-Log-MAP algorithm.

- 1.  $\gamma$ : branch metrics or probability of transitions

- 2.  $\alpha$  and  $\beta$ : Node metrics or probability of states

- 3. A: Log likelihood ratio (LLR)

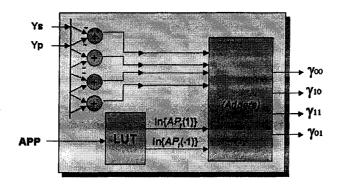

Figure 3.1 shows the block diagram of the proposed Max-Log-MAP decoder and its units. Inputs to the decoder are the a priori probability, systematic data and parity data. The a priori probability comes from the output of another Max-Log-MAP decoder inside the turbo decoder. Remember that turbo decoder includes two constituent decoders and Figure 3.1 shows one of them. Systematic and parity data inputs on the other hand are channel outputs and distorted by the noise of the channel. In a pipeline process bits received in input go to branch metric calculation unit and afterward to  $\alpha$  calculation unit.  $\gamma$  and  $\alpha$  values are then computed and saved into memories. Therefore, in forward recursion,  $\gamma$  and  $\alpha$  calculation units work in parallel, until one complete frame or block of bits is received. By reaching to the end of each frame,  $\gamma$  and  $\alpha$  units stop their execution, backward recursion starts and  $\beta$  and soft output (LLR) calculation units compute their values in parallel. The output is a probability that help us decide for each received bit from the channel to be originally 1 or -1.

Figure 3.1 Block diagram of the proposed Max-Log-MAP decoder

This design is very fast because of its parallel and pipeline nature and suitable for implementation. The only drawback of parallel and pipeline architecture is the need for using large memories, which in tern makes the design larger. In the proposed architecture, by computation of the LLR in backward recursion and in parallel with  $\beta$  calculation unit, one large memory is omitted and it saves about 30% of the area size and reduces the implementation cost of the chip.

Memories used are 4k, 8bits and there are for different  $\gamma$  or  $\alpha$  values for each received bit. Therefore, a 4k memory can store  $\gamma$  or  $\alpha$  values for a frame of up to 1024 bits. The number of bits per frame can be increases by using larger memories in other applications; however for a general application such as the current work, 1024 bits per frame is an adequate number.

### 3.2 New Branch Metric Calculation Unit

Recall from section 2.5.4 that there were still some multiplications and additions in equation (14). The decoder design can be further simplified by considering the insensitivity of Max-Log-MAP algorithm to the AWGN channel variance of the noise (N0/2). In [worm] it was shown that performance of turbo decoding with the Max-Log-MAP decoder, as its constituent decoder was SNR independent; however, turbo-decoding with the Log-MAP decoder theoretically requires SNR estimates. Elimination of the SNR significantly reduces the complexity of the decoder and yields an ASIC with a smaller area and lower cost.

If in Equation (14) we consider  $N_0=2$ ,

$$\ln \gamma_{i}(m',m) = \frac{2Y_{i_{d}}X_{i}}{N_{0}} + \frac{2Y_{i_{p}}X_{i}}{N_{0}} + \ln AP_{i} + K$$

there will be no multiplication (or division) in the calculation of  $\gamma$  values. Since  $X_{t_p}$  is equal to either 1 or -1, the four final values for  $\ln \gamma$  are:

$$\ln \gamma_{t,00}(m',m) = (-Y_{t_d} - Y_{t_p}) + \ln AP_t(-1)$$

$$\ln \gamma_{t,01}(m',m) = (-Y_{t_d} + Y_{t_p}) + \ln AP_t(-1)$$

$$\ln \gamma_{t,10}(m',m) = (+Y_{t_d} - Y_{t_p}) + \ln AP_t(+1)$$

$$\ln \gamma_{t,11}(m',m) = (+Y_{t_d} + Y_{t_p}) + \ln AP_t(+1)$$

(3.1)

For implementation of these four equations, only adders and a small look up table are required. The input to the look up table is the a priori probability<sup>2</sup>, and the outputs are  $\ln AP_t(+1)$  and  $\ln AP_t(-1)$ . The following equations clear the relationship between input and outputs of the LUT:

$$APP = \ln(\frac{AP_t(+1)}{AP_t(-1)})$$

and because

$$AP_t(+1) + AP_t(-1) = 1$$

we can write

$$APP = \ln(\frac{AP_t(+1)}{1 - AP_t(+1)})$$

$$e^{APP} = \frac{AP_t(+1)}{1 - AP_t(+1)}$$

and

$$AP_{t}(+1) = \frac{e^{APP}}{1 + AP_{t}(+1)}$$

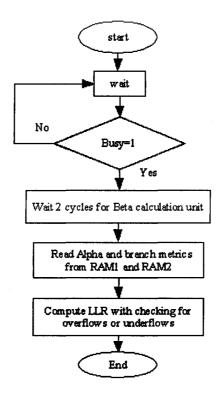

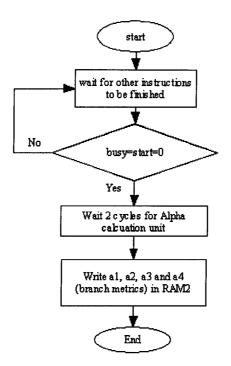

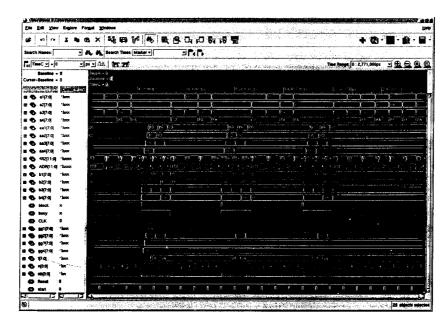

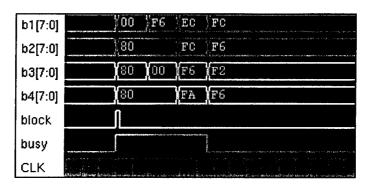

$$AP_t(-1) = 1 - \frac{e^{APP}}{1 + AP_t(+1)}$$