#### University of Windsor

## Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2004

# A SigmaDelta modulator for digital hearing instruments using 0.18 mum CMOS technology.

Iman Yassin. Taha University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Taha, Iman Yassin., "A SigmaDelta modulator for digital hearing instruments using 0.18 mum CMOS technology." (2004). *Electronic Theses and Dissertations*. 747. https://scholar.uwindsor.ca/etd/747

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

## A ΣΔ Modulator for Digital Hearing Instruments Using 0.18 μm CMOS Technology

by

Iman Yassin Taha

# A Thesis Submitted to the Facility of Graduate Studies and Research through Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada

2004

© 2004 Iman Taha

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-96390-X Our file Notre référence ISBN: 0-612-96390-X

The author has granted a nonexclusive license allowing the Library and Archives Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## Canadä

## **Abstract**

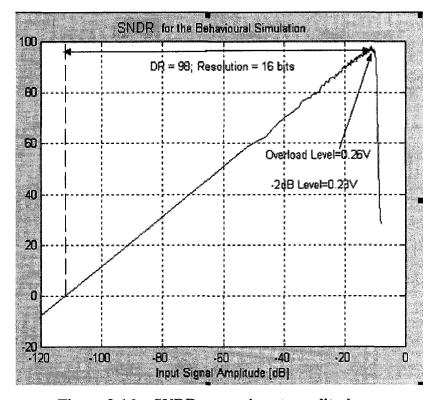

This thesis develops the design methodology for a low-voltage low-power  $\Sigma\Delta$  Modulator, realized using a switched op-amp technique that can be used in a hearing instrument. Switched op-amp implementation allows scaling down the design to the latest CMOS technology. A single-loop second-order  $\Sigma\Delta$  Modulator topology is chosen. The modulator circuit features reduced complexity, area reduction and low conversion energy. The modulator has a sampling rate of 8.2 MHz with an over-sampling ratio (OSR) of 256 to provide an audio bandwidth of 16 kHz. The modulator is implemented in a 0.18  $\mu$ m digital CMOS technology with metal-to-metal sandwich structure capacitors. The modulator operates with a supply voltage of 1.8 V. The active area is 0.403 mm². The modulator achieves a 98 dB signal-to-noise-and-distortion ratio (SNDR) and a 100 dB dynamic range (DR) at a Nyquist conversion rate of 32 kHz and consumes 1321  $\mu$ W with a joule/conversion figure of merit equal to  $161x10^{-12}$  J/s.

The design methodology is developed through the extensive use of simulation tools. The behaviour simulation is carried out using Matlab/ SIMULINK while circuits are simulated with Hspice using the Cadence design tools. Full-custom layout for the analog and the digital circuits is performed using the Cadence design tool. Post-processing simulation of the extracted modulator with parasitic verifies that results meet the requirements. The design has been sent to CMC for fabrication.

## **Acknowledgments**

First and foremost, I would like to express my sincere gratitude first to my supervisor, Professor William Miller, for giving me the opportunity to research in the field of mixed-signal design and for his patience, guidance, constant encouragement, technical and financial support throughout the course of the research.

I would like to express my deepest gratitude to Dr. Majid Ahmadi for his continuous encouragement and support in facing all the obstacles that affect my career.

I would like to express my best regards to Dr. Edwin Tam, of the Civil and Environmental Engineering Department, for his valuable comments.

I would like to thank Till Kuendiger for his assistant in helping me to solve the problems in using the Cadence design tool.

Finally, I would like to thank all the graduate students in the VLSI lab for the technical discussion and interaction.

## **Contents**

| A            | bstract          | • • • • • • • • • • • • • • • • • • • • | iii               |

|--------------|------------------|-----------------------------------------|-------------------|

| A            | cknowledge       | ent                                     | iv                |

| Li           | ist of Tables    |                                         | ix                |

| Li           | ist of Figure    |                                         | x                 |

| $\mathbf{A}$ | bbreviation      |                                         | xiii              |

| 1.           | Introduction     |                                         |                   |

|              |                  |                                         |                   |

|              |                  |                                         |                   |

|              | J                |                                         | 3                 |

| 2.           | _                | Basic Concepts                          |                   |

|              | 2.1. Oversamp    | ADC                                     | 4                 |

|              | 2.2. First Order | Modulator                               | 7                 |

|              | 2.2.             | Time Domain Behavior                    | 7                 |

|              | 2.2.             | Z-Domain Behavior                       | 8                 |

|              | 2.3. Second Or   | ΣΔ Modulator                            | 9                 |

|              | 2.4. Performan   | Criteria                                | 11                |

|              | 2.4.             | Signal-to-Noise Ratio (SNR)             | 11                |

|              | 2.4.             | Signal-to-Noise-and-Distortic           | on Ratio (SNDR)12 |

|              | 2.4.             | Dynamic Range (DR)                      | 12                |

|              | 2.4.             | Effective Resolution (B)                | 12                |

|              | 2.4.             | Power Dissipation                       |                   |

|              | 2.5. Top-Down    | sign Methodology Motivation             | n14               |

|              | 2.6. Switched    | Amp ΣΔ Modulator Design M               | fethodology14     |

| 3.           | System Leve      | ehavior                                 |                   |

|              | 3.1 Cor          | rison between Modulator Arc             | hitectures 17     |

|    | 3.2      | Single Loop $\Sigma\Delta$ Modulators using Half Delay Integrators | 19 |

|----|----------|--------------------------------------------------------------------|----|

|    | 3.3      | Cascade $\Sigma\Delta$ Modulators Using Half Delay Integrators     | 22 |

|    | 3.4      | Multibit Topology                                                  | 24 |

|    | 3.5      | Topology Selection.                                                | 25 |

|    | 3.6      | $\Sigma\Delta$ Modulators Non-idealities                           | 27 |

|    | 3.7      | Clock Jitter Model                                                 | 27 |

|    | 3.8      | Integrator Noise Model                                             | 28 |

|    |          | 3.8.1 Switch Thermal Noise (KT/C) Model                            | 30 |

|    |          | 3.8.2 Op-Amp Noise Model                                           | 31 |

|    | 3.9      | Integrator Non-idealities Model                                    | 32 |

|    |          | 3.9.1 DC Gain                                                      | 32 |

|    |          | 3.9.2 Bandwidth and Slew Rate                                      | 33 |

|    |          | 3.9.3 Saturation.                                                  | 35 |

|    | 3.10     | Capacitor Mismatching.                                             | 35 |

|    | 3.11     | Comparator                                                         | 35 |

|    | 3.12     | Behavioral Simulation for the Ideal $\Sigma\Delta$ Modulator       | 35 |

|    | 3.13     | Behavioral Simulation for the Non-Ideal $\Sigma\Delta$ Modulator   | 39 |

| 4. | Low Vol  | tage Low Power Design Techniques                                   |    |

|    | 4.1      | Switch Behavior.                                                   | 44 |

|    | 4.2      | Single Switch Behavior                                             | 48 |

|    | 4.3      | Existing Solutions                                                 | 50 |

|    | 4.4      | Original SO Technique                                              | 51 |

|    | 4.5      | Modified SO Technique.                                             | 52 |

|    | 4.6      | Quantization and Circuit Noise                                     | 54 |

|    | 4.7      | Intrinsic Constraint of Power Consumption                          | 57 |

|    | 4.8      | Practical Constraints of Power Consumption                         | 58 |

|    | 4.9      | Suppression of Noise Generated Inside the Loop                     | 58 |

|    | 4.10     | System Level Power Saving                                          | 59 |

| 5. | Building | Block Design                                                       |    |

|    | 5.1      | Switched Op-Amp.                                                   | 60 |

|    | 5.2         | Switch   | ned Op-Am   | p Integrator66                           | ı  |

|----|-------------|----------|-------------|------------------------------------------|----|

|    | 5.3         | Compa    | arator      |                                          |    |

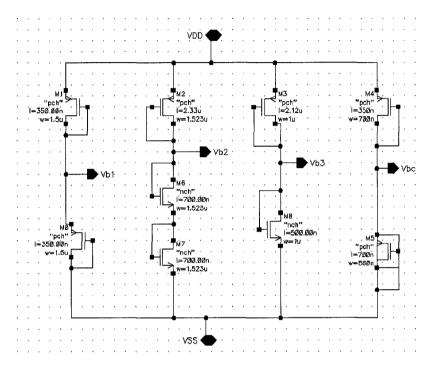

|    | 5.4         | Biasin   | g Circuit   | 75                                       |    |

|    | 5.5         | Half D   | elay Circu  | it                                       |    |

|    | 5.6         | Clock    | Generator.  | 77                                       | ,  |

| 6. | System I    | mpler    | nentatio    | 1                                        |    |

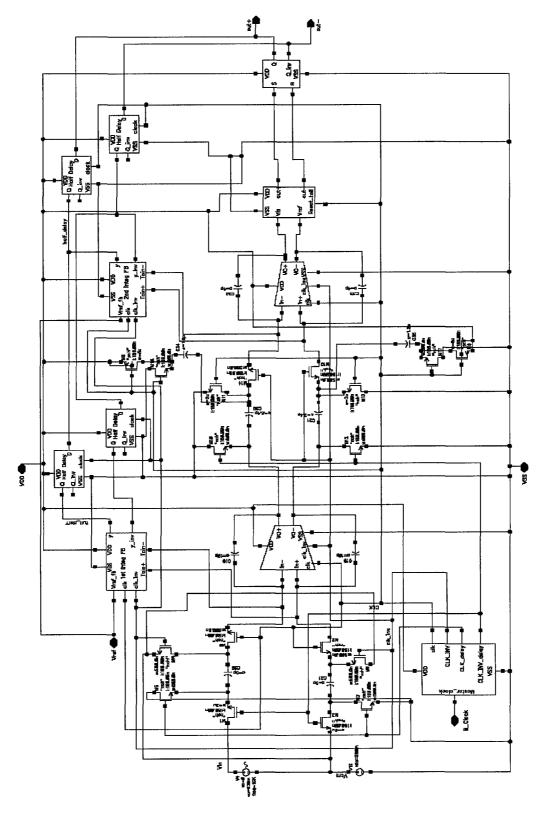

|    | 6.1. Modu   | lator Sc | chematic ar | nd Implementation79                      | ı  |

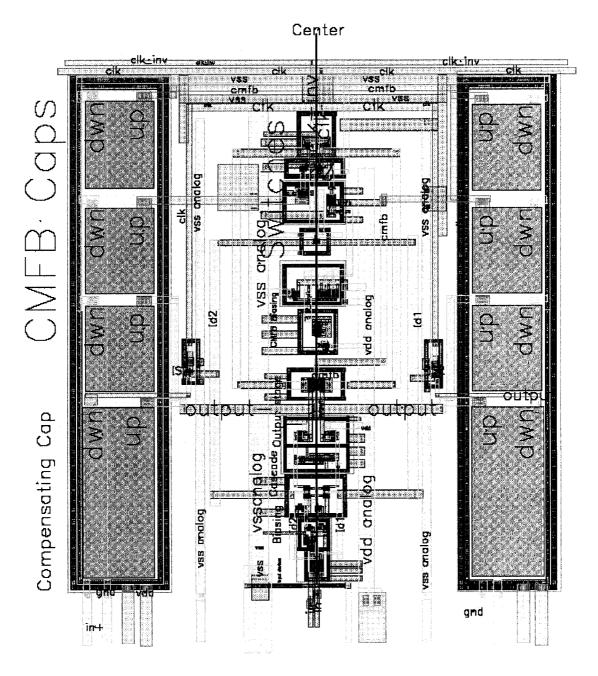

|    | 6.2. Modu   | lator La | ayout Meth  | odology84                                |    |

|    | 6.3. Floor- | plannin  | ıg          | 85                                       |    |

|    |             | 6.3.1.   | Power Su    | pply Strategy 85                         |    |

|    |             | 6.3.2.   | Interface S | Signals Definition86                     |    |

|    |             | 6.3.3.   | Special D   | esign Requirements Consideration86       |    |

|    |             | 6.3.4.   | Size Appr   | oximation86                              | 1  |

|    | 6.4. Sub-b  | lock im  | plementati  | on 87                                    | ,  |

|    |             | 6.4.1    | Compone     | nt Placement87                           | ,  |

|    |             | 6.4.2    | Special D   | esign Requirements87                     | ,  |

|    |             |          | 6.4.2.1     | Matching of Fully Differential Design 87 | ,  |

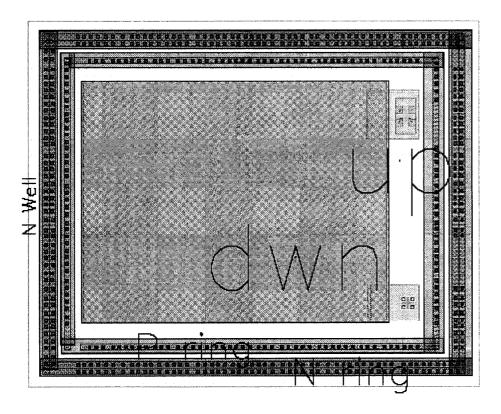

|    |             |          | 6.4.2.2     | Guard Rings90                            | }  |

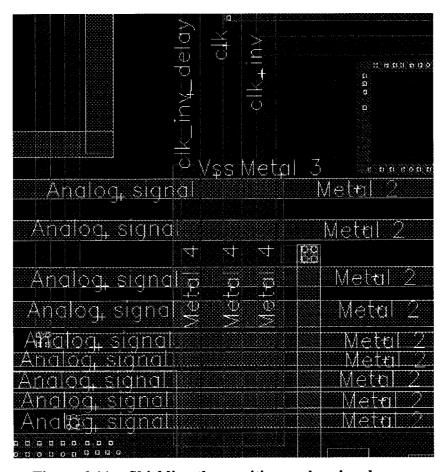

|    |             |          | 6.4.2.3     | Shielding90                              | )  |

|    |             |          | 6.4.2.4     | Capacitor Layout                         |    |

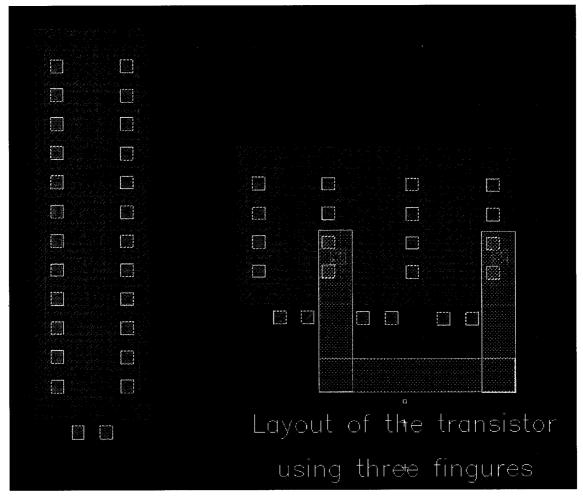

|    |             |          | 6.4.2.5     | Multi-finger Transistors                 |    |

|    |             | 6.4.3    | Compone     | nt Connection                            | Ļ  |

|    |             | 6.4.4    | Sub-Block   | x Layout Verification                    | ·  |

|    |             | •        |             | the Modulator Layout10                   |    |

|    |             |          |             | 10                                       |    |

|    |             |          |             | ile10                                    | 0  |

| 7. | Conclus     | ions a   | nd Recon    | nmended Future Work                      |    |

|    | 7.1 Conclu  | usions   |             |                                          | 15 |

|    | 7.2 Dagger  | monda    | d Enturo W  | ork 10                                   | 16 |

## Appendix A

| Vita        | Auct   | oris                                                 | 119   |

|-------------|--------|------------------------------------------------------|-------|

| Refe        | rence  | s                                                    | . 112 |

|             | A.3.1  | Extraction of a Sinusoidal Waveform from a Bitstream | 111   |

| A.3         | SNR C  | Calculation                                          | 110   |

| A.2         | PSD P  | lotting                                              | .108  |

| <b>A.</b> 1 | Slew F | Rate Modeling                                        | 107   |

## **List of Tables**

| 3-1. | Comparison between modulator architectures           | 18  |

|------|------------------------------------------------------|-----|

| 3-2. | Non-idealities of the fundamental basic blocks       | 27  |

| 3-3. | Second-order modulator coefficients and parameters   | 42  |

| 3-4. | Building block requirements                          | 42  |

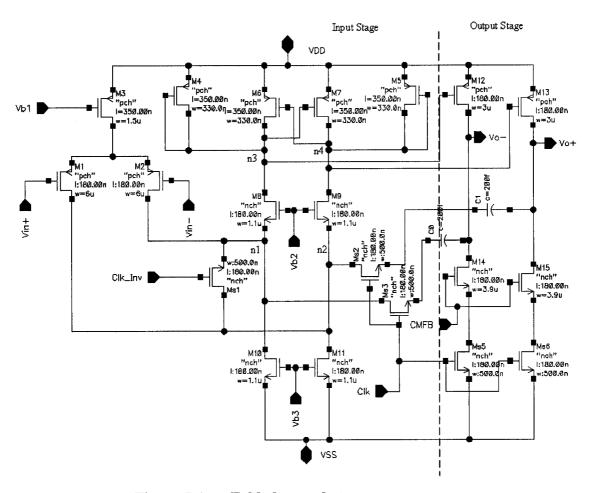

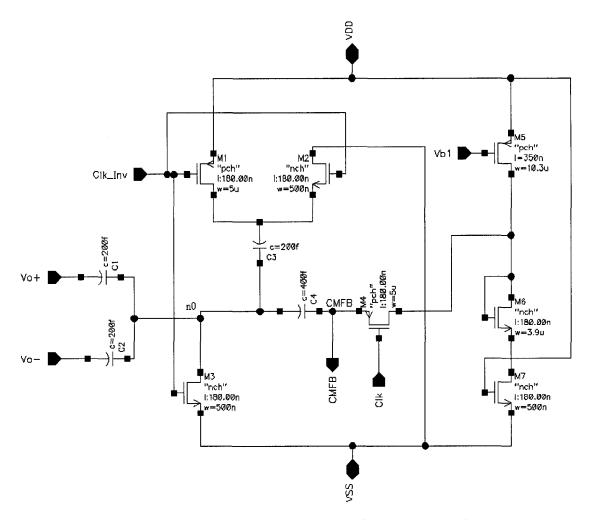

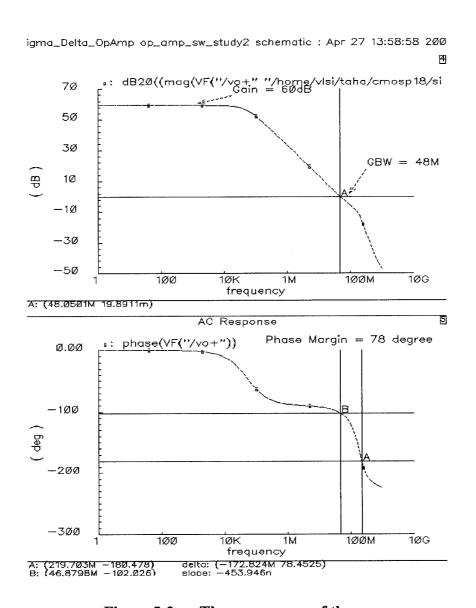

| 5-1. | Cell values for the op-amps                          | 63  |

| 5-2. | Simulated performance of the first and second op-amp | 65  |

| 5-3. | Cell values of the comparator                        | 74  |

| 5-4. | Comparator specifications                            | 74  |

| 5-5. | Cell values for the biasing circuit                  | 75  |

| 6-1. | Modulator specifications                             | 103 |

| 6.2. | Comparison between this work and previous designs    | 104 |

## **List of Figures**

| 2-1.  | Typical ADCs block diagrams                                                 | . 5  |

|-------|-----------------------------------------------------------------------------|------|

| 2-2.  | Nyquist rate and oversampling ADC                                           | 5    |

| 2-3.  | Pulse density output from a $\Sigma\Delta$ modulator for a sine wave input  | . 6  |

| 2-4.  | Digital and decimation filtering in the $\sum \Delta$ ADC                   | 7    |

| 2-5.  | First-order $\sum \Delta$ modulator                                         | 8    |

| 2-6.  | Z domain representation of the first-order $\sum \Delta$ modulator          | . 8  |

| 2-7.  | Second-order $\sum \Delta$ modulator                                        | 9    |

| 2-8.  | Comparison of noise shaping for the first, second and third-order           |      |

|       | $\sum \Delta$ modulator                                                     | 11   |

| 2-9.  | Oversampling ratio versus resolution for the first, second and third        |      |

|       | -order $\sum \Delta$ modulator                                              | 13   |

| 2-10. | SO $\sum \Delta$ modulator design methodology                               | 16   |

| 3-1.  | Classic $n^{th}$ order single loop $\sum \Delta$ modulator topology         | . 19 |

| 3-2.  | Second-order, single-loop $\sum \Delta$ modulator topology                  | 19   |

| 3-3.  | The nth order single loop $\sum \Delta$ modulator topology using half delay |      |

|       | integrators                                                                 | 20   |

| 3-4.  | Block diagram of a cascaded $\sum \Delta$ modulator                         | . 23 |

| 3-5.  | Cascaded 2-1 $\sum \Delta$ modulator with half delay integrators            | 23   |

| 3-6.  | Modeling a random sampling jitter                                           | 28   |

| 3-7.  | Noisy integrator model                                                      | 29   |

| 3-8.  | Single-ended SC integrator                                                  | 29   |

| 3-9.  | Modeling thermal noise (KT/C)                                               | 30   |

| 3-10. | Op-amp noise model                                                          |      |

| 3-11. | Real integrator model                                                       | 32   |

| 3-12. | SIMULINK model for an ideal second-order $\sum \Delta$ modulator            | 36   |

| 3-13  | SIMULINK simulation scope's results for the input, first and second         |      |

|       | integrator and the modulator output                                         | 37   |

| 3-14. | Simulated output spectra with –2 dB input sinusoidal for the                      |    |

|-------|-----------------------------------------------------------------------------------|----|

|       | ideal second-order modulator                                                      | 8  |

| 3-15  | SIMULINK model for the non-ideal second-order $\sum \Delta$ modulator 3           | 9  |

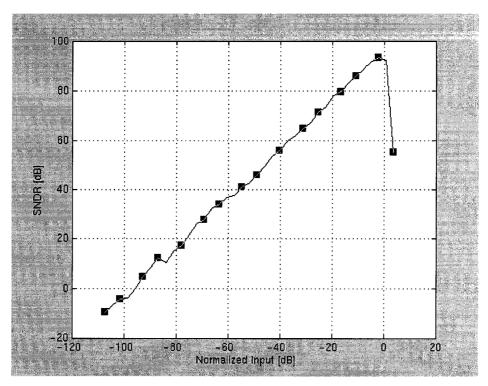

| 3-16  | SNDR versus input amplitude                                                       | 10 |

| 3-17  | Simulated output spectra with -2 dB input sinusoidal for the non-ideal            |    |

|       | second-order ∑∆modulator                                                          | 1  |

| 4-1.  | Non-inverting SC integrator                                                       | 15 |

| 4-2.  | Complementary switch                                                              | 6  |

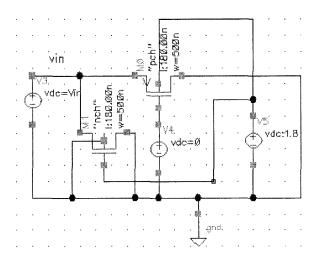

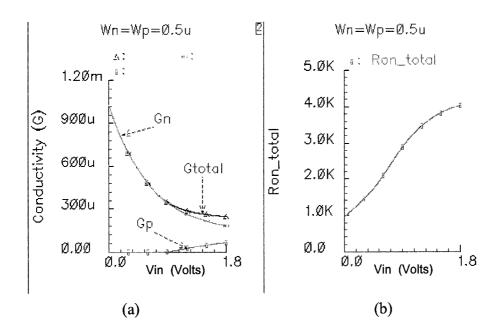

| 4-3.  | Complementary switch simulation results in 0.18 µm process                        | 17 |

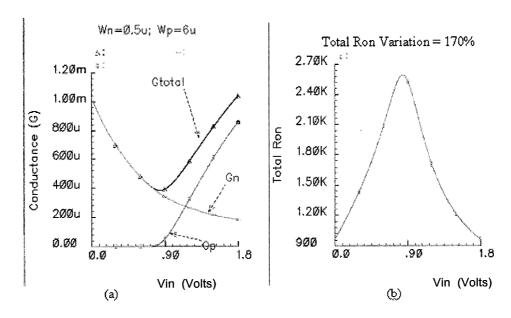

| 4-4.  | Complementary switch with symmetrical on-resistance simulation results            |    |

|       | in 0.18 μm process                                                                | 17 |

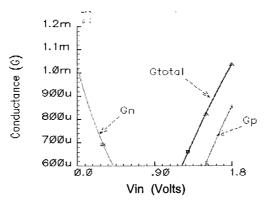

| 4-5.  | Simulation results of the symmetrical on-resistance complementary                 |    |

|       | switch if the minimum conductivity desired is $600~\mu\text{G}$ (equivalent to an |    |

|       | on-resistance of $2.1 \text{K}\Omega$ )                                           | 18 |

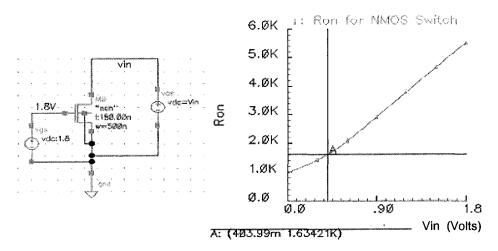

| 4-6.  | Simulation of the N-type switch in 0.18 μm technology                             | 19 |

| 4-7.  | Simulation of the P-type switch in 0.18 µm technology                             | 19 |

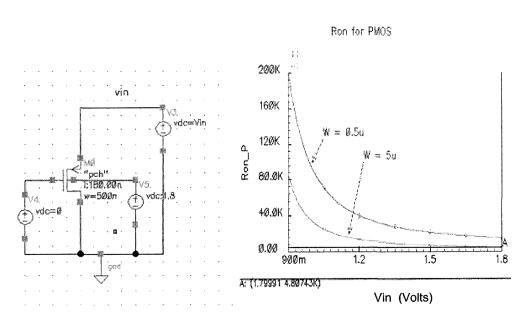

| 4-8.  | The SO integrator preceded by another integrator                                  | ;2 |

| 4-9.  | The signal swings in the modified SO technique                                    | ;3 |

| 4-10. | The differential modified SO integrator cell                                      | ;3 |

| 4-11. | The noise power spectral densities                                                | 6  |

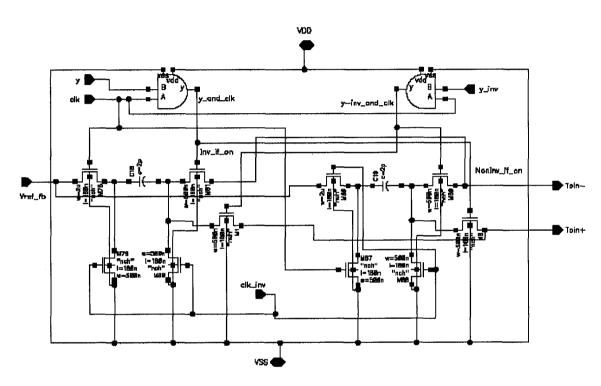

| 5-1.  | Folded cascade two stage op-amp                                                   | 52 |

| 5-2.  | The common-mode feed back circuit                                                 | 53 |

| 5-3.  | The ac response of the op-amp                                                     | 54 |

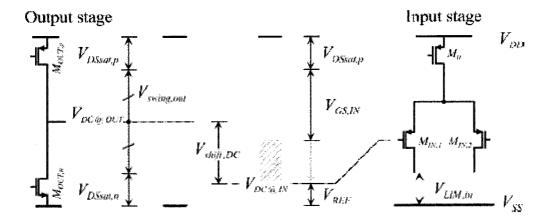

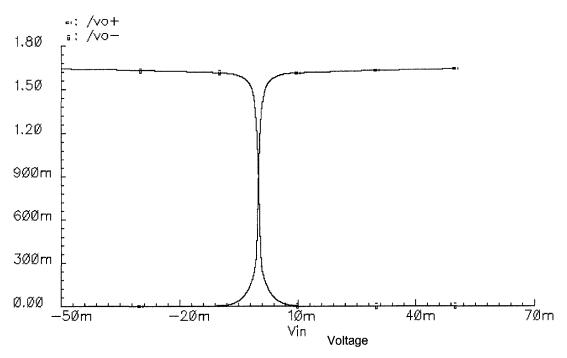

| 5-4.  | The DC response of the op-amp                                                     | 5  |

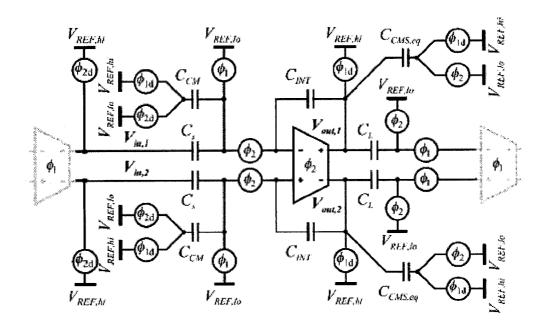

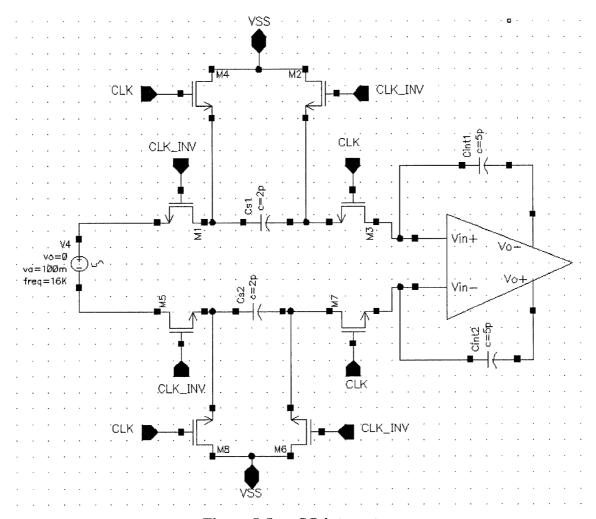

| 5-5.  | SO integrator                                                                     | 66 |

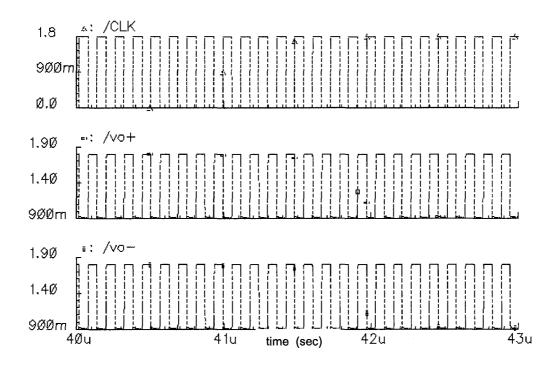

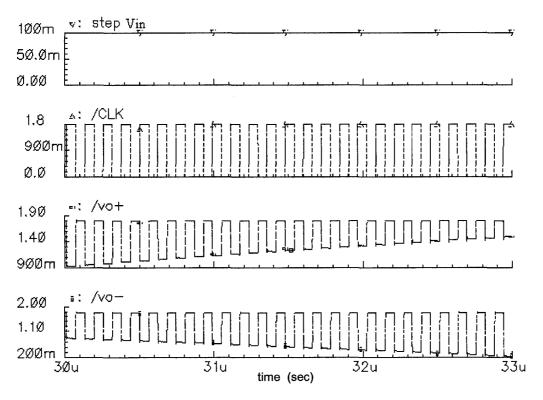

| 5-6.  | Output CM simulation result                                                       | 57 |

| 5-7.  | Transient response to a step input                                                | 57 |

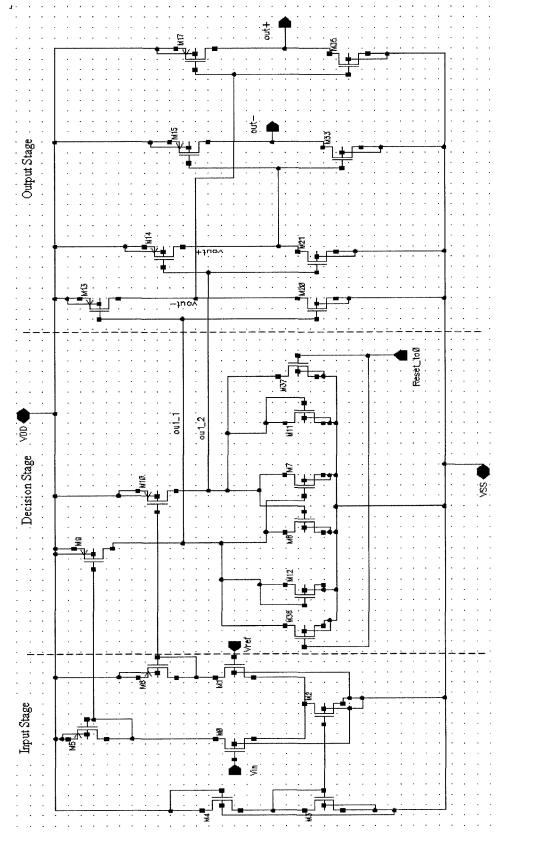

| 5.8.  | Three-stage comparator                                                            | 70 |

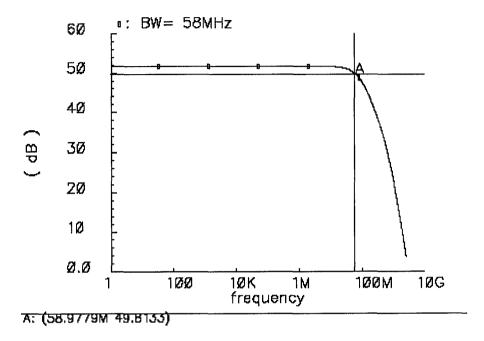

| 5-9.  | The ac response of the comparator                                                 | 1  |

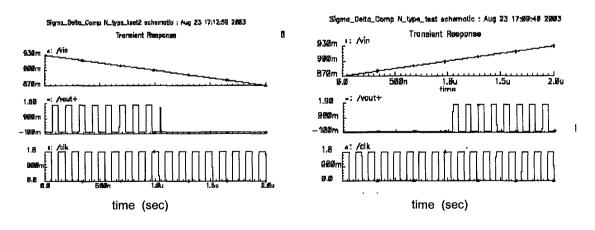

| 5-10. | Comparator response to a ramp input                                               | 1  |

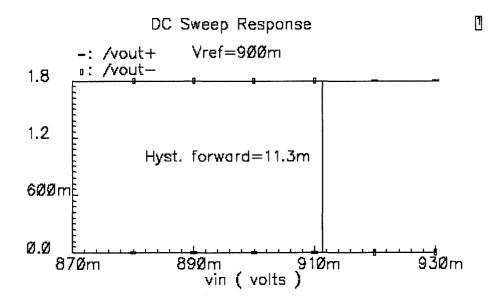

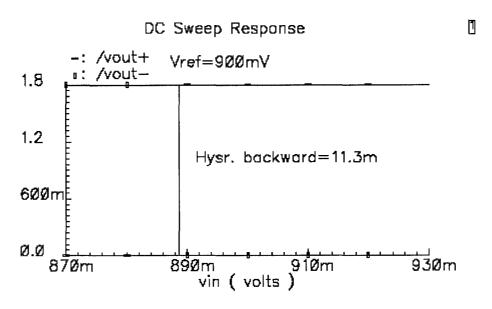

| 5-11. | Simulating hysteresis in the forward direction                                    | 12 |

| 5-12. | Simulating hysteresis in the backward direction                           | . 72  |

|-------|---------------------------------------------------------------------------|-------|

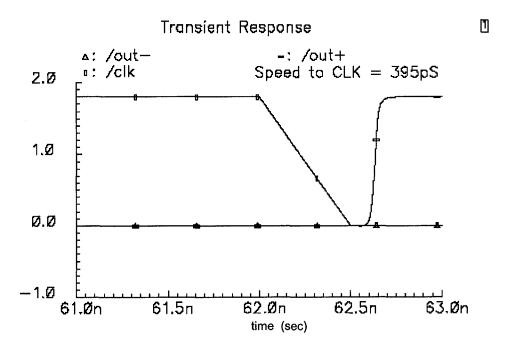

| 5-13. | Simulating the comparator speed                                           | 73    |

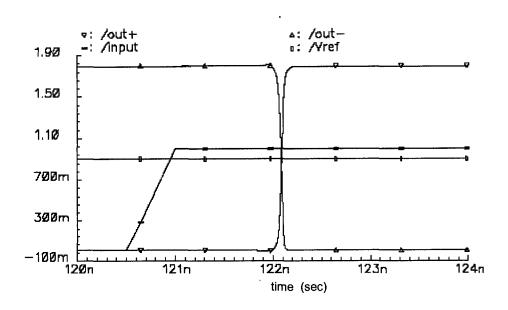

| 5-14. | Simulating the comparator propagation delay                               | 73    |

| 5-15. | The biasing Circuit.                                                      | 75    |

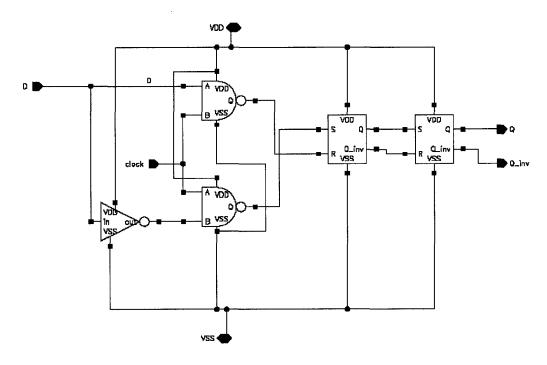

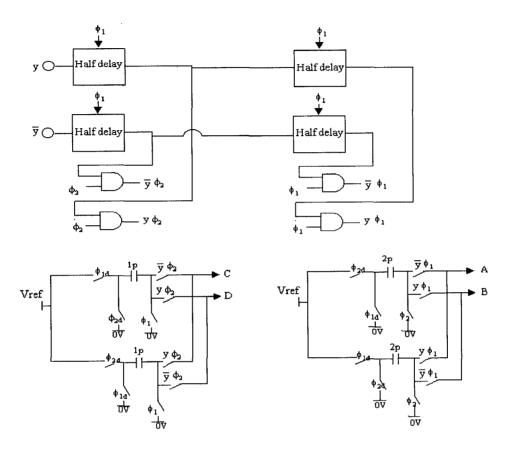

| 5-16. | Half delay circuit                                                        | 76    |

| 5-17. | Half delay circuit simulation result                                      | .76   |

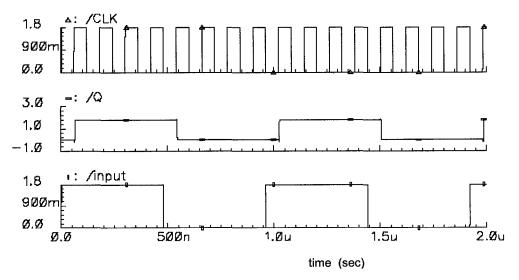

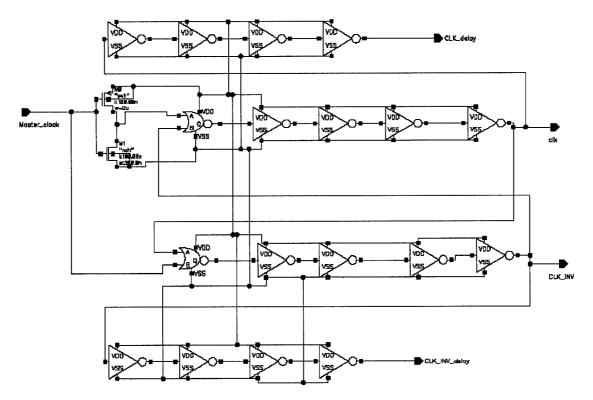

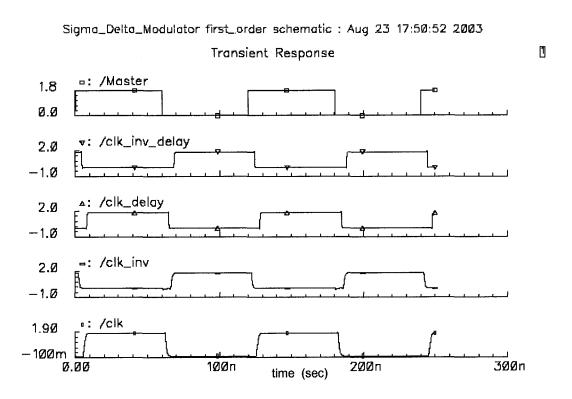

| 5-18. | Clock generation.                                                         | . 77  |

| 5-19. | Timing diagram                                                            | 78    |

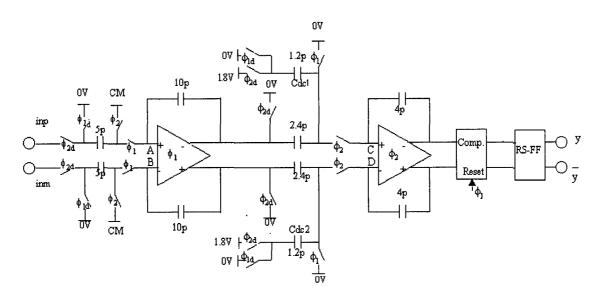

| 6-1.  | Circuit schematic of the second-order single-loop $\sum \Delta$ modulator | 79    |

| 6-2.  | Feedback network                                                          | 81    |

| 6-3.  | Feedback circuit implementation                                           | 82    |

| 6-4.  | Second-order single-loop SO $\Sigma\Delta$ modulator                      | . 83  |

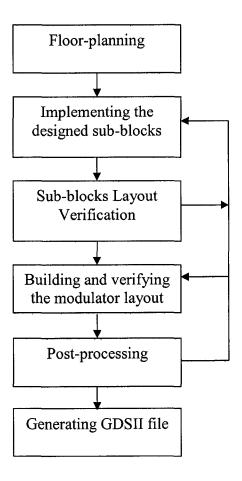

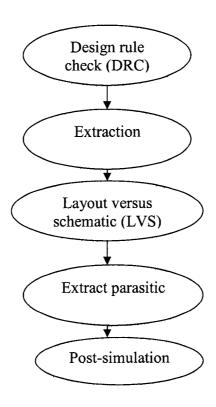

| 6-5.  | Layout methodology                                                        | . 84  |

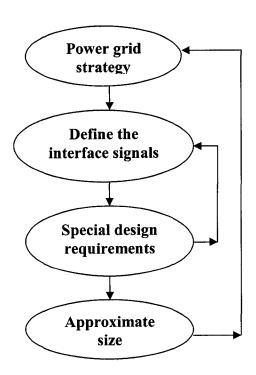

| 6-6.  | Floor-planning steps                                                      | 85    |

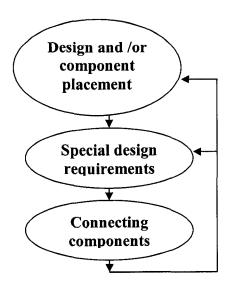

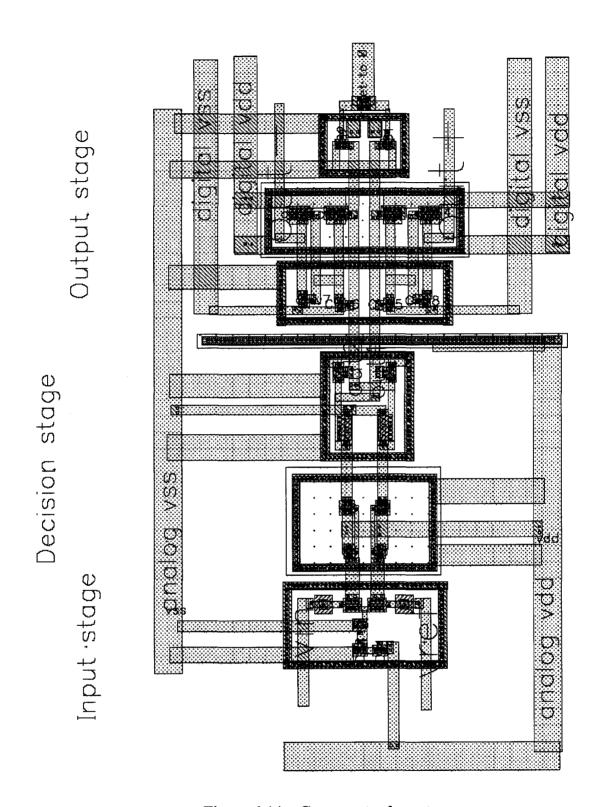

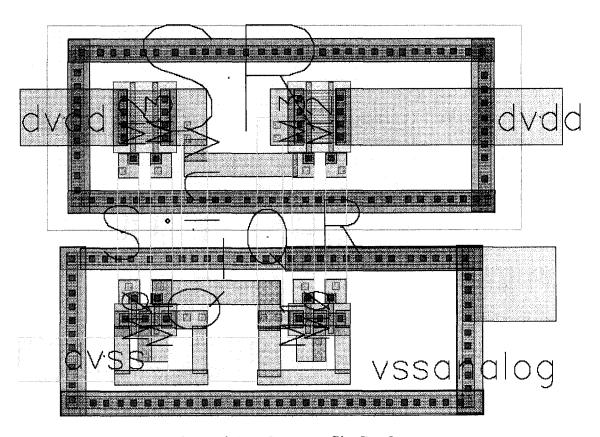

| 6-7.  | Implementing the designed sub-blocks                                      | 88    |

| 6-8.  | Common centroid input stage transistors                                   | 88    |

| 6-9.  | Op-amp layout                                                             | . 89  |

| 6-10. | Capacitor layout with guard rings                                         | 91    |

| 6-11. | Shielding the sensitive analog signals                                    | . 92  |

| 6-12. | Multi-fingering.                                                          | 93    |

| 6-13. | Building block layout verification steps                                  | . 95  |

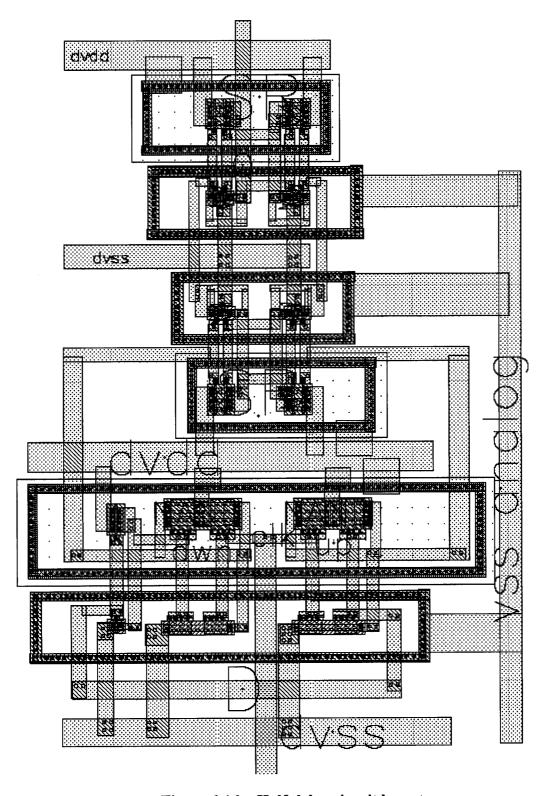

| 6-14. | Comparator layout                                                         | . 96  |

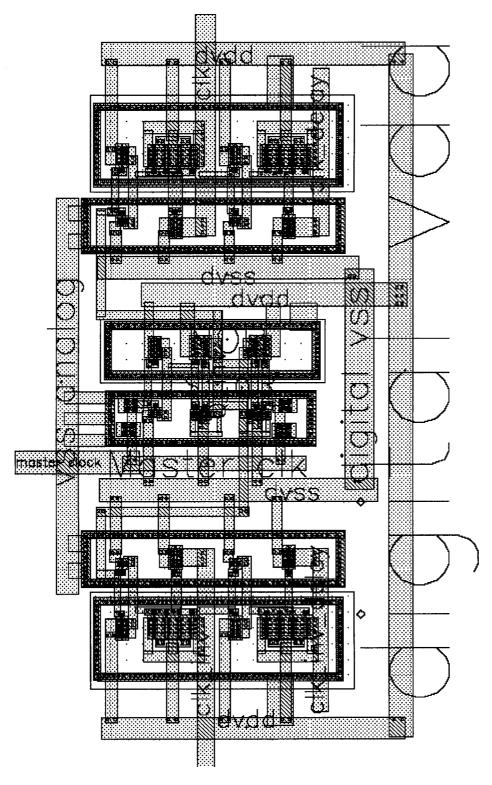

| 6-15. | Clock generation layout                                                   | 97    |

| 6-16. | Half-delay circuit layout.                                                | 98    |

| 6-17. | Set-reset flip flop layout.                                               | 99    |

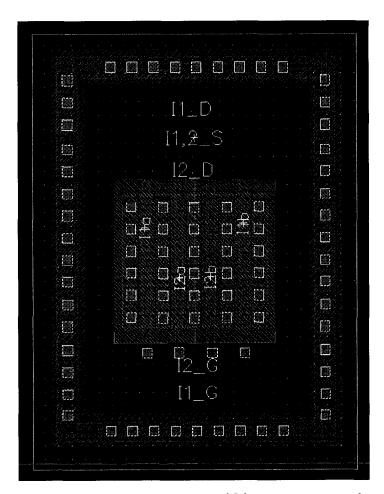

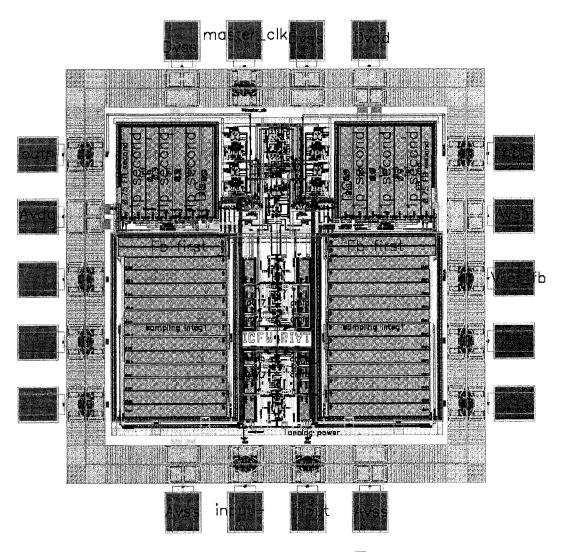

| 6-18. | The implemented $\sum \Delta$ modulator                                   | . 101 |

| 6-19. | The generated bitstream                                                   | 102   |

| 6-20. | The output spectrum                                                       | 102   |

| 6-21. | SNDR versus signal amplitude                                              | 103   |

## **Abbreviations**

ADC Analog-to-digital converter

**CM** Common-mode

**CMFB** Common-mode feedback

**CMOS** Complementary metal-oxide semiconductor

**DAC** Digital-to-analog converter

**DR** Dynamic range

**DRC** Design rule checker

FF Flip-flop

**FOM** Figure-of-merit

**GBW** Gain bandwidth product

GUI Graphical user interface

LVS Layout versus schematic

MOSFET Metal-oxide semiconductor field effect transistor

NMOST Negative-channel metal-oxide semiconductor transistor

**NTF** Noise transfer function

**Op-Amp** Operational amplifier

**OSR** Oversampling ratio

**PMOST** Positive-channel metal-oxide semiconductor transistor

**PSD** Power spectral dnsity

RMS Root mean square

RC Resistance capacitor

**SC** Switched capacitor

**ΣΔ** Sigma-delta

**SNDR** Signal-to-noise and distortion ratio

**SNR** Signal to noise ratio

**SO** Switched op-amp

**SOC** System on chip

SR Slew rate

**SR FF** Set-reset flip-flop

**STF** Signal transfer function

**VLSI** Very large scale integration

## Chapter 1

## Introduction

#### 1.1 Motivation

Modern electronics systems in computers, communications, automotive and instrumentation are mostly mixed-signal systems. An analog to digital converter (ADC) is a standard building block, unavoidable as interface between the analog world and the digital signal processing hardware. The market for portable electronic systems and system-on-chip (SOC) such as wireless communications devices and hearing aids, is continuously expanding. Both low voltage and low power operation are of great importance for portable applications and SOC. Low voltage operation is demanded because it is desirable to use as few batteries as possible for size and weight considerations. Low power consumption is necessary to ensure a reasonable battery lifetime.

The  $\Sigma\Delta$  converters are based on noise shaping and over-sampling. It has been known for nearly thirty years, but only recently has the technology of high-density digital VLSI existed to manufacture them as inexpensive integrated circuits. Without the CMOS technology, the digital filtering required in  $\Sigma\Delta$  converters for decimation and interpolation makes these circuits too expensive. Low voltage low power design can be achieved as the CMOS technology is scaled down.  $\Sigma\Delta$  converters have low sensitivity to the component mismatches at the price of extensive use of digital processing [1].

There are a lot of architectures available to implement  $\Sigma\Delta$  converters, from single-loop [2] to the more sophisticated with multiple feedback loops, cascade connection or multi-bit quantization [3] [4] [5] [6] [7] [8]. Most of these architectures have been successfully implemented. CMOS  $\Sigma\Delta$  converters with 20-bit effective resolution in instrumentation [9] [10] [11], 16-bit in audio and data acquisition [12] [13] [14] [15] [16] and 12-bit or more in communications are feasible [17] [18] [19] [20].

The first and probably largest application of  $\sum \Delta$  converters is in the field of digital telephony [21]. Digital audio is the most obvious application that takes full advantage of

the inherent qualities of  $\Sigma\Delta$  converters [22] [23] [24] [25] [26]. For digital-audio applications, the previous researches have already proven that switched-capacitor (SC)  $\Sigma\Delta$  structure is a good candidate. However, these works either employ supply voltages as high as 5 V [27], or use out-of-date CMOS technologies with bigger transistor channel lengths [27] [28]. In the 0.18  $\mu$ m technology,  $\Sigma\Delta$  modulator is presented for digital-audio applications using a bootstrapped switch [29]. To the author's knowledge, there is a lack of papers on implementation of digital-audio  $\Sigma\Delta$  modulators with guaranteed performance that is compatible with the latest CMOS technologies. The market does post a continuing demand to design  $\Sigma\Delta$  modulators using technologies with channel length as small as 0.18 $\mu$ m or even smaller to be compatible with the latest CMOS technologies and with less area-occupation, high-resolution, and low power.

## 1.2 Objectives

This thesis investigates the development of a switched op-amp (SO)  $\Sigma\Delta$  modulator for digital-audio instrumentations to provide compatibility with the continuously decreasing CMOS technology feature size. The specific design objectives are:

- To develop a top down design methodology in order to perform an analysis at the system architectural level before starting transistor level design. To use Matlab/ SIMULINK to implement the system architecture and model non-idealities.

- 2. To choose the proper topology to design the  $\sum \Delta$  modulator for digitalaudio instrumentations, while considering low-power and low-voltage design constraints.

- 3. To carry out the design of the individual building blocks using the 0.18 µm CMOS process. To integrate the building blocks. To verify the designed individual circuits and the whole modulator by simulation using Hspice in the Cadence design tools.

- 4. To implement the Layout considering the mixed-signal design requirements. To verify that the designed  $\sum \Delta$  modulator meets the

required specifications thought post-simulation with parasitic and testing the fabricated chip.

#### 1.3 Thesis Organization

Chapter 2 is an introduction to  $\Sigma\Delta$  modulators. It includes discussing oversampling ADC, analyzing the behavior of  $\Sigma\Delta$  modulators in the Z-domain and discussing the performance metrics. The motivation for top-down design methodology is discussed and the implemented methodology for this work is shown. In Chapter 3 different kinds of topologies are compared and the reasons for selecting the single-loop, second-order  $\Sigma\Delta$  modulator for this work are discussed. Non-idealities issues associated with  $\Sigma\Delta$  modulator design and modeling in MATLAB/ SIMULINK are given and the behavior simulation to optimize the system and building blocks parameters is then developed. In Chapter 4, the switch design constraint and low-voltage, low-power design techniques are addressed. Chapter 5 focuses on the implementation of each building block in the TSMC 0.18  $\mu$ m CMOS technology with the simulation results from the analog environment of the cadence design tool. Chapter 6 deals with integrating the building blocks to implement the SO  $\Sigma\Delta$  modulator and simulating the results. In Chapter 7, conclusion remarks and recommendations for future work are discussed.

## Chapter 2

## **ΣΔ Modulator Basic Concepts**

This Chapter introduces the concept of oversampling ADC, describes the basic function of the  $\Sigma\Delta$  Modulator and explains how the  $\Sigma\Delta$  Modulation is so beneficial for generating high-resolution data. The performance criteria that are necessary to measure the performance of the  $\Sigma\Delta$  Modulator are defined. A top-down design methodology using SIMULINK for the design of  $\Sigma\Delta$  modulator is discussed. The motivation and the benefits of the top-down optimization are presented, which featured a shorter design cycle, along with ease of implementation and reproducibility. The design steps for the SO  $\Sigma\Delta$  modulator are summarized

## 2.1 Oversampling ADC

Analog-to-digital converters can be separated into two categories depending on the rate of sampling. The first category samples the input at the Nyquist rate, such that:

$$f_N = 2F$$

Where F is the signal bandwidth and  $f_N$  is the sampling rate. The second type samples the signal at a rate much higher than the signal bandwidth. This type is called the oversampling converter [30].

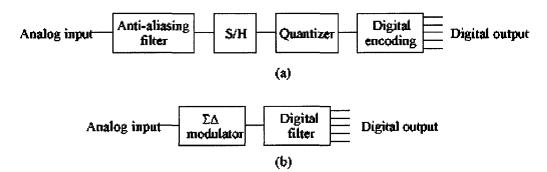

Figure 2-1 shows the typical process used in ADC. After filtering the signal, to help minimizing aliasing effects, the signal is sampled, quantized, and encoded using simple digital logic to provide the digital data in the proper format.

Figure 2-1. Typical ADCs block diagrams. (a) Nyquist rate ADC. (b) Oversampling ADC

Sampling frequency is twice the signal bandwidth.

Oversampling frequency is many times the signal bandwidth.

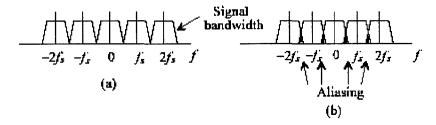

Figure 2-2. Nyquist rate and oversampling ADC. (a) Frequency domain for Nyquist rate ADC. (b) Aliasing effect for Nyquist rate ADC. (c) Frequency domain for oversampling ADC.

A sampled signal in the frequency domain appears as a series of band-limited signals at multiples of the sampling frequency. As the sampling frequency decreases, the frequency spectra begin to overlap causing aliasing effect. Figure 2-2a shows the frequency spectra, while Figure 2-2b shows the aliasing effect when using Nyquist rate converters. Complex filters are required to correct the problem. For oversampled ADC, aliasing becomes much less of a factor. Since the sampling rate is much greater than the bandwidth of the signal, the frequency domain representation shows that the spectra are

widely spaced, as seen in Figure 2-2c. Thus using oversampling ADC, little if any, anti\_alias filtering is needed.

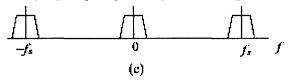

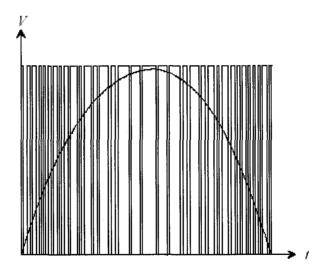

Oversampling converters typically employ SC circuit and therefore do not need sample-and-hold circuits. Quantization is provided in the form of a pulse-density modulated signal that represents the average of the input signal. The modulator is able to construct these pulses in real time, so it is not necessary to hold the input value and perform the conversion. Figure 2-3 illustrates the output of the modulator for the positive half of a sine wave input. For the peak of the sine wave, most of the pulses are high. As the sine wave decreases in value, the pulses become distributed between high and low according to the sine wave value.

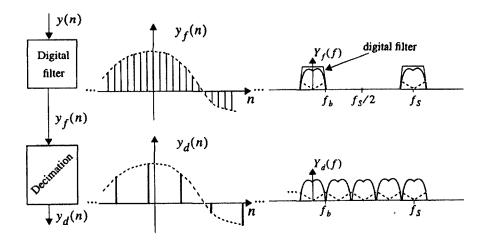

Digital signal processing should be utilized for the oversampling ADC, which filter any out-of-band quantization noise and attenuate any spurious out-of-band signals. The output of the filter is then down sampled to the Nyquist rate so that the resulting output of the ADC is the digital data, which represents the average value of the analog voltage over the oversampling period. Figure 2-4 shows the block diagram and the frequency spectrum of the digital part.

Figure 2-3. Pulse density output from a  $\sum \Delta$  modulator for a sine wave input

Figure 2-4. Digital and decimation filtering in the  $\sum \Delta$  ADC

## 2.2 First Order ΣΔ Modulator

This section examines the time domain and the frequency domain behaviour to determine why  $\Sigma\Delta$  Modulation is so beneficial for generating high-resolution data. Noise shaping, which is a powerful concept used within oversampling ADC, is explained.

#### 2.2.1 Time Domain Behaviour

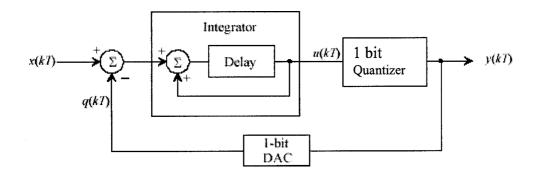

A basic first order  $\sum \Delta$  modulator can be seen in Figure 2-5. An integrator and a 1-bit quantizer are in the forward path, and a 1-bit digital-to-analog (DAC) is in the feedback path of a single-feedback loop system. The 1-bit quantizer is simply a comparator that converts an analog signal into either a high or low. From the Z-domain representation shown in Figure 2-6, the input-output relation can be written in terms of a difference equation as [31]:

$$y(KT) = x(KT - T) + Q_{e}(KT) - Q_{e}(KT - T)$$

(2-1)

Where K is an integer. T is the inverse of the sampling frequency  $(f_s)$ .  $Q_e$  is the quantization noise expressed as:

$$Q_{\alpha}(KT) = y(KT) - u(KT)$$

Figure 2-5. First-order  $\sum \Delta$  modulator

Figure 2-6. Z domain representation of the first-order  $\sum \Delta$  modulator. (a) Z-domain representation. (b) Conceptual representation.

Therefore, the output of the modulator consists of a quantized value of the input signal delayed by one sample period, plus a differencing of the quantization error between the present and previous values. Thus, the real power of the  $\Sigma\Delta$  Modulator is that the quantization noise  $Q_e$ , cancels itself out to the first order.

#### 2.2.2 Z-Domain Behaviour

Figure 2-6 shows the Z-domain model for the first order  $\sum \Delta$  modulator. The ideal integrator is represented with the transfer function  $\frac{Z^{-1}}{1-Z^{-1}}$ . The 1-bit quantizer is

modeled as a simple error source Q(Z), and the DAC is considered to be ideal. The output can be expressed as:

$$Y(z) = z^{-1}X(z) + (1-z^{-1})Q(z)$$

(2-2)

Where Y(z), X(z) and Q(z) are the z-transform of the modulator output, input, and the quantization error respectively.

The multiplication factor of X(z) is called the signal transfer function (STF), whereas that of Q(z) is called the noise transfer function (NTF). It can be noted that  $z^{-1}$  represents a unit delay, while the NTF has high pass characteristics, allowing noise suppression at low frequencies. The modulator has essentially pushed the power of the noise out of the bandwidth of the signal. This high-pass characteristic is known as noise shaping. The digital filter will then perform low pass filtering in order to remove all of the out-of-band quantization noise, which then permits the signal to be down sampled to yield the final high-resolution output

## 2.3 Second Order $\sum \Delta$ modulators

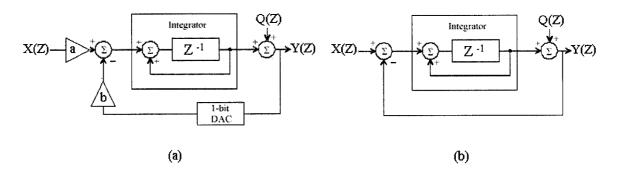

Second order  $\Sigma\Delta$ modulator provides a greater amount of noise shaping. A second-order modulator is shown in Figure 2-7.

Figure 2-7. Second-order  $\sum \Delta$  modulator

The output of the modulator can be expressed in the time domain as [31]:

$$y(KT) = x(KT - T) + Q_{a}(KT) - 2Q_{a}(KT - T) + Q_{a}(KT - 2T)$$

(2-3)

The output contained a delayed version of the input plus a second-order differencing of the quantization noise  $Q_e$ .

The z-domain equivalent is given by [32]:

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})^{2}Q_{e}(z)$$

(2-4)

The NTF  $(1-z^{-1})^2$  has two zeros at dc, resulting in second-order noise shaping. In general L<sup>th</sup>-order noise shaping can be obtained by placing L integrators in the forward path of a  $\Delta\Sigma$  modulator. For L<sup>th</sup>-order noise differencing, the noise transfer function (NTF) is given by:

$$NTF_{\mathcal{O}}(z) = (1 - z^{-1})^{L}$$

(2-5)

In the frequency domain, the magnitude of the noise transfer function can be written as:

$$|NTF_{Q}(f)| = |1 - e^{-j2\pi f T_{s}}|^{L} = (2\sin \pi f T_{s})^{L}$$

(2-6)

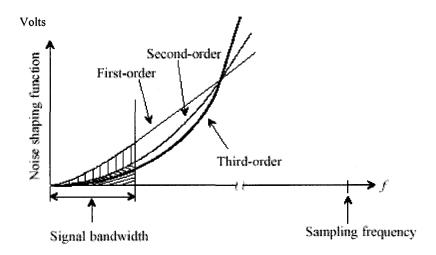

Figure 2-8 shows the noise shaping functions of the first, second, and third-order modulator. The crosshatched area under each of the curves represents the noise that remains in the signal bandwidth. As the order increasers, more of the noise is pushed out into the higher frequencies, thus decreasing the noise in the signal bandwidth. Almost all of the noise is out of the signal bandwidth; it can be easily filtered, leaving only a small portion within the signal bandwidth. As the modulator order and/ or oversampling ratio increases, the portion of the quantization noise that falls into the signal band decreases.

Figure 2-8. Comparison of noise shaping for the first, second and third-order  $\sum \Delta$  modulator.

In practice, the single-loop modulator having noise-shaping characteristics in the form of  $(1-Z^{-1})^{L}$  is unstable for (L>2), unless an L-bit quantizer is used [33] [34]

#### 2.4 Performance Criteria

The figures of merit used to characterize  $\Delta\Sigma$  modulator are the signal-to-noise ratio (SNR), signal-to-noise-and-distortion ratio (SNDR), Dynamic range (DR), the effective resolution and the power dissipation.

#### 2.4.1 Signal-to-noise ratio (SNR)

SNR is the ratio between the output power at the frequency of a sinusoidal input and the in-band noise power. Ideally with quantization noise only, the SNR results in:

$$SNR(dB) = 10\log_{10}\left(\frac{A^2/2}{P_Q}\right)$$

(2-7)

Where A is the amplitude of the input signal and P<sub>Q</sub> is the quantization noise power.

#### 2.4.2 Signal-to-noise-and-distortion ratio (SNDR)

It is the ratio of the output signal power to the in-band noise power due to the non-idealities of the circuitry and the quantization noise. Then by definition, SNDR is given by:

$$SNDR(dB) = 10\log_{10}\left(\frac{A^2/2}{P_Q + P_D}\right)$$

(2-8)

Where P<sub>D</sub> is the harmonic distortion power due to the non-idealities.

Peak SNDR is a useful metric for evaluating the capability of a  $\Sigma\Delta$  modulator for handling large in-band signals at acceptable linearity. It is especially important for applications such as digital audio applications. Peak SNDR is frequency dependant and can be used to measure the degradation of the modulator performance as the input signal increases in frequency. Since the output data is digital, discrete Fourier transform can be used to examine the data in the digital domain.

#### 2.4.3 Dynamic range (DR)

The DR is defined as the ratio between the output power at the frequency of a sinusoidal input with full-scale range amplitude and the output power when the input is a sinusoidal of the same frequency, but of small amplitude, so that it cannot be distinguished from noise; that is, with SNR equals to 0 dB. DR is also called the useful signal range [35]. For a single-bit quantizer, DR is given by [32]:

$$DR^{2} = \frac{3}{2} \frac{2L+1}{\pi^{2L}} M^{2L+1}$$

(2-10)

Where M is the OSR and L is the modulator order

#### 2.4.4 Effective resolution

The number of bits (B) or effective resolution of the  $\sum \Delta$  modulator as a function of its DR is [32]:

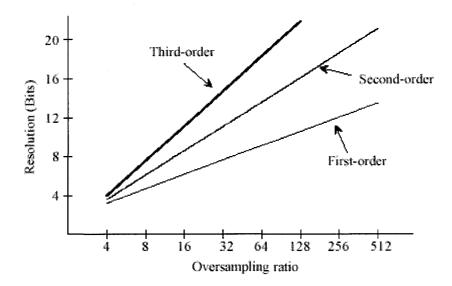

Figure 2-9. Oversampling ratio versus resolution for the first, second and third-order  $\Sigma\Delta$  modulator.

$$B(bit) = \frac{DR(dB) - 1.76}{6.02} \tag{2-11}$$

Thus for 16 bit data conversion, one must design a circuit that will have DR of 98 dB. The resolution also increases as the order of the  $\Sigma\Delta$  modulator and the oversampling ratio increases, as seen in Figure 2-9 [30]

It can be concluded from equation (2-10) and (2-11) that using a first-order modulator, DR increases by 9dB with every doubling of the oversampling ratio. This correlates to an approximate increase of 1.5 bits in resolution. The higher order modulators have even greater gain in resolution as 2.5 bit increase is attained with each doubling of the oversampling ratio using a second-order modulator, while the third-order modulator increases by 3.5 bits.

#### 2.4.5 Power Dissipation

In low-voltage, low-power design, power dissipation is an important parameter. It is opposes a design constraint. Power dissipation is normally discussed as a trade off parameter with target metrics.

#### 2.5 Top-Down Design Methodology Motivation

Despite a high tolerance for non-idealities of the  $\Sigma\Delta$  Modulator, it is still governed by the limitations of its analog building blocks, especially at the input stage, where, no noise shaping has taken place. The design of an analog system consists of three obstacles:

- 1. Architecture selection.

- 2. Determining the specifications of the analog building blocks necessary to implement the chosen architecture.

- 3. Minimizing the effects of the circuit non-idealities.

If these obstacles are treated separately, the number of design iteration is big and consequently the design cycle will take too long to practically meet the market demands for the technology. Due to the uncertainty that arises with a change in technology, it is more amenable to consider a design process that can begin without a complete dependence on a specific technology. Some tools exit aimed at fully automating the design process, however they are limited to a small number of fixed schematic [36] [37]. These tools, which are not designed to be reproduced, remove the designer from the process, and do nothing to increase the designer's knowledge. Furthermore, the techniques used in these programs are hidden and cannot be applied to other designs.

## 2.6 Switched Op-Amp ΣΔ Modulator Design Methodology

To reduce the number of the design iteration and better explore the design options, it is beneficial to perform an analysis at the system architectural level before starting transistor level design. This allows for a feasibility analysis in which all the design considerations are treated at the highest level of abstraction. The ultimate goal is to have the low level circuit parameters dictated by the selected architecture and desired performance. High-level optimization geared design avoids the complete dependence on a specific technology and provide the designers with values for familiar parameters (such as g<sub>m</sub> or r<sub>out</sub> for an op-amp), which provide excellent guidelines for the construction of a device. A top-down design methodology is needed in conjunction with an optimization process for the creation of analog or mixed signal integrated circuits.

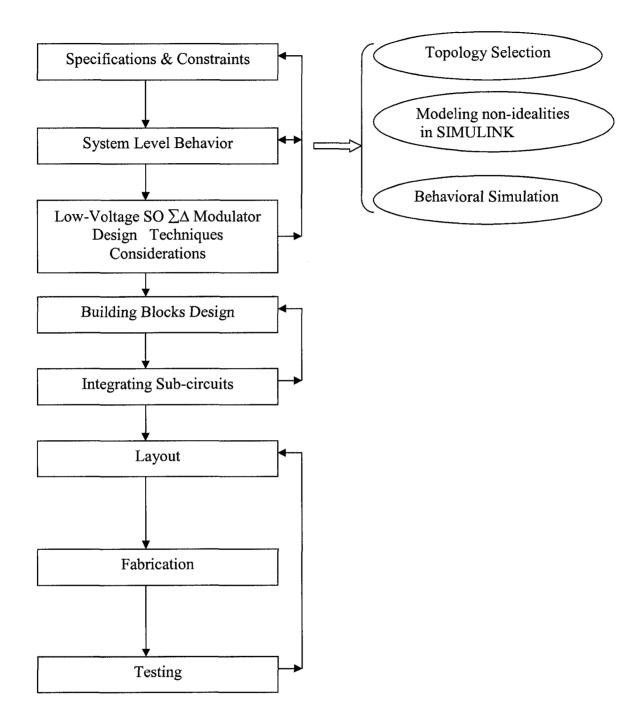

There is also a need to provide a mean of tackling the design problem by presenting a simple to implement methodology that makes use of widely used and available tools. This allows the procedure to be implemented and reused with little difficulty or expense [38]. SIMULINK is used to implement the system architecture and model non-idealities, while MATLAB [39] is used to create routines to optimize the circuit parameters. As a result, the requirements of the building blocks will be specified prior to the undertaking of transistor level simulation, saving valued design time. Top down design methodology is proposed to design  $\Sigma\Delta$  modulator. The systematic design methodology that is followed in this work is shown in Figure 2-10.

Starting with the required specification, the topology required for hearing-aid application is investigated and the optimal architecture is chosen. The system behavior simulation is necessary to optimize the  $\Delta\Sigma$  modulator topology parameters on the system level. SIMULINK is used for the behaviour simulation. The key parameters are isolated and the sub-circuits is modeled for non-idealities and the behaviour simulation is run again to derive the required circuit specification in order to ensure that the real system, with non-ideal components, reaches the intended performance. This methodology avoids estimation of the required circuit specifications; it is an important part of low power design. The building blocks are designed in 0.18  $\mu$ m process at the circuit level such that they achieve the given specifications and hence ensure the overall system performance. All the sub-modules and sub-circuits are integrated and simulated. The simulation results are compared with the required specification. The system then enters the layout phase. Post-simulation is necessary to ensure that the parasitic effect is considered. Finally it is sent for fabrication.

Figure 2-10. SO  $\Sigma\Delta$  modulator design methodology

## Chapter 3

## **System Level Behavior**

A variety of  $\Sigma\Delta$  modulator architectures have been explored recently.  $\Sigma\Delta$  modulators can be classified in two primary groups, the single-loop and cascade. Each of which has its advantages and drawbacks. Among these, perhaps the most robust is a second-order  $\Sigma\Delta$  modulator [34]. The second-order  $\Sigma\Delta$  modulator is attractive for digital-audio signal acquisition for their stable operation and its tolerance to circuit non-idealities.

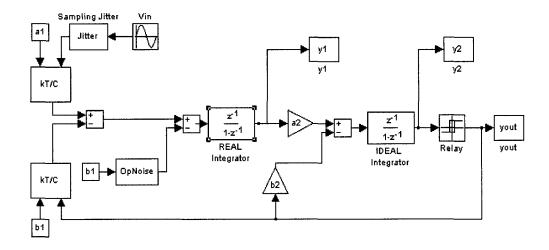

A complete set of SIMULINK models are needed to perform exhaustive behavioral simulation of the SC  $\Sigma\Delta$  modulator taking into account most of the non-idealities, such as sampling jitter, KT/C noise and op-amp parameters (noise, finite gain, finite bandwidth (GBW), slew-rate (SR) and saturation voltages). The models, which simulate non-idealities, are utilized in the behavior simulation. The behavior model is presented and the results obtained with the modeled blocks for the second-order  $\Sigma\Delta$  modulator are reported.

## 3.1 Comparison between Modulator Architectures

Different kinds of  $\Sigma\Delta$  modulators exist. Depending on the number of quantizers, modulator can be classified as single-loop and cascade. They can also be classified as one-bit or multi-bit modulator according to the number of quantization levels employed by the quantizer. The advantage and disadvantage of these topologies are summarized in Table 3-1.

Table 3-1

Comparison between modulator architectures

| Modulator Type     | Advantages                                     | Disadvantages                |

|--------------------|------------------------------------------------|------------------------------|

| Low-order          | Guaranteed stability                           | • High value of OSR for      |

| Single-loop        | Simple loop filter design                      | high SNR                     |

| Single-bit         | Simple circuit design                          | • More prone to noise        |

|                    |                                                | pattern                      |

| High-order         | High SNR for low OSR                           | Difficult loop filter design |

| Single-loop        | Less prone to noise pattern                    | • Stability is signal        |

| Single-bit         | Simple circuit design                          | dependent                    |

|                    |                                                | Maximum input range          |

| !                  |                                                | must be restricted to        |

|                    |                                                | ensure stability             |

| Multi-loop cascade | High SNR for low OSR                           | • Requires near perfect      |

|                    | Stability guaranteed                           | matching between analog      |

|                    | <ul> <li>Maximum useful input range</li> </ul> | integrator and digital       |

|                    |                                                | differentiator.              |

|                    |                                                | Complex SC circuits are      |

|                    |                                                | required to ensure           |

|                    |                                                | matching.                    |

| Multi-bit          | High SNR for very low OSR                      | More complex circuit         |

|                    | • Stability is much easier to be               | design                       |

|                    | achieved than for high-order                   | Sensitive to DAC non-        |

|                    | loops.                                         | linearity                    |

|                    | Smaller noise pattern                          |                              |

Figure 3-1. Classic  $n^{th}$  order single loop  $\sum \Delta$  modulator topology.

Figure 3-2. Second-order, single-loop  $\sum \Delta$  modulator topology

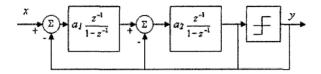

## 3.2 Single Loop $\sum \Delta$ modulators using Half Delay Integrators

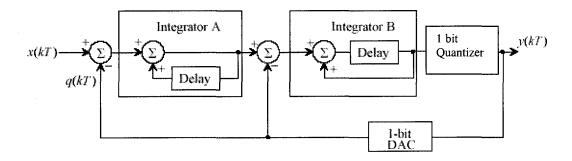

Single-loop  $\Sigma\Delta$  modulators are extremely insensitive to circuit mismatches. Practically, second-order, third order, fourth-order, or even higher order  $\Sigma\Delta$  modulators are used [40] [41]. Figure 3-1 shows the block diagram of an  $n^{th}$  order classic single bit modulator. The topology has been organized to have the minimum of independent parameters. It uses full delay integrators with a transfer function of:

$$I(z) = a \frac{z^{-1}}{(1 - z^{-1})} \tag{3-1}$$

Second-order  $\sum \Delta$  modulator for audio applications was suggested by [40]. Figure 3-2 shows the second-order modulator topology. The output of this modulator in the frequency domain is given as follows:

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})^{2}E(z)$$

(3-2)

In equation 3-2, the noise transfer function  $(1 - z^{-1})^2$  works as a second-order shaping filter to the quantization noise

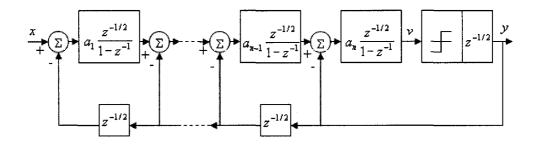

Figure 3-3. The  $n^{th}$  order single loop  $\sum \Delta$  modulator topology using half delay integrators.

The basic SO integrator cell offers only and exactly a half delay to the signal, thus its transfer function is given by:

$$I_{\frac{1}{2}}(z) = a \frac{z^{-1/2}}{(1-z^{-1})} \tag{3-3}$$

The half-delay integrator must be followed by an analog half-delay block to function as a full-delay integrator [42] [43]. This can be implemented by a SC amplifier with unity gain, deploying the SO technique. However, this requires an extra op-amp, and hence causes an increased power and area allocation. For the purpose of a  $\Sigma\Delta$  modulator, these additional amplifiers can be avoided by making use of a rearrangement topology. In the architecture of Figure 3-3, the half-delay element has been shifted to the feedback path [44]. There they are in the digital domain. They can be implemented with a half-delay latch and their power consumption is now negligible as compared to the analog implementation. Furthermore, the properties of the modulator are identical to the full-delay implementation. The loop coefficients that optimize the SNR have not changed.

The power spectral density of the shaped quantization noise of an  $n^{th}$ -order oversampling  $\sum \Delta$  modulators is calculated as [45]

$$S_{Q}(f) = S_{E}(f) \left| 1 - e^{-j2\pi \frac{f}{f_{s}}} \right|^{2n} = \frac{\Delta^{2}}{12f_{s}} \cdot 2^{2n} \sin^{2n} \left( \pi \frac{f}{f_{s}} \right)$$

(3-4)

Where  $\Delta$  is the separation between two consecutive levels

The in-band noise power is calculated by integrating the power spectral density of the quantization error expressed in equation 3-4, in the signal band  $(-f_b, f_b)$ :

$$N_Q = \int_{-f_b}^{f_b} S_Q(f) df = \frac{\Delta^2}{12} \cdot \frac{\pi^{2n}}{(2n+1) \cdot OSR^{(2n+1)}}$$

(3-5)

Where OSR is the is the oversampling ratio, expressed as:

$$OSR = 2f_b/f_s$$

Then the DR is calculated as:

$$DR = 10\log\left[\frac{(\Delta/2)^2}{2N_Q}\right] = 10\log\frac{(6n+3)OSR^{(2n+1)}}{2\pi^{2n}}$$

(3-6)

Equation 3-6 shows that the DR is a strong function of the OSR and the order (n) of the  $\Sigma\Delta$  modulator. For each doubling of the OSR, an extra (2n+1)/2 bits can be obtained. Thus the designers can tradeoff between OSR and n to meet the required DR. On the other hand, the main constraints for single-loop modulators of an order greater than 2 is the stability problem. Increasing the loop parameters worsens the stability of the loop [46] as they become conditionally stable. Stabilizing a high-order modulator requires the use of deliberately chosen parameters and more complicated transfer functions than just a cascade of integrators and possibly the use of reset circuits in the integrators in case instability happens. All of these tend to reduce the DR well below the upper bound given by equation 3-6 for a single-loop modulator with orders higher than two.

The second-order modulator is widely used because it is simple to implement and insensitive to component mismatch. The NTF " $(1-z^{-1})^2$ " filters out the quantization noise out to the second-order. From equation 3-4, the power spectral density of the shaped quantization noise is deduced as:

$$S_{Q}(f) = S_{E}(f) \left| 1 - e^{-j2\pi \frac{f}{f_{s}}} \right|^{4} = \frac{\Delta^{2}}{12f_{s}} .16 \sin^{4}\left(\pi \frac{f}{f_{s}}\right)$$

(3-7)

From equation 3-5, the in band power of the second-order modulator is calculated as:

$$N_Q = \int_{-f_b}^{f_b} S_Q(f) df = \frac{\Delta^2}{12} \cdot \frac{\pi^4}{5.OSR^5}$$

(3-8)

Equation. 3-8 shows that doubling the OSR leads to decrease of 15dB/octave of the inband noise power.

The DR can be calculated from equation.3-6 as:

$$DR = 10\log\left[\frac{15.OSR^5}{2\pi^4}\right] = 50\log OSR - 11.1354$$

(3-9)

# 3.3 Cascade ∑∆ Modulator using Half Delay Integrators

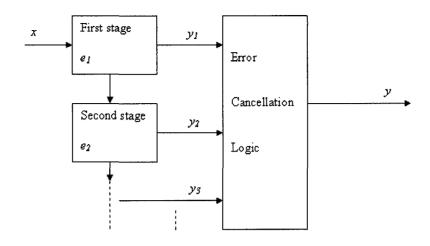

To avoid the instability problem of higher order single-loop modulator, cascade architecture could be an alternative. Figure 3-4 shows a block diagram of a cascaded  $\Sigma\Delta$  modulator. It uses combinations of inherently stable first and second-order  $\Sigma\Delta$  modulators to achieve higher-order noise shaping. Outputs from all stages pass through a digital error cancellation logic to cancel the quantization errors except for that of the last stage.

Figure 3-4. Block diagram of a cascaded  $\sum \Delta$  modulator

Figure 3-5. Cascaded 2-1  $\Sigma\Delta$  modulator with half delay integrators

It is also possible to implement cascade topologies using half-delay. Figure 3-5 shows a cascade 2-1 topology with half delay integrators. Linear analysis of these structures allows expressing the output signal as a combination of the input signal and the quantization noise of the last stage [43].

$$Y(z) = z^{-\frac{5}{2}}X(z) + \frac{1}{c_1}(1 - z^{-1})^3 E_2(z)$$

(3-10)

We can see that the output of this cascaded modulator is a third-order noise shaping. The in-band noise power is calculated by using a method similar to equation 3-5.

$$N_{Q} = \int_{-f_{b}}^{f_{b}} S_{Q}(f) df = \frac{\Delta^{2}}{12} \cdot \frac{\pi^{6}}{7.c_{1}^{2} \cdot OSR^{7}}$$

(3-11)

Accordingly, the DR for the 2-1 cascade structure is calculated to be:

$$DR(dB) = 10\log\left[\frac{(\Delta/2)^2}{2P_Q}\right] = 10\log\left(\frac{21.c_1.OSR^7}{2\pi^6}\right)$$

(3-12)

Equation 3-12 shows that the DR increases by 21dB for every doubling of the OSR. It is clear that the scaling coefficient c1 tend to reduce the DR.

Similarly, a stable higher-order multi-stage  $\Sigma\Delta$  modulator can be obtained. In [47] a 2-1-1 fourth-order cascaded  $\Sigma\Delta$  modulator can be realized with an OSR of 24 with 15 bits resolution. It can be concluded that the noise shaping of a cascaded architecture is comparable to, or even better than that of a single-stage modulator whose order is the sum of all the orders in the cascade.

#### 3.4 Multibit Topology

The cascade architecture can be combined with multibit DAC converters to improve DR further. For example, a 2-1 cascade with a 3-bit DAC converter in the second stage achieves 12-bit resolution with an OSR of 24 and 2.1 MS/s Nyquist rate [48]. However, multibit DAC converter is constrained by linearity problem so calibration techniques are often needed to make the modulator designed works well. The common way to ease the linearity requirements is only using multibit DAC converter at the last stage rather than at the overall modulator input as shown in [48].

# 3.5 Topology Selection

For audio applications, both single-loop and cascade structures are published [27] [41] [49] [50] [51]. In comparing the single loop topologies with cascaded topologies, generally the former are always much worse than the later in term of PSNR. Therefore, if the main goal is high resolution, the cascaded topology offers a much better solution than single loop topologies. This, however, comes at the cost of much higher sensitivity to non-idealities of the building blocks [52]. Although cascade topology offers higher SNR and maximizes the input range, the SO technique do not make use of the maximum input range. This is because SO technique, only eliminate the need for rail-to-rail switching operation at the output of the integrator, however, the input switch for the input signal path remains, and it could be implemented as a single switch with limited signal range as will be explained in details in Chapter 5.

Single-loop architecture, as compared to cascade, is relatively insensitive to component mismatches. As an example, a fourth-order interpolative topology can tolerate up to 5% mismatch in its coefficients [53]. In contrast, a 2-2-cascade modulator requires about 1% between the analog and digital inter-stage gains to achieve 14-bit performance. For a second-order modulator, variation of  $\pm 20\%$  in the gain of the first integrator has only a minor impact on the modulator's performance. This gain tolerance translates into tolerance for incomplete settling of the integrator outputs as long as the settling process is linear [40].

If the second-order modulator is used to implement a  $\sum \Delta$  modulator of 16 bit resolution, the OSR needs to be 256 for the hearing aids application with a signal bandwidth of 16 KHz, the sampling rate ( $f_s$ ) needed is 8.2 MHz. This frequency can be realized with 0.18  $\mu$ m CMOS technology that is used to implement this work. Drawback for using such frequency is the need for higher SR and clock jitter requirements. With the help of the behavior simulation that consider non-idealities, SR can be estimated and a decision can be made if the figure is practical. Dynamic power dissipation doubles for every doubling of the sampling frequency, however if SO  $\sum \Delta$  modulator is used, the duty cycle is 50% as will be explained in Chapter 7.

This design is exploring the possibly of using SO technique to implement a SO  $\Sigma\Delta$  modulators using the latest IC technology with specified resolution and power

consumption requirement for a 16 bit hearing aid application with a bandwidth of 16 KHz. It was suggested in [40] that an ideal second-order  $\Sigma\Delta$  modulator combined with oversampling ratio of 256 can be employed to realize a 16 dB resolution A/D converter. This discussion suggests that second-order single-loop architecture is favorable for this design, due to the inherent stability, simplicity and compatibility with SO technique for reduced power consumption and the constraint of the reduced input signal range.

Table 3-2 Non-idealities of the fundamental basic blocks

| Basic Block Clock |            | Non-ideality Jitter | Consequences  Jitter noise                               |  |

|-------------------|------------|---------------------|----------------------------------------------------------|--|

|                   |            |                     |                                                          |  |

| SC Integrator     |            | Thermal noise       |                                                          |  |

|                   | Op-Amp     | DC gain             | Increases in quantization noise and harmonic distortion. |  |

|                   |            | BW and SR           | Incomplete settling noise and harmonic distortion        |  |

|                   |            | Saturation          | Overloading and harmonic distortion                      |  |

|                   | Capacitors | Mismatching         | Increase in quantization noise and harmonic distortion   |  |

| Comparator        |            | Hysteresis, Offset  | Quantization noise increase                              |  |

### 3.6 ΣΔ Modulators Non-Idealities

Table 3-2 compiles the fundamental basic blocks and the non-idealities considered.

#### 3.7 Clock Jitter Model

The effect of clock jitter, on a SC  $\Sigma\Delta$  modulator can be calculated based on the complete charge transfers during each of the clock phases. Once the analog signal has been sampled, the circuit is a sampled data system where variations of the clock period have no direct effect on the circuit performance. Therefore, the effect of clock jitter on the SC circuit is completely described by computing its effect on the sampling of the input signal. This means also that the effect of clock jitter on a  $\Sigma\Delta$  modulator is independent of the structure or order of the modulator.

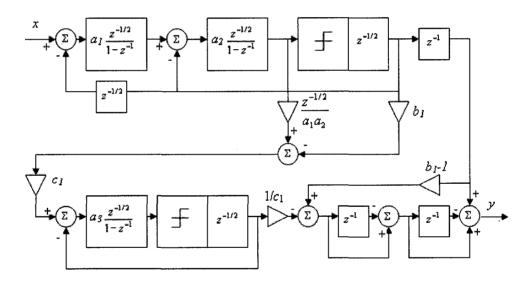

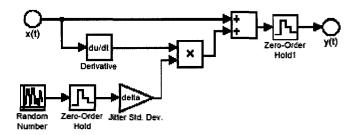

Figure 3-6. Modeling a random sampling jitter

Clock jitter results in a non-uniform sampling and increases the total error power in the quantizer output. The magnitude of this error is a function of both the statistical properties of the jitter and the input signal to the converter. The error introduced when a sinusoidal signal with amplitude A and frequency  $f_{in}$  is sampled at an instant, which is in error, by an amount  $\delta$  is given by:

$$x(t+\delta)-x(t)\approx 2\pi f_{in}\delta A\cos(2\pi f_{in}t)=\delta\frac{d}{dt}x(t)$$

(3-13)

This effect can be simulated with SIMULINK by using the model shown in Figure 3-6, which implements equation 3-13. Here, it is assumed that the sampling uncertainty  $\delta$  is gaussian random process with "delta" standard deviation. Whether oversampling is helpful in reducing the error introduced by the jitter depends on the nature of the jitter. The jitter is assumed to be white, so the resultant error has uniform power spectral from 0 to  $f_s/2$ , with a total power of  $(2\pi f_{in} deltaA)^2/2$ . In this case, the total error power will be reduced by the oversampling ratio [54].

# 3.8 Integrator Noise Model

While the performance of the theoretical  $\sum \Delta$  modulator is only determined by the in-band quantization noise suppression, the physical implementation of the system with solid-state devices has to deal with other noise sources as well. The main additional noise sources of a silicon implementation are thermal noise and flicker (1/f) noise.

The circuit noise to be dealt with in a  $\sum \Delta$  modulator is the noise injected into the input summing node of the first integrator, since it is added directly to the input signal and appears in the output spectrum without any filtering. White noises from the rest of the integrators are attenuated by different powers of the oversampling ratio, depending on the position of the integrator, and can be neglected.

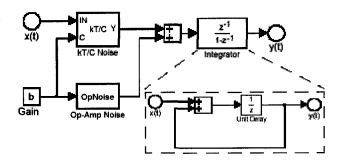

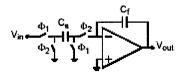

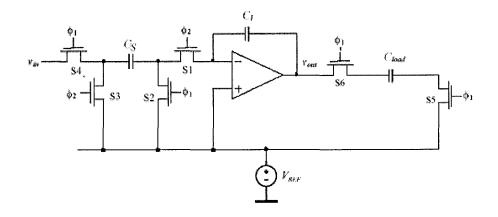

The circuit thermal noise generated in an integrator has two main origins, the white noise due to the resistance of the MOS switches and the op-amp noise of the input stage. These noise sources originate a broadband and sampled noise component at the output of the integrator. These effects can be successfully simulated with SIMULINK using the model of a "noisy" integrator shown in Figure 3-7, where the coefficient b represents the integrator gain, which, referring to the schematic of a single-ended SC integrator shown in Figure 3-8, is equal to  $C_s/C_f$ . Each noise source and its relevant model will be described in the following sub-sections.

Figure 3-7. Noisy integrator model

Figure 3-8. Single-ended SC integrator

Figure 3-9. Modeling thermal noise (KT/C block)

#### 3.8.1 Switch Thermal Noise (KT/C) Model

A critical source of noise in the system is the KT/C noise injected into the first stage integrator of the modulator. As a result, the input capacitor must be large enough to counter the additive noise effect that results. Therefore the first key parameter is the input sampling capacitor of the first integrator (C<sub>s</sub>).

Thermal noise is caused by the random fluctuations of carriers due to thermal energy and presents even at equilibrium. Thermal noise has a white spectrum and wide band limited only by the time constant of the SCs or the bandwidths of the op-amps. Therefore, it must be taken into account for both the switches and the op-amps in the SC circuits. For instant, the sampling capacitor Cs in the single-ended SC integrator shown in Figure 3-8, is in series with a switch, with finite resistance R<sub>on</sub> that periodically opens, sampling a noisy voltage onto the capacitor. The switch thermal noise voltage e<sub>T</sub> (usually called KT/C noise) can be found by evaluating the integral [27]:

$$e_T^2 = \int_0^\infty \frac{4KTR_{on}}{1 + (2\pi f R_{on} C_s)^2} df = \frac{kT}{C_s}$$

(3-14)

Where K is the Boltzman constant and T is the absolute temperature The switch thermal noise voltage  $e_T$  is superimposed to the input voltage x(t) leading to:

$$y(t) = \left[x(t) + e_t(t)\right]b = \left[x(t) + \sqrt{\frac{kT}{bC_f}}n(t)\right]b$$

(3-15)

30

Where n(t) denotes a gaussian random process with unity standard deviation and b is the integrator gain expressed as:

$$b = C_s/C_f$$

Equation (3-15) is implemented by the model shown Figure 3-9

Since the noise is aliased in the band from 0 to  $f_s/2$ , its final spectrum is white with a spectral density:

$$S(f) = \frac{2kT}{f_s C_s} \tag{3-16}$$

The first integrator will have two switched input capacitor, one carrying the signal and the other providing the feedback from the modulator output, each of them contributing to the total noise power.

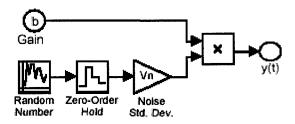

#### 3.8.2 Op-Amp Noise Model

Figure 3-10 shows the model used to simulate the effect of the op-amp noise. Here  $V_n$  represents the total RMS noise voltage referred to the op-amp input. Flicker (1/f) noise, wide-band thermal noise and dc offset, contribute to this value. The total op-amp noise power  $V_n^2$  can be evaluated, through circuit simulation, on the circuit of Figure 3-8 during  $\Phi_2$ , by adding the noise contribution of all the devices referred to the op-amp input and integrating the resulting value over the whole frequency spectrum.

Figure 3-10. Op-amp noise model

Figure 3-11. Real integrator model

## 3.9 Integrator Non-Idealities Model

The op-amp is the most critical component of the modulator, as its non-idealities causes an incomplete transfer of charge, leading to non-linearities. Key parameters that govern its behaviour are the noise, finite gain, finite bandwidth, SR, and saturation voltages. The SIMULINK model of an ideal integrator with unity gain is shown in the inset of Figure 3-2. Its transfer function is expressed as:

$$H(z) = \frac{z^{-1}}{1 - z^{-1}} \tag{3-17}$$

Analog circuit implementation of the integrator deviate from this ideal behaviour due to several non-ideal effects. One of the major causes of performance degradation in  $SC \sum \Delta$  modulators, indeed, is due to incomplete transfer of charge in the SC integrators. This non-ideal effect is a consequence of the op-amp non-idealities, namely finite gain and bandwidth, SR and saturation voltages. These will be considered separately in the following subsections. Figure 3-11 shows the model of the real integrator including all the non-idealities.

#### 3.9.1 DC Gain

The dc gain of the integrator described by equation 3-17 is infinite. In practice, however, the gain is limited by circuit constraints. The consequence of this integrator

leakage is that only a fraction of the previous output of the integrator ( $\alpha$ ) is added to each new input sample. The transfer function of the integrator with leakage becomes:

$$H(z) = \frac{z^{-1}}{1 - \alpha z^{-1}} \tag{3-18}$$

Therefore the dc gain H0 becomes:

$$H_0 = H(0) = \frac{1}{1 - \alpha} \tag{3-19}$$

The limited gain at low frequencies increases the in-band noise.

#### 3.9.2 Bandwidth and Slew Rate

The finite bandwidth and the SR of the op-amp are modeled in Figure 3.11 with a building block placed in front of the integrator, which implements a MATLAB function. The effect of the finite bandwidth and SR are related to each other and may be interpreted as a non-linear gain [55]. With reference to the SC integrator shown in Fig (3.8), the evolution of the output node during the nth integration period (when  $\Phi_2$  is on) is:

$$v_o(t) = v_o(nT - T) + \alpha V_s \left(1 - e^{-\frac{t}{\tau}}\right), \quad nT - \frac{T}{2} < t < nT$$

(3-20)

Where  $\alpha$  is the integrator leakage,  $\tau$  is the time constant of the integrator expressed as:

$$\tau = 1/(2\pi \text{ GBW})$$

Vs is defined as:

$$V_s = V_{in} (nT - T/2)$$

The slope of this curve reaches its maximum value when t = 0, resulting in:

$$\frac{d}{dt}v_o(t)\big|_{\max} = \alpha \frac{V_s}{\tau} \tag{3-21}$$

Two separate cases will be considered:

- 1. The value specified by equation 3-21 is lower than the op-amp SR. In this case there is no SR limitation and the evolution of  $v_0$  fits equation 3-20.

- 2. The value specified by equation 3-21 is larger than SR. In this case, the opamp is in slewing and, therefore, the first part of the temporal evolution of  $v_0$  (for  $t < t_0$ ) is linear with the slope SR. The following equations hold (assuming  $t_0 < T$ ):

$$v_{o}(t) = v_{o}(nT - T) + SRt; \ t \le t_{o}$$

(3-22)

$$v_o(t) = v_o(t_0) + \left(\alpha V_s - SRt_o\right) \left(1 - e^{-\frac{t - t_0}{\tau}}\right); \ t > t_0$$

(3-23)

Imposing the condition for the continuity of the derivatives of equation 3-22 and 3-23 in  $t_0$ , we get:

$$t_0 = \frac{\alpha V_s}{SR} - \tau \tag{3-24}$$

If  $t_0 \ge T$  only Equation.3-22 holds.

The MATLAB function in Figure 3-11 implements the above equations to calculate the value reached by  $v_o(t)$  at time T, which will be different from Vs due to the gain, bandwidth and SR limitations of the op-amp. The SR and bandwidth limitations produce harmonic distortion reducing the total SNDR of the  $\sum \Delta$  modulator. Appendix A.1 shows the MATLAB function.

#### 3.9.3 Saturation

The dynamic of signals in a  $\Sigma\Delta$  modulator is a major concern. It is therefore important to take into account the saturation levels of the op-amp used. It can simply be done in SIMULINK using the saturation block inside the feedback loop of the integrator, as shown in Figure 3-11

## 3.10 Capacitor Mismatching

One of the main advantages of SC circuits is that high precision can be obtained as the integrator coefficients are realized with capacitor ratios. However, fabrication process still results in capacitor mismatching and causes error to the values of these coefficients [56]. Consequently the quantization noise increases. In [53], it is shown that single-loop  $\Sigma\Delta$  modulator can tolerate this type of error to as large as 5%. This is one of the advantages for selecting single-loop, second-order topology, rather than the cascaded topology.

# 3.11 Comparator

The principle design parameter of a comparator include speed, input offset, input-referred noise, and hysteresis. Owing to its position in a  $\sum \Delta$  modulator, the offset and input-referred noise are subjected to noise shaping by feedback loop so can be neglected. For digital-audio design, speed is also not a problem. The sensitivity of an A/D converter performance to comparator hysteresis can be modeled quite well by an additively white noise. This noise also undergoes the same spectral noise shaping as the quantization noise. Thus the design requirement for the comparator is usually quite relaxed.

## 3.12 Behavioral Simulation for the Ideal ∑∆ modulator

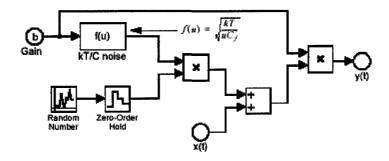

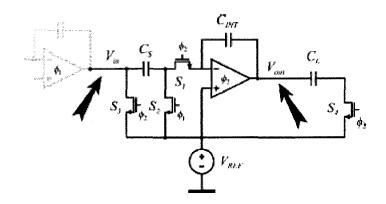

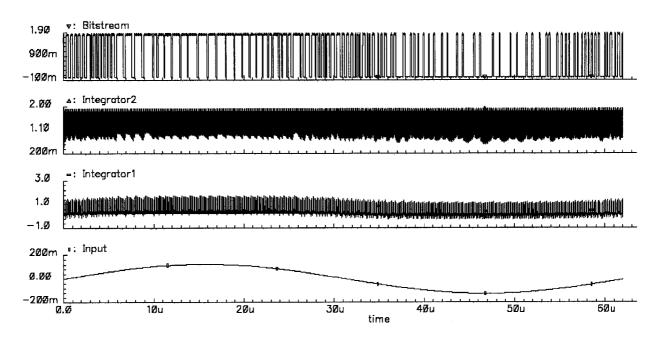

Behavioral simulation can be accomplished using SIMULINK tool, as it provides a GUI tool so the designer can easily build block diagram, perform simulation, and view the simulation results at each point. The necessary functions and programs can be written in MATLAB to measure the performance of the modulator. Figure 3-12 shows the block diagram of a second-order  $\Sigma\Delta$  modulator that is built in SIMULINK for behavioral simulation. All of the blocks are predefined in SIMULINK and are ideal. These

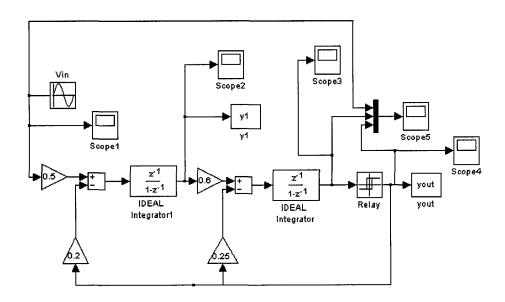

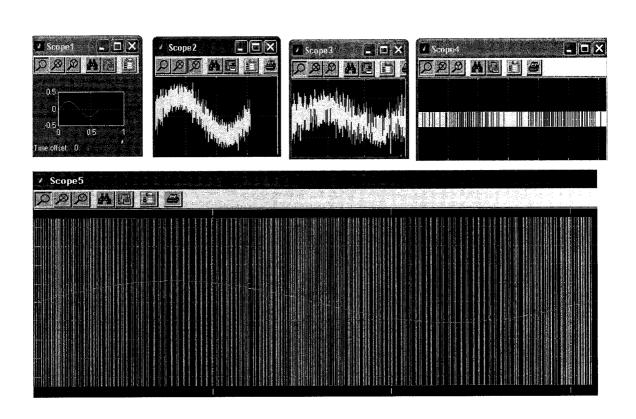

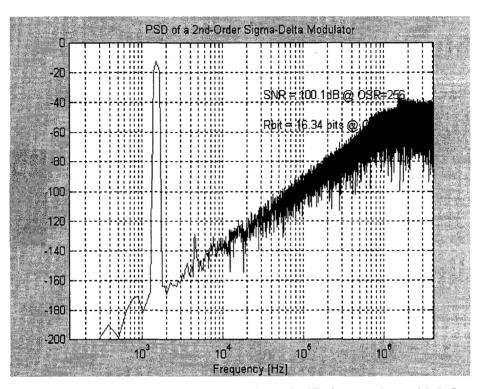

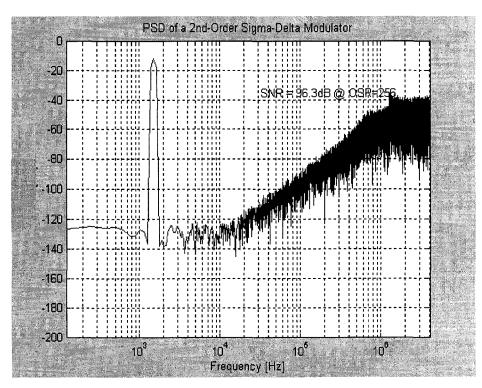

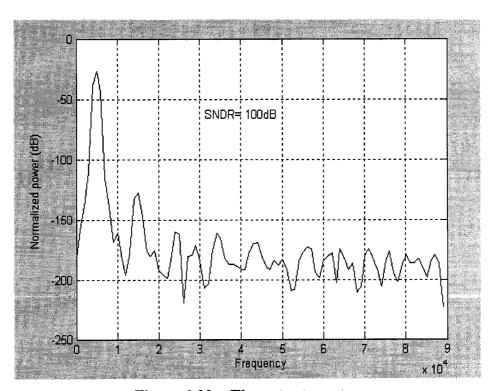

fundamental blocks are the ideal integrator, single-bit quantizer, adders and multipliers. Through adequate connections of these few blocks, a full  $\Sigma\Delta$  modulator can be obtained. Scopes are used to monitor all of the critical points. Figure 3-13 shows the input sinusoidal, the outputs of the integrators and the modulator output superimposed on the input and the second integrator output. Figure 3-14 shows the normalized power spectral density at the output with 0.23 V input sinusoidal signal. By setting the different integrator coefficients and performing simulation, it is possible for the designer to choose the integrator coefficients that maximize the integrator output swing. However, owing to the use of ideal building blocks for the modulator, the simulation results cannot be very accurate and need to be fine-tuned by further behavioral simulation by using the blocks that model non-idealities in Chapter 5.

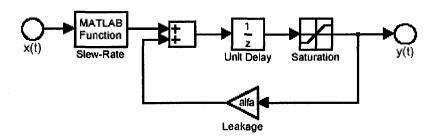

Figure 3-12. SIMULINK model for an ideal second-order  $\sum \Delta$  modulator

Fig. 3-13 SIMULINK simulation scope's results for the input, first and second integrator and the modulator output

Figure 3-14. Simulated output spectra with -2 dB input sinusoidal for the ideal second-order modulator

Figure 3-15. SIMULINK model for the non-ideal second-order  $\sum \Delta$  modulator

### 3.13 Behavioural Simulation for the Non-Ideal $\sum \Delta$ modulator

The behavior of  $\Sigma\Delta$  modulator can be affected by errors. The integrator is a fundamental block within a  $\Sigma\Delta$  modulator. Its non-idealities, however, largely affects the operation of the modulator. The non-ideality for the first integrator only is considered, since their effects are not attenuated by the noise shaping. A single-bit quantizer is implemented with a comparator, which is a perfectly linear block and does not introduce any non-linearity error. Though linear block, comparators are subject to non-idealities such as input offset, comparator hysteresis, etc. However, due to its position in the  $\Sigma\Delta$  modulators, the impact of the comparator non-idealities in the operation of  $\Sigma\Delta$  modulators is much smaller than of integrators as these errors are subject to the same treatment as quantization noise.