# University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

1992

# Implementation of a high performance floating point unit multiplier.

Biniam. Mesfin *University of Windsor*

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### Recommended Citation

Mesfin, Biniam., "Implementation of a high performance floating point unit multiplier." (1992). *Electronic Theses and Dissertations*. Paper 2388.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

335, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre rélérence

Our file Notre rélérence

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# **Canadä**

# IMPLEMENTATION OF A HIGH PERFORMANCE FLOATING POINT UNIT MULTIPLIER

by

#### Biniam Mesfin

#### A Thesis

Submitted to the Faculty of Graduate Studies through the

Department of Electrical Engineering in Partial Fulfilment

of the Requirements for the Degree of

Master of Applied Science at the

University of Windsor

Windsor, Ontario, Canada May, 1992

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our tile Notre rélérence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive Bibliothèque permettant à la nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette à la disposition des thèse personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-78864-X

All R 12 30

# Biniam Mesfin 1992

© All Rights Reserved

#### **ABSTRACT**

This work presents a new fast and efficient algorithm for a floating point multiplier that adheres to the IEEE 754 standard and also investigates its VLSI implementation. As a verification tool, VHDL is used to simulate the hardware model of the new floating point multiplier algorithm. In addition this work describes and compares several parallel multiplier architectures including a new parallel multiplier architecture which is both time optimal and regular in structure. This new multiplier architecture will be used as part for the new floating point multiplier algorithm. Finally the BICMOS implementation of the new multiplier architecture is discussed.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere thanks and appreciation to Dr. G. A. Jullien for his tremendous support and guidance throughout my undergraduate and post-graduate program. My thanks are to Dr. M. Ahmadi for his encouragement and indispensable advice. I thank Dr. N. Wigley for kindly consenting to be the external examiner.

I would also like to express my special thanks to Dr. Wang for his opinions and ideas. In addition, I would also like to thank Mr. B. Erickson, Mr. M. Jovanovic, Mr. S. Bizzan, Mrs. A. Sarkar and Mr. Chan Wa Lai for their inexpressible support.

Thanks must also go to my parents for their love and care, my sisters and brothers for their patience, understanding and encouragement throughout the progress of my thesis.

Finally, I would like to thank all those people not mentioned here in particular the VLSI research group members, who aided me to complete my post-graduate program.

# TABLE OF CONTENTS

| ABSTRA            | <b>CT</b> iv                                                                                                                                                                                                                          | , |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| ACKNO             | WLEDGEMENTSv                                                                                                                                                                                                                          |   |

| TABLE             | OF CONTENTSvi                                                                                                                                                                                                                         | i |

| LIST OF           | FIGURESx                                                                                                                                                                                                                              |   |

| LIST OF           | TABLESx                                                                                                                                                                                                                               | V |

| Chapter           | 1: Introduction1                                                                                                                                                                                                                      |   |

| 1.1               | Introduction1                                                                                                                                                                                                                         |   |

| 1.2               | Historical Overview Of Floating Point Systems2                                                                                                                                                                                        |   |

| 1.3               | Thesis Organization4                                                                                                                                                                                                                  |   |

|                   |                                                                                                                                                                                                                                       |   |

| Chapter           | 2: IEEE Floating Point Standard5                                                                                                                                                                                                      |   |

| •                 | 2: IEEE Floating Point Standard5 Introduction                                                                                                                                                                                         |   |

| 2.1               | •                                                                                                                                                                                                                                     |   |

| 2.1<br>2.2        | Introduction5                                                                                                                                                                                                                         |   |

| 2.1<br>2.2        | Introduction                                                                                                                                                                                                                          | ı |

| 2.1<br>2.2        | Introduction                                                                                                                                                                                                                          |   |

| 2.1<br>2.2        | Introduction                                                                                                                                                                                                                          |   |

| 2.1<br>2.2        | Introduction       5         Data Formats       5         Precision       6         2.3.1 Single Precision       7         2.3.2 Double Precision       7                                                                             |   |

| 2.1<br>2.2<br>2.3 | Introduction       5         Data Formats       5         Precision       6         2.3.1 Single Precision       7         2.3.2 Double Precision       7         2.3.3 Single Extended       8                                       |   |

| 2.1<br>2.2<br>2.3 | Introduction       5         Data Formats       5         Precision       6         2.3.1 Single Precision       7         2.3.2 Double Precision       7         2.3.3 Single Extended       8         2.3.4 Double Extended       9 | • |

| 2.6.1 NANs                                                     | . 11 |

|----------------------------------------------------------------|------|

| 2.6.2 Infinity                                                 | . 12 |

| 2.6.3 Signed Zero                                              | . 13 |

| 2.6.4 Denormalized Numbers                                     | . 14 |

| 2.7 Rounding                                                   | . 18 |

| Chapter 3: Floating Point Multiplier                           | .23  |

| 3.1 Introduction                                               | 23   |

| 3.2 Hardware Implementation of a Floating Point Multiplier     | 24   |

| 3.3 A Simple Round to Nearest/up Algorithm                     | 26   |

| 3.4 Parallel Addition Schemes                                  | 28   |

| 3.5 Obtaining the IEEE Round to Nearest Result                 | 33   |

| 3.6 Computing the Sticky Bit                                   | 34   |

| 3.6.1 A Simple Method to Compute the Sticky Bit                |      |

| 3.6.2 Computing Sticky Bit From Input Operands                 | 35   |

| 3.7 A New and Efficient Technique for Computing the Sticky Bit | 38   |

| 3.8 A New Technique for Computing the Exponent                 | 39   |

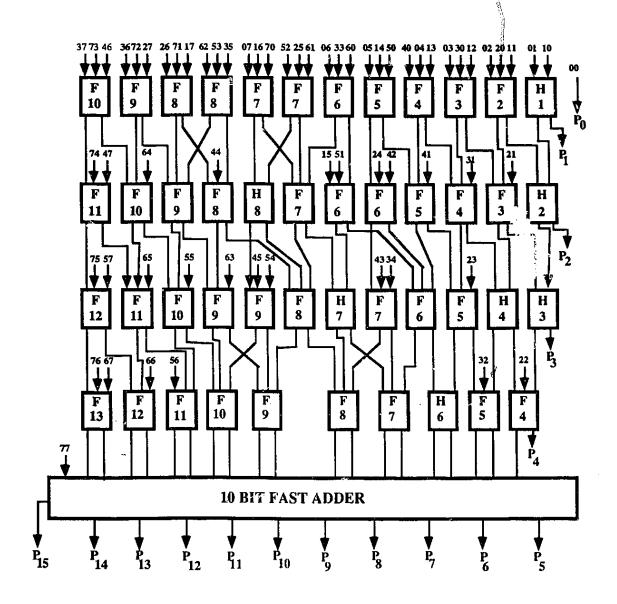

| Chapter 4: Multiplier Architectures                            | 51   |

| 4.1 Introduction                                               | 51   |

| 4.2 Binary Multiplication                                      | 52   |

| 4.3 Array Multipliers                                          | 54   |

| 4.4 Five Bit Counter Multiplier                                | 56   |

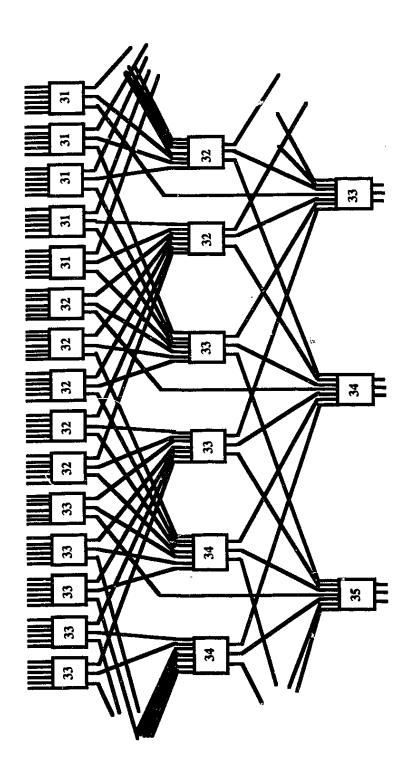

| 4.5 Wallace and Dadda Multipliers                              | 66   |

| 4.6 (4·2) Compressor                                           | 70   |

| 4.7 (7:3) Counter73                                            |

|----------------------------------------------------------------|

| 4.8 New Tree Structure78                                       |

| 4.9 High Speed Adders84                                        |

| 4.9.1 Carry Look Ahead84                                       |

| 4.9.2 Binary Carry Look Ahead84                                |

| 4.9.3 Modified Brent and Kung's Adder86                        |

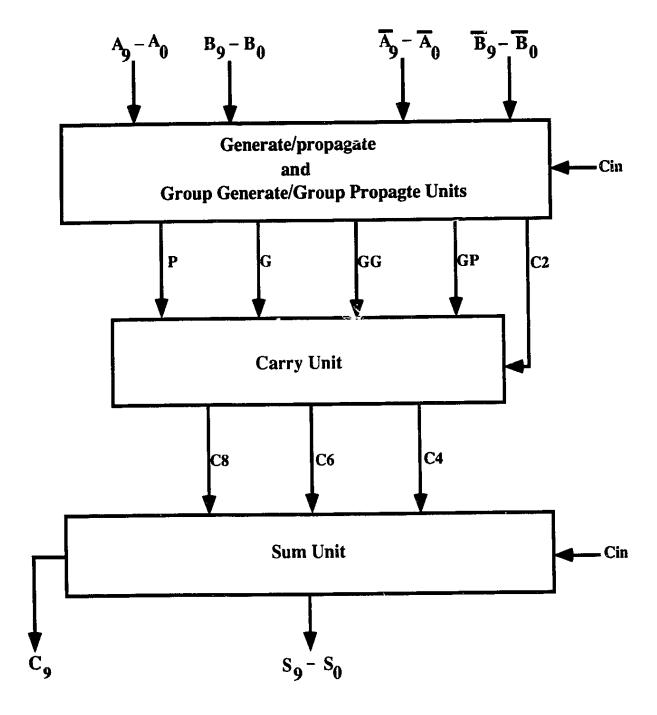

| 4.9.4 A New Adder Structure91                                  |

| 4.10 Implementation                                            |

| Chapter 5: Conclusion and Future Work106                       |

| 5.1 Conclusion106                                              |

| 5.2 Future Work                                                |

| REFERENCES110                                                  |

|                                                                |

| Appendix 1A: Behavioral Model for a floating point             |

| Appendix 1A: Behavioral Model for a floating point  Multiplier |

| Appendix 1A: Behavioral Model for a floating point  Multiplier |

| Appendix 1A: Behavioral Model for a floating point  Multiplier |

| Appendix 1A: Behavioral Model for a floating point  Multiplier |

| Appendix 1D: Architectural Model for Column              |       |

|----------------------------------------------------------|-------|

| Compression Multiplier                                   | 209   |

| Appendix 1E: A Report on the Design and Layout of a 10 - | 225   |

| Bit Adder                                                | . 225 |

| E.1 Introduction                                         | . 226 |

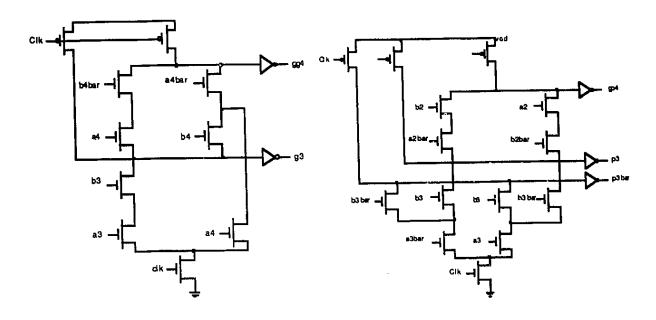

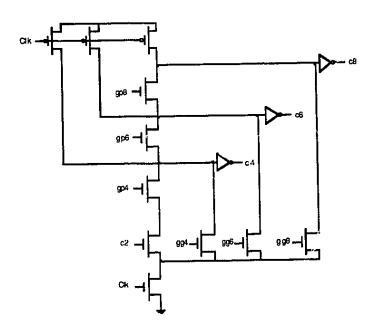

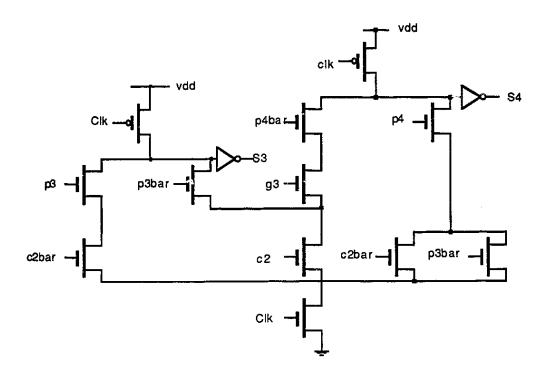

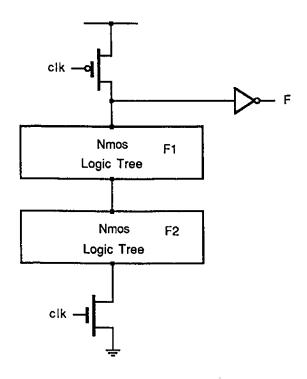

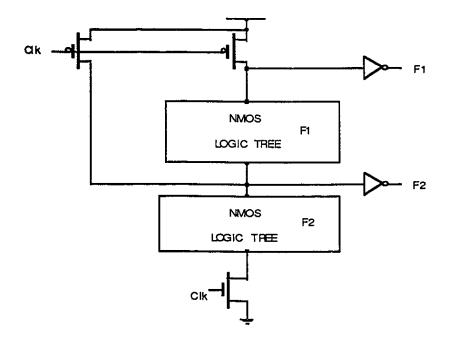

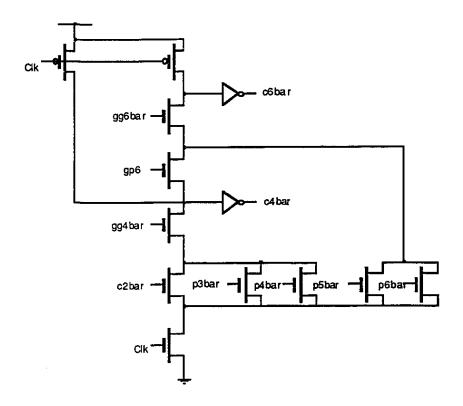

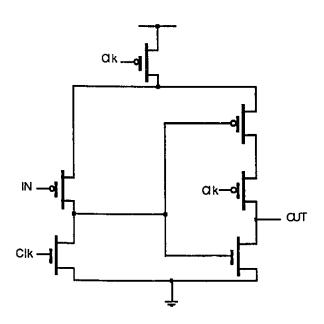

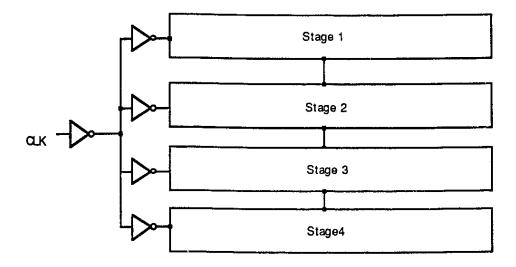

| E.2 Multiple Output Domino Logic                         | . 227 |

| E.3 Description of MODL                                  | . 227 |

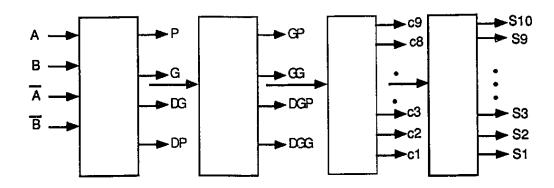

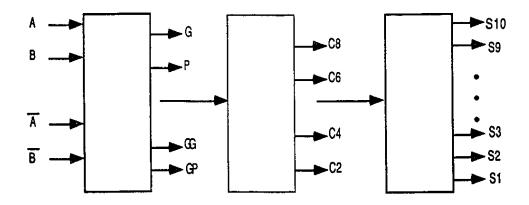

| E.4 10-Bit MODL Adder                                    | . 229 |

| E.5 Clocking Scheme and Distribution                     | . 231 |

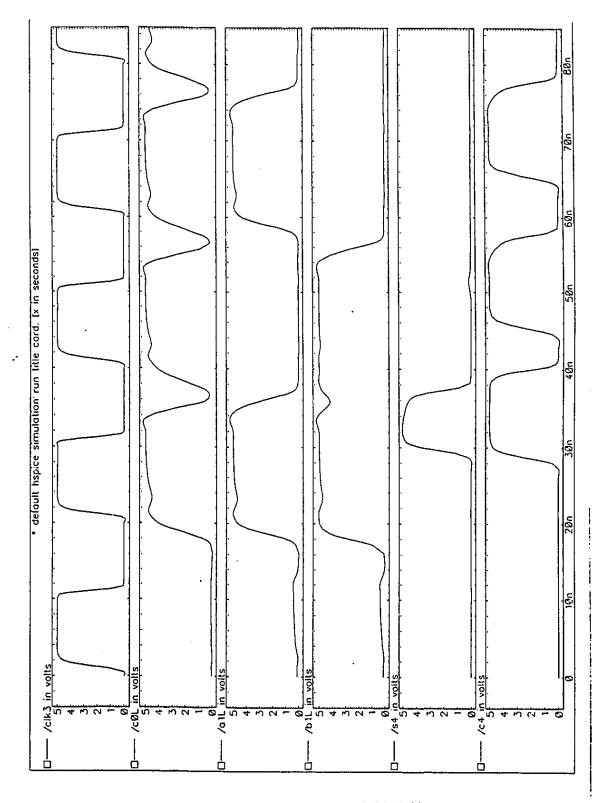

| E.6 Simulation Results                                   | . 233 |

| E.7 Chip Implementation                                  | . 233 |

| E.8 Conclusion                                           | . 242 |

| References                                               | . 242 |

|                                                          |       |

# VITA AUCTORIS

2001 LL 100

# LIST OF FIGURES

| 2. Single Precision Format                                                          |

|-------------------------------------------------------------------------------------|

| 2.2 Double Precision Format                                                         |

| 2.3 Flush to Zero Compared with Gradual Underflow                                   |

| 2.4 Gradual Underflow Error17                                                       |

| 3.1 Floating Point Multiplier Data Path25                                           |

| 3.2 Algorithm 3a Data Flow                                                          |

| 3.3 Bits to be Summed for Correct Round to Nearest Up29                             |

| 3.4 Algorithm 3b Data Flow                                                          |

| 3.5 Algorithm 3c Data Flow                                                          |

| 3.6 L-Bit Restorer35                                                                |

| 3.7 Floating Point Multiplier Data Path which Incorporates Fast Round Techniques 37 |

| 3.8 Summation of Partial Products39                                                 |

| 3.9 Underflow and Overflow Detector                                                 |

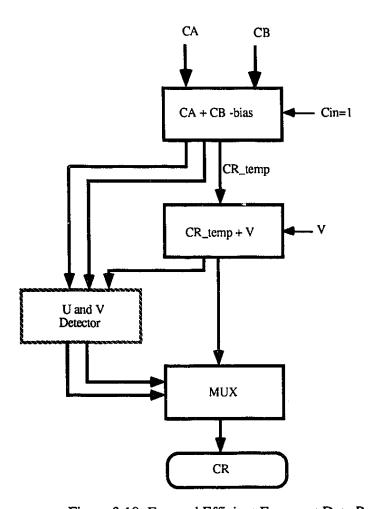

| 3.10 Fast and Efficient Exponent Data Path46                                        |

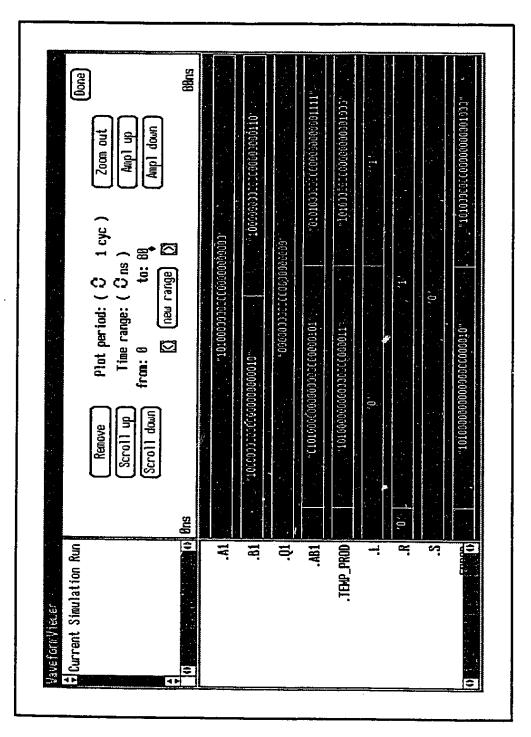

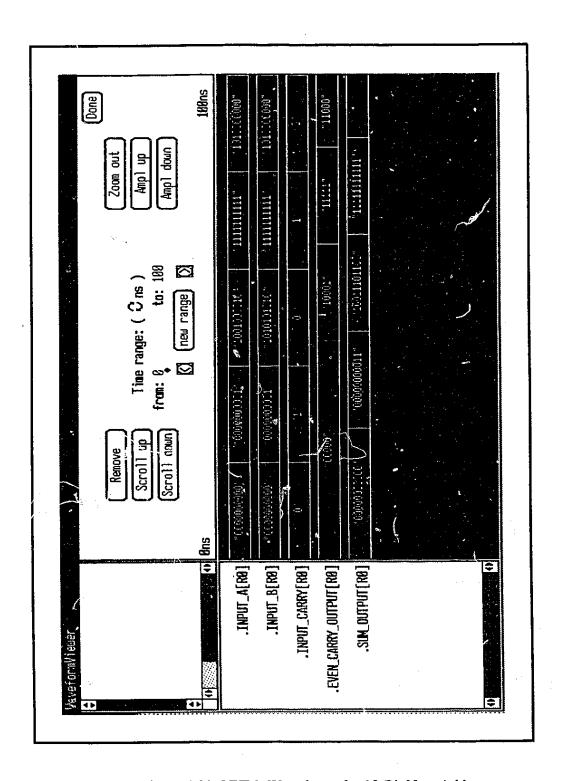

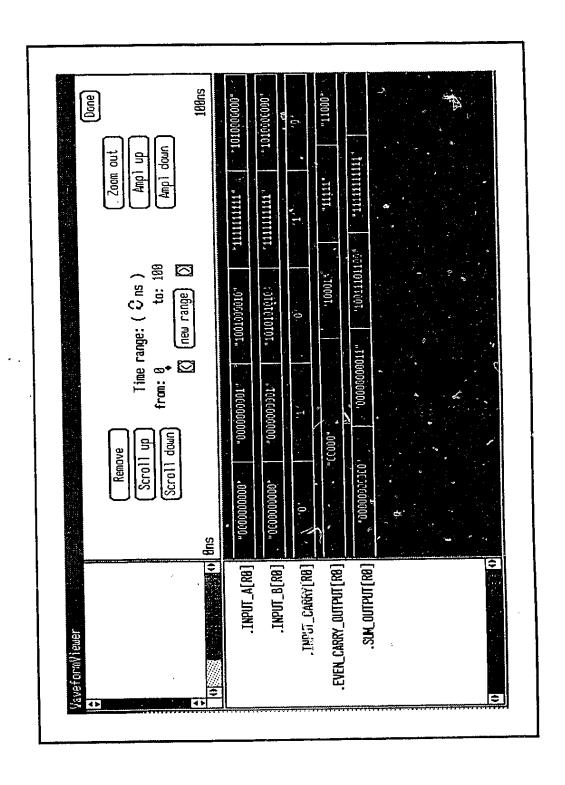

| 3.11 VHDL Waveforms for Exponent Data Path                                          |

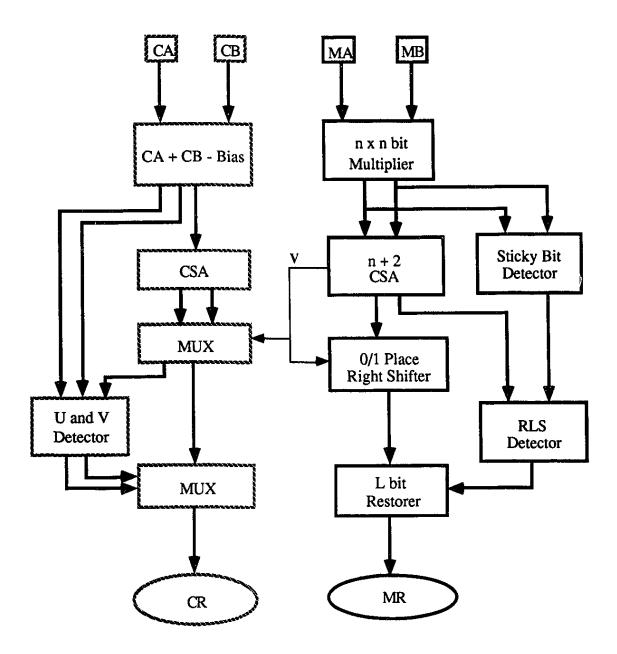

| 3.12 Improved Floating Point Multiplier Data Path                                   |

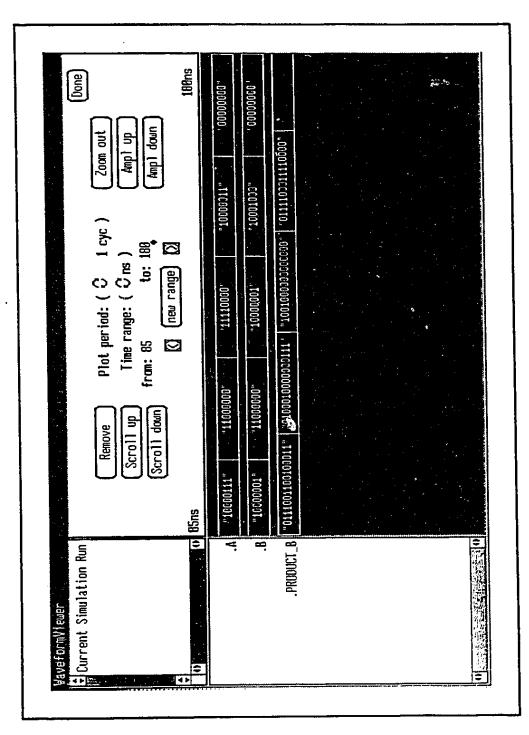

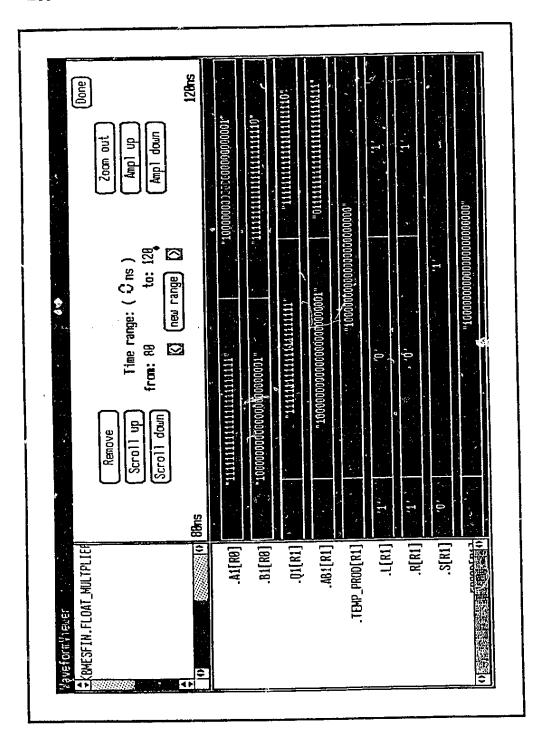

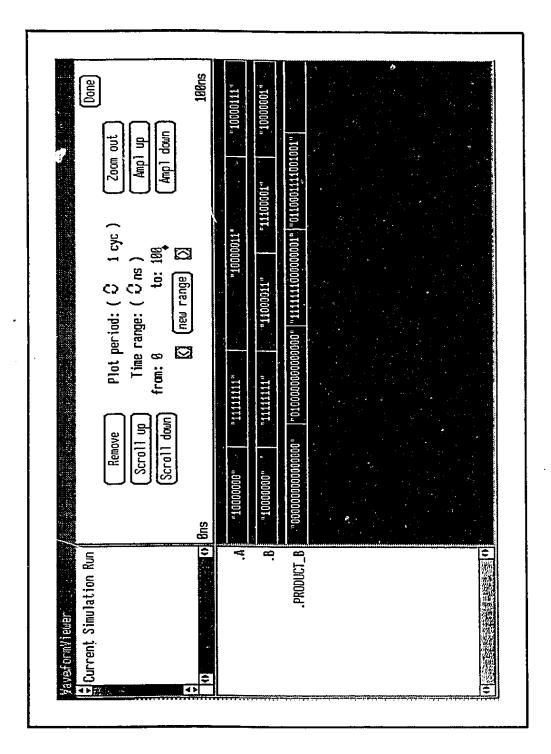

| 3.13 VHDL Waveforms for a Single Precision Floating Point Multiplier49 |

|------------------------------------------------------------------------|

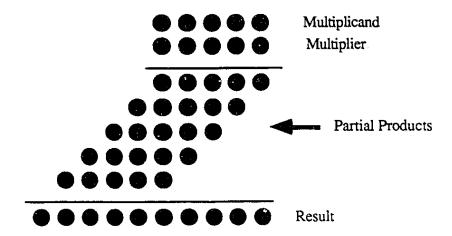

| 4.1 Basic Multiplication Data Flow                                     |

| 4.2 8x8 Bit Linear Array Multiplier                                    |

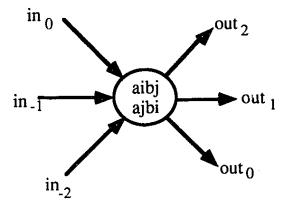

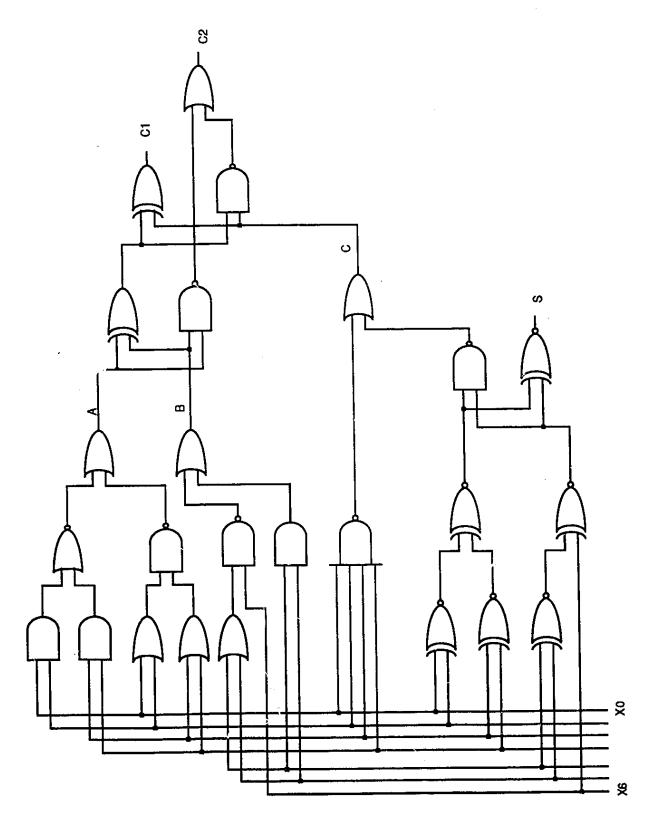

| 4.3 A 5-Bit Counter Cell                                               |

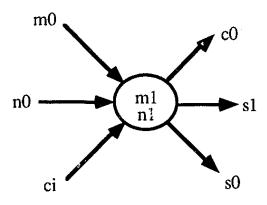

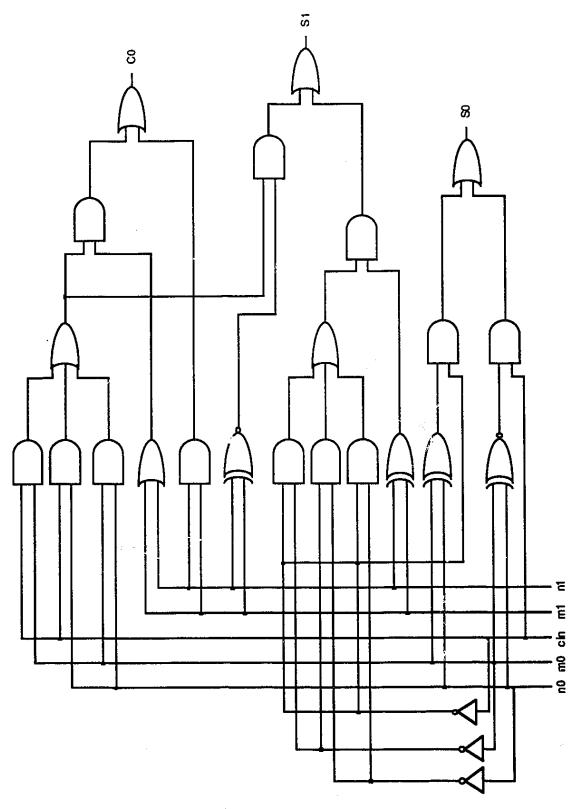

| 4.4 A Two-Bit Full-Adder Cell                                          |

| 4.5 Type_1 Two-Bit Full-Adder59                                        |

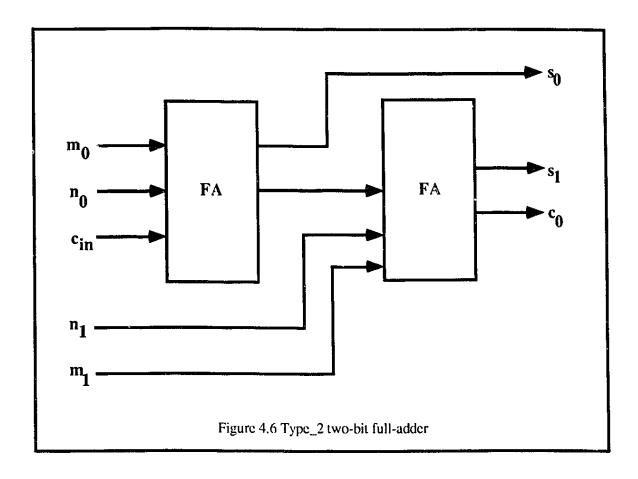

| 4.6 Type_2 Two-Bit Full-Adder                                          |

| 4.7 8x8 Bit Two-Bit Full-Adder Multiplier                              |

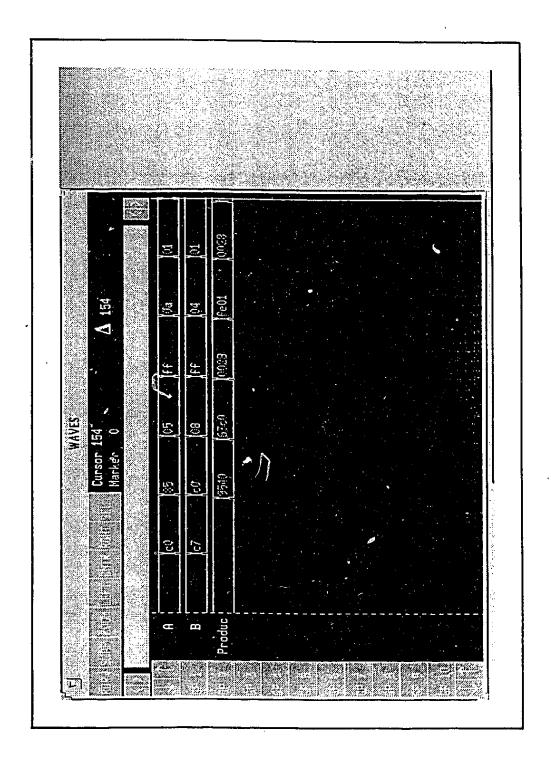

| 4.8a VHDL Waveforms for Type_1 Two-Bit Full-Adder Multiplier           |

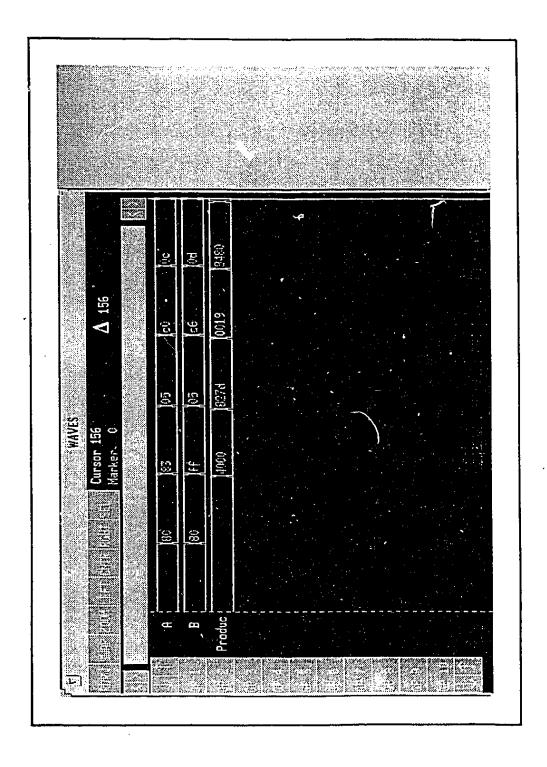

| 4.8a VHDL Waveforms for Type_2 Two-Bit Full-Adder Multiplier63         |

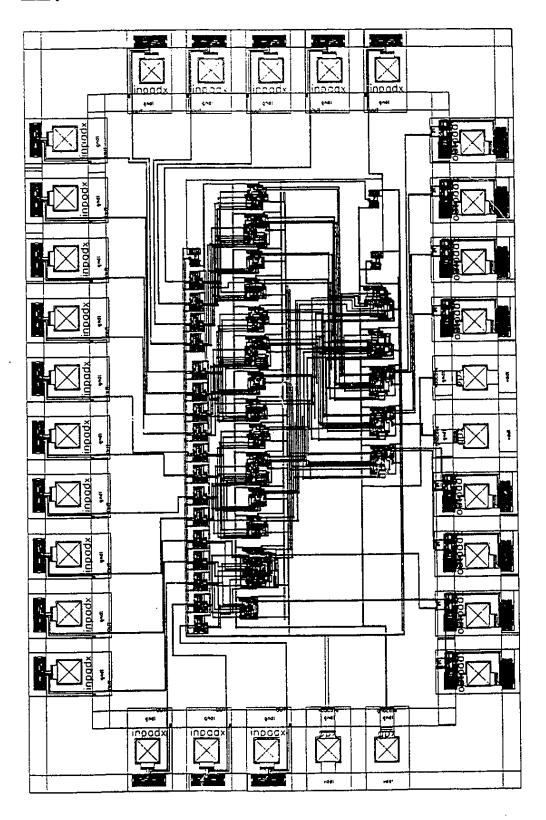

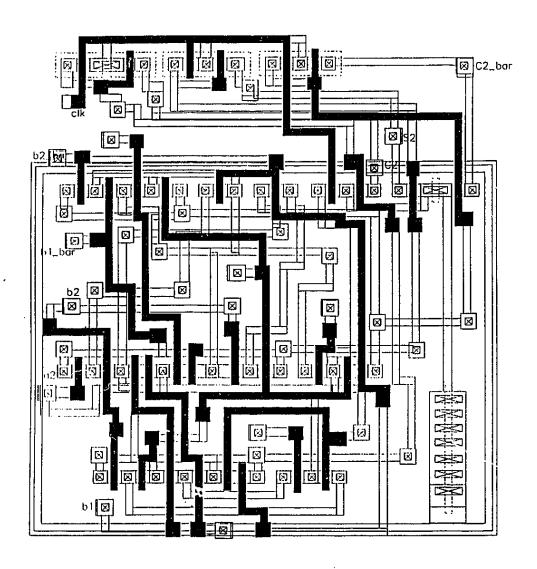

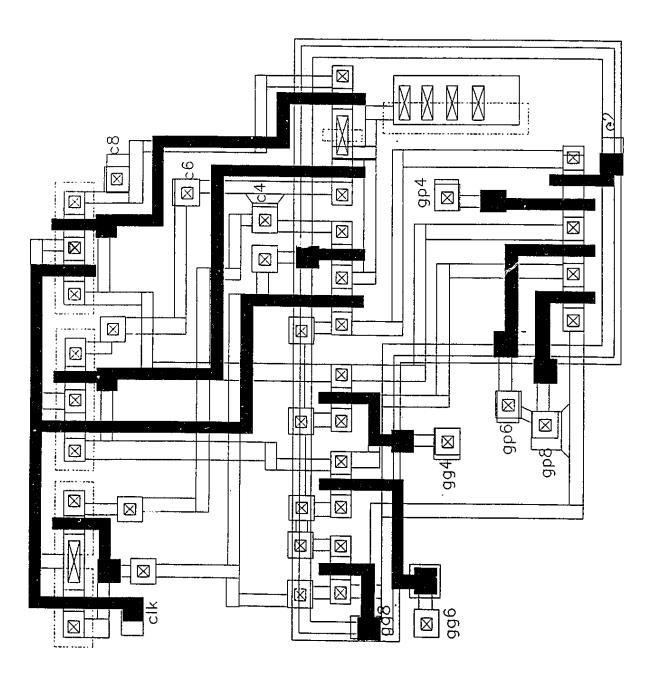

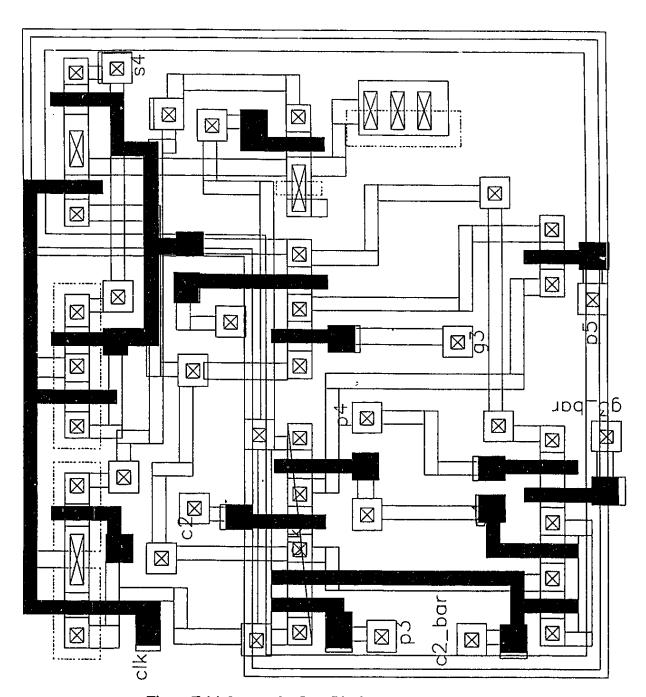

| 4.9a Layout for Type_1 Two-Bit Full-Adder Multiplier64                 |

| 4.9b Layout for Type_2 Two-Bit Full-Adder Multiplier65                 |

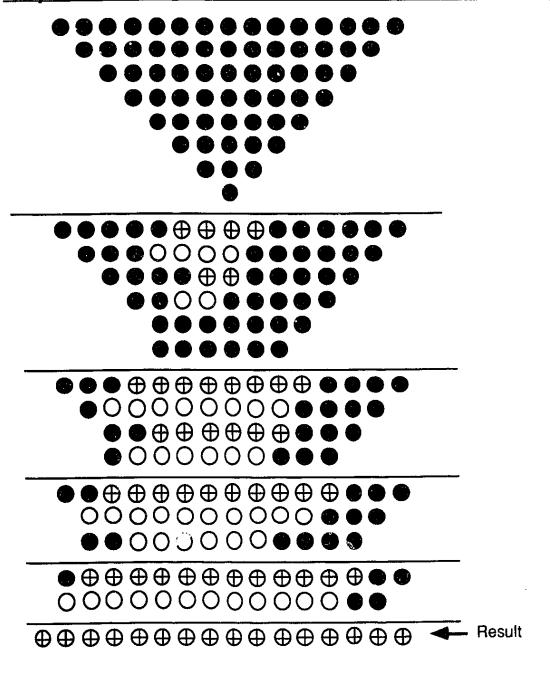

| 4.10 Dadda Algorithm Reduction Scheme for an 8x8 Bit Multiplier        |

| 4.11 Dadda Architecture for an 8x8 Bit Multiplier69                    |

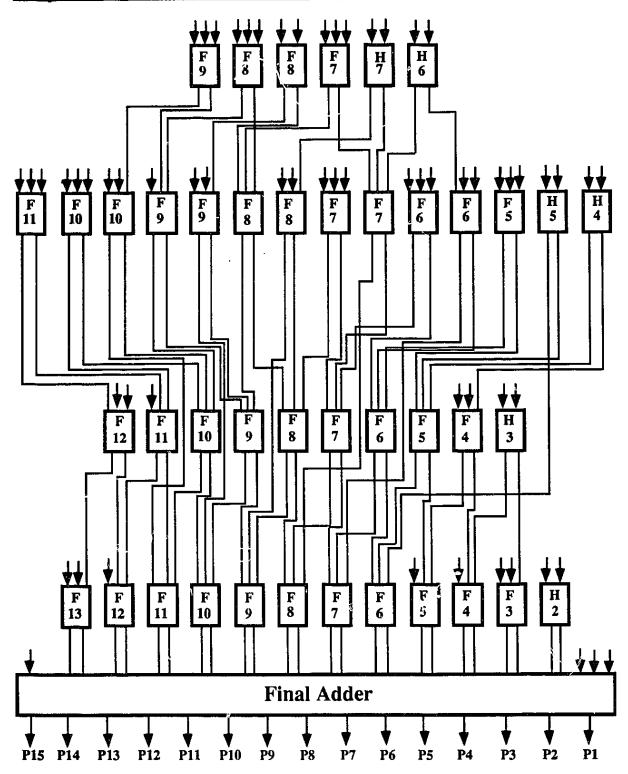

| 4.12a (4:2) Compressor                                                 |

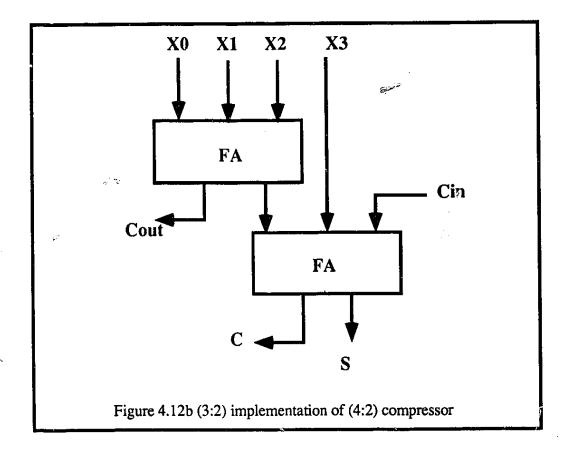

| <b>4.12b (3:2) Implementation of (4:2) Compressor71</b>                |

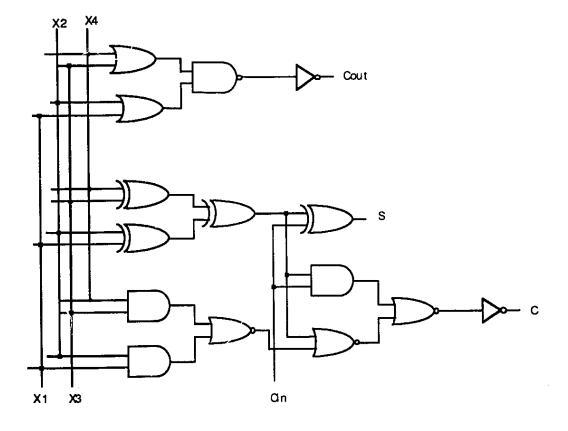

| 4.12c Circuit for (4:2) Compressor                                     |

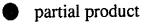

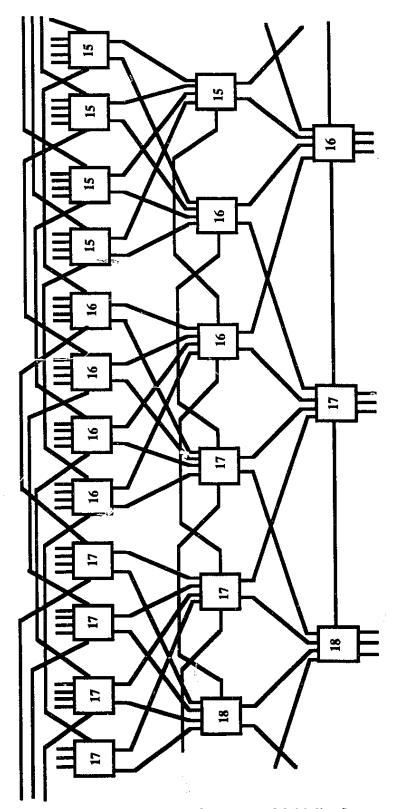

| 4.13 Typical (4:2) Compressor Multiplier Structure                 |

|--------------------------------------------------------------------|

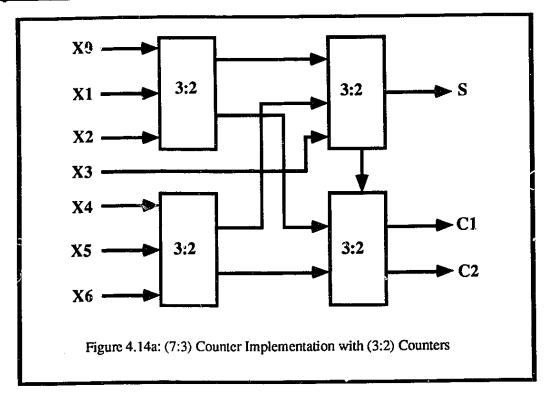

| 4.14a (7:3) Counter Implementation with (3:2) Counters             |

| 4.14b Alternative Implementation of a (7:3) Counter                |

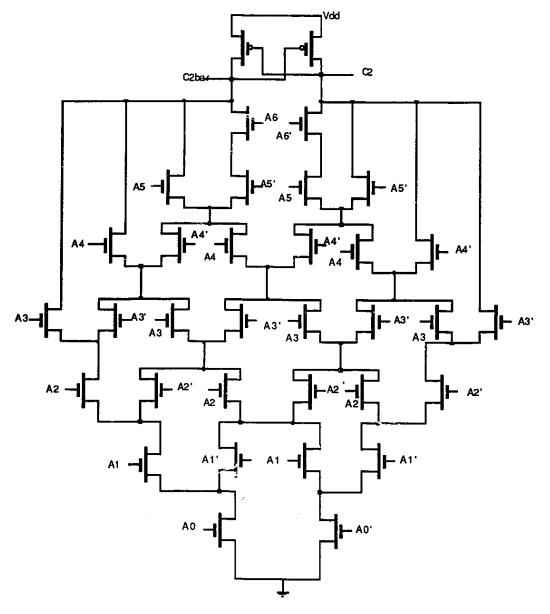

| 4.14c (7:3) Counter Implementation with Folded Transistors         |

| 4.14d Typical (7:3) Counter Multiplier Structure79                 |

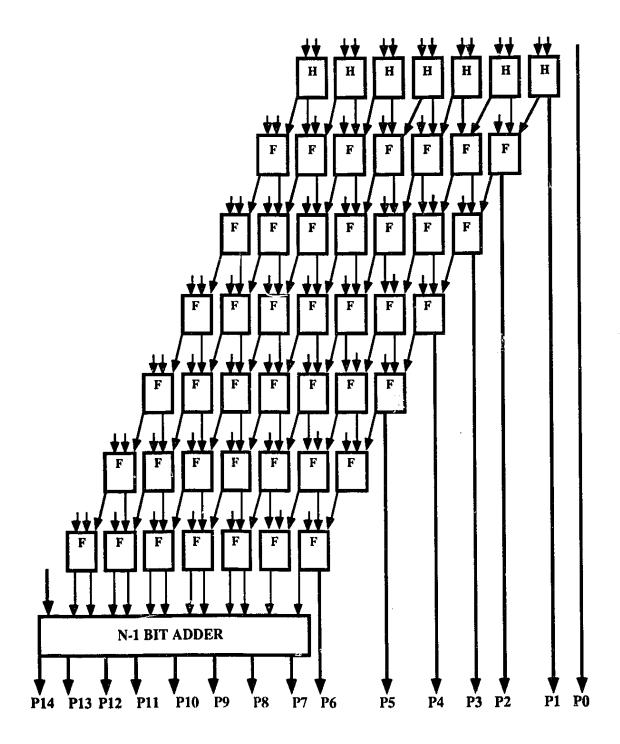

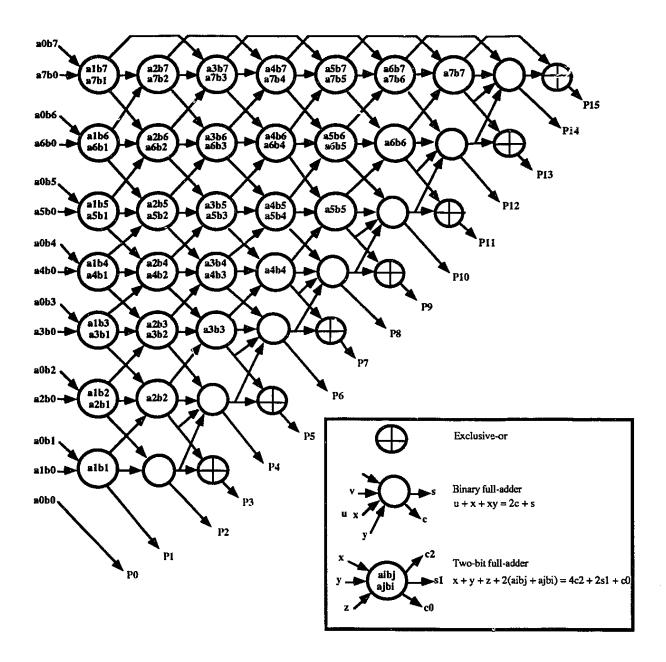

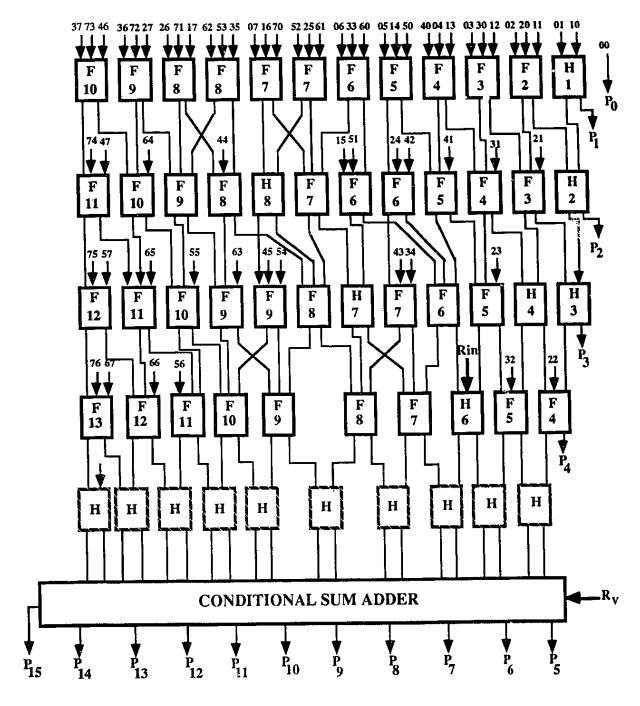

| 4.15 8x8 Bit Column Compression Multiplier80                       |

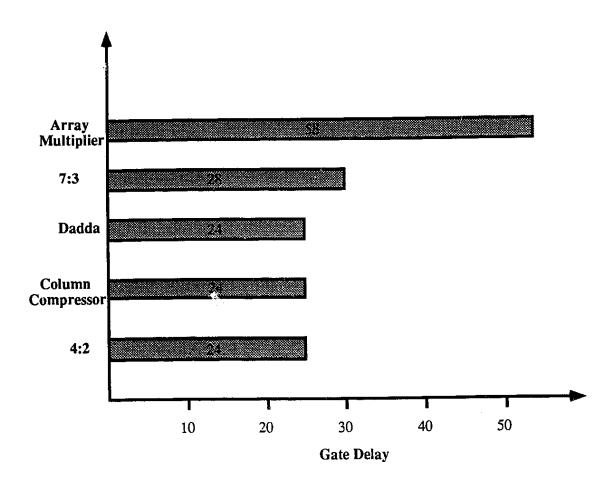

| 4.16 Performance Measure of various 16x16 Bit Multipliers82        |

| 4.17 Organization of a 10-Bit Ripple Adder85                       |

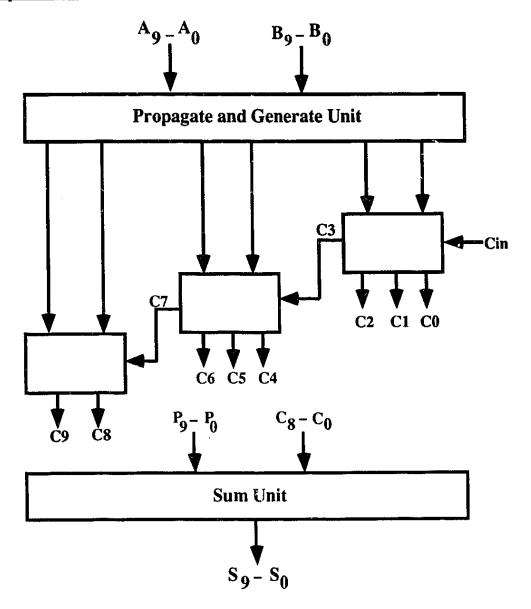

| 4.18 10-Bit Binary Carry Look Ahead87                              |

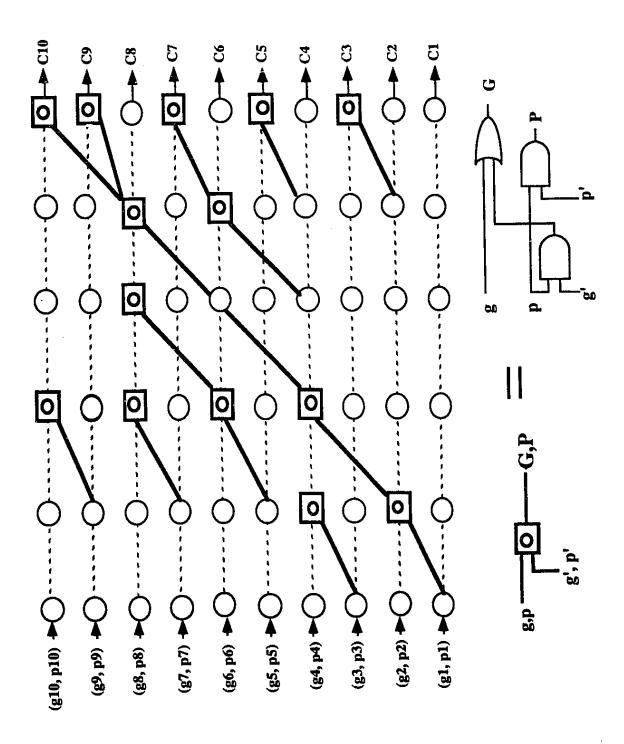

| 4.19 10-Bit Modified Brent and Kung's Adder90                      |

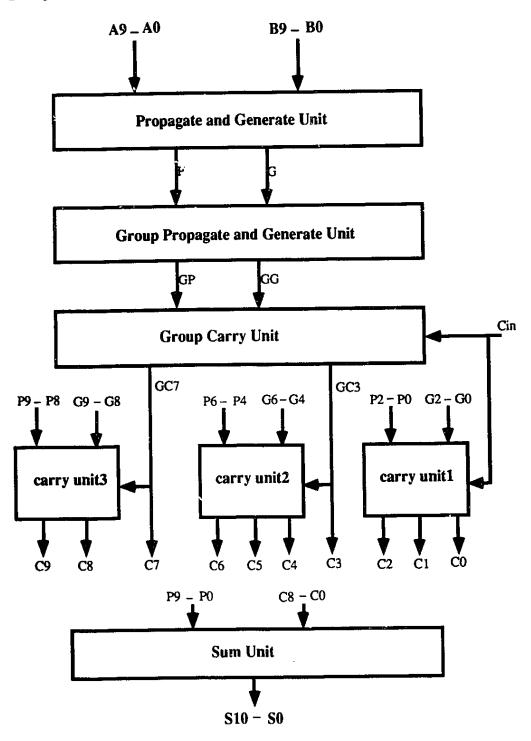

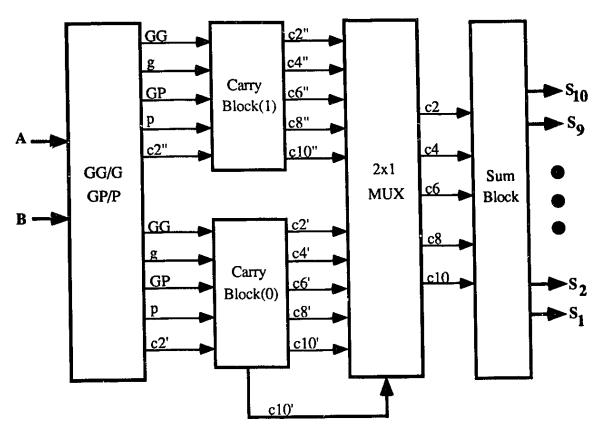

| 4.20 Structure of a 10-Bit New Adder92                             |

| 4.21a MODL gates for Propagate and Generate Terms93                |

| 4.21b MODL gate for the Carry Block93                              |

| 4.21c MODL gate for the Sum Block94                                |

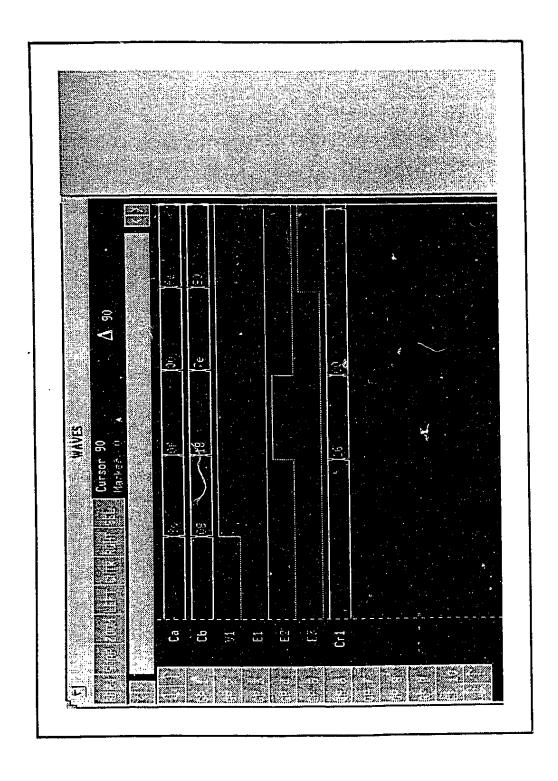

| 4.22 VHDL Waveforms for the 10-Bit New Adder96                     |

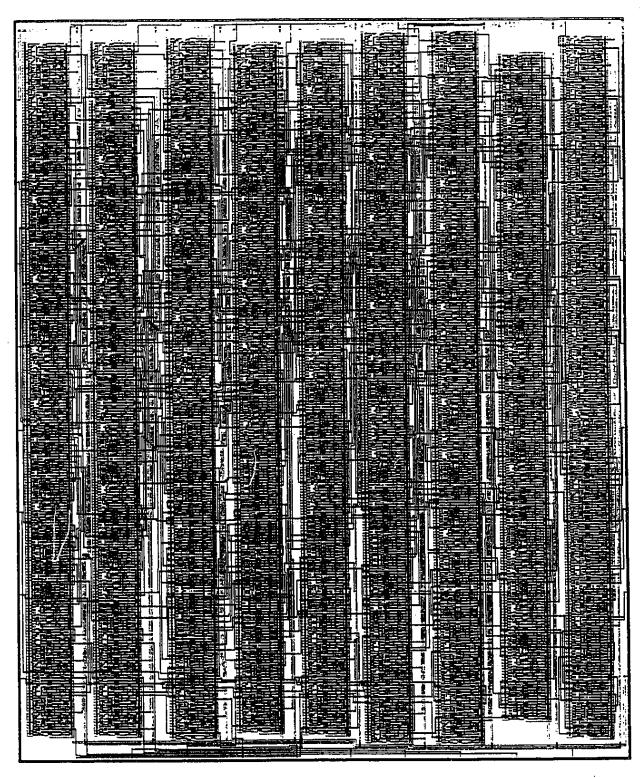

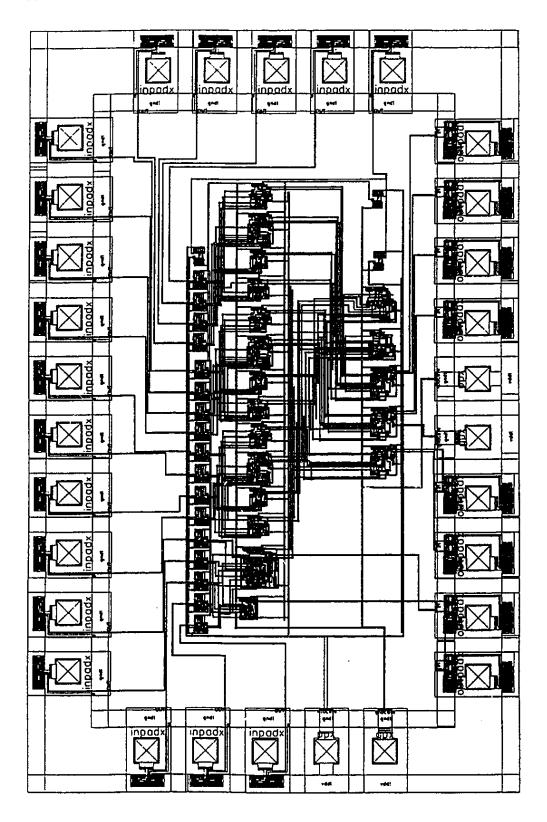

| 4.23 Layout for the 10-Bit New Adder97                             |

| 4.24 VHDL Waveforms for an 8x8 Bit Column Compression Multiplier99 |

| 4.25 Layout for the 3x8 Bit Column Compression Multiplier          |

| 4.26 Mantissa Section for an 8x8 Bit Floating Point Multiplier   |

|------------------------------------------------------------------|

| 4.27 Conditional Sum Adder                                       |

| 1A.1 VHDL Waveforms for a Floating Point Multiplier              |

| 2A.1 VHDL Waveforms for Exponent Data Path                       |

| 2B.1 VHDL Waveforms for the New Adder                            |

| 1C.1 VHDL Waveforms for Type_1 Two-Bit Full-Adder Multiplier 194 |

| 2C.1 VHDL Waveforms for Type_2 Two-Bit Full-Adder Multiplier208  |

| D1.1 VHDL Waveforms for Column Compression Multiplier            |

| E.1 Domino implementation of F with F=F1F2228                    |

| E.2 MODL implementation of the same function                     |

| E.3 Structure of the Original Adder                              |

| E.4 Structure of the Modified Adder229                           |

| E.5 MODL gate for Carry_Bar Generator                            |

| E.6 True Single Phase Latch                                      |

| E.7 Clock Distribution                                           |

| E.8 Simulation Result for the 10-Bit Adder234                    |

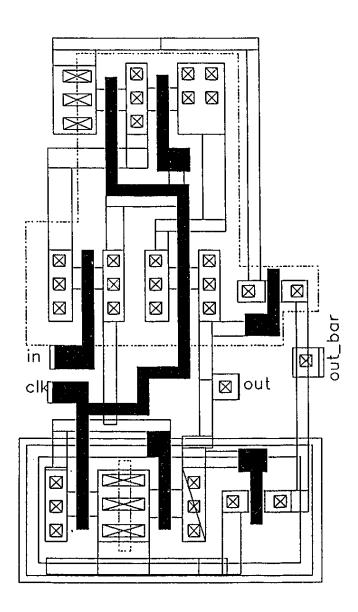

| E.9 Layout for S2 and C2 Block                                   |

| F 10 Layout for True Single Phase Latch 236                      |

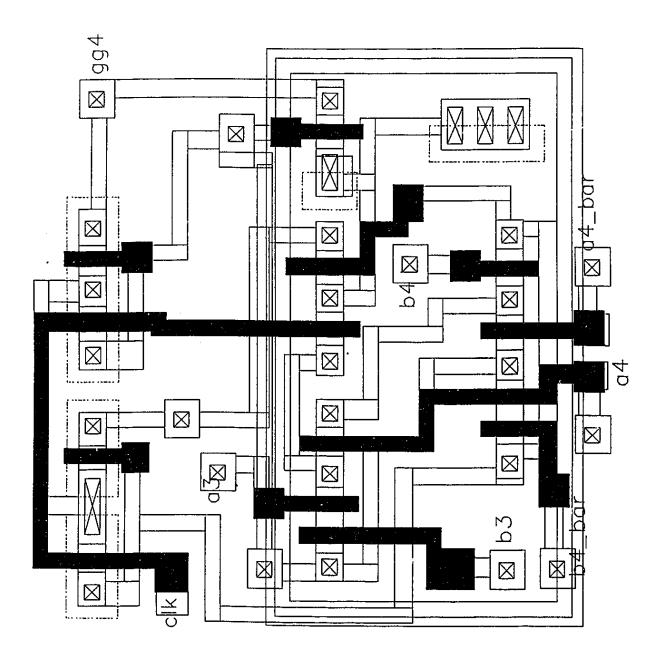

| E.11 Layout for Generate and Group Generate Block   | 237 |

|-----------------------------------------------------|-----|

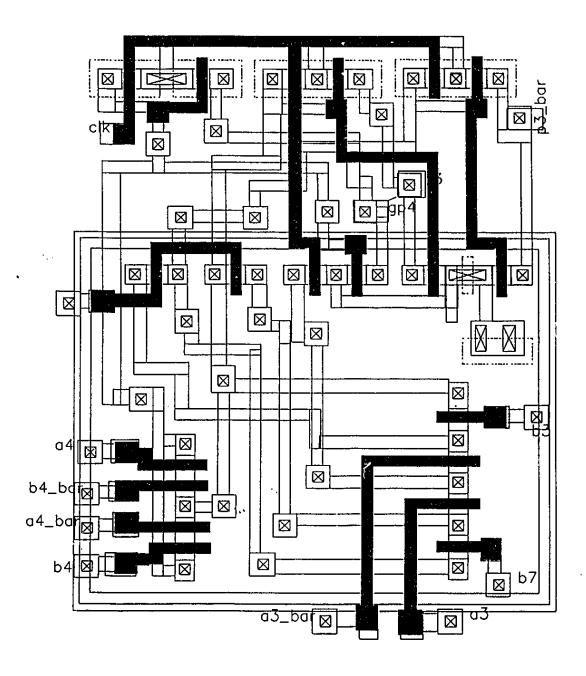

| E.12 Layout for Propagate and Group Propagate Block | 238 |

| E.13 Layout for Carry Generate Block                | 239 |

| E.14 Layout for Sum Block                           | 240 |

| E.15 Layout for the 10-Bit Adder                    | 241 |

# LIST OF TABLES

| 1.1 | Comparison of floating point specification of three popular computers | }          |

|-----|-----------------------------------------------------------------------|------------|

| 2.1 | IEEE 754 Special Values1                                              | l <b>1</b> |

| 2.2 | Operations that produce a NAN                                         | 13         |

| 2.3 | Unbiased Rounding                                                     | 21         |

| 3.1 | Round to Nearest/even versus Round to Nearest/up                      | 33         |

| 3.2 | Detection of Underflow and Overflow Conditions                        | 45         |

| 4.1 | Comparison of two two-bit full-adder multipliers                      | 60         |

| 4.2 | Truth table for the (4:2) Compressor                                  | 72         |

| 4.3 | Comparison of the complexity of various 16x16 bit Multipliers         | 81         |

| 4.4 | Comparison of three adders                                            | 95         |

| 4.5 | VHDL Simulation Result for an 8x8 Bit Floating Point multiplier       | 104        |

# CHAPTER 1

Introduction

#### 1.1 Introduction

The growing market for fast floating-point co-processors, digital signal processing chips, and graphics processors has created a demand for high speed area efficient multipliers. Current architectures range from small, low-performance shift and add multipliers, to large, high performance array and tree multipliers. Conventional linear array multipliers achieve high performance in regular structure, but require large amounts of silicon. Tree structures achieve even higher performance than linear arrays but the tree interconnection is more complex and less regular making them even larger than linear arrays. Ideally, one would want the speed benefits of a tree structure, the regularity of an array multiplier, and the small size of a shift and add multiplier.

This thesis considers an implementation of a new tree multiplier architecture which is faster than linear arrays, and more regular than traditional multiplier trees. In addition, since the need for high speed and high precision computation has been increasing in applications for image processing, computer graphics, model simulation and so on this thesis will investigate a hardware implementation of a floating point multiplier that adheres to the IEEE 754 standard. This standard will be explained briefly in the next section starting with its origin.

# 1.2 Historical Overview Of Floating Point Systems

Almost all of the early computers provided only fixed point arithmetic operations, the only exceptions being the Model V Relay Computer designed by George R. Stibitz of the Bell telephone Laboratories [1,2] and the Harvard Mark II Computer [3] designed by Horward Aiken. To facilitate scientific and engineering calculations, the early machines often used long word lengths for number representations. Forty bit numbers were used in machines patterned after an Institute of Advanced Study Machine, and forty five bit numbers were used in the SEAC (Bureau of Standards Eastern Automatic Computer) family. However, merely providing greater precision for number representation did not solve the need for greater range in the size of the numbers. To scale large numbers into the range afforded by the machine involved a great deal of programming effort, as well as a rather thorough analysis of the problem being solved so as to determine the appropriate scaling factors in advance. The technique of automatic scaling or floating point arithmetic, came into wide spread use in the mid 1950's, first as a software option and as a hardware feature. Nowadays all computers for scientific and engineering use have built in floating point features.

Presently there are more than twenty different floating point formats in use by various computer manufacturers. Table 1.1 shows the formats of three computer which are popular for scientific computing. From table 1.1 it can be simply seen that there is hardly any similarity between the various formats. This situation which prohibits data portability

produced by numerical software, vas the main motivation for setting up in 1978 an IEEE (Computer Society) 754 committee to standardize floating point arithmetic. The main goal of the standardization effort was to establish a standard which will allow communication between systems at the data level without the need for conversion.

| System /Bits_Layout | IBM/370                  | DEC<br>PDP-11            | CDC<br>Cyber 70 |

|---------------------|--------------------------|--------------------------|-----------------|

|                     | S = Short $L = Long$     | S = Short<br>L = Long    |                 |

| Word length         | S: 32 bits<br>L: 64 bits | S: 32 bits<br>L: 64 bits | 60 bits         |

| Exponent            | 7 bits                   | 8 bits                   | 11 bits         |

| Significand         | S: 6 digits              | S: (1) + 23 bits         | 48 bits         |

|                     | L: 14 digits             | L: (1) + 55 bits         |                 |

| Bias of Exponent    | 64                       | 128                      | 1024            |

| Radix               | 16                       | 2                        | 2               |

| Hidden '1'          | No                       | Yes                      | No              |

Table 1.1: Comparison of floating point specification of three popular computers

In addition to the respectable goal of the "the same format for all computers," the committee wanted to ensure that it would be the best possible standard for given number of bits. Specifically, the concern was to ensure correct results, that is the same as those given by the corresponding infinite precision with an error of 1/2 LSB. Furthermore, to ensure portability of all numerical data. A more detail explanation of the IEEE 754 standard will be given in the next chapter.

# 1.3 Thesis Organization

The next chapter provides background information on the IEEE 754 standard. In particular the three major aspects of the IEEE 754 floating point standard are dexcribed, that is the format of the data types, the arithmetic and the exception handling. In addition, it covers in detail the IEEE 754 rounding modes.

Chapter 3 focuses on the VLSI implementation of a floating point multiplier which adheres to the IEEE 754 standard presented in Chapter 2. This chapter also introduces a high performance hardware model for a floating point multiplier which incorporates several high performance rounding algorithm proposed by Mark Santario. In addition, in this chapter a new fast and efficient method for computing the exponent and the sticky bit are presented.

Chapter 4 covers the background information on the basics of binary multiplication. The advantages and disadvantages of various hardware multiplier architectures, including linear arrays, trees; two new multiplier architectures are also discussed. In addition, a comparison of several adder structures and BICMOS implementation of the two new multiplier architectures are presented.

Finally Chapter 5 presents a summary of the contributions of this thesis and describes directions for future investigations.

# **CHAPTER 2**

**IEEE Floating Point Standard**

# 2.1 Introduction

This chapter provides a tour of the IEEE 754 floating point standard. Each subsection discusses one aspect of the standard and why it was included. It is not the purpose of this thesis to argue that the IEEE 754 standard is the best floating point standard but rather to accept the standard as given. This chapter will start by first explaining the three major aspects in the IEEE 754 floating point standard [4]: the format of the data types, the arithmetic, and the exception handling.

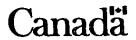

### 2.2 Data Formats

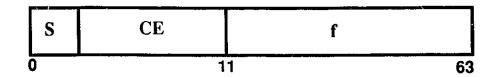

The floating point data format is made up of three parts (from left to right): sign bit, biased exponent (characteristics), and significand (mantissa).

| S | CE | F |

|---|----|---|

|   |    |   |

where:

S = Sign bit (indicates sign of the significand)

CE = Biased Exponent

F = Significand

then

e = true exponent = CE - bias

f = true significand = 1.F

A normalized non-zero number X, has the following interpretation

$$X = (-1)^{S} * 2^{CE-bias} * (1.F)$$

Floating point numbers are usually represented in normalized form. For example, both  $0.01 \times 10^{-1}$  and  $1.00 \times 10^{-1}$  represent 0.1. If the leading digit is non-zero the representation is said to be normalized. The floating point number  $1.00 \times 10^{-1}$  is normalized, whereas  $0.01 \times 10^{-1}$  is not. Requiring that a floating point representation be normalized makes the representation unique. Unfortunately this restriction makes it impossible to represent zero. A natural way to represent zero is with  $1.0 \times 2^{(emin-1)}$  (emin is the smallest allowable exponent), since this preserves the fact that the numerical ordering of non-negative real numbers corresponds to the lexicographical ordering of their floating point representation. When the exponent is stored in a k bit field, this implies that only  $2^k$  - 1 values are available for use as exponents, since one must be reserved to represent zero.

### 2.3 Precision

The IEEE 754 standard defines four different precisions: Single, Double, Single\_Extended and Double\_Extended.

#### 2.3.1 Single Precision

Single precision occupies a single 32 bit word. A 32-bit format for binary floating point number X is divided as shown in Figure 2.1. The component fields of X are the 1-bit sign S, the 8-bit biased exponent CE, and the 23-bit fraction f. The value V of X is as follows:

- (a) If CE = 255 and f# 0, then V = NAN

- **(b)** If CE = 255 and f=0, then  $V = (-1)^S x$  infinity

- (c) If 0 < CE < 255, then  $V = (-1)^{S} 2^{CE-127} (1.f)$

- (d) If CE = 0 and f # 0, then  $V = (-1)^S 2^{-126}(0.f)$

- (e) If CE = 0 and f = 0, then  $V = (-1)^S 0$ , (Zero)

Figure 2.1: Single Precision Format

#### 2.3.2 Double Precision

Double precision occupies a 64-bit word. The 64-bits for a binary floating point number X is divided as shown in Figure 2.2. The component fields of X are the 1-bit sign S, the 11-bit biased exponent CE, and the 52-bit fraction f. The value of X is as follows:

- (a) If CE = 2047 and f# 0, then V = NAN

- (b) If CE = 2047 and f=0, then  $V = (-1)^S x$  infinity

(c) If

$$0 < CE < 2047$$

, then  $V = (-1)^{S} 2^{CE-1023}$  (1.f)

(d) If

$$CE = 0$$

and  $f # 0$ , then  $V = (-1)^{S} 2^{-1022}(0.f)$

(e) If

$$CE = 0$$

and  $f = 0$ , then  $V = (-1)^{S}0$ , (Zero)

Figure 2.2: Double Precision Format

#### 2.3.3 Single-Extended

Extended is an implementation dependent format. An extended binary floating point number X has four components: a 1 bit sign S, an exponent CE of specified range combined with an implementation dependent bias, a 1-bit integer j, and a fraction f with at least 31 bits. The exponent shall range between a minimum value m < -1023 and a maximum value M >1024. The value of V of X is as follows:

- (a) If CE = M and f# 0, then V = NAN

- (b) If CE = M and f=0, then  $V = (-1)^S x$  infinity

- (c) If m < CE < M, then  $V = (-1)^S 2^{CE}$  (j.f)

- (d) If CE = m and j = f = 0, then  $V = (-1)^S 0$ , (normal zero)

#### 2.3.4 Double-Extended

The double-extended format is the same as single extended described in 2.3.3, except that the exponent can range between m < -16383 and M > 16384, and a fraction shall have at least 63 bits.

# 2.4 Exponent

Since the exponent can be positive or negative, some methods must be chosen to represent its sign. Two common methods of representing signed numbers are sign/magnitude and two's complement. Sign/magnitude is the system used for the sign of the significand in the IEEE formats: 1 bit used to hold the sign; the rest of the bits represent the magnitude of the number. The two's complement representation is often used in integer arithmetic.

The IEEE binary standard does not use either of these methods to represent the exponent but instead uses a biased representation. In the case of single precision, where the exponent is stored in 8 bits, the bias is 127 (for double precision it is 1023). What this means is that if CE is the value of the exponent bits interpreted as an unsigned integer, then the exponent of the floating point number is CE-127. This is often called the biased exponent to distinguish it from the unbiased exponent E. An advantage of biased representation is that non-negative floating point numbers can be treated as integers for comparison purposes.

## 2.5 Arithmetic Operations

All conforming implementations of the IEEE standard provide the following operations:

#### 1. Numerical Operations

- i) Add

- ii) Subtract

- iii) Multiply

- iv) Divide

- v) Square Root

- vi) Reminder

#### 2. Conversion Operations

- i) Floating point Integer

- iii) Binary (floating) → Decimal (floating)

#### 3. Miscellaneous Operations

- i) Move from one format width to another

- ii) Compare and set condition code

- iii) Find Integer part

# 2.6 Exception Handling

On some floating point hardware every bit pattern represents a valid floating point number. The IBM system/370 is an example of this. On the other hand, the VAX reserves some bit patterns to represent special numbers called *reserved operands*. The idea goes back to the CDC 6600, which had bit patterns for the special quantities Indefinite and Infinity.

The IEEE 754 standard continues in this tradition and has NANs (not a number) and infinities. Without special quantities, there is no good way to handle exceptional situations, such as taking the square root of a negative number, other than aborting the computation.

Under IBM System/370 FORTRAN, the default action in response to computing the square root of a negative number results in the printing of an error message. In IEEE arithmetic a NAN is returned in this situation. The IEEE standard specifies the special quantities shown in table 2.1.

| Exponent                                | Fraction | Represents              |

|-----------------------------------------|----------|-------------------------|

| e = e <sub>min</sub> -1                 | f = 0    | ±0                      |

| e = e <sub>min</sub> -1                 | f ≠0     | 0.f x 2 <sup>emin</sup> |

| e <sub>min</sub> ≤ e ≤ e <sub>max</sub> | -        | 1.f x 2 <sup>e</sup>    |

| $e = e_{max} + 1$                       | f = 0    | ± infinity              |

| $e = e_{\text{max}} + 1$                | f≠0      | NAN                     |

Table 2.1: IEEE 754 Special Values

#### 2.6.1 NANs

Traditionally, the computation of 0/0 or the square root of -1 has been treated as an unrecoverable error that causes computations to halt. There are however, examples for which it makes sense for a computation to continue in such a situation. Consider a subroutine that finds the zeros of a function f, say zero(f). Traditionally, zero finders require the user to input an interval [a,b] on which the function is defined and over which the zero finder will search. That is, the subroutine is called as zero(f,a,b). A more useful zero finder would not require the user to input this extra information. This more general zero finder is especially appropriate for calculators, where it is a natural to key in a function and awkward to then have to specify the domain. It is easy, however, to see why most

zero finders require a domain. The zero finder does its work by probing the function f at various values. If it is probed for a value outside the domain of f the code for f might well compute 0/0 or the square root of -1, and the computation will halt, unnecessarily aborting the zero finding process.

This problem can be avoided by introducing a special value called NAN and specifying that the computation of expressions like 0/0 and the square root of -1 produce NAN rather than halting. A list of the situations that can cause a NAN is given in table 2.2. Then, when zero(f) probes outside the domain of f, the code for f will return NAN and the zero finder can continue. That is, zero(f) is not "punished" for making an incorrect guess. With this example in mind, it is easy to see what the result of combining NAN with an ordinary floating point number should be. Suppose that the final statement of f is return(-b + sqrt(d))/(2a). If d<0, sqrt(d) is a NAN and -b + sqrt(d) will be a NAN. Similarly, if one operand of a division operation is a NAN, the quotient should be a NAN. In general, whenever a NAN participates in a floating point operation, the result is another NAN.

In the IEEE 754 standard, NANs are represented as floating point numbers with the exponent  $e_{max} + 1$  and non-zero significands.

#### 2.6.2 Infinity

Just as NANs provide a way to continue a computation when expressions like 0/0 or the square root of -1 are encountered, infinities provide a way to continue when an overflow occurs. This is much safer than simply returning the largest representable number. As an example, consider computing  $(x^2 + y^2)^{1/2}$ , when base( $\beta$ )=10, precision(p) =3 and e<sub>max</sub> = 98. If x = 3x10<sup>70</sup> and y = 4x10<sup>70</sup>, then x<sup>2</sup> will overflow and be replaced by 9.99 x 10<sup>98</sup>. Similarly y<sup>2</sup> and x<sup>2</sup> + y<sup>2</sup> will each overflow in turn and be replaced by 9.99 x 10<sup>98</sup>. So the final result will be  $(9.99 \times 10^{98})^{1/2} = 3.16 \times 10^{49}$ , which is drastically in

error. The correct answer is  $5x10^{70}$ . In IEEE 754 standard arithmetic, the result of  $x^2$  is infinity, as is  $y^2$ ,  $x^2+y^2$ , and  $sqrt(x^2+y^2)$ . So the final result is infinity, which is safer than returning an ordinary floating point number that is considerably different from the correct answer.

| Operation   | NAN produced by         |

|-------------|-------------------------|

| +           | infinity + (- infinity) |

| -           | 0 x infinity            |

| /           | 0/0, infinity/infinity  |

| REM         | x REM 0, infinity REM y |

| square root | sqrt(x)(when x < 0)     |

Table 2.2: Operations that produce a NAN

#### 2.6.3 Signed Zero

Zero is represented by the exponent  $e_{min}$ -1 and a zero significand. Since the sign bit can take on two different values there are two zeros, +0 and -0. If a distinction were made when comparing +0 and -0, simple tests, such as if(x=0), would have unpredictable behavior, depending on the sign of x. Thus, the IEEE standard defines comparisons so that +0 equals -0 rather than -0 < +0. Although it would be possible to always ignore the sign of zero, the IEEE standard does not do so. When a multiplication or division involves a signed zero, the usual sign rules apply in computing the sign of the answer. Thus, 3(+0) = +0 and +0/-3 = -0. If zero did not have a sign, the relation 1/(1/x) = x would fail to hold

when x = + or - infinity. The reason is 1/(- infinity) and 1/(+ infinity) both result in zero and 1/0 results in + infinity, the sign information has been lost. One way to restore the identity 1/(1/x) = x is to have only one kind of infinity, however that would result in the disastrous consequence of losing the sign of an overflowed quantity.

Another example of the use of signed zero concerns underflow and functions that have a discontinuity at zero such as  $\log$ . In IEEE arithmetic, it is natural to define  $\log(0)$  = negative infinity and  $\log(x)$  to be a NAN when x < 0. Suppose x represents a small negative number that has underflowed to zero, with a signed zero, x will be negative so  $\log$  can return a NAN. If there were no signed zero, however, the  $\log$  function could not distinguish an underflowed negative number from 0 and would therefore have to return negative infinity.

Although distinguishing between +0 and -0 has advantages, it can occasionally be confusing. For example, signed zero destroys the relation x = y 1/x = 1/y, which is false when x = +0 and y = -0. The IEEE committee decided, however that the advantages of using signed zero outweighed the disadvantages.

#### 2.6.4 Denormalized Numbers

Consider normalized floating point numbers with  $\beta = 10$ , p = 3 and  $e_{min} = -98$ . The numbers  $x = 6.87 \times 10^{-97}$  and  $y = 6.81 \times 10^{-97}$  appear to be perfectly ordinary floating point numbers, which are more than a factor of 10 larger than the smallest floating point number  $1.00 \times 10^{-98}$ . They have a strange property, however: x - y = 0 even though  $x \ne y$ . The reason is that  $x - y = .06 \times 10^{-97} = 6.0 \times 10^{-99}$  is too small to be represented as a normalized number and so be flushed to zero.

How important is it to preserve the property

$$x = y - x - y = 0$$

? (2.1)

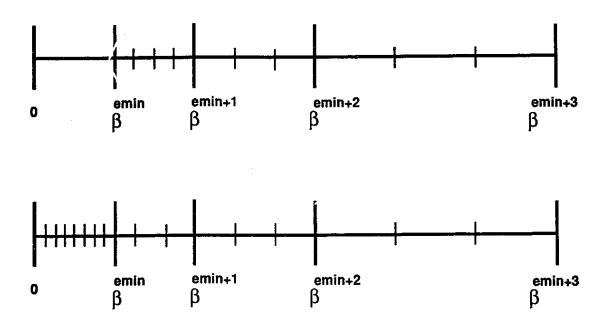

The IEEE standard uses denormalize numbers, which guarantee(2.1), as well as other useful relations. They are the most controversial part of the standard and probably accounted for the long delay in getting 754 approved. Most high performance hardware that claims to be IEEE compatible does not support denormalized numbers directly but rather traps when producing denormals, and leaves it to software to simulate the IEEE standard. The idea behind denormalized numbers goes back to Goldberg (1967) and is simple. When the exponent is  $e_{min}$ , the significand does not have to be normalized. For example, when  $\beta = 10$ , p = 3 and  $e_{min} = -98$ ,  $1.00 \times 10^{-98}$  is no longer the smallest floating point number, because  $0.98 \times 10^{-98}$  is also a floating point number.

There is small snag when  $\beta=2$  and a hidden bit is being used, since a number with an exponent of  $e_{min}$  will always have a significand greater than or equal to 1.0 because of the implicit leading bit. The solution is similar to that used to represent 0 and is summarized in table 2.1. The exponent  $e_{min}$ -1 is used to represent denormals. More formally, if the bits in the significant field are  $b_1, b_2, \ldots, b_{p-1}$  and a value of the exponent is  $e_n$ , then when  $e_n$  emin -1, the number being represented is  $0.b_1b_2 \ldots b_{p-1} \times 2^e$ , whereas when  $e_n$  emin-1 the number being represented is  $0.b_1b_2 \ldots b_{p-1} \times 2^{e+1}$ . The +1 in the exponent is needed because denormals have an exponent of  $e_{min}$ , not  $e_{min}$ -1. Recall the example  $\beta=10$ ,  $p_n=3$ ,  $e_{min}=-98$ ,  $e_n=6.87 \times 10^{-97}$ , and  $e_n=6.81 \times 10^{-97}$  presented at the beginning of this section. With denormals,  $e_n=6.81 \times 10^{-97}$  presented at the beginning of this denormalized number  $e_n=6.81 \times 10^{-98}$ . This behaviour is called gradual underflow. It is easy to verify that (2.1) always holds when using gradual underflow.

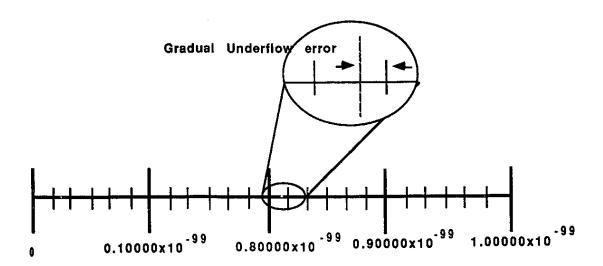

Figure 2.3 illustrates denormalized numbers. The top number line in the figure shows normalized floating point numbers. Notice the gap between 0 and the smallest normalized number  $1.0 \times \beta^{emin}$ . If the result of a floating point calculation falls into this gap, it is flushed to zero. The bottom number line shows what happens when denormals are added to the set of floating point numbers. The gap is filled in, when the result of a calculation is less than  $1.0 \times \beta^{emin}$ ; it is represented by the nearest denormal. When denormalized numbers are added to the number line, the spacing between adjacent floating point numbers varies in a regular way. Adjacent spacings are either the same length or differ by a factor of  $\beta$ . Without denormals the spacing abruptly changes from  $\beta^{-p+1}\beta^{emin}$  to  $\beta^{emin}$ , which is a factor of  $\beta^{p-1}$ , rather than the orderly change by a factor of  $\beta$ . As a result of this, many algorithms that can have relative error for normalized numbers close to the underflow threshold are well behaved in this range when gradual underflow is used. Figure 2.4 shows the error which results from gradual underflow comparing to flush to zero.

Example 2.1:

Comparison of various schemes in six-digit decimal arithmetic with  $e_{min} = -99$

$$(1.23456 \times 10^{-60}) \times (6.54321 \times 10^{-40}) = 8.0779853376 \times 10^{-100}$$

(Exact)

$\longrightarrow 0.80780 \times 10^{-99}$  (Gradual Underflow)

$\longrightarrow 0.0$  (Store 0)

$\longrightarrow$  UN (UN symbol)

Figure 2.3: Flush to zero compared with gradual underflow

Figure 2.4: Gradual Underflow Error

# 2.7 Rounding

Squeezing infinitely many real numbers into a finite number of bits requires an approximate representation. Although there many infinitely many integers, in most programs the result of integer computations can be stored in 32 bits. In contrast, given any fixed number of bits, most calculations with real numbers will produce quantities that cannot be exactly represented using that many bits. Therefore, the result of a floating point calculation must often be rounded in order to fit back into its finite representation.

In IEEE 754 standard there are four rounding modes. Unbiased rounding to nearest, Round toward zero, Round toward minus infinity, and Round toward plus infinity. Of the four only the first is mandatory and the rest are optional. Unbiased rounding is very similar to the conventional round to nearest which is implemented by adding 1/2 of the digit to be discarded and then truncate to the desired precision.

Example 2.2:

However, suppose the number to be rounded is exactly half way between two number, which one is the nearest? To answer the question let's add the same 0.5 to the two following numbers:

| 38.5    | 39.5 |

|---------|------|

| 00.5    | 00.5 |

| 39.0 39 | 40.0 |

Notice that in both cases we rounded up even though each number was exactly half way between smaller and larger numbers. Therefore, by simply adding 0.5 and truncating a biased rounding is generated. In order to have unbiased rounding the IEEE 754 standard rounds to even when there is a tie between two numbers. Now, using the previous numbers we get:

In the first case the number is rounded down and in the second case the number is rounded up. Therefore, we have statistically unbiased rounding. Of course, the same unbiased rounding could be obtained by rounding to odd (instead of even) in the tie case. This time the rounding looks like this:

However, rounding to even is preferred because it may result in "nice" integer numbers as in the following examples:

Whereas rounding to odd results in the more frequent occurrence of non-integer numbers:

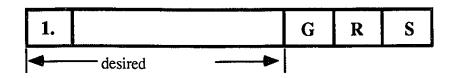

Now, we illustrate the implementation of unbiased rounding to even, and introduce the the so called "sticky bit".

The conventional system for rounding is to add half of the LSD position of the desired precision, to the MSD of the portion to be discarded. This scheme has a problem as is illustrated below (the XXXXX are additional bits). Thus:

00.5

39.0

Two cases have to be distinguished:

Case 1: XXXXXX  $\neq$  0 and the rounding is correct since 39 is nearest 38.5 +  $\delta$ , where  $0 < \delta < 0.5$ .

Case 2: XXXXXX = 0 Note the rounding is incorrect because we have a tie case which requires the result to be rounded to even (38).

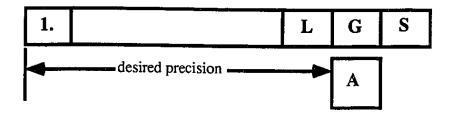

It is obvious that regardless of the number of X bits, all possible permutations can be mapped into one of the two above cases. Therefore, one bit can be used to distinguish between Case 1 and Case 2. This bit is called the "sticky bit", and it has the value one for Case 1 and the value zero for Case 2. The logic implementation of the sticky bit is simply ORing of the bits to the right of the second guard bit, as illustrated below for the addition/subtraction operation

In the case of a left shift(normalization after subtraction), S does not participate in the left shift, but instead zeros are shifted into R. In the case of a right shift due to significand overflow (during magnitude addition), the R guard bit is ORed into S during the shift. The above format (with two guard bits) is necessary only during the addition/subtraction process: the final result just before rounding has only one guard bit and the sticky bit.

The proper action to obtain unbiased rounding to even is determined from the following table 2.3:

| L | G | s | Action                             | Α    |

|---|---|---|------------------------------------|------|

| х | 0 | 0 | Exact result                       | х    |

| х | 0 | 1 | Inexact result                     | х    |

| 0 | 1 | 0 | The tie case with even significand | 0    |

| 1 | 1 | 0 | The tie case with odd significand  | 1    |

| х | 1 | 1 | Rounding to nearest                | 1_1_ |

Table 2.3: Unbiased Rounding

In addition to round to nearest, as mentioned previously the IEEE 754 standard define three other optional rounding modes. These "directed" rounding modes are round toward plus infinity, round toward minus infinity and round toward zero. Once round to nearest has been implemented, the other rounding modes are relatively simple. To begin

with, consider round toward zero. This is simply a truncation. We now look at round toward plus infinity. The standard states that "when rounding toward plus infinity the result shall be the format's value (possibly plus infinity) closest to and no less than the infinitely precise result". Basically, what this says is that in case of positive result, if all the bits to the right of the LSB of the desired result are zero, then the result is correct. If any of these bits are a one then a 1 should be added to the LSB of the result. If the result is negative it should be truncated. When rounding toward minus infinity the exact opposite holds.

In conclusion, this chapter has described the IEEE 754 floating point standard which is widely accepted by most computer manufacturers. Details on the data formats, exception handling and rounding methods have been explained. In the next chapter, implementation of a floating point multiplier that satisfies the IEEE standard will be discussed.

# **CHAPTER 3**

Floating Point Multiplier

### 3.1 Introduction

Many applications exist in which integer, or non-IEEE floating point multiplication is sufficient. However, to be widely accepted, current and future floating point co-processors must adhere to IEEE standard for floating point arithmetic [4]. The standard can be implemented in software, hardware, or a combination of the two [5]. The performance requirements of modern digital systems demand direct hardware floating point multipliers. To match the performance of the hardware multipliers, the rounding modes must also be implemented in hardware.

In this chapter a hardware implementation of a floating point multiplier will be presented. Since dealing with tie case for the round to nearest/even mode slows the performance of the multiplier, three algorithms will be presented for implementing round to nearest/up [6].

Then it will be shown how the round to nearest up result can be adjusted to produce the correct IEEE rounded result. In addition two techniques for computing the sticky bit will be presented. All of the rounding algorithms and sticky methods presented are technology independent and can be used with several types of multiplier architectures. Finally the floating point multiplier hardware model obtained by incorporating the fast rounding techniques will be given.

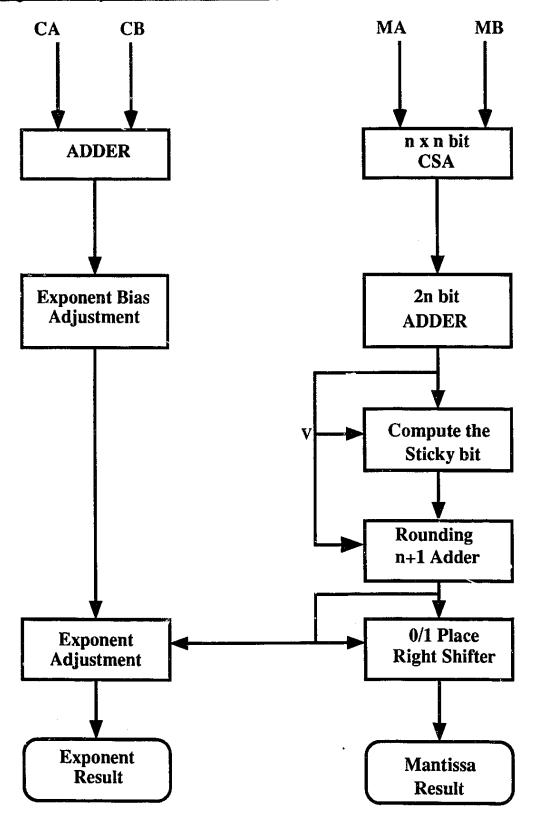

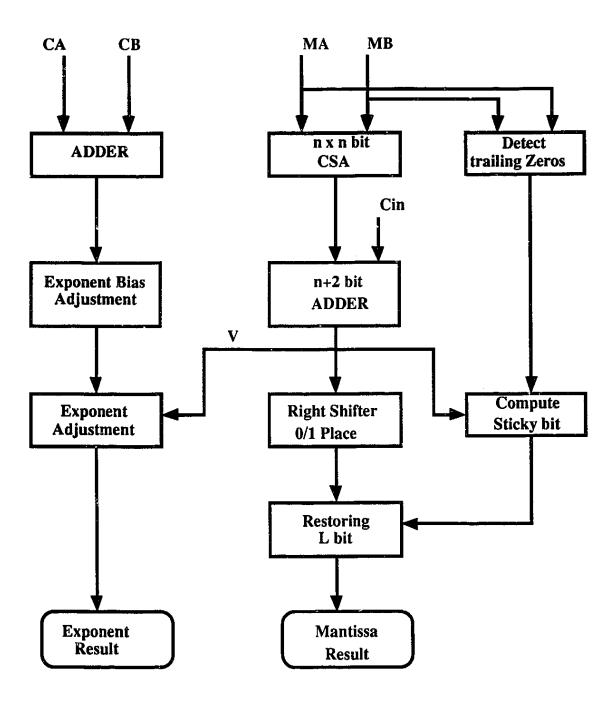

## 3.2 Hardware Implementation of a FPU Multiplier

A hardware realization of a floating point unit multiplier is shown in Figure 3.1. This algorithm is made up of two distinct sections. On the right side the mantissa are handled as fixed point operands, while the left side computes the exponent. The mantissa, and the characteristic of the "A" operand are designated MA, and CA respectively, while MB, and CB are similar part of the B operand. The result of multiplication is designated by R; and MR, and CR are the mantissa, and the characteristic of the R result. In general the floating point multiplication algorithm involve the following operations:

- 1) Perform fixed point multiplication of the mantissa of the two operands

- 2) Round the result

- 3) Normalize the result of the mantissa multiplier

- 4) Add the two characteristics and correct for bias

- 5) Check for underflow and overflow conditions

Figure 3.1: Floating Point Multiplier Data Path

The performance of the algorithm shown in Figure 3.1 can be enhanced by removing the computation of the sticky bit from the critical path and incorporating Mark Santario fast rounding techniques [6]. These two techniques will be presented in the next sections.

## 3.3 A Simple Round to Nearest/up Algorithm

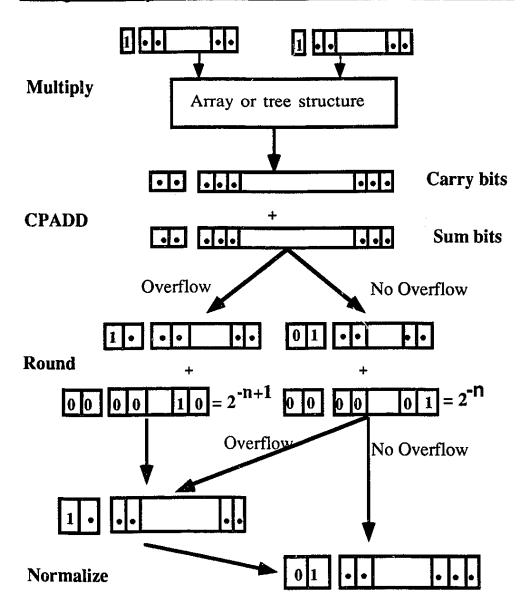

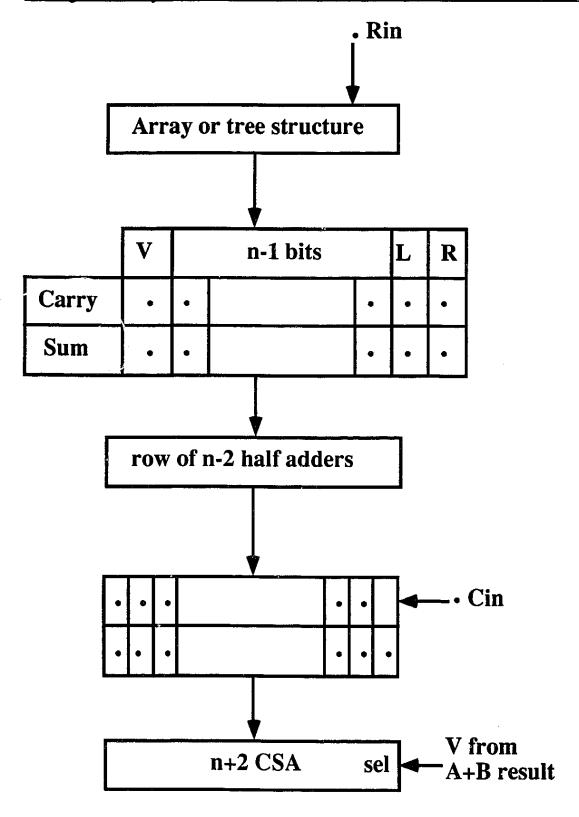

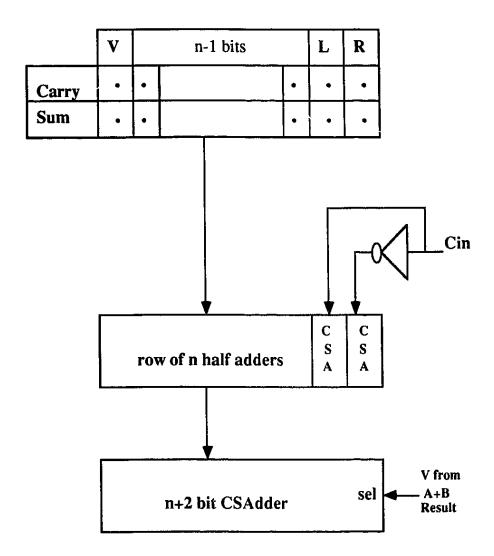

Most high performance VLSI multipliers use some sort of array or tree structure to sum the partial products in the mantissa portion of a floating point multiply [7]. Figure 3.2 shows a flow diagram for the mantissa handling section of a floating point multiply unit. This simple round to nearest/up scheme will be referred to as Algorithm 3a.

The top section (multiply) accepts two normalized mantissas and uses some type of reduction structure which produces the product in carry save form (two 2n bit numbers). These two numbers are then added in the CPADD section to produce a complete 2n bit product. The are two possible rounding operations which then occur, depending on the most significant bit(MSB) of this product. If the resulting product is in the range  $2 \le \text{product} < 4$  (overflow), the constant  $2^{(-n+1)}$  is added to the product and the result is truncated on -2 bits to the right of the decimal point. A normalization shift (Normal) of 1 to the right is then necessary to restore the rounded product to the range  $1 \le \text{rounded}$  product < 2, with an appropriate adjustment of the exponent. If the original 2n bit product was in the range 1 < product < 2 (no overflow), then the constant  $2^{(-n)}$  is added. In most cases this rounded product will be less than 2, and the rounding operation is finished. However, it is possible that the addition of  $2^{(-n)}$  could cause the rounded product to be equal to 2, in which case a normalization shift of 1 and an exponent adjustment is necessary (as in the left branch).

Figure 3.2: Algorithm 3a Data Flow

The low order n-2 bits from the CPADD section of Figure 3.2 are not used in any of the following steps. The only effect that these bits have on the final result is due to the carry they generate into the most significant n+2 bits. Thus, the carry propagate adder need never actually compute the sum of the least significant n-2 bits. The 2n bit carry propagate adder can be replaced by an n+2 bit carry propagate adder, with an input carry from the least significant n-2 bits. The small adder is clearly an advantage where a hardware

implementation is concerned. Algorithm 3a requires two carry propagate additions in series. In section 3.4 algorithm 3b and algorithm 3c concentrate on computing these additions in parallel, which significantly increases performance.

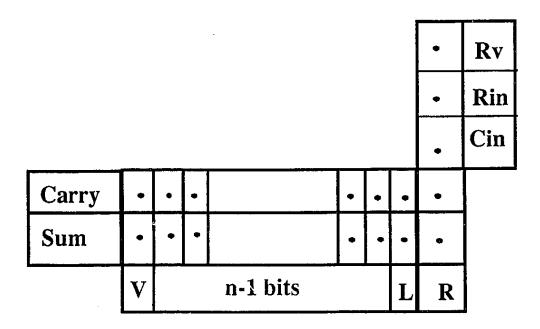

## 3.4 Parallel Addition Schemes

If an n+2 bit carry propagate adder is used in the **CPADD** section of Figure 3.2, then the carry from the lower bits (**Cin**) will be added at the  $2^{(-n)}$  bit position. Assuming that no overflow occurred, an additional  $2^{(-n)}$  will be added to the result in the **Round** section. The  $2^{(-n)}$  bit position will thus be called the round bit position, or R bit. The 1 that always get added to the R bit position for rounding will be identified as **Rin**. If no overflow occurs, adding Cin and Rin to the R bit position will produce the correct round to nearest/up result.

Now consider the overflow case. The MSB, known as the overflow bit (V), is a 1. By assuming that no overflow would occur,  $2^{(-n)}$  was added for rounding. If an overflow did occur, then  $2^{(-n+1)}$  should have been added for rounding. The difference of  $2^{(-n)}$  must be added to correct the rounding. This can be done by defining a new bit that is added to the  $2^{(-n)}$  bit position in the case of an overflow. This bit will be called the overflow rounding bit (Rv). The correct rounding can thus be obtained by simply adding the carry from the lower order bits (Cin), the rounding bit (Rin), and in the case of an overflow (Rv) to the R bit position. This bits are shown in Figure 3.3.

Figure 3.3: Bits to be Summed for Correct Round to Nearest/up

Fast and effective implementation schemes for summing the bits in Figure 3.3 must overcome two problems. First, the value of Rv is not known until the sum of all the other bits have been computed. Second, an adder with 5 input slots at the LSB is required.

The first problem can be overcome by computing two carry propagate additions in parallel. The first assuming Rv=0, and second, assuming Rv=1. When the overflow condition is known, the correct sum can then be selected using a multiplexer. These two additions are related, as the first is simply one larger than the second. This provides many possibilities for the designer. An efficient technique is to simply merge the two carry propagate adders into one. A conditional sum adder (CSAdd), or carry select adder as it is often known, computes two possible outputs [8]. The first assumes the input carry is a zero, and the second assumes the input carry is a one. When the input carry is known the correct output is selected. This compound adder requires much less hardware than two separate adders,

since only the carry chain need be duplicated. In the more general sense, a conditional sum type adder produces two results in the form of A+B and A+B+1.

Now for the second problem Rearry and Rsum use the carry and sum slots. Rv uses the input carry slot to the CSAdder. This leaves no empty slots for Rin and Cin to be added to the R bit position. Two algorithms were proposed by Mark Santario to fix this problem [6]. Both involve adding Cin and Rin to the R bit position, without propagating the carry, before computing the carry propagate result.

The data flow of algorithm 3b is shown in Figure 3.4. A row of half adders is used to partly sum the carry and sum bits. This leaves a hole in the CSAdder at Rcarry. The Cin from the lower order bits can be placed into this hole. Rin must still be added to the R bit position. An additional row of half adders could be used as on Cin, but there are more economical techniques. Array multipliers typically have empty slots. A 1 can often be injected into the array, or corresponding structure, in the appropriate place so that the effect is to add Rin to the R bit. Once Rin and Cin have been added to the R bit position and the CSAdd has completed, the correct result can be picked based upon the overflow bit from the A+B result. The V bit from the A+B result is used, because the overflow bit must be checked before Rv has been added in. The A+B+1 result has already added Rv to the sum, potentially corrupting the V bit. If the V bit from the A+B result is a 0, the A+B result is chosen. If the V bit is a 1 from the A+B+1 result is picked. In this case an overflow has occurred, the result must be normalized and the exponent adjusted.

In some cases a slot may not exist, or it may be difficult to inject Rin into the multiplier array or accumulator. Figure 3.5 shows the data flow for algorithm 3c. This algorithm is similar to algorithm 3b, except that Rin is not injected into the array. Instead, two least significant half adders are replaced with CSA's, providing two additional slots as the L and R bit positions. Rin, which is always 1, can be combined with Cin and placed into these

Figure 3.4: Algorithm 3b Data Flow

empty slots. If Cin equals 0, then a 1 from Rin should be added to the R bit. If Cin equals 1, then 2 should be added to the R bit position; one from Rin and one from Cin. Adding 2 to the R bit position is equivalent to adding 1 to the R+1(L) bit position. The output of the half-adder/CSA row may then fed to the CSAdder as in algorithm 3b.

Figure 3.5: Algorithm 3c Data Flow

# 3.5 Obtaining the IEEE Round to Nearest Result

It was stated earlier that round to nearest/up produces exactly the same result as round to nearest/even, except when a tie occurs. To produce the correct round to nearest/even result from the unrounded result, a '1' is potentially added to the round bit. The bit (E) to be added to the round bit (R) for correct IEEE round to nearest is based up on the L, R, and sticky (S) bits as shown in table 3.1.

| Before Rounding |   | Add to R bit |   | L after | L after Rounding |                |

|-----------------|---|--------------|---|---------|------------------|----------------|

| L               | R | S            | E | U       | L <sub>E</sub>   | L <sub>U</sub> |

| х               | 0 | 0            | d | 1       | X                | X              |

| х               | 0 | 1            | d | 1       | x                | X              |

| 0               | 1 | 0            | 0 | 1       | 0                | 1              |

| 1               | 1 | 0            | 1 | 1       | 0                | 0              |

| X               | 1 | 1            | 1 | 1       | X                | X              |

#### Where:

E = Bit added to R bit for correct round to nearest/even

U = Bit added to R bit for correct round to nearest/up

$L_E$  = The L bit after round to nearest/even

$L_{II}$  = The L bit after round to nearest/up

d = Don't care. E can not effect  $L_E$

Table 3.1: Round to Nearest/even versus Round to Nearest/up

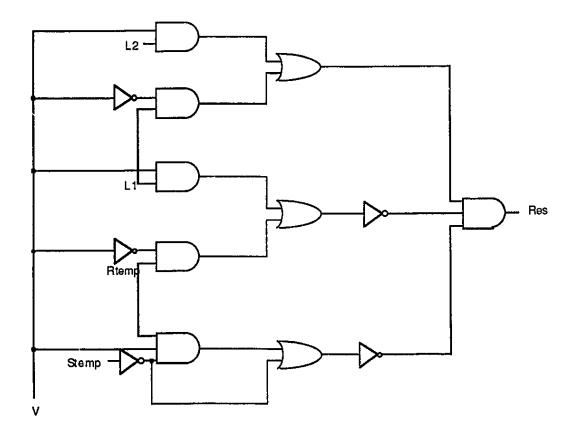

In contrast, round to nearest/up assumes that the bit to be added to the R bit for correct rounding (U) is always a 1. The only case where the round to nearest/up bit (U) will produce different result from the round to nearest/even bit (E) is shown in row 3 of table 3.1, where E=0, and U=1. In this case round to nearest/up changed the L bit from a 0 (L=0) to a 1 (L<sub>E</sub>=1), while round to nearest/even left the L bit unchanged (L<sub>U</sub>=0). The important thing to notice is that when round to nearest/up changed the L bit to a 1, the 1 was not propagated. As such, only the L bit was effected. This means that the correct round to nearest/even result can be obtained from the round to nearest/up result by restoring the L bit to a zero.

By assuming that the round bit will be a 1, the round to nearest/up algorithms have an advantage over the round to nearest/even method in that the carry propagate addition can take place before the sticky bit has been computed. This means that the round to nearest/up result can be obtained using any of the methods presented in the earlier sections. The correct IEEE round to nearest result can then be obtained by observing only the L, R and sticky bits, and forcing the L bit to a zero if required. The circuit used for restoring the L bit depending on L, R, and S bits is shown on Figure 3.6.

## 3.6 Computing the Sticky Bit

## 3.6.1 A Simple Method to Compute the Sticky Bit

The first method for determining the sticky bit is conceptually the simplest, as it stems from the very definition of the sticky bit. Recall that the sticky bit was defined to be equal to zero if the value of all the bits to the right of the round bit is zero. To determine the sticky bit, begin with a carry propagate addition on all of the bits. The Sticky bit(S) will be the OR of all the bits to the right of the R bit. This method is very simple in concept, and is

often used in practice. One drawback is that a full carry propagate addition, followed by a logical OR, must be done on all of the lower order carry save bits.

Figure 3.6: L Bit Restorer

# 3.6.2 Computing Sticky Bit From Input Operands

The sticky bit may also be computed directly from the inputs to be multiplied, bypassing the multiply array completely. The number of trailing zeros in the binary number  $X \bullet Y$  (product of X and Y) is exactly equal to the number of trailing zeros in X plus the number of trailing zeros in Y (Note the number of trailing zeros in the product is exactly equal to the sum of the trailing zeros in the operands, for any representation in which the

base is prime. This is true because prime numbers cannot be factored. Non prime bases can be factored; therefore, the number of trailing zeros in the product can be greater than the sum of the trailing zeros in the operands). The trailing zeros in X and Y can be counted and summed while the multiply is taking place. If the sum is greater than the sum of the bits to the right of the round bit, then the sticky bit is a zero. The advantage of using this method is that the sticky bit can be computed in parallel with the actual multiplication, removing the sticky bit from the critical path.

The floating point multiplier which incorporates the fast rounding technique and the new sticky bit computation technique is shown in Figure 3.7. This new floating point algorithm was fully simulated using a VHDL simulator. From the simulation results it was found that even though this new algorithm has a better performance than the one shown in Figure 3.1 it has the following three major drawbacks.

First, since the result of the mantissa multiplier is in range  $1 \le (1.F) < 4$ , the exponent must increment when V=1 (or the mantissa is between  $2 \le (1.F) < 4$ ). This increment of the exponent can not be done until the mantissa multiplication is completed. Thus this operation is on the critical path of the floating point multiplication.

Second, the exponent data path is twenty percent slower than the mantissa data path.

Therefore the speed of the multiplier is determined by the exponent datapath.

Thirdly, the performance gain obtained by computing the sticky bit from input operands is offset by its hardware complexity.

The first problem was solved by using a conditional sum adder to remove the computation of the exponent from the critical path. To solve the other problems, new techniques for computing the sticky bit and exponent have been developed. These techniques are explained in the next sections.

Figure 3.7: Floating Point Data Path which Incorporates the Fast Rounding Techniques

# 3.7 A New and Efficient Technique for Computing the Sticky Bit

The new technique computes the sticky bit by ORing the Carry Save bits. That is, a simple logical OR on the Carry Save bits formed from the bits to the right of the round bit will yield the correct sticky bit. This simple ORing of the carry save bits works for the following reasons. If the 2n bit carry save result is scanned from right to left, the first non-zero carry/sum pair will contain a single one. That is, either the carry or the sum will be a 1 but not both. This single one could not generate a carry during a carry propagate addition, and since all of the bits to its right are zero, there is no carry to propagate. This will cause a single one to remain in its current position. If this position is to the right of the R bit, the sticky bit will be a 1.

To see why this is true, refer to Figure 3.8. This figure shows a section of the partial products for the multiplication of A B. Each row represents a single partial product which will be generated and later summed to form the carry save form of the final product. AOBO represents the partial product represented by the logical AND of bit A0 with bit B0, and so on.

Assume A2B2 in column 4 is a 1, and column 4 is the first column in which a 1 appears. Since A2 is a 1, B1 and B0 must both be zero, or there would be a one in an earlier column formed by A2B1 in column 3, row 1, or A2B0 in column 2, row 0. All products above A2B2 in column 4 contain either a B1 or a B0 and thus must be zero. Looking across row 2, B2 is a 1. This means A1 and A0 must be both zero, or a 1 would exist in columns 3 or 2. All products below A2B2 in column 4 contain either A1 or A0, and thus must also be zero. Therefore, A2B2 is the only non-zero partial product in this column. This can easily

be generalized to any element in any column, proving that the first column in which a 1 exist will contain a single 1.

|   | 5    | 4    | 3    | 2    | 1    | 0    |  |

|---|------|------|------|------|------|------|--|

| 0 | A5B0 | A4B0 | A3B0 | A2B0 | A1B0 | A0B0 |  |

| 1 | A4B1 | A3B1 | A2B1 | AlB1 | A0B1 |      |  |

| 2 | A3B2 | A2B2 | A1B2 | A0B2 |      |      |  |

| 3 | A2B3 | A1B3 | A0B3 |      |      | •    |  |

| 4 | A1B4 | A0B4 |      |      |      |      |  |

| 5 | A0B5 |      |      |      |      |      |  |

Figure 3.8: Summation of Partial Product

This new technique of computing the sticky bit is much more efficient in terms of both hardware complexity and speed in comparison to the computation of the sticky bit directly from input operands.

# 3.8 A New technique for Computing the Exponent

It was mentioned earlier that the exponent data path is much slower than the mantissa section. The main reason for low performance of the exponent data path is due to the need of three serial adders for computing the exponent. To improve the performance of the exponent computation a new technique has been developed that reduces the number of

serial adders from three to two. This new technique will be illustrated through the following examples.

In floating point multiplication the exponent of the two operands are added together to generate the exponent of the result. As the exponents are represented by biased code (Characteristic) a correction is necessary.

The characteristic of A is:

CA = EA + 127

The characteristic of B is:

CB = CB + 127

Adding the two characteristic gives:

CA + CB = EA + EB + 254

The characteristic of the result should be:

C(A+B) = (EA + EB) + 127

Thus, correct the exponent by subtracting the bias : C(A+B) = CA+CB-127

Let's call the corrected characteristic of the result CR

$$CR = CA + CR_{temp} + V$$

where:

$$CR_{temp} = CB - bias$$

V is the overflow bit from the mantissa

In the next first two examples, only the computation of CR\_temp will be analyzed. CR temp will be computed using 2's complement addition that is

$$CR_{temp} = CB - Bias = CB + Bias_bar + 1$$

Example 1:

CB = 10000000

Bias = 011111111

CB 10000000

Bias\_bar 10000000

00000001

CR\_temp 100000001 00000001

Note in 2's complement addition the most significant bit of the result indicates the sign bit. That is if the most significant bit (E) is 1 the sign of the result is positive otherwise it is negative. Therefore, the sign of the result for example 1 is positive.

### Example 2:

CB = 11100000 Bias = 01111111

CB 11100000

Bias\_bar 10000000

00000001

CR\_temp 101100001 01100001

Note the final results of the above two examples can be simply obtained by inverting the most significant bit (MSB) of CB and adding a one to its least significant bit. The result obtained using this technique are shown on the right hand side of the final results written in bold form. The question is how to detect the sign of the result obtained using this new technique. The sign can be simply detected by looking at the most significant bit of CB, that is if MSB of CB is a one then the result is positive otherwise it is negative.

In the previous two examples the final results are positive, the next example will justify that the new technique of computing CR\_temp also holds for negative final result.

Example 3:

$$CB = 00001000$$

Bias = 01111111

| CB          | 00001000  |          |

|-------------|-----------|----------|

| Bias_bar    | 10000000  |          |

|             | 00000001  |          |

| CR_temp     | 010001001 | 10001001 |

| CR _tempbar | 01110110  | 01110110 |

|             | 00000001  | 00000001 |

|             | 01110111  | 01110111 |

Since the most significant bit of CR\_temp (E) in example 3 is zero, CR\_temp must be complemented and then a one is added to its least significant bit (LSB) to obtain the correct result. Both final results obtained using 2's complement addition and the new technique are the same. Therefore the new technique holds for both E=0 and E=1.

In the next examples, it will be investigated whether the adjustment of CR\_temp is necessary when E=0, by looking at the full computation of the exponent (that is computing CR). Since in the previous examples it was demonstrated that computing CR\_temp using 2's complement addition gives the same result as the new technique, for the coming examples the new technique will be used to compute CR\_temp.

### Example 4:

| CA = 10001100 |                   | CB = 00001000 | V= 0 |

|---------------|-------------------|---------------|------|

| CR_temp       | 10001001          |               |      |

| CA            | 10001100          |               |      |

| CR'           | 100010101         |               |      |

| V             | 00000000          |               |      |

| CR            | <b>0</b> 00010101 |               |      |

$$E1 = 0$$

$E2 = 1$   $E3 = 0$

where:

E1 is MSB of CB

E2 is MSB of CR'

E3 is MSB of CR

Since E1 is zero the intermediate result (CR\_temp) is negative. Therefore CR' is the sum of a negative number (CR\_temp) and a positive number (CA). In this case the MSB of CR' indicates the sign of CR'. Since E2 equals one for the above example the result is positive 21 as expected. The next example illustrates the condition when both E1 and E2 are zero.

### Example 5:

$$CA = C00011111$$

$CB = 00011000$   $V = 1$

CR\_temp 10011001

CA 00001111

CR' 010101000

V <u>00000001</u>

CR **0**10101001

E1 = 0 E2 = 0 E3 = 0

Since E1 and E2 are both zero, the output CR is in two's complement form. Is it necessary to adjust CR to get the true result? No, since the minimum biased exponent in IEEE

standard is zero, negative biased exponent indicates an underflow condition. Therefore, if CR is negative it not necessary to adjust the exponent rather it will be setted to underflow. In general, if both E1 and E2 are zero, they indicate an underflow condition independent of E3.

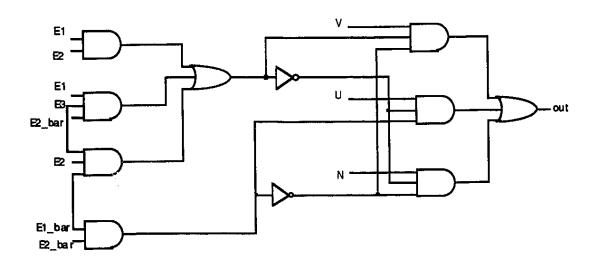

If E1 is one and at the same time either E2 or E3 are one, it indicates an overflow condition. If E1 equals one it means that the intermediate result (CR\_temp) is positive. Therefore, the subsequent additions involve the addition of positive numbers and consequently the most significant bit of the result is an overflow bit, not a sign bit as shown in example 3. Table 3.2 shows how overflow and underflow conditions are detected using the three bits E1, E2 and E3. Figure 3.9 shows the circuit used to detect underflow and overflow conditions.

### Example 6:

|         | CA = 111111110    | CB = 10000000 | V = 1 |

|---------|-------------------|---------------|-------|

| CR_temp | 00000001          |               |       |

| CA      | <u>11111110</u>   |               |       |

| CR'     | <b>0</b> 11111111 |               |       |

| V       | 00000000          |               |       |

| CR      | 100000000         |               |       |

E1 = 1 E2 = 0 E3 = 1

| E1 | E2 | E3 | U | V  |

|----|----|----|---|----|

| 0  | 0  | Х  | 1 | 0  |

| 0  | 0  | 1  | 1 | 0  |

| o  | 1  | 1  | 0 | 1  |

| 1  | 0  | 1  | 0 | 1  |

| 1  | 1  | 0  | 0 | 1  |

| 1  | 1  | 1  | 0 | 11 |

Table 3.2: Detection of Underflow and Overflow Conditions

Figure 3.9: Underflow and Overflow Detector