### University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

2013

# Experimental Comparison of Store-and-Forward and Wormhole NoC Routers for FPGA's

Krunal Jetly University of Windsor

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### **Recommended** Citation

Jetly, Krunal, "Experimental Comparison of Store-and-Forward and Wormhole NoC Routers for FPGA's" (2013). *Electronic Theses and Dissertations*. Paper 4856.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# Experimental Comparison of Store-and-Forward and Wormhole NoC Routers for FPGA's

By

**Krunal Jetly**

A Thesis Submitted to the Faculty of Graduate Studies Through Electrical and Computer Engineering In Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada 2013

### © 2013 Krunal Jetly

All Rights Reserved. No Part of this document may be reproduced, stored or otherwise retained in a retrieval system or transmitted in any form, on any medium by any means without prior written permission of the author

# Experimental Comparison of Store-and-Forward and Wormhole NoC Routers for FPGA's

By

Krunal Jetly

APPROVED BY:

G. Zhang Mechanical, Automotive, and Materials Engineering

> R. Rashid Electrical and Computer Engineering

> M. A. S Khalid, Advisor Electrical and Computer Engineering

> > April, 2013

### Author's Declaration of Originality

I hereby certify that I am the sole author of this thesis and that no part of this thesis has been published or submitted for publication.

I certify that, to the best of my knowledge, my thesis does not infringe upon anyone's copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material from the work of other people included in my thesis, published or otherwise, are fully acknowledged in accordance with the standard referencing practices. Furthermore, to the extent that I have included copyrighted material that surpasses the bounds of fair dealing within the meaning of the Canada Copyright Act, I certify that I have obtained a written permission from the copyright owner(s) to include material from two different theses as follows:

- (i) From Chapter 3 section 3.1.1.3 (Routing Algorithm), Figure 3.1, Figure 3.2, Figure 3.4, Figure 3.7, Figure 3.8 from Thesis by Mike Brugge "Design and Evaluation of a Parameterizable NoC Router for FPGAs". Sep 21 2009

- (ii) From Chapter 2 Section 2.3 (Interface and Signals), Chapter 3 section 3.3.1(Adapter Overview), Chapter 4 Section 4.3 (NIOS II Programing) and section 4.4 (Modelsim Simulation), Figure 3.5, Figure 3.6, figure 4.6 and figure 4.9 From Thesis by Matt Murawski "NoC Prototyping on FPGAs: Component Design, Architecture Implementation and Comparison". May 18 2012

I have included copies of such copyright clearance permission forms to my Appendix A and the permissions were received through copyright holder's email. I declare that this is a true copy of my thesis, including any final revisions, as approved by my thesis committee and the Graduate Studies office, and that this thesis has not been submitted for a higher degree to any other University or Institution.

### Abstract

Network on Chip (NoC) is an interconnection paradigm which is scalable and efficient for connecting increasing number of components on Field Programmable Systems on Chip (FPSOC). The router is a key component in NoC that impacts area performance, power consumption, etc. In this thesis we evaluate and compare two different router designs using real world benchmark. The first router uses Store-And-Forward strategy (SAF) and XY routing algorithm and the second router uses Wormhole (WH) as forwarding strategy and source routing algorithm. These routers were used to implement 4x4 mesh NoCs. A multi processor system benchmark obtained from Altera was implemented in each NoC. This enabled us to evaluate and compare the routers using the real world benchmark design. The evaluation metrics used were area, throughput, power consumption and maximum clock frequency. Experiment results show that the SAF router is superior to the WH Router.

### Acknowledgements

It is an honor for me to have worked with Dr. Mohammed A. S. Khalid throughout my Meng degree and Master's in applied science degree here at the University of Windsor. His guidance, encouragement, wisdom and support carried me through the course of this thesis. My deepest gratitude goes out to him. My appreciation also goes out to my thesis committee members, G.Zhang and R.Rashid, for their time to sit on my committee and reviewing my thesis

I want to thanks my family for all their constant support and encouragement. Thanks to my parents for their understanding me. Thanks for helping to keep me focused day after day.

Finally, I need to acknowledge my friends and fellow graduate students at the University of Windsor. Matt Murawski and Mike Brugge thank you for your friendship and guidance. Thanks to Matt for your company and taking those long calls at your office and helping me out in my Research. You could always provide me with the help I needed. Lastly, thanks to the rest of my colleagues; amanjot, manveen who made this great milestone in my life so enjoyable.

# Table of Contents

| Author's Declaration of Originalityiv   |

|-----------------------------------------|

| Abstractvi                              |

| Acknowledgementsvii                     |

| List of Figuresxi                       |

| List of Tablesxiii                      |

| List of Abbreviationsxiv                |

| Chapter 1: Introduction                 |

| 1.1 Thesis Objectives                   |

| 1.2 Thesis Organization                 |

| Chapter 2: Background and Previous Work |

| 2.1 FPGA Technology                     |

| 2.2 Overview of NoC                     |

| 2.2.1 NoC Building Blocks               |

| 2.2.1.1 Links                           |

| 2.2.1.2 Network Adapters                |

| 2.2.1.3 Routing Node                    |

| 2.2.2 Parameters of NoC                 |

| viii                                    |

| 2.3 Interfaces and Signals [22]                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 2.3.1 Wishbone                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

| 2.3.1.1 Signals                                                                                                                                                                                                                                                                                                                                                                                                         | 9                                                                                            |

| 2.3.2 Avalon Interface                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| 2.3.2.1 Avalon-MM                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

| 2.3.2.2 Avalon-ST                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                                                           |

| 2.3.2.3 Avalon-MM Tristate                                                                                                                                                                                                                                                                                                                                                                                              | 19                                                                                           |

| 2.3.2.4 Clock                                                                                                                                                                                                                                                                                                                                                                                                           | 20                                                                                           |

| 2.3.2.5 Interrupt                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                                                           |

| 2.3.2.6 Conduit                                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                                                           |

| 2.4 CAD Tools for NoC Implementation on FPGAs                                                                                                                                                                                                                                                                                                                                                                           | 20                                                                                           |

| 2.4.1 Altera Quartus II                                                                                                                                                                                                                                                                                                                                                                                                 | 20                                                                                           |

| 2.4.2 Altera SOPC Builder                                                                                                                                                                                                                                                                                                                                                                                               | 22                                                                                           |

| 2.4.3 Nios II Embedded Design Suite (EDS)                                                                                                                                                                                                                                                                                                                                                                               | 22                                                                                           |

| 2.4.4 Mentor Graphics ModelSim                                                                                                                                                                                                                                                                                                                                                                                          | 22                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| 2.5 Related Work                                                                                                                                                                                                                                                                                                                                                                                                        | 22                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| 2.5 Related Work                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 2.5 Related Work                                                                                                                                                                                                                                                                                                                                                                                                        | 24                                                                                           |

| 2.5 Related Work<br>2.6 Summary<br>Chapter 3: Description of SAF and WH Router Architecture                                                                                                                                                                                                                                                                                                                             | 24<br>                                                                                       |

| <ul> <li>2.5 Related Work</li> <li>2.6 Summary</li> <li>Chapter 3: Description of SAF and WH Router Architecture</li> <li>3.1 Functionality</li> </ul>                                                                                                                                                                                                                                                                  | 24<br>25<br>25<br>25                                                                         |

| <ul> <li>2.5 Related Work</li> <li>2.6 Summary</li> <li>Chapter 3: Description of SAF and WH Router Architecture</li></ul>                                                                                                                                                                                                                                                                                              | 24<br>25<br>25<br>25<br>25                                                                   |

| <ul> <li>2.5 Related Work</li> <li>2.6 Summary</li> <li>Chapter 3: Description of SAF and WH Router Architecture</li> <li>3.1 Functionality</li> <li>3.1.1 Protocols and Algorithms</li> <li>3.1.1.1 Flow Control</li> </ul>                                                                                                                                                                                            | 24<br>25<br>25<br>25<br>25<br>26                                                             |

| <ul> <li>2.5 Related Work</li> <li>2.6 Summary</li> <li>Chapter 3: Description of SAF and WH Router Architecture</li> <li>3.1 Functionality</li> <li>3.1.1 Protocols and Algorithms</li> <li>3.1.1.1 Flow Control</li> <li>3.1.1.2 Switching Mode</li> </ul>                                                                                                                                                            | 24<br>25<br>25<br>25<br>25<br>25<br>25<br>26<br>26                                           |

| <ul> <li>2.5 Related Work</li> <li>2.6 Summary</li> <li>Chapter 3: Description of SAF and WH Router Architecture</li> <li>3.1 Functionality</li> <li>3.1.1 Protocols and Algorithms</li> <li>3.1.1.1 Flow Control</li> <li>3.1.1.2 Switching Mode</li> <li>3.1.1.3 Routing Algorithm [21]</li> </ul>                                                                                                                    | 24<br>25<br>25<br>25<br>25<br>25<br>26<br>26<br>26<br>30                                     |

| <ul> <li>2.5 Related Work</li> <li>2.6 Summary</li> <li>Chapter 3: Description of SAF and WH Router Architecture</li> <li>3.1 Functionality</li> <li>3.1.1 Protocols and Algorithms</li> <li>3.1.1.1 Flow Control</li> <li>3.1.1.2 Switching Mode</li> <li>3.1.1.3 Routing Algorithm [21]</li> <li>3.1.1.4 Scheduling</li> </ul>                                                                                        | 24<br>25<br>25<br>25<br>25<br>25<br>25<br>26<br>26<br>26<br>30<br>30                         |

| <ul> <li>2.5 Related Work</li> <li>2.6 Summary</li> <li>Chapter 3: Description of SAF and WH Router Architecture</li> <li>3.1 Functionality</li> <li>3.1.1 Protocols and Algorithms</li> <li>3.1.1.1 Flow Control</li> <li>3.1.1.2 Switching Mode</li> <li>3.1.1.3 Routing Algorithm [21]</li> <li>3.1.1.4 Scheduling</li> <li>3.2 Router Implementation</li> </ul>                                                     | 24<br>25<br>25<br>25<br>25<br>25<br>26<br>26<br>26<br>30<br>30<br>30<br>32                   |

| <ul> <li>2.5 Related Work</li> <li>2.6 Summary</li> <li>Chapter 3: Description of SAF and WH Router Architecture</li> <li>3.1 Functionality</li> <li>3.1.1 Protocols and Algorithms</li> <li>3.1.1.1 Flow Control</li> <li>3.1.1.2 Switching Mode</li> <li>3.1.1.3 Routing Algorithm [21]</li> <li>3.1.1.4 Scheduling</li> <li>3.2 Router Implementation</li> <li>3.2.1 Internal Structure and Data Transfer</li> </ul> | 24<br>25<br>25<br>25<br>25<br>26<br>26<br>26<br>26<br>30<br>30<br>30<br>30<br>32<br>36       |

| <ul> <li>2.5 Related Work</li></ul>                                                                                                                                                                                                                                                                                                                                                                                     | 24<br>25<br>25<br>25<br>25<br>26<br>26<br>26<br>30<br>30<br>30<br>30<br>30<br>32<br>36<br>37 |

| Chapter 4: NoC Implementation and Evaluation Framework            | 45 |

|-------------------------------------------------------------------|----|

| 4.1 Real World Benchmark Design                                   | 45 |

| 4.2 Implementation of NoC in SOPC Builder Add description of SOPC | 47 |

| 4.3 Nios II Programming                                           | 51 |

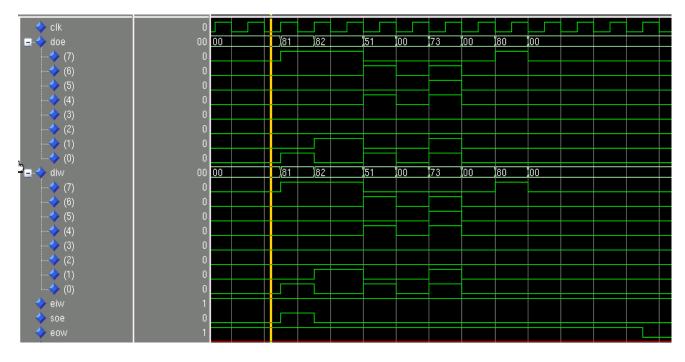

| 4.4 Modelsim Simulation                                           | 54 |

| 4.5 Re-design of SAF Router                                       | 55 |

| 4.6 Summary                                                       | 56 |

| Chapter 5: Experimental Comparison                                | 57 |

| Results                                                           | 57 |

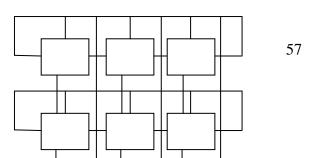

| 5.1 Mesh Topology                                                 | 57 |

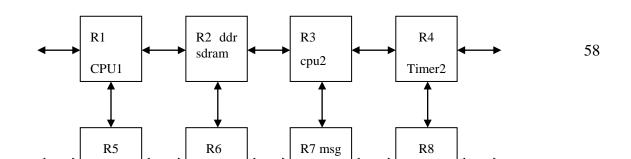

| 5.1.1 Placement of the IP Cores                                   | 58 |

| 5.2 Design Space Exploration and Comparison of SAF and WH Routers | 59 |

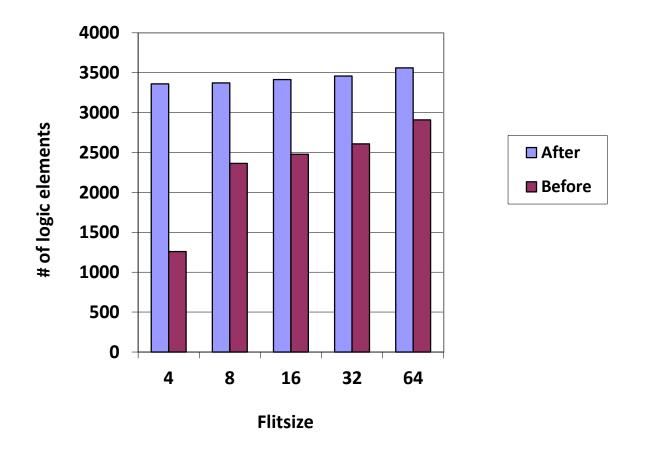

| 5.2.1 Redesign the SAF router                                     | 59 |

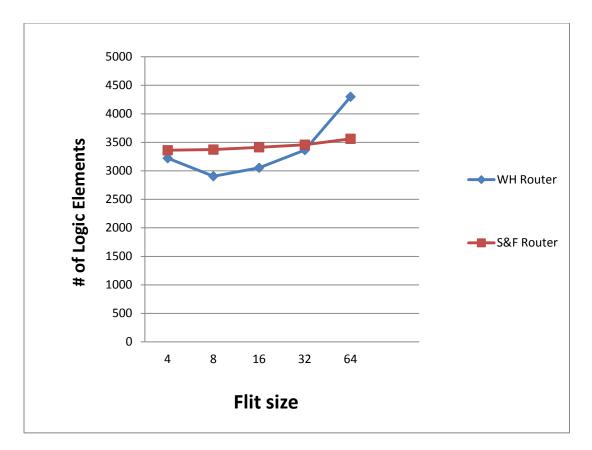

| 5.2.2 Area Results                                                | 60 |

| 5.2.3 Power Consumption Results                                   | 64 |

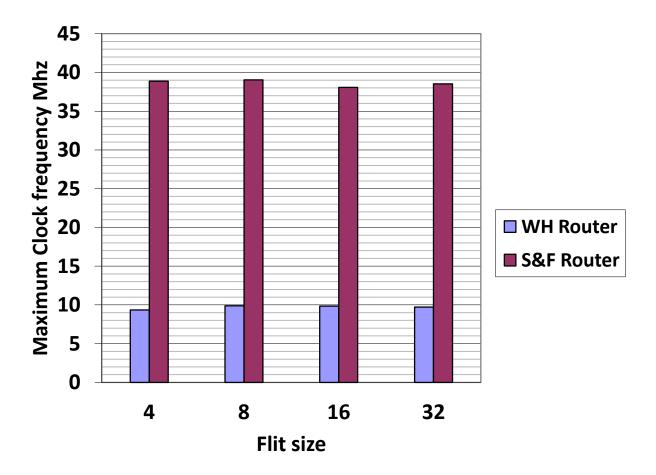

| 5.2.4 Clock Frequency Results                                     | 65 |

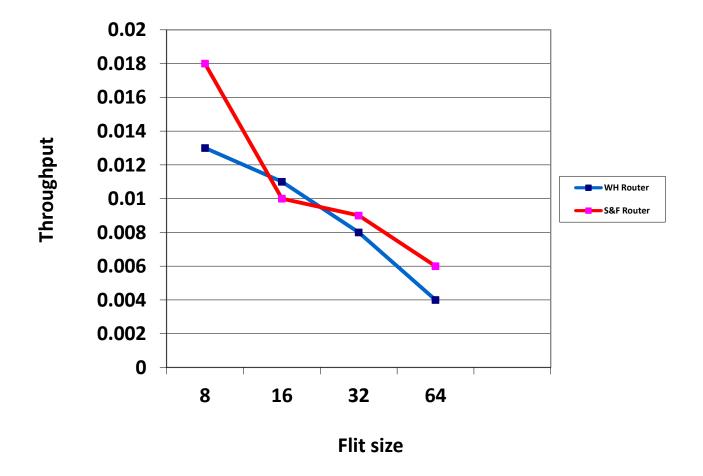

| 5.2.5 Throughput Results                                          | 66 |

| 5.3 Conclusion                                                    | 68 |

| Chapter 6: Conclusions and Future Work                            | 69 |

| 6.1 Research Contributions                                        | 70 |

| 6.2 Future Work                                                   | 70 |

| Appendix A                                                        | 71 |

| Copyright Permissions                                             | 71 |

| References                                                        | 74 |

| VITA AUCTORIS                                                     | 77 |

# List of Figures

| Figure 2.1: Altera Logic Element Architecture [5]                    | 6  |

|----------------------------------------------------------------------|----|

| Figure 2.2: A NoC Interconnection Networks 4 Basic Functional Blocks | 7  |

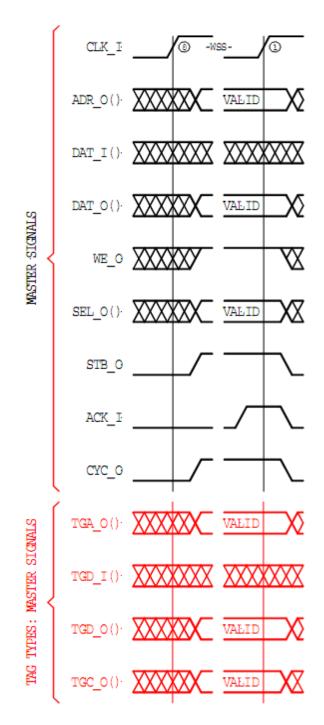

| Figure 2.3: Single Transfer Hand Shake                               | 11 |

| Figure 2.4: Single Read Transfer                                     | 12 |

| Figure 2.5: Single Write Request Signals                             | 13 |

| Figure 2.6: Wishbone RMW                                             | 14 |

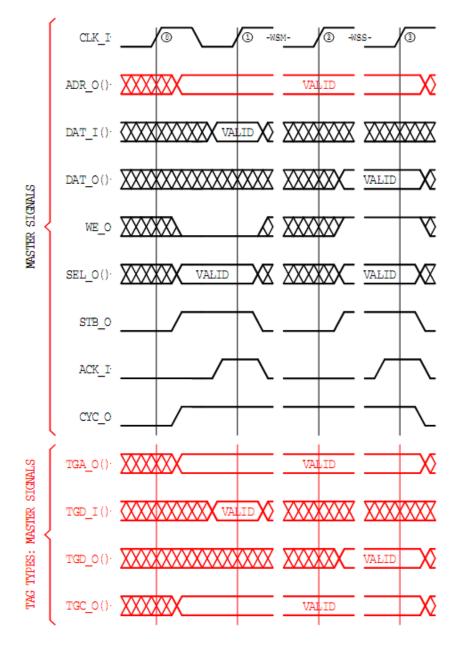

| Figure 2.7: Block Read Request for Wishbone                          | 15 |

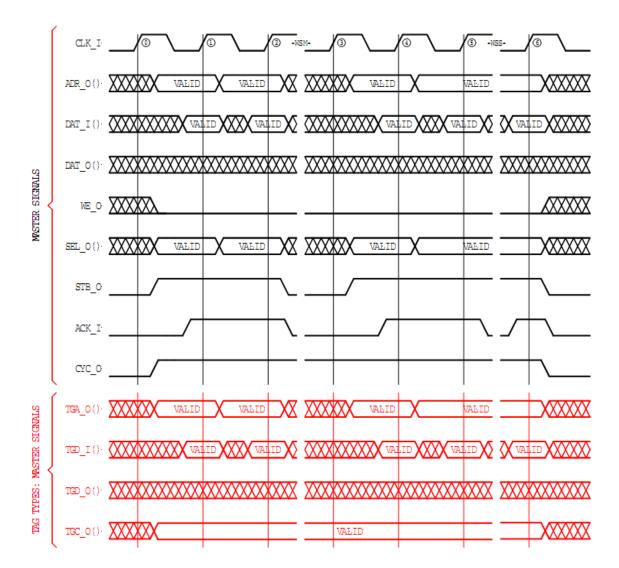

| Figure 2.8: Incrementing Bursts for Wishbone                         | 17 |

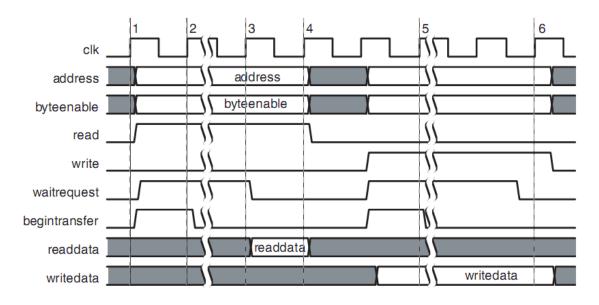

| Figure 2.9: Avalon MM Transfer                                       | 19 |

| Figure 2.10: Quartus II Design Flow                                  | 21 |

| Figure 3.1: Coordinate Configuration for XY Routing                  | 27 |

| Figure 3.2: Configuration of Local Ports for XY Routing              |    |

| Figure 3.3: Port correlation in routing table                        | 29 |

| Figure 3.4: SAF Routers Exterior Structure                           | 31 |

| Figure 3.5: WH routers Exterior Structure                            | 32 |

| Figure 3.6: WH router's Internal Structure                           |    |

| Figure 3.7: SAF Router's Internal Structure                          | 35 |

| Figure 3.8: Architecture of Switching Fabric                         | 37 |

| Figure 3.9: Adapters Overview                                        |    |

| Figure 3.10: Adapter Internal Design Overview                        | 40 |

| Figure 3.11: Avalon Wish bone Glue Logic                             | 41 |

| Figure 3.12: Slave Sampler Process Flow Chart                        | 42 |

| Figure 3.13: Master Sampler Process Flow Chart                       | 43 |

| Figure 4.1: Mapping of Benchmark Design Components on 4x4 NoC                                   |

|-------------------------------------------------------------------------------------------------|

| Figure 4.2: Altera Multiprocessor Design Example47                                              |

| Figure 4.3: NoC Parameters in SOPC Builder                                                      |

| Figure 4.4: SAF Router based NoC Implemented in SOPC Builder                                    |

| Figure 4.5: SAF Routers NoC Connected to Slave Components                                       |

| Figure 4.6: Bridging Example51                                                                  |

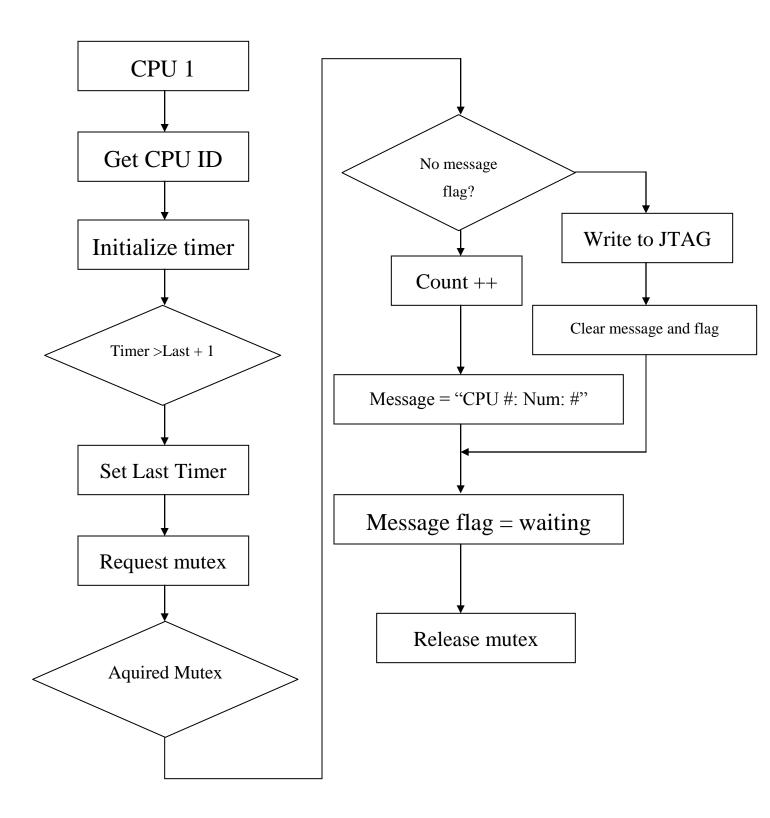

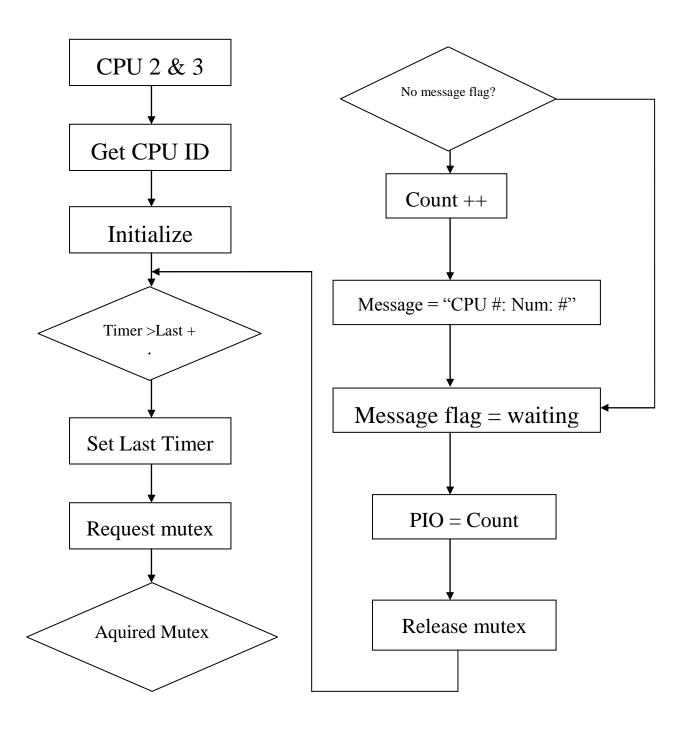

| Figure 4.7: CPU 1 Benchmark Flowchart52                                                         |

| Figure 4.8: CPU2 and CPU 3 Benchmark Flowchart53                                                |

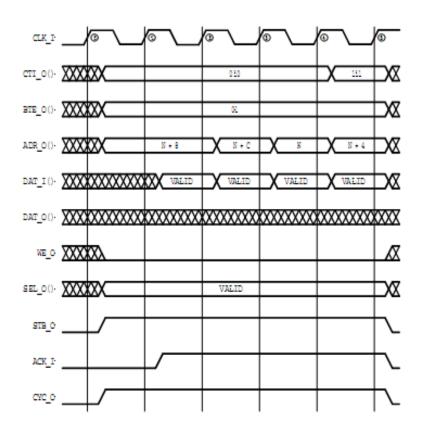

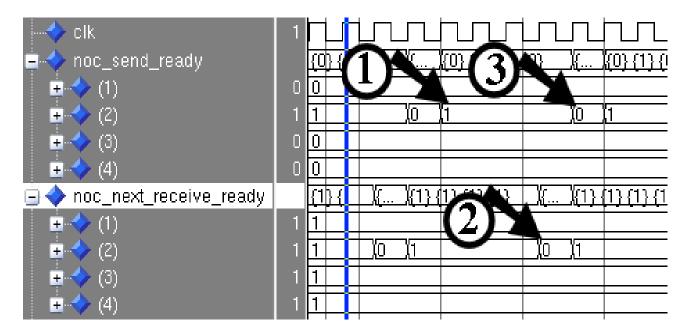

| Figure 4.9: WH Routers Regional Handshaking54                                                   |

| Figure 4.10: RF Routers Regional Handshaking55                                                  |

| Figure 5.1: Mesh and Torus Topology                                                             |

| Figure 5.2: 10-node ring topology                                                               |

| Figure 5.3: Placement and Routing                                                               |

| Figure 5.4: Comparison of SAF router area consumption before and after redesign60               |

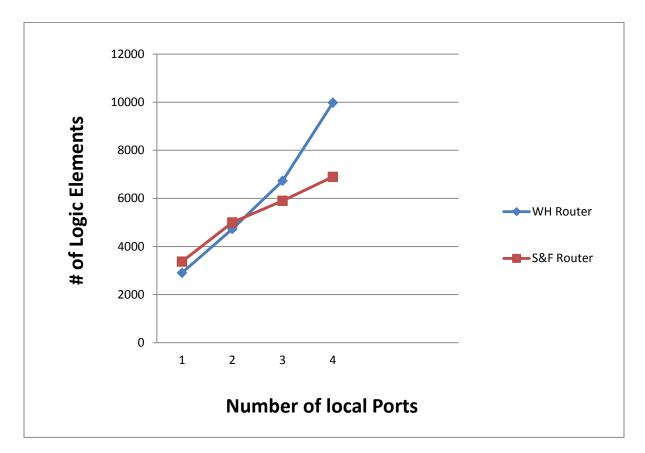

| Figure 5.5: Area consumption of standalone routers with respect to flit size61                  |

| Figure 5.6: Area consumption of standalone routers with respect to number of local ports.62     |

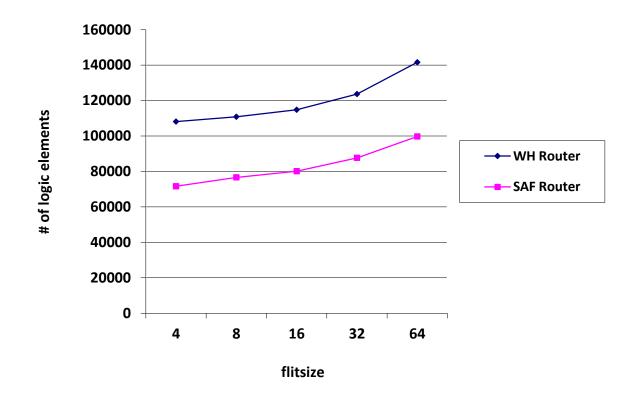

| Figure 5.7: Area consumption of the whole NoC with respect to flit size (# of local ports is 1) |

|                                                                                                 |

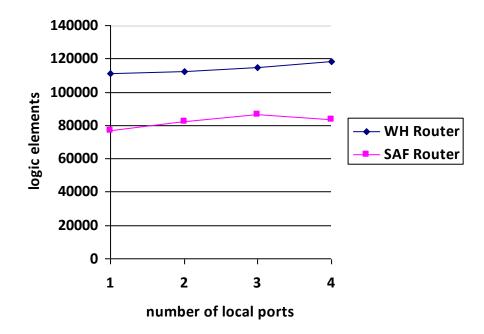

| Figure 5.8: Area of consumption for whole NoC with respect to number of local ports (flit       |

| size=8)64                                                                                       |

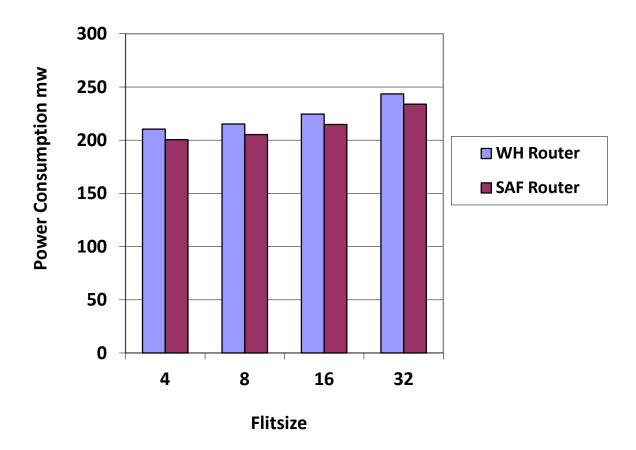

| Figure 5.9: Power Consumption Versus flit size for standalone routers                           |

| Figure 5.10: Maximum Clock frequency versus flit size for standalone routers                    |

| Figure 5.11: Throughput versus flit size for the whole NoC                                      |

# List of Tables

| Table 2.1: Cycle Type Identifier | 16 |

|----------------------------------|----|

| Table 2.2: Burst Type Extension  | 16 |

| Table 3.1: Request Type Design   | 57 |

# List of Abbreviations

### Abbreviation Definition

| ALUT | Adaptive Look Up Table                  |

|------|-----------------------------------------|

| ASIC | Application Specific Integrated Circuit |

| AVM  | Avalon Master                           |

| AVS  | Avalon Slave                            |

| AWB  | Avalon-Wishbone                         |

| BE   | Best Effort                             |

| BTE  | Burst Type Extension                    |

| CAD  | Computer Aided Design                   |

| CLK  | Clock                                   |

| CPU  | Central Processing Unit                 |

| CS   | Chip Select                             |

| CTI  | Cycle Tag Identifier                    |

| DDR  | Double Data Rate                        |

| EDS  | Embedded Design Suite                   |

| FIFO | First In, First Out                     |

| FPGA | Field Programmable Gate Array           |

| GS   | Guaranteed Service                      |

| HDL  | Hardware Description Language           |

| I/O  | Input / Output                          |

| IC   | Integrated Circuit                      |

| IDE  | Integrated Development Environment      |

| IP   | Intellectual Property                   |

|      |                                         |

| IRQ   | Interrupt Request                |

|-------|----------------------------------|

| JTAG  | Joint Test Action Group          |

| QoS   | Quality of Service               |

|       |                                  |

| KB    | Kilo Byte                        |

| LAN   | Local Area Network               |

| LE    | Logic Element                    |

| LED   | Light Emitting Diode             |

| MB    | Mega Byte                        |

| MPSoC | Multi-Processor System on Chip   |

| NA    | Network Adapter                  |

| NoC   | Network on Chip                  |

| OCP   | Open Core Protocol               |

| OE    | Output Enable                    |

| OSI   | Open Systems Interconnection     |

| PIO   | Peripheral Input Output          |

| PWR   | Parameterizable Wormhole Router  |

|       |                                  |

| RAM   | Random Access Memory             |

| RISC  | Reduced Instruction Set Computer |

| SAF   | Store and Forward                |

| SDRAM | Synchronous Dynamic Random       |

| 1     | Access Memory                    |

| SoC   | System on Chip                   |

| SOPC  | System on Programmable Chip      |

| TDM   | Time Division Multiplexing       |

| UART  | Universal Asynchronous           |

| I     | Receiver/Transmitter             |

| VC    | Virtual Channel                  |

| VCI   | Virtual Component Interface      |

|       | -                                |

| Virtual Cut Through                |

|------------------------------------|

| Very High Speed Integrated Circuit |

| Hardware Description Language      |

| Very Large Scale Integration       |

| Wishbone                           |

| Wormhole                           |

|                                    |

### **Chapter 1: Introduction**

### INTRODUCTION

The world of silicon integrated circuits has changed a lot in recent years. We have seen the feature size of IC decreased from 90nm to 40nm as predicted by moore's law. This has enabled systems on chip (SoC) which can implement complex systems on a single chip which earlier needed the Printed Circuit Boards. The electronic industry has continuously changed and evolved by packing more functionality in smaller area of silicon, which has resulted in Increasing transistor density, higher operating frequencies, shorter time-to-market and reduced product life cycle [1]. As the number of computational modules in single IC continuous to increase the new interconnection paradigm is needed that is efficient and scalable.

The electronic industry started from IC which used to perform basic logic functions and then moved to PLD, CPLD, micro controllers and microprocessors along with these digital blocks complex modules that could implement computationally intensive task were implemented on single IC's. Further, with increase in transistor density it was feasible to add more of these blocks in smaller area which lead us to the embedded systems. An embedded system is a combination of processor and supporting digital blocks which is designed to perform a specific task. In today's technologically advanced world embedded system plays an important role as we can find embedded systems almost everywhere for example cameras, DVD players, washing machines and also in large stationary units like cellular base stations and factory controllers. At the present time SoC enabled us to implement a complete embedded system on a single chip.

As the transistor density is still increasing it was possible to incorporate more digital blocks and so SoCs started to contain many hardware and/or software blocks, such as processors, DSPs, memories, peripheral controllers, gateways, and other custom logic blocks. SoCs have just started to get intricately complex and in future there will be more issues coming up with more shrinkage in size of transistors. Interconnection Techniques and routing methodologies has become one of the most research intensive areas in SoC designs [2]. The issues concerned with interconnection methodologies and routing methodologies has been one of the most research intensive areas as it affects each facet of SoCs design. Interconnection methods greatly impact cost and performance of a SoC.

In earlier days the number of blocks in single IC were limited hence a point to point or simple Bus interconnection was used. But, as the designs started to get complex Bus based systems could not handle the increase in number of blocks. The routing methods used after SoCs introduction was point to point connection between IP's. Dedicated wires were effective until the system were not much complex and less number of the IP's were there on the SoC's, but as the complexity increased the routing resources were consumed too quickly. Also dedicated wiring leads to decrease in the resource reusability and flexibility. So to overcome this limitation designer incorporated usage of shared bus where a set of wire is common between different multiple cores of the system this increased the reusability and scalability of the resources. For achieving this Master and slave scheme has been carried out which uses control signals and slave waits for the data to be received or requested from the master. However, with the systems started having more masters and slave the contention increased and results to bottleneck which gets worse with increase in complexity. Along with this there is concerns regarding complication of the protocols while trying to eliminate the scalability problems. Design and verification times also grow with SoC complexity [3].

ASIC designs are application specific ICs they are used to replace the time consuming part of the software. ASIC's help in increasing the speed of the system by great extent. The ASIC design not just concentrates on increasing speed it also decreases area and power consumption of the system. ASICs have been a good implementation for large amount of production because ASIC is not easy to implement as the systems are very complex and even though automation has helped the industry ASIC designing takes away a lot of engineering resources. So to overcome this difficulty the ASICs have started to be replaced by FPGA's. The competitive world of technology has made a new requirement of bringing the new technology out as soon as possible, which is stated as "time to market". This has made the designers to shift to other resources which are much faster to design and validate. FPGA has been an answer to that and this is the reason why we see usage of FPGA when there is a small scale requirement FPGA is the viable choice but for large scale production still ASIC is preferred.

FPGA has captured significant part of the IC market. Before FPGA were replacing small units as it was not containing much of the logic elements and because of that we did not care of the routing carried out in FPGAs .With the increase in transistor density more number of logic elements were packed into FPGAs and current FPGAs can be considered to be FPSoCs (Field Programmable Systems on Chips). With the current trend of integration of more complex FPSoC's we need a better communication infrastructure and protocol which will alleviate the problem of scalability by supporting multiple concurrent connections between IP cores and along with that it should allow the reuse of area specific pre-designed and pre-tested IP cores.

NoC is a promising interconnection paradigm that can be used in SoC's and FPSoC's. The Basic concept behind NoC is similar to computer networks, multiple computers are connected to different routers and these routers are connected to each other using different topologies. The same concept is used in NoC's with IP cores replacing computers. Much research needs to be done in Exploring the design space of NoC implementation in FPGA's

This Thesis is intended to shed light on some of the tradeoffs involved in NoC implementation on FPGA's. We implemented two different Router designs and compared them using a real world benchmark application. Previous research has evaluated compared router designs using data from traffic generators which is not as good as the traffic generated by a real world application. Our research results will be useful to the future designers of NoC based systems on FPGAs.

### **1.1 Thesis Objectives**

The main goal of this research is to evaluate and compare two NoC routers developed in previous research work. The Evaluation metrics used to compare the two routers are area, flit – size, Ports, power, throughput and clock frequency. Our research results will help designers working on implementation of large complex NoC based systems on FPGAs by allowing them to make informed choices on design tradeoffs. This research has the following major objectives:

- 1. Investigate SAF router implementation on FPGAs.

- 2. Developed network adapter based on wishbone protocol that could be interfaced to both SAF and WH router.

- 3. Implement two mesh NoCs using SAF and WH Routers respectively, to run a real world bench mark design.

- 4. The two Mesh NoCs were synthesized and results were evaluated and compared using metrics area, power, clock and throughput.

For the first objective, we have investigated and understood the functionality and design of SAF Router, WH router and NoC adapters. This led us to make changes to SAF Router and NoC adapters. Testing was done with the help of a realistic benchmark. The experimental framework was developed in VHDL, allowing NoC synthesis in Altera Quartus II design environment (Simulation was done using Modelsim). SOPC Builder CADtool was used to implement the mesh to NoCs. NIOSII IDE was used to run the Benchmark design on the NoCs implemented in FPGA.

#### **1.2 Thesis Organization**

The remainder of this thesis is organized as follows. In chapter 2, we present the background and related work for FPGAs and NoCs. Chapter 3 covers detailed description of the routers used and the network adapters. Chapter 4 describes NoC implementation and Evaluation framework. Chapter 5 presents experimental comparison and analysis. Chapter 6 concludes the thesis and discusses possible future work.

### **Chapter 2: Background and Previous Work**

In this chapter, we will go through previous work done and also the background that is relevant to this research is presented. This chapter begins with a brief overview of FPGA technology, detailing the benefits. Then describe different aspects of Network-on-Chip (NoC). This is followed by description of the standard sockets used in NoC's. We cover the Avalon [4] and Wishbone interfaces [5]. Finally the CAD tools used in our research are briefly described and the chapter concludes with the description of related research.

### 2.1 FPGA Technology

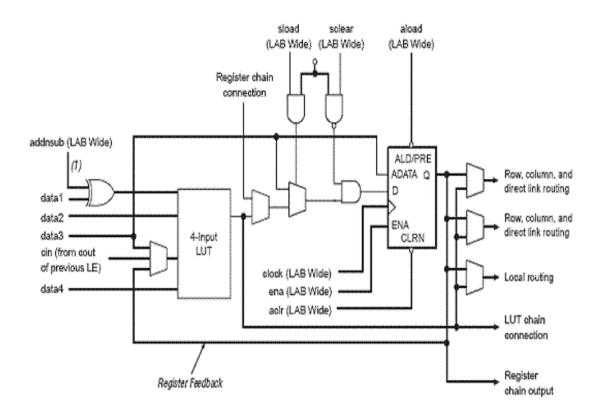

Field Programmable Gate Arrays (FPGA) is special integrated circuit, in which the logic elements, routing resources are pre-fabricated. Different digital circuits can be specified using hardware description languages such as VHDL and Verilog and then synthesized and implemented on FPGAs. In many real world applications which requires low to medium volumes FPGAs have replaced ASICs due to their many advantages such as low non recurring expenses (NRE), fast time to market and flexibility. FPGAs are made up of Logic Elements (LE), in the form of look-up tables, which are used to implement custom logic. FPGAs have also evolved and with advances in technology and contain advanced components, such as DSP blocks, memory blocks, serial interfaces and hard or soft CPU cores. In this thesis, FPGAs are used as implementation fabric to evaluate and compare NoC routers.

Figure 2.1: Altera Logic Element Architecture [5]

### 2.2 Overview of NoC

This section describes the basic building blocks used in NoCs and their operation.

### 2.2.1 NoC Building Blocks

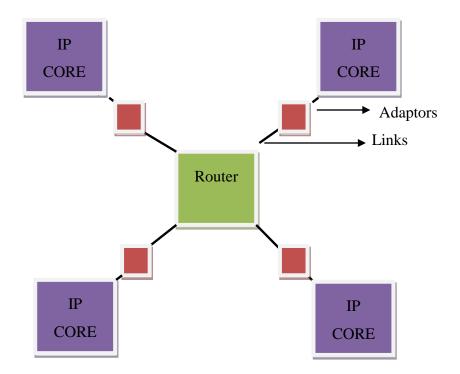

NoC aims to provide a network on the chip which allows effective communication between computational components (IP cores). Figure 2.2 depicts a sample NoC which consists of 4 IP cores which are connected using a single router. An adapter is used to connect an IP Core to the router and a link is used to connect a router to adapter or to another router.

Figure 2.2: A NoC Interconnection Networks 4 Basic Functional Blocks

### 2.2.1.1 Links

This component provides one to one connections for a routing node with a network adapter or another routing node. It also provides separate control lines for connection establishment and teardown.

### 2.2.1.2 Network Adapters

Network Adapters convert the high level protocols (HLP) that IP uses into the packet-based communication protocols of the NoC and vice versa. They are responsible for storing IP core addresses, creating and disassembling messages, forming packets and breaking them into flits, implementing end-to-end flow control, crossing clock domains, and other higher level network issues.

### 2.2.1.3 Routing Node

The Routing node handles the flow of packets (Traffic) in the network based in NoC. It basically runs the routing algorithm which determines the method of flow of packets and it is also a central component of the NoC. The parameters of the routers are thus important as they can affect the performance of the network to a large extent. The parameters of routers are routing algorithm, forwarding strategies, flit size, and number of ports.

#### 2.2.2 Parameters of NoC

Every NoC has its own unique parameters. The three main parameters are: Mapping, Communication Mechanism and Infrastructure. These parameters play an important role in the overall performance of the NoC and so it has been the most important research topic for the NoC researchers. It is preferred that these parameters should be chosen according to the application requirement in order to enhance the NoC performance for that particular application. This thesis attempts to provide an insight into how the choice of parameter selection affects tradeoffs in cost, performance and power consumption of NoCs in FPGAs.

### 2.3 Interfaces and Signals [22]

This Section describes in detail the interfaces used in our thesis along with their protocols and signals used for communication. The standard sockets used in this thesis include Silicore/Opencore.org's Wishbone and Altera's Avalon interfaces.

#### 2.3.1 Wishbone

Wishbone is one of the handshaking protocol, we have used it as a general purpose interface between IP core modules because it's an open source synchronous SoC interconnection architecture. It also has a great range of bandwidth in terms of data transfer speed.

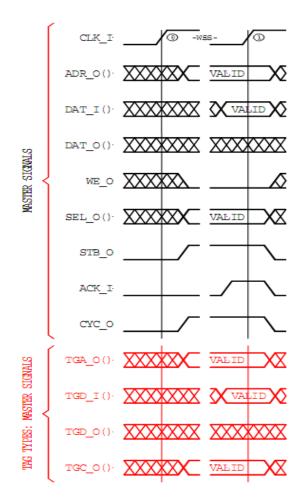

### 2.3.1.1 Signals

Wishbone has a variety of signals, used to provide flexibility and compatibility for attached IP cores. The signals common to both master and slave devices are:

CLK\_I – Clock input. All Wishbone output signals are registered on the rising clock edge.

DAT\_I – Input data array, with a maximum size of 64 bits.

DAT\_O – Output data array, with a maximum size of 64 bits.

RST\_I – Synchronous reset signal

TGD\_I – Input data tag array, containing information regarding the DAT\_I signal. The data tag contains user defined information.

TGD\_O – Output data tag array, associated with the DAT\_O signal.

Master signals include:

ACK\_I – Acknowledge signal used for the handshaking protocol, which indicates the termination of a bus cycle.

ADR\_O – Address output array

CYC\_O – Cycle output signal, indicating a valid bus cycle when asserted. For burst and block cycles, the CYC\_O signal is held high for multiple transfers until the final cycle.

ERR\_I – Error input signal, used as an alternative to ACK\_I to indicate a failed transfer. The exact functionality of this signal depends on the IP core.

LOCK\_O – Lock output signal, used to ensure a transfer is uninterruptable. The exact functionality of this signal depends on the IP core.

RTY\_I – Retry input signal, used as an alternative to ACK\_I. The exact functionality of RTY\_I depends on the IP core.

SEL\_O – Select output array, used for fine control over data granularity. The size of SEL\_O depends on the data width and granularity. For example, 8 bits are used for a 64 bit data bus with byte granularity.

STB\_O – Strobe output signal, used to indicate valid data transfer cycles. Unlike CYC\_O, STB\_O is deasserted after a transfer.

TGA\_O – Address tag output signal, used to contain tag information associated with the ADR\_O signal. For burst transfers, the TGA\_O tag contains Cycle Tag Identifier (CTI), and Burst Type Extension (BTE) tags regarding burst specifics.

TGC\_O – Cycle tag output signal, used to contain tag information regarding a bus cycle. It can be used to distinguish between a single, block or RMW cycle. WE\_O – Write enable output signal, used to indicate a write transfer.

Slave signals receive the exact same master signals, but in an opposite direction. For example, CYC\_I receives the cycle output signal, whereas ACK\_I sends an acknowledge response from the slave to the master's ACK\_O signal. The types of Wishbone bus cycles are divided into three sections – Single, block and burst.

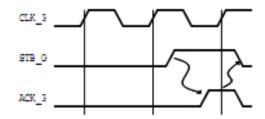

Single transfers use a handshaking protocol shown in Figure 2.3. The master core initiates a transfer with the strobe signal, where the slave responds with ACK, ERR or RTY. Strobe is held

high until a response is received, where the stobe signal is then de-asserted. A cycle termination signal (ACK, RTY or ERR) must be asserted according to the logical AND of STB and CYC.

Figure 2.3: Single Transfer Hand Shake

A more detailed waveform is shown in Figure 2.4, where a sample single read transfer is shown. CYC and STB are asserted to indicate a read request, where the address, selection and associated tags are also applied. The slave responds with an acknowledge signal at (1), as well as the data and associated tags.

Figure 2.4: Single Read Transfer

A single write request is very similar, shown in Figure 2.5, where WE\_O is asserted, data is provided by the master on DAT\_O and the slave terminates the transfer with an acknowledge at edge (1).

Figure 2.5: Single Write Request Signals

These two requests can be performed in a Read-Modify-Write (RMW) request, shown in Figure 2.6. The CYC signal is held high for the duration of the transfer, while the separate strobe signals perform the actual individual transfers.

Figure 2.6: Wishbone RMW

The block transfers operate slightly differently, where the acknowledge signal may be held high for a number of cycles for multiple transfers for increased bandwidth and reduced delay. A block

read request is shown in Figure 2.7. Note that CYC is asserted for the entire duration of the transfer.

Figure 2.7: Block Read Request for Wishbone

Burst transfers address the issue of the additional delays involved when cycle termination signals, in order to reduce wire routing delay, become synchronous. Additional tag signals are used in order to let the slave know of predictable transfers in advance. The Address Tag contains two additional identifiers, used to specify burst characteristics: Cycle Tag Identifier (CTI) and Burst Type Extension (BTE). CTI is 3 bits, and BTE is 2 bits. They are shown in Table 2.1 and Table 2.2.

| CTI (2:0) | Description                      |

|-----------|----------------------------------|

| 000       | Classic Cycle                    |

| 001       | Constant address burst cycle     |

| 010       | Incrementing address burst cycle |

| 011-110   | Unused                           |

| 111       | End-of-Burst                     |

Table 2.1: Cycle Type Identifier

| BTE (1:0) | Description        |

|-----------|--------------------|

| 00        | Linear burst       |

| 01        | 4-beat wrap burst  |

| 10        | 8-beat wrap burst  |

| 11        | 16-beat wrap burst |

Table 2.2: Burst Type Extension

The Classic Cycle is not a burst transfer, where no information about future master cycles is given. End-of-Burst is used to indicate that the current cycle is the last cycle in the burst. Constant address cycle causes a continual access to the same address, until End-of-Burst is given. Lastly, incrementing address burst uses the Burst Type Extension tag to further define the address behavior. Consecutive addresses, based on BTE are applied. Linear burst simply adds one to the address per cycle, while the beat wrap bursts are modulo the wrap size. Figure 2.8 is an example of an incrementing address burst transfer.

Figure 2.8: Incrementing Bursts for Wishbone

### 2.3.2 Avalon Interface

Altera's Avalon interface is a flexible interconnection architecture aimed at SoCs on FPGAs. While Avalon has six different types of interface – Memory Mapped, Streaming, Tristate, Clock, Interrupt and Conduit – the Memory Mapped interface will be the main focus due to the nature of the research. The other types will be briefly explained.

#### 2.3.2.1 Avalon-MM

The slave interface uses the following signals. Note that not all of them are required.

Read – Read is asserted to indicate a read transfer, where readdata is required.

Write – Write is asserted to indicate a write transfer, where writedata is required.

Address – Contains the address used for read and write requests, and can be up to 32 bits. Readdata – Contains the data for a read response.

Writedata – Contains the data for a write request.

Byteenable – Used for fine control over data granularity. Selects a specific byte lane for transfer, and has the available bit widths of 1, 2, 4, 8, 16, 32, 64 and 128.

Begintransfer – Asserted for the first cycle of each transfer, regardless of waitrequest. Waitrequest – Asserted by the slave to indicate that it is unable to respond to a request. Readdatavalid – Asserted when data is supplied in response to a read request.

Burstcount – Indicates the number of transfers that a burst contains, with a maximum size of 32 bits.

Beginbursttransfer – Asserted on the first burst cycle to indicate the start of a burst transfer. Figure 2.9 demonstrates examples of slave read and write transfers using Avalon-MM.

Figure 2.9: Avalon MM Transfer

### 2.3.2.2 Avalon-ST

Avalon Streaming (Avalon-ST) interfaces are used for driving unidirectional and high bandwidth data, where applications include DSP, packets and multiplexed streams. Connected components act as either a source or a sink, with data flowing from the source into the sink.

#### 2.3.2.3 Avalon-MM Tristate

Avalon Memory-Mapped tri-state interfaces allow off-chip components to be used. It is relatively similar to Avalon-MM, but with the inclusion of Chip Select (CS) and Output Enable (OE) signals, as well as a bidirectional data line. When chip select is present, all signals are ignored unless CS is asserted. When OE is de-asserted, the slave will not drive its data lines.

## 2.3.2.4 Clock

Clock provides synchronization for the Avalon interface and includes a synchronous reset signal. All internal logic returns to initial states when reset is asserted.

#### 2.3.2.5 Interrupt

Each applicable slave device has an interrupt output signal (IRQ), which is asserted when service is needed. The master device receives up to 32 interrupt signals and, depending on the IRQ scheme, services each interrupt according to a priority table.

## 2.3.2.6 Conduit

The Conduit interface is used with Altera's SOPC Builder software and is used for exporting signals for connection with external FPGA pins.

# 2.4 CAD Tools for NoC Implementation on FPGAs

## 2.4.1 Altera Quartus II

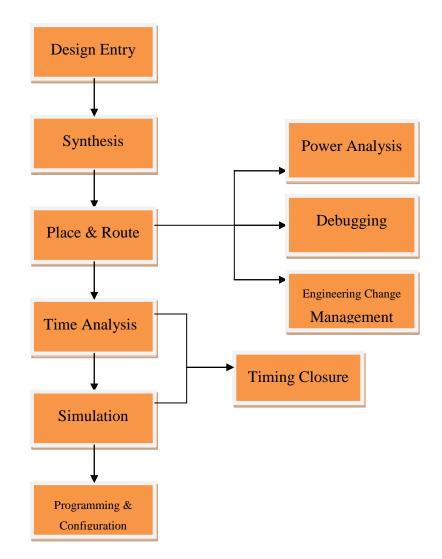

Quartus II Software is CAD tool suite provided by Altera Corporation. It is designed to map hardware designs conveniently and efficiently to altera FPGAs. The design flow for Quartus II is shown in figure 2.10

As shown in the flow chart first step of the design flow is the design specification. The design entry is done by creating an HDL file. Synthesis is the process where the HDL code is checked for any syntax or semantic errors. The HDL is compiled to an intermediate form and then an equivalent and optimized RTL implementation is synthesized. Place and Route maps the hardware described at the RTL level to available logic and routing resources on the FPGA. Timing Analysis evaluates the performance of the design implemented on FPGA and attempts to meet timing requirements and attain timing closure. Simulation is used to verify the functionality

of the HDL model and its FPGA implementation. Finally, Programming and Configuration stage generates the bit stream required to configure. Quartus II Version 9.0 running on sun solaris was used in this research.

Figure 2.10: Quartus II Design Flow

## 2.4.2 Altera SOPC Builder

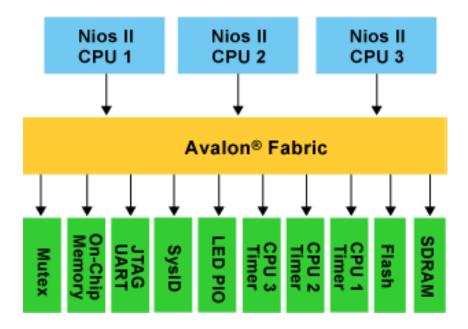

System-On-a-Programmable-Chip (SOPC) Builder is included with the Quartus II software. SOPC Builder provides an environment for design implementation using pre-designed components such as Nios II CPU for the embedded systems. In our research we have used these pre-designed components and they are interconnected with the help of default Avalon fabric and our NoC component which was imported as VHDL coded files.

## 2.4.3 Nios II Embedded Design Suite (EDS)

The Nios II EDS consists of Eclipse IDE and provides an environment where we can configure, program, debug and carry out simulation of Nios II CPUs. All this is carried out by using C/C++ programming language which is further compiled, linked and assembled for Nios II. It also supports in-circuit debugging and Flash Programming

# 2.4.4 Mentor Graphics ModelSim

Mentor Graphics ModelSim [6] is a tool which provides an environment to run the simulation tests for the VHDL or Verilog designs. It has many features to debug the problem, like assertion tests, breakpoints and in-depth signal variable simulations. It also provides us with code coverage and all these features are not well supported in Quartus II's [7] simulation engine.

#### 2.5 Related Work

Our Routers has been designed and synthesized for an Altera Cyclone IV FPGA. This section provides a brief review of the state of the art for NoC routers. After that, we describe the Avalon-Wishbone glue logic and discuss related work in that area. Next, we look at related work in the area of NoC adapters, followed by related work that builds a NoC with the Nios II CPU and supporting software. Other areas of related work include similar routers synthesized for FPGAs and their evaluation methodologies.

Vestias et al. propose GNoC in [8], a generic router which supports a range of routing, switching and arbitration protocols. They create a tool for exploring the sharing of some decentralized components to reduce area that is based on the injection rate of ports. Unfortunately, they lock all protocols to certain values and do not explore them further. Their tool shows how they can save area when injection rates are low but does not test to see if performance is degraded.

MoCres, designed by Janarthanan et al. in [9], uses complex VCT flow control and attempts to reduce area by combining multiple components into a single component. They create multi-clock domain to enable high clock frequencies during transfers. Optimizations from XY routing in the crossbar matrix have been extended to the routing algorithm, and gave us the idea for a further arbitration unit extension. We have also used their idea of creating VHDL wrappers to simulate the stand-alone router or routing configurations to compare parameters.

Porting from Wishbone Bus to Avalon Bus was the concept given by Xing, Xu, et al. They have discussed regarding the glue logic between the Wishbone and Avalon interface sockets, a Wishbone compatible I2C controller was ported to the Avalon bus [10]. The glue logic was verified with simulation results. While the logic is correct for single transfers, there is much missing in the way of variable latency support and high speed Avalon block transfers. The *readdatavalid* signal is not supported in this paper and block transfers will not be queued and hence, forced into a wait state. Lastly, there is no mention of burst transfer glue logic.

A packet-switched wormhole router was implemented [11], utilizing Virtex-4 SRL16 components for FIFO implementation, which increases efficiency but decreases portability and design reuse. A Wishbone adapter was included, which supports burst transfers. Since the routers are input queued, deadlock becomes an issue and was solved by adding a separate read request buffer into the Wishbone adapters, which halts any incoming request when the buffer fills. They tested the design with a 16 switches, memories and transaction generators. The individual router was synthesized for Xilinx FPGAs with four and five ports and compared to related work.

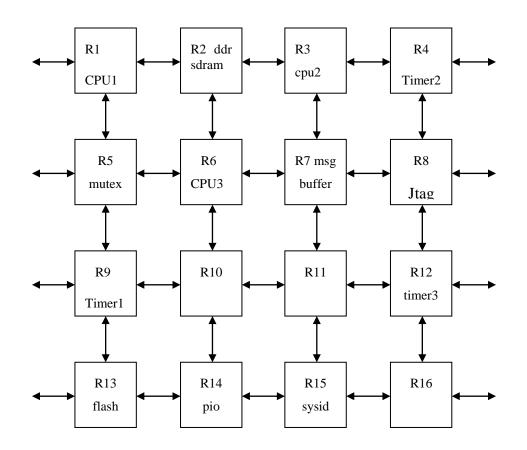

Design and implementation of a Plesiochronous multicore system [12], a 4x4 packetswitched mesh NoC was implemented with SOPC Builder using Nios II CPUs. Multiple Stratix II FPGA boards running at 50MHz were used in order to fit the entire design, which results in an on-board throughput of 650Mbps. Inter- board communication operates at 50MBps. A software driver is used to access NoC functions within the Nios II CPUs. The system was verified by probing certain NoC components as a message traverses the network and returns to the sender, and it was found that the maximum communication rate was 434,000 Packets/second. This large difference between the theoretical bandwidth of 640Mbps is due to the large amount of time required for the packet to traverse the software routines.

In HERMES [13], a packet-switched wormhole router with input queuing was designed and analyzed. The router has four regional ports and one local port, and uses X-Y routing. 3x3 mesh NoC architecture was implemented with traffic generators attached. The buffer size and traffic patterns were analyzed and explored, resulting in overall increased performance as buffer size increased. A 2x2 NoC was synthesized targeting a Xilinx XC2V1000 FPGA.

#### 2.6 Summary

In this chapter, the relevant background material and related previous work was presented. First, the basic concepts of FPGA technology were discussed then a short collection of concise definitions of NoC building blocks was presented. We then listed relevant concepts and theories about interfaces and signals. Finally, the Chapter concluded with a discussion of some of the previous work that is closely related to this research, and how it was used to motivate our research. In Chapter 3, a detailed description of architecture and functionality of SAF and WH routers is presented.

# Chapter 3: Description of SAF and WH Router Architecture

This chapter discusses the design and implementation of Routers and Adapters explored and evaluated in this thesis. It begins with a discussion of basic functionality of the NoC router. That is followed by a discussion of the NoC router architectures, describing their components, and data flow.

# **3.1 Functionality**

In the following sections, we discuss the functionality of the routers which includes protocols and algorithms. This will give us a basic idea of how routers differ from each other.

# **3.1.1 Protocols and Algorithms**

NoC router protocols and algorithms govern the flow of data through the NoC network. They make decisions on where data flows, at what speed, in what order, how it is stored, etc. Therefore they directly affect performance and area consumption. Careful selection is crucial and there is much work to be done in testing existing protocols and algorithms and proposing and evaluating new ones. The following section describes protocol and algorithm choices used in SAP and WH router.

## 3.1.1.1 Flow Control

Both the routers used packet switched flow control (PS). In PS networks, data is separated into small blocks called packets at the core. This packet includes a header which has information about its destination. Upon creation of the packet, IP cores simply release the packet into the

network where a series of interconnected routers forward the packet to its destination. PS is referred to as connectionless as there is no direct connection between communicating cores. This is an attractive choice as it allows multiple IP cores to communicate concurrently without contention.

## 3.1.1.2 Switching Mode

Switching mode can often be confused with flow control as it plays a large part on the flow of the packet. Switching mode is only a parameter of PS networks. This parameter determines how a packet is allocated with buffers and channels and when it will receive service. A packet is broken down into flow control units (flits). Each flit is the size of the channel. The two routers have two different switching modes (i) store-and-forward scheme and (ii) wormhole scheme. In SAF scheme, packets are buffered at each router, and the router waits for the full packet to arrive before forwarding. This prevents a single packet from blocking more than one channel at a time. The disadvantage is that it increases the buffering requirements of each router. While in WH router instead of full packet only the flit is stored and then the path is blocked for the rest of the flits. This scheme mitigates the disadvantage of SAF Router as there is no buffering required. However, after evaluating these routers we realized that each switching mode has its advantages under different applications.

# 3.1.1.3 Routing Algorithm [21]

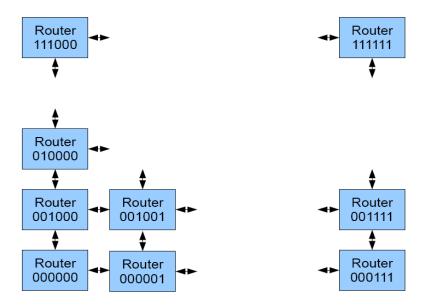

The routing algorithm is used in the router and determines how the path is chosen to the packets destination. SAF Router uses XY routing algorithm known for its simplicity and low area overhead. WH Router uses source routing which is a deterministic algorithm that gives the designer a chance to determine the routing path and optimize placement with the help of floor planning. We will now briefly discuss how the XY routing algorithm and how the WH routing works.

Figure 3.1: Coordinate Configuration for XY Routing [21]

In XY routing, each router is given a coordinate based on its position in the network. We restrict our mesh size to 4X4 and therefore our coordinate is 4 bits. The most significant 2 bits portrays the routers vertical displacement with 00 being the lowest (southern) router and 11 being the highest (northern) router. The least significant 2 bits portrays the routers horizontal displacement with 00 being the left most (western) router and 11 being the right most (eastern) router. Figure 3.1 shows router coordinate configuration within a mesh. A packet arrives at the This header contains the destination of the packet along with the router with a 16 bit header. type of packet. The vertical displacement is checked first. If the destination is greater than the coordinate, the packet is forward north. If the destination is lesser then the coordinate, the packet is forward south. If the destination is equal to the coordinate, then its vertical displacement is ok. The same process then occurs for the horizontal displacement. Eventually, the packet arrives at the router with the proper coordinate. At this point the packet is at the proper port and must now be forwarded to the correct destination port. Since routers in our mesh can have up to 4 ports, the least significant 2 bits of the header are used to distinguish among local ports. Figure 3.2 shows the configuration of local ports within the router.

Figure 11: Configuration of Local Ports for XY Routing [21]

An important note can be made about this algorithm. Since the vertical displacement is always found first, a packet coming in from the east or west ports must already be in its proper vertical position. Therefore, a packet coming in from the east or west ports cannot be forward north or south. This observation is exploited later to optimize the area selected components.

XY routing prevents livelock from occurring. Since all packets leaving the same source and headed for the same destination will travel the same path, it also prevents having to deal with complex scenarios like packet reordering. Unfortunately, using the same logic, XY routing cannot provide any type of congestion control.

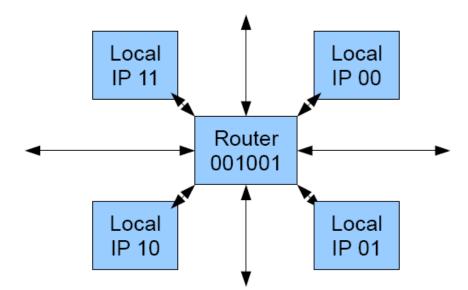

WH router uses source routing as an algorithm. In source routing the routers do not need any router coordinates to be given. Source routing completely depends on routing table which helps determining the port that packet has to use in order to progress towards destination. In source routing the number of IP cores is an important factor in determining the resource usage because more number of IP cores leads to a larger routing table. The routing table is a simple lookup table where the information of the next hop is provided to the packet after reading the source and destination address from the header flit. In source routing the header flit consists of the source and destination address. Depending on the flit size, the size of router input buffer is determined, as it is used to store the header flit which can be consisting of two or more flits. First, the header flit is read and from there the source and destination address is extracted, the source and destination widths can be determined by designer as it is a generic parameter and can be given as input. There is a specific port assigned to the packet with respect to the source and destination addresses of the packet. The port determination is shown in Figure 3.3.

|          | Destination 1 | Dest 2 | Dest 3 | Dest 4 | Dest 5 |

|----------|---------------|--------|--------|--------|--------|

| Source 1 | Port 1        | Port 4 | Port 1 | Port 4 | Port 2 |

| Source 2 | Port 2        | Port 1 | Port 2 | Port 1 | Port 1 |

| Source 3 | Port 4        | Port 1 | Port 1 | Port 2 | Port 1 |

| Source 4 | Port 3        | Port 2 | Port 3 | Port 3 | Port 3 |

| Source 5 | Port 1        | Port 3 | Port 1 | Port 1 | Port 4 |

#### Figure 12: Port correlation in routing table

Figure 3.3 gives a clear idea of how a designer can determine the path of the packet. This is the reason why source routing is said to be a deterministic routing algorithm. Building the routing table is considered to be the most important task of the designer, as avoiding livelock, deadlock and congestion is possible by proper port allocation. Along with this the designer can do floor planning and improve the overall performance by placing densely connect IPs closer to each other.

#### **3.1.1.4 Scheduling**

Scheduling determines the order in which the data is sent and can be done by both the IP cores and routers. If 2 or more packets request the same port at the same time or while it is busy, the requested (output) port will have to make a decision on which to grant access first. This is called arbitration. Both the routers allows for some flexibility in choosing arbiter schemes. Arbitration schemes consider priority of packets in routers among the network and include static and dynamic.

In static arbitration schemes, the priority of each port is chosen during design. One of the examples is generic fixed scheme where priority is given to the north first, and degrades clockwise. While, dynamic arbitration makes a decision at run-time and is more flexible, also requires a larger area. However, dynamic schemes can avoid deadlock. One of the schemes gives priority to the port that has been busiest (sending the most requests).

When comparing the two routers we used a first come first serve arbitration scheme more details will be provided in the following chapters. This was done to make a fair comparison between the routers.

#### **3.2 Router Implementation**

We now discuss the general structure of both the routers. The SAF Router was designed with 4 ports for communication with neighboring routers, North, East, South, and West and anywhere from 0 to 4 local ports for communication to IP cores. A router with no local ports would be used just to complete a mesh or act as a congestion control unit within the network. Generic port and component design was used. Therefore, input port has the ability to forward to its own output port, although this situation could never occur. The router is decentralized meaning each port runs its own control logic and hence can request and set up concurrent connections. The block diagram of SAF Router is shown in Figure 3.4.

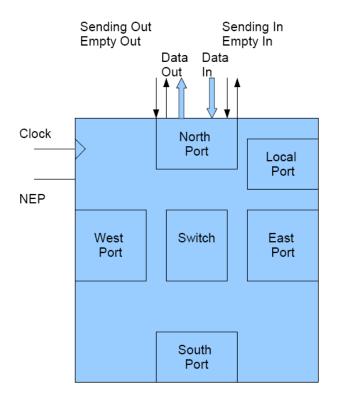

Figure 13: SAF Routers Exterior Structure [21]

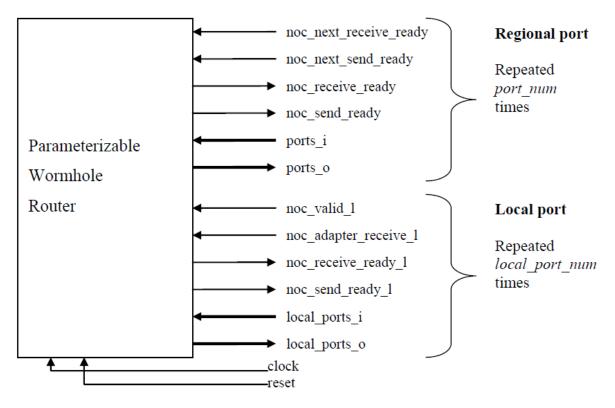

The WH router was designed with the flexibility of choosing the number of ports. Generic ports give us opportunity to save area, for example the boundary routers will not need all the ports for connection. It also gives us the design flexibility to implement many topologies without any changes to VHDL code. The Block diagram of WH router is shown in Figure 3.5.

Figure 14: WH routers Exterior Structure [22]

# 3.2.1 Internal Structure and Data Transfer

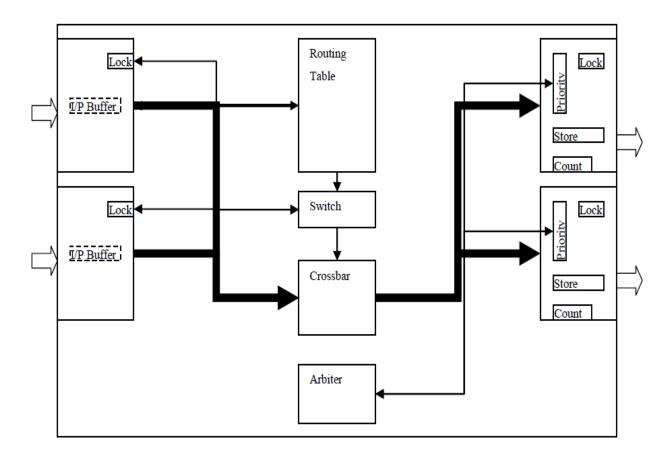

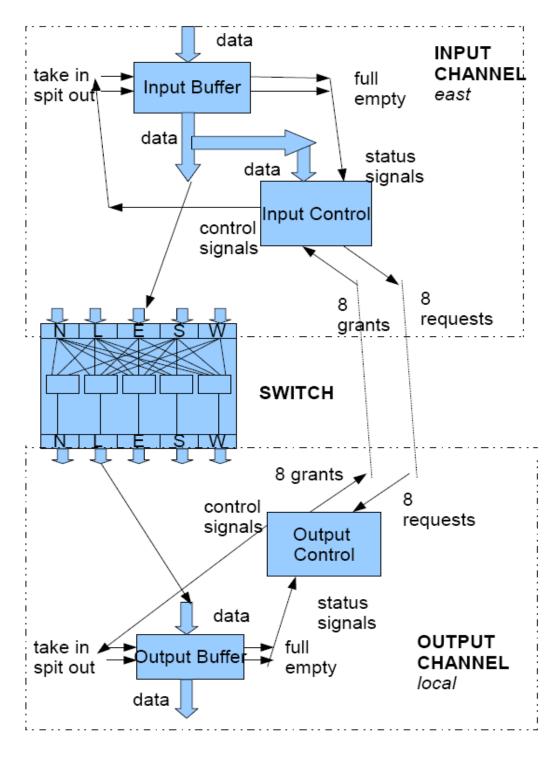

The WH Router's internal structure consists of functional blocks such as input buffer, output buffer, arbiter, crossbar, routing table, switch, priority table and a counter as shown in figure 16. We now briefly explain the functionality of aforementioned blocks. The input buffer register is used to store the incoming flits. Once it is stored, the input and output ports are locked and a counter is started. As the counter reaches zero, the worm is completed and the entire packet is sent through the node. Now, in parallel we have to decide which node to go through for that we have a routing table which contains the path for the worm to follow and on that basis the input and output ports are locked as mentioned before. The worm travels through the router as shown by thick lines in Figure 3.6.

The most resource consuming blocks in this design are the routing table, crossbar and the input and output buffers. This has implication on how the flit size affects the area of the router.

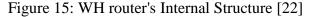

Figure 3.7 shows all the functional blocks of the SAF router. It consists of input buffer, output buffer, Partial crossbar switch, input control and output control. The input buffer stores all the flits of the incoming packet. Once the whole packet is stored header is read by the input controller. It determines the next hop and notifies the output controller of the respective output buffer. For this we have two separate sets of control signals full, empty, take in, spit out and another set is request and grant. The first set of signals get activated during communication between input buffer, input controller and also between output buffer and output controller while the other set of signals gets activated during communication between the input and output controller. Now these signals are used to build up a sequence for the data to flow inside the router.

So as soon as the input buffer is full the full signal is sent to the input controller of the respective input buffer. Along with full signal we sent the first two flits of the packet. They contain the destination address and indirectly the information of next hop. Input controller reads the header and determines which port has to be blocked and then communicate with the output controller of that respective port. Output controller will grant permission to the request. The request is only granted after the output controller confirms that the output buffer of the requested port is empty and ready to receive data through the crossbar switch this confirmation is done by the checking the empty signal coming from the output port. Now the path is blocked during this time and it works same as in worm switching technique but only during this period of the data flow. The output controller de-asserts the grant once it receives a full signal from the respective output buffer. The data flow is shown in figure 3.7 which is in form of thick blue line and control signals are denoted by thin black lines.

Figure 16: SAF Router's Internal Structure [21]

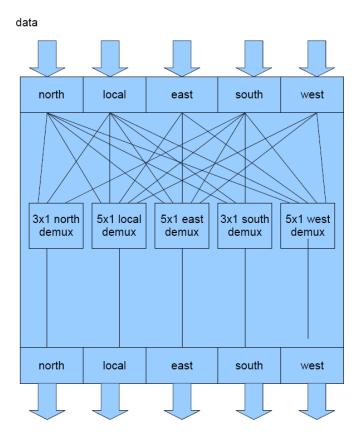

## 3.2.2 Switching Mechanism

The crossbar switch is shown in figure 3.8. It is a set of demultiplexers having an interconnection allowing all possible connections between input and output channels. The crossbar switch is used in both the routers but there were some optimizations done in SAF Router's crossbar switch as it reduced the area consumption without affecting the functionality of the system. First, it uses a partial scheme, which includes one 5 by 1 unit for each output rather than one 5 by 5 unit for all outputs, for a 5 port router. Initial design included 2 switching options, full and partial switch. Early synthesis results eliminated the full switch design because it was larger in terms of area and delay. Each output is connected to a different port. Next, there are no multiplexers in the design. The input data is connected to all partial crossbar units which will choose the appropriate data for the output. The fact that at a time, the output channel can only serve one input request is exploited here. The final optimizations are made in the partial units of the north and south. Though analysis of the XY routing algorithm, we can conclude that these units will never receive data from the east or west. This reduces the inputs of all of these units by two.

WH router on the other hand has fully functional crossbar switch as the above optimization were not appropriate for the routing scheme decided for this router. This lead to more area consumption by the cross bar switch.

Figure 17: Architecture of Switching Fabric

## **3.3 Standard Sockets**

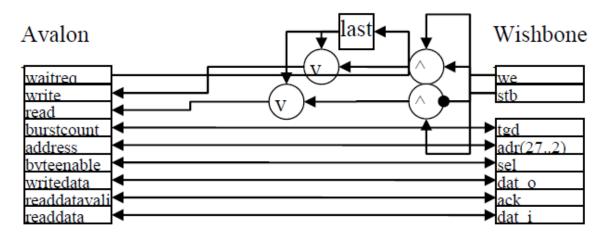

This section describes the standard sockets used in our research. Standard sockets are predesigned IP cores that allow easy interface between computational blocks and routers in an NoC. For example in our research the computational blocks are designed to work on Avalon protocols while the router works on wishbone protocols so our socket converts signal between Avalon and wishbone protocols and can be used as network adapters in NoCs. This kind of design practice reduces the design cycle time and also allows designer to concentrate on the core functionality of the system. In our case the core functionality is that of the routers while the network adapters are used as standard sockets.

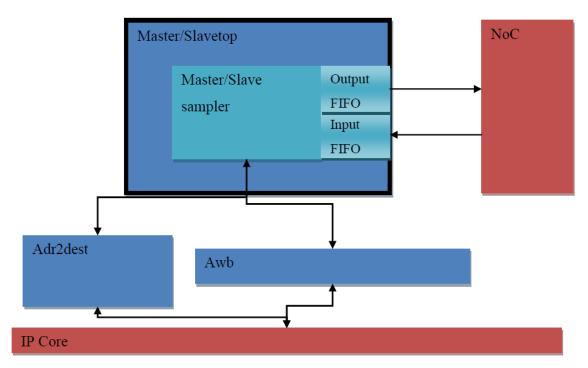

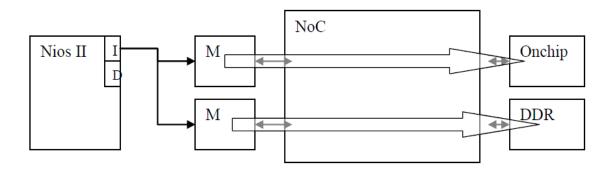

# 3.3.1 Adapter Overview [22]

The adapter acts as an interface between IP cores and the routers. Its main function is packetizing and de-packetizing. The adapter is designed for wishbone protocol [14] which is open source and supported by many IP Core vendors

The adapter works with routers designed for wishbone protocols and IP cores Designed for Avalon protocols. This adapter facilitates NoC implementation on Altera FPGAs with router running on wishbone protocols.

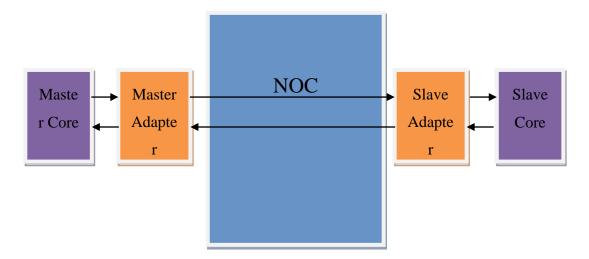

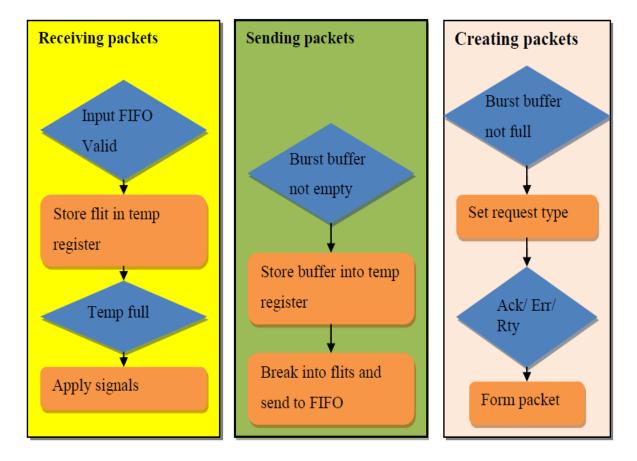

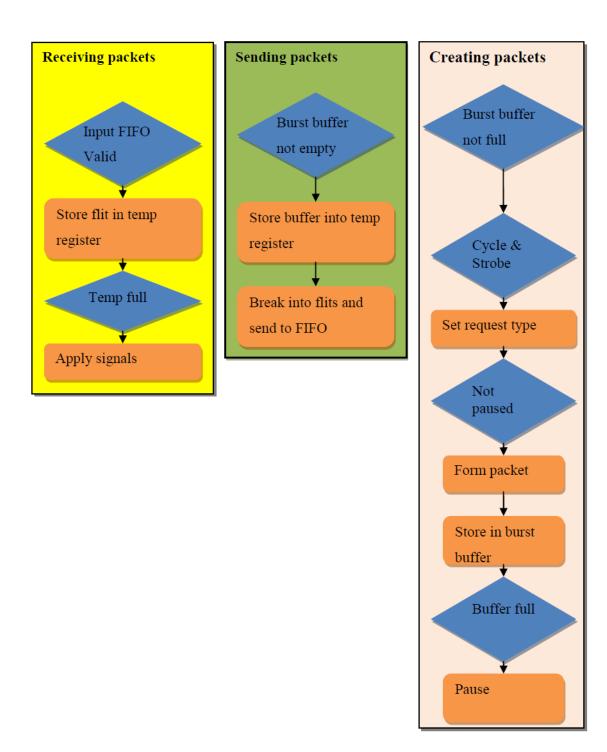

There are two types of adapters – Master and Slave. As illustrated in Figure 3.9, the Master adapter is responsible for receiving requests from a master component (such as a CPU) and providing the response signals. The Slave adapter is responsible for receiving the master requests and providing the slave responses.

Figure 18: Adapters Overview