# University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

1988

# VLSI fault-tolerant systolic architectures.

Majid. Taheri University of Windsor

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### Recommended Citation

Taheri, Majid., "VLSI fault-tolerant systolic architectures." (1988). Electronic Theses and Dissertations. Paper 4536.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service Service des thèses canadiennes

्

Ottawa, Canada KIA 0N4

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted ... the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, tests publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30.

# VLSI FAULT-TOLERANT SYSTOLIC ARCHITECTURES

By

Majid Taheri

A Dissertation

Submitted to the

Faculty of Graduate Studies and Research

through the Department of

Electrical Engineering in partial fulfillment

of the requirements for the Degree of

Doctor of Philosophy

at the University of Windsor

Windsor, Ontario, Canada

Permission has been granted to the National Library of Canada to microfilm this thesis and to lend or sell copies of the film.

The author (copyright owner) has reserved other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without his/her written permission.

L'autorisation a été accordée à la Bibliothèque nationale du Canada de microfilmer cette thèse et de prêter ou de vendre des exemplaires du film.

L'auteur (titulaire du droit d'auteur) se réserve les autres droits de publication; ni la thèse ni de longs extraits de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation écrite.

ISBN 0-315-43775-8

Majid Taheri

1988

#### ABSTRACT

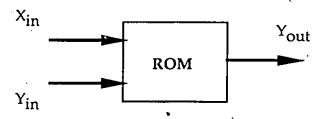

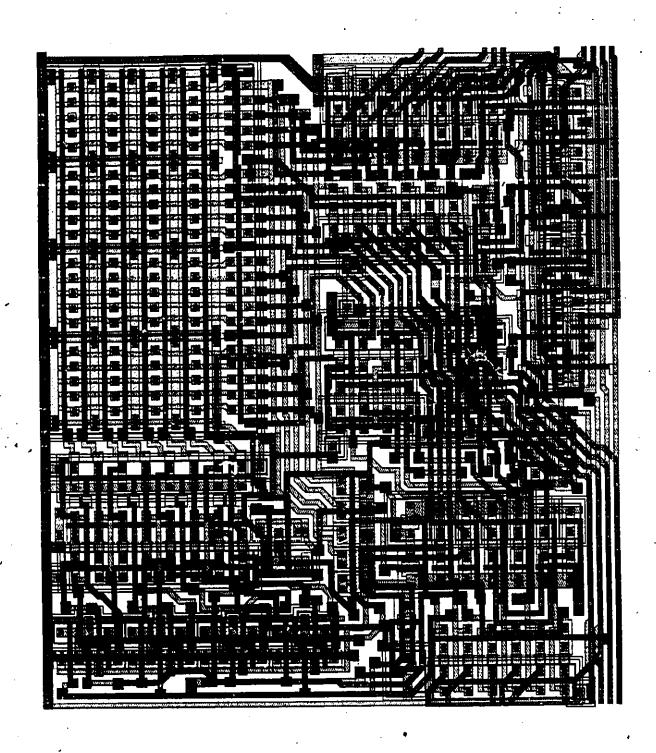

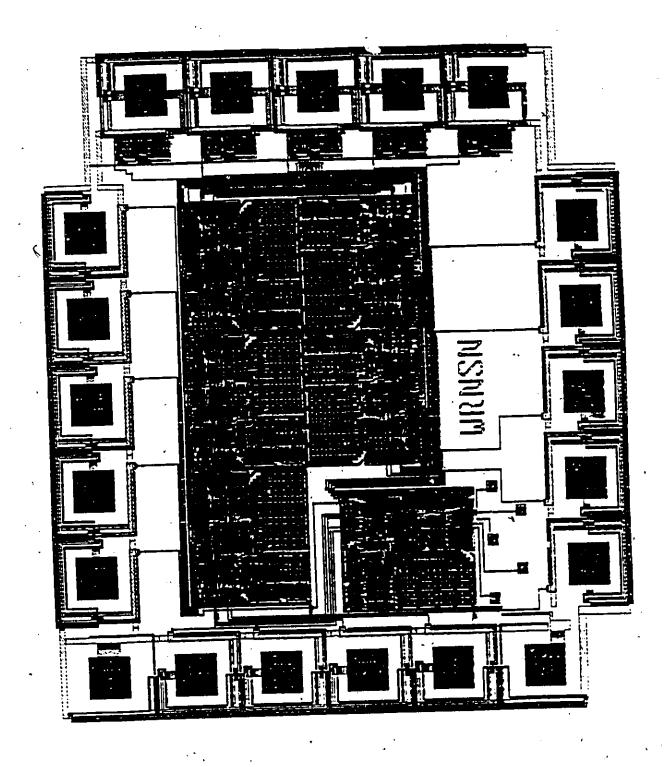

This work presents systolic architectures for implementing finite rings and fields operations in VLSI. By decomposing these operations, at the bit level, a generic cell, consisting of a small ROM and ancillary circuitry, can be used to compute most of the commonly used digital signal processing algorithms.

Various implementations for modular addition and multiplication, based on this cell, are given and compared to conventional single ROM techniques. The advantages of the new method, from the point of view of saving memory locations, silicon area, and increasing throughput are discussed.

The application of the technique in the area of Digital Signal Processing has been investigated. Structures for implementing Finite Impulse Response (FIR) filters, both bit serial and bit parallel, are presented. The design of fixed coefficient FIR filters implemented using Residue Number Systems (RNS) and binary are compared, and it is shown that the RNS approach requires less silicon area and operates at very high speeds.

A novel distributed fault detection technique has been introduced. A small amount of extra hardware enables the cell to detect run time faults. It is shown that only one redundant modulus is required to correct errors when this distributed fault detection is used, as opposed to two moduli in conventional Redundant Residue Number Systems (RRNS). The issue of the testability of the fabricated designs has also been addressed, and a simple procedure for testing arrays of these generic cells is proposed which takes

advantage of the contents of the ROMs and the capability of by-passing subsections of the array.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere thanks and appreciation to my cupervisor, Dr. G.A. Jullien for his invaluable advice, guidance and constant encouragement throughout the progress of this thesis. The advice of Dr. W.C. Miller, Dr. S. Bandyopadhyay is gratefully acknowledged.

# TABLE OF CONTENTS

| ABSTRACTii                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACKNOWLEDGEMENTSiv                                                                                                                                                                                                                |

| TABLE OF CONTENTSv                                                                                                                                                                                                                |

| LIST OF FIGURESviii                                                                                                                                                                                                               |

| LIST OF SYMBOLSx                                                                                                                                                                                                                  |

| CHAPTER 1 -                                                                                                                                                                                                                       |

| Introduction                                                                                                                                                                                                                      |

| CHAPTER 2                                                                                                                                                                                                                         |

| DISCRETE MATHEMATICS AND THE RESIDUE NUMBER SYSTEMS                                                                                                                                                                               |

| 2.3.3. Redundant Residue Number system (RRNS)       27         2.4. Operations in RNS       28         2.4.1. Forward Mapping       28         2.4.2.Reverse Mapping       29         2.4.2.1. Chinese Remainder Theorem       29 |

| 2.4.2.2. Mixed Radix Conversion                                                                                                                                                                                                   |

# CHAPTER 3

| Finite Ring and Field Architectures,                         | 34  |

|--------------------------------------------------------------|-----|

| Abstract                                                     |     |

| 3.1. Introduction                                            |     |

| 3.2. Inner Product Step Processor                            |     |

| 3.3. RNS Based Inner Product Step Processor                  |     |

| 3.4. Bit Level Inner Product Step Processor for Finite Rings | 41  |

| 3.5. Complexity Analysis                                     |     |

| 3.5. RNS Subtraction                                         | 52  |

| 3.6. General RNS Multiplication                              | 53  |

| 3.6 Forward Mapping                                          |     |

| 3.7. Summary                                                 |     |

|                                                              | 07  |

| CHAPTER 4                                                    |     |

| CHAI I EN I                                                  | _   |

| Circustures for High Chand DCD Algorithms                    | 71  |

| Structures for High Speed DSP Algorithms                     |     |

| Abstract4.1. Introduction                                    | /1  |

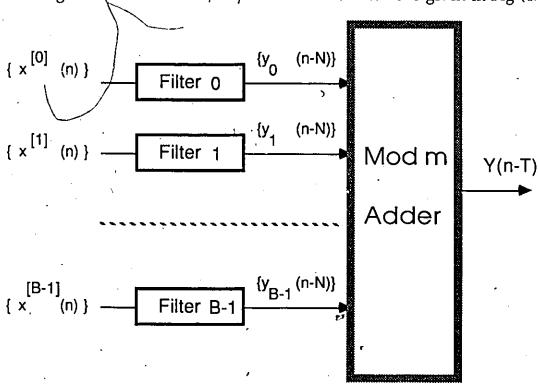

| 4.2. RNS based FIR filters                                   | 72  |

|                                                              |     |

| 4.2.1. Word serial/bit serial FIR filter                     |     |

| 4.2.1.1 Word serial/bit serial FIR filter                    |     |

| implementation                                               | 75  |

| 4.2.2. Word serial/bit parallel FIR filter                   | 82  |

| 4.2.2.1. Word serial/bit parallel FIR filter                 |     |

| implementation                                               | 83  |

| 4.2.2.2. Word serial/bit parallel FIR filter without         |     |

| adder                                                        | 86  |

| 4.3. Comparisons                                             |     |

| 4.3.1. RADIUS, an RNS based image processor                  | 89  |

| 4.3.2. Impiementation of RADIUS based on BIPSPm              | :90 |

| 4.4. High Speed Correlator                                   |     |

| 4.5.Reverse Mapping                                          | 102 |

| 4.6. Summary                                                 |     |

|                                                              |     |

| CHAPTER 5                                                    |     |

|                                                              |     |

| Distributed Fault Detection                                  | 108 |

| Abstract                                                     |     |

| 5.1. Introduction                                            |     |

| 5.2. Errors, Faults, and Reliability                         | 100 |

| J.L. 211013, Tauris, and Nenavilly                           |     |

| ,           | 5.2.1. Error               | 'S          | •••••                                   |                                         | •••••                                   | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | 111              |

|-------------|----------------------------|-------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|------------------|

| •           | 5.2.1                      | l.1. Codes. | •••••                                   | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | **********                              | 111              |

| Į.          | 5.2.2. RELI                | ABLE SYS    | STEMS                                   | ***********                             |                                         |                                         | • • • • • • • • • • • • • • • • • • • • | 114              |

| 5.3.Fau     | 5.2.2. RELI<br>lt Detectio | n in BIPS   | SPm                                     |                                         |                                         | · · · · · · · · · · · · · · · · · · ·   | *********                               | 117              |

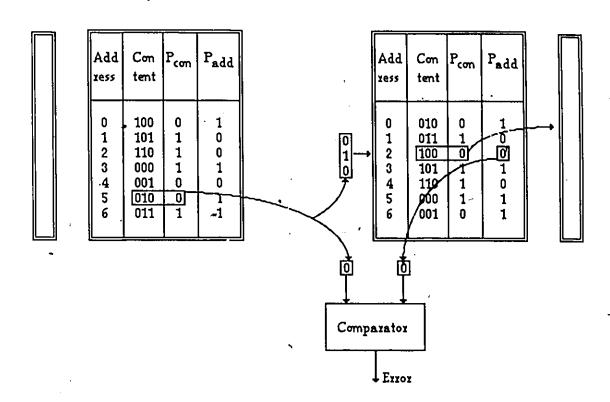

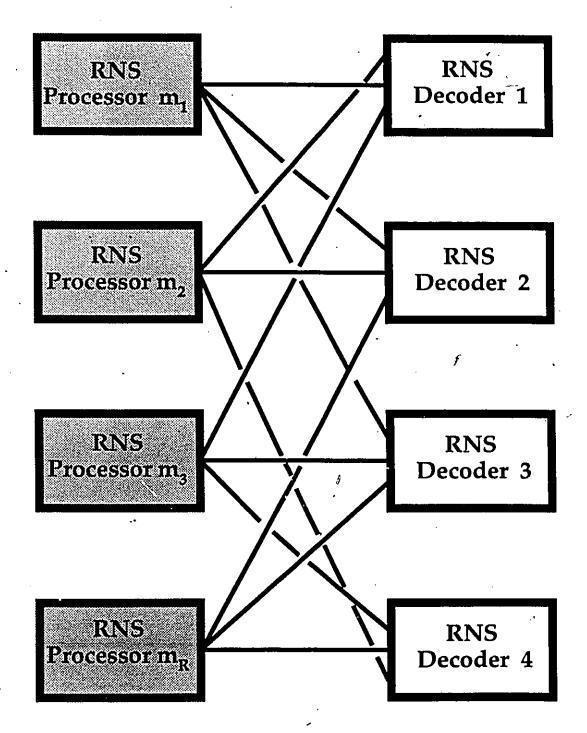

| 5.4. Ap     | plication o                | of BIPSPm   | in RR                                   | NS                                      |                                         | ,                                       | •••••                                   | 124              |

|             | 5.4.1. R                   |             |                                         |                                         |                                         |                                         |                                         |                  |

| •           | <b>TECHNIQ</b>             | UE\$        | • • • • • • • • • • • • • • • • • • • • | **********                              |                                         | , -<br>                                 |                                         | 124              |

| į           | 5.4.2. Appl                | ication Ex  | ample.                                  |                                         | •                                       | ***********                             |                                         | 126              |

| 5.5.Des     | ign For Te                 | stability ( | DFT)                                    |                                         |                                         |                                         |                                         | 133              |

|             | ign For Te<br>5.5.1. Testi | ng the Ar   | ravs Ba                                 | sed on                                  | BIPSP                                   | n                                       | -                                       | 135              |

| 5.6. SU     | MMARY.                     |             |                                         |                                         |                                         |                                         | · <del></del>                           | .139             |

|             |                            |             |                                         |                                         |                                         |                                         |                                         |                  |

| CHAPTER 6   | Ι'                         |             |                                         | ¥.                                      | · <del></del>                           |                                         | . *                                     |                  |

| THE TEN     |                            |             | . •                                     | `,                                      |                                         |                                         |                                         |                  |

| ONICE LICEO | NIC .                      |             |                                         |                                         |                                         |                                         |                                         | 140              |

| CONCLUSIO   | 1 <b>13</b>                | ••••••      | ••••••                                  | • • • • • • • • • • • • • • •           |                                         | ************                            |                                         | L140             |

|             | •                          |             |                                         |                                         |                                         |                                         | •                                       |                  |

| APPENDIX A  | ٠                          |             |                                         |                                         | •••••                                   | • • • • • • • • • • • • • • • • • • •   | • • • • • • • • • • • • • • • • • • • • | 144              |

|             | •                          | •           |                                         |                                         |                                         |                                         | •                                       |                  |

| APPENDIX B  |                            |             |                                         | • • • • • • • • • • • • • • • • • • • • |                                         |                                         |                                         | 147              |

|             |                            |             |                                         |                                         | .*                                      | **                                      | •                                       | •                |

| REFERENCE   | S                          |             | ,<br>                                   |                                         |                                         |                                         |                                         | 154 <sup>°</sup> |

## LIST OF FIGURES

| Fig 2.1 Operation tables for $\langle Z2, \oplus_2 \rangle$ and $\langle Z3, \otimes_3 \rangle$ | 18          |

|-------------------------------------------------------------------------------------------------|-------------|

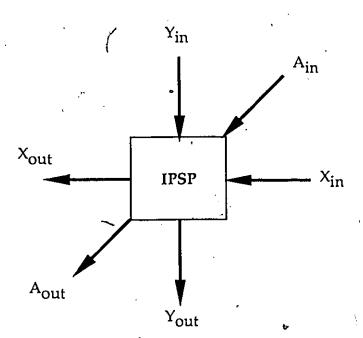

| Fig 3.1 The IPSP                                                                                |             |

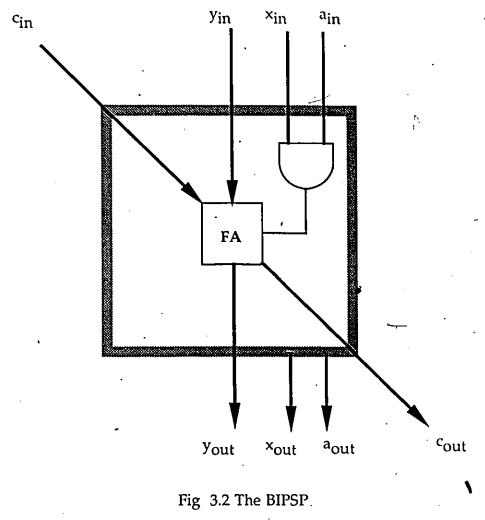

| Fig 3.2 The BIPSP                                                                               | 39          |

| Fig 3.3 IPSP for Finite Ring Calculations                                                       |             |

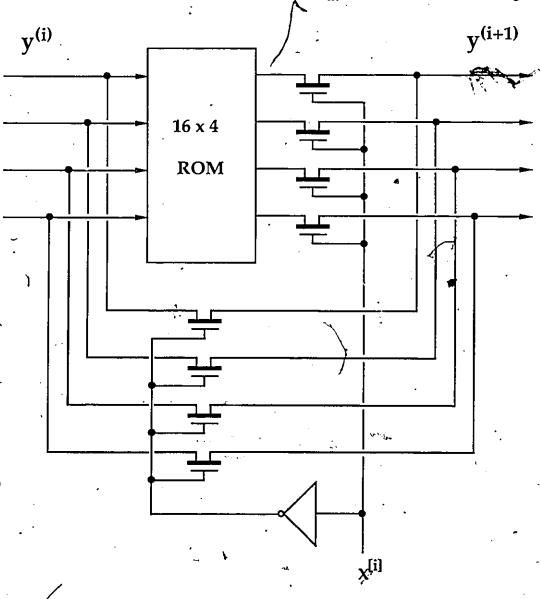

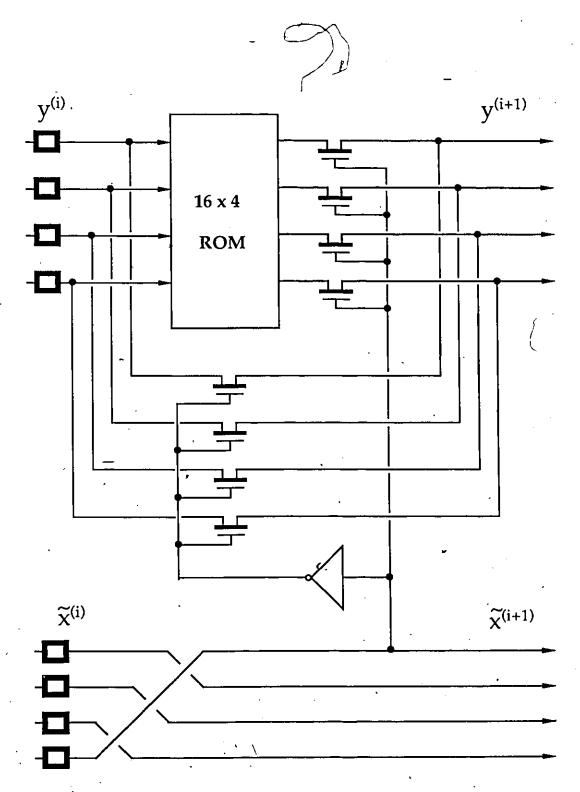

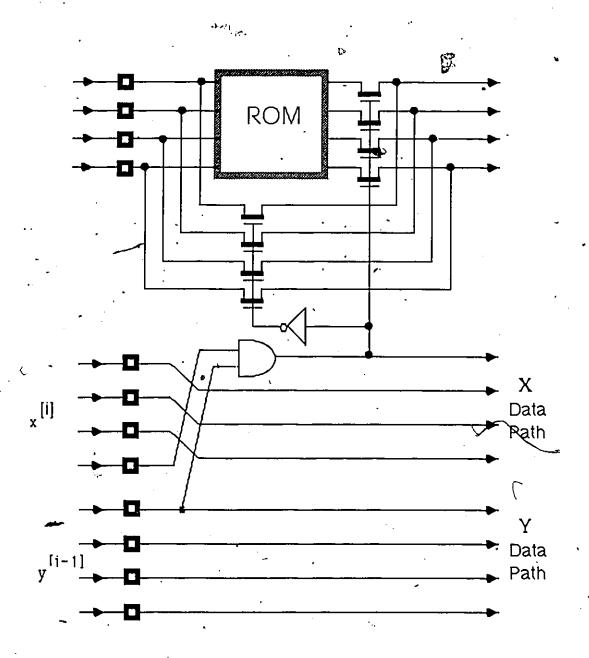

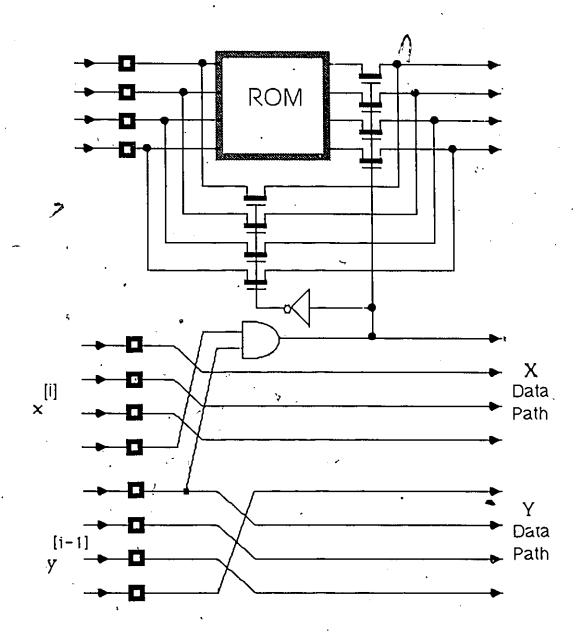

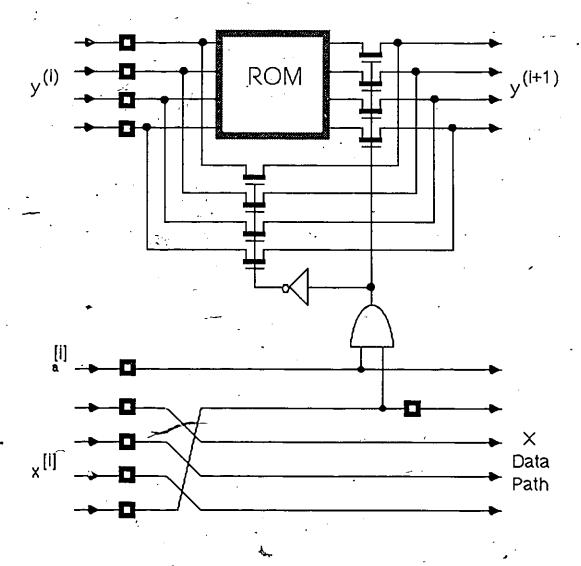

| Fig 3.4 Implementation of the BIPSPm cell                                                       | 42          |

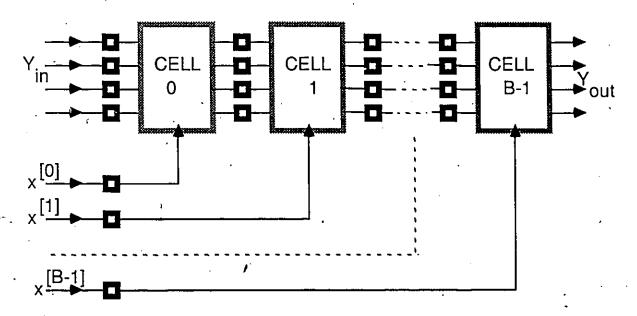

| Fig 3.5 The IPSPm cell implemented using an array of BIPSPm cells                               | 43          |

| Fig 3.6 Systolic BIPSPm Cell                                                                    |             |

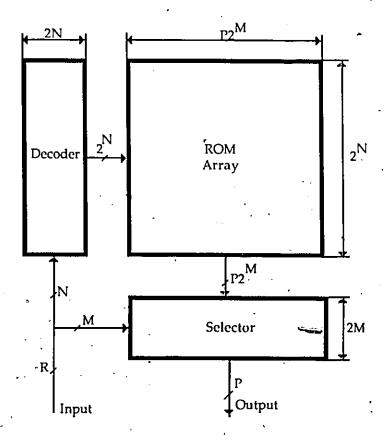

| Fig 3.7 ROM structure [Gla'85]                                                                  | 49          |

| Fig 3.8 Subtraction using BIPSPm                                                                | 53          |

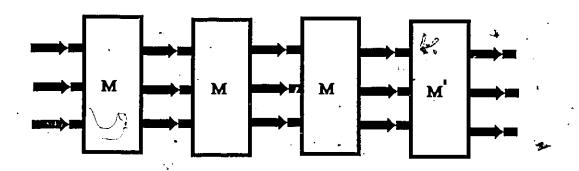

| Fig 3. 9 Cell M for the multiplier array                                                        | 56          |

| Fig 3. 10 Cell M' for the multiplier array                                                      | 57          |

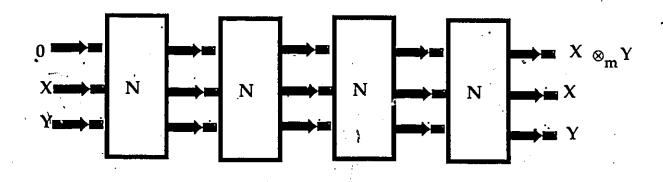

| Fig 3.11 Cell N, a substructure for modular multiplication                                      |             |

| Fig 3.12 Modular multiplication using BIPSPm                                                    | 58          |

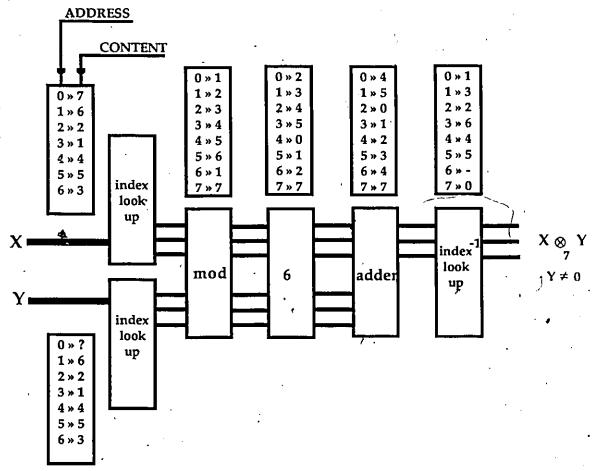

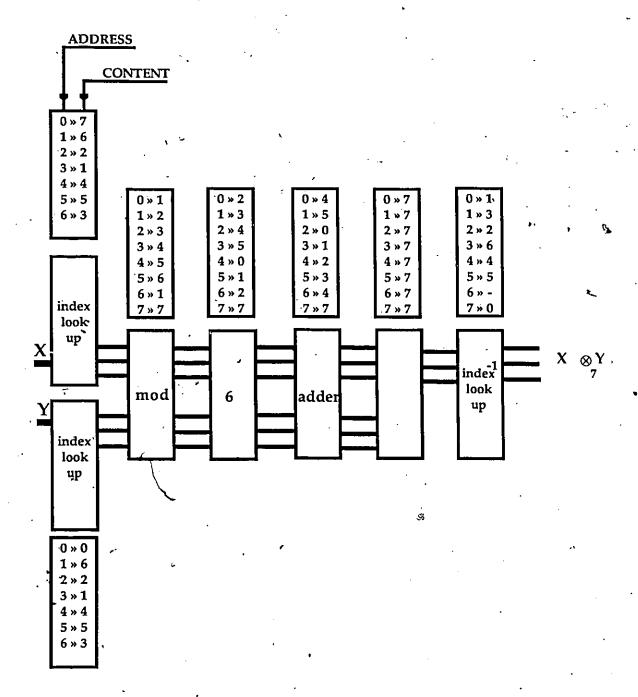

| Fig 3.13 Prime base multiplication when Y≠0,                                                    | 59          |

| Fig 3. 14 A structure for prime moduli multiplication                                           |             |

| Fig 3.15 Cell for prime moduli multiplication                                                   | 62          |

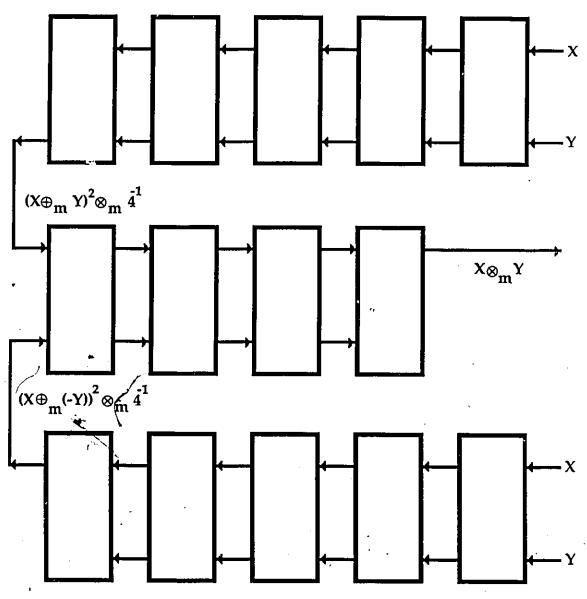

| Fig 3.16 A mod m multiplier based on quarter square technique                                   |             |

| Fig 3.17 Modulo m reduction using an array of BIPSPm cells                                      | 66          |

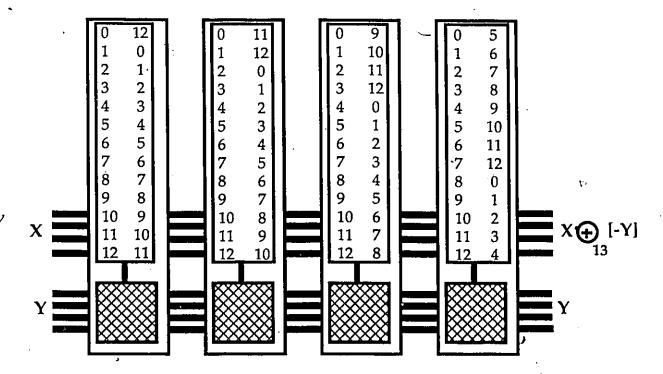

| Fig 3.18 ROM Contents for -29 ⊗ <sub>11</sub> 13                                                | 67          |

| Fig 3.19 Reducing a 14 bit binary number using the original cell                                |             |

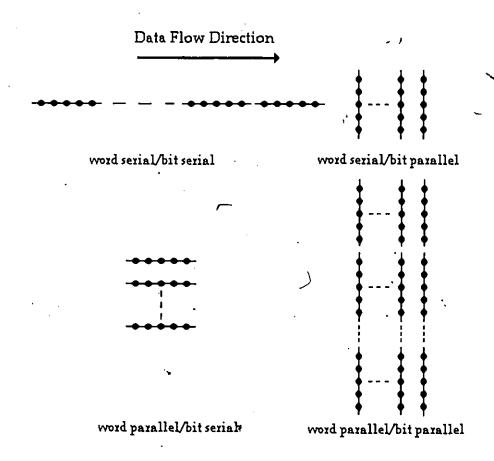

| Fig 4.1 Input data flow                                                                         | 74          |

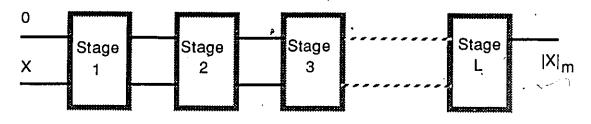

| Fig 4.2 Block diagram for word serial/bit serial                                                | 75          |

| Fig 4.3 Timing for a serial bit FIR filter                                                      | 76          |

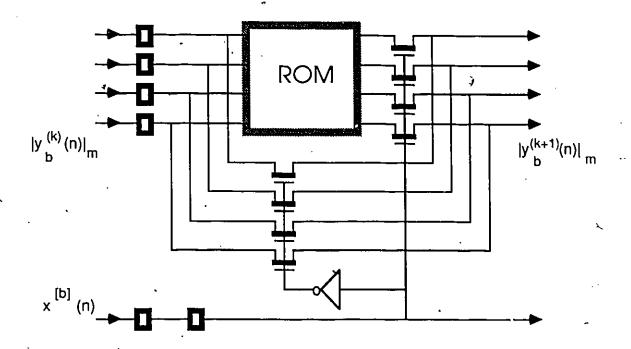

| Fig 4.4 BIPSPm cell for the bit serial FIR filter                                               | 78          |

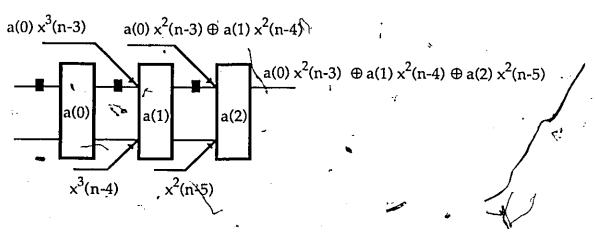

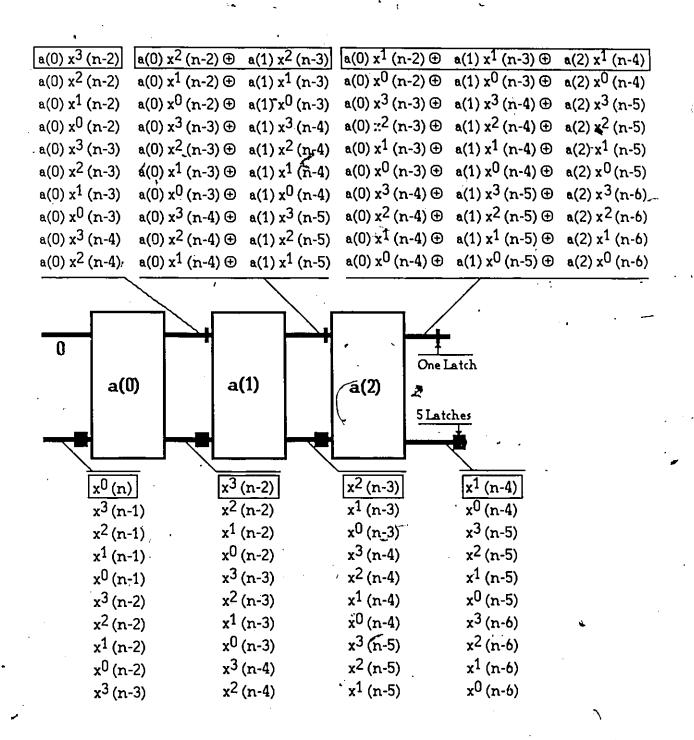

| Fig 4.5 Bit serial FIR filter for N=3, B=4                                                      | <b>.</b> 79 |

| Fig 4.6 Adder block for bit serial FIR filter                                                   | 80          |

| Fig 4.7 Bit parallel FIR filter structure                                                       | 82          |

| Fig 4.8 BIPSPm with a modified X data path                                                      | 84          |

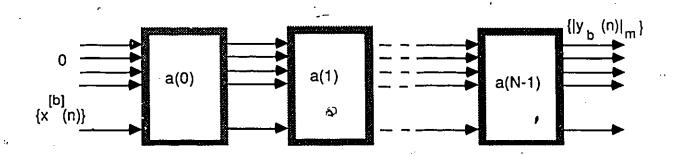

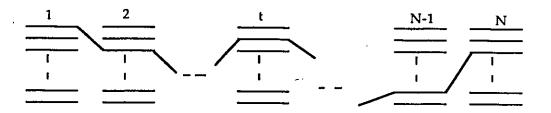

| Fig 4.9 Linear array for an Nth order FIR filter                                                | 84          |

| Fig 4.10 Modulo m adder for FJR filter                                                          | 85          |

| Fig 4.11 The modified cell for word serial/bit parallel FIR filter | 87  |

|--------------------------------------------------------------------|-----|

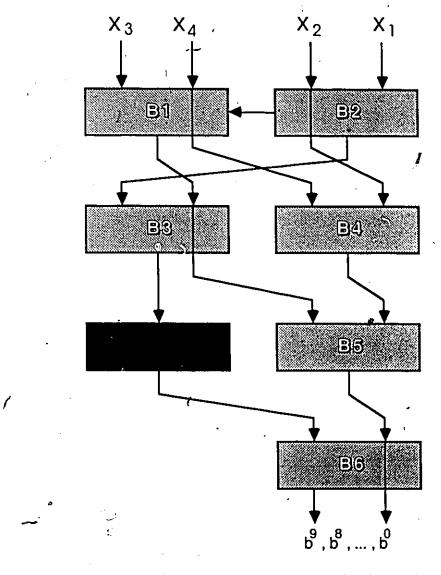

| Fig 4.12 A simplified block diagram of RADIUS                      | 90  |

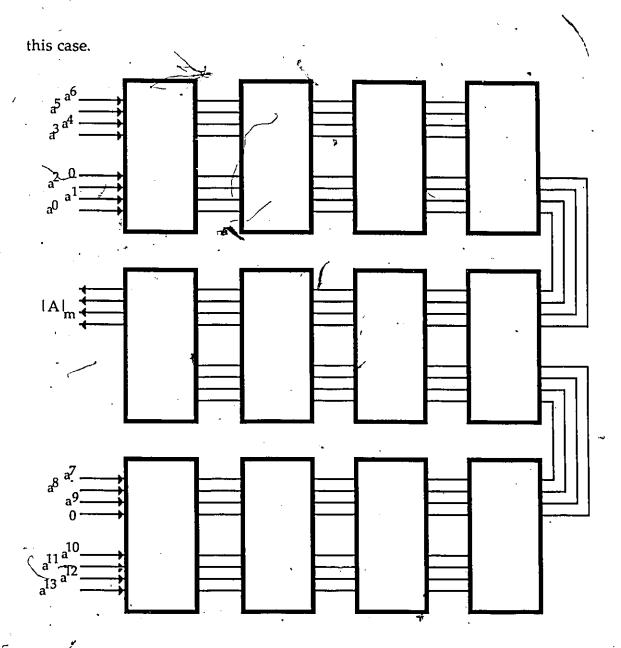

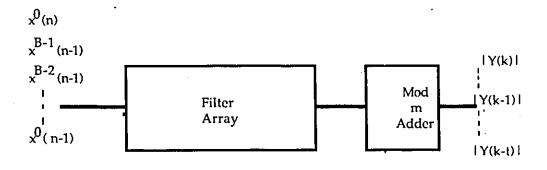

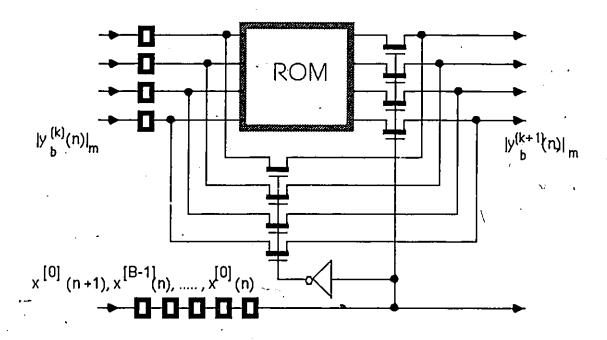

| Fig 4.13 Block Diagram of RADIUS using BIPSPm                      | 92  |

| Fig 4.14 Structure for binary correlator                           | 95  |

| Fig 4.15 The correlator cell based on BIPSPm                       |     |

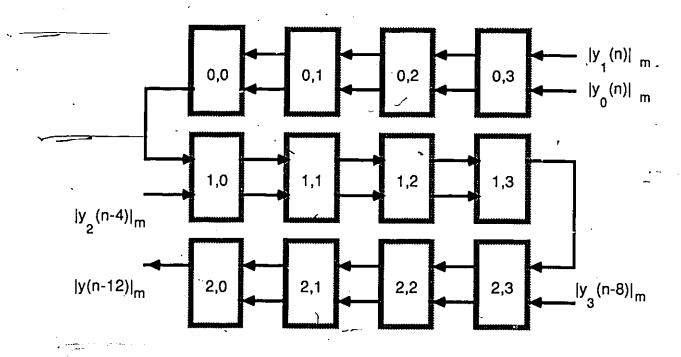

| Fig 4. 16 Scaling and reverse mapping array for four 5-bit moduli, |     |

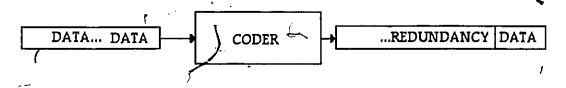

| Fig. 5.1 Systematic codes                                          | 112 |

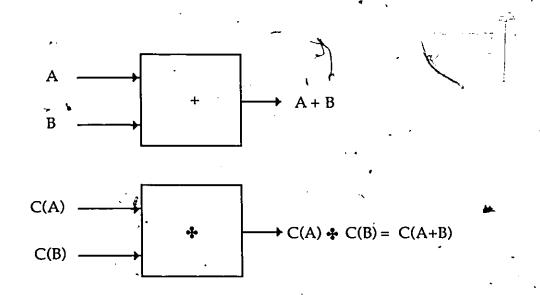

| Fig 5.2 Separate adder and checker                                 |     |

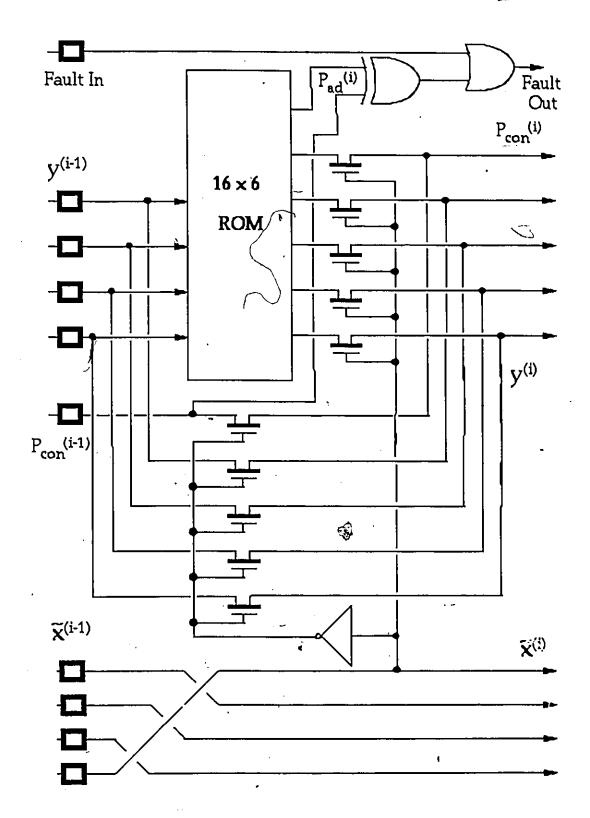

| Fig 5.3 Systolic Cell with Fault Detection Circuit                 | 118 |

| Fig 5.4 Operation of the cell in an array                          | 120 |

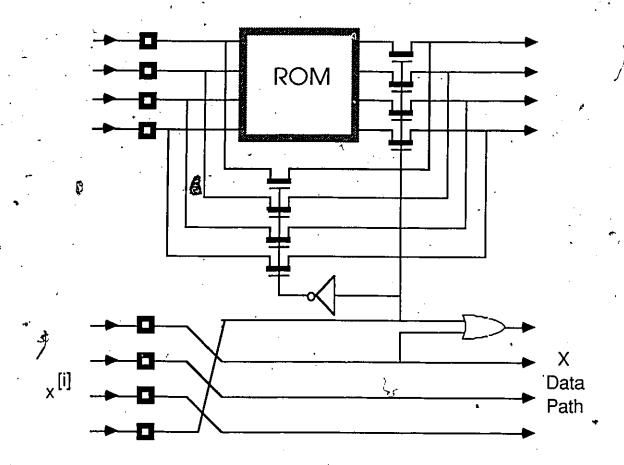

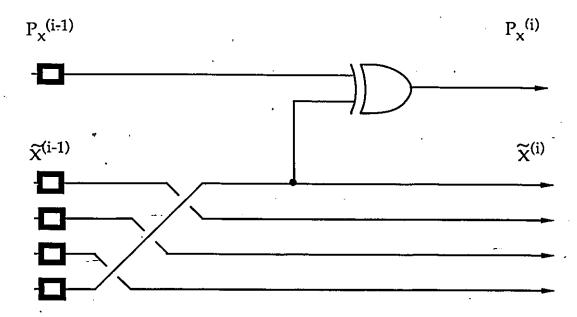

| Fig 5.5 Parity fault detection circuitry for X(i) data             | 124 |

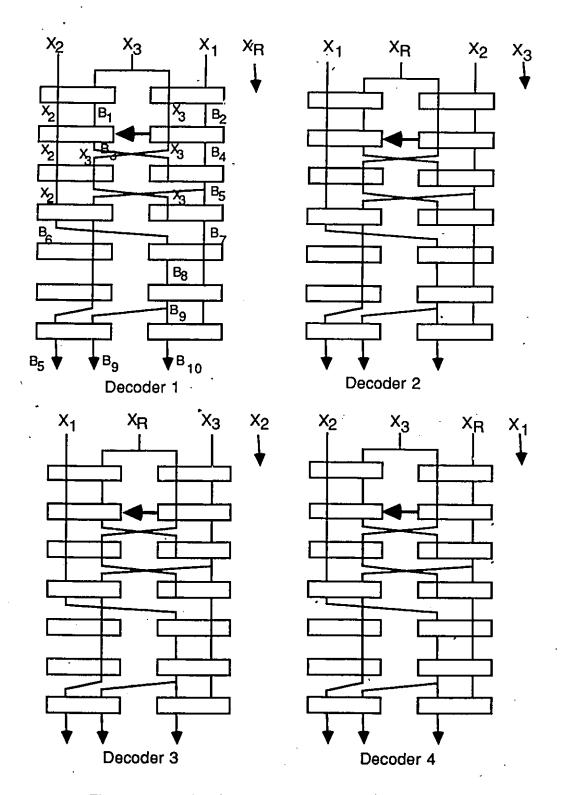

| Fig 5.6 Redundant Decoder for L=3 r=1                              |     |

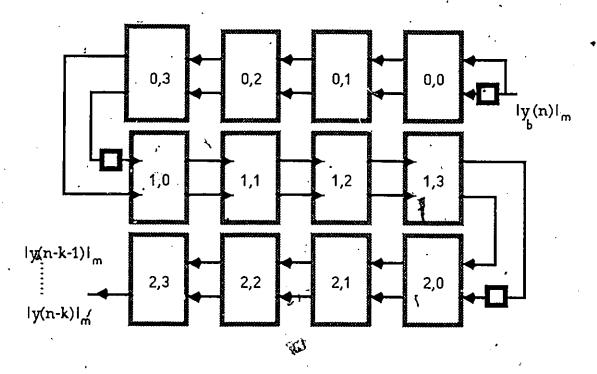

| Fig 5.7 Example of Fault-tolerant decoder for L=3, r=1             | 131 |

| Fig 5.8 A representation of a ROM with its function                | 136 |

| Fig 5.9 Test vector path in the array                              | 137 |

### LIST OF SYMBOLS

| gcd (a,b)                      | greatest common divisors of a, and b           |  |  |  |

|--------------------------------|------------------------------------------------|--|--|--|

| a <sup>-1</sup>   <sub>m</sub> | multiplicative inverse of a modulo m           |  |  |  |

| L                              | number of moduli                               |  |  |  |

| lxl <sub>m,</sub>              | the residue of x modulo m                      |  |  |  |

| В .                            | binary operation on groups                     |  |  |  |

| c                              | is an identity element                         |  |  |  |

| <ga, b=""></ga,>               | group with operation $B$                       |  |  |  |

| < R, B, ] >                    | ring with operations B, ]                      |  |  |  |

| R(m)                           | ring with modulo m addition and multiplication |  |  |  |

| $\oplus_{m}$                   | addition modulo m                              |  |  |  |

| ⊗ <sub>m</sub>                 | multiplication modulo m                        |  |  |  |

| $\sum_{m}$                     | summation modulo m                             |  |  |  |

|                                | round down operation                           |  |  |  |

| Г.]                            | round up operation                             |  |  |  |

| X                              | The additive inverse of X                      |  |  |  |

| M                              | dynamic range                                  |  |  |  |

| $M_{\mathrm{T}}$               | total dynamic range                            |  |  |  |

| В                              | number of bits in m                            |  |  |  |

| T.                             | number of redundant moduli                     |  |  |  |

| y <sup>lil</sup>               | i <sup>th</sup> bit in y                       |  |  |  |

| a V b                          | logical OR of a and b; a, and $b \in \{0, 1\}$ |  |  |  |

# CHAPTER 1

#### Introduction

Over the past four decades the computer industry has experienced four generations of development, physically marked by the rapid evolution of building blocks from relays and vacuum tubes, to discrete diodes and transistors, to small and medium-scale integrated circuits, and, finally, to large and very-large-scale integrated devices. An increase of many orders of magnitude of device speeds, together with dramatic reductions in hardware cost and physical size, have greatly enhanced computer performances. Constant demand for higher performance architectures, however, has

There are two main limitations to the von Neumann architecture which must be overcome:

accelerated the need for processing systems that are radical departures from

the classical von Neumann architecture, or control flow computer, which has

dominated computer design over the last four decades.

A. The sequential nature of such machines is a major bottleneck to high speed processing and places a basic limit on their operating capabilities. The purely sequential nature of most conventional

computing systems also imposes certain constraints on the associated algorithms and programs used.

B. In many typical computers, processors are separated from memory by long communication paths. Ultimately, the computation speed of such a machine will be dominated by the time taken to communicate information between the processor and the memory rather than the intrinsic switching speeds of logic devices. The full potential of future high speed switching technologies will therefore not be realized unless computational circuits are developed in which communication paths are short.

The limitations described above have been recognized for some twenty years or more and have stimulated research on novel forms of computer architecture. As Kuhn points out [Kuh'81]:

"Whenever a computer designer has reached for a level of performance beyond that provided by hiscontemporary technology, parallel processing has been his apprentice."

Parallelism in computing systems is simply simultaneous processing of more than one task at a time, and clearly there is no limit in principle to the number of concurrent actions. Thus, parallelism has the potential of offering an arbitrary degree of improvement in computing speed. The fundamental argument is that, if a job can be broken down into N independent sub-tasks, then up to an N fold increase in computation speed may be obtained by

allowing these sub-tasks to be processed on N elements running concurrently. More information on the background and the subject of parallel computers, is available in the text by Hwang and Briggs [Hwa'84], Kuhn [Kuh'81], and Zakharov [Zak'84] and their references.

Parallel computation is not a new idea and it seems to have occurred, in one form or another, to nearly all the pioneers of computing from the earliest times. The idea of parallelism certainly appears to have been considered by John von Neumann who was also the major pioneer in parallel computing via his research on array computers or cellular automata. It is important to note that there have been a large number of good ideas in parallel processing that could not be implemented in the past, or only implemented with poor effectiveness, because of the difficulties associated with hardware limitations.

It is only with the advent of VLSI and the promise of cheap processing power that the subject of Parallel Processing has really come of age. VLSI provides the medium through which many, previously conceptual, ideas can be implemented economically. With this advance, it has been realized that methods of exploiting the potentials are not well understood and that we are only beginning to appreciate the constraints imposed by the technology.

The digital microelectronic technologies with the highest complexity also have definite performance limitation the fundamental limitation is the high cost of communication, relative to logic and storage. Communication is expensive in chip area, most of the area of a chip is covered with wires on several levels with transistor switches rarely taking more than five percent of the area on the lowest level [Sei'84]. When it comes to performance,

communication is expensive in delay where the non zero resistance of the wires, together with the parasitic distributed capacitance, imposes a delay in the wire itself that is becoming increasingly significant at smaller geometries. Communication is also expensive in sending signals between chips, when package pin limitation, the area used for bonding pads and pad drivers are considered.

Finally, the dynamic power supplied to the chip, and dissipated in the circuit that switch capacitive signal nodes, is typically dominated by the parasitic capacitance of the internal wires, bonding pads, and inter chip wires, rather than by the capacitance of the transistor gates.

Thus both the cost and performance matrices of VLSI favour architectures in which communication is localized. This principle of locality is seen at every level of VLSI design.

In VLSI, there is an emphasis on keeping the overall architecture as regular and modular as possible, thus reducing the overall complexity. If a structure can truly be decomposed into a few types of simple substructures or building blocks great saving can be achieved. This is specially true for VLSI design where a single chip comprises hundreds of thousands of components.

Homogeneous machines are certainly simpler to design; one merely patterns the layout for one of these processing elements and replicates this pattern appropriately. Such iterative layout patterns have been applied in the past for silicon memories, registers, and array multipliers. Similar techniques also have been used in constructing large software systems.

A "good" VLSI architecture in this context should possess one or more of the following properties [Fos'80]:

- A. The architecture is implementable by a few different types of simple cells. \_

- B. The architecture's data and control path are simple and regular, so that the cells may be connected by a network with local and regular interconnections.

- C. The architecture uses extensive pipelining and multiprocessing.

In this way a large number of cells are active at one time so that the overall computational rate of the simple cell is high.

Under certain circumstances, mostly in real-time application areas, the supervisory overhead incurred in general-purpose computers often makes them too slow and expensive for real time signal and image processing. To achieve a throughput rate adequate for these applications, the only feasible alternative appears to be massively concurrent processing by special-purpose hardware.

During the late 70's, H.T. Kung and his colleagues at Carnegie-Mellon University, observed that certain problems can be solved by means of a regular, locally interconnected array of identical Processing Elements (PEs) that repeatedly execute a set of identical instructions in a lock-step fashion. They used the term "systolic array" to describe such hardware architectures. These architectures capitalize on regular and modular structures that match the computational requirements of many algorithms. Much research has

been done and much has been written about the design of algorithms and architectures suitable for such structures. The applications for which systolic designs have been proposed can be broadly categorized into, signal and image processing, matrix arithmetic, and non-numeric applications.

Digital signal and image processing encompasses a variety of mathematical and algorithmic techniques. Most signal and image processing algorithms are dominated by convolution and correlation filtering, and certain key linear algebraic methods. These algorithms possess properties such as regularity, recursiveness, and locality, and these properties can be exploited using systolic design concepts.

To synthesize a systolic array from the description of an algorithm, a designer needs an understanding and familiarity with the principles behind systolic design concepts, the application, the algorithm, and the technology. The design process is slow and error prone and normally the resulting designs are not guaranteed to be optimal. Progress has been made in the development of systematic design techniques to automate this process [For'85]. These techniques are not complete, however, and until more is learned about automating the design process there will commue to be need for 'hand-crafting' designs by skilled people. The basic operation performed in each cycle by each processing element in the various systolic arrays can range from a simple bit-slice operation [Mac'82], to word level [Cap'81], and even execution of a complete program [Fou'87].

During the last few years special attention have been paid to some aspects of the systolic design concept. These include array synchronization, testing of the fabricated chips, run time reliability, partitioning of large problem, and universal building blocks.

#### Synchronization:

In large synchronous systolic arrays, clock lines, the only global signals in true systolic designs, can introduce clock skew. Possible approaches that avoid the problem of clock skew include using efficient layout of the the clock distribution network, and unidirectional data flow. An alternative to the design of a globally synchronous array is to achieve a self timed system through the use of an asynchrounous handshaking mechanism established between the adjacent cells. This category of array designs are referred to as wavefront arrays [Kun'83].

#### Testing:

Even the most advanced manufacturing techniques may produce faulty chips. The yield figures drop rapidly as the number of devices increase. The increase in the ratio of logic to pins which drastically reduces the controllability and observability of the logic on the chip which makes fault diagnoses difficult. Testing of the existing complex chips are already causing difficulties, and it is expected to be more difficult with the higher complexity chips that are being proposed. Techniques for reducing the test time and simpler methods for generating test vectors applicable to special cases have

been proposed in the past [Kor'86] but more is left to be done in this area.

#### Reliability:

Even satisfactorily tested chips may not be flawless, or they may become damaged during their operation. Since any functional error in a high performance system may seriously jeopardize the operation of the system, some level of fault tolerance must be incorporated. The problem of run time fault tolerance also requires more attention with the goal of maximizing the reliability while minimizing the corresponding overhead [Abr'86].

#### Partitioning of large problems:

State of the art technology allows only a limited number of processing elements, with respect to the size of large problems, to be fabricated on the same chip or wafer. The problem must be partitioned so that the same algorithm can be used to solve the smaller problems and so that an array of small, fixed size can be used [Mol'86]. A partitioned approach may also be needed to circumvent the I/O problem of the systolic arrays [Haw'84].

#### Universal building blocks:

The modular design of systolic arrays allows designers to rapidly prototype their designs using off-the-shelf devices, such as microprocessors. This has led to the development of "universal

building blocks" that can be used for many systolic arrays. Commercially available chips worthy of consideration as basic modules include INMOS Transputer, TMS32010, and NEC dataflow chip  $\mu$ PD 7281 [For'87]. The problems involved with this approach include the development of programming tools and support for flexible interconnections.

It appears that designing a chip containing hundreds of thousands of devices to perform highly complex functions is not the sole goal any more. If testing of the chip becomes too expensive or the reliability of the system based on this chip is lower than an acceptable level, it would not have commercial success.

Let us first examine the problem of clock skew more closely. Consider a simple 1-D convolution which, in practice, maps onto a 2-D grid array with the carry and data information flowing in different directions. It is known that clocking a large 2-D array is a non trivial matter, while large linear arrays can be effectively synchronized, even in the presence of large signal propagation delays. As Fisher and H.T. Kung [Fis'85], pointed out:

" ... one-dimensional arrays can be clocked at a rate independent of their size under fairly robust assumption, while two-dimensional arrays and other graphs with similar properties cannot."

A possible solution is to employ Residue Number Systems (RNS) to alleviate the carry flow across the second dimension. RNS naturally restricts the propagation of the carries within smaller computational rings rather than the entire dynamic range. Also, the fact that Redundant Residue Number Systems (RRNS) have properties useful for error detection, error correction, and fault tolerance in digital signal processing necessitates its thorough study for the implementation of suitable algorithms in VLSI. The following provides a brief background on RNS.

#### 1.1. RNS and Signal Processing

The first published report on a residue based electronic computer, was that of Svoboda and Valach in Czechoslovakia [Svo'55]. This report described a hardwired small-moduli, RNS computer used to study error codes. At approximately the same time, Garner [Gar'59], worked independently on the basic concepts of RNS arithmetic.

During 50's researchers became interested in fault tolerant properties of RNS which could improve the reliability of vacuum tube digital computers. But with the availability of transistors, more reliable digital computers, were designed. This resulted in a decline in the interest in fault tolerant residue arithmetic. Fortunately the interest did not disappear entirely, researchers developed the theory of RNS arithmetic and error detection and correction further in late 60's and early 70's [Bar,73], [Man'72]. The availability of inexpensive semiconductor chips brought more interested researchers into this field, a number of digital signal processors based on RNS were implemented [Jen'77], [Hua'81], [Nag'83], [Mil'84].

The VLSI era arrived in the 70's, but it took sometime before researchers, who were interested in RNS, started exploring the new media [Jen'82b], [Ban'86].

#### 1.2. The Objectives and Review of the Research Work

There is a strong belief that RNS can alleviate some of the problems discussed earlier in this chapter. To prove this, we will start anew by taking a different approach, one that satisfies, in the first place, the requirements of "good" VLSI design. This is because mapping designs suitable for discrete components does not take into account the limitations of the technology and may create more problems than they can solve. Once this basic goal is achieved, the objective is to implement all aspects of digital signal processing algorithms, from binary to RNS encoding, the signal processing algorithm itself, and decoding back into binary.

Finally the capabilities of the new technique, in mitigating some of the problems related to VLSI systems, such as fault detection and correction, and testing will be studied.

#### 1.3. Organization of Thesis

Chapter 2 covers the pre-requisite material for the research. In particular a concise review of some of the fundamentals on finite ring and field structure is presented and the mathematical concepts of Residue Number Systems

(RNS) are introduced. This chapter provides a background for the definitions and notations used through the thesis.

Chapter 3 describes our proposed architecture, a generic cell which can be used to perform finite ring addition, and multiplication operations. Comparison of two techniques for performing modular addition, the conventional approach and the proposed technique, is given. Examples of subtraction, multiplication, and binary to residue encoder operations based on this architecture are given.

Chapter 4 discusses the use of the new structure for Digital Signal Processing Applications. Different structures for implementation of Finite Impulse Response (FIR) filters— both bit serial and bit parallel approaches are provided. A fixed coefficient FIR filter implemented using both, a very efficient bit sliced binary and the proposed approach in this chapter are compared. Finally the operation of residue to binary decoding and scaling are discussed and suitable structures are given.

Chapter 5 deals with the important issues of fault detection and correction using the cell discussed in previous chapters. It is shown that a small hardware overhead enables the cell to perform a concurrent fault detection operation in the structure. A simplified Redundant Residue Number System (RRNS) which uses one redundant modulus instead of two is discussed and used in a fault correcting system.

Enhancements in testability of the structures based on the new cell is also discussed in this chapter. It is shown that the ability to bypass the entire

memory and a major part of the logic used in the cell simplifies testing the chip and shortens the time period required.

Chapter 6 summarizes the result of this research.

# CHAPTER 2

#### **DISCRETE MATHEMATICS AND**

#### THE RESIDUE NUMBER SYSTEMS

#### **Abstract**

This chapter provides the theoretical background required for the understanding of the work developed later in this dissertation. Some of the fundamental concepts of discrete mathematics are reviewed to the extent needed for appreciation of Residue Number Systems (RNS). A brief introduction to the RNS then follows.

## 2.1. Introduction

There is at present a growing body of opinion that in the decades ahead discrete mathematics will be of increasing importance. Certainly, one reason for this opinion is the rapid development of computer technology, and the use of discrete mathematics as one of its major tools. The increasing interest in the investigation of the theory of formal languages, computer cryptography, and theory of coding are some of the uses of discrete

mathematical structures.

In this chapter we intend to present some of the preliminary concepts of discrete mathematics, the emphasis is on the basics which form the foundations of the work under taken in this thesis. A review of discrete mathematical structures of groups, rings, and fields, their properties and various ways of forming them are given. Residue number systems and certain RNS operations, the so called difficult operations, used in this work are explained.

The notation used throughout this dissertation will also be introduced. A notation already exists for residue number systems; however, for cascaded, mixed ring (field) operations, the notation can become confusing, with unwieldy nesting of modulo parentheses. We will use special symbols for operating over the different systems, so that such operations can be readily understood in an expression. Numerous references are provided for the interested reader to further explore in these topics.

#### 2.2. Discrete Mathematical Structures

As a starting point, it would seem appropriate to formally define the meaning of a binary operation:

#### Definition

A binary operation, +, on a set is a rule (a method, a function, or a formula)

that assigns to each ordered pair of elements of the set some element of the set.

Note that the word "ordered" is very important in this definition, because it allows the possibility that the element assigned to the pair (a,b) be different from the element assigned to the pair (b,a). Also this definition permits the result of the binary operation to be any one of the operands or a third element of the set (property of closure). Addition and multiplication on an infinite set of integers is an example of a binary operation.

Definition

A binary operation + is said to be associative if and only if

$$(a+b)+c=a+(b+c)$$

and is commutative if and only if

$$a + b = b + a$$

for all a,b,c belonging to the set.

With the above definitions we can now review some of the algebraic structures which are used frequently in discrete mathematics. We start with the structure of a group, a term coined by Galois about 150 years ago to describe sets of one-to-one functions on finite sets that could be grouped together to form a closed set [Gal'86,34].

#### Definition

A group  $\langle G, + \rangle$  is a set G, together with a binary operation + on G, such that the following axioms are satisfied:

Э

- g1. The binary operation is associative.

- g2. There is an element e in G such that e + x = x + e = x, this element, e is an identity element for the binary operation on G.

- g3. For each a in G, there is an element a' in G with the property that

$$a' + a = a + a' = e$$

.

The element a' is the inverse of a with respect to binary operation +.

Note that the property of closure is implied as a consequence of the binary operation and therefore is not added to the above list of axioms.

If the binary operation is also commutative the group is named abelian. The set of all the integers with the operation of addition generates a group, while the same set and the operation of multiplication is not a group because not all the elements have inverses. The simple algebraic structure of the group enables us to solve all the linear equations of the form a + x = b.

The order of an element a in a group G is the smallest positive integer n such...

that  $a^n = e$ . The number of elements of a group (finite or infinite) is called its order, the symbol |G| is normally used to denote the order of the group, G.

Definition

Let  $\langle G_a, +^a \rangle$  and  $\langle G_b, +^b \rangle$  be groups. A one to one onto (bijective) function  $f: G_a \rightarrow G_b$ ; with the property that for any two elements  $g_a$  and  $g_a$  in  $G_a$

$$f(g_a + a g_k) = f(g_a) + b f(g_a)$$

is called an isomorphism from  $G_a$  to  $G_b$  [Pin'82,89]. For example, consider the groups defined by multiplication modulo 3, shown as  $\otimes_3$ , on  $Z'_3=Z_3-\{0\}$  and addition modulo 2, shown as  $\oplus_2$ , on  $Z_2$  as given in Fig (2.1).

|   | 0 | 1 |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 1 | 0 |

Table for addition mod 2

|   |   | 0 | 1 | 2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---|---|---|---|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 0 | 0 | 1 | 2  | 771 _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 1 | 0 | 1 | 2  | <sup>2</sup> 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| l | 2 | 0 | 2 | 1] | \range \r |

Table for multiplication mod 3

Fig 2.1 Operation tables for  $\langle Z_2, \oplus_2 \rangle$  and  $\langle Z'_3, \otimes_3 \rangle$

It is simple to find the  $f: Z_3 \to Z_2$  for which f(2)=1 and f(1)=0 maps  $\langle Z_3, \otimes_3 \rangle$  isomorphically into  $\langle Z_2, \oplus_2 \rangle$ .

When the group contains an element g which generates all the group's elements as given here

$$G=\{g^n; n\in Z\}$$

then g is said to be a generator and the group G is a cyclic group.

It can be proven that the set  $\{0,1,2,3,...,n-1\}$  is a cyclic group  $Z_n$  of elements under addition modulo n.

Next we will discuss the algebraic structure of a ring. The term "ring" was coined by the German mathematician David Hilbert, in the late 19 century, to define a set of elements with two binary operations.

#### Definition

A ring < R, +, \* > is a set R together with two binary operations + and \*, (normally called addition and multiplication), defined on R such that the following axioms are satisfied:

- r1.  $\langle R, + \rangle$  is an abelian group.

- r2 ★ or multiplication is associative.

- r3. For all  $a,b,c \in \mathbb{R}$  the distributive law holds.

$$a * (b + c) = (a * b) + (a * c)$$

$$(a+b)*c = (a*c)+(b*c)$$

For example the set of complex numbers, C, together with the operations of addition and multiplication is a ring. Another appropriate example of the rings is the set of  $Z_n=\{0,1,2,...,n-1\}$  and the operation of addition and multiplication modulo n.

Note that the operation of \*, is considerably weaker than the operation of + in the rings since the operation does not have to be commutative and

multiplicative identity need not exist.

Groups and rings can be built in many different ways, as an example assume the group structures

it is proven that the structure

$$\widetilde{G} = \langle (g_0, g_0), (g_0, g_1), (g_0, g_1), ...(g_{a-1}), g_{b}(b-1)); \widetilde{+} \rangle$$

is a group with order  $|\tilde{G}|$  =ab, under the operation  $\tilde{+}$  defined as follows

$$(g_{a}^{i}, g_{b}^{k}) \stackrel{\sim}{+} (g_{a}^{p}, g_{b}^{q})) = (g_{a}^{i} + g_{a}^{p}, g_{b}^{k} + g_{b}^{q}))$$

The group,  $\tilde{G}$ , formed as above, is said to be the direct product of  $G_a$  and  $G_b$  shown as  $G_a \times G_b$ .

The same technique can be utilized to create new rings. Suppose we have the two rings  $<R_a; +\hat{a}, **a>$  and  $<R_b; +b, *b>$ . Using a similar method the resultant ring is  $<\tilde{R}; +, **a>$ , the elements of which are  $(r_a^i, r_b^k)$ ,  $0 \le i \le a-1$  and  $0 \le k \le b-1$  and the operations are defined as:

$$(r_a^i, r_b^k) \stackrel{\sim}{+} (r_a^p, r_b^q) = (r_a^i + a r_a^p, r_b^k + b r_b^q)$$

$$(r_a^i, r_b^k) \stackrel{\sim}{*} (r_a^p, r_b^q) = (r_a^i *^a r_a^p, r_b^k *^b r_b^q)$$

It seems logical to name the ring  $\widetilde{R}$  as constructed above as the direct product of rings  $R_a$  and  $R_b$ , shown as  $R_a \times R_b$ ; however, this is not the case and the

⅝

term direct sum is most often used<sup>†</sup>. This construction can be iterated any finite number of times to obtain the direct product (sum) of a finite number (n) of groups (rings).

Another interesting example of forming rings is to use the set of all polynomials in the indeterminate x with integer coefficients in ring R, this structure is a ring under polynomial addition and multiplication as described below.

Polynomial Rings:

Let R be a commutative ring with unity. Each expression of the form

$$a_n x^n + ... + a_2 x^2 + a_1 x^1 + a_0$$

is called a polynomial in x with coefficients,  $a_k$ , in ring R. Obviously there exists infinitely many such polynomials (even when ring R is finite).

The set of all these polynomials and the operations of addition and multiplication, defined for these polynomials, give algebraic structures known as polynomial rings, shown as R[x].

Polynomial ring addition is defined by combining the like terms binary operations of addition addition operation of the ring R. Multiplication is defined by combining the polynomial coefficients as performed in conventional polynomial multiplication, using the addition and multiplication over the ring R [Blo'87]. Ring isomorphisms are similar to

<sup>†</sup> In fact the term direct sum and direct product has been used interchangeably in different texts , for the procedure explained above [Gal'86], [Pin'82], [Jac'51], [Sto'73], [Gol'73].

group isomorphisms as defined below.

Definition

Let  $\langle R_a, +a, *a \rangle$  and  $\langle R_b, +b, *b \rangle$  be two rings. If there exists a one to one onto (bijective) function such as f for which

$$f(\mathbf{r}_{a}^{i} + \mathbf{r}_{a}^{k}) = f(\mathbf{r}_{a}^{i}) + \mathbf{b} f(\mathbf{r}_{a}^{k})$$

$$f(\mathbf{r}_{a}^{i} * \mathbf{a} \mathbf{r}_{a}^{k}) = f(\mathbf{r}_{a}^{i}) * \mathbf{b} f(\mathbf{r}_{a}^{k})$$

and the identities are the same  $f(1^{Ra}) = 1^{Rb}$ , then two rings are isomorphic rings [Gil'76,174], shown as  $R_a = R_b$ .

It is proven that the direct product (sum) of  $R_a \times R_b$  is identical to  $R_{ab}$  to within isomorphism if and only if gcd (a,b) = 1 [Gil'76,177]. It is this theorem that enables us to slice a large ring into several smaller rings, the bases for building residue number systems.

A nonzero element of a commutative ring need not have a multiplicative inverse. If all the elements of a ring, except the null element, have multiplicative inverses, the structure is said to be a field. For example  $\langle Q,+,x\rangle$  is a field, where Q is the set of all rational numbers. It is proven that the ring  $Z_p$  and addition and multiplication modulo p is a field, when p is a prime, and is denoted as a Galios Field, GF(p), after the French mathematician Evariste Galois. GF(p) has exactly p elements  $\{0,1,2,...,p-1\}$ , and since there are infinitely many primes, this construction yields infinitely many finite fields.

Every finite field has at least one generator g∈ GF(p); such that the first (p-1)

powers of g , together with 0, constitutes the complete set GF(p) of the field elements. For example with p=11, g=2 is a generator.

The exponents are referred to as indices, and can be viewed as a set of finite field logarithms. Suppose a and b are elements of GF(p) and  $a=g^{\alpha}$ ,  $b=g^{\beta}$ , then

$$a \otimes_p b = g^{(\alpha \oplus_{p-1} \beta)}$$

This is a good example of the use of isomorphism between a multiplicative group g having elements  $\{g_n\}=\{1,2,3,...,p-1\}$  with multiplication modulo p, and the additive group k having elements  $\{k_n\}=\{1,2,3,...,p-2\}$ . In chapter 3, we will present a structure which uses this property to multiply two numbers.

Instead of forming a field from  $Z_p$ , with p prime, one can take a ring of polynomials together with an irreducible polynomial where coefficients  $\in Z_p$ , and build an extension field. As an example let us take GF(2) and form a ring of polynomials with the coefficients in GF(2) and the irreducible polynomial as  $p(x)=x^3+x+1$ . Since p(x) is cubic, we can take as representatives of (mod p) equivalence classes the 8 polynomials of the form  $a^2x^2+a^1x+a^0$ ,  $a^i\in GF(2)$ . The number of elements in these types of field is always  $p^n$ , where [McE'87,25]

$$n = deg(p(x))$$

Addition in the extension field simply follows the addition rule discussed previously, while multiplication of two elements such as  $a^2x^2+a^1x+a^0$  and

$a'^2x^2+a'^1x+a'^0$  generates  $x^4$  and  $x^3$  terms which in our example must be replaced by  $x^3=x+1$ , and  $x^4=x^3+x$  in order to have the field properties preserved.

Rings and fields with modular addition and multiplication show special properties. Some of these properties were discussed above, in the following a brief discussion of a general class of modular systems formed by selecting several simple modular structures (either rings or fields) called residue number systems will be given.

The notations for ring with modular addition and modular multiplication are similar to that used so far in this chapter, only the modular ring will be given as a subscript of the operations. Thus  $\oplus_m$ ,  $\otimes_m$ ,  $\sum_m$  indicates the addition, multiplication, and summation over the ring with modulus m.

### 2.3. Residue Number Systems

The roots of this number system go-back almost 2000 years. The residue number system is a non weighted integer system which differs radically in many aspects from the more conventional weighted magnitude number systems, such as the binary and decimal, fixed radix systems.

Like many other number systems it has advantages and disadvantages. It is easy and efficient to add and multiply; however, not so easy to divide and compare. It is also easy to perform forward transformation (code) but more difficult to perform reverse transformation (decode). It has been shown that it

is inefficient to build general purpose computers based on RNS [Sza'67], however some very efficient special purpose hardware has been reported using this system [Fou'82], [Nag'83], [Mil'84].

It is more appropriate and helpful to review RNS in terms of 2 classes: standard residue number systems (RNS) and redundant residue number systems (RRNS).

#### 2.3.1. Standard Residue Number system (RNS)

As discussed in section 2.2, the direct sum of L rings,  $(z_{m_1}, z_{m_2}, z_{m_3}, ..., z_{m_L})$  and  $(z_{m_1}, z_{m_2}, z_{m_3}, ..., z_{m_L})$  and  $(z_{m_1}, z_{m_2}, z_{m_3}, ..., z_{m_L})$

gcd

$$(m_i, m_k) = 1$$

; for i,k  $\in \{1, 2,...,L\}$  and i  $\neq k$

where

$$M = \prod_{i=1}^{L} m_i$$

This unique mapping between a large ring and several smaller rings is used to code and decode numbers represented.

The RNS is defined in terms of a set of L relatively prime moduli.

$$(m_1, m_2, m_3, ..., m_L)$$

where L is the number of moduli in the system and gcd  $(m_i, m_k) = 1$  for  $i \neq k$ ,  $i,k \in \{1,2,...,L\}$ . Any integer X<M can be represented as an L-tuple

$$X = (x_1, x_2, x_3, ..., x_L)$$

where  $x_i = X \mod m_i = |X|_{m_i}$   $i \in \{1, 2, ..., L\}$

The dynamic range is defined as the set of integers that can be encoded in the RNS system and is given by

$$-M = \prod_{i=1}^{L} m_i$$

Let \* represent the binary operation of addition, subtraction, or multiplication. If Z=X\*Y, then we can easily show that

$$|Z|_{m_i} = z_i = x_i *_{m_i} y_i$$

(2.1)

This equation shows the independence of binary operations on different moduli. It is this property which allows very fast parallel implementation of addition and multiplication, in contrast with conventional fixed radix representation where a carry or a borrow is passed between adjacent digits.

## 2.3.2. Signed Residue Number System

The dynamic range is partitioned into two portions the lower portion which represents the positive numbers and the upper portion representing negative numbers. Signed numbers can be introduced by defining a number X to be positive if

$$X \triangleleft M/2$$

and negative if

## $X \ge \lceil M/2 \rceil$

where  $\lfloor \alpha \rfloor$  and  $\lceil \alpha \rceil$  are round down and round up functions respectively.

The additive inverse of X,  $\overline{X}$  is defined by the relationship

$$X \oplus_{M} \overline{X} = 0$$

where  $\overline{X} = (\overline{x}_1, \overline{x}_2, ..., \overline{x}_L)$  with  $\overline{x}_i = m_i - x_i$ ; for  $i \in \{1, 2, ..., L\}$

If we use the above definitions to represent a signed number system, then the operations defined by eqn (2.1), preserve the rule of signed arithmetic [Jul'78]. Thus, binary operations can be carried out between signed numbers without an explicit knowledge of the sign or magnitude of the two numbers. Since sign determination is difficult, it is essential to use such a system.

## 2.3.3. Redundant Residue Number system (RRNS)

A redundant Residue Number System is defined as a standard residue number system to which r additional moduli are appended. All L+r moduli must be relatively prime to ensure a unique representation for each number. The r redundant moduli are not considered to increase the conventional dynamic range

$$M = \prod_{i=1}^{L} m_i \tag{2.2}$$

The total range is defined as:

$$M_T = \prod_{i=1}^{L+r} m_i \tag{2.3}$$

Any integer in the legitimate range  $0 \le X < M$  is represented by L+r residue digits; the interval, [M,M<sub>T</sub>), is called the illegitimate range.

Obviously, the RRNS has all the properties of the standard RNS, discussed above. The redundant moduli enable the system to detect errors if the reverse mapping of the number falls into illegitimate range. It is proven that an RRNS with r redundant moduli is capable of detecting r errors, or correcting  $\frac{r}{2}$  errors [Man'72].

## 2.4. Operations in RNS

As was described above, performing closed operations in RNS (addition, subtraction, and multiplication) in RNS is easy and straight forward with no interaction between the residue digits. However, there are some other operations such as division and RNS to binary conversion in which the different residue digits have to be combined together. In the following we will briefly discuss direct sum forward and reverse mappings.

## 2.4.1. Forward Mapping

Encoding an S bit binary number, x, into RNS is a simple and straightforward

operation considering that

$$x = \sum_{i=0}^{S-1} x^{[i]} 2^{i}$$

(2.4)

where  $x^{[i]}$  is the i<sup>th</sup> bit in x. The residue of x mod m,  $|x|_m$  can be computed using the following [Sza'67]:

$$|x|_{m} = \sum_{i=0}^{S-1} x^{[i]} |2^{i}|_{m}$$

(2.5)

## 2.4.2.Reverse Mapping

Decoding an RNS number into a weighted magnitude number system, is a more difficult operation and can be performed using two different techniques, as explained in the following.

## 2.4.2.1. Chinese Remainder Theorem

The Chinese Remainder Theorem (CRT) is the classical method of reconstructing an integer number from a set of residue digits.

It is given by

$$|X|_{M} = \sum_{i=0}^{L-1} \hat{m}_{i} \otimes_{M} (x_{i} \otimes_{m_{i}} \hat{m}_{i}^{-1})$$

(2.6)

where.

$$\hat{\mathbf{m}}_{i} = \frac{M}{m_{i}} \tag{2.7}$$

and  $m_i^{-1} \otimes_m m_i = 1$ . The fact that the moduli are relatively prime ensures that m, revists. One of the major difficulties in using this method is reducing the result modulo, M, usually a large number and not close to a power of 2.

#### 2.4.2.2. Mixed Radix Conversion

Mixed radix systems are weighted number system and can be defined in general using a set of radices, {...b2, b1, b0; b31, b-2, b-3...}. A real number X is represented as:

$$X \Leftrightarrow \{...a_{2}, a_{1}, a_{0}; a_{-1}, a_{-2}, a_{-3}...\}$$

where ai are mixed radix digits. X can be computed using [Knu'81'192]

$$X = ...a_3b_2b_1b_0 + a_2b_1b_0 + a_1b_0 + a_0 + a_{-1}/b_{-1} + a_{-2}/b_{-1}b_{-2} + ...$$

(2.8)

In the simplest form the  $\{b_i\}$  are positive integers and  $0 \le a_i < b_i$ . A residue number system is said to be associated with a mixed radix system if  $b_i$ = $m_i$  for  $i \in \{1, 2, 1, L\}$ . As an example the integer X, can be represented using residue arithmetic and mixed radix notation as:

$$X = (x_1, x_2, x_3, ..., x_L)$$

$$X = (a_1, a_2, a_3, ..., a_L)$$

(2.9)

$$X = (a_1, a_2, a_3, ..., a_L)$$

(2.10)

It is a simple task to map the integer X into a more conventional fixed radix number system such as decimal using the mixed radix digits, a<sub>i</sub>, as given below:

$$X = a_L (m_{L-1}, m_{L-2}, m_{2-3}, ..., m_1) + ... + a_3 (m_2, m_1) + a_2 m_1 + a_1$$

(2.11)

or in its compact form [Sca'86]:

$$X = \prod_{k=1}^{L} a_k \sum_{i=1}^{k-1} m_i$$

(2.12)

It is preferable to decode an RNS number to binary in two levels, first from RNS to its associated mixed-radix form; once the mixed radix digits are computed it is a straightforward matter to convert it to the binary form. The large modulo M adder is removed in this approach; however, a large binary adder is still needed. Another widely used operation in RNS is extension of the base, which will be reviewed next.

#### 2.4.2.3. Extension of Base

In residue arithmetic, it is frequently necessary to find the residue digit  $x_L$  when a new modulus  $m_L$  is appended to the existing set. The problem, therefore, is to find the residue digits for a new set of moduli, given the residue digits relative to another set of moduli [Sza'67]. This is best performed by a mixed-radix conversion followed by an extra step as follows.

Assume an associated mixed-radix form for the extended RNS as

$$X = a_{L+1} \prod_{i=0}^{L} m_i + a_L \prod_{i=0}^{L-1} m_i + ... + a_3 m_1 m_2 + a_2 m_1 + a_1$$

(2.13)

at the final step of computing mixed-radix digits, the fact that  $a_{L+1}=0$  is used to form an equation. The unknown residue digit is the solution of this equation. For example consider a residue system with 3 moduli,  $m_1$ ,  $m_2$ , and  $m_3$  with the dynamic range  $M=m_1$   $m_2$   $m_3$ . Assume an expansion of the base for  $m_4$  is required. An integer X in this associated mixed radix system can be represented as:

$$X = a_4 (m_1 m_2 m_3) + a_3 (m_1 m_2) + a_2 m_1 + a_1$$

(2.14)

where  $a_i < m_i$  and a larger dynamic range of M' =  $m_1 m_2 m_3 m_4$ . Hence we must have  $a_4 = 0$  in order to satisfy X<M.

#### 2.5. Summary

This chapter has presented a review of some of the fundamental concepts of discrete mathematics. Algebraic structures of groups, rings, and fields have been discussed along with some of their properties. Alternative approaches for constructing these structures were specified and isomorphisms of the groups and rings were also discussed. The fundamental issue in decomposing a large algebraic structure into several smaller structures was examined.

The basics of both standard and redundant residue number systems, were

outlined. The notation used throughout this dissertation for the ring and field operations was introduced.

## CHAPTER 3

## Finite Ring and Field Architectures,

## A Unified Approach

#### **Abstract**

This chapter presents a class of completely pipelined VLSI architectures. It is well suited to digital signal processing applications based on finite rings and fields. These architectures are based on using regular interconnections of a number of simple basic "cells" to perform complex functions at a very high throughput rates.

The technique evolves from the decomposition of each closed calculation using the ring/field associativity property. The cells are perfectly matched to the VLSI medium. Linear systolic arrays, composed of a number of cells, each of a single generic form, are used to carry out the required computations. Examples of different operations are given to illustrate the technique.

#### 3.1. Introduction

The concept of systolic array design, introduced by H.T. Kung and C.E.

Leiserson [Kun'78], is the result of advances in semiconductor technology and of applications that require high throughput. The term "array" originates in the systolic array's resemblance to a grid in which each point corresponds to a processor and a line corresponds to a link between the processors.

Systolic arrays derive their efficiency from:

Pipelining execution of the operations belonging to different instances of the algorithm simultaneously.

Regularity use of regular interconnection topology between the cells.

Homogeneity implementing the algorithm with the use of a few types of identical building blocks.

Algorithms suitable for implementing in systolic arrays have been found in many applications, such as digital signal and image processing, linear algebra and non-numeric applications. These applications are computationaly intensive and require high throughput for their implementations when used in real-time environments.

Many applications and suitable algorithms have been discussed and implemented in the past few years. Often the algorithms can been described by recurrence equations where the required computation is defined recursively using a few simple operations.

Many specialized systolic arrays can be regarded as hardware implementations

of a given algorithm with the basic operation performed in each cycle by the processing elements, ranging from a simple bit level operation [Mca'82], to word level multiplication and addition, and even to execution of a complete program.

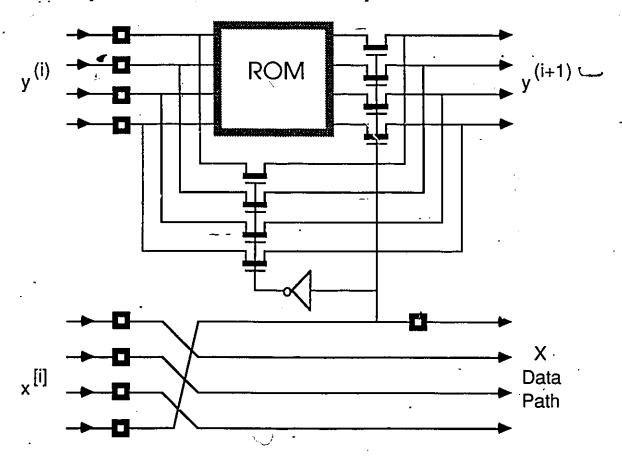

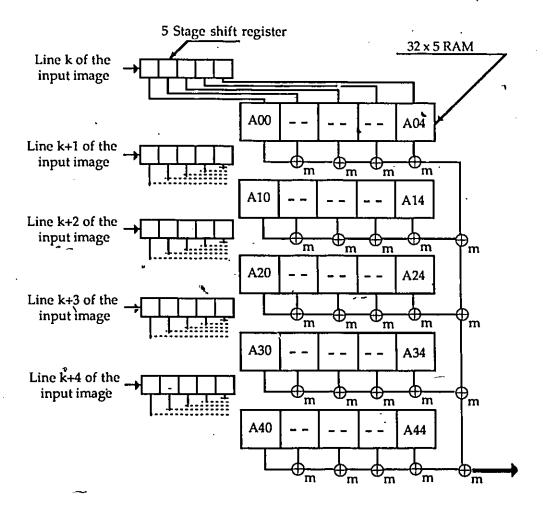

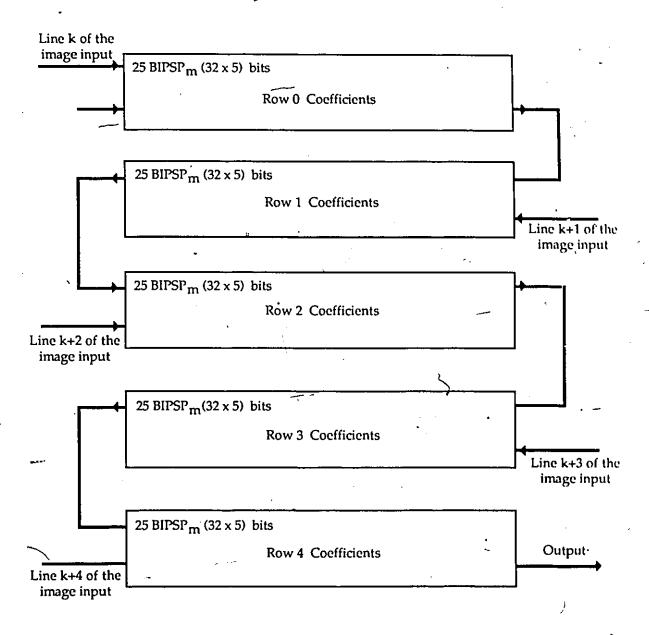

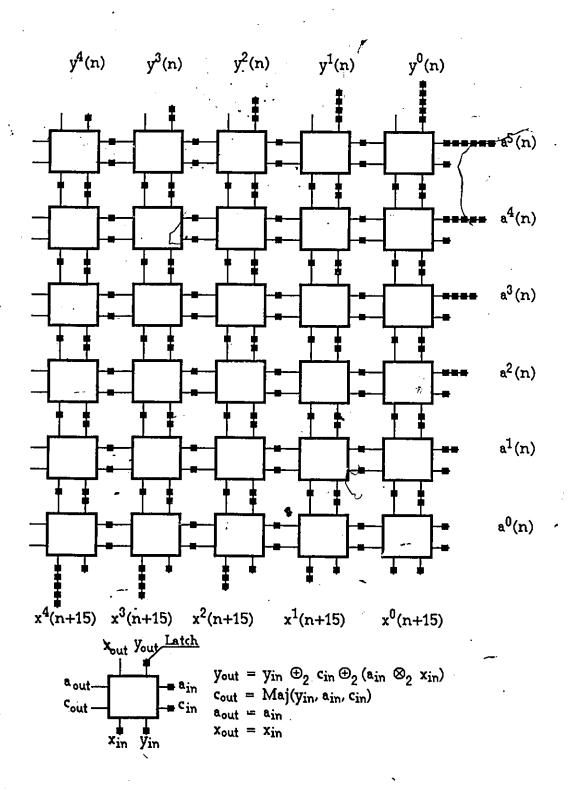

With the advent of VLSI, the case of architectures based on computations over finite rings and fields is an unexplored situation. The major issue is the question of what the offerings of VLSI are in this case. To answer this question, two main approaches can be taken; the first is to take the existing designs and simply map them into the new medium, [Tay'82]. Simple mappings obviously may not lead to an efficient usage of the new technology. The second approach is to look for styles and techniques which make best use of the advantages and avoid the limitations of the technology, as much as possible.