# University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

2001

# Inner product computational architectures using the double base number system.

Stanley Jonathan. Eskritt *University of Windsor*

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### Recommended Citation

Eskritt, Stanley Jonathan., "Inner product computational architectures using the double base number system." (2001). *Electronic Theses and Dissertations*. Paper 2453.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# "Inner Product Computational Architectures Using the Double Base Number System"

by

### "Stanley Jonathan Eskritt"

#### A Thesis

Submitted to the Faculty of Graduate Studies and Research through the Department of Electrical and Computer Engineering in partial fulfillment of the requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada 2001

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-62212-6

#### © 2001 "Stanley Jonathan Eskritt"

All Rights Reserved. No part of this document may be reproduced, stored or otherwise retained in a retrieval system or transmitted in any form, on any medium or by any means without the prior written permission of the author.

# **List of Symbols**

| m   | mantissa                                    |

|-----|---------------------------------------------|

| r   | base or radix                               |

| SNR | Signal to Noise Ratio                       |

| Φ   | Look-up table operator for DBNS addition    |

| Ψ   | Look-up table operator for DBNS subtraction |

| t   | DBNS ternary exponent                       |

| b   | DBNS binary exponent                        |

# **List of Abbreviations**

ALU Arithmetic Logic Unit

CMOS Complementary Metal-Oxide Semiconductor

CNN Cellular Neural Network

dB Decibels

DBNS Double Base Number System

DFT Discrete Fourier Transform

DSP Digital Signal Processing

FIR Finite Impulse Response

HDL Hardware Description Language

IC Integrated Circuit

IIR Infinite Impulse Response

LNS Logarithmic Number System

MAC Multiply ACcumulate

MOSFET Metal-Oxide Semiconductor Field Effect Transistor

PE Processing Elements

ROM Read Only Memory

RAM Random Access Memory

SFG Signal Flow Graph

SNR Signal to Noise Ratio

VLSI Very Large Scale Integration

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuits

# Acknowledgments

There are several people who deserve my sincere thanks for their generous contributions to this project.

I would first like to thank my supervisor Dr. G. A. Jullien for his guidance, advice and for bringing this challenging project to my attention. I am grateful to Gennum Corp. for providing funding. I would also like to thank my committee members Dr. Vassil Dimitrov, Dr. Alioune Ngom.

I would also like to recognize the following individuals and corporations for their contributions: Paul Horbal for his time and comments on the first drafts of this thesis. CMC for providing and supporting the design software and computing hardware which made this project possible. Micronet R&D for providing financial and networking support. Roberto Muscedere for his aid with HDLs, Cadence tools and helping in producing the hybrid DBNS microchip.

# **Abstract**

Digital signal processing (DSP) permeates many of the products we see around us today. DSP systems manipulate signals as sequences of numbers, and require massive arithmetic computations to perform algorithmic processing such as filtering. Traditionally these systems are designed using the binary number system to perform the computations. This thesis presents an exploration into the construction of finite impulse response (FIR) filters using a recently introduced number system. The number system uses two orthogonal bases and has been referred to in literature as the Double-Base Number System (DBNS). We use an index calculus implementation of the DBNS to take advantage of the logarithmic-like properties of the associated arithmetic.

Using the index calculus form of the Double Base Number System (DBNS), instead of the classical binary representation, a number of advantages are gained. The logarithmic-like properties of the index calculus DBNS allow for reduced complexity multiplication and division, expensive operations using binary arithmetic; the orthogonal nature of the index computations and the multi-digit extensions of the representation reduce the complexity of computations compare to the Logarithmic Number System. Finally, the non-linear nature of the representation allows for a natural mapping for some special systems, such as hearing devices, that require non-linear compression operations.

This thesis investigates a recently disclosed architecture for inner product computations in the DBNS. This architecture is expanded from the initial single-digit DBNS form to a hybrid (mix of 1-digit and 2-digit forms) and finally a full 2-digit form, and we show the efficiencies obtained in using the full 2-digit form. We target the implementation of large tap length Finite Impulse Response (FIR) filters, and we examine both the problem of finite precision index coefficient design and the design and fabrication of a systolic

# **Abstract**

architecture using DBNS processors. In particular we introduce a mapping scheme that allows the output of full-precision filter design packages to be easily converted to finite precision DBNS indices with close to optimum results, and we fabricate and successfully test a 15-tap filter design using a  $0.35\mu$  CMOS process. We finally examine the use of asymmetrical dynamic ranges on the 2 orthogonal indices in order to reduce the area and power of the filter architecture with minimal reduction in precision.

# **Publications and Presentations**

The following refereed conference publications and invited talks were generated from the work presented in this thesis.

- [1] V.S.Dimitrov, J.Eskritt, L.Imbert, G.A.Jullien and W.C.Miller. "The use of the multidimensional logarithmic number system in DSP applications." 15<sup>th</sup> IEEE Symposium on Computer Arithmetic, Vail, Colorado, June 2001. Accepted for presentation.

- [2] J. Eskritt, "2-digit, 2-Dimensional Logarithms for Efficient FIR Filter Architectures", invited presentation at the Micronet Annual Workshop, April 2001 (accepted for presentation).

- [3] J. Eskritt, "Hybrid and 2-digit DBNS Filter Architectures", invited presentation, Gennum Corporation, February 2001.

- [4] J. Eskritt, "Inner Product Computional Architectures Using the Double Base Number System", VLSI Research Group, University of Windsor, December 2000.

- [5] J. Eskritt, R. Muscedere, G.A. Jullien, V.S. Dimitrov and W.C. Miller. "A 2-Digit DBNS Filter Architecture." Proceedings of the 2000 IEEE Workshop on Signal Processing Systems (SiPS 2000), Lafayette, LA, October. Pages 447-456.

- [6] J. Eskritt, "Inner Product DBNS Computation", VLSI Research Group, University of Windsor, September 2000.

- [7] J. Eskritt, "DBNS Research for the Micronet Project S. I. WII", invited presentation, Gennum Corporation, March 2000.

# **Table of Contents**

| Chapter | 1   | Introduction                            | 1  |

|---------|-----|-----------------------------------------|----|

|         | 1.1 | Introduction                            |    |

|         | 1.2 | VLSI Technology                         | 3  |

|         | 1.3 | Double Base Number System               | 5  |

|         | 1.4 | Thesis Objectives                       | 6  |

|         | 1.5 | Thesis Organization                     | 6  |

| Chapter | 2   | The Double Base Number System           | 8  |

|         | 2.1 | Introduction                            | 8  |

|         | 2.2 | Representation                          | 8  |

|         | 2.3 | Index Calculus                          | 13 |

|         |     | 2.3.1 Multiplication and Division       | 13 |

|         |     | 2.3.2 Addition and Subtraction          | 14 |

|         |     | 2.3.3 Multi-digit DBNS Arithmetic       | 16 |

|         | 2.4 | Asymmetric Exponents                    | 16 |

|         | 2.5 | Logarithmic Number System               | 18 |

|         | 2.6 | Different Odd Bases                     | 20 |

|         | 2.7 | Conversion Between Binary and DBNS      | 21 |

|         |     | 2.7.1 Binary to DBNS Conversion         | 22 |

|         |     | 2.7.2 DBNS to Binary conversion [9]     | 22 |

|         | 2.8 | Summary                                 | 23 |

| Chapter | 3   | DBNS Finite Precision FIR Filter Design | 24 |

|         | 3.1 | Introduction                            | 24 |

|         | 3.2 | Coefficient Design Techniques           | 24 |

|         |     | 3.2.1 Genetic Algorithms                | 25 |

|         |     | 3.2.2 Integer Programming               |    |

|            | 3.2.3 Direct mapping                 | 29 |

|------------|--------------------------------------|----|

| 3.3        | Summary                              |    |

|            | -                                    |    |

| Chapter 4  | DBNS FIR Filter Architectures        | 38 |

| 4.1        | Introduction                         | 38 |

| 4.2        | Systolic Arrays                      | 38 |

|            | 4.2.1 Pipelining                     | 40 |

| 4.3        | Basic Processing Element             | 41 |

| 4.4        | Hybrid 2 digit DBNS Architecture     | 43 |

| 4.5        | 2 Digit DBNS Architecture            | 44 |

|            | 4.5.1 Two Digit Channel Reduction    | 46 |

| 4.6        | Comparison to Binary                 | 50 |

| 4.7        | Summary                              | 52 |

| Chapter 5  | A DBNS FIR Filter Case Study         | 53 |

| 5.1        | Introduction                         | 53 |

| 5.2        | Verilog Simulation                   |    |

| 5.3        | VHDL Synthesis                       |    |

| 5.5        | 5.3.1 Placement and Routing          |    |

| 5.4        | Final Chip Assembly                  |    |

| 5.5        | Testing the Chip                     |    |

| 5.6        | Comparison to 2 digit DBNS           |    |

| 5.7        | Summary                              |    |

| Chapter 6  | Conclusions and Future Work          | 66 |

| Chapter 0  | Conclusions and Future Work          |    |

| 6.1        | Conclusions                          | 66 |

| 6.2        | Contributions                        | 67 |

| 6.3        | Suggestions for Future Work          | 67 |

| REFERENCE: | S                                    | 69 |

|            |                                      |    |

| Appendix A | VHDL Code for Hybrid DBNS FIR Filter | 71 |

| A.1        | Introduction                         | 71 |

| A.2        | Binary to DBNS Coversion Stage       |    |

| A.3        | DBNS MAC Cell                        |    |

| Appendix | В   | VHDL Code for 2 Digit DBNS FIR Filter      | 85  |

|----------|-----|--------------------------------------------|-----|

|          | B.1 | Introduction                               | 85  |

|          | B.2 | MAC Cell                                   |     |

| Appendix | C   | C Code for Mapping into DBNS               | 89  |

|          | C.1 | Introduction                               | 89  |

|          | C.2 |                                            |     |

|          | C.3 |                                            |     |

| Appendix | D   | Genetic Algorithm Code                     | 102 |

|          | D.I | DBNS Coefficient Generation                | 102 |

| Appendix | E   | A Brief Tutorial in High Level Chip Design | 113 |

|          | E.1 | Introduction                               | 113 |

|          | E.2 | System Design                              | 113 |

|          | E.3 | Synthesizing the System                    | 115 |

# **List of Figures**

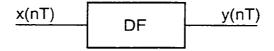

| Figure 1.1  | Block diagram of a digital filter                                      | 2  |

|-------------|------------------------------------------------------------------------|----|

| Figure 2.1  | A 2D DBNS Representation of 79                                         | 10 |

| Figure 2.2  | A 2D DBNS Representation of 7.25                                       | 11 |

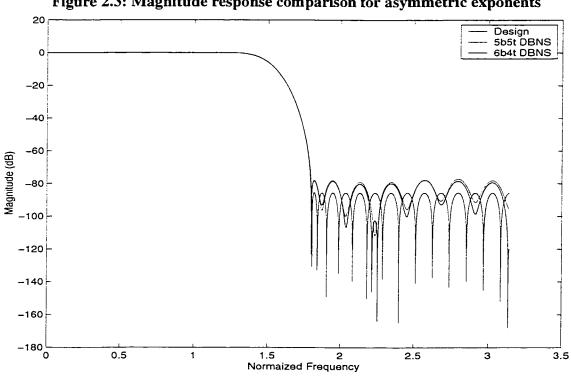

| Figure 2.3  | Magnitude response comparison for asymmetric exponents                 | 17 |

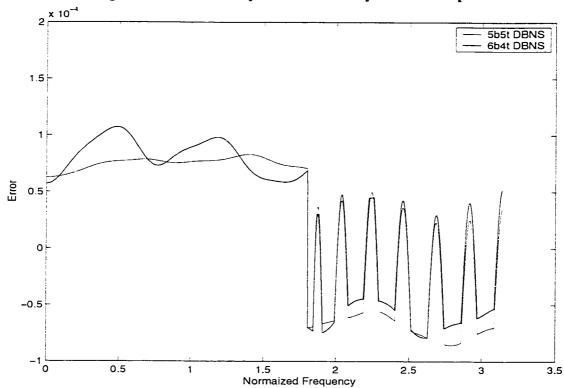

| Figure 2.4  | Error for symmetric and asymmetric responses                           | 18 |

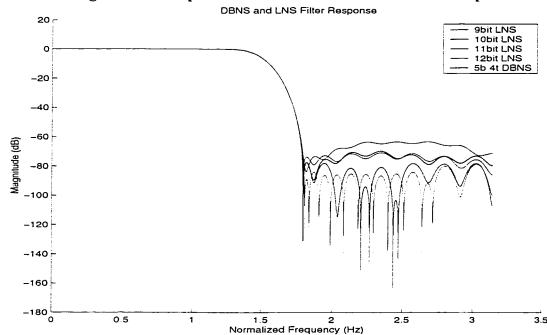

| Figure 2.5  | Comparison between LNS and DBNS filter responses                       |    |

| Figure 2.6  | Magnitude response of DBNS filters with different odd bases            | 21 |

| Figure 3.1  | Crossover                                                              | 26 |

| Figure 3.2  | Frequency response of a genetic algorithm produced DBNS FIR filter.    | 28 |

| Figure 3.3  | Result curve due to optimization                                       | 29 |

| Figure 3.4  | A histogram showing the coefficient values for over 200 filters        | 30 |

| Figure 3.5  | Filter response of a floating point coefficient filter                 | 32 |

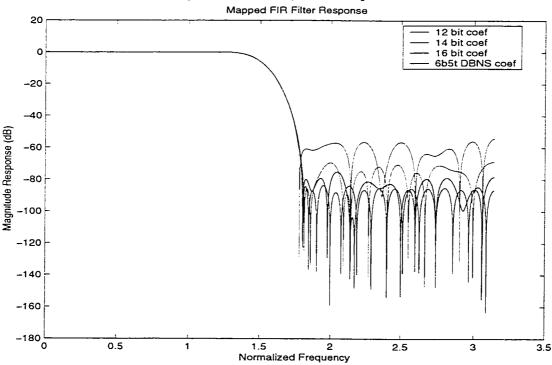

| Figure 3.6  | Magnitude response for the mapped filters                              | 34 |

| Figure 3.7  | Mapped filters' error                                                  | 34 |

| Figure 3.8  | Error of mapped DBNS responses                                         | 35 |

| Figure 3.9  | Error between designed response and binary and DBNS mappings           | 36 |

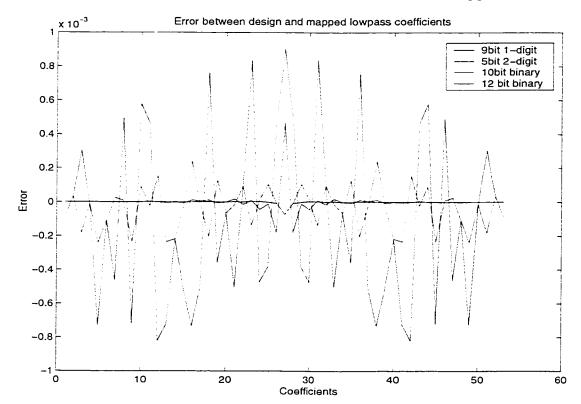

| Figure 3.10 | Error between designed coefficient values and mapped coefficients      | 37 |

| Figure 4.1  | A unidirectional systolic array convolver and processing element       | 39 |

| Figure 4.2  | A DBNS Multiply Accumulate Cell                                        | 42 |

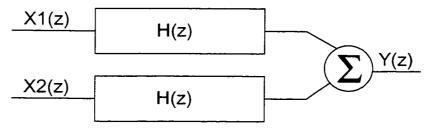

| Figure 4.3  | Hybrid 2 digit DBNS Architecture                                       | 44 |

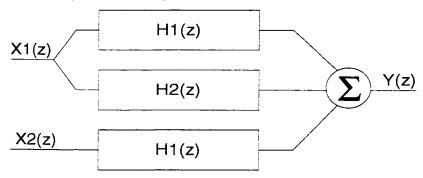

| Figure 4.4  | Four channel filter architecture for 2 digit DBNS                      | 45 |

| Figure 4.5  | 2 digit reduced channel architecture                                   | 48 |

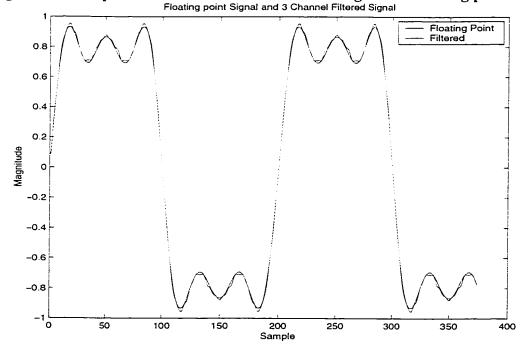

| Figure 4.6  | Comparison between 3 channel filtered signal and floating point signal | 48 |

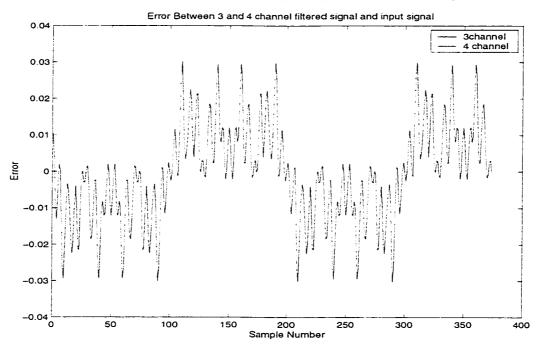

| Figure 4.7  | Error between input signal and filtered signals                        | 49 |

| Figure 4.8  | Binary filter responses.                                               | 50 |

| Figure 4.9  | Binary multiplier cell (660x925mm)                                     | 51 |

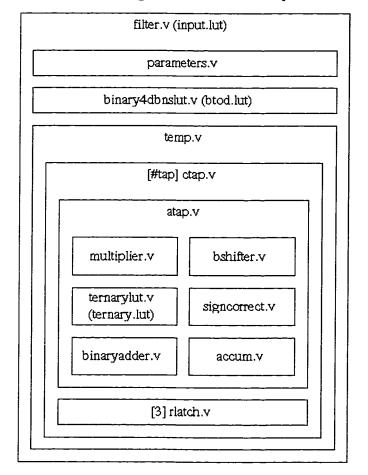

| Figure 5.1  | Hierarchal diagram for HDL description of a DBNS filter                | 54 |

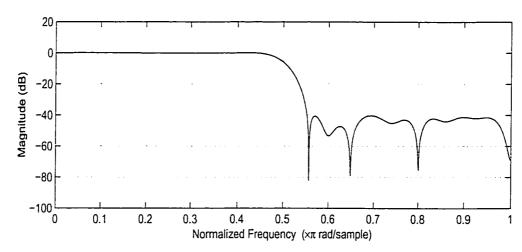

| Figure 5.2  | Magnitude response of genetic algorithm designed DBNS FIR filter       | 55 |

|             |                                                                        |    |

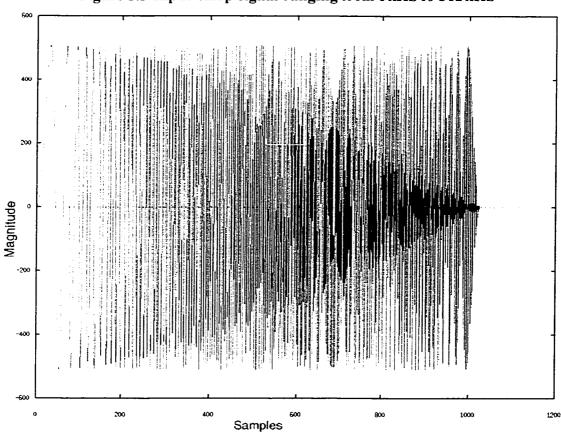

| Figure 5.3 | Input chirp signal ranging from 1kHz to 512kHz                                                 | 56 |

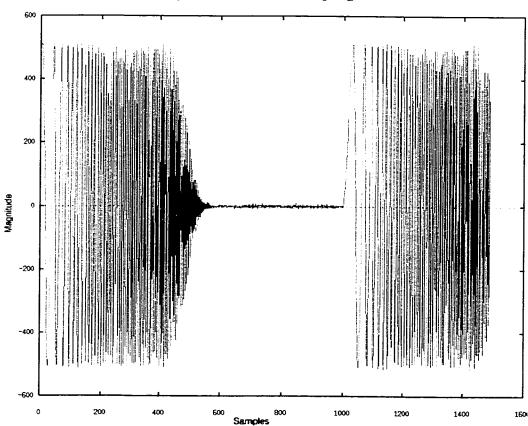

|------------|------------------------------------------------------------------------------------------------|----|

| Figure 5.4 | Filtered chirp signal                                                                          | 57 |

| Figure 5.5 | Input Stage, Binary to DBNS Conversion ROM (2969x666mm)                                        | 60 |

| Figure 5.6 | DBNS MAC cell (3526x857 mm)                                                                    | 60 |

| Figure 5.7 | Output Stage, Accumulator for both Filter Channels (328x113 mm)                                | 60 |

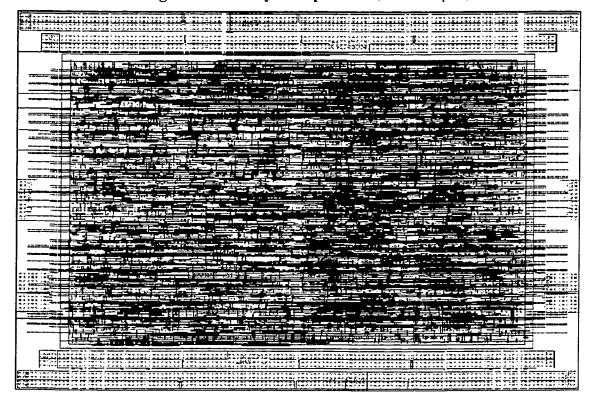

| Figure 5.8 | Final Chip Layout (16x9 mm)                                                                    | 62 |

| Figure 5.9 | 15 tap, hybrid DBNS FIR filter (left) and a 53 tap, reduced channel, 2 DBNS FIR filter (right) | _  |

# **List of Tables**

| Table 2.1 | Stopband Attenuation (in Decibels) for Mapped DBNS Filter Coefficients |    |  |

|-----------|------------------------------------------------------------------------|----|--|

|           | with Varying Bases                                                     | 21 |  |

| Table 3.1 | Mapped Filter Specifications                                           | 33 |  |

| Table 4.1 | Unidirectional systolic convolver results                              | 40 |  |

| Table 4.2 | 53DBNS bandpass FIR filter coefficients                                | 47 |  |

| Table 4.3 | Area comparison between binary and DBNS filter taps                    | 52 |  |

# Chapter 1

### Introduction

### 1.1 Introduction

Digital signal processing (DSP) increasingly permeates our lives. Almost every field of science and engineering relies on processing signals. Signals can be received and analyzed through test equipment or generated through simulation hardware. Signals are responsible for allowing us to communicate over large distances and for entertaining us through radio and television. DSP comes into play when these signals are discrete. Discrete signals are signals that exist only at specified points in time and can only assume a finite number of values [16]. DSP is used in many areas, such as digital filtering, image processing and even computer systems.

The representation of signals as discrete is not a large constraint, as non-discrete bandlimited signals are easily made discrete. Non-discrete signals, called continuous signals, exist at every point in a specified time or space. For example, the speed of a car or a person talking into a telephone. These signals can be quantized and converted into digital signals. To quantize a signal, it is measured at specific time intervals and the value is recorded to within a certain numerical precision.

A fundamental operation in DSP is filtering. By filtering a signal, unwanted portions of the signal spectrum can be removed or the signal can be modified and reshaped. For example, filtering is used to provide the selected channels for display on a television or for selecting stations on a radio. A basic block diagram of a digital filter is shown in Figure 1.1, where x(nT) is the discrete input and y(nT) is the discrete response of the filter.

Figure 1.1: Block diagram of a digital filter

This can be represented mathematically as:

$$y(nT)) = \Re[x(nT)] \tag{1.1}$$

where  $\Re$  is an operator representing the transfer function of the filter. Furthermore, filters are classified by whether or not they are time-invariant, linear or causal [16].

- <u>Definition 1.1</u> Time-invariance A filter is time-invariant if the filter's response to a given input signal does not depend on the time the input signal is applied.

- **Definition 1.2** Linearity A filter is considered linear if it can satisfy the following two conditions.

$$\Re[\alpha x(nT)] = \alpha \Re[x(nT)] \tag{1.2}$$

$$\Re[x_1(nT) + x_2(nT)] = \Re[x_1(nT)] + \Re[x_2(nT)]$$

(1.3)

**Definition 1.3** Causality – A filter is said to be causal if the response of the filter, at a given moment, does not depend on any future value of the input.

One of the most basic structures used in DSP is the Finite Impulse Response (FIR) filter, or nonrecursive filter. A FIR filter is a filter that does not depend on any past output values

Introduction Introduction 2

of the filter. If it is assumed that the FIR filter is linear, time-invariant and causal, then the response of the filter, y(nT), can be expressed as a difference equation.

$$y(nT) = \sum_{i=0}^{N} a_i x(nT - iT)$$

(1.4)

where  $a_i$  represents constants, and N is the order of the filter. A benefit of using nonrecursive filters is that they are guaranteed to be linear and have a linear phase response.

Another type of filter is the Infinite Impulse Response (IIR) filter or recursive filter. An IIR filter uses past outputs to influence the current response of the filter. Recursive filters usually require a much lower order of filter to produce the same magnitude response of a FIR filter, but IIR filters are not guaranteed to be stable or have linear phase. The output response, y(nT), of a recursive filter can be described by the difference equation:

$$y(nT) = \sum_{i=0}^{N} a_i x(nT - iT) - \sum_{i=1}^{M} b_i y(bT - iT)$$

(1.5)

where  $a_i$  and  $b_i$  represent constants. Therefore, at any given moment, the response of the filter is dependent on the past N values of the input and the past M values of the output.

For applications that require a linear phase response, such as video and audio applications, FIR filters are typically used. This is due to the guarantee of linear phase response, ease of design and stability.

### 1.2 VLSI Technology

VLSI (Very Large Scale Integration) technology has changed the lives of almost everyone in the world today. It is the technology that produces high density microchips. Incredibly sophisticated systems can be built on a piece of silicon the size of a fingernail. These

Introduction VLSI Technology 3

microchips exist in almost every device or product we buy, from computers, stereos and cellular phones to children's toys and household appliances.

VLSI was first introduced in 1977 to describe commercial products being sold at that time. It was used to describe any integrated circuit of greater than 2000 logic blocks [29]. Today's microchips consist of considerably more logic blocks than 2000. In the past 20 years the transistors used to form VLSI circuits have increase in switching speeds by over 20 times, while decreasing the area used by the transistor to less than 1% [28].

The transistor was invented in 1947. This transistor was a bipolar transistor. Bipolar transistors were a great advance to electronic circuits that previously used vacuum tubes. and circuits were reduced to a fraction of their previous size and power requirements. It took eleven years (1958) before the first integrated circuit was made, this further reduced the size and power requirements of electronic circuits. In 1960, the first MOSFET transistors (both p-channel and n-channel) were invented. The MOSFET transistors were easier to manufacture, and had better packing densities than the bipolar transistors, but the MOSFETs had slower switching speeds. In 1963, Complementary Metal-Oxide Semiconductor (CMOS) circuits were invented. CMOS offered the ease of manufacture and packing densities of MOSFET transistors, but had the added benefit of negligible standby power dissipation. The only time power is consumed is when a circuit is switched. This offered a tremendous advantage over bipolar transistors which dissipated a lot of power. Bipolar transistors are still in use today, in circuits that require the raw circuit speed of bipolar transistors, but are typically used in small stand alone bipolar chips, or in a BiCMOS process that uses CMOS for the majority of the circuits and only a small number of bipolar circuits [28].

Microchips are produced by forming multiple specialized layers. CMOS transistors are formed by diffusing gaseous boron and phosphorous into a wafer of single crystal silicon and using polycrystalline silicon as the gate electrode. Connections are made by layers of metal traces that are insulated from each other. These traces are usually made of aluminum. Current processes have up to seven layers of metal available. The more layers

Introduction VLSI Technology 4

of metal available to the process, the more densely packed the system can be, allowing for larger systems to be produced in the same area.

The current trend in VLSI design is to produce high quality libraries of basic cells, logic gates and basic operations (adders, counters, multiplexers, etc.) and design the system using a hardware description language (HDL). HDLs allow a system to be designed using a technology independent, high level, programming-like language. Once the system is fully described in an HDL, it can be compiled from components of the libraries and fabricated. This process leads to more modular designs and greatly speeds up the design and testing time of a chip, at the expense of not being optimally designed.

## 1.3 Double Base Number System

In the area of digital signal processing considerable demand exists for compact, high speed/real time digital filters for use in applications such as radar image processing. However, available real-time digital filters are often too slow, too costly, too complex or require too much power. To correct for this, the attention of some researchers has been directed to different techniques for designing high speed digital filters making use of special coding schemes or number systems. Traditional algorithms used in digital signal processing do not "parallelize" nor "modularize" easily, hence not allowing the maximum use of the VLSI technology. It becomes clear that different design approaches are needed that can incorporate modularity and parallelism. One such approach is a multi-digit Double Base Number System (DBNS), whose arithmetic is broken up into independent sub-terms, providing a modular hardware implementation.

The DBNS is a recently developed number system [8], though it does have some relation to the Logarithmic Number System (LNS), and can be viewed as a multi-dimensional form of the LNS [10]. DBNS offers a highly redundant number system with a very sparse representation, through the used of two orthogonal bases.

A large number of DSP functions, such as FIR filtering and Discrete Fourier Transform (DFT), require the use of inner product computations. Inner product computations are based on multiply-accumulate (MAC) operations. Therefore, specialized DSP hardware, such as FIR filter microchips, heavily rely on optimized MAC operations. Through the use of DBNS, a MAC architecture can be built without the need of binary multipliers, thus reducing the overhead of MAC dependent systems such as filters. DBNS also has a non-linear number representation that can be advantageous in some systems.

# 1.4 Thesis Objectives

There are two main thrusts of the work presented in this thesis. The first is to investigate and expand upon architectures for use with DBNS and FIR filters and, using these architectures, make a comparison to equivalent binary architectures. The second thrust is to provide proof of concept by producing a working microchip using the VHSIC Hardware Description Language (VHDL). Also investigated is the mapping of floating point numbers into the DBNS representation.

## 1.5 Thesis Organization

This thesis is organized into six chapters and four appendices. The first chapter (this chapter) is an introduction. Chapter 2 covers the Double Base Number System, and the arithmetic associated with it. The second chapter also makes a comparison between the DBNS and the LNS number systems. Chapter 3 presents the methods used to generate the coefficients for the DBNS filters. Chapter 4 looks at the architectures used in producing a FIR filter that uses DBNS for filter coefficients and data. Chapter 5 provides verification of the DBNS architectures through the production of a working microchip of a 15-tap, hybrid DBNS, FIR filter, designed using VHDL. Finally, Chapter 6 presents conclusions and future work for this thesis.

The appendices include additional information that did not fit neatly into the thesis body. Appendix A and Appendix B contain the VHDL code used to produce the hybrid and two digit DBNS microchip described in Chapter 5. Appendix C contains the code for the decimal to DBNS mapping of data and coefficients. Appendix D contains the code for the genetic algorithm used for generating DBNS FIR filter coefficients. Finally, Appendix E provides a brief introduction to high level microchip design, and points the reader to more complete tutorials and information.

Introduction Thesis Organization 7

# Chapter 2

# The Double Base Number System

### 2.1 Introduction

The Double Base Number System (DBNS) is a recently introduced [8], highly redundant number system with a very sparse representation. The DBNS has a number of properties that can be advantageous to DSP applications, such as the possible overhead reduction for a DSP system heavily reliant on multiplications. Also the DBNS, in an index calculus form, has a non-linear number representation that may benefit certain specialized applications, such as those requiring accurate representation of both large and small signals. Recently, the index calculus Double Base Number System has been compared to the Logarithmic Number System, as a multi-dimensional form of that number system [10].

### 2.2 Representation

The DBNS representation of a number differs slightly from the traditional fixed radix form of representation. Typically a number is represented in the form:

$$x = \sum_{i=0}^{N} m_i r^i \tag{2.1}$$

where  $m \in \{0, 1, ..., r-1\}$ , *i* is an integer and r is the radix. For example in the decimal system r=10, and in the binary system r=2.

The DBNS representation varies from this by replacing the radix, r, with two orthogonal bases, restricting the range of the mantissa, m, to represent the sign. The equation for DBNS number representation is:

$$x = \sum_{i=0}^{N} m_i 2^{b_i} 3^{t_i} \tag{2.2}$$

where  $b_i$ ,  $t_i$  and i are integers. Since m is signed, both positive and negative numbers are representable. The mantissa, or sign component, must also sometimes equal zero. This is required because a DBNS digit, using the exponential representation  $2^{b_i} \cdot 3^{t_i}$ , cannot express a value of zero.

Equation (2.2) shows the binary number system to be a subset of the DBNS if  $t_i$ =0 for all i. Equation (2.2) also leads to a very simple two dimensional representation [15].

$\begin{bmatrix}

2^0 & 2^1 & 2^2 & 2^3 & 2^4 \\

3^0 & & & & & \\

3^1 & & & & & \\

3^2 & & & & & \\

3^3 & & & & & & \\

3^3 & & & & & & \\

3^1 & & & & & & \\

3^2 & & & & & & \\

3^3 & & & & & & \\

3^3 & & & & & & \\

3^1 & & & & & & \\

3^2 & & & & & & \\

3^3 & & & & & & \\

3^4 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & & \\

3^5 & & & & & \\

3^5 & & & & & \\

3^5 & & & & & \\

3^5 & & & & & \\$

Figure 2.1: A 2D DBNS Representation of 79

Figure 2.1 shows one of the possible mappings of 79 into DBNS. The black squares represent the location of a DBNS digit. The digits used are  $2^03^0 + 2^13^1 + 2^33^2 = 1 + 6 + 72 = 79$ . The white squares represent the '0' digits and the black squares represent the digits that are '1'. From Figure 2.1 the very sparse representation of the DBNS number system can be seen.

If negative exponents are used, a much wider range of numbers are available and representation of real numbers, with arbitrary precision, is possible. Representation of integer numbers will require less digits if their representation allows for negative exponents. The two dimensional map of Figure 2.1 can still be used for negative exponents, but it will require a little expanding. Figure 2.2 shows the representation of the real number 7.25 using 2 DBNS digits  $2^{-2}3^3 + 2^{-1}3^0 = 6.75 + 0.5 = 7.25$ .

3<sup>3</sup> 3<sup>2</sup> 31 3<sup>0</sup> 3-2

Figure 2.2: A 2D DBNS Representation of 7.25

Only a small number of digits are required to represent a number. For example, the number 103 can represented, approximately, by the two DBNS digits  $2^{-24}3^{18} + 2^{19}3^{-8}$ and 2315 can be represented, exactly, by the two digits  $2^{0}3^{7} + 2^{7}3^{0}$ . Since the Double Base Number System is a redundant number system, most numbers will have more than one representation. For example 4.25 has 3 error free two digit DBNS representations, while 7.25 has a single unique, error free, two digit DBNS representation. It is provable [10] that every real number may have at most 91 error free, two digit DBNS representations, but realistically the majority will have at most 4 or 5 error free representations. This redundancy can be useful in allowing you to choose the best possible representation for your application.

The previous examples all used the form of  $\pm 2^{b_1}3^{t_1} \pm 2^{b_2}3^{t_2}$  to first display the DBNS numbers. This is a more convenient and informative way of writing DBNS numbers, as apposed to the two dimensional map representation. In this form the number is represented by the sign and the exponents (also called indices). The exponent on the base of 2 is called the binary exponent, and the exponent on the base of 3 is called the ternary exponent. If we

fix the binary and ternary exponents to a signed, fixed length representation, we can represent any real number to arbitrary precision.

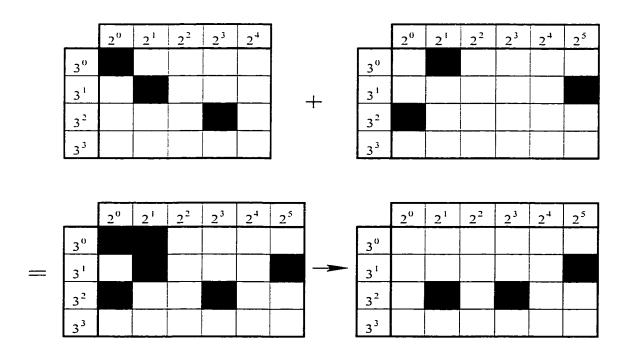

#### **DBNS Two Dimensional Map Arithmetic**

To add any two numbers using the DBNS two dimensional map representation (Figure 2.1 and Figure 2.2), simply overlap the two DBNS maps. Furthermore, a series of reductions of the DBNS map can be performed in order to reduce the number of resulting DBNS digits. These reductions can be summarized in three equations [15]:

$$2^{i}3^{j} + 2^{i+1}3^{j} = 2^{i}3^{j+1} (2.3)$$

$$2^{i}3^{j} + 2^{i}3^{j-1} = 2^{i-2}3^{j} (2.4)$$

$$2^{i}3^{j} + 2^{i}3^{j} = 2^{i-1}3^{j} (2.5)$$

Example 2.1The addition of the 2D mapped DBNS representations of 79 and 107

The result of this map arithmetic is  $2^{1}3^{2} + 2^{3}3^{2} + 2^{5}3^{1} = 18 + 72 + 96 = 186$ .

Little work is being done with the two dimensional DBNS map arithmetic as it is difficult to perform in hardware, though Cellular Neural Networks (CNN) have had some success [27]. CNNs are analog circuits that can perform digital computations and produce a digital output. There is currently no way to perform multiplication using the two dimension DBNS map.

#### 2.3 Index Calculus

Double base numbers are usually represented by their binary and ternary exponents, or indices. In order to perform mathematical operations with DBNS numbers using these exponents we need to define these operations. When performing these operations we will represent the DBNS numbers with the triple  $(s_x, b_x, t_x)$ , where  $s_x$  is the sign,  $b_x$  and  $t_x$  are integers, such that  $s_x 2^{b_x} 3^{t_x}$  is a DBNS representation of a number x. Performing mathematical operations using this representation of DBNS numbers is called index calculus, because the numbers are represented by their exponents, or indices.

### 2.3.1 Multiplication and Division

Multiplication and division are the simplest operations in index calculus DBNS, and offer very little overhead, or complexity. The equations for multiplication and division, given  $x=(s_x, b_x, t_x)$  and  $y=(s_x, b_y, t_y)$ , are [8]:

$$x \cdot y = ((s_x + s_y) \mod 2, b_x + b_y, t_x + t_y)$$

(2.6)

$$x/y = ((s_x + s_y) \mod 2, b_x - b_y, \dot{t}_x - t_y)$$

(2.7)

Equations (2.6) and (2.7) show that DBNS multiplication can be implemented in hardware using simple binary adders. This feature of DBNS can be used to reduce the overhead of a binary system that utilizes many multipliers by replacing them with a DBNS system, since

DBNS multipliers are two binary adders and simple logic for the sign correction. The binary adders should also require less time to evaluate than the corresponding binary multiplier.

#### 2.3.2 Addition and Subtraction

Unfortunately, as with logarithms, addition and subtraction operations are not as simple as multiplication and division operations. Addition and subtraction must be handled through a set of identities and look-up tables. The identities are [8][9]:

$$2^{a}3^{b} + 2^{c}3^{d} = 2^{a}3^{b}(1 + 2^{c-a}3^{d-b})$$

$$\approx 2^{a}3^{b}\Phi(c-a, d-b)$$

(2.8)

$$2^{a}3^{b} - 2^{c}3^{d} = 2^{a}3^{b}(1 - 2^{c-a}3^{d-b})$$

$$\approx 2^{a}3^{b}\Psi(c-a, d-b)$$

(2.9)

The operators  $\Phi$  and  $\Psi$  are lookup tables that must be precomputed and store the approximate values of:

$$\Phi(x, y) = 1 + 2^x 3^y \approx 2^\alpha 3^\beta$$

(2.10)

$$\Psi(x, y) = 1 - 2^x 3^y \approx 2^{\gamma} 3^{\delta}$$

(2.11)

The use of large look-up tables, implemented through the use of ROMs, for the evaluation of addition and subtraction operations is the traditional approach in systems such as the Logarithmic Number System [24][25]. This technique is only feasible for very small ranges of DBNS numbers. It is more practical to convert the DBNS numbers to binary and perform the addition and subtraction using binary representation (see Section 2.7.2).

In order to design efficient DBNS hardware, an algorithm should be designed to have all additions and subtractions operations either before or after the multiplication operations, so conversion to and from DBNS will only have to take place one time each. This is easily done in architectures such as FIR filters. The conversions from DBNS to binary will still

require a look-up table, but one that is much smaller than required for handling DBNS addition and subtraction. The look-up table is used to convert the ternary portion of the DBNS number into a binary representation. Therefore the size of the look-up table is dependent on the number of bits used to represent the ternary exponent.

#### Example 2.2The addition of the index representation of 72 and 48

$$2^{3}3^{2} + 2^{4}3^{1}$$

$$= 2^{3}3^{2} \cdot \Phi(4-3, 1-2)$$

$$= 2^{3}3^{2} \cdot 2^{-4}3^{3}$$

$$= 2^{3-4}3^{2-3}$$

$$= 2^{-1}3^{5}$$

$$= (121)_{10}$$

Note that the answer 121 is incorrect, it should be 120. However, this is a close approximation, when performing integer arithmetic. This also shows how unsuited DBNS is for index calculus addition, justifying a conversion to binary before addition.

#### Example 2.3The multiplication of the index representation of 72 and 48

$$2^{3}3^{2} \cdot 2^{4}3^{1}$$

$$= 2^{3-4}3^{2-1}$$

$$= 2^{7}3^{3}$$

$$= (3456)_{10}$$

Note how much easier multiplication is in index calculus DBNS than addition. The results are as accurate as the numbers being used. This is because a look-up table of approximate values is not required.

#### 2.3.3 Multi-digit DBNS Arithmetic

Multi-digit DBNS arithmetic is simply an extension of the single digit DBNS arithmetic, and is necessary when numbers are represented by more than one DBNS digit (see Equation (2.2)). When performing a computation using multi-digit DBNS each digit can be treated as an independent DBNS number and the operations handled separately. For example, if X and Y are 2 digit DBNS numbers such that  $X = x_1 + x_2$  and  $Y = y_1 + y_2$  then:

$$X \cdot Y = (x_1 + x_2)(y_1 + y_2) = x_1y_1 + x_1y_2 + x_2y_1 + x_2y_2$$

(2.12)

where  $x_i$  and  $y_i$  are single digit DBNS numbers.

#### Example 2.4 An example of 2 digit DBNS multiplication of 27 and 23

$$(2^{2}3^{2} - 2^{0}3^{2}) \cdot (2^{5}3^{0} - 2^{0}3^{2})$$

$$= 2^{2}3^{2} \cdot 2^{5}3^{0} - 2^{2}3^{2} \cdot 2^{0}3^{2} - 2^{0}3^{2} \cdot 2^{5}3^{0} + 2^{0}3^{2} \cdot 2^{0}3^{2}$$

$$= 2^{2-5}3^{2-0} - 2^{2-0}3^{2-2} - 2^{0-5}3^{2-0} + 2^{0-0}3^{2-2}$$

$$= 2^{7}3^{2} - 2^{2}3^{4} - 2^{5}3^{2} + 2^{0}3^{4}$$

$$= (1152)_{10} - (324)_{10} - (288)_{10} + (81)_{10}$$

$$= (621)_{10}$$

The independence of the arithmetic operations is very important, as it allows for parallel architectures. Furthermore, these parallel structures can be asynchronously clocked, reducing the power requirement of the circuit. This parallel architecture is not restricted solely to multi-digit DBNS, but extends to hybrid DBNS systems. A hybrid DBNS system is one that combines single digit and multi-digit DBNS.

### 2.4 Asymmetric Exponents

It is not necessary for the exponents or indices to be of the same number of bits. There are advantages to having asymmetric indices. As will be seen in Chapter 4, the area

complexity of a DBNS multiply accumulator is heavily based on the size of the ternary exponent, due the ternary binary conversion ROM necessary for addition, and binary exponent size has very little effect on the area of the cell. Therefore decreasing the ternary exponent is an important factor in minimizing the overall area. It is possible, to a limited extent, to decrease the ternary exponent and increase the binary exponent, while still maintaining similar accuracy in the number representation. Such asymmetric exponents can greatly decrease area while still maintaining high accuracy.

Figure 2.3 shows the magnitude responses of two DBNS mapped FIR filters. The lowpass filter chosen for the example is a typical interpolation filter used for audio and video applications. One filter was mapped into 5 bit exponents for both the binary and ternary exponents. The other filter was mapped into DBNS having 6 bit binary and 4 bit ternary exponents. Note that there is very little difference between these two filter responses. The error, from the designed response, can be seen in Figure 2.4.

Figure 2.3: Magnitude response comparison for asymmetric exponents

Figure 2.4: Error for symmetric and asymmetric responses

# 2.5 Logarithmic Number System

The Logarithmic Number System (LNS) is a more mature and documented number system than the DBNS. In the LNS a number, n, is represented by:

$$n = s_i 2^{a_i} \tag{2.13}$$

where  $a_i$  is an arbitrary real number. This representation is very similar to the DBNS number representation. In fact it could be said that DBNS is a multi-dimensional form of the logarithmic number system. Multi-dimensional forms of LNS (like DBNS) offer many advantages over the more traditional single dimensional LNS [10]:

- The area complexity in DBNS systems is based on the size of the ternary exponent. By using asymmetric exponents, the area can be decreased while maintaining accuracy.

- Multi-digit LNS does not offer substantial area complexity reduction. Multi-digit DBNS does offer substantial area complexity reduction.

- Linear data maps to the DBNS better and, more often, has error free representations. This is especially true when using multi-digit DBNS.

- The DBNS is a highly redundant number system, and the LNS is not. A redundant number system has multiple error free representations. While this redundancy is not exploited in the DBNS filters described here, it can be very useful. One "redundancy" that is useful for DBNS filters is the ability to accurately represent a floating point number with DBNS numbers containing widely varying exponents. This will be shown later with channel reduction.

- When performing mathematical operations on DBNS numbers whose exponent values are close to overflow, the numbers can be multiplied by an approximation of 1 to reduce the value of the exponents and prevent overflow.

- The DBNS architecture is extremely flexible in that it allows the odd base (the 2nd base) to be any convenient odd base in accordance with any special requirements. This base change will not affect the architecture, though the values in the look-up tables will have to be changed.

- The DBNS corresponds to a much smaller hardware representation as opposed to classical LNS

Some filter magnitude response comparisons have been made between LNS and DBNS (Figure 2.5). They show that it takes 12bit LNS to exceed the response of a 2 digit, 5bit binary, 4bit ternary, direct mapped DBNS filter, and that 11bit LNS does not have enough accuracy to match the DBNS response.

Figure 2.5: Comparison between LNS and DBNS filter responses

## 2.6 Different Odd Bases

Typically when using the DBNS the bases used are 2 and 3. The odd base is not restricted to 3, however, and any convenient odd base can be used. Switching the odd base can be done to fulfill a special requirement of the design. For example using a 10 bit exponent for an odd base of 35 has shown good characteristics in mapping hearing aid data. Switching to a new odd base does not introduce any major design changes. DBNS systems use the same hardware and architecture no matter the odd base. Only exponent sizes may change with a change of bases.

Overall, a base of 3 offers the best results for filter coefficients. Table 2.1 shows the stopband attenuation of DBNS filters using different odd bases. A filter was designed in Matlab using floating point coefficients, and mapped using a modified Greedy Algorithm (see Modified Greedy Mapping in Chapter 3) into DBNS coefficients. The DBNS coefficients are two digit DBNS, with 5bit binary and 4bit odd base exponents. Figure 2.6

shows a graph of the magnitude responses of the ideal, designed, filter and of the two digit DBNS filter response for the filters with an odd base of 3 and 47.

Table 2.1: Stopband Attenuation (in Decibels) for Mapped DBNS Filter Coefficients with Varying Bases

| Base          | Ideal | 3  | 5  | 7    | 11   | 47   |

|---------------|-------|----|----|------|------|------|

| Stopband (dB) | 85.5  | 78 | 70 | 64.5 | 71.3 | 63.3 |

Mapped Multiple Base FIR Filter Response 2digit DBNS base2,3 2digit DBNS base2,47 -20 -40 -60 -80 -100 -120 -140 -160 -180 L 0.5 1.5 2.5 3 Normalized Frequency

Figure 2.6: Magnitude response of DBNS filters with different odd bases

#### **Conversion Between Binary and DBNS** 2.7

The majority of systems today rely on the use of the binary number system. In order for any system utilizing the Double Base Number System to be compatible with existing systems, conversions to and from binary will be required.

#### 2.7.1 Binary to DBNS Conversion

There are two methods that can be used to convert from binary representation to DBNS representation. The first method is the most straightforward method. It relies on a ROM to convert a binary input into DBNS exponents and signs. While the ROM look-up table is very easy to produce, the size of the ROM can become overwhelmingly large if the number of bits in the binary representation becomes too high.

The second method of binary to DBNS conversion is the use of a binary to DBNS converter system. This system converts binary numbers into DBNS numbers based on the repetitive patterns in the DBNS number system [26]. This process relies on a number of very small look-up tables and can take many stages. Fortunately these stages can be pipelined to increase the throughput of the conversion systems. There are two prerequisites before this system can be used. First, the number of bits used for the ternary exponent must be equal to or larger than the number of bits used for the binary exponent. Secondly the DBNS exponents must be of at least 6 bits in length.

### 2.7.2 DBNS to Binary conversion [9]

Converting DBNS to binary is three step process. The first step is to convert the ternary exponent into a binary manissa and a binary shift value:

$$3^t \to m \cdot 2^s \tag{2.14}$$

Where t is the ternary exponent, m is the mantissa and s is the shift factor. For example the ternary  $3^1$  could be translated into  $11_b \cdot 2^0$ , where the subscript b denotes a binary representation. This conversion is handled through the use of a look-up table ROM.

In the second step the shift value is added to the binary exponent. This will produce an "overall" shift value. This result is used in the third stage as a shift value for the mantissa. Once the mantissa has been shifted, the final result is a binary number that approximates

the DBNS representation. For example, to convert the DBNS representation of 6 into binary would require:

$$n = 2^{1} \cdot 3^{1} \qquad (3^{1} = 11_{b} \cdot 2^{0})$$

$$= 2^{1} \cdot 11_{b} \cdot 2^{0}$$

$$= 11_{b} \cdot 2^{1-0}$$

$$= 110_{b}$$

In this case the converted value exactly matches the DBNS representation. This is not always true, but the approximation can be quite accurate depending on the number of bits used to represent the mantissa.

## 2.8 Summary

This chapter discussed advantages and flexibility of the Double Base Number system. DBNS is well suited for tasks where overhead, due to multiplications, can be reduced. The difficulties that arise when performing arithmetic can be avoided by converting the DBNS into binary, through the use of a ROM, binary adder and a barrel shifter. The size of the ROM is governed by the number of bits in the ternary exponent. The size of the ternary exponent can be reduced through the use of asymmetric coefficients and by using two digit DBNS. The non-linear nature of the single digit DBNS makes it ideal for mapping non-linear data, such as data for hearing devices. The odd base in DBNS is not restricted to a base of three, but can be changed to any odd base to suit any specialized needs. This change of the odd base does not change the DBNS architecture in any way, only the contents of the any conversion ROMs.

# Chapter 3

# DBNS Finite Precision FIR Filter Design

### 3.1 Introduction

Good hardware design is not the only requirement for good filter design. Another important requirement, besides good hardware design, is good coefficient design. The design of coefficients determines the quality of the filter, such as stopband attenuation and passband ripple, as well as the order of the filter. The order of the filter determines the number of hardware stages required by the filter. Poor coefficient design can produce the desired filter response, but at a much higher hardware cost. The technique used to design the filter coefficients may restrict the hardware design, or the hardware design may restrict the choice of coefficient design algorithms.

## 3.2 Coefficient Design Techniques

There are many different techniques to design filter coefficients. Many of which require the use of special number representations, such as canonic signed digit binary representation. For Finite Impulse Response (FIR) filters the main categories of these design techniques are:

- 1. Approximation digital filter design [16]: Techniques to approximate digital filters, such as using numerical analysis, Fourier series and windowing functions [19], or the Discrete Fourier Transform for non recursive filter design.

- 2. Linear programming: Filter design through the use of linear optimization methods. These techniques will produce results closer to the optimal design, but at the cost of taking more time. Includes methods such as Remez Exchange Algorithm [16].

- 3. Non-linear programming: Filter design through the use of non-linear optimization techniques. This method is used for very complicated systems where it would be difficult to use linear programming. One method used is genetic algorithms [13][23].

The techniques that were investigated for the design of filter coefficients for use with the Double Base Number System (DBNS) filters were genetic algorithms, integer programming and direct mapping. The filter designed through these was a lowpass filter suitable for interpolation of video signals.

#### 3.2.1 Genetic Algorithms

Designing coefficients for a DBNS filter at first appears very difficult. Only linear and non-linear programming techniques can be used because there are no standard methods for DBNS filter design. The DBNS coefficients are to be in index form, meaning the coefficients have 3 parts, representing the sign and the two exponents of the DBNS number. A small change to the value of a coefficient is not a straightforward process. A small change in one of the exponents of the coefficients can mean a very large change in the coefficient's value. This makes a linear programming approach more difficult and a non-linear programming approach much more appealing. Genetic Algorithms (GA) [13][23] were chosen as the preferred non-linear method.

Genetic algorithms are a relatively recent optimization technique, initially disclosed in 1975 [21]. Genetic Algorithms are a non-linear programming technique that use the natural selection properties of evolution to produce a desired result. Multiple random starting points are selected, referred to as chromosomes. Each chromosome is a series of

coefficients that are encoded into sub-chromosomes. These sub-chromosomes are a single bit sequence representing a DBNS digit. The chromosomes are then subject to a set of predetermined fitness tests. These fitness tests require the decoded chromosomes to conform to a set of filter specifications. The chromosomes that produce the best results are then combined through a process called crossover.

Crossover is used to produce the next generation of chromosomes from parent chromosomes of the previous generation. Keeping with the random nature of evolution, crossover selects pairs of parent chromosomes randomly, using the results of the fitness test as a weighting factor. Once a chromosome pair is selected, a pair of offspring chromosomes are produced by switching a random number of contiguous bits between the two parent chromosomes (see Figure 3.1). It can take hundreds of thousands of generations to produce the desired result.

**Crossover Point** 1 1 1 Parent Chromosomes 0 1 0 0 : 0 0 Crossover Operator 0 0 0 0 1 1 1 Offspring Chromosomes 0 1 0 0 0 1

Figure 3.1: Crossover

To keep the population of chromosomes from evolving into a non optimal state, there are two precautions that can be taken. The first is the use of a mutation factor. The mutation factor introduces a random change into the chromosomes. There is a very small chance

that a random bit of a chromosome will be switched. The mutation factor affects the offspring chromosomes immediately after the crossover operation is performed. The second technique is to set conditions where low performing chromosomes will be discarded and replaced with new, random coefficients. The genetic algorithm used for designing DBNS filter coefficients used a mutation factor.

Another technique used to speed up the convergence of the genetic algorithm is multipoint crossover and mutation [22]. Because the chromosomes are of such length and complexity, they can be broken up into segments and have crossover and mutation on these segments. A good design choice would be to have these segments designed into natural groupings. For example, in the DBNS genetic algorithm, these segments are the individual chromosomes, which were each a distinct sub-chromosome. Therefore the crossover and mutation are performed on a coefficient by coefficient basis.

There were some problems with the genetic algorithm used. The first was that the GA is very slow. Secondly, there is no guarantee that the GA will converge, producing the correct answer. Finally, the results produced were not close to optimal. The best filter design achieved had the following statistics:

- 57<sup>th</sup> order

- 40.35dB stopband attenuation

- 1.75dB pass band ripple

- 0.09 Hz transition band (normalized to 1 Hz)

Figure 3.2 shows the frequency response of the genetic algorithm filter, using a normalized frequency range.

Figure 3.2: Frequency response of a genetic algorithm produced DBNS FIR filter

### 3.2.2 Integer Programming

Finding the best DBNS approximation of a designed filter's coefficients is an integer programming task. This is due to the fact that the DBNS exponents, both binary and ternary, are integers. In general, integer programming is a NP-complete problem. That is the reason why genetic algorithms were tried first for generating the coefficients. There are, however, some purely integer programming methods that can be used as well.

The integer programming method used was to map floating point decimal numbers into DBNS. There are four variables to optimize for each number, one for each DBNS exponent.

$$n = \pm 2^a 3^b \pm 2^c 3^d \tag{3.1}$$

To simplify the solution, the first three variables, a, b and c, are set using an exhaustive search, and only the fourth variable, d, is optimized. An important concern, when dealing with fractional results, is to ensure the more optimal choice is selected.

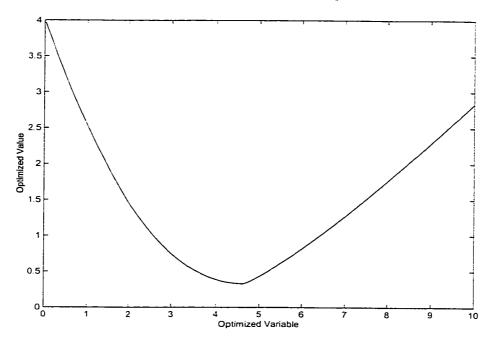

Figure 3.3: Result curve due to optimization

For example if the result curve due to optimization is similar to Figure 3.3, then rounding a fractional result would produce the result of 5, and not the most optimal result of 4. The results of the integer programming were very similar to that of the direct mapping scheme described next, though the required computational time was much higher.

## 3.2.3 Direct mapping

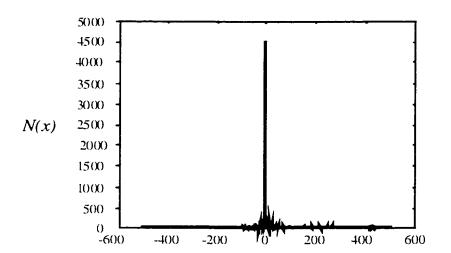

A study of filter coefficients can be performed to show the typical number range of filter coefficients for a large set of designs. A histogram showing a study of the coefficient distribution of over 200 filters is shown in Figure 3.4 [14]

Figure 3.4: A histogram showing the coefficient values for over 200 filters

Looking at Figure 3.4. it can be seen that the vast majority of the coefficients are zero or very close to zero. This corresponds very well with the DBNS representation accuracy.

In the DBNS, approximately one half of all representable numbers lie in the range between zero and one. This means that if a number is less than one it can be very accurately represented in DBNS. This accurate representation of numbers less than one allows for a direct mapping of these numbers into DBNS.

Filter coefficients can be designed using standard filter design tools, for example MatLab. Filter design functions in MatLab, such as *remez()*, can be used to design filter coefficients in the internal floating point representation. The floating point coefficients can then be converted directly into a DBNS representation. The conversion, or mapping, can be performed in two different ways. The first method is the modified Greedy Mapping algorithm, and the second is optimal mapping using a form of linear programming (in our case an exhaustive search was conducted).

#### **Modified Greedy Mapping**

The Greedy Algorithm was first proposed in [15]. For a single digit, the DBNS number closest to the target number is selected. Multi-digit DBNS works in a similar way, the first digit is selected to be as close to the target number as possible. The following digits are selected to be as close as possible to the remaining value after subtracting the values of the previous DBNS digits.

The modified greedy mapping algorithm is very similar to the Greedy Algorithm. It was designed for use with one and two digit DBNS mapping. For one digit it behaves exactly as the Greedy Algorithm. For two digits, it selects the two closest numbers to the target value, then fine tunes the mapping with a second digit. The best result of the two possible is then selected. This produces a more accurate mapping than the Greedy Algorithm alone.

One advantage of the modified greedy mapping method over the optimal mapping is speed. The modified greedy mapping time increases linearly with an increased representation range (i.e. more bits per exponent). Another possible advantage to the modified greedy mapping will be discussed in Chapter 4.

#### **Optimal Mapping**

Optimal mapping is performed just as the name implies. The entire representation range is searched for the best possible match to the target value. This method becomes more efficient if a sorted list is used. The mapping time increases approximately along a square law with increased representation range. Despite the square law increase in speed, the mapping of fifty-three, 2 digit DBNS numbers, using 12bit exponents requires less than a minute on a Sun Ultra 10 workstation.

#### An Example of Mapping

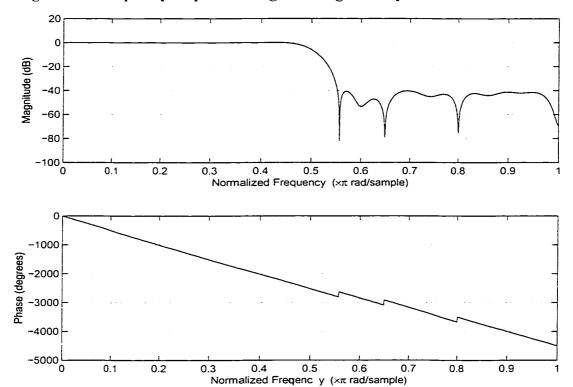

A filter was designed using MatLab's remez() function. The filter designed had the following specifications:

- 53<sup>rd</sup> order

- 85.36dB stopband attenuation

- 0.000468 dB pass band ripple

- 0.12Hz transition band (normalized to 1Hz)

53 Order FIR Filter 50 0 Magnitude (dB) -50 -100 -150-200 <u>|</u> 0.1 0.2 0.3 0.4 0.5 0.8 0.6 0.7 0.9 Normalized Frequency (×π rad/sample) -500 Phase (degrees) -1000 -1500 -2000 -2500 -3000 0 0.2 0.1 0.3 0.4 0.5 0.6 0.7 0.8 0.9 Normalized Frequency ( $\times \pi$  rad/sample)

Figure 3.5: Filter response of a floating point coefficient filter

Figure 3.5 shows the frequency response of this filter. The filter coefficients are all in floating point representation. This gives the filter coefficients an accuracy hard to achieve in hardware.

The designed filter is mapped using both the optimal mapping and the modified greedy mapping. The DBNS representation used for these mappings is two digit, with 5 bits being used for the binary exponent and 4 bits used for the ternary exponent. These bit widths

include the sign bit for the exponents. The resulting filters had the following specifications as shown in Table 3.1.

**Table 3.1: Mapped Filter Specifications**

|                                   | Designed | Optimal  | M. Greedy |

|-----------------------------------|----------|----------|-----------|

| Order                             | 53       | 53       | 53        |

| Passband Ripple (dB)              | 0.000468 | 0.001339 | 0.001341  |

| Stopband Attenuation (dB)         | 85.36    | 77.98    | 77.52     |

| Transitionband Width (normalized) | 0.12     | 0.12     | 0.12      |

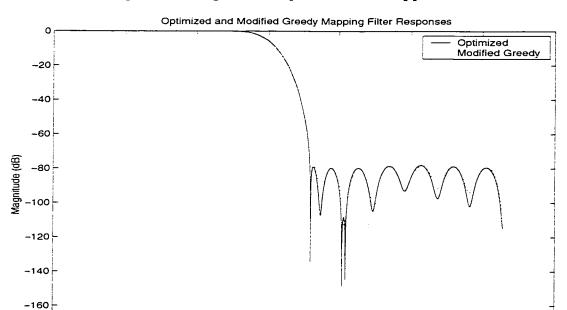

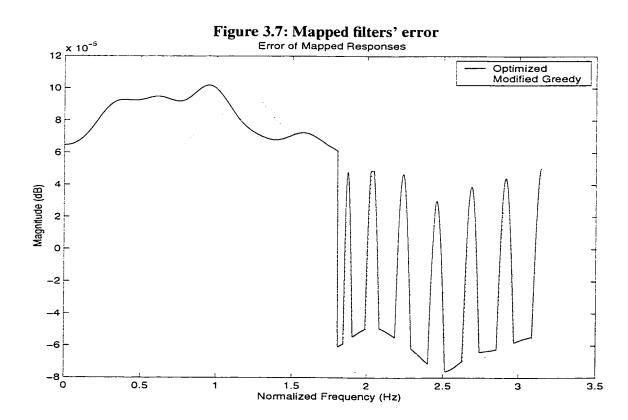

The filters' magnitude response is shown in Figure 3.6, and the error between the design response and the mapped response is shown in Figure 3.7.

As can be seen from both the table and the figures, there is very little error between the designed and mapped filters. The optimal mapping method does not offer a significant accuracy advantage over the modified Greedy Algorithm. The entire design, from generating the designed filter, to producing the output graphs and statistics took less than a minute on a Sun Ultra 10 workstation. This is very fast and produces very good filters, especially when compared to the genetic algorithm approach.

1.5 2 Normalized Frequency (Hz)

2.5

3

3.5

Figure 3.6: Magnitude response for the mapped filters

-180 L

0.5

#### **Comparing DBNS and Binary Direct Mapping**

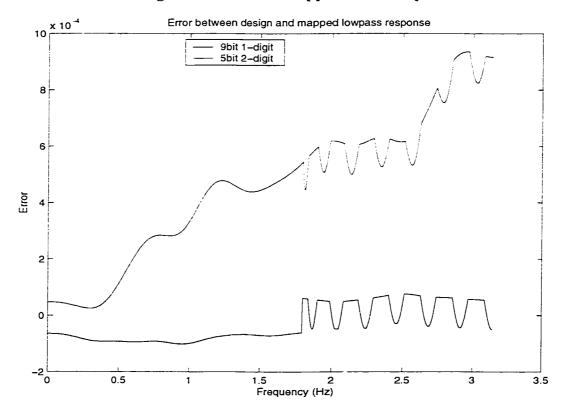

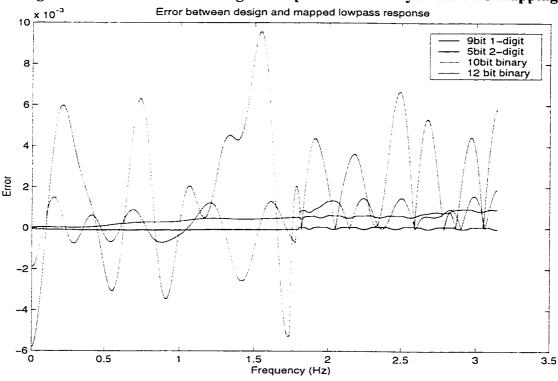

Direct mapping of DBNS can be accurate, as seen in the last section. Consider the direct mapping scheme to binary and DBNS of one and two digits. For the comparison, the remez() FIR filter from the previous section (Figure 3.5) was used as the base filter to be mapped. For the DBNS mapping 9 bit binary and ternary exponents were used for the single digit DBNS, and 5 bit binary, 4 bit ternary were used for the two digit DBNS. All the DBNS mappings used the modified Greedy Algorithm. The number of binary bits used for the mapping was 10 and 12 bit.

The error between the mapped DBNS responses and the designed magnitude response can be seen in Figure 3.8. The two digit DBNS mapping is much more accurate, by an order of magnitude, than the single digit DBNS mapping.

Figure 3.8: Error of mapped DBNS responses

Figure 3.9 shows the error between the designed magnitude response and the magnitude response of both the binary mappings and both the DBNS mappings. The stopband attenuation achieved by these mappings are as follows: 10 bit binary 45dB, 12 bit binary 55dB, single digit DBNS 60dB and 2 digit DBNS is 77dB. It can be clearly seen that the DBNS mappings offer a more accurate mapping, particularly in the case of the two digit mapping.

Figure 3.9: Error between designed response and binary and DBNS mappings

Figure 3.10 shows the error between the designed coefficient values and the mapped coefficients. The binary design has varying errors across all the filter's coefficients. The largest error in the DBNS mappings is focused at the central coefficients, and rapidly drops off for the outer coefficients. As typical in a lowpass FIR filter, the central coefficients have the largest value and the value of the coefficients decreases towards the outer coefficients [16]. The smaller the number, the more accurately the DBNS can represent it, thus the reason there is more error in the central coefficients. The larger

central coefficients have more weight in determining the output, therefore if their error could be decreased it would greatly decrease the error in the mapped response.

Figure 3.10: Error between designed coefficient values and mapped coefficients

# 3.3 Summary

This chapter covered different techniques to generate coefficients for DBNS FIR filters. While it is possible to use complex and time consuming techniques, such as genetic algorithms, it is not necessary. The results produced by the use of direct mapping are better quality filters (i.e. better stopband attenuation) than that of the genetic algorithm, and are achieved much more quickly than the genetic algorithm or other iterative optimization techniques. By using standard, well-defined filter design tools, and mapping the results into DBNS we achieve better results in a fraction of the time.

# Chapter 4

# DBNS FIR Filter Architectures

### 4.1 Introduction

One of the basic structures in DSP is the FIR filter. FIR filters are used to modify and transform discrete data in a number of applications. FIR filters exist in many devices, from CD players to cell phones to radios. FIR filters can be used in traditional filtering tasks, or for weighted or moving average calculations. The FIR filters described here are primarily designed for video rate applications (approximately 40 MHz), though they can be used in any general application. This chapter will discuss two architectures used for Double Base Number System (DBNS) FIR filters. These architectures are the hybrid 2 digit DBNS and the 2 digit DBNS filters.

## 4.2 Systolic Arrays

Filter architectures require many additions and multiplications. Each multiply block represents a filter coefficient, contributing to the order of the filter. Fifteen multiplication blocks represent a fifteenth order filter. In order to arrange the multipliers and adders into a parallel architecture, where there are a minimum number of binary two operand adders, we need to use systolic arrays.

39

Systolic arrays are a class of pipelined array architectures, and feature the properties of modularity, local connectivity, regularity, high level of pipelining, and highly synchronized multiprocessing [11]. Systolic arrays are useful architectures for systems that have multiple operations performed on each data element in a repetitive manner. This gives the system a highly parallel processing architecture. These repeated operational blocks in the systolic array are called processing elements.

Filtering of data is performed in the time domain using convolution. A unidirectional systolic array convolver was used as the base filter architecture in all DBNS filters described herein. Figure 4.1 [11] shows the typical unidirectional systolic array convolver. The circles in the figure represent a multiply accumulate processing element.

Figure 4.1: A unidirectional systolic array convolver and processing element

The top portion of Figure 4.1 is a signal flow graph (SFG). In a SFG a "D" represents a delay element, and the processing elements (the circles) are considered to have no delay. Realistically, the processing element hardware would contain delay, and care must be taken to ensure the signals arrive at the correct time. This can be handled through the addition of delay elements, such as latches.

#### Example 4.1

If u(n) were to consist of the elements  $\{u_0, u_1, u_2, u_3\}$ , the data passing through the convolver would produce the following table. The columns represent the output of the given processing element. The output of the final processing element is the output of the filter and is therefore labelled as such.

PE 0 PE 1 Time PE 2 Output  $u_0w_0$ 1  $u_I w_0$  $u_0w_I$ 2  $u_2w_0$  $u_0w_0+u_1w_1$  $u_0w_2$ 3  $u_3w_0$  $u_1 w_0 + u_2 w_1$  $u_0 w_1 + u_1 w_2$  $u_0w_3$ 4  $u_2w_0+u_3w_1$  $u_0w_0+u_1w_1+u_2w_2$  $u_0w_2+u_1w_3$ 5  $u_1w_0+u_2w_1+u_3w_2$  $u_0 w_1 + u_1 w_2 + u_2 w_3$  $u_3w_0$ 6  $u_2w_0 + u_3w_1$  $u_0w_0+u_1w_1+u_2w_2+u_3w_3$ 7  $u_1w_0+u_2w_1+u_3w_2$  $u_3w_0$ 8  $u_2w_0+u_3w_1$ 9  $u_3w_0$

Table 4.1: Unidirectional systolic convolver results

#### 4.2.1 Pipelining

In hardware design, a pipeline is a structure that breaks up computational tasks into smaller independent computations that can be cascaded together and computed concurrently. The importance of the pipeline is that the input data only waits for a single stage to compute, rather than the entire task.

The pipelinability of a systolic array is an important feature. Through pipelining the data can proceed through the sub-tasks without having to wait for the entire computation to be completed. Hence by breaking a computational task into multiple independent sub-tasks the throughput of the system is increased.

DBNS FIR Filter Architectures Systolic Arrays 40

An example of pipelining is the systolic array convolver discussed above. Instead of waiting for the data to pass through the convolver individually, each processing element acts independently and concurrently. Real world hardware does not perform without a propagation delay, as assumed by processing elements in the SFG. Thus it makes sense to pipeline the processing elements. The processing elements can be pipelined by breaking multiply accumulate operation into an independent multiplication and addition. This has the potential effect of doubling the clock frequency, and the throughput.

## 4.3 Basic Processing Element

The systolic array convolver is made up of a network of identical processing elements. Each of these elements performs an inner product calculation, which is performed through a multiply accumulate (MAC) operation. That is, the processing element performs the following calculation:

$$p_i = p_{i-1} + u(n) \cdot w_i \tag{4.1}$$

where  $p_i$  is the output of the *i*th processing element, *i* is the index of the element, and *n* is the index of the input data being operated on. When chained together to form a systolic array filter, the output equation becomes:

$$y(n) = \sum_{i=0}^{N} u(n) \cdot w_i$$

(4.2)

where *N* is the order of the filter.

The DBNS equivalent to a MAC cell is shown in Figure 4.2 [9]. Because the DBNS is represented in hardware by the triple  $(s_i, b_i, t_i)$ , there are three pieces of data on which to be operated. The binary and ternary exponents of the data  $(b_d \text{ and } t_d)$  are added to the exponents of the coefficients  $(b_c \text{ and } t_c)$  in order to perform the multiplication portion of the MAC calculation. The two adders required for this multiplication are in the top part of

Figure 4.2. The sign bits are handled by simple logic and are used for sign correction before the final accumulation.

The accumulation stage cannot be performed directly after the multiplication, due to the difficulty in adding two DBNS numbers. It is easier to convert the DBNS value to binary for the accumulation. This conversion is handled by the ROM, shifter and adder in the middle of the figure. The ROM contains the data for converting the ternary portion of a DBNS digit into a binary value. This data is a fixed point binary mantissa and a shift value.

$\{b_c, t_c\}$   $\{b_d, t_d\}$ Binary

ROM

Exponent Sum p(n)  $h_c \cdot h_d$   $h_c \cdot h_d$  p(n+1)

Figure 4.2: A DBNS Multiply Accumulate Cell

The binary portion of the DBNS digit also corresponds to a shift. Therefore the binary exponent and the shift data from the ROM are added to find the final shift value for the mantissa data from the ROM. The ROM increases size along a square law based on the number of bits required to represent the ternary exponent. Therefore it is important to keep the ternary exponent as small as possible.

Once the DBNS to binary conversion has taken place, the accumulation can be performed. The accumulation sums the previous multiplication with all the values generated by the preceding MAC cells.

## 4.4 Hybrid 2 digit DBNS Architecture

Architecture describes the structure of a system. It consists of the sub-blocks of the system and the interconnects or buses between each of these sub-blocks. The architecture of a system can be hierarchical. For example, the DBNS MAC can be considered a single sub-block of a system, even though it has its own architecture.

The first architecture investigated was the hybrid 2 digit DBNS architecture. This system uses two digit DBNS for the data and single digit DBNS for the coefficients. This architecture was first introduced in [9]. Two digits were used for the data to produce a pseudo-linear mapping space. This reduced the error introduced by the conversion to DBNS. Approximately one half of all numbers representable by a DBNS digit are less than 1, and the majority of all filter coefficients are also below 1 [9]. This allows for a large number of coefficient values that can be represented by a single digit.