#### University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

2011

# A Prototype CVNS Distributed Neural Network

Golnar Khodabandehloo University of Windsor

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### **Recommended** Citation

Khodabandehloo, Golnar, "A Prototype CVNS Distributed Neural Network" (2011). Electronic Theses and Dissertations. Paper 433.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

### A Prototype CVNS Distributed Neural Network

by

Golnar Khodabandehloo

A Dissertation Submitted to the Faculty of Graduate Studies through the Department of Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at the University of Windsor

Windsor, Ontario, Canada 2011

#### © 2011 Golnar Khodabandehloo

All Rights Reserved. No Part of this document may be reproduced, stored or otherwise retained in a retreival system or transmitted in any form, on any medium by any means without prior written permission of the author.

A Prototype CVNS Distributed Neural Network

by

Golnar Khodabandehloo

APPROVED BY:

Y. Savaria Department of Electrical Engineering, Polytechnique Montral

A. Jaekel School of Computer Science, University of Windsor

C. Chen Department of Electrical and Computer Engineering, University of Windsor

M. Khalid Department of Electrical and Computer Engineering, University of Windsor

M. Ahmadi Department of Electrical and Computer Engineering, University of Windsor

M. Mirhassani Department of Electrical and Computer Engineering, University of Windsor

G. Reader Department of Mechanical, Automotive and Materials Engineering, University of Windsor

March 25, 2011

## **Declaration of Previous Publication**

This thesis includes 5 original papers that have been previously published/submitted for publication in peer reviewed journals, as follows:

| Thesis Chapter                                                             | Publication title                                                                            | Publication status |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------|

| Chapters 3,4, and 6                                                        | Chapters 3,4, and 6 A prototype CVNS distributed neural network using synapse-neuron modules |                    |

| Chapter 5                                                                  | Chapter 5 A 16-level current-mode CVNS memory                                                |                    |

| Chapter 5                                                                  | CVNS-based storage and refreshing scheme for a multi-valued dynamic memory                   | In-press           |

| Chapter 2                                                                  | Resistive-type CVNS distributed neural networks with improved noise to signal ratio          | Published          |

| Chapter 4 Analog implementation of a novel resistive-type sigmoidal neuron |                                                                                              | In-press           |

I certify that I have obtained a written permission from the copyright owner(s) to include the above published material(s) in my thesis. I certify that the above material describes work completed during my registration as graduate student at the University of Windsor.

I declare that, to the best of my knowledge, my thesis does not infringe upon anyone's copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material from the work of other people included in my thesis, published or otherwise, are fully acknowledged in accordance with the standard referencing practices. Furthermore, to the extent that I have included copyrighted material that surpasses the bounds of fair dealing within the meaning of the Canada Copyright Act, I certify that I have obtained a written permission from the copyright owner(s) to include such material(s) in my

thesis. I declare that this is a true copy of my thesis, including any final revisions, as approved by my thesis committee and the Graduate Studies office, and that this thesis has not been submitted for a higher degree to any other University or Institution.

# **Abstract**

Artificial neural networks are widely used in many applications such as signal processing, classification, and control. However, their practical implementation is challenging due to the number of inputs, the cost of storing the required weights, and the difficulty in realizing the activation function.

In this work, Continuous Valued Number System (CVNS) distributed neural networks are proposed which are providing the network with self-scaling property. This property aids the network to cope spontaneously with different number of inputs. The proposed CVNS DNN can change the dynamic range of the activation function spontaneously according to the number of inputs providing a proper functionality for the network.

In addition, multi-valued CVNS DRAMs are proposed to store the weights as CVNS digits. These memories scan store up to 16 level, equal to 4 bits, on each storage cell. In addition, they use error correction codes to detect and correct the error over the stored values.

A synapse-neuron module is proposed to decrease the design cost. It contains both synapse and neuron and the relevant components. In these modules, the activation function is realized through analog circuits which are far more compact compared to the digital look-up-tables while quite accurate. Furthermore, the redundancy between CVNS digits, together with the distributed structure of the neuron make the proposal stable against process variations and reduce the noise to signal ratio. To my family,

with love ...

# **Acknowledgments**

There are several people who deserve my sincere thanks for their generous contributions to this project. I would first like to express my sincere gratitude and appreciation to Dr. Mitra Mirhassani and Dr. Majid Ahmadi, my supervisors for their invaluable guidance and constant support throughout the course of this thesis work.

In addition to my advisors, I would like to thank the rest of my thesis committee: Dr. Chunhong Chen and Dr. Mohammed Khalid from the electrical and computer engineering department, Dr. Arunita Jaekel from the school of computer science, and Dr. Yvon Savaria from the Polytechnique Montreal for their participation in my seminars, reviewing my thesis, and their constructive comments.

Also, I would like to thank Dr. Roberto Muscedere for his assistants regarding the VLSI CAD tools and facilities used during the course of the project.

I am grateful to my colleague, friend, and partner Ashkan H. Namin who has supported and believed in me.

Finally, my deepest gratitude goes to my family for their unconditional love, support, and encouragement.

# Contents

| De | eclara  | tion of Previous Publication                  | iv   |

|----|---------|-----------------------------------------------|------|

| Ał | ostrac  | t                                             | vi   |

| De | edicat  | ion                                           | viii |

| Ac | know    | vledgments                                    | ix   |

| Li | st of I | Figures                                       | xiii |

| Li | st of ] | <b>Fables</b>                                 | xvi  |

| Li | st of A | Abbreviations                                 | xvii |

| 1  | Intr    | oduction                                      | 1    |

|    | 1.1     | Summary of Contributions                      | 7    |

|    | 1.2     | Outline of the Thesis                         | 7    |

| 2  | CVN     | NS Distributed Neural Network                 | 9    |

|    | 2.1     | Previous Structures of Resistive-Type ANNs    | 9    |

|    |         | 2.1.1 Lumped Neural Network                   | 10   |

|    |         | 2.1.2 Conventional Distributed Neural Network | 11   |

|    | 2.2     | CVNS Distributed Neural Network               | 12   |

|   |      | 2.2.1 Scalability                               | 16 |

|---|------|-------------------------------------------------|----|

|   |      | 2.2.2 2-2-1 XOR                                 | 16 |

|   | 2.3  | CVNS Fully Distributed Neural network           | 17 |

|   | 2.4  | Stochastic Model                                | 18 |

|   | 2.5  | Comparison                                      | 23 |

|   | 2.6  | Conclusion                                      | 24 |

| 3 | Tru  | ncated CVNS Distributed Neural Network          | 26 |

|   | 3.1  | Truncated CVNS DNN                              | 27 |

|   | 3.2  | Effect of Truncation on Performance             | 31 |

|   | 3.3  | NSR Calculation                                 | 33 |

|   | 3.4  | Conclusion                                      | 35 |

| 4 | Syna | apse-Neuron Module                              | 37 |

|   | 4.1  | CVNS DRAM                                       | 38 |

|   | 4.2  | Multiplier Module                               | 41 |

|   | 4.3  | Interface Circuit                               | 42 |

|   | 4.4  | Sigmoidal Neuron                                | 44 |

|   | 4.5  | Voltage-Mode ADC                                | 45 |

|   | 4.6  | Conclusion                                      | 47 |

| 5 | CVN  | IS Multi-Valued Dynamic Memory                  | 48 |

|   | 5.1  | CVNS Modifications for Implementation           | 51 |

|   | 5.2  | Noise Margin and Error Correction Based on CVNS | 54 |

|   | 5.3  | CVNS-Based Storage Circuitry                    | 58 |

|   | 5.4  | CVNS-Based Refreshing Scheme and Circuits       | 64 |

|   |      | 5.4.1 Analog to Digital Converter               | 66 |

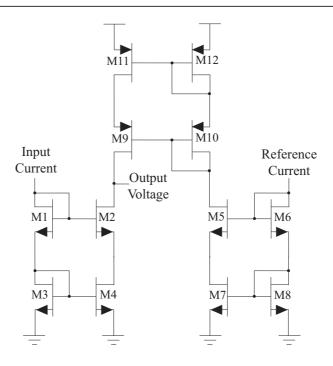

|   |      | 5.4.1.1 Current Comparators                     | 70 |

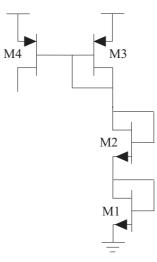

|   |      | 5.4.1.2 Current Mirrors                         | 71 |

|   |      |                                                 |    |

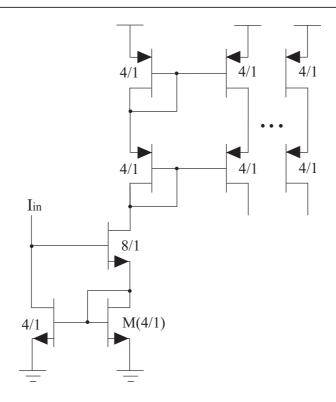

|    |               | 5.4.2 Digital to Analog Converter         | 72 |

|----|---------------|-------------------------------------------|----|

|    | 5.5           | Simulation Results and Comparisons        | 77 |

|    | 5.6           | Conclusion                                | 81 |

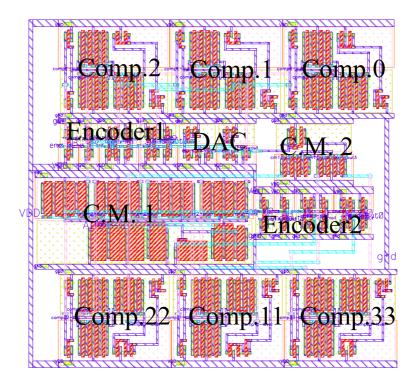

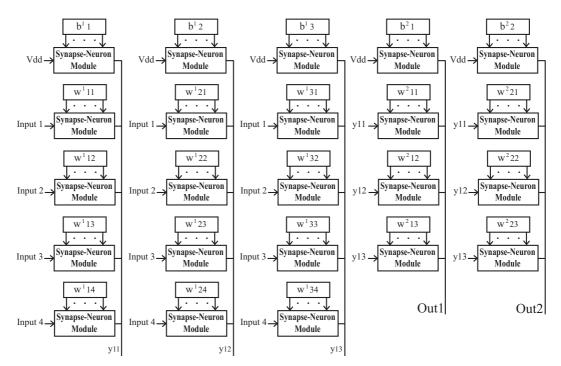

| 6  | A 4-          | 3-2 CVNS DNN using Synapse-Neuron Modules | 83 |

|    | 6.1           | Prototype CVNS DNN                        | 83 |

|    | 6.2           | Comparisons                               | 87 |

|    | 6.3           | Conclusion                                | 89 |

| 7  | Con           | clusions and Future Work                  | 90 |

|    | 7.1           | Conclusions                               | 90 |

|    | 7.2           | Future Work                               | 91 |

| Re | eferen        | ices                                      | 93 |

| VI | VITA AUCTORIS |                                           |    |

# **List of Figures**

| 1.1 | Block diagram of the CVNS digit generation from binary digits                            | 4  |

|-----|------------------------------------------------------------------------------------------|----|

| 2.1 | (k+1)-input resistive-type lumped neural network                                         | 10 |

| 2.2 | Block diagram of a $(k + 1)$ -input resistive-type DNN                                   | 11 |

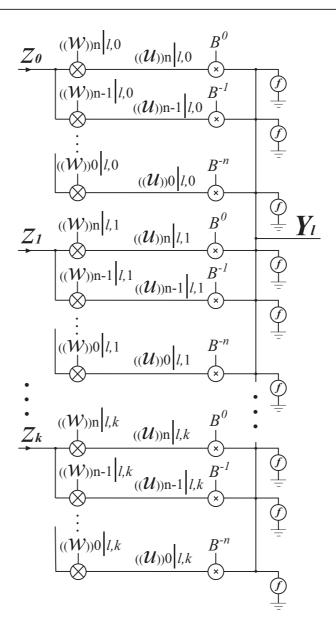

| 2.3 | Proposed resistive-type CVNS DNN configuration.                                          | 13 |

| 2.4 | Block diagram representation of the CVNS multiplication (equation $(2.5)$ ).             | 14 |

| 2.5 | Scalability of the proposed DNN for a sigmoidal activation function                      | 17 |

| 2.6 | Block diagram of the $2 - 2 - 1$ XOR network                                             | 18 |

| 2.7 | Off-line network training by back propagation algorithm                                  | 19 |

| 2.8 | $(k+1)\text{-input resistive-type CVNS}$ fully distributed neural network. $\ . \ . \ .$ | 20 |

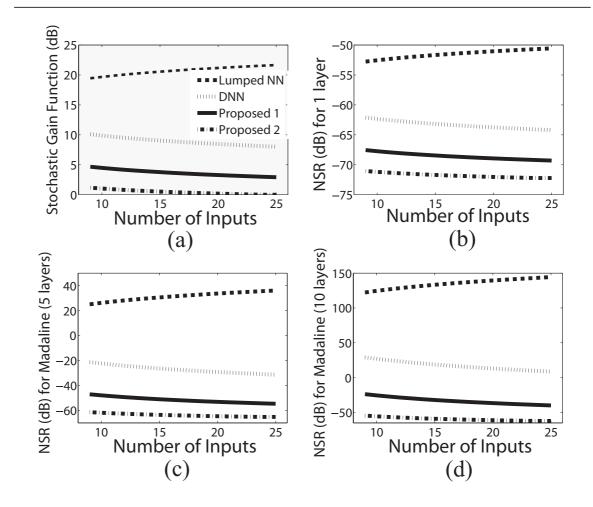

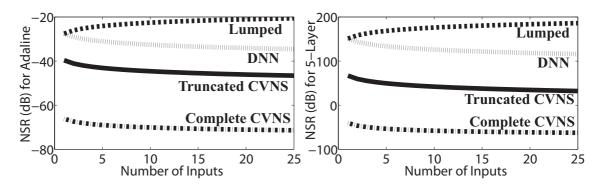

| 2.9 | Comparison for input range of $[9, 25]$ : (a) Stochastic Gain Function for               |    |

|     | Adaline, NSR for (b) Adaline, (c) 5-layer Madaline, (d) 10-layer Madaline.               | 23 |

| 3.1 | Final multiplication result in a high resolution environment                             | 30 |

| 3.2 | Final multiplication result in a low resolution environment                              | 31 |

| 3.3 | Simulation result of an XOR based on the truncated CVNS DNN                              | 31 |

| 3.4 | NSR comparisons for Adalines and 5-layer Madalines                                       | 35 |

| 4.1 | Block diagram of the proposed synapse-neuron module                                      | 38 |

| 4.2 | Block diagram of the 13-bit multi-valued DRAM.                                           | 39 |

| 4.3 | Layout of the 13-bit multi-valued DRAM                                                   | 40 |

|     |                                                                                          |    |

| 4.4  | Block diagram of the multiplier module                                              | 41 |

|------|-------------------------------------------------------------------------------------|----|

| 4.5  | Block diagram of the partial multiplication module.                                 | 41 |

| 4.6  | Simulation result of '1, 1111, 1010, 1011' multiplied by '0111'                     | 42 |

| 4.7  | Layout of the multiplication module.                                                | 43 |

| 4.8  | Schematic of the interface circuit.                                                 | 43 |

| 4.9  | Schematic of the proposed resistive-type neuron to realize the sigmoid              |    |

|      | function                                                                            | 44 |

| 4.10 | Simulation result of the sigmoidal neuron                                           | 45 |

| 4.11 | schematic of a set of inverters used in the proposed voltage-mode ADC               | 46 |

| 5.1  | Block diagram of simplified CVNS digit generation using the group method.           |    |

|      | Squares show the weighted sum operation units.                                      | 52 |

| 5.2  | Block diagram of the modified CVNS digit generation with $\psi = 4$ and $\nu = 1$ . | 55 |

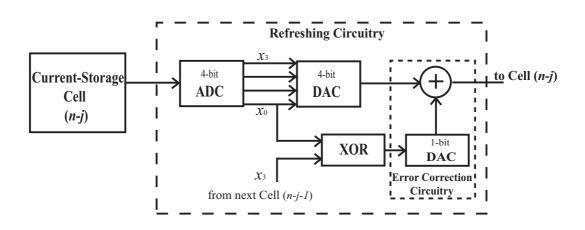

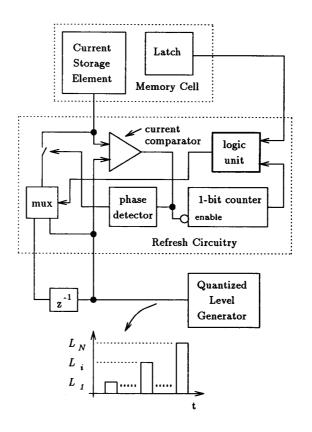

| 5.3  | Overall block diagram of the proposed memory                                        | 59 |

| 5.4  | General storage scheme for a 16-bit input. In order to increase the reliabil-       |    |

|      | ity of the cells, the LSB input to each cell is repeated and is used for error      |    |

|      | correction                                                                          | 59 |

| 5.5  | Self-biased dynamic current mirror memory (current copier)                          | 60 |

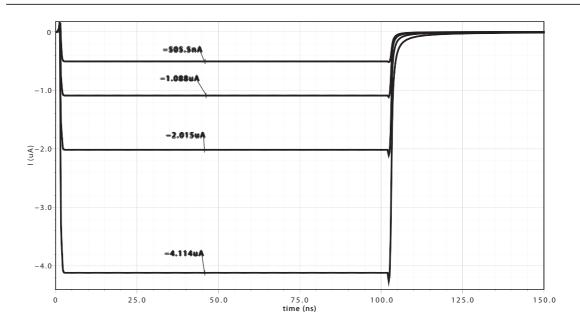

| 5.6  | Simulation results of different resistors in storage cell                           | 62 |

| 5.7  | Storage cell layout                                                                 | 63 |

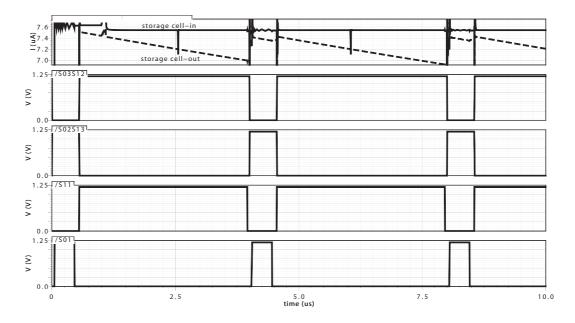

| 5.8  | Simulation result of storage cell layout for '1111' binary input                    | 63 |

| 5.9  | Block diagram of the refreshing system for a CVNS DRAM cell                         | 65 |

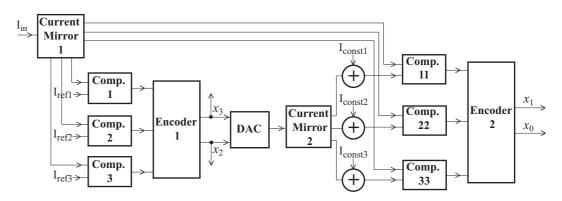

| 5.10 | Block diagram of the ADC                                                            | 66 |

| 5.11 | 4-bit ADC layout                                                                    | 69 |

| 5.12 | Schematic of a current comparator                                                   | 71 |

| 5.13 | Schematic of a current source                                                       | 71 |

| 5.14 | Schematic of the first current mirror                                               | 73 |

| 5.15 | Schematic of the second current mirror                                              | 74 |

|      |                                                                                     |    |

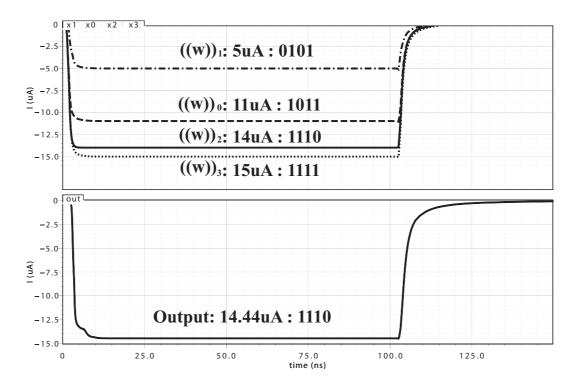

| 5.16 | Overall configuration of the 4-bit DAC.                                   | 74 |

|------|---------------------------------------------------------------------------|----|

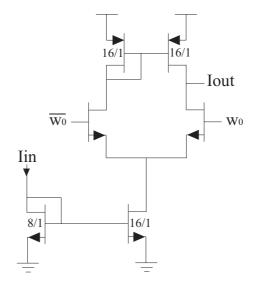

| 5.17 | Schematic of a one-bit weighted current mirror                            | 75 |

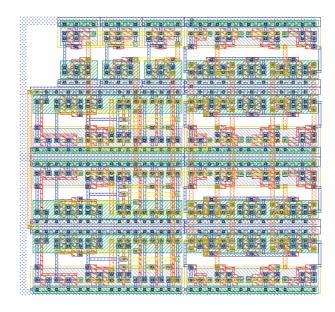

| 5.18 | DAC layout                                                                | 76 |

| 5.19 | DAC layout simulation results for input of '1111'                         | 77 |

| 5.20 | Post layout simulation result of total circuit for '1110' binary input    | 78 |

| 5.21 | Block diagram of the DRAM proposed by Lee et al. [1]                      | 80 |

| 6.1  | Block diagram of the 4-3-2 CVNS DNN                                       | 84 |

| 6.2  | Training pattern set for the 4-3-2 CVNS DNN                               | 85 |

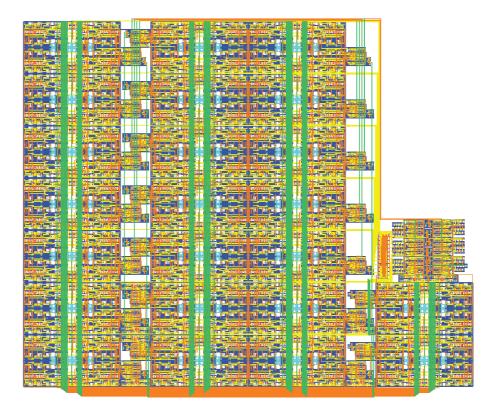

| 6.3  | Layout of the proposed 4-3-2 CVNS DNN                                     | 86 |

| 6.4  | Simulation result of the 4-3-2 CVNS DNN to solve the classification prob- |    |

|      | lem of Figure 6.2                                                         | 87 |

# **List of Tables**

| 1.1  | An example for radix-10 CVNS digits                                           | 4    |

|------|-------------------------------------------------------------------------------|------|

| 2.1  | NSR of sigmoidal Adalines from <i>case study</i> 2                            | 21   |

| 2.2  | Comparison of different sigmoidal Adalines for a $k + 1$ input                | 24   |

| 3.1  | Multiplication partial results for <i>case study 1</i>                        | 30   |

| 5.1  | An example for the CVNS digits with different group lengths and digit links   | 54   |

| 5.2  | An example for error correction when the binary input is $1011,0101,1110,001$ | 1 58 |

| 5.3  | Schematic storage cell and layout storage cell simulation results             | 64   |

| 5.4  | Values of all currents in the ADC block diagram                               | 67   |

| 5.5  | Extraction of $x_3$ and $x_2$ from the output of current comparators          | 67   |

| 5.6  | Comparison made between the proposed ADCM and some published meth-            |      |

|      | ods for a 4-bit ADC                                                           | 68   |

| 5.7  | Schematic ADC and layout ADC simulation results                               | 70   |

| 5.8  | Transistor sizes for each current source in the layout                        | 72   |

| 5.9  | Transistor sizes for each current mirror                                      | 76   |

| 5.10 | Schematic DAC and layout DAC simulation results                               | 77   |

| 5.11 | Comparison made between the proposed DRAM circuit and available pub-          |      |

|      | lished structures                                                             | 79   |

# List of Abbreviations

| Adaline  | Adaptive Linear Neuron.                            |

|----------|----------------------------------------------------|

| ADC      | Analog to Digital Converter.                       |

| ANN      | Artificial Neural Network.                         |

| CMOS     | Complementary Metal-Oxide-Semiconductor.           |

| CN       | Common Node.                                       |

| CVNS     | Continuous Valued Number System.                   |

| DAC      | Digital to Analog Converter.                       |

| DNN      | Distributed Neural Network.                        |

| DRAM     | Dynamic Random Access Memory.                      |

| ECC      | Error Correction Code.                             |

| FDNN     | Fully Distributed Neural Network.                  |

| IEEE     | Institute of Electrical and Electronics Engineers. |

| LID      | Least Informed Digit.                              |

| LSB      | Least Significant Bit.                             |

| LUT      | Look-Up-Table.                                     |

| Madaline | Multiple Adaline.                                  |

| MID      | Most Informed Digit.                               |

| MSB      | Most Significant Bit.                              |

| NSR      | Noise to Signal Ratio.                             |

| QLG      | Quantized Level Generator.                         |

| SCCV     | Simulated Constant Current Value.                  |

| TSMC     | Taiwan Semiconductor Manufacturing Company.        |

| XOR      | Exclusive OR.                                      |

|          |                                                    |

## Chapter 1

## Introduction

In the past decades, studies have been performed to use Artificial Neural Networks (ANNs) in different applications such as signal processing, pattern recognition, control, and many others [2–8]. One of the important features of an ANN is its scalability which means how the network responds if the number of inputs changes as different applications may need different number of inputs.

In conventional lumped ANNs, there is one neuron corresponding to all the synapses in each layer, where changing the number of inputs results in malfunctioning of the network [9]. In the case of a sigmoidal neuron, increasing the number of inputs would cause a larger saturation area for the neuron which changes the sigmoidal function to a hard limiting function. Decreasing the number of inputs, on the other hand, will result in a low-gain function. To overcome these problems, the neuron should be redesigned whenever the number of inputs changes which is not possible in hardware implementations. Therefore, the application of a lumped ANN becomes limited to applications with a certain number of inputs.

Resistive-type Distributed Neural Network (DNN) was introduced as an alternative for lumped neural networks [2, 3, 9, 10]. DNNs provide a self-scaling property for the network to cope with variable number of inputs, spontaneously. In DNNs, there are sub-neurons instead of neurons. Each sub-neuron is dedicated to one input; consequently, changing the number of inputs changes the number of sub-neurons. Therefore, DNNs can stretch or shorten the dynamic range of the activation function to keep the overall neuron characteristic in its proper functionality for different number of inputs. This causes an instant change in the dynamic range of the overall activation function according to the number of inputs. The use of sub-neurons in DNNs also provides some advantages for the network such as higher immunity to noise and process variations [9]. Noise to Signal Ratio (NSR) can be used to study the noise immunity of the ANNs [11]. Generally, a distributed configuration decreases the NSR compared to the lumped networks [3,9,10]. Here, NSR is used instead of signal to noise ratio to create a simple analytical expression.

In this work, a structure for feed-forward neural networks is proposed based on the Continuous Valued Number System (CVNS) as a derivative of conventional DNNs. The CVNS [12, 13] is a redundant number system which has been successfully employed in building high performance low power arithmetic units, multi-valued memories, and neural networks [14–20].

Considering inputs and outputs of the CVNS memory as binary digits, it is shown that there is an easy way for converting digits from binary to the CVNS and vise versa. The general representation of an (m + 1)-bit binary value is as follows.

$$x = \pm \sum_{i=0}^{m} x_i \cdot \beta^i \tag{1.1}$$

where  $x_i$  represents binary digits and  $\beta$  shows the radix;  $\beta = 2$  for a binary radix.

For example, a binary value of x = 101001 is equal to  $1 \times 2^5 + 0 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 = 41$ .

A CVNS set is an ensemble of multiple CVNS digits,  $((x))_i$ , which are generally generated based on two methods: a series method and a parallel method [13]. The former one,

called *cascade Digit Generation*, starts from the first CVNS digit and generates digits one by one in series; each digit is extracted from the previously generated digits.

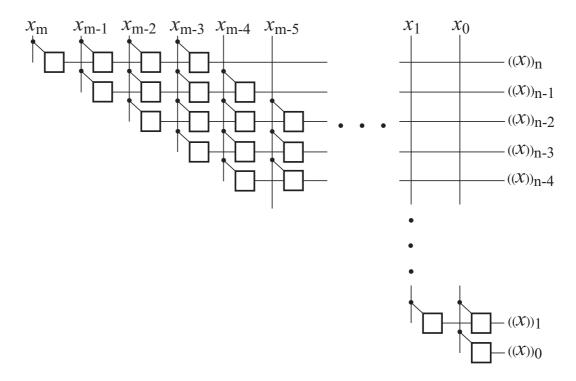

An other method called *Modular Reduction Digit Generation* is used in this work. It generates all the CVNS digits at the same time, in parallel, and independent to each other. Thus, this method provides a higher speed of conversion together with a lower complexity compared to the series method and is as follows.

$$((x))_{n-i} = \left(\frac{x}{M} \cdot \beta^{n-i+1}\right) \mod \beta = \left(\frac{x}{M} \cdot 2^{n-i+1}\right) \mod 2 \tag{1.2}$$

where *n* is the maximum index of the CVNS digits,  $0 \le i \le n$ . *M* is the maximum representation range, and  $\beta$  is the CVNS radix which is chosen low, equal to 2 ( $\beta = 2$ ), in order to reduce the complexity of the circuit further more. *mod* stands for the modular reduction operation on any continuous real value such that  $(a)mod\beta = a - I \times \beta$  where  $0 \le (a)mod\beta < \beta$ . *I* is an integer ( $I = 0, 1, \dots, \beta - 1$ ) which in this case is either 0 or 1.

In order to simplify the conversion between binary and CVNS, the maximum range of the representation for both the binary and the CVNS systems is selected as  $2^{m+1} = 2^{n+1} = M$ . Therefore, the number of binary digits, m + 1, and the CVNS digits, n + 1, are the same.

Under these conditions, a CVNS digit is directly generated from its corresponding binary digits through a general expression by modifying expression (1.2) as follows.

$$((x))_{n-j} = \sum_{i=0}^{m-j} x_i \cdot 2^{i+j-m}, \ j = 0, 1, ..., n$$

(1.3)

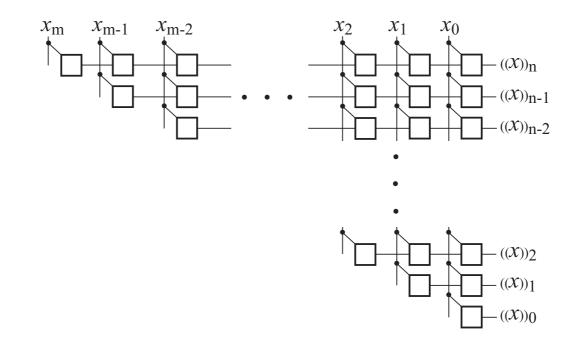

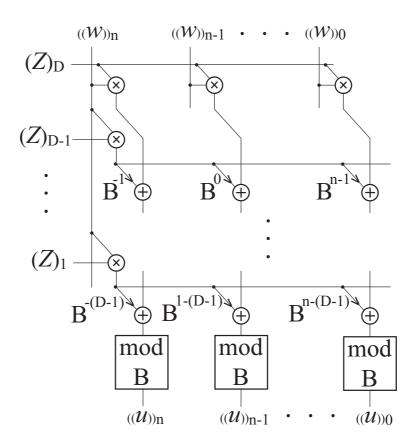

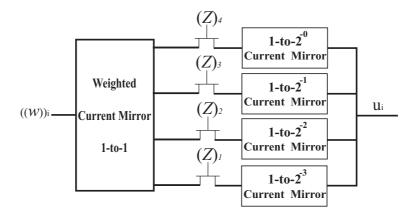

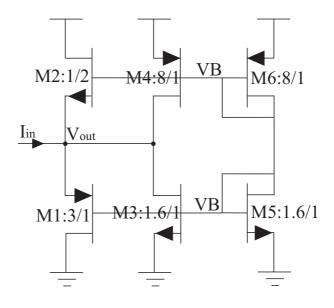

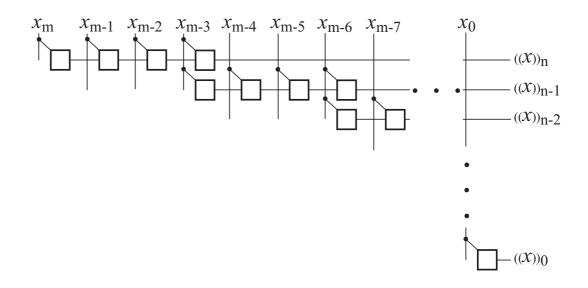

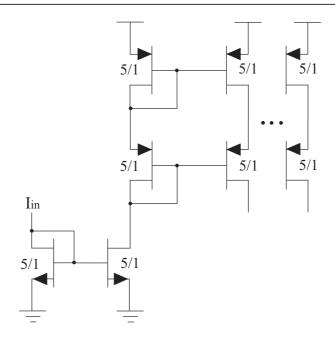

By eliminating mod2 operation in digit generation, this pre-congruent relation reduces the number of required gates for system implementation. According to the expression given by the equation (1.3), the CVNS digit generation directly from the binary digits can be realized employing simple weighted current mode mirrors. A block diagram representation of equation (1.3) is shown in Figure 1.1, where squares show the weighted sum operation units.

Figure 1.1: Block diagram of the CVNS digit generation from binary digits.

Table 1.1 shows the first five CVNS digits,  $((x))_i$ , of an arbitrary chosen value in radix-10 with maximum level of redundancy. Here, the original value is 89.0537412.

Table 1.1: An example for radix-10 CVNS digits

| $((x))_n$  | $((x))_{n-1}$ | $((x))_{n-2}$ | $((x))_{n-3}$ | $((x))_{n-4}$ |

|------------|---------------|---------------|---------------|---------------|

| 8.90537412 | 9.0537412     | 0.537412      | 5.37412       | 3.7412        |

In Table 1.1, {8} appears only in the first CVNS digit, {9} is repeated in only first two CVNS digits while {3,7,4,1,2} are repeated in first five CVNS digits. In other words, in a CVNS digit set, lower index CVNS digits can be rebuilt from higher index CVNS digits  $(((x))_{n-3} = (((x))_{n-2} \times 10) \mod 10 = (((x))_{n-1} \times 10^2) \mod 10 = (((x))_n \times 10^3) \mod 10).$ Also, lower index CVNS digits can help in recovering the higher index ones  $(((x))_n =$  $8 + ((x))_{n-1}/10 = 8.9 + ((x))_{n-2}/10^2).$  The CVNS representation also offers some degrees of freedom in selecting some representation dimensions such as the level of information overlap between the digits and the number of the required CVNS digits according to design demands. The CVNS digit generation is limited by the resolution of the environment. Therefore, truncation methods are applied to the CVNS digits to make them cope with lower resolution environments while still keeping the CVNS properties [14, 15]. One of the advantages of applying these methods is reducing the area consumption; however, it may result in lower accuracy as well.

Consequently, the CVNS digits have information overlap with each other; every digit has some level of knowledge about the digits with lower indices in the same set. This digit level redundancy is used to detect and correct errors in the digit set which makes the system more robust against the noise. The proposed CVNS DNN has all the advantages of using DNNs; furthermore, it results in a reduced NSR for the network compared to conventional DNNs. This makes the CVNS DNNS a great candidate for hardware implementations.

The CVNS can be implemented through current-mode analog circuitries which generally provide lower noise, lower voltage swing, and the ability of working with lower power supply voltages [21–23]. Nevertheless, some functions such as addition can be easily realized through current-mode circuitries.

In this work, a current-mode synapse-neuron module is designed based on the CVNS which can be used as the building block for a wide variety of applications. The synapse-neuron module decreases the design cost and increases the fan-out [3]. The weights to this module are considered to be equal to 13 bits. Truncated CVNS digits equivalent to weights are generated and stored in multi-valued DRAMs with the ability of error correction [14, 15]. These memories can store up to 16-level equivalent to 4-bit on each storage cell.

Each two adjacent CVNS digits, in the proposed DRAM, has equivalent to one binary digit overlap; this common digit is used for error correction in the system. This configuration provides a novel multi-valued DRAM with increased noise margin and reduced area. A fast Analog to Digital Converter (ADC) [24] is proposed for the refreshing circuitry. This ADC has a parallel configuration and can convert two bits simultaneously. It can reduce the overall delay of the refreshing circuitry.

The proposed DRAM has to be refreshed continuously; the voltage over the storing capacitor drops after a while due to the leakage currents of the storage cell. During the refreshing cycle, the storage capacitor is charged to the correct value indicated by the error correction codes.

Except for the multi-valued memory, the proposed synapse-neuron module contains multiplication module, interface module, and sub-neuron. The multiplication module multiplies the truncated CVNS digits by the input. A voltage-mode Analog to Digital Converter (ADC) extracts the digits of the input for the sake of multiplication. The inputs are converted to a 4-bit value and are applied as multipliers to the multiplication modules.

Sign, the 13<sup>th</sup> bit of the weight, is applied to the multiplier output in the interface module releasing the final synapse output which goes to a Common Node (CN). CN is common between all the synapse-neuron modules in a layer and acts as an input/output node. In this node, currents from synapses are added up together and divided by the number of sub-neurons. Accordingly, all the sub-neurons receive an identical current. Each sub-neuron in the synapse-neuron module decides the output value based on this current.

The sigmoid function is selected as the activation function which always has a value between 0 and 1. A new analog resistive-type neuron is designed which generates the sigmoid function based on the transistor characteristics in both triode and saturation regions.

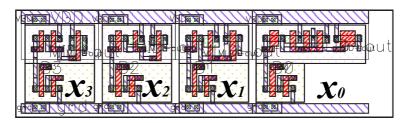

To justify the design concept, the proposed synapse-neuron modules are used to design a prototype 4-3-2 network with four digital inputs and two final digital outputs. This prototype is trained off-line based on a classification pattern. The circuitries are designed, simulated, and laid out in  $0.18\mu m$  TSMC CMOS technology [25] using a power supply voltage of 1.8V.

### **1.1 Summary of Contributions**

In this dissertation, a new family of the CVNS DNNs are introduced. The scalability and noise immunity of the proposal are studied and compared to the lumped and conventional distributed networks. Studies show that it outperforms the previous structures because of its low NSR.

The proposed CVNS DNN is implemented considering the environmental resolution limitations which is equal to 4-bit in the employed technology. Multi-valued DRAMs with error correction abilities are designed to convert and store the weights in the form of the CVNS digits. The proposed multi-valued memories are a significant progress in this field because of their lower area and power consumption as well as lower refreshing cycle time.

A 4-3-2 network is designed, laid out, and trained off-line based on a pattern set. The post-layout simulations are performed which show the proper functionality of the design.

### **1.2** Outline of the Thesis

The next chapters are organized as follows. In Chapter 2, the structures of a typical lumped ANN and a conventional DNN are shown and the proposed CVNS DNN structure is introduced. It also studies the scalability in the proposed DNN, and shows how the CVNS DNN is used to solve an XOR problem. Designing CVNS fully distributed neural network according to the CVNS DNN is discussed. A Stochastic NSR model is used, and NSR of different sigmoidal Adalines are compared together.

Chapter 3 presents the environmental limitations for implementation of the proposed CVNS DNN. Truncated methods are used to cope with these limitations. The effect of truncation on the performance and noise immunity are studied. Simulations show that the truncated CVNS DNN still has lower NSR compared to the lumped and conventional distributed neural networks.

The synapse-neuron module is presented in Chapter 4. The sub-modules of each synapse-

neuron module are the storage module, multiplication module, interface module, and subneuron. For each sub-module, the task and circuitries are discussed. The synapse-neuron module is designed in current-mode. There is also a voltage-mode ADC to convert the output of each layer to 4 bits that can be used as the input to the next layer.

The proposed current-mode multi-valued CVNS DRAM is introduced in detail in Chapter 5. In this chapter, the CVNS is described and the truncated CVNS is introduced in detail. Sub-modules of the CVNS DRAM and their circuitries are presented. The proposed DRAM is using a series combination of ADC and DACs for conversion, storage, and correction. A fast current-mode ADC method is proposed and compared to current-mode ADC methods in literature. A method for decreasing the refresh rate is also proposed. Error correction in this DRAM is discussed based on the CVNS features. Finally, the proposed memory is compared to current-mode memories in literature.

In chapter 6, a prototype 4-3-2 network is designed. This network is trained based on a pattern set to solve a classification problem. The weights and biases are calculated in MATLAB and used for post-layout simulations. The final layout and post-layout simulation results are also shown in this chapter. The circuitries are designed in  $0.18\mu m$  TSMC CMOS technology.

Finally, concluding remarks and future work are presented in Chapter 7.

## Chapter 2

## **CVNS Distributed Neural Network**

In this chapter, a new family of resistive-type feed-forward distributed neural networks is proposed based on the CVNS. The proposed CVNS DNN is used for off-line training of a prototype XOR. A stochastic model is employed to formulate NSR of a sigmoidal Adaline based on the proposed CVNS DNN. This is compared to the NSR of sigmoidal Adalines based on other comparable structures. A fully distributed neural network is designed based on the proposed CVNS DNN which can provide even lower level of NSR in the network while using more neurons. The reduced sensitivity to noise property of the proposed structures makes them robust against process variations; hence, they are potential candidates for hardware applications such as industrial sensors.

### 2.1 **Previous Structures of Resistive-Type ANNs**

In resistive-type ANNs, the neuron function is realized by a nonlinear load that receives current from the synapses in a general node and generates a corresponding voltage at the same node [3,9,10].

Although numerous designs of neural networks have been reported, in this chapter, the basic structure of resistive-type feed-forward neural networks is categorized into two main groups: lumped and distributed neural networks.

#### 2.1.1 Lumped Neural Network

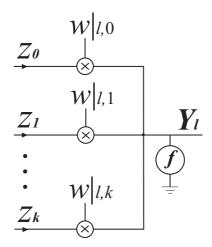

Lumped ANN is the original structure of neural networks in which all synapses are connected to one neuron in each layer. The block diagram of a (k + 1)-input resistive-type lumped ANN for the  $l^{th}$  layer is shown in Figure 2.1. Each input is multiplied by a synaptic weight. All of the multiplication results are added up together in a common node, and the result goes to an activation function to generate the final output.

Figure 2.1: (k + 1)-input resistive-type lumped neural network.

The output of the neuron,  $Y_l$ , is generated through the following equation.

$$Y_l = f(\sum_{t=0}^k Z_t \times w | l, t)$$

(2.1)

where  $Z_t$  shows the  $t^{th}$  input, and w|l, t shows its corresponding synaptic weight. Activation function is represented by f.

#### 2.1.2 Conventional Distributed Neural Network

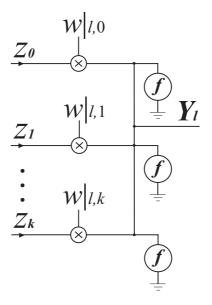

Resistive-type DNNs provide one neuron for each synapse. The block diagram of a (k+1)input resistive-type DNN [3,9,10] is shown in Figure 2.2.

Here, instead of one neuron, sub-neurons are used to realize the activation function. The input and weight multiplication results are added up together. The result is divided by the number of sub-neurons so that each sub-neuron receives the same amount of current. It should be noted that in each layer, all the sub-neurons have the same activation function. The output of such a network is calculated as follows.

$$Y_{l} = f(\frac{1}{k+1} \sum_{t=0}^{k} Z_{t} \times w | l, t)$$

(2.2)

Figure 2.2: Block diagram of a (k + 1)-input resistive-type DNN.

As there is one sub-neuron corresponding to each input, the number of sub-neurons changes by the number of inputs. This self-scaling property of the DNN causes an increase or a decrease in the dynamic input range of the activation function as the number of inputs increases or decreases, respectively. The scalability feature of DNNs is used to build a new family of neural networks as is discussed next.

#### 2.2 CVNS Distributed Neural Network

The proposed network is a distributed neural network in which weights are stored as CVNS digits. A family of CVNS neural networks was introduced in [20] where the output was generated from a Reverse Evolution (RE) unit using complicated sub-functions. In the proposed network, the design is modified to avoid RE and sub-functions which decreases the network complexity and makes it more suitable for practical hardware implementations.

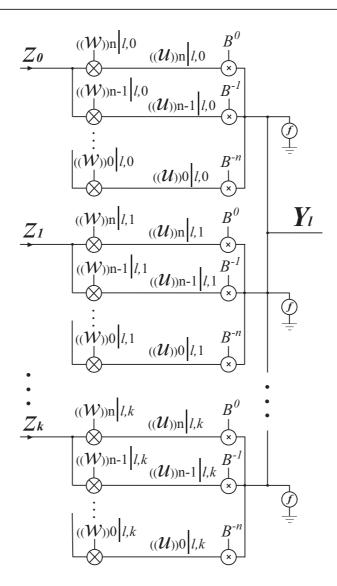

Figure 2.3 shows the proposed (k + 1)-input resistive-type CVNS DNN configuration for the  $l^{th}$  layer.

In Figure 2.3,  $((w))_{n-j|l,t}$  (j = 0, 1, ..., n and t = 0, 1, ..., k) stands for the CVNS presentation of weights which are generated through the following equation.

$$((w))_{n-j}|_{l,t} = (\frac{w_t}{M} * B^{j+1}) \mod B \ j = 0, 1, ..., n$$

(2.3)

where  $w_t$  stands for the value of the weight corresponding to the  $t^{th}$  input, M is the maximum acceptable value of weights, and B is the CVNS radix.

In a CVNS digit set, digits with higher indices have information overlap with the lower index digits. For example the equivalent CVNS digits of the randomly chosen value of  $w_t = 31.89$  for M = 100 and B = 10 are  $((w))_3 = 3.189$ ,  $((w))_2 = 1.89$ ,  $((w))_1 = 8.9$ ,  $((w))_0 = 9$ . These CVNS digits can be shown in a CVNS digit set as  $\{3.189, 1.89, 8.9, 9\}$ .

The CVNS multiplication [13] of  $Z_t$  (t = 0, 1, ..., k) and  $((w))_{n-j}$  (j = 0, 1, ..., n) is calculated as follows.

First, the digits of the multiplier,  $(Z)_{D-d}$ , are extracted as is shown in the following equation.

$$(Z)_{D-d} = (Z_t \times B^d) \mod B - \frac{(Z_t \times B^{d+1}) \mod B}{B}$$

(2.4)

where D shows the number of digits of  $Z_t$  and d = 0, 1, ..., D - 1.

In the next step, the CVNS multiplication result,  $((u))_{n-j}$ , is calculated through the

Figure 2.3: Proposed resistive-type CVNS DNN configuration.

following equation. The block diagram representation is shown in Figure 2.4.

$$\begin{aligned} ((u))_{n-j} &= Z \bigotimes ((w))_{n-j} \\ &= \{(Z)_D \times ((w))_{n-j} \\ &+ \sum_{i=1}^{D-1} (Z)_{D-i} \times ((w))_n \times B^{j-i} \} mod B \end{aligned}$$

(2.5)

Case study 1: In a high resolution environment, the CVNS multiplication result for a

Figure 2.4: Block diagram representation of the CVNS multiplication (equation (2.5)).

multiplier of  $Z_t = 2.14$  (digits are [2, 1, 4]) and a CVNS digit set multiplicand of  $\{3.189, 1.89, 8.9, 9\}$  with B = 10 is as follows:

$$\begin{aligned} &((u))_3 &= \{2 \times 3.189 + 1 \times 3.189 \times 10^{-1} + 4 \times 3.189 \times 10^{-2}\} mod \ 10 = 6.82446 \\ &((u))_2 &= \{2 \times 1.89 + 1 \times 3.189 \times 10^0 + 4 \times 3.189 \times 10^{-1}\} mod \ 10 = 8.2446 \\ &((u))_1 &= \{2 \times 8.9 + 1 \times 3.189 \times 10^1 + 4 \times 3.189 \times 10^0\} mod \ 10 = 2.446 \\ &((u))_0 &= \{2 \times 9.0 + 1 \times 3.189 \times 10^2 + 4 \times 3.189 \times 10^1\} mod \ 10 = 4.46 \end{aligned}$$

Digits in the multiplication output set, {6.82446, 8.2446, 2.446, 4.46}, are CVNS digits as they fit in the following equation which shows the relation between digits in a CVNS

digit set.

$$(((x))_{n-j} \times B) \mod B = ((x))_{n-j-1} \quad j = 0, 1, ..., n$$

(2.6)

As it is shown in equation (2.6), there is a redundancy between the CVNS digits. Lower index CVNS digits can be calculated from the higher index digits; however, the process can not be reversed. In other words, the higher the index of a CVNS digit is, the higher the level of its information will be. However, to add the CVNS digits together, they have to be of the same information level. To meet this requirement,  $((u))_{n-j}|_{l,t}$  is multiplied by  $B^{-j}$ (j = 0, 1, ..., n) in Figure 2.3.

In Figure 2.3, the total output of the CVNS DNN is calculated as  $Y_l = f(y)$  where y is generated from the CVNS multiplication outputs as follows.

$$y = \frac{1}{k+1} \{ ((u))_n |_{l,0} + \frac{((u))_{n-1} |_{l,0}}{B} + \dots + \frac{((u))_0 |_{l,0}}{B^n} + ((u))_n |_{l,1} + \frac{((u))_{n-1} |_{l,1}}{B} + \dots + \frac{((u))_0 |_{l,1}}{B^n} + \dots + ((u))_n |_{l,k} + \frac{((u))_{n-1} |_{l,k}}{B} + \dots + \frac{((u))_0 |_{l,k}}{B^n} \}$$

$$(2.7)$$

From the CVNS features, it can be observed that CVNS addition of different CVNS digit sets results in CVNS digits as well. The following example shows the CVNS addition of four randomly chosen CVNS digit sets:  $\{2.345, 3.45, 4.5, 5\}$ ,  $\{7.891, 8.91, 9.1, 1\}$ ,  $\{3.042, 0.42, 4.2, 2\}$ , and  $\{9.157, 1.57, 5.7, 7\}$ .

$$(2.345 + 7.891 + 3.042 + 9.157)mod10 = 2.435$$

$$(3.45 + 8.91 + 0.42 + 1.57)mod10 = 4.35$$

$$(4.5 + 9.1 + 4.2 + 5.7)mod10 = 3.5$$

$$(5 + 1 + 2 + 7)mod10 = 5$$

The output digit set is a CVNS digit set according to equation (2.6).

In equation (2.7), the CVNS digits with the same index can be added up together as follows.

$$(((u))_{n-j}|_{l,0} + ((u))_{n-j}|_{l,1} + \dots + ((u))_{n-j}|_{l,k}) \mod B = ((y))_{n-j}|_l$$

(2.8)

It should be noted that  $A = A \mod B + I \times B$  where I shows the quotient of A divided by B. Therefore, equation (2.8) can be rewritten as the following equation.

$$((u))_{n-j}|_{l,0} + ((u))_{n-j}|_{l,1} + \dots + ((u))_{n-j}|_{l,k} = ((y))_{n-j}|_{l} + I_{n-j} \times B$$

(2.9)

According to equation (2.9), equation (2.7) can be represented as follows.

$$y = \frac{1}{k+1} \{ ((y))_n |_l + \frac{((y))_{n-1} |_l}{B} + \dots + \frac{((y))_0 |_l}{B^n} + Cons \}$$

(2.10)

where *Cons* is equal to  $\sum_{j=0}^{n} \frac{I_{n-j} \times B}{B^{j}}$ .

#### 2.2.1 Scalability

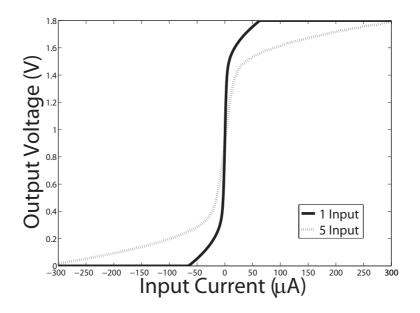

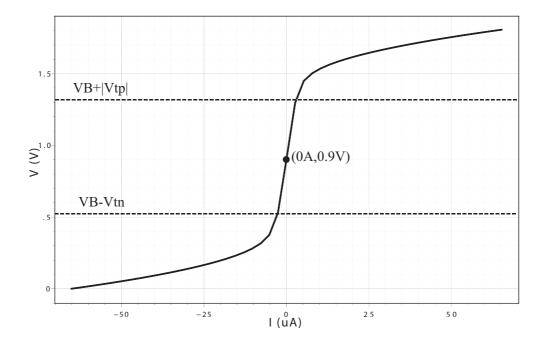

For studying the self-scaling property of the proposed DNN, the value of the total current entering the sub-neurons,  $y \times (k + 1)$ , is considered to be between  $-60\mu A$  and  $60\mu A$  for 1-input (k = 0). Consequently for 5-input (k = 4), the corresponding current,  $y \times (5)$ , will be in the range of  $-300\mu A$  and  $300\mu A$ . Self-scaling property of the proposed DNN is shown in Figure 2.5 where it compares the output for networks with 1 and 5 inputs together for a sigmoidal activation function.

As is shown in Figure 2.5, the network is properly stretching the dynamic range to cope with the increased number of inputs. Note that without a proper scaling, the output of 5-input case will be equal to 0V for all inputs in the range of  $[-300\mu A, -60\mu A]$  and will be 1.8V for inputs in the range of  $[60\mu A, 300\mu A]$ .

#### 2.2.2 2-2-1 XOR

The proposed CVNS DNN is used to build a prototype 2-2-1 XOR as is shown in Figure 2.6.

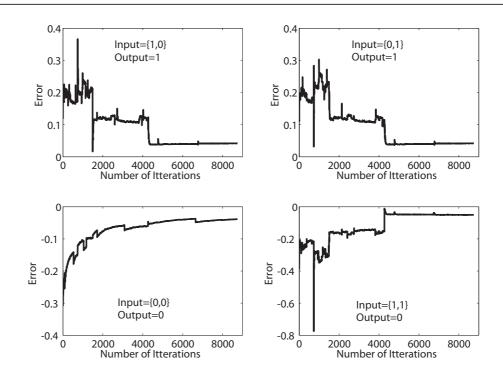

Here, B is chosen equal to 10, sigmoid function is chosen as the activation function, and n is selected equal to 5. The network is trained off-line using the back propagation algorithm [5, 26], and weights are calculated while the biases are considered to be zero.

Figure 2.5: Scalability of the proposed DNN for a sigmoidal activation function.

The training result is shown in Figure 2.7. Random sets of weights are selected for initialization. The error from the ideal value is less than 0.05 (5.0%) for all input combinations.

#### 2.3 CVNS Fully Distributed Neural network

Based on the proposed CVNS DNN, a Fully Distributed Neural Network (FDNN) is introduced. In this fully distributed CVNS network, the number of neurons depends not only on the number of inputs, k + 1, but also on the number of the CVNS digits in each CVNS digit set of weights, n + 1.

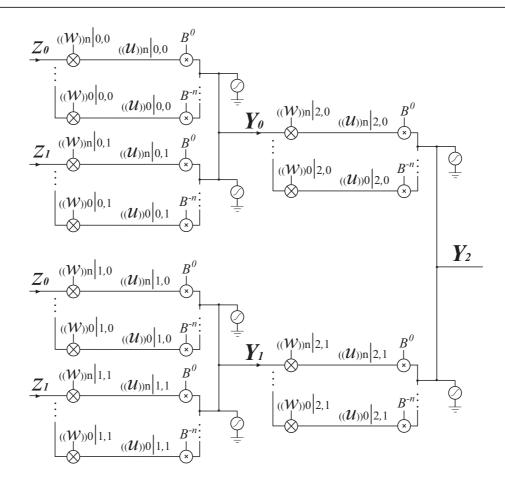

The block diagram of the proposed CVNS FDNN with (k+1)-input is shown in Figure 2.8.

The output is  $Y_l = f(y)$ , where y is calculated using the following equation.

$$y = \frac{1}{(k+1)(n+1)} \{ ((y))_n |_l + \frac{((y))_{n-1}|_l}{B} + \dots + \frac{((y))_0|_l}{B^n} + Cons \}$$

(2.11)

Figure 2.6: Block diagram of the 2 - 2 - 1 XOR network.

Although this network benefits from the feature of scalability, the number of neurons in this design is more than that of the CVNS DNN. Adding one input to the network will result in a n + 1 increase in the number of neurons. Sensitivity of the proposed structures to the noise is studied by calculating the NSR in the next section.

### 2.4 Stochastic Model

A stochastic model based on the one presented in [11] is used in this section to find the NSR of different sigmoidal Adalines and to compare them together.

Figure 2.7: Off-line network training by back propagation algorithm.

According to this model, NSR of a (k+1)-input sigmoidal Adaline with lumped neuron is as follows [11].

$$NSR_{Lumped} = g(\sqrt{k+1}\sigma_Z\sigma_w) \times \left(\frac{\sigma_{\Delta Z}^2}{\sigma_Z^2} + \frac{\sigma_{\Delta w}^2}{\sigma_w^2}\right)$$

(2.12)

where g is the stochastic gain function,  $\Delta Z$  and  $\Delta w$  show input error and weight error, respectively.  $\sigma$  stands for the standard deviation, and  $\sigma^2$  is the variance.

In a DNN, the effect of each weight is divided by the number of inputs:  $\sigma_{w_{DNN}} = \frac{\sigma_w}{k+1}$ ,  $\sigma_{w_{DNN}}^2 = \frac{\sigma_w^2}{(k+1)^2}$ , and  $\Delta w_{DNN} = \frac{\Delta w}{k+1}$ . Therefore, NSR of a sigmoidal Adaline with distributed neuron is calculated as follows [9].

$$NSR_{DNN} = g(\sqrt{k+1}\sigma_Z \frac{\sigma_w}{k+1}) \times (\frac{\sigma_{\Delta Z}^2}{\sigma_Z^2} + \frac{\sigma_{\Delta w}^2/(k+1)^2}{\sigma_w^2/(k+1)^2})$$

$$= g(\frac{\sigma_Z \sigma_w}{\sqrt{k+1}}) \times (\frac{\sigma_{\Delta Z}^2}{\sigma_Z^2} + \frac{\sigma_{\Delta w}^2}{\sigma_w^2})$$

(2.13)

In a CVNS network, weights are CVNS digits with digit level redundancy. An error in

Figure 2.8: (k + 1)-input resistive-type CVNS fully distributed neural network.

a CVNS digit is corrected in the CVNS generation module except for the error in the digit with the lowest index [13]. Therefore, the only weight vulnerable to error is  $((w))_0$  which has an effect of  $((w))_n/B^n$ .  $((w))_n$  has the highest level of information in the CVNS digit set. Accordingly, equation (2.14) is proposed to calculate NSR of a sigmoidal Adaline with a CVNS DNN structure. Note that the effect of each weight is still divided by the number of inputs because of its distributed nature.

$$NSR_{CVNS-DNN} = g\left(\frac{\sigma_Z \sigma_{((w))_n}}{B^n \sqrt{k+1}}\right) \times \left(\frac{\sigma_{\Delta Z}^2}{\sigma_Z^2} + \frac{\sigma_{\Delta((w))_n}^2}{\sigma_{((w))_n}^2}\right)$$

(2.14)

The NSR of a sigmoidal Adaline with a CVNS fully distributed structure is similar to the NSR of a sigmoidal Adaline with the CVNS DNN structure except for the fact that effect of each weight is also decreased by the number of CVNS digits.

$$NSR_{CVNS-FDNN} = g\left(\frac{\sigma_Z \sigma_{(\!(w)\!)_n}}{B^n \sqrt{k+1}(n+1)}\right) \times \left(\frac{\sigma_{\Delta Z}^2}{\sigma_Z^2} + \frac{\sigma_{\Delta(\!(w)\!)_n}^2}{\sigma_{(\!(w)\!)_n}^2}\right)$$

(2.15)

*Case study* 2: For a sigmoidal Adaline with k + 1 = 9, considering both inputs and weights uniformly distributed in the range of [-10, 10], input and weight variances will be  $\sigma_Z^2 = \sigma_w^2 = \sigma_{((w))n}^2 = \frac{20^2}{12}$ . Weight error variance for a 12-bit quantization scheme is  $\sigma_{\Delta w}^2 = \sigma_{\Delta((w))n}^2 = \frac{(20/2^{12})^2}{12}$ . Note that  $20/2^{12}$  is the equivalent space between levels. Input error variance,  $\sigma_{\Delta Z}^2$  is considered to be zero as the aim is to study the effect of noise introduced to weights on the networks.

NSR of the four considered sigmoidal Adalines is calculated as shown in Table 2.1. For the CVNS networks, B and n + 1 are assumed to be 2 and 3, respectively.

| Structure  | NSR                               | Improvement |  |

|------------|-----------------------------------|-------------|--|

| Lumped ANN | $3.21 \times 10^{-6} = -54.94 dB$ | _           |  |

| DNN        | $3.84 \times 10^{-7} = -64.16 dB$ | 16.78%      |  |

| CVNS DNN   | $1.2 \times 10^{-7} = -69.2 dB$   | 25.95%      |  |

| CVNS FDNN  | $6 \times 10^{-8} = -72.22 dB$    | 31.45%      |  |

Table 2.1: NSR of sigmoidal Adalines from case study 2

According to equations (2.12), (2.13), (2.14), and (2.15), as the number of inputs

changes, stochastic gain function will change. Stochastic gain function, g, of all four networks are compared together for an input range of [9, 25]. The comparison result is shown in Figure 2.9 where  $\sigma_Z \sigma_w = \sigma_Z \sigma_{((w))_n}$  is a constant value, B = 2, and n + 1 = 3. It should be noted that g(X) is almost equal to 1 for X < 2 and can be estimated by the following equation for X > 2 [9].

$$g(X) = 0.5 + 0.53 \times X \tag{2.16}$$

From Figure 2.9(a), stochastic gain function of the DNN, Proposed 1 (CVNS DNN), and Proposed 2 (CVNS FDNN) are almost half, one forth, and one twelfth of that of the lumped ANN, respectively. Stochastic gain function of the lumped neuron is greatest among all, and it increases by the number of inputs. Larger stochastic gain function will result in a larger NSR, Figure 2.9(b). Lumped neurons should be redesigned as the number of inputs increases to keep the NSR lower. The other three networks, because of their distributed neurons, can cope with an increase in the number of inputs which will also decrease the NSR gradually.

The NSR of a sigmoidal Madeline is calculated similarly to that of a sigmoidal Adaline by considering the effect of NSR of each layer on the next layer. Figure 2.9(c) and Figure 2.9(d) compare the NSR of Madalines with five and ten sigmoidal Adalines of *Case study* 2, respectively. Although the NSR of each layer is slightly bigger than the NSR of the previous layer, the proposed structures result in a smaller total NSR for the Madaline.

The number of CVNS digits is another variable in the proposed networks which can decrease the NSR. By increasing the number of CVNS digits,  $B^n$  becomes larger resulting in a smaller stochastic gain function. In the fully distributed neural network, increasing the number of CVNS digits also increases the n + 1 factor, which decreases the NSR even more; however, it causes an increase in the number of sub-neurons.

According to Figure 2.9, practical implementation of the lumped neural network looks impossible as the number of layers increases. However, the distributed configurations still look promising for hardware implementations of networks with up to 10 layers.

Figure 2.9: Comparison for input range of [9, 25]: (a) Stochastic Gain Function for Adaline, NSR for (b) Adaline, (c) 5-layer Madaline, (d) 10-layer Madaline.

### 2.5 Comparison

Applying equation (2.16) in the NSR calculation of lumped sigmoidal Adaline, equation (2.12), the NSR of the lumped sigmoidal Adaline can be rewritten as follows.

$$NSR_{Lumped} = (0.5 + 0.53\sqrt{k+1}\sigma_Z\sigma_w) \times \left(\frac{\sigma_{\Delta Z}^2}{\sigma_Z^2} + \frac{\sigma_{\Delta w}^2}{\sigma_w^2}\right)$$

$$= (0.5 + 0.53R)D \approx RD$$

(2.17)

where R and D stand for  $\sqrt{k+1}\sigma_Z\sigma_w$  and  $\frac{\sigma_{\Delta Z}^2}{\sigma_Z^2} + \frac{\sigma_{\Delta w}^2}{\sigma_w^2}$ , respectively. This approximation is correct specially for a large number of inputs.

Accordingly, the NSR of the other three sigmoidal Adalines are approximated in Table 2.2. The number of CVNS digits is equal to n + 1 when applicable.

| NN<br>Structure | Number of<br>Neurons | NSR                        | Neuron× NSR      |  |

|-----------------|----------------------|----------------------------|------------------|--|

| Lumped<br>ANN   | 1                    | RD                         | RD               |  |

| DNN             | k+1                  | $\frac{RD}{k+1}$           | RD               |  |

| CVNS<br>DNN     | k+1                  | $\frac{RD}{B^n(k+1)}$      | $\frac{RD}{B^n}$ |  |

| CVNS<br>FDNN    | (k+1)(n+1)           | $\frac{RD}{B^n(k+1)(n+1)}$ | $\frac{RD}{B^n}$ |  |

Table 2.2: Comparison of different sigmoidal Adalines for a k + 1 input

There is a tradeoff between the number of neurons and the value of NSR in distributed neural networks. To measure the overall efficiency of each network in Table 2.2, a comparison factor, Neuron $\times$ NSR, is defined which is the result of multiplying the number of neurons by NSR for each structure. It is shown that the proposed networks outperform the other two networks due to their smaller Neuron $\times$ NSR values.

#### 2.6 Conclusion

Two novel CVNS Distributed Neural Networks are proposed. They have the self-scaling property which can potentially decrease the noise to signal ratio. The NSR of the proposed

structures are compared to those of lumped neural networks and conventional distributed neural networks. It is shown that significant improvements are attained specially as the number of inputs increases. The proposed CVNS DNN can defeat both lumped ANN and conventional DNN with its low NSR while it uses the same number of neurons as the latter one does.

# Chapter 3

# Truncated CVNS Distributed Neural Network

the CVNS has been used to build a new family of distributed neural networks [16] where it is used in a high resolution environment. The CVNS DNN was shown to provide a NSR lower than that of the conventional DNNs. However, practical implementation of the CVNS systems is limited by the resolution of the environment. For example, a CVNS digit which is extracted from 12 binary bits needs at least a reliable 12-bit resolution for hardware implementation, which is not the case in generally using technologies.

Truncation methods are applied to the CVNS digits to make them cope with lower resolution environments while still keeping the CVNS properties such as the redundancy between digits [14, 15]. One of the advantages of applying these methods is reducing the area consumption; however, it may result in lower accuracy as well.

Here, the CVNS DNN is studied according to the environmental considerations. The resolution is limited by the  $0.18\mu m$  CMOS technology characteristics. Studies are per-

formed on the accuracy and the NSR of the proposed truncated CVNS DNN for an environment with the reliable resolution of 4-bit. Studies show that the NSR is higher than the NSR of the complete CVNS DNNs, as expected; however, it is still less than that of the conventional DNNs.

#### **3.1 Truncated CVNS DNN**

The acceptable resolution for  $0.18\mu m$  CMOS technology using a power supply voltage of 1.8V is considered to be 4-bit [15]. As a result, all arithmetic operations are assumed to be correct up to 4 bits, and additional values may need to be checked and corrected.

The first truncation is applied to the number of bits which are used to generate each CVNS digit. This number of bits is called group length and is selected as 4 for the sake of the practical resolution. In other words, in this work, each CVNS digit is generated from up to 4 bits.

Another flexible parameter in the CVNS digit sets is called digit link which is the number of common bits used to generate the CVNS digits. Keeping the digit link in its maximum means that the number of the CVNS digits and the binary digits are exactly the same when the radices are equal as is shown in equation (3.1); there will be 13 CVNS digits equivalent to 13 bits. This will increase the number of partial multiplications and additions and consequently the complexity of the system.

$$((w))_{n-j}|_{l,t} = \sum_{i=0}^{m-j} w_i \cdot 2^{i+j-m}, \ j = 0, 1, ..., n$$

(3.1)

To overcome this problem, digit link is decreased to its minimum which is equal to 1. This reduces the redundancy as well as the noise immunity of the digits. However, a proper design of the CVNS generation module will suppress this problem; error correction is generally performed over digits in a CVNS generation module [13].

The following equation shows the CVNS digit generation from binary digits with group

length of 4 and digit link of 1 [15].

$$((w))_{n-j} = \sum_{i=m-j(4-1)-4+1}^{m-j(4-1)} w_i \cdot 2^{i+j(4-1)-m}, \ j = 0, 1, ..., n$$

(3.2)

where  $w_i$  shows the  $i^{th}$  bit in binary representation.

There is a relation between the number of binary digits, m + 1, and the number of the CVNS digits, n + 1, as follows.

$$n+1 = R(\frac{m+1}{group \, length - digit \, link}) \tag{3.3}$$

where R is the classical Rounding function.

Using the CVNS digit set generated from equation (3.2) as the multiplicand, the CVNS multiplication equation is no longer applicable. This equation needs the maximum link between digits as well as the maximum group length to be adjusted.

A new method is proposed to perform the multiplication over the truncated CVNS digits. Here, the proposed multiplication method is particularized for a case that the multiplicand is a CVNS digit set with 4 CVNS digits,  $((x))_i$  (i = 3, ..., 0), and the multiplier has 4 bits,  $(Z)_i$  (i = 4, ..., 1). The radix of the CVNS system is equal to 2.

First, four partial results,  $y_i$  (i = 3, ..., 0), are generated.

$$y_{3} = ((w))_{3} \times \sum_{i=4}^{1} (Z)_{i} 2^{i-4}$$

$$y_{2} = (((w))_{2} \mod 1) \times \sum_{i=4}^{1} (Z)_{i} 2^{i-4}$$

$$y_{1} = (((w))_{1} \mod 1) \times \sum_{i=4}^{1} (Z)_{i} 2^{i-4}$$

$$y_{0} = (((w))_{0} \mod 1) \times \sum_{i=4}^{1} (Z)_{i} 2^{i-4}$$

(3.4)

The mod1 shows the modulo 1 operation and is applied as there is 1 digit link between the CVNS digits. This operation omits the effect of the first binary digit, digit link, in  $y_2$ ,  $y_1$ , and  $y_0$ ; therefore, it prevents the double effect of the common digit in the final result. It should be noted that finally the partial results are added up together to generate the final synapse output.

Note that the partial results are not in the CVNS form as there is no longer any overlap between them; they are just continuous values equivalent to 8 bits.

There is one total output for the synapse; thus, these partial results are scaled and added up together as follows.

$$y = ((y_0 \times 2^{-3} + y_1) \times 2^{-3} + y_2) \times 2^{-3} + y_3$$

(3.5)

However, there are some practical limitations applied to equations (3.4) and (3.5) because of the resolution of the environment. These are discussed through the following case study.

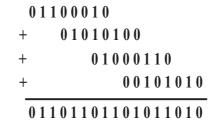

*Case study 1*: The randomly chosen value for multiplicand is '0111, 1101, 0101, 1', and the multiplier is chosen equal to '1110'. The CVNS digits for the multiplicand are extracted using equation (3.2): [0.875, 1.75, 0.625, 1.375]. The partial results are calculated through equation (3.4) as is shown in Table 3.1.

The first columns in Table 3.1 shows the partial results in a high resolution environment. The results in an environment with 4-bit resolution are shown in the second columns. They are rounded values of the previous column. Therefore, the classic Rounding function should be added for partial results extractions in equation (3.4) for hardware implementations.

The lower resolution environment also has an effect on equation (3.5). According to equation (3.5), the final output in the high resolution environment is found as shown in Figure 3.1 which is equal to '0110, 1101, 1010, 1101, 0', 6.8547 in decimal.

In a 4-bit resolution environment, the classic Rounding function should be added for each scaling addition in equation (3.5). Consequently, each 7-bit result will be rounded to a 4-bit equivalent result and be scaled for the next addition.

| High Resolution |                 | Low Resolution |                 |  |

|-----------------|-----------------|----------------|-----------------|--|

| Partial Result  | Equivalent Bits | Partial Result | Equivalent Bits |  |

| $y_3 = 1.53125$ | 0110,0010       | $y_3 = 0.75$   | 0110            |  |

| $y_2 = 1.3125$  | 0101,0100       | $y_2 = 0.625$  | 0101            |  |

| $y_1 = 1.09375$ | 0100,0110       | $y_1 = 0.5$    | 0100            |  |

| $y_0 = 0.65625$ | 0010, 1010      | $y_0 = 0.375$  | 0011            |  |

Table 3.1: Multiplication partial results for *case study 1*.

Figure 3.1: Final multiplication result in a high resolution environment.

Figure 3.2 shows the multiplication process in a 4-bit resolution environment. The result, '0111' (7 in decimal), is the rounded value of the result in Figure 3.1.

From Figure 3.2, the effect of the lower index digits is contributed to the highest index digits. Without this, the output would be only calculated from the first CVNS digit resulting in '0110' (6 in decimal) which is far from the right answer.

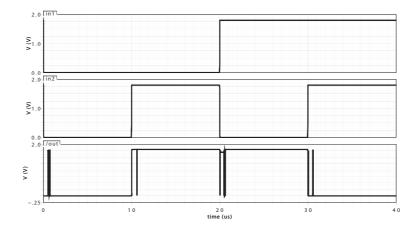

The proposed truncated CVNS DNN is used to build a 2 - 2 - 1 XOR with sigmoidal activation function. The simulation result is shown in Figure 3.3.

```

\begin{array}{c} 0\,1\,0\,0 \\ + & 0\,0\,1\,1 \\ \hline 0\,1\,0\,0\,0\,1\,1 & \longrightarrow 0\,1\,0\,0 & 0\,1\,0\,1 \\ + & 0\,1\,0\,0 \\ \hline 0\,1\,0\,1\,1\,0\,0 & \longrightarrow 0\,1\,1\,0 & 0\,1\,1\,0 \\ + & 0\,1\,1\,0 & \hline \\ 0\,1\,1\,0\,1\,1\,0 & \longrightarrow 0\,1\,1\,1 \end{array}

```

Figure 3.2: Final multiplication result in a low resolution environment.

Figure 3.3: Simulation result of an XOR based on the truncated CVNS DNN.

#### **3.2** Effect of Truncation on Performance

In this environment, with 4-bit resolution, each partial result can effect the next partial result as long as it has a value greater than '0100'. In other words, each partial result has a chance of  $P(y_i, y_{i+1}) = \frac{16-5}{16}$  which is equal to 69% to effect the next partial result. However, each partial result is added to the scaled previous partial result, and the result will be scaled to be added to the next partial result. Therefore, the previous partial result can increase the probability of the second and the third partial results to effect the final result. If the current partial result is '0100', the previous partial result can increase it to '0101'. The new probability of effecting the final result for the middle partial results is  $0.69 + 0.69 * \frac{1}{16} = 0.73$ .

Subsequently, the probability of each partial result for effecting the final answer,  $P(y_i, y)$ , is roughly estimated as follows.

$$P(y_3, y) = 1 = 100\%$$

$$P(y_2, y) = P(y_2, y_3) \times P(y_3, y) = 0.73 \times 1 = 0.73 = 73\%$$

$$P(y_1, y) = P(y_1, y_2) \times P(y_2, y) = 0.73 \times 0.73 = 0.53 = 53\%$$

$$P(y_0, y) = P(y_0, y_1) \times P(y_1, y) = 0.69 \times 0.53 = 0.37 = 37\%$$

Each multiplicand CVNS digit is multiplied by the multiplier generating a partial result equivalent to 8-bit rounded to 4-bit. The minimum value for the 8-bit result to be considered in the rounded result is equivalent to '0000, 1001'. Thus, the probability of the first CVNS digit not to affect the 4-bit partial result is as follows.

$$P(((w))_{3}, y_{3}) = P(0000, Z) + P(0000, ((w))_{3}) + P(0001, Z) \times [P(0001, ((w))_{3}) + P(0010, ((w))_{3}) + P(0011, ((w))_{3}) + P(0100, ((w))_{3})] + P(0010, Z) \times [P(0001, ((w))_{3}) + P(0010, ((w))_{3})] + P(0100, Z) \times P(0001, ((w))_{3}) + P(0100, Z) \times P(0001, ((w))_{3}) = \frac{1}{16} + \frac{1}{16} + \frac{1}{16} \times [\frac{4}{16}] + \frac{1}{16} \times [\frac{2}{16}] + \frac{1}{16} \times [\frac{1}{16}] + \frac{1}{16} \times [\frac{1}{16}] = 0.16 = 16\%$$

(3.6)

However, this is only correct for the first CVNS digit as there is a modulo operation for the others. This operation deletes the effect of the first bit making each CVNS digit equivalent to 3 bits. Therefore, all the  $\frac{1}{16}$  in the previous equation corresponding to the CVNS digits, should be changed to  $\frac{1}{8}$  for all the CVNS digits except for the first one. In this case,  $\overline{P(((w))_i, y_i)}$  for i = 2, 1, 0 would be equal to 25%.

According to equation (3.6), the probability of the first CVNS digit to affect the relevant partial result is  $P(((w))_3, y_3) = 1 - 0.14 = 0.86 = 86\%$  while this probability is equal to 75%

for the other CVNS digits. The probability of each CVNS digit to effect the final result is estimated through the following equations.

$$P(((w))_{3}, y) = P(((w))_{3}, y_{3}) \times P(y_{3}, y) = 86\%$$

$$P(((w))_{2}, y) = P(((w))_{2}, y_{2}) \times P(y_{2}, y) = 55\%$$

$$P(((w))_{1}, y) = P(((w))_{1}, y_{1}) \times P(y_{1}, y) = 40\%$$

$$P(((w))_{0}, y) = P(((w))_{0}, y_{0}) \times P(y_{0}, y) = 28\%$$

Consequently, the CVNS implementation in a low resolution environment provides a considerable probability to a high resolution value aiding the production of an accurate result.

#### **3.3 NSR Calculation**

Noise to signal ratio is a very important feature in neural networks which shows their immunity to noise and dictates the required resolution for synaptic weight implementations. Lower NSR makes the network less vulnerable to errors and violations and makes it more potential for hardware implementations.

The NSR of the proposed truncated CVNS DNN is calculated here for an Adaline. It is compared to Adalines with lumped, distributed, and complete CVNS distributed structures.

The NSR of a (k + 1)-input sigmoidal Adaline with lumped structure is calculated through a model based on the stochastic gain function, g, proposed by Piche [11].

$$NSR_{Lumped} = g(\sqrt{k+1}\sigma_Z\sigma_w) \times \left(\frac{\sigma_{\Delta Z}^2}{\sigma_Z^2} + \frac{\sigma_{\Delta w}^2}{\sigma_w^2}\right)$$

(3.7)

where  $\Delta Z$  shows input error and  $\Delta w$  stands for weight error.  $\sigma$  is the standard deviation, and  $\sigma^2$  is the variance.

Sub-neurons in a DNN cause a dividing in the effect of each weight:  $\sigma_{w_{DNN}} = \frac{\sigma_w}{k+1}$ ,  $\sigma_{w_{DNN}}^2 = \frac{\sigma_w^2}{(k+1)^2}$ , and  $\Delta w_{DNN} = \frac{\Delta w}{k+1}$ . Therefore, NSR of a sigmoidal Adaline with distributed

structure is calculated as follows.

$$NSR_{DNN} = g(\frac{\sigma_Z \sigma_w}{\sqrt{k+1}}) \times (\frac{\sigma_{\Delta Z}^2}{\sigma_Z^2} + \frac{\sigma_{\Delta w}^2}{\sigma_w^2})$$

(3.8)

In a CVNS digit generation module, the error in a CVNS digit is corrected using the redundancy between the digits. However, the lowest index digit is not subject to this error correction, and it is the only digit which might be corrupted with errors [13].  $((w))_0$ , as the lowest index digit, has an effect of  $((w))_n/B^n$  on the system where  $((w))_n$  is the digit with the highest level of information in the CVNS digit set. Note that  $((w))_0$  should be multiplied by  $B^n$  to be in the same order as  $((w))_n$  is.

Accordingly, the NSR of a sigmoidal Adaline with a complete CVNS DNN structure is calculated as follows.

$$NSR_{CVNS-DNN} = g\left(\frac{\sigma_Z \sigma_{(\!(w)\!)_n}}{B^n \sqrt{k+1}}\right) \times \left(\frac{\sigma_{\Delta Z}^2}{\sigma_Z^2} + \frac{\sigma_{\Delta(\!(w)\!)_n}^2}{\sigma_{(\!(w)\!)_n}^2}\right)$$

(3.9)

In the case of the proposed truncated CVNS DNN, the effect of each weight is still divided by the number of inputs due to the distribution of sub-neurons. The CVNS digits are also generated in the modules with error correction capabilities. However, the lowest index CVNS digit in a truncated digit set, has an effect of  $((w))_{nn}/B^{nn}$ . Here, the highest index is nn where  $nn + 1 = R(\frac{n+1}{group \ length - digit \ link})$  which is equal to  $R(\frac{n+1}{3})$  with group length of 4 and digit link of 1. The NSR will be calculated through the following equation.

$$NSR_{Truncated} = g\left(\frac{\sigma_Z \sigma_{(\!(w)\!)_{nn}}}{B^{nn}\sqrt{k+1}}\right) \times \left(\frac{\sigma_{\Delta Z}^2}{\sigma_Z^2} + \frac{\sigma_{\Delta(\!(w)\!)_{nn}}^2}{\sigma_{(\!(w)\!)_{nn}}^2}\right)$$

(3.10)

The NSR of the proposed truncated network is compared to that of other structures through the following case study.

*Case study* 2: NSR of all configurations are compared together for an input range of [1, 25], constant value for  $\sigma_Z \sigma_w = \sigma_Z \sigma_{((w))_n}$ , B = 2, and n+1 = 13 resulting in nn+1 = 4. The NSR is calculated for Adalines and 5-layer Madalines as is shown in Figure 3.4. In Madalines, NSR of each layer has an effect on NSR of the next layer. As is shown in in Figure 3.4, the NSR in lumped neural network is increasing as the number of inputs increases, and it is always less than the NSR of other structures. The other distributed structures are facing a decrease in NSR for higher number of inputs. The truncated CVNS DNN has an NSR larger than that of the complete CVNS DNN; however, its NSR is always less than the NSR of both lumped and conventional distributed neural networks. It should be noted that the number of interconnections and the CVNS weights in the truncated network are less than those numbers in the complete CVNS DNN compared to the complete one. Furthermore, it is completely practical for hardware implementations in an environment with low resolution of 4-bit. However, it should be noted that as the number of layers increases, the hardware implementation of the truncated structure looks impossible because of the high value of the NSR.

Figure 3.4: NSR comparisons for Adalines and 5-layer Madalines.

#### 3.4 Conclusion

The truncated CVNS distributed neural network is proposed which is adaptable for implementation in a low resolution environment. The proposed network is simulated in  $0.18 \mu m$ CMOS technology with 4-bit resolution where it shows a proper functionality. The NSR is calculated for Adaline and Madaline with the proposed truncated CVNS structures. The NSR calculations show that the truncated CVNS network surpasses both the lumped and conventional distributed structures.

# **Chapter 4**

## Synapse-Neuron Module

ANNs usually have two main parts: synapses and neurons. A synapse receives the input and multiplies it by the corresponding stored weights. The result goes into the neuron where the output value is generated from the input based on the activation function. In a distributed neural network, there is one sub-neuron for each synapse. Therefore, the synapse and its corresponding neuron can be merged together resulting in a synapse-neuron module.

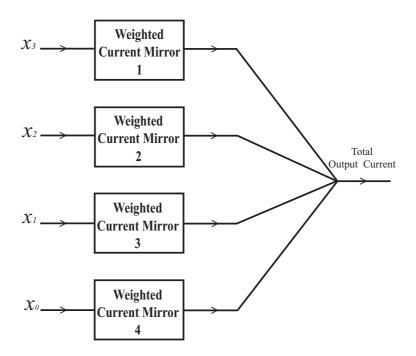

Using the synapse-neuron module will decrease the design cost and interconnections [2]. Once designing the synapse-neuron module, it can be used as building block of neural networks where it needs setting up the interconnections between synapse-neuron modules. The block diagram of the proposed synapse-neuron module is shown in Figure 4.1.

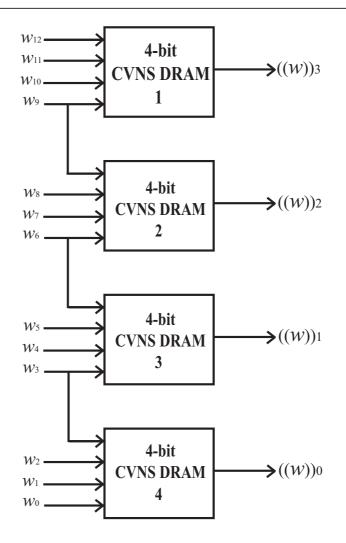

A 13-bit multi-valued CVNS DRAM is used to store the weights,  $w_{12}, ..., w_0$ . The DRAM generates the CVNS digits,  $((w))_3, ..., ((w))_0$ , from the binary weights and stores them on the storage cells. The stored CVNS digits proceed to the multiplication module.

Multiplication module performs the multiplication of the stored CVNS digits by the input. The input is converted to 4 bits,  $(Z)_4, ..., (Z)_1$ . Consequently, the CVNS digits are

Figure 4.1: Block diagram of the proposed synapse-neuron module.

multiplied by the binary bits resulting in an analog value with 4-bit resolution.

The interface unit applies the sign,  $w_0$ , to the multiplication output and transfers the result to the common node. In this node, the currents from all the synapse-neuron modules are added up together and divided by the number of modules. A sigmoidal neuron is employed to extract the output according to the received current in the Common Node (CN).

There is also a voltage-mode ADC to convert the input to each layer to 4 bits. Note that as the input to the network is digital, there is no need of using an ADC for the inputs to the first layer.  $(Z)_4$  is the only digit which is changing from '0' to '1', and the other three digits are considered to be equal to '0'. Accordingly, The maximum value for the input happens for an input equal to 1.8V which is equivalent to '1000'.

This synapse-neuron module is the building block in implementing distributed neural networks.

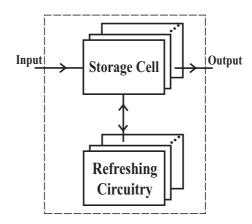

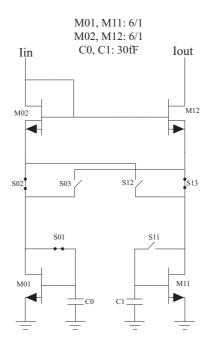

#### 4.1 CVNS DRAM

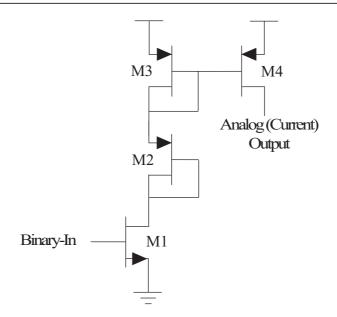

The 13-bit DRAM contains four 4-bit (16-level) multi-valued DRAMs [14,15] as is shown in Figure 4.2.

Working in current-mode, each 16-level DRAM generates a CVNS digit in the form of

Figure 4.2: Block diagram of the 13-bit multi-valued DRAM.

current from the corresponding 4-bit input in the form of voltage.

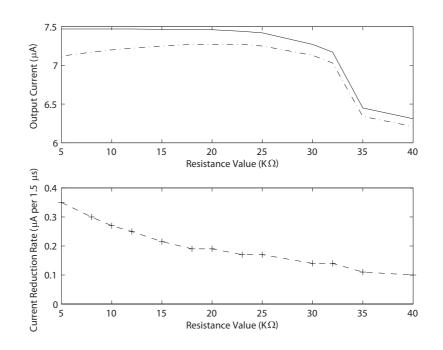

There is a 4-bit Digital to Analog Converter (DAC) in each one of 4-bit DRAMs which is responsible for the CVNS digit generation. This DAC contains four 1-bit weighted current sources. In this work, the current sources of DAC are designed to generate currents equal to  $8\mu A$ ,  $4\mu A$ ,  $2\mu A$ , and  $1\mu A$  for the first (most significant), the second, the third, and the fourth (least significant) bits, respectively. The output currents from the current sources are summed up together, and the result generates a CVNS digit in the form of a current changing between 0 to  $15\mu A$ .

Each CVNS digit is stored on a dynamic current mirror (current copier) [27]. Each storage cell has the ability of storing up to 4 bits equivalent to 16 levels with the capacitor size of 20.3 fF.

There is a link of 1-bit between the CVNS digits; the Least Significant Bit (LSB) input to each 4-bit DRAM is repeated as the Most Significant Bit (MSB) to the next 4-bit DRAM as is shown in Figure 4.2. This common bit is used as the Error Correction Code (ECC).

The value of stored CVNS digits changes with the time because of the leakage current of the storage capacitor. This changes the stored value and causes an error. In each refreshing cycle, the possible error is detected and corrected based on the redundancy between the stored CVNS digits, ECC.

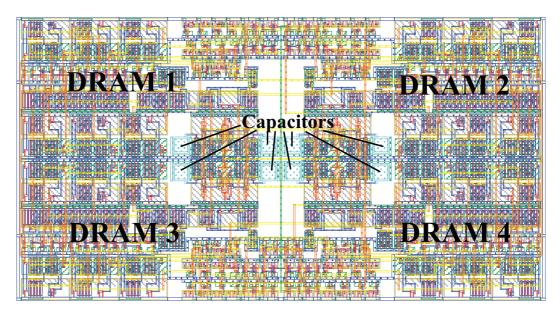

Figure 4.3 shows the layout of the 13-bit multi-valued CVNS DRAM. The capacitors are metal-insulator-metal capacitors and are laid out using metal 5 and metal 6.

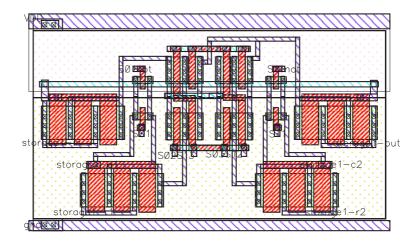

Figure 4.3: Layout of the 13-bit multi-valued DRAM.

### 4.2 Multiplier Module

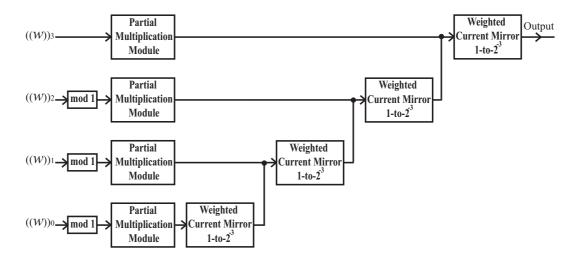

The output of this module is in the form of current and is generated through the block diagram of Figure 4.4.

Figure 4.4: Block diagram of the multiplier module.

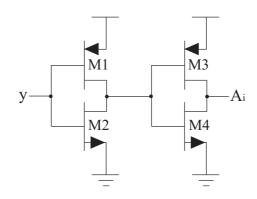

In Figure 4.4, *mod1* is the modulo 1 operation module. Partial multiplication modules are generating the partial results as is shown in Figure 4.5. Weighted current mirrors are used for scaling purposes.

Figure 4.5: Block diagram of the partial multiplication module.

Here, the multiplier digits are applied as switches. For a digit of '1', the switch is close, and the CVNS digit in the form of current is passing through it.

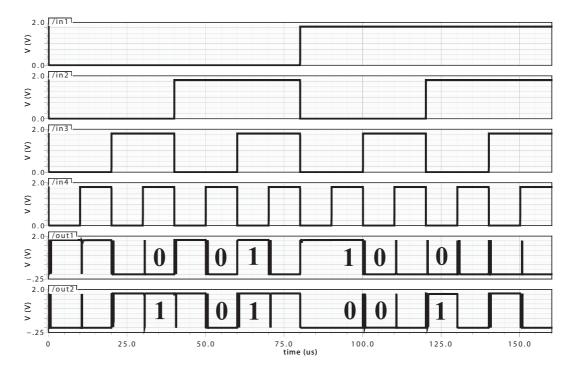

The simulation result for multiplication of '1, 1111, 1010, 1011' by '0111' in the proposed circuitries for the multiplier module is shown in Figure 4.6.

Figure 4.6: Simulation result of '1, 1111, 1010, 1011' multiplied by '0111'.