## University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

2013

# An FPGA Based Controller for a MEMS Tri-mode FMCW Radar

Sabrina Zereen *University of Windsor*

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### Recommended Citation

Zereen, Sabrina, "An FPGA Based Controller for a MEMS Tri-mode FMCW Radar" (2013). Electronic Theses and Dissertations. Paper 4892.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# An FPGA Based Controller for a MEMS Tri-mode FMCW Radar

#### By

#### **SABRINA ZEREEN**

#### A Thesis

Submitted to the Faculty of Graduate Studies through Electrical and Computer Engineering in partial fulfillment of the requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario

2013

© 2013 Sabrina Zereen

## An FPGA Based Controller for a MEMS Tri-mode FMCW Radar

| By<br>Sabrina Zereen                                              |

|-------------------------------------------------------------------|

| Approved By:                                                      |

| Jessica Chen<br>School of Computer Science                        |

|                                                                   |

| Mohammed Khalid Department of Electrical and Computer Engineering |

| Sazzadur Chowdhury, Advisor                                       |

| Department of Electrical and Computer Engineering                 |

## **Author's Declaration of Originality**

I hereby certify that I am the sole author of this thesis and that no part of this thesis has been published or submitted for publication.

I certify that, to the best of my knowledge, my thesis does not infringe upon anyone's copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material from the work of other people included in my thesis, published or otherwise, are fully acknowledged in accordance with the standard referencing practices. Furthermore, to the extent that I have included copyrighted material that surpasses the bounds of fair dealing within the meaning of the Canada Copyright Act, I certify that I have obtained a written permission from the copyright owner(s) to include such material(s) in my thesis and have included copies of such copyright clearances to my appendix.

I declare that this is a true copy of my thesis, including any final revisions, as approved by my thesis committee and the Graduate Studies office, and that this thesis has not been submitted for a higher degree to any other University or Institution.

#### **Abstract**

In this thesis a Xilinx Virtex 5 FPGA platform based signal processing algorithm has been developed and experimentally verified for use in a MEMS based tri-mode 77GHz FMCW automotive radar to determine range and velocity of targets in the vicinity of a host vehicle. The Xilinx Virtex 5 FPGA based signal processing and control algorithm dynamically reconfigures a MEMS based FMCW radar to provide a short, medium, and long-range coverage using the same hardware. The MEMS radar comprises of MEMS SP3T RF switches, microfabricated Rotman lens and a microstrip antenna embedded with MEMS SPST switches, in additional to other microelectronic components. A CA-CFAR module has been used to eliminate false targets in a multi target clutter affected scenario. The refresh rate for the current design is 2.048ms for each mode of radar which is nearly 40 times lower than the BOSCH LRR3. The maximum percent difference from analytical to HDL calculated range values was found to be 0.16% which can be lowered with further refinement. The developed FPGA based radar signal processing algorithm can be implemented as an ASIC which can be batch fabricated to lower down the production cost so that automotive radars can become a standard item for all the vehicles on the road.

#### **A Sincere Dedication**

To mom, dad, Nowreen, Azad, Ayan, and my friends without whom this endeavor would not have been possible

Bismillaahir Rahmaanir Raheem

In the name of Allah, The Beneficent The Merciful

#### Acknowledgement

Firstly, I would like to express my gratitude to the Almighty Allah, who blessed me with good health and opportunity to finish my masters from a reputed University. He also helped my acquainting me with some lovely people who have helped me in this endeavour.

I would sincerely like to thank my advisor and my co-advisor Dr. Sazzadur Chowdhury and Dr. Khalid, whose relentless support and guidance have helped me to finish my work. Also I would like to express my appreciation to Dr. Jessica Chen who has agreed to become my committee member.

I am especially grateful to Karl Leboeuf and Ahmed Ridwan for their knowledge of coding, which has helped with me with the basic knowledge of Xilinx and also helped me to pull through from several tight spots.

One another person in the University of Windsor, who played a vital role in my masters and without the help of whom things would have been really difficult, was Andria Ballo. She was always there for all the engineering students with her sympathetic ears and helpful hand for every small problem. Her miraculous ability to solve almost every problem and make life for an international student like myself easy and fun is one of her most appreciative trait.

I would also want to thank my MEMS team members, for creating such an entertaining and enjoyable workplace.

To conclude I would like to thank my parents, my sisters and the rest of my family whose prayers, support, patience and never ending belief in me has helped to work through some exasperating situations during the course of my research.

|             | <b>Table of Contents</b>                                                       |      |

|-------------|--------------------------------------------------------------------------------|------|

| Author      | r's Declaration of Originality                                                 | iii  |

| Abstra      | act                                                                            | iv   |

| A Sinc      | eere Dedication                                                                | ٧    |

| Ackno       | wledgement                                                                     | Vİ   |

| List of     | Figures                                                                        | Х    |

| List of     | Tables                                                                         | xii  |

| List of     | Abbreviations                                                                  | xiii |

| Nome        | nclature                                                                       | ΧV   |

| 1 C         | CHAPTER 1: Introduction                                                        | 1    |

| 1.1         | Problem statement                                                              | 1    |

| 1.2         | Automotive Radar                                                               | 3    |

| 1.3         | The MEMS Radar                                                                 | 4    |

| 1.4         | Operating principle of the MEMS Radar:                                         | 6    |

| 1.5         | Research Hypothesis                                                            | 7    |

| 1.6         | Research Motivation                                                            | 8    |

| 1.7         | Principle Results                                                              | 8    |

| 1.8         | Thesis Organization                                                            | 9    |

| 2 C         | CHAPTER 2:                                                                     | 11   |

| Literat     | ture Survey                                                                    | 11   |

| 2.1         | Literature review                                                              | 11   |

| 2.2         | Pulse Doppler Radar                                                            | 12   |

| 2.3         | Continuous Wave Radar                                                          | 14   |

| 2.4         | Radar type preference for the designed project                                 | 15   |

| 2.5         | Generating and tuning of the frequency                                         | 16   |

| 2.6<br>Syst | Selection of the Development Platform for the Tri-Mode Radar Signal Processing | 17   |

| 2.7         | State- of- the- art Automotive Radar                                           | 19   |

| 2.8         | Work done in LFMCW Radar sensor design with FPGA-based platform                | 24   |

| 3 C         | CHAPTER 3                                                                      | 26   |

| Target      | FMCW Radar Design Specifications                                               | 26   |

| 3.1      | Ide         | ntifying operating parameters for the system design      | 26 |

|----------|-------------|----------------------------------------------------------|----|

| 3.2      | All         | ocation of the LFMCW Waveform                            | 27 |

| 3.3      | The         | Linear Frequency Modulated Continuous Wave (LFMCW) Radar | 28 |

| 3.4      | Dei         | ivation of equation for Range and Velocity               | 31 |

| 3.4      | 4.1         | Instance One: For Stationary Target Situation            | 31 |

| 3.4      | 4.2         | Instance two: Moving target situation                    | 32 |

| 3.5      | Gei         | neration of LFMCW radar signal using VCO                 | 35 |

| 3.6      | Mo          | dification of the Received signal                        | 36 |

| 3.7      | Dig         | ital Signal Processing for the Radar design              | 37 |

| 3.7      | 7.1         | Windowing                                                | 38 |

| 3.7      | 7.2         | Fast Fourier Transform (FFT)                             | 44 |

| 3.7      | 7.3         | Constant False Alarm Rate (CFAR) Processing unit         | 45 |

| 3.8      | Mu          | ltifarious Aspects Considered for the Radar Design       | 48 |

| 3.8      | 8.1         | Radar Targets                                            | 48 |

| 3.8      | 8.2         | Noise                                                    | 49 |

| 3.8      | 8. <i>3</i> | Attenuation                                              | 50 |

| 3.8      | 8.4         | Clutter and Jamming                                      | 51 |

| 4 Ch     | naptei      | 4                                                        | 53 |

| Signal I | Proce       | ssing Algorithm and Control of the Radar System          | 53 |

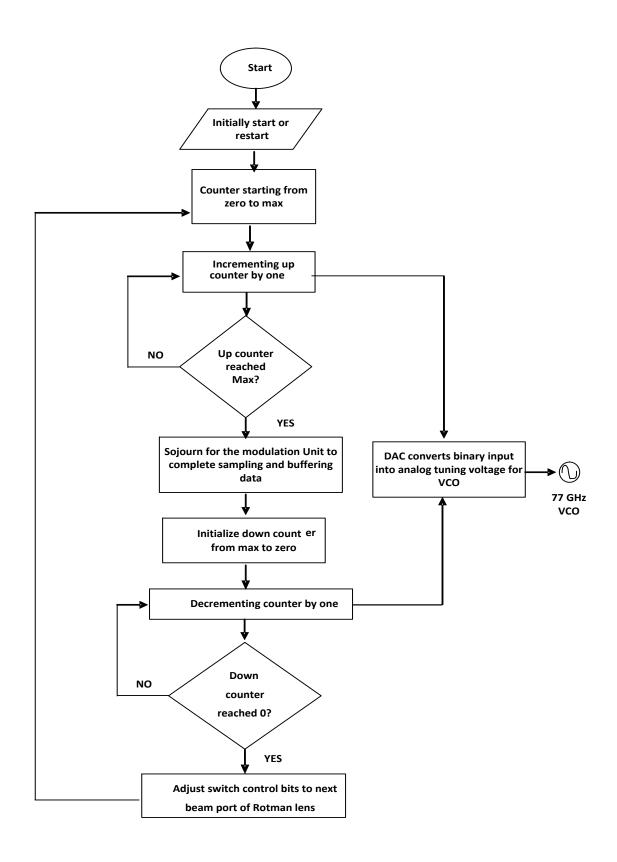

| 4.1      | Rac         | lar Transmitter Processing and Control Algorithm         | 54 |

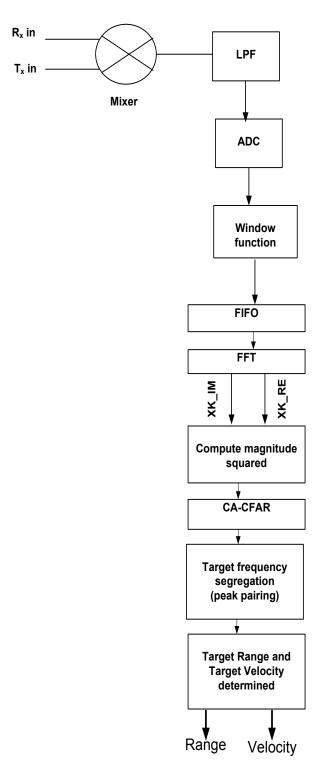

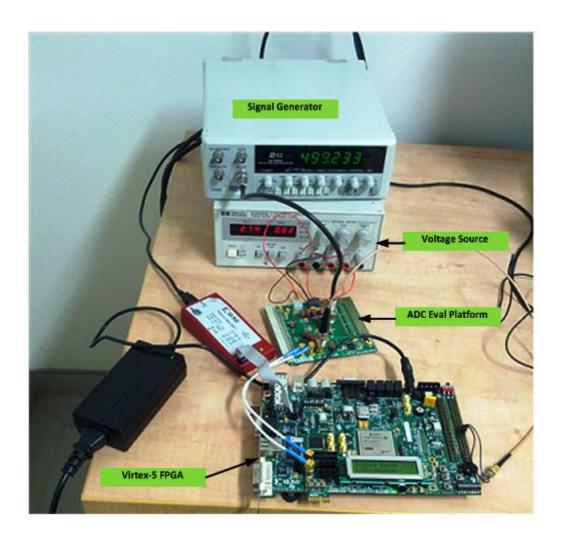

| 4.2      | Rac         | lar Receiver Processing and Control Algorithm            | 56 |

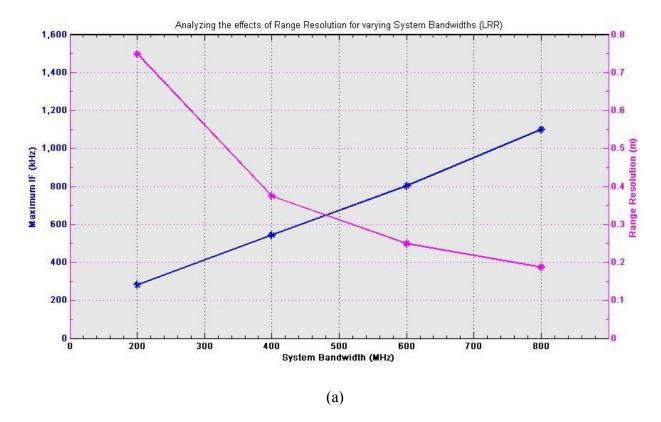

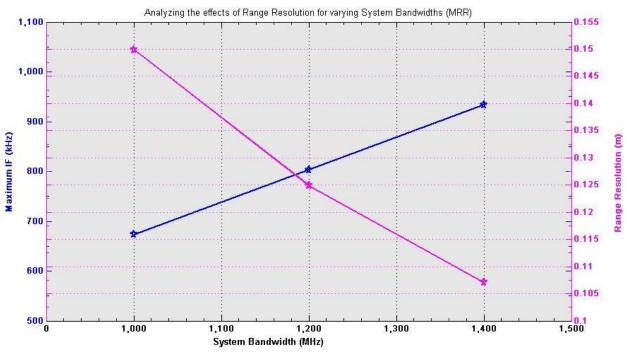

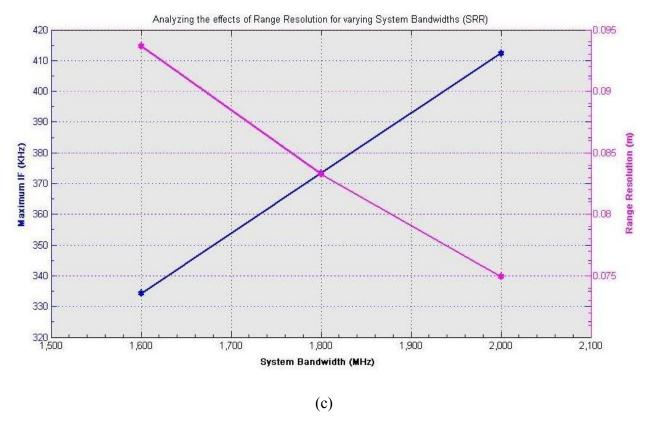

| 4.3      | Rac         | lar Bandwidth Selection for the Tri-mode radar           | 58 |

| 4.4      | Oth         | er System Components Configuration                       | 61 |

| 4.5      | Alg         | orithm Summary                                           | 62 |

| 5 Ch     | naptei      | 5                                                        | 65 |

| Softwar  | re Im       | plementation of the Designed Project                     | 65 |

| 5.1      | Sof         | tware Simulation of the Design System                    | 66 |

| 5.2      | Vei         | rification of the Test Scenario                          | 75 |

| 5.3      | Mu          | ltiple target Test Scenario                              | 77 |

| 5.4      | Obs         | servation Summary                                        | 83 |

| 6 Ch     | naptei      | 6                                                        | 84 |

| Hardw  | are Implementation of the Tri-mode Radar Design                     | 84  |

|--------|---------------------------------------------------------------------|-----|

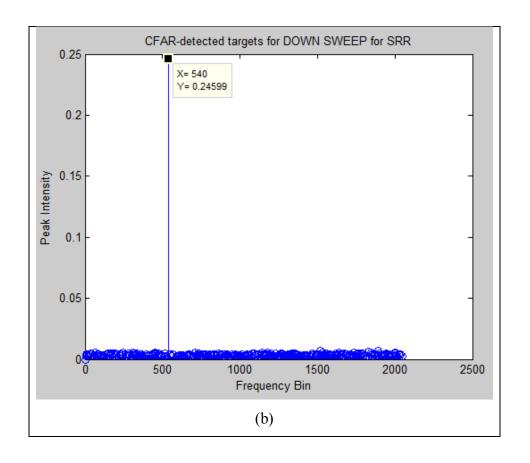

| 6.1    | Hardware Implementation                                             | 84  |

| 6.2    | Radar Signal Processing Algorithm                                   | 86  |

| 6.3    | The Processing Blocks Used In the Design                            | 87  |

| 6.4    | The Hardware Simulation technique and the Individual Process Blocks | 89  |

| 6.5    | Range and Velocity Calculation Methodology                          | 90  |

| 6.6    | RTL Design View of the Process Blocks                               | 90  |

| 6.7    | Hardware Synthesis Results for the Radar design                     | 99  |

| 6.8    | Results Comparison between HDL implementation and MATLAB Simulation | 101 |

| 7 C    | hapter 7                                                            | 105 |

| Conclu | asion and Future Work                                               | 105 |

| 7.1    | Future work                                                         | 105 |

| Refere | nces                                                                | 107 |

| APPE   | NDIX-1                                                              | 112 |

| (a) MA | ATLAB codes                                                         | 112 |

| (b) HD | OL codes                                                            | 121 |

| VITA   | AUCTORIS                                                            | 190 |

## **List of Figures**

| FIGURE 1.1 BLOCK DIAGRAM OF THE WINDSOR AUTOMOTIVE                                                           | 5             |

|--------------------------------------------------------------------------------------------------------------|---------------|

| FIGURE 1.2 (A) THE BEAM COVERAGE OF THE TRI-MODE RADAR AND (B) THE DISTANCE COVERED IN METER                 | 6             |

| FIGURE 2.1 THE RADAR CLASSIFICATION                                                                          | 12            |

| FIGURE 2.2 TIME DEPENDENT BEHAVIOR OF A) TRANSMITTED AND                                                     | 13            |

| FIGURE 2.3 TRANSMIT SIGNAL FREQUENCY OF (A) FSK AND (B) FREQUENCY MODULATION SHOWING A TRIANGU WAVEFORM      |               |

| FIGURE 2.4 VCO TRANSFER FUNCTION                                                                             |               |

| FIGURE 2.5 DISTRONIC PLUS                                                                                    |               |

| FIGURE 2.6 RADAR APPLICATIONS OF THE SRR                                                                     | 20            |

| FIGURE 2.7 FIELD OF VIEW AND RANGE COVERED FOR THREE FUNCTIONS                                               |               |

| FIGURE 2.8 (A) BOSCH LRR3 SENSOR (B) BOSCH MRR SENSOR (C) CONTINENTAL ARS300 (D) IMST SRR SENSOR             |               |

| Figure 2.9 (a) 77GHz 3D Millimeter Wave Radar,(b) 76-GHz 2D Millimeter Wave Radar                            |               |

| FIGURE 2.10 LAYOUT OF THE NEXT GENERATION DRIVER ASSISTANCE APPLICATIONS                                     |               |

| FIGURE 2.11 (A) BOSCH 2ND GENERATION LRR (B) DENSO'S 77 GHZ LRR (C) TOYOTA CRDL 77 GHZ LRR                   |               |

| FIGURE 3.1 FMCW WAVEFORMS (A) SINE WAVE (B) SAW-TOOTH (C) TRIANGULAR                                         |               |

| FIGURE 3.2 (A) TRANSMITTED WAVE AND RECEIVED LFMCW SIGNALS (B) BEAT FREQUENCY OR INTERMEDIATE                |               |

| FREQUENCY FOR A STATIONARY TARGET                                                                            | 29            |

| FIGURE 3.3(A) TRANSMITTED WAVE AND RECEIVED LFMCW SIGNALS (B) BEAT FREQUENCY OR INTERMEDIATE                 |               |

| FREQUENCY FOR A MOVING TARGET                                                                                | 30            |

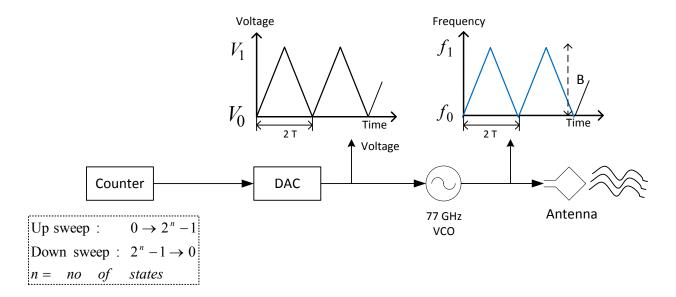

| FIGURE 3. 4 FPGA BASED VOLTAGE TUNING TO GENERATE FREQUENCY CHIRPS BY THE VCO                                | 35            |

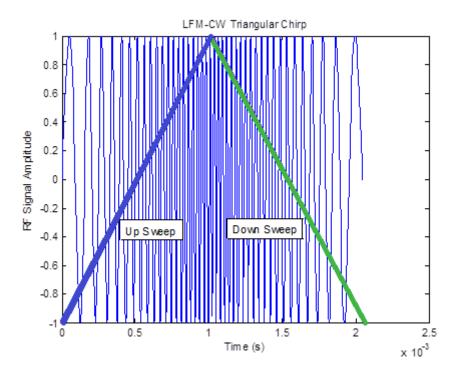

| FIGURE 3.5 TIME-DOMAIN RF SIGNAL FOR THE LMFCW RADAR DISPLAYING UP AND DOWN CHIRP                            | 36            |

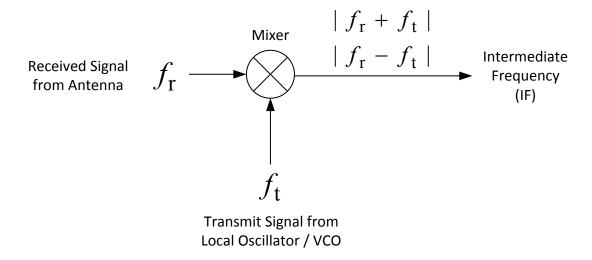

| FIGURE 3.6 THE MIXING PROCESS OF AN RF SIGNAL                                                                | 37            |

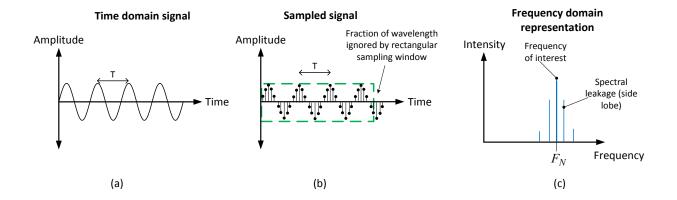

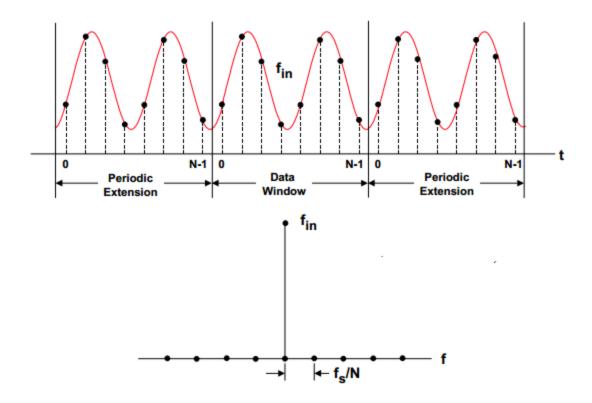

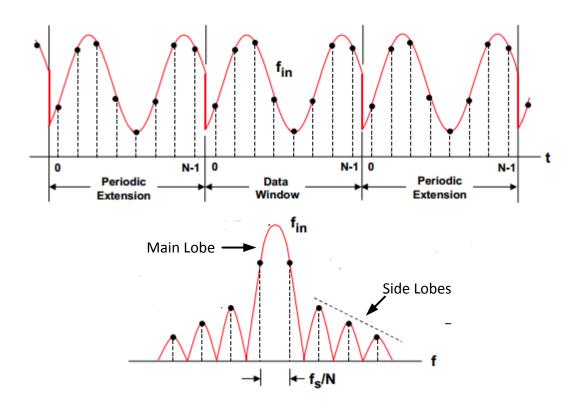

| Figure 3.7 (a)Signal under investigation with period T (b) Sampled signal convolved with a                   |               |

| rectangular window-function and, (c) Spectral leakage due to the windowing where $F_{\scriptscriptstyle N}=$ | 1/ <i>T</i> . |

|                                                                                                              | 39            |

| FIGURE 3.8 FFT SINE WAVE WITH INTEGRAL NUMBER OF CYCLES IN THE DATA WINDOW                                   |               |

| FIGURE 3.9 FFT SINE WAVE WITH NON- INTEGRAL NUMBER OF CYCLES IN THE DATA WINDOW                              |               |

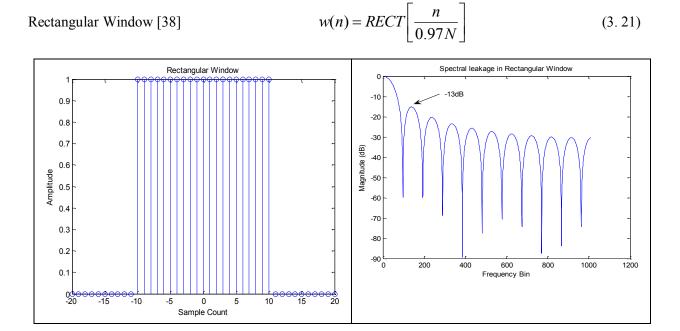

| FIGURE 3.10 TIME-DOMAIN AND FREQUENCY DOMAIN REPRESENTATION OF THE RECTANGULAR WINDOW FUNCT                  |               |

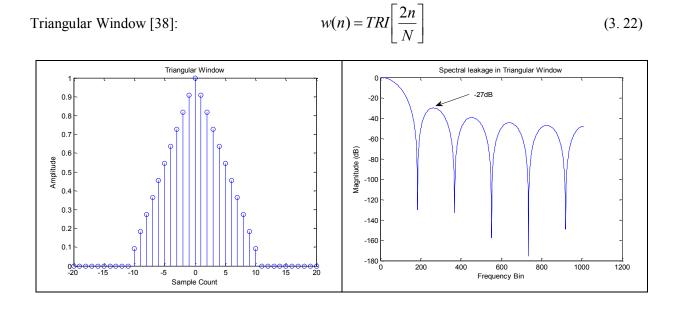

| Figure 3.11 Time-domain and frequency domain representation of the Triangular Window Functio                 |               |

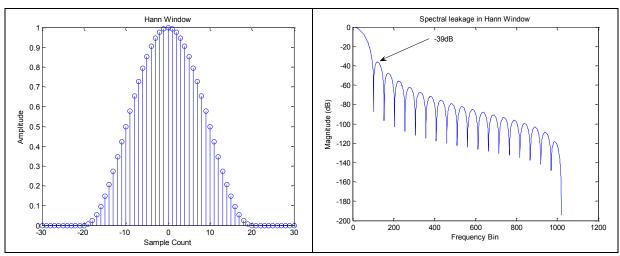

| FIGURE 3.12 TIME-DOMAIN AND FREQUENCY DOMAIN REPRESENTATION OF THE HANNING WINDOW FUNCTION                   | 43            |

| FIGURE 3.13 TIME-DOMAIN AND FREQUENCY DOMAIN REPRESENTATION OF THE HAMMING WINDOW FUNCTION                   | 43            |

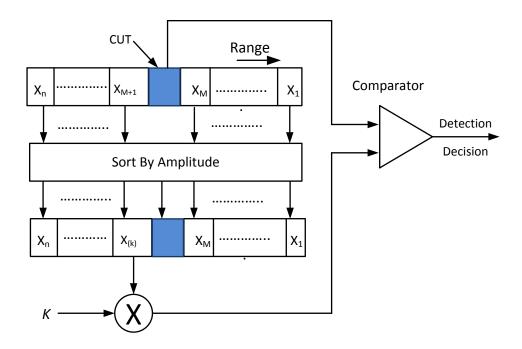

| FIGURE 3.14 OS-CFAR ARCHITECTURE                                                                             | 46            |

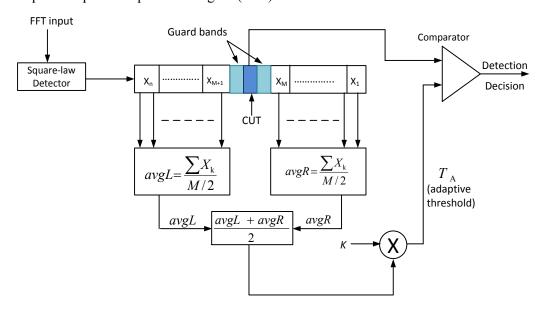

| FIGURE 3.15 CA-CFAR ARCHITECTURE USED IN THE THESIS                                                          | 47            |

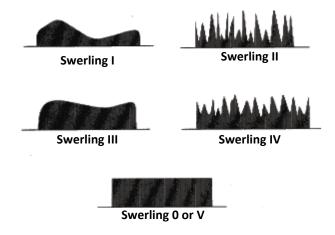

| FIGURE 3.16 THE DIFFERENT SWERLINGFLUCTUATING MODELS                                                         | 49            |

| FIGURE 4 1 RADAR TRANSMITTING AND PROCESSING ALGORITHM                                                       | 55            |

| FIGURE 4.2 RADAR SIGNAL PROCESSING ALGORITHM OF THE DESIGN SYSTEM PORTRAYING THE HIERARCHY OF TI             | ΗE            |

| TOTAL OPERATION                                                                                              | 57            |

| Figure 4.3 Results for Maximum IF and Range Resolution for Different Bandwidth for (a) LRR (b)               |               |

| MRR AND (C) SRR                                                                                              |               |

| FIGURE 5.1 TEST SITUATION SCENARIO FOR A SINGLE TARGET SITUATION                                             |               |

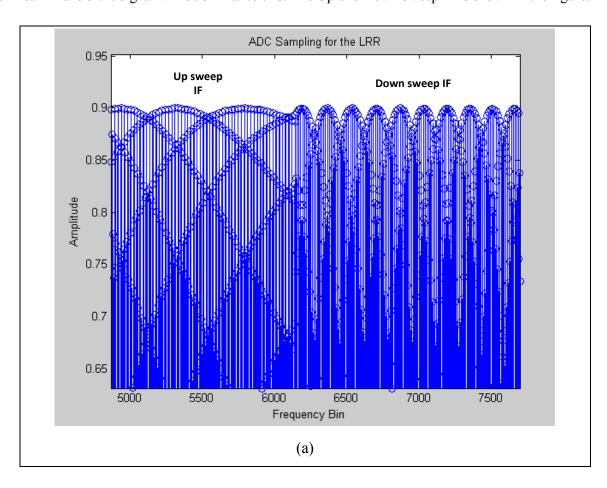

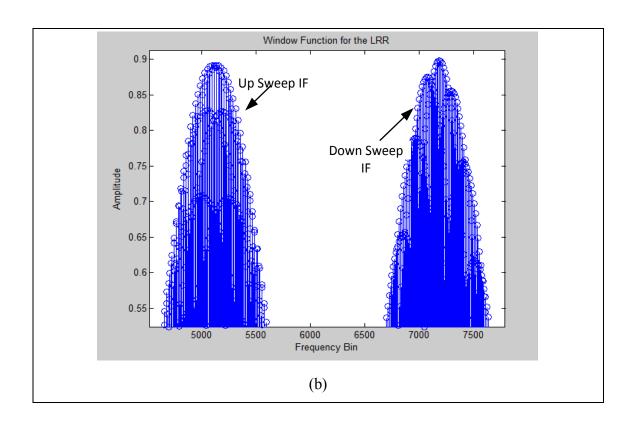

| FIGURE 5.2 ADC SAMPLING AND WINDOWING OF IF FROM THE TARGET DETECTED IN THE LONG RANGE                       | 68            |

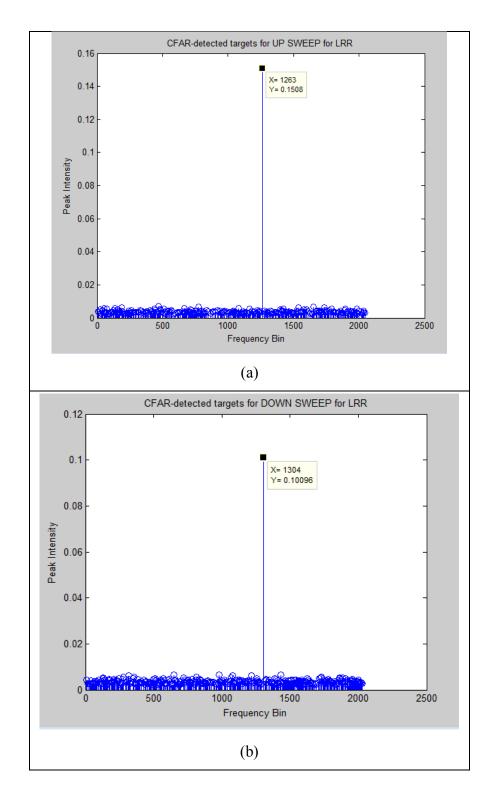

| FIGURE 5.3 TARGET DETECTION BY THE CFAR FROM THE FFT OUTPUT SHOWING FOR BOTH UP AND DOWN CHIR                | P 69          |

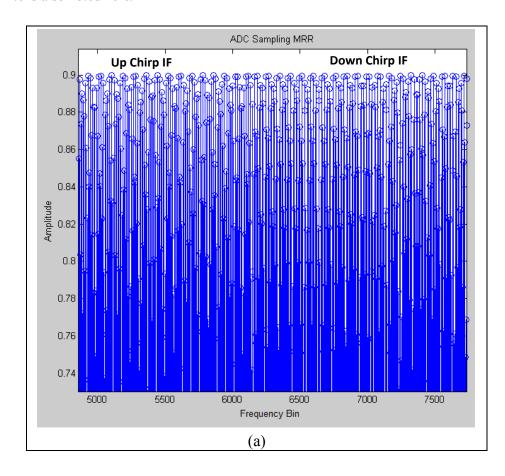

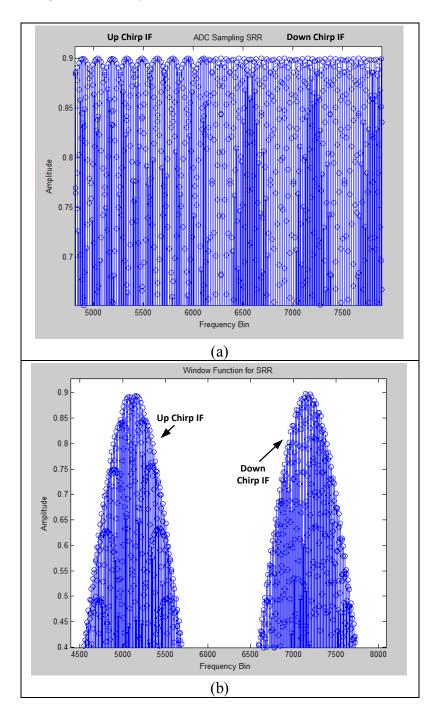

| Figure 5.4 (a) ADC sampling for the Up and Down IF signal and (b) The signal after being multiplied i                             | 3Y   |

|-----------------------------------------------------------------------------------------------------------------------------------|------|

| THE HAMMING WINDOW FUNCTION                                                                                                       | . 71 |

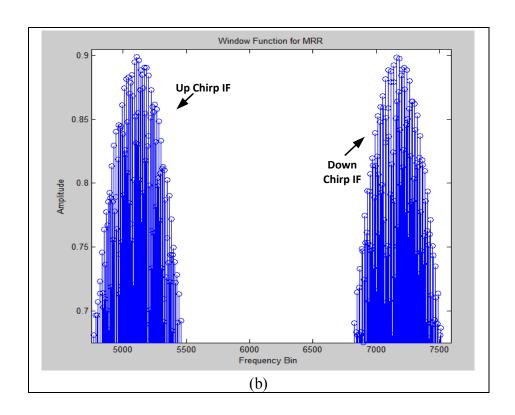

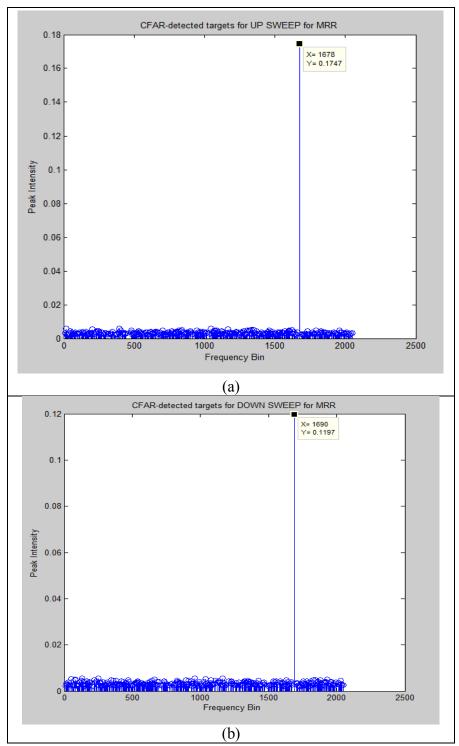

| FIGURE 5.5 TARGET DETECTION IN THE MID-RANGE SHOWN FOR UP AND DOWN SWEEP                                                          | . 72 |

| FIGURE 5.6 ADC SAMPLING OF THE UP AND DOWN SWEEP SIGNAL AND THE CORRESPONDING SIGNAL AFTER BEEN                                   |      |

| MULTIPLIED BY THE HAMMING WINDOW FUNCTION                                                                                         | . 73 |

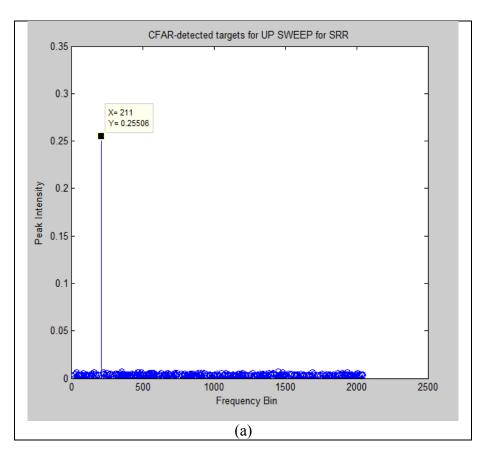

| FIGURE 5.7 TARGET DETECTION WITHIN THE BEAM 3 REGION OF THE SHORT RANGE RADAR IS SHOWN AND VERIFIEI                               | O    |

| FOR THE UP AND DOWN SWEEP                                                                                                         | . 75 |

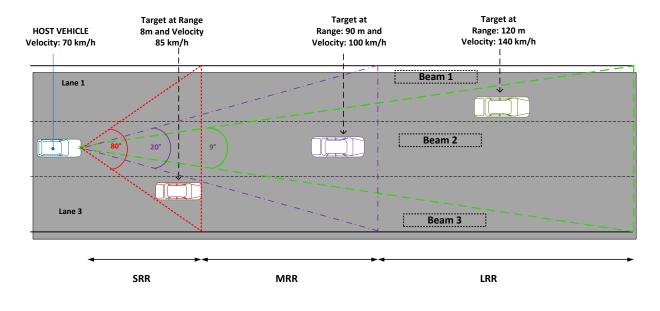

| FIGURE 5.8 CONCOCTED MULTIPLE TARGETS SCENARIO FOR OBSERVING THE TRI-MODE RADAR DETECTION                                         |      |

| EFFICIENCY                                                                                                                        | . 77 |

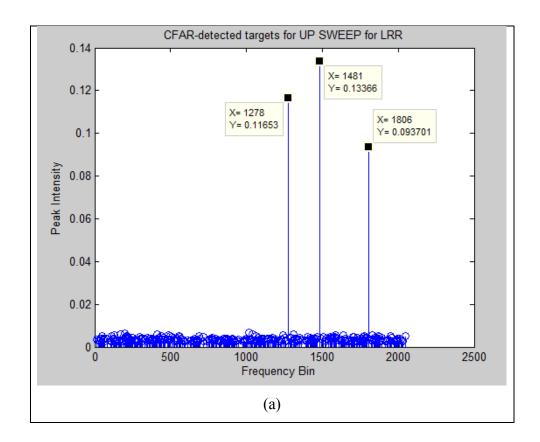

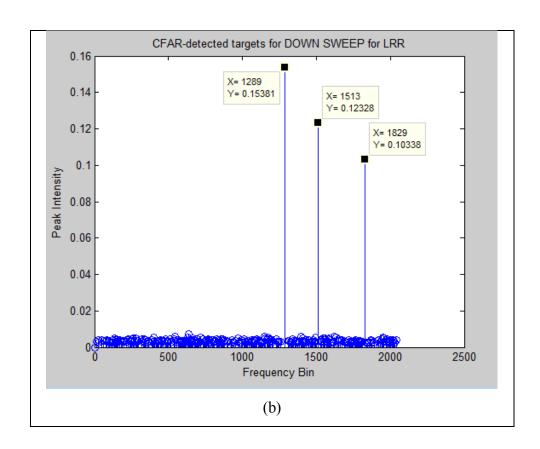

| FIGURE 5.9 MULTIPLE TARGETS DETECTED FROM THE HYPOTHETICAL SCENARIO IN THE LRR MODE                                               | . 79 |

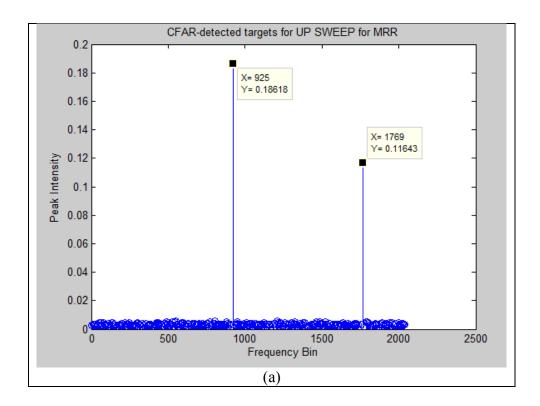

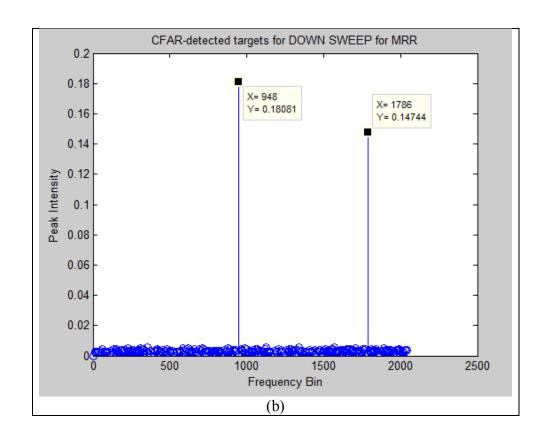

| FIGURE 5.10 TARGETS DETECTED BY MRR IN THE MULTIPLE TARGETS SITUATION                                                             | . 80 |

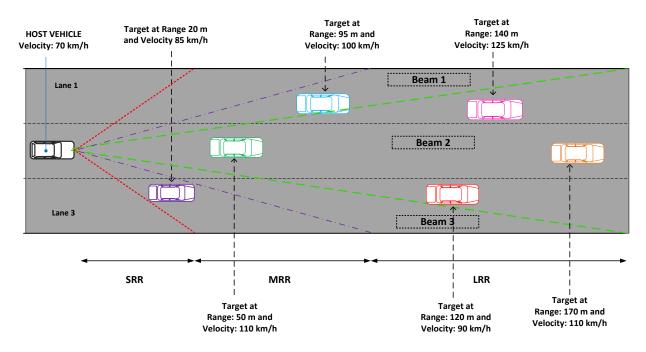

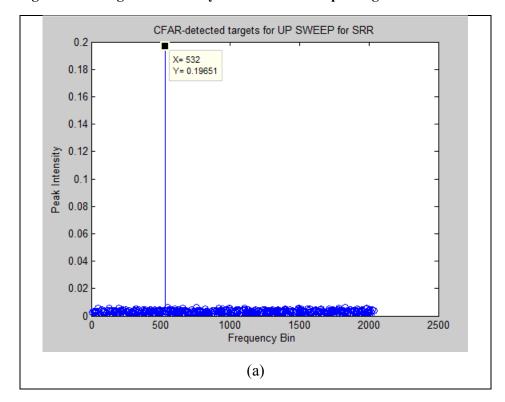

| FIGURE 5.11 TARGET DETECTED BY SRR SENSOR IN THE MULTIPLE TARGETS SCENARIO                                                        | . 81 |

| Figure $6.1\mathrm{TheVirtex}$ - $5\mathrm{FPGA}$ platform and $\mathrm{ADC}$ platform used in the design of Tri-mode radar sign. | ٩L   |

| PROCESSING                                                                                                                        | . 86 |

| FIGURE 6.2 BLOCK DIAGRAM SHOWING THE PROCESSING STAGES OF THE HDL ALGORITHM                                                       | . 88 |

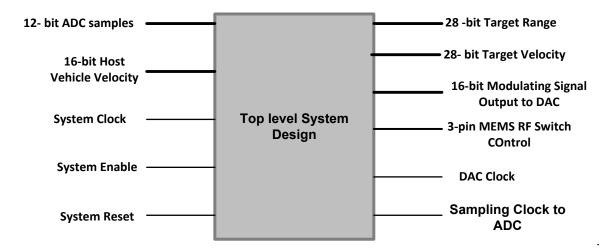

| FIGURE 6.3 BLACK BOX VIEW OF THE RADAR SIGNAL PROCESSING ALGORITHM. THE THICKER LINES INDICATES BUS                               | 3    |

| AND THE INPUTS LINES ARE ON THE LEFT AND THE OUTPUTS ARE ON THE RIGHT                                                             | . 89 |

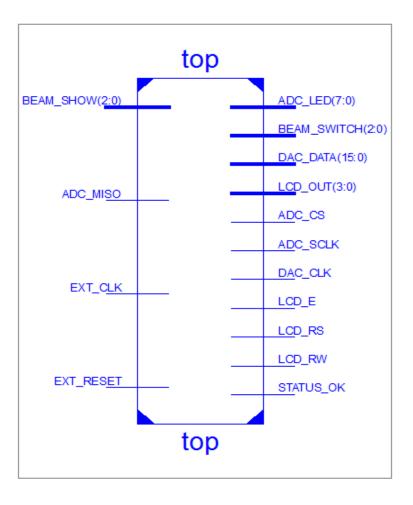

| FIGURE 6.4 THE TOP MODULE OF THE HDL ALGORITHM                                                                                    | . 90 |

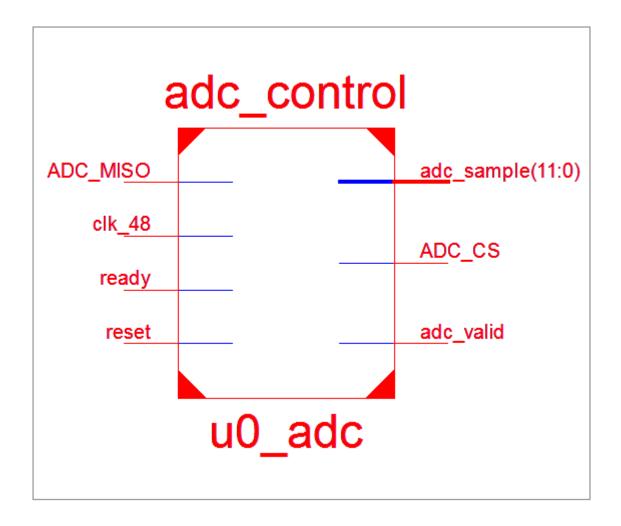

| FIGURE 6.5 THE RTL DESIGN VIEWER OF THE ADC COMPUTATION                                                                           | . 92 |

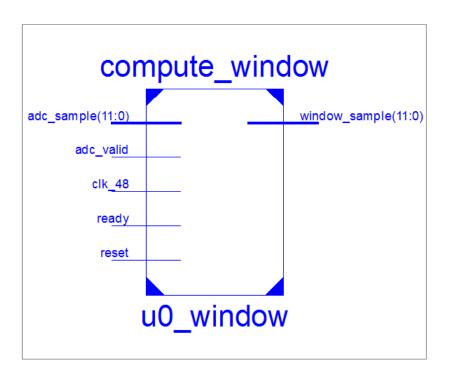

| FIGURE 6.6 RTL VIEW OF THE WINDOW PROCESSING BLOCK                                                                                | . 93 |

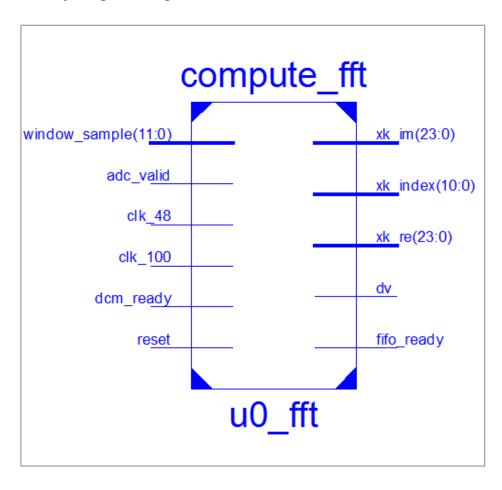

| FIGURE 6.7 RTL VIEW OF THE FFT PROCESS BLOCK                                                                                      | . 94 |

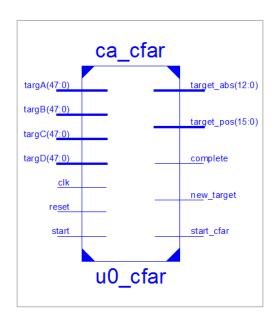

| FIGURE 6.8 THE RTL DESIGN VIEW OF THE CA-CFAR PROCESS                                                                             | . 95 |

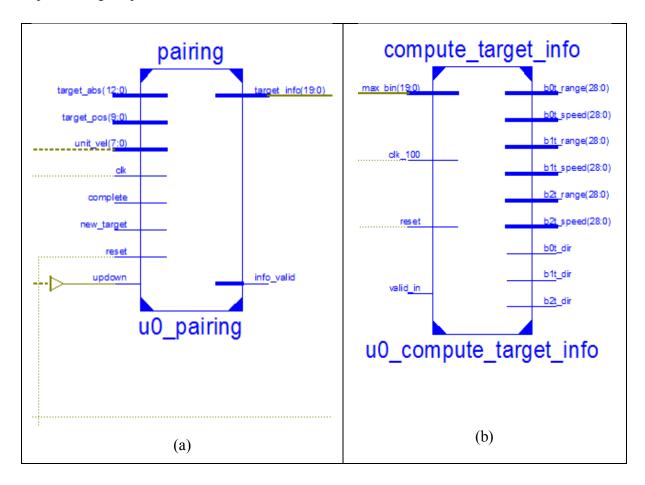

| FIGURE 6.9 PROCESS BLOCK SHOWING THE (A) PEAK PARING AND (B) RESULT COMPUTATION PROCESS                                           | . 97 |

## **List of Tables**

| Table 1.1 Road Traffic Deaths per 100, 000 Inhabitants / per billion vehicle - kilometers            |        |

|------------------------------------------------------------------------------------------------------|--------|

| TABLE 1.2 RADAR SIMULATION RESULTS.                                                                  | 9      |

| TABLE 2.1 COMPARISONS BETWEEN EXISTING SENSORS IN THE CURRENT MARKET                                 | 22     |

| TABLE 2.2 FORMER GENERATION RADARS HIGHLIGHTING SOME KEY FEATURES                                    | 23     |

| TABLE 3.1 SENSOR CLASSIFICATION FOR TRI-MODE RADAR SYSTEM                                            | 26     |

| TABLE 3.2 COMPARISONS BETWEEN DIFFERENT WINDOW FUNCTIONS                                             | 44     |

| TABLE 3.3 ATTENUATION AT 70-80GHz DUE TO ATMOSPHERIC CONDITIONS                                      | 51     |

| TABLE 4.1 INTRODUCTORY SYSTEM SPECIFICATIONS                                                         | 53     |

| TABLE 4.2 SIGNAL PROCESSING UNIT FOR THE RADAR SYSTEM                                                | 62     |

| TABLE 4.3 SPECIFICATION FOR THE LONG RANGE RADAR DESIGN                                              | 63     |

| TABLE 4.4 SPECIFICATION FOR THE MEDIUM RANGE RADAR DESIGN                                            | 63     |

| TABLE 4.5 SPECIFICATION FOR THE SHORT RANGE RADAR DESIGN                                             | 64     |

| TABLE 5.1 UP AND DOWN FREQUENCY VALUES CALCULATED FOR THE RANGE AND VELOCITY FOR SINGLE TARGE        | Т      |

| SITUATION                                                                                            | 75     |

| TABLE 5.2 MATLAB RESULTS OF THE RANGE AND VELOCITY FOR SINGLE TARGET SITUATION                       | 76     |

| TABLE 5.3 DIFFERENCE BETWEEN MATLAB AND ACTUAL VALUES                                                | 77     |

| TABLE 5.4 UP AND DOWN FREQUENCY SWEEP CALCULATED FOR THE HYPOTHETICAL SITUATION FOR THETRI-MO        | DE     |

| RADAR TEST SCENARIO                                                                                  | 81     |

| TABLE 5.5 RESULTS OBTAINED FROM THE MATLAB SIMULATION FOR THE GIVEN SITUATION                        | 82     |

| TABLE 5.6 ERROR CALCULATIONS BETWEEN THE ACTUAL VALUES AND THE SIMULATED VALUES                      |        |

| TABLE 6.1 DETAILS FOR THE PINS SHOWN IN THE TOP MODULE                                               | 91     |

| TABLE 6.2 PINS CONFIGURATION OF THE ADC BLOCK                                                        | 93     |

| TABLE 6.3 PINS CONFIGURATIONS FOR THE WINDOW BLOCK                                                   | 94     |

| TABLE 6.4 TABLE SHOWING THE PIN CONFIGURATIONS                                                       | 95     |

| TABLE 6.5 HDL PORT CONFIGURATION                                                                     | 96     |

| TABLE 6.6 PINS DESCRIPTION FOR THE PROCESS BLOCK GIVEN ABOVE                                         |        |

| Table 6.7 Resources used for (a) SRR (b MRR) (c) LRR                                                 | 99     |

| Table $6.8$ Comparison between the LRR designed in this thesis with a previous version of LRR design |        |

| IN THE UNIVERSITY OF WINDSOR [20]                                                                    | 100    |

| TABLE 6.9 PROCESSING TIME FOR EACH PROCESS BLOCK FOR (A) SRR (B) MRR AND (C) LRR                     | 100    |

| Table $6.10$ Results obtained from the MATLAB simulations is compared against calculated value       | ES 102 |

| TABLE 6.11 RESULTS OBTAINED FROM THE LCD DISPLAY AND COMPARED WITH THE CALCULATED VALUES             | 103    |

| TABLE 6.12 ERROR PERCENTAGE BETWEEN THE MATLAB SIMULATED VALUES AND HDL VALUES                       | 104    |

#### **List of Abbreviations**

MEMS - Microelectromechanical Systems

Radar - Radio Detection and Ranging

RF – Radio Frequency

SP3T – Single Pole Triple Throw

PRF – Pulse Repetition Frequency

DSP – Digital Signal Processor(-ing)

FPGA – Field Programmable Gate Array

DAC – Digital to Analog Converter

ADC – Analog to Digital Converter

FSK – Frequency Shift Keying

LFMCW - Linear Frequency Modulated Continuous Wave

HDL – Hardware Description Language

SARA - Strategic Automotive Radar Frequency Allocation

FFT – Fast Fourier Transform

DFT - Discrete Fourier Transform

DIT – Decimation In Time

DIF – Decimation In Frequency

CA (OS)-CFAR – Constant False(Ordered Statistics) Constant False Alarm Rate

RTL – Register Transfer Level

RCS - Radar Cross-Section

CPI – Coherent Processing Interval

VCO – Voltage Controlled Oscillator

LRR – Long Range Radar

MRR – Medium Range Radar

SRR – Short Range Radar

IF – Intermediate Frequency

MSPS - Mega-Samples Per Second

LUT – Look-Up Table

FF – Flip-Flop

BUFG - Global Buffer

BUFGCTLR – Global Clock Buffer

RAM – Random Access Memory

ROM – Read-Only Memory

DSP48E – Xilinx Digital Signal Processing Slice (5<sup>th</sup> Generation)

ISE - Integrated System Environment

LPF - Low Pass Filter

AWGN - Additive White Gaussian Noise

EM-Electro-Magnetic

MMIC – Monolithic Microwave Integrated Circuits

#### **Nomenclature**

r =target range c =speed of RF waves through air  $T_{\text{two-wav}}$  = two-way travel time for RF wave from radar sensor to target and back  $v_{\text{rel}}$  = relative velocity  $v_{\text{target}} = \text{target velocity}$  $v_{\text{host}}$  = host vehicle velocity  $f_{\rm d}$  = Doppler frequency shift  $\lambda$  = radio wave wavelength  $f_b$  = beat frequency or instantaneous intermediate frequency  $f_{\rm t}$  = transmit signal frequency  $f_{\Gamma}$  = received signal frequency  $\tau_0$  = travel time for RF wave from radar sensor to target B = LFMCW sweep bandwidth T = LFMCW sweep duration k = rate of change of frequency in LFMCW sweep = B/T $X_k$  = frequency domain sample  $x_n$  = time domain sample  $P_{fa}$  = probability of false alarm  $T_{\rm A} = {\rm CFAR}$  dynamic threshold  $\sigma$  = Radar Cross-Section of a target  $N_{\mathsf{Th}}$  = thermal noise  $SNR_Q$  = quantization signal-to-noise ratio  $f_{\rm S}$  = sampling frequency  $f_{\text{res}}$  = frequency resolution of FFT

#### **CHAPTER 1:**

#### Introduction

In this chapter the research work is defined explicating the importance of active safety systems. Some of the active safety systems include adaptive cruise control (ACC), collision warning systems including automotive steering and braking intervention. Analyzing actual crash records form 2004-2008 it has been found that a forward collision warning system, using radar sensors, will palliate crashes up to 1.2 million crashes per year [1]. Although it was found that the forward collision warning features are found only in luxury vehicles because they are costly.

#### 1.1 Problem statement

The objective of this thesis is to design a FPGA based controller for a 77GHz MEMS FMCW automotive radar using three bandwidths, for covering long, medium and short range.

Road-accidents have played a major role for the loss of millions of lives every year. This deplorable situation can be minimized by making use of a microelectromechanical (MEMS) system based sensor technology to detect the propinquity of vehicles, pedestrians and other obstacles in the vicinity of a host vehicle in real-time. Among the existing state of the art radars in the market are long range radar (LRR) from BOSCH introduced in 2009, ARS 300 by Conti in 2009 and by Denso's third generation long range radar which was introduced a year before [2]. However the current technology in the market like ultrasonic sensors and sensor arrays, lasers, cameras attached on the side mirrors and electromagnetic radar units (which are only available with high-end vehicles) are not adequate to ensure complete safety against accidents. This is because of their slow signal processing system and also for radars; they have to scan the target area mechanically. The cost of such stand-alone devices is too high for the manufacturers to integrate them in low-cost vehicles. As such the dilemma regarding road safety remains nearly same, in spite of some vehicles being equipped with collision warning or pre-crash warning devices.

Strategic Analytics a market research firm has anticipated that within the period of 2006-2011 there would be an increase of the usage of the long-range distance radar for pre-collision warning will increase by 65% annually, the demand reaching 3 million units in 2011, with 23 million of them using radar sensors. By 2014, 7 percent of all new cars will include a distance warning system, mostly in Europe and Japan [3].

Table 1.1 is from IRTAD, an International Group and Database on Road Safety Data, shows the statistics for death count per 100, 000 in habitants and per billion vehicles-km for a number of countries, which are members of IRTAD [4]. The Table shows a considerable amount of decrease in death counts over the years 1970 to 2010, although there is an increase in count for some countries. The decrease can be due to the effective safety measures that are being introduced into the vehicles now-a-days.

However, while high income countries are showing a major reduction in the death rate due to road traffics, the same cannot be said for countries where there is a rapid increase in the number of vehicles on the road. In 2010, 1.3 million people around the world died due to road crashes and more 50 million were injured. Of these death counts about 90% are in low-income and middle-income countries. In May 2011, a Decade of Action for Road Safety was launched by the United Nations with an aspiration to stabilize and then reduce the global road traffic deaths by 2020 [4].

Table 1.1 Road Traffic Deaths per 100, 000 Inhabitants / per billion vehicle - kilometers

| Different             | Death per 100, 000 inhabitants Death per billion vehicle-kilometers |      |      |      |                  |       |       | eters |      |                  |

|-----------------------|---------------------------------------------------------------------|------|------|------|------------------|-------|-------|-------|------|------------------|

| Country               | 1970                                                                | 1980 | 1990 | 2000 | 2010             | 1970  | 1980  | 1990  | 2000 | 2010             |

| Australia             | 30.4                                                                | 22.3 | 13.7 | 9.5  | 6.1              | 49.3  | 28.2  | 14.4  | 9.3  | 6.1              |

| Austria               | 34.5                                                                |      | 20.3 | 12.2 | 6.6              | 109   | 56.3  | 27.9  | 15.0 | -                |

| Belgium               | 31.8                                                                | 24.3 | 19.9 | 14.4 | 8.8 <sup>b</sup> | 104.6 | 50    | 28.1  | 16.4 | 9.6 <sup>b</sup> |

| Canada <sup>a</sup>   | 23.8                                                                | 22.7 | 14.9 | 9.4  | 6.6 <sup>b</sup> | -     | -     | -     | 9.3  | 6.5 <sup>b</sup> |

| Czech<br>Republic     | 20.2                                                                | 12.2 | 12.5 | 14.5 | 7.6              | -     | 53.9  | 48.3  | 36.7 | 16.2             |

| Denmark               | 24.6                                                                | 13.5 | 12.4 | 9.3  | 4.6              | 50.5  | 25    | 17.3  | 10.7 | 5.6              |

| France                | 32.6                                                                | 25.4 | 19.8 | 13.7 | 6.4              | 90.4  | 44    | 25.7  | 15.1 | 7.1              |

| United<br>Kingdom     | 14.0                                                                | 11.0 | 9.4  | 6.1  | 3.1              | 37.4° | 21.9° | 12.7° | 7.3° | 3.7°             |

| United<br>States      | 25.7                                                                | 22.5 | 17.9 | 15.3 | 10.6             | 29.6  | 20.9  | 12.9  | 9.5  | 6.8              |

| Germany               | 27.3                                                                | 19.3 | 14.0 | 9.1  | 4.5              | -     | 37.3  | 20    | 11.3 | 5.2              |

| Hungary               | 15.8                                                                | 15.2 | 23.4 | 12.0 | 7.4              | -     | -     | -     | -    | -                |

| Israel                | 17.1                                                                | 10.8 | 8.7  | 7.1  | 4.6              | 87.9  | 38.8  | 22.4  | 12.4 | 7.1              |

| Italy                 | 20.5                                                                | 16.3 | 12.6 | 12.4 | 6.8              | -     | -     | -     | -    | -                |

| Japan                 | 21                                                                  | 9.7  | 11.8 | 8.2  | 4.5              | 96.4  | 29.3  | 23.2  | 13.4 | 7.7 <sup>b</sup> |

| Korea                 | 11.0                                                                | 17.0 | 33.1 | 21.8 | 11.3             | -     | -     | -     | 49.5 | 18.7             |

| Malaysia <sup>a</sup> | -                                                                   | -    | 22.7 | 25.9 | 23.8             | -     | -     | -     | 26.3 | 16.2             |

| Poland | 10.6 | 16.8 | 19.2 | 16.3 | 10.2 | - | - | - | - | - |

|--------|------|------|------|------|------|---|---|---|---|---|

| Spain  | 16.0 | 17.7 | 23.2 | 14.5 | 5.4  | - | - | - | - | - |

Death within 30 days. Data recorded by the police. a = accession country. b = 2009 c = Great Britain

"Radar technology is the key to building innovative driver assistance systems to help avoid automobile accidents," says Hans Adlkofer, VP and general manager of Infineon Technologies' Sense and Control business unit [3].

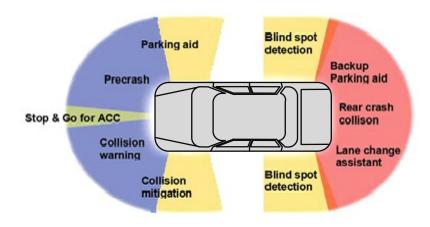

The radar technology initially came with the high-end luxury vehicles, but the cost has dropped down and can be used in reasonably priced vehicles. Automotive industries all over the world are utilizing the radar technology for a wide range of detection systems such as:

- 1. Adaptive Cruise Control with stop and go functionality.

- 2. Blind-spot detection.

- 3. Self-parking system.

- 4. Side-sensors for parking aids

- 5. Pre-crash warning system.

- 6. Lane Changing assistance to the driver.

- 7. Backup camera and sensor for impact warning.

- 8. Car to computer communication devices utilizing GPS tracking system.

- 9. Remote speed sensor.

The global economic cost for road crashes and injuries is estimated to be around US\$ 518 billion annually. Unless appropriate actions is taken road traffic injuries is predicted to become the third leading contributing factor in the global burden of disease and injury. It cost European Union 180 billion euros annually for road traffic injuries which is twice the annual budget for all other activities in these countries. This huge public health and development problem kill almost 1.2 million people a year and cause injury or disability to 20 to 50 million or more people. Data from World Bank and WHO show that unless proper action is taken the injury count will increase drastically by 2020, especially in countries where there is a rapid increase of motor vehicles [5]. Hence the multi-range radar technology is a constitutive feature to enhance highway safety and mitigate loss of lives and property damage.

#### 1.2 Automotive Radar

On 9th June, 1904 Christian Hülsmeyera German inventor was the first to use radar waves to demonstrate his "anti-ship-colliding system" [6]. He got a German patent on 2<sup>nd</sup> August, 1904 for the

detection device and then later on in the same year he obtained another patent from UK for his complete design of the Telemobiloskop, or Remote Object Viewing Device [6], [7].

The use of radar is more beneficial than devices like lasers and infrared visions equipment as radar can function through bad weather condition like rain, snow or fog. The current market has radars with frequencies of 24GHz and 77GHz. The choice of these frequencies is based on the requirement of small antenna size, relative attenuation of spectrum and fast attenuation of radio signals [8]. Automotive radars are used to calculate the target range, target velocity and azimuth angle in a short time for multiple target situations.

#### 1.3 The MEMS Radar

Automotive radar application system is analyzed in accordance with the range it covers. Long range radars (LRR) and medium range radars (MRR) are used in cruise control and collision avoidance systems and short range radar (SRR) is used in collision avoidance, crash-prevention and parking-assist systems.

Previous discussion ascertained the importance of automotive radars in reducing the numbers of road traffic accidents, however lower cost and reliable performance are also much needed to improve the road conditions all over the world. The cost of the radars needs to be decreased to ensure cars at various price levels can afford to be equipped with it in order to enhance road safety.

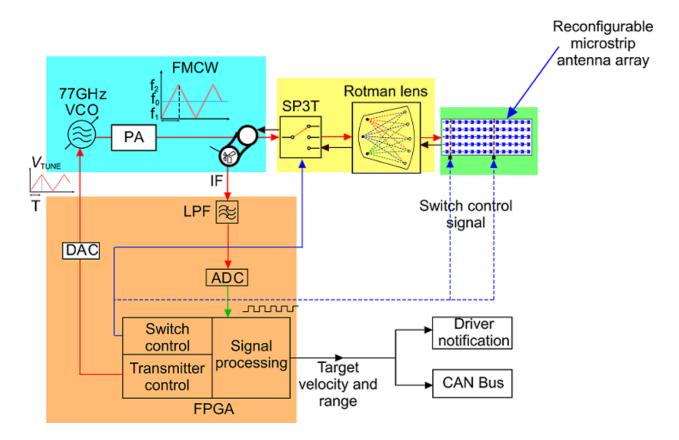

MEMS based design offers the advantage of fabricating low cost, batch production of RF components like RF switches, Rotman Lens that can be used to apprehend compact high performance radar in a small form factor. Such a MEMS based radar system is being developed in the University Of Windsor, Ontario, Canada. The block diagram shown is Fig 1 exhibits the major components of the existing automotive radar system.

Figure 1.1 Block Diagram of the Windsor Automotive

Radar System

The main components used in the Windsor Automotive Radar System are:

- > FPGA/ ASIC implemented controller

- ➤ MEMS SP3T RF switches

- > Microfabricated Rotman lens

- ➤ MEMS reconfigurable microstrip array antenna

- > 77GHz transceiver chipset

- ➤ MEMS SPST RF switch

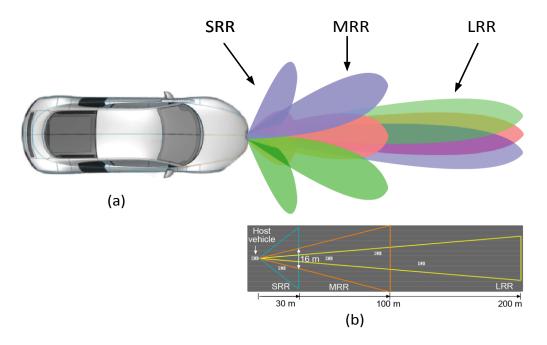

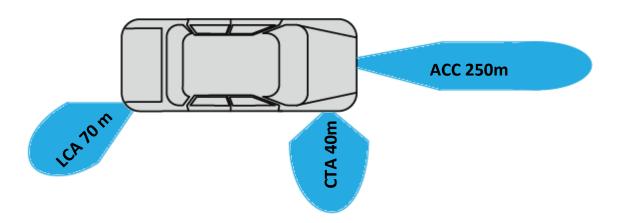

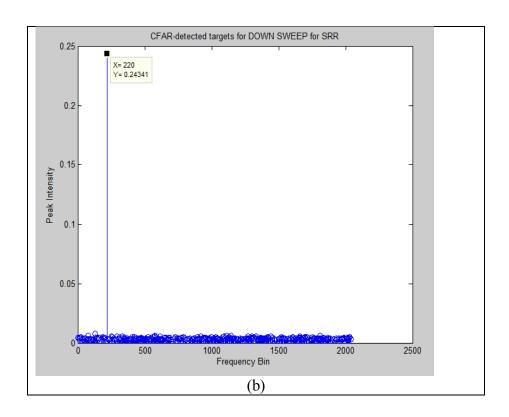

The tri-mode radar coverage of the current design in shown in Fig 2 (a) and (b)

Figure 1.2 (a) The beam coverage of the Tri-mode radar and (b) the distance covered in Meter

## 1.4 Operating principle of the MEMS Radar:

- A voltage controlled oscillator (VCO) is attuned by an FPGA implemented control circuit which generates a triangular signal (V<sub>tune</sub>). The VCO then generates a linear frequency modulated continuous wave (LFMCW) signal with a bandwidth of 800MHz, 1400MHz and 2000MHz respectively for Long Range Radar (LRR), Medium Range Radar (MRR) and Short Range Radar (SRR) with a center frequency of 77GHz.

- 2. The signal generated is then fed into a MEMS SP3T switch.

- 3. The SP3T switch regulated by an FPGA implemented control circuit sequentially switches the LFMCW signals between the three beams of the Rotman lens.

- 4. The LFMCW signals after travelling through the Rotman lens cavity arrive at the array ports of the Rotman lens. The time-delayed in-phase signals are then fed into a microstrip antenna array which radiates the signal in a specific direction.

- 5. The microstrip has SPST switches embedded into it. The scan area of the antenna array depends on the antenna beamwidth, which in turn depends on the number of patches in the microstrip. Increasing the no of patches makes the beam narrower.

- 6. The beam from the Rotman lens can be steered across the target area in steps determined by a predefined angle. This steering can be done by the sequential switching of the input signal among the beamports of the Rotman lens.

- 7. The existing Rotman lens can transmit and receive signals. An FPGA based control circuit controls the operation of the receiver SPST switch so that the signal output at a specific beamport of the receiver Rotman lens can be mixed with the corresponding transmit signal.

- 8. The received signals obtained from the SP3T switch are then fed into a mixer where it is mixed with the transmitted signal to generate Intermediate Frequency (IF).

- 9. The IF generated are then passed into an Analog to Digital (ADC) converter, where they are sampled and converted into digital signals.

- 10. Lastly the output from the ADC is then processed through an FPGA implemented algorithm to calculate the range and velocity of the target detected.

The objective of this thesis is the development of an FPGA implemented algorithm to utilize a MEMS Tri-mode Radar System to detect the range and velocity of targets for three different ranges. The designed radar will certainly triumph over the use of three separate radars for long, medium and short range existing in the current market.

#### 1.5 Research Hypothesis

The FMCW radar requires a high chirp bandwidth to improve the resolution of range and velocity and the bandwidths chosen for the design of the tri-mode radar ensures better results. Furthermore the design of the FPGA based control and signal processing algorithm can be implemented as an ASIC which offers batch fabrication of the system at a low production cost for high volume production. Accumulating the rest of the MEMS components mentioned above the target system will offer a high performance compact form of radar architecture. This will amend the highway safety situation and lower the number of road collisions which will help save lives and avoid property damage.

#### 1.6 Research Motivation

It goes without saying that the idea of avoiding a collision is always preferable than crash protection for automotive safety scheme. The introduction of radar in the automotive industry occurred in the late 50's. In the 70's profound radar developments embarked starting at microwave frequencies. However the use of radar in automotive market became possible in the 90's where it used for safety and security purpose for the driver [9].

Radar systems in the 77GHz frequency domain give good performance in range and azimuth angle and hence can be used for several purposes to increase the efficiency of the safety system in a car [2]. It can be applied for several automotive applications like:

- > For ACC and Cut-in and Stop & Go situations the short range radars make use of wider beam rather than the directive long range sensor.

- ➤ Parking assistant with more precision, longer range frequent update rates than the conventional ultrasonic systems.

- ➤ Using for Blind Spot Detection with a low cost technology.

- Pre-crash detection with fast detection rates.

The aim of the thesis is to develop MEMS tri-mode FMCW radar for the detection of range and velocity of targets for three ranges long, medium and short to enhance the automotive safety systems.

#### 1.7 Principle Results

A LFMCW radar signal processing algorithm for FPGA/ASIC is created to control the operation of a MEMS SPST switch to dynamically alter the beamwidth of the antenna array mentioned in the radar system above to switch the radar constantly from SRR to MRR and then to LRR mode. The performance specifications achieved from the developed system are tabulated below:

**Table 1.2 Radar Simulation results**

| Parameters                                                  | SRR      | MRR      | LRR      |

|-------------------------------------------------------------|----------|----------|----------|

| Operating Frequency                                         | 77GHz    | 77GHz    | 77GHz    |

| Bandwidth                                                   | 2000MHz  | 1400MHz  | 800MHz   |

| Maximum Distance                                            | 30m      | 100m     | 200m     |

| Range Resolution                                            | 0.07m    | 0.11m    | 0.19m    |

| Maximum target range error                                  | 2cm      | 4cm      | 5cm      |

| Maximum relative velocity (approaching and receding target) | 300km/h  | 300km/h  | 300km/h  |

| Velocity resolution                                         | 6.84km/h | 6.84km/h | 6.84km/h |

| Beam width (in degrees)                                     | 80       | 20       | 9        |

#### 1.8 Thesis Organization

Chapter 1 emphasizes the importance of the work and result to this present day. It recapitulates the significance of the radar technology and their function in the automotive industry. A report of the IRTAD on road safety data is also given in this chapter in Table 1.1 tabulating the statistics of the fatality rate in different regions.

Chapter 2 encapsulates the existing literature of the radar technology and its applications in the automotive industry. The chapter also provides a good background of the proposed MEMS radar system.

Chapter 3 provides a profound mathematical and conceptual background of the radar technology, emphasizing on the LFMCW radar theory. The concept of the Cell-Averaging Constant False Alarm Rate and the digital signal processing tools used in the design is also discussed in this chapter.

Chapter 4 explicates the radar signal processing of the proposed design with block diagram and design parameters. Short descriptions of the components used in the design are also provided here.

Chapter 5 comprises of MATLAB modeling and simulation of the design. Results from MATLAB are given here with relevant graphs for single and multiple target situations for the three mode radars.

Chapter 6 constitutes the hardware implementation of the design with RTL schematics of the blocks used and table comparing the results obtained from both MATLAB modeling and hardware implementations.

Lastly Chapter 7 contributes with ideas that can be worked upon in future for further improvement of the tri-mode radar design and gives a conclusive summary of the project

#### **CHAPTER 2:**

#### **Literature Survey**

oIn this chapter the literature of the existing radar system will be reviewed with classification of the different radar systems available. The chapter also comprises the study of the FMCW radar over other radar types like pulsed Doppler and frequency shifting; establishing the reason for choosing FMCW radar for the target automotive radar design. The chapter covers a survey of the platform chosen for the radar design portraying its features and advantages. The state-of-the-art in the automotive radar system is also discussed in the later part of this chapter.

#### 2.1 Literature review

The principle of radar is based on the characteristics of electromagnetic waves and the reflections properties from different materials [10]. Around 1987-88 Hienrich Hertz with his revolutionary experiments, was able to exhibit that metals and dielectric objects can reflect electromagnetic waves. In 1922 Guglielmo Marconi gave a conceptual idea about detecting object using radio signals, although it was in 1933 when he was able to demonstrate a working device [11]. Some of the applications of radar systems in the modern world are satellite radar for altitude mapping and surveillance, weather detection, synthetic aperture radar (SAR) and advanced moving target indicators (MTI) for automobiles [12]

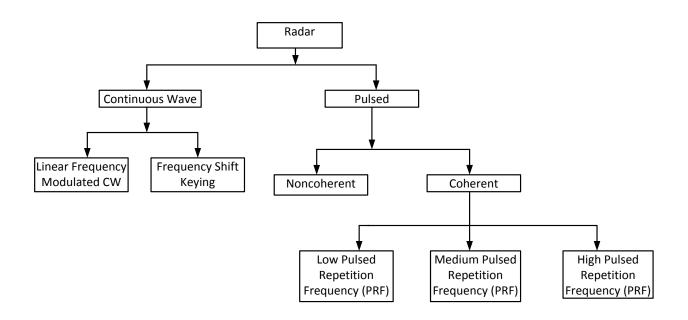

The radar system classification can be best described using Figure 2.1

Figure 2.1 The Radar Classification

#### 2.2 Pulse Doppler Radar

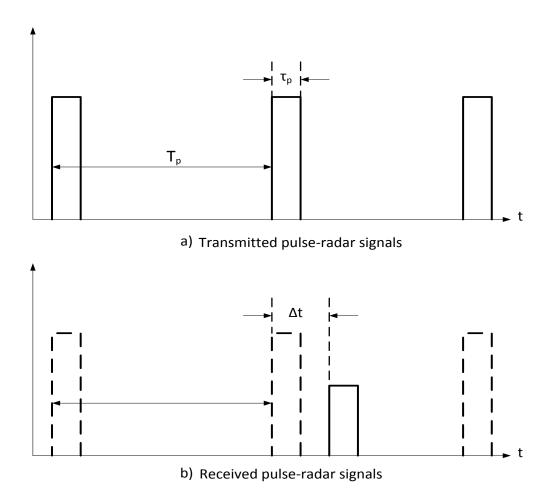

Pulsed radar transmits a high frequency modulated pulse of high power. The transmitter remains inactive for a fixed period of time during which it awaits for the received signal from the target detected. The range between the target and the radar can be calculated by measuring the round trip propagation delay between the transmitted and the received signal. The relative velocity of the target with respect to the radar can be determined from the Doppler shift frequency of the received signal. The Doppler shift frequency  $f_d$  is found by the difference between the received and the transmitted frequency. The Doppler shift is used to describe the motion of the target relative to the source from which the transmitted signal is being generated. An approaching target generates a positive frequency shift whereas the value becomes negative for a receding target. The following equations are used to calculate the range and radial velocity in a Pulsed Doppler Radar system [13], [10]:

Range :

$$R = \frac{cTp}{2}$$

(2.1)

Radial Velocity :

$$v_r = \frac{cf_d}{2f_t}$$

(2.2)

where c is the speed of light

T<sub>p</sub> is the pulse repetition rate

f<sub>d</sub> is the Doppler shift frequency

#### ftis the transmitted frequency

The figure below shows the transmitted and received Pulse-Doppler radar signal where the distance to the target is calculated to be  $T_p$  +  $\Delta t$ . Here Tp is the pulse repetition rate,  $\tau_p$  is the pulse width and  $\Delta t$  is the propagation delay.

Figure 2.2 Time dependent behavior of a) transmitted and b) received signals in a pulse-radar system

13

#### 2.3 Continuous Wave Radar

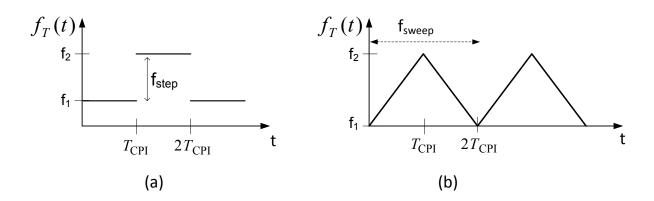

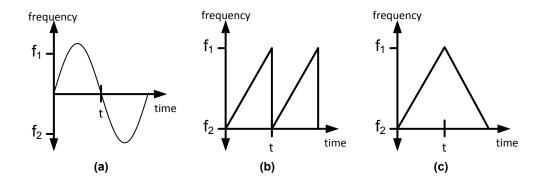

Continuous Wave (CW) radar transmits a signal continuously with a selected frequency. The pure sinusoidal signal can be represented by  $\cos 2\pi f_o t$  where the echo from the stationary target and the clutter will concentrate at  $f_o$ . When a moving target is detected the echoes received from it will shift the center frequency  $f_o$  by  $f_d$ , the Doppler frequency. The radial velocity of the target is then calculated by measuring the difference between  $f_o$  and  $f_d$ . Due to the continual nature of the signal emission of CW it is not possible to calculate the range unless modifications are made [13]. Continuous wave can be implemented in two ways: Frequency Shift Keying (FSK) and Frequency Modulated CW (FMCW). Frequency Shift Keying modulation makes use of frequencies steps over Coherent Processing Interval (CPI) of length  $T_{CPI}$  to calculate the range. The Frequency Modulation on the other hand makes use of frequency chirp in a sinusoidal, saw-tooth or triangular form to calculate the range and velocity which will be discussed in detail in the next chapter [14]. The transmit waveforms for the two types of CW is shown in Figure 2.3.

Figure 2.3 Transmit signal frequency of (a) FSK and (b) Frequency Modulation showing a triangular waveform

The range and the radial velocity for the FSK is calculated using the following equation:

$$R = -\frac{c \cdot \Delta \varphi}{4\pi \cdot f_{step}}$$

Range : (2. 1)

$$v_r = -\frac{f_d \cdot \lambda}{2}$$

Radial Velocity : (2.2)

Here,  $\Delta \phi$  is the phase difference in the two frequency peaks  $f_1$  and  $f_2$

$f_d$  is the Doppler Shift frequency and

$\lambda$  is the operating wavelength.

#### 2.4 Radar type preference for the designed project

From the discussions above comprehended the two types of radar. The Pulsed Doppler, FSK and FMCW are characterized by their waveform, power at which they operate, hardware required for implementation, cost in the computation process and the applications in which they can be used. For this project Linear Frequency Modulated Continuous Wave (LFMCW) radar has been chosen. The reason for choosing this radar was reinforced by the list of disadvantages of the Pulse-Doppler Radar and the FSK radar.

Disadvantages of the Pulsed Radar for automotive application:

- The velocity calculation gets constrained when the Doppler frequency becomes equal to a multiple of the PRF causing blind speed situation.

- To avoid blind speed high PRF can be used but that results in range ambiguity.

- For selection of the PRF it has to be maintained so that blind speed is not created near the target's expected speed.

- For automotive application it requires relatively high power.

- Difficult to detect short range targets.

#### Disadvantages of FSK-CW radar:

- Does not allow any target resolution in range.

- It has phase discontinuities at the timings of frequency shifts which insinuate phase noise.

- Large Coherent Processing Interval (CPI) is needed to avoid range ambiguity.

Advantages of LFMCW over these shortcomings from the two types of radar are:

- Precise target range calculation.

- Determination of the velocity of the selection target.

- Low measurement time and low computation complexity.

- Less affected by clutter and atmospheric conditions.

- Power rating is lower compared with that of Pulse Doppler.

- Continual results can be obtained as opposed to Pulse Doppler.

- Is not effected by blind speed situation.

- Can also be used to detect short range targets.

Evaluation of the above points elucidates the use of Linear Frequency Modulated CW for the current design of the MEMS Tri-mode radar system.

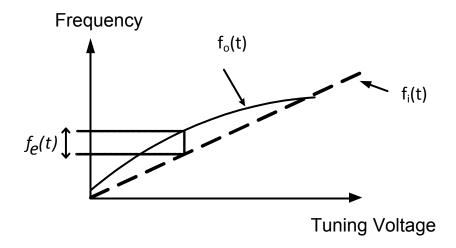

#### 2.5 Generating and tuning of the frequency

The RF radar signal is generating using a Voltage Control Oscillator (VCO). As it is in the case of Pulse Doppler and FSK CW radar a constant frequency pulse and CPI respectively are generated whereas for a LFMCW the VCO is attuned using a triangular modulating signal to output a frequency chirp. With the generation of Linear FM rises the concern for non-linearity errors in the output signals. The quality of the linear FM signals generated is extremely vital for radar purposes as it has influence on the radar range resolution and its accuracy to a certain degree [15]. The following equation defines the FM linearity:

Linearity

$$S = \frac{\left| f_e(t) \right|_{\text{max}}}{B}$$

(2.3)

Here  $f_e(t)$  is the difference between the instantaneous frequency of the actual output of the VCO  $f_o(t)$  and the ideal linear instantaneous frequency  $f_i(t)$  that is envisaged from the VCO ( i.e  $f_e(t) = f_o(t) - f_i(t)$  ). The term  $\left| f_e(t) \right|_{\max}$  denotes the maximum absolute value of  $f_e(t)$ . B is the bandwidth of the linear FM signal.

The non-linearity in the VCO also affects the performance of the system. Generally all analog VCOs exhibit some non-linear attributes because of the varactor non-linearity. A varactor is a

semiconductor device in which if a voltage is applied at the boundary of the semiconductor material and an insulator the device capacitance is affected. The following equation defines the transfer function of the VCO [16]:

$$K_o = f_e(t) - \Delta V \tag{2.4}$$

Where  $\Delta V$  is the change in the modulation voltage.

Figure 2.4 VCO Transfer function

# 2.6 Selection of the Development Platform for the Tri-Mode Radar Signal Processing System

The Transmitter control aggregates the radar signal generation, tuning and linearity of the waveform; attributes which are vital for the LFMCW radar as it needs linear frequency sweep. The signal generation and sweep modulation is done using a digital approach. Previously analog Phased Locked Loop (PLL) with a VCO was used for the chirp generation technique, but was replaced by digital technology. The choice to adapt a digital approach is because for radar system designs digital electronics vindicates better frequency response, excellent linearity in chirp generation and less susceptible to noise [16].

In the digital implementation of the transmitter for the proposed design the signal processing algorithm is based on Digital Signal Processor (DSP) and Field Programmable Gate Array (FPGA). The DSP part comprises of the window function, FFT, CA-CFAR and the target information calculation.

The analog portion of the design is done using the Analog to Digital Convertor (ADC) board (AD7x76/77CBZ). The throughput rate of the device is 3MSPS (Mega sample per second) and is a 12-bit 6-leadt TSOT package. It operates from a single 2.35 to 3.6V power supple. The ADC board has a low power consumption rate and also the clock speed management is very flexible. In addition to this the product comprises of a low noise, track-and-hold amplifier with a wide bandwidth which can handle input frequencies up to 55MHz. The analog input range can vary from 0 to VDD and has no delay during pipelining process. It can perform a standard successive approximation analog to digital conversion with accurate control of the data sampling with the  $\overline{CS}$  pin and the serial clock, allowing the device to interface with microprocessors or DSPs [17].

A Field Programmable Gate Array (FPGA) is a semiconductor device encompassed of many logic blocks with configurable interconnections between them. The firmware is a combination of hardware and software of which the software implies to the data or program written into a ROM (Read only Memory) needed to control the hardware. The programmable function logic of the FPGA can be compiled to work as basic logic gates such as AND, OR, XOR or INVERT. It is also possible to configure it for more complex functions such as decoders and simple mathematical functions. FPGAs are capable to perform pipelining and parallelization process.

FPGA are becoming extremely popular for their exceptional performance in radar system designs. Its ability to optimize intellectual property (IP) core implementations for acute compute-intensive digital signal processing algorithms like FFT has made it become one of the building blocks in advanced radar design [16], [18].

FPGA contributes in reducing implementation area and improve throughput by accepting nostandard word-length sizes and semi- or full-parallel signal processing. In addition FPGA based emulation platform can offer real-time prototyping of ASIC (Application Specific Integrated Circuits) logic which helps with the implementation and verification of the designed system in an environment related to the target system.

In DSP design, initially the development and analyzing of the algorithm is done in a floating-point environment such as C/C++ or MATLAB. The algorithm is then converted to a fixed-point model and the unison is verified. This is done because hardware specifications are based on fixed-point representations and are also used to manually create RTL models and test benches. The RTL design associates with the method of representing a sequential circuit as a set of registers and transfer functions which describe the data flow in between the registers. The design is usually simulated at the RTL level to confirm that it is functional. A complete design environment of FPGA is offered by Xilinx (ISE),

Altera and Mentor Graphics. Currently the use of intellectual property (IP) cores and customizable designware for common DSP functions like FIFO and FFT are available which helps to reduce development time and makes the system design more efficient [19].

From the study above it can be confirmed that the FPGA development platform is optimal for the radar design. A single mode radar sensor based on FPGA technology has already been designed by the MEMS team in the University of Windsor [20].

#### 2.7 State- of- the- art Automotive Radar

The automotive radar research first started in the late 50's and by 70's radar development started at the microwave frequencies, however it wasn't until in the 90's commercialism of the automotive radars began. The aim of the automotive industry is to configure sensor for comfort and safety purpose in terms of operation, robustness, reliability and dependence on unpropitious weather conditions, cost etc. Although passive safety systems like parking aid and airbag is very helpful in the reduction of road accidents but the implementation of active safety systems like Adaptive Cruise Control (ACC) and automotive braking system further mitigates the problem as they affect the vehicle dynamics directly.

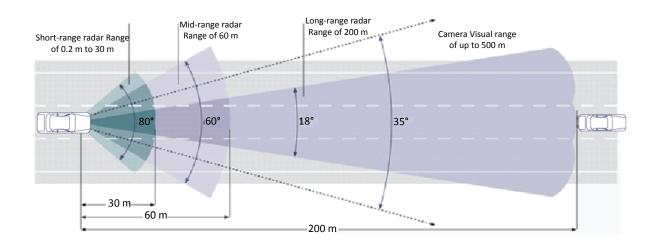

Among the first warning systems was the parking aids, collision warning systems and ACC. Greyhound installed more than 1600 24GHz radar sensors in their buses and experienced a 21% reduction in the number of accidents in 1993 compared with that in the previous year. In 1995 Japan was the first one to commercialize ACC where they favoured Lidar-ACC. In 1999 US Company Mercedes-Benz introduced the 77GHz "Distronic" into the S-class which was followed by other preeminent models like BMW 7 series, Jaguar (XKR, XK6), Cadillac (STS, XLR), Audi, A8 and Phaeton. In 2003 the Japanese Companies Toyota and Honda introduced active braking assistance system for preventing collision based on 77GHz Long Range Radar (LRR) technology. Mercedes-Benz improved their PRE-Safe break with the introduction of DISTRONIC plus in 2006 which makes use of two Short Range Radar (SRR) sensors behind the front bumper and a LRR sensor in the radiator grill to assist the driver to prevent collision by providing collision-warnings and assistance with the braking system [21]. The following figure shows the range covered by the DISTRONIC plus implemented in the new E-Class and model year 2009 S-Class Mercedes-Benz. The radar covers 200m for the LRR instead of the 150m previously used; also the new radar has Medium range coverage of 60m with 60 degree beam coverage. In addition to these the SRR sensors are still used with coverage of 80 degree beam width and range of 30m [22].

Figure 2.5 DISTRONIC Plus

In 2004 the European Commission delineated the frequency 77GHz- 81GHz as the allocated assigned frequency for the SRR [23]. However the use of 24GHz range for the SRR till 2018 has been made official by the European Union on June, 2011 giving it time to transit it to 79GHz technology. Studies by the automotive consortium SARA member showed that using radar-based brake assistance reduced the rear-end collisions by 20 percent and a further 25 percent reduction can be seen in the severity of the accidents [24]. The following figure shows the applications of SRR implemented in Mercedes-Benz:

Figure 2.6 Radar applications of the SRR

The transition to 77/79GHz technology for the SRR has prompted the German Federal Ministry of Education and Research (BMBF) to fund projects KOKON (2004 to 2007) and RoCC (Radar- on-

Chips) (2008-2011) to develop a cost efficient platform. The outcome of the research is the successful development of a low cost and sturdy platform based in the SiGe technology although further technical and operational studies need to be done to operate the sensor in real-time system [23].

A crucial facet for the integration of the radar sensor in vehicles is the component size. The dimension of the automotive radar is determined by the antenna aperture. For the 77GHz technology the antenna size can be decreased for a given beamwidth requirement enabling it to achieve a better angular resolution. On the other hand in order to achieve the same performance like that of the 77GHz technology, the 24GHz technology needs to increase the antenna size by three times. In future the short range radar will be designed with an absolute bandwidth of up to 4GHz, this renders to about 5% of the relative bandwidth with the 77GHz whereas it is about 17% using the 24GHz, thus making the design of antennas and wavelength related components easier. One other advantage for the choice of the 77GHz is that it allows the combination of high transmission power (> -40 dBm/MHz) and high bandwidth (> 250 MHz) which yield long range operation together with high distance separability concurrently; whereas is not possible at 24GHz technology [2].

With the increase in driver assistance systems in the current market more functions are being insinuated like improvement in the ACC, where the speed can be automatically varied or brought to complete zero depending on the situation. In addition to this other functions like lane changing assistance (LCA) and cross traffic alert (CTA) are also being introduced. In order for these multifarious aspects to functions the use of Medium range was announced in 2011 to be used in alliance with the LRR and SRR. To specify the MRR is used for the LCA and CTA. The following figures portrait the use of the LRR and MRR followed by illustrations of various technologies existing for driving assistance [2], [10].

Figure 2.7 Field of view and range covered for three functions

Table 2.1 gives a brief review of the existing radar sensors in the market with significant differential factors in between them [2].

| Parameter                 | Bosch<br>LRR3 | Conti<br>ARS 300 | Denso<br>DNMWR004 |

|---------------------------|---------------|------------------|-------------------|

| Dimensions                | 74x70x58 mm   | 120x90x49 mm     | 78x77x38 mm       |

| R <sub>max</sub> detected | 250 m         | 200 m            | 150 m             |

| Horizontal Field of View  | 30°           | 58°/17°          | 20°               |

| Number of beams           | 4             | 15/17            | 5                 |

| Beamsteering technique    | Fixed-beam    | Mechanical       | Electronic        |

| Multirange capability     | Single        | Multiple         | Single            |

Table 2.1 Comparisons between existing sensors in the current market

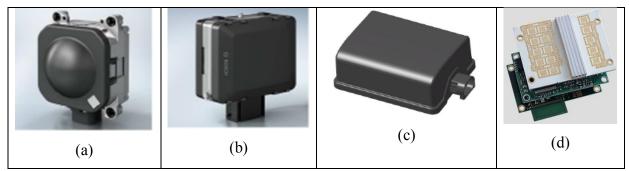

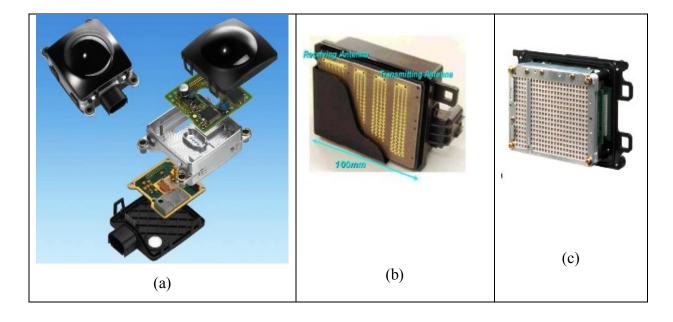

The Bosch LRR3 [Figure 2.8(a)] sensor was in the market since 2009 with the features like dielectric lens antenna providing high gain to achieve maximum distance of 250m. The device was the first in the market to use SiGe integrated circuits at 77GHz. Bosch also launched the MRR sensor [Figure 2.8 (b)] using SiGe MMIC. Among the first radar sensors was the ARS300 [Figure 2.8 (c)] by Continental, which was used by Mercedes. It key feature was the scanning antenna which was based on a dielectric waveguide like a constant rotating drum with a special grating structure [25]. A SRR sensor with an integrated planar antenna array was introduced by IMST in Low Temperature Cofired Ceramics (LTCC) technology [Figure 2.9 (c)] operating at 24GHz [26].

Figure 2.8 (a) Bosch LRR3 sensor (b) Bosch MRR sensor (c) Continental ARS300 (d) IMST SRR sensor

In Table 2.2 a brief overview of former generation radars are given with the name of their manufacturer and some key features; a report from Fujitsu Ten Ltd [27].

Table 2.2 Former generation radars highlighting some key features

| M anufacturer                   | 0 ur com pany | A D C           | Delphi          | Bosch      | Honda elesys | Denso      | H itach i      |

|---------------------------------|---------------|-----------------|-----------------|------------|--------------|------------|----------------|

| A ppearance                     |               | Acasti.         |                 |            |              |            |                |

| External Dimensions (nm)        | 89×107×86     | 136×133×68      | 137×67×100      | 91×124×79  | 123×98×79    | 77×107×53  | 80×108×64      |

| M odulation M ethod             | FM -CW        | FM Pulse        | FM ←W           |            | FM €W        | FM -CW     | 2-frequency CW |

| Detection                       | 4m to 120m    | A pprox.        | A pprox.        | 2m to 120m | 4m to 100m   | A pprox.   | A pprox.       |

| Range                           | or greater    | 1m to 150m      | 1m to 150m      | or greater | or greater   | 2m to 150m | 1m to 150m     |

| H orizontal<br>D etection Angle | ±8°           | A pprox.<br>±5° | A pprox.<br>±5° | ±4°        | ±8°          | ±10°       | ±8°            |

| Angle Detection                 | M echanical   | Beam            | M echanical     | Beam       | Beam         | Phased     | M1             |

| M ethod                         | Scan          | Conversion      | Scan            | Conversion | Conversion   | A rray     | M onopulse     |

| EHF Device                      | M M IC        | GUNN            | GUNN            | GUNN       | M M IC       | M M IC     | M M IC         |

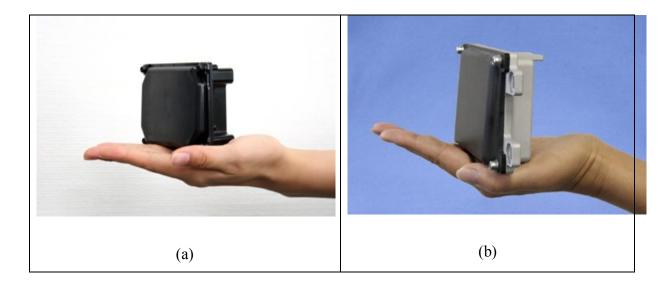

In a press release of October 2012 Fujitsu Ten Ltd declared about the development of compact 77GHz automotive radar with a 3D electronic scanning capability, which was a step up from the 2D millimeter wave radar (Press release October, 2010). However the product will be commercialized in the automotive market from 2014. The latest 3D automotive radar sensor will detect object in three dimensions i.e. it will cover "elevation" range together with distance and azimuth angle [28].

Figure 2.9 (a) 77GHz 3D Millimeter Wave Radar, (b) 76-GHz 2D Millimeter Wave Radar

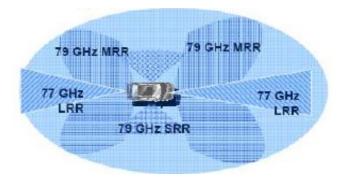

A next generation driver assist technology which the three range coverage ability for better safety purpose in given the figure below:

Figure 2.10 Layout of the next generation driver assistance applications

#### 2.8 Work done in LFMCW Radar sensor design with FPGA-based platform

Some the primary manufacturers of the 77 GHz LRR sensors are ADC, BOSCH, Delphi, Denso, TRW (Autocruise), Fujitsu Ten and Hitachi. In Figure 2.11(a) a BOSCH LRR second generation radar sensor is shown which uses an analog beamforming approach. The production of the sensor started from 2004 and uses a FMCW modulation with triangular waveform. Japanese companies introduced a radar sensor with digital beamforming in 2003 (Figure 2.11 (b)). Toyota CRDL && GHz LRR sensor also makes use of digital beamforming using nine digital receiver channels (Figure 2.11 (c)) [9].

Figure 2.11 (a) BOSCH 2nd Generation LRR (b) Denso's 77 GHz LRR (c) Toyota CRDL 77 GHz LRR

A prior study on FPGA-based LRR radar design using LFMCW radar signal processing algorithm is done in the University of Windsor using Xilinx Virtex-5 FPGA at 100MHz. The sampling time of the system was 6.78ms and the processing time of 211.63µs. From the resources used by the developer it was seen that using Virtex-5 FPGA board only 4% of sliced registers, 23% slice LUTs, 6% of DSP48 slices and 21% of the FPGA fabric area is used [20].

The aim of this thesis is to design a tri-mode radar sensor with a faster signal processing algorithm and also optimize the accuracy of the results obtained from both the software and hardware simulations alike.

#### **CHAPTER 3**

# **Target FMCW Radar Design Specifications**

In this chapter the mathematical models correlated with the FMCW radar is discussed in details and the relevant equations and expressions required to calculate the range and velocity of the detected targets are provided here. Detailed equation study for calculating range and velocity for both stationary and moving target scenario is discussed here. The operating parameters for the design are also identified from the mathematical studies done. A brief review is also done on additional concerns like atmospheric attenuations, temperature effects, false rate alarm, clutter removal and radar types.

#### 3.1 Identifying operating parameters for the system design

The state-of-the-art for automotive radar system requirements for long, medium and short range radar is listed in Table 3.1 [2]. The parameters considered in this thesis are bandwidth, range coverage, range resolution, range accuracy, velocity accuracy and velocity resolution.

Table 3.1 Sensor Classification for Tri-Mode Radar System

| Туре                            | LRR        | MRR         | SRR         |

|---------------------------------|------------|-------------|-------------|

| Maximum Transmit power (EIRP)   | 55dBm      | -9dBm/MHz   | -9dBm/MHz   |

| Frequency Band                  | 76-77GHz   | 77-81GHz    | 77-81GHz    |

| Bandwidth                       | 600MHz     | 600MHz      | 4GHz        |

| Distance range RminRmax         | 10-250m    | 1-100m      | 0.15-30m    |

| Distance Resolution ΔR          | 0.5m       | 0.5m        | 0.1m        |

| Distance accuracy <b>o</b> R    | 0.1m       | 0.1m        | 0.02m       |

| Velocity Resolution Δv          | 0.6m/s     | 06.m/s      | 0.6m/s      |

| Velocity accuracy δv            | 0.1m/s     | 0.1m/s      | 0.1m/s      |

| Angular accuracy δΦ             | 0.1°       | 0.5°        | 1°          |

| 3dB beamwidth in azimuth ±Φmax  | ±15°       | ±40°        | ±80°        |

| 3dB beamwidth in elevation vmax | ±5°        | ±5°         | ±10°        |

| Dimensions                      | 74X77X58mm | 50X50X50 mm | 50X50X20 mm |

With regard to the above table and [20] the target tri-mode radar signal processing system is required to correlate with at least the following performance:

(a) Range: for LRR 200m, for MRR 100m and for SRR 30m

(b) Range Accuracy < 0.1m

(c) Relative velocity: -100 to 250 km/h

(d) Velocity accuracy:  $\pm 0.1$  m/s

(e) Cycle time < 6.78ms

#### 3.2 Allocation of the LFMCW Waveform

After the detail discussion done in Chapter-2 the choice of FMCW radar was established. To be more specific the radar system chosen for this design is LFMCW which is a class of FMCW where the modulating waveform is linear. The FMCW radar however can implement other waveforms like sinusoidal, triangular and saw-tooth. The different types of radar waveforms generated are illustrated in Figure 3.1.

Figure 3.1 FMCW waveforms (a) Sine wave (b) Saw-tooth (c) Triangular

Sinusoidal waveform is rarely used for FMCW radar system because of the extra latency added in the computing and adjusting the wave coefficients. In addition the sine wave has less tolerance for VCO non-linearity when compared with the linear waveforms of FMCW. Although at lower operating frequencies analog modulation is possible without the need for waveform generations using digital approach.

The saw-tooth (or ramp) waveform provides only positive frequency sweep, which makes the control and electronic tuning uncomplicated. However for moving targets, the problem of range Doppler coupling arises when using the saw-tooth modulation technique [29].

The approbate technique for the design was found to be triangular modulation as the range and velocity could be calculated simultaneously. In the triangular waveform with the difference between the two equal upslope and downslope linear sweeps tantamount to twice the Doppler shift of the detected target, consequently allowing the calculation of both range and radial velocity. The other advantage of using the triangular modulation is that the different sweep directions make the system better resistant to stationary clutter and jamming signals as they have more dynamic instantaneous frequency.

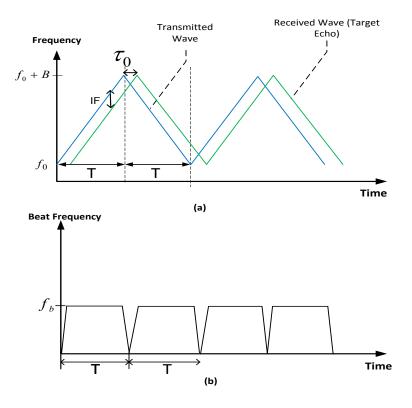

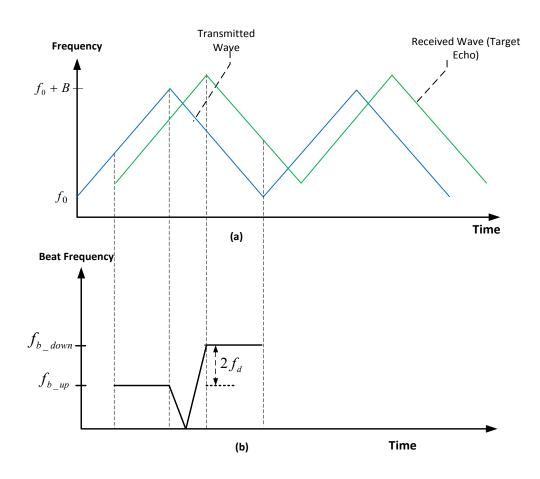

## 3.3 The Linear Frequency Modulated Continuous Wave (LFMCW) Radar

The LFMCW technique permits the use of linear frequency sweeps (or chirp) over a selected bandwidth and measure the range and velocity using the beat frequencies from all the targets detected within the FoV (Field of View) of the radar beam. The beat frequency is the difference between the transmitted and received radar signal:

$$f_b(t) = f_t(t) - f_v(t)$$