### University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

1994

# Hardware realization of real-time two-dimensional IIR filters for broadcast TV images.

Herbert Joseph. Kaufman *University of Windsor*

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### Recommended Citation

Kaufman, Herbert Joseph., "Hardware realization of real-time two-dimensional IIR filters for broadcast TV images." (1994). *Electronic Theses and Dissertations*. Paper 2273.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontano K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontano) K1A 0N4

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

مريحيا فومي مرمين البراجيج

Commence of the second

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

### Canadä

### HARDWARE REALIZATION OF REAL-TIME TWO-DIMENSIONAL IIR FILTERS FOR BROADCAST TV IMAGES

by

Herbert J. Kaufman

A Dissertation

submitted to the

Faculty of Graduate Studies and Research

through the Department of

Electrical Engineering in Partial Fulfilment

of the requirements for the degree

of Doctor of Philosophy at

the University of Windsor

Windsor, Ontario, Canada 1993

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontano K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontano) K1A 0N4

granger - grane dependent

Car has been been suppressed in

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-93280-5

#### ABSTRACT

In this dissertation, architectures, hardware design and prototypes for the realization of 2-D filters are presented. These filtering architectures are capable of attaining real-time processing rates for advanced television systems and are economical in terms of hardware cost, fabrication cost, and power consumption.

Sample-and-hold type realizations, operating on 2-D sampled data, based on the standard 2-D discrete-time transfer function  $H(z_1,z_2)$  are presented. Both IIR and FIR realizations are developed in terms of high-speed systolic architectures. The design process culminates in the development of a 2 x 2 recursive prototype.

Instead of using the standard discrete-time transfer function it is also possible to develop 2-D filters based on a 2-D hybrid transfer function H(z,s) which involves both z-domain and s-domain variables. These are highly suitable for filtering a raster scanned image, which can be characterized as an input signal X(z,s), which is a function of these same two variables. Design considerations are presented which culminate in the development of a 1 x 1 recursive prototype.

The sample-and-hold systolic architecture was employed together with switched-capacitor circuit techniques to develop a 2-D real-time switched-capacitor recursive filter. This type of filter features greater accuracy than a conventional analog circuit as well as advantages for VLSI implementation.

In addition to presenting novel design methodologies for hardware prototypes, a novel function block approach for the SPICE simulation of 2-D modular systems with true 2-D data

is provided. This approach will serve to greatly facilitate 2-D filter development and improve the efficiency of the design cycle.

#### **ACKNOWLEDGEMENTS**

I would like to express my deep gratitude and sincere appreciation to Dr. M.A.

Sid-Ahmed, my supervisor, for his guidance, support, advice, encouragement and commitment throughout the course of this research.

I would also like to thank Professors: Soltis, Alexander and Toews for serving on my committee and providing helpful suggestions, and comments.

Finally, I wish to thank my colleague, Dr. John Cardillo, for his support, encouragement and helpful suggestions.

#### TABLE OF CONTENTS

| ABST   | RACT                        | •            | •         | •          | •         |         |         | •       | •         | ii   |

|--------|-----------------------------|--------------|-----------|------------|-----------|---------|---------|---------|-----------|------|

| ACKI   | NOWLEDGEMENT                | rs .         | •         |            | •         |         |         | •       | •         | iv   |

| TABL   | E OF CONTENTS               |              | •         | •          |           |         |         |         | •         | v    |

| LIST   | OF FIGURES                  | •            | •         | •          | •         |         |         |         |           | vii  |

| I:     | INTRODUCTION                | N .          | •         |            | •         | •       |         | •       |           | 1    |

| 1-1    | Background                  |              |           |            |           |         |         |         |           | 1    |

| 1-2    | Literature Survey           | •            |           | -          | •         | •       | •       | •       | •         | 4    |

|        | Fundamental Cond            | cepts        | -         | -          | _         |         | •       | •       | •         | 4    |

|        | Direct Realizations         | •            |           | -          |           | •       | •       | •       | •         | 8    |

| 1-2.3  | Realization from C          | -<br>Continu | ed and F  | Partial Fr | raction E | Expans  | sion    | •       | •         | 12   |

|        | Architectures for 2         |              |           |            |           |         |         | _       | •         | 13   |

| 1-2.4. |                             |              | -         | ipath 2-I  | Digita    | l Filte | ring    | •       |           | 13   |

| 1-2.4. |                             |              |           |            |           |         |         | _       | <u>.</u>  | 18   |

| II:    | REALIZATION (<br>TECHNIQUES |              |           |            |           | ·       |         | MAD-11  |           | 25   |

| 2-1    | Introduction .              | •            |           | •          |           |         |         | •       | •         | 25   |

| 2-2    | Details of Hardwa           | re Desi      | gn with   | Applicat   | tion to H | Iomor   | norphic | Filteri | ng .      | 35   |

| 2-2.1  | 2-D Semi-Systolic           |              | •         | •          | •         |         | •       |         |           | 35   |

| 2-2.2  | Design of 1H Dela           | ay Line      |           | •          | •         | •       | •       | •       | •         | 38   |

| 2-2.2. | 1 The                       | CCD I        | ic.       | •          | •         |         |         |         | •         | 42   |

| 2-2.2. |                             | ltiplexe     | d vs. Se  | rial Mod   | le Opera  | ition . | •       | •       | •         | 43   |

| 2-2.2. | 3 Clo                       | ck Driv      | er Circu  | uit .      | •         |         |         | •       | •         | 43   |

| 2-2.2. | 4 Inpi                      | ut Coup      | ling Cir  | cuit and   | Biasing   |         | •       | •       | •         | 47   |

| 2-2.2. | 5 Out                       | put Co       | upling C  | ircuit     | •         | -       | •       | •       | •         | 47   |

| 2-2.2. | 6 Lov                       | v Pass I     | Filter    | •          | •         | •       | •       | •       | •         | 47   |

| 2-2.3  | Design of PE.               | •            |           | •          | •         | •       | •       | •       | •         | 47   |

| 2-3    | Homomorphic Filt            | ering        | •         | •          |           | •       |         | •       | •         | 51   |

| 2-4    | SPICE Simulation            | of the       | 2-D Sen   | ni-Systol  | ic Filter | Struc   | ture    | •       | •         | 58   |

| 2-4.1  |                             |              |           | •          |           | •       |         | •       | •         | 58   |

| 2-4.2  | SPICE Modelling             | of the (     | Overall 2 | 2-D Sam    | ple-and-  | -Hold   | Semi-S  | ystolic | Structure | e 68 |

| 2-4.3  |                             |              |           | te 2-D     | Systoli   | c Stru  | cture   | •       | •         | 76   |

| 2-5    | The Hardware Ass            | •            | •         | •          | •         | •       |         | •       |           | 79   |

| 2-5.1  |                             | erter        | •         | •          | •         |         |         | •       | •         | 79   |

| 2-5.2  | •                           | •            | •         | •          | •         | •       |         | •       |           | 80   |

| 2-6    | Filtering of Image          | ς .          |           |            |           |         |         |         |           | 82   |

|                                                     |                                                                                                           |                                                                        |                                   |         |            |        |              |                 |       | vi                                            |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------|---------|------------|--------|--------------|-----------------|-------|-----------------------------------------------|

| 2-7                                                 | Cost of Realization                                                                                       | on - Digita                                                            | l vs. Ana                         | log     | -          | •      | ••           |                 | •     | 85                                            |

| 2-8                                                 |                                                                                                           |                                                                        |                                   |         |            | •      | •            | •               | •     | 87                                            |

| пі:                                                 | REALIZATION                                                                                               |                                                                        |                                   |         | AL HY      | BRID I | IIR FIL      | TERS.           |       | 88                                            |

| 3-1                                                 | Introduction .                                                                                            |                                                                        | _                                 |         |            | •      | •            | •               | •     | 90                                            |

|                                                     | A Realization .                                                                                           | •                                                                      | -                                 |         |            |        | •            | •               | •     | 93                                            |

|                                                     | Details of the Ha                                                                                         | rdware Da                                                              | sien                              |         | •          | -      | •            | •               | -     | 93                                            |

|                                                     | Design of Analog                                                                                          |                                                                        |                                   |         |            |        | •            |                 | •     | 93                                            |

|                                                     | Design of 1H De                                                                                           |                                                                        |                                   |         | •          | •      | •            | •               | •     | 101                                           |

| 3-3                                                 | SPICE Simulation                                                                                          |                                                                        |                                   |         |            |        | •            |                 |       | 102                                           |

| 3-3 1                                               | A SPICE Model                                                                                             |                                                                        | emi-Systo                         | lic Hyt | rid Filt   | ers    | •            | •               | •     | 102                                           |

| 3-3.1.                                              | Simulatio                                                                                                 | n of the SI                                                            | PICE PE                           | •       |            |        | •            | •               | •     | 109                                           |

| 3-4                                                 | A Hardware Pro                                                                                            |                                                                        |                                   |         |            | •      | •            | •               |       | 112                                           |

| 3-4.1                                               | Evaluatio                                                                                                 |                                                                        | -                                 |         |            | •      | •            | •               | •     | 116                                           |

| 3-5                                                 | Conclusion .                                                                                              | •                                                                      | •                                 |         |            | •      | •            | •               | •     | 117                                           |

|                                                     |                                                                                                           |                                                                        |                                   |         |            |        |              |                 |       |                                               |

| rv:                                                 | SWITCHED-CARATES                                                                                          | APACITO<br>-                                                           | R IMPL                            | EMEN    | TATIO      | NS OF  | F 2D FI      | LTERS<br>•      | FOR V | / <b>IDEO</b><br>118                          |

|                                                     | RATES                                                                                                     | APACITO                                                                | R IMPL                            | EMEN    | TATIO<br>· | NS OF  | F 2D FI<br>- | LTERS           | •     | 118                                           |

| 4-1                                                 | RATES Introduction .                                                                                      | •                                                                      | •                                 |         | TATIO<br>· | NS OF  | F 2D FI<br>- | LTERS           | •     | 118<br>118                                    |

| 4-1<br>4-2                                          | RATES Introduction . The 2-D Semi-S                                                                       | ystolic Rez                                                            |                                   |         |            | NS OF  | F 2D FI      | LTERS<br>·<br>· | •     | 118                                           |

| 4-1<br>4-2<br>4-3                                   | RATES Introduction . The 2-D Semi-S A Switched-Cap                                                        | ystolic Rea<br>acitor Real                                             | dization<br>ization               |         | TATIO      | NS OF  | F 2D FI      | LTERS           | •     | 118<br>118<br>120                             |

| 4-1<br>4-2<br>4-3<br>4-3.1                          | RATES Introduction . The 2-D Semi-S A Switched-Cap Design o                                               | ystolic Real<br>acitor Real<br>f Line Del                              | . dization ization ay.            |         | •          | NS OF  | F 2D FI      | LTERS           | •     | 118<br>118<br>120<br>122                      |

| 4-1<br>4-2<br>4-3<br>4-3.1<br>4-3.2                 | RATES Introduction . The 2-D Semi-S A Switched-Cap Design o Realization                                   | ystolic Rea<br>acitor Real<br>f Line Deli<br>on of PE in               | . dization ization ay . i SC Circ |         | •          | NS OF  | F 2D FI      | LTERS           | ·     | 118<br>118<br>120<br>122<br>123<br>125        |

| 4-1<br>4-2<br>4-3<br>4-3.1<br>4-3.2<br>4-3.3        | RATES Introduction . The 2-D Semi-S A Switched-Cap Design o Realization                                   | ystolic Real<br>acitor Real<br>f Line Del                              | . dization ization ay . i SC Circ |         | •          | NS OF  | F 2D FI      | LTERS           | ·     | 118<br>118<br>120<br>122<br>123               |

| 4-1<br>4-2<br>4-3<br>4-3.1<br>4-3.2                 | RATES Introduction . The 2-D Semi-S A Switched-Cap Design o Realization                                   | ystolic Rea<br>acitor Real<br>f Line Deli<br>on of PE in               | . dization ization ay . i SC Circ |         | •          | NS OF  | F 2D FI      | LTERS           | ·     | 118<br>118<br>120<br>122<br>123<br>125<br>131 |

| 4-1<br>4-2<br>4-3<br>4-3.1<br>4-3.2<br>4-3.3        | RATES Introduction . The 2-D Semi-S A Switched-Cap Design o Realization                                   | ystolic Real<br>acitor Real<br>f Line Deli<br>on of PE in<br>tput Summ | . dization ization ay . i SC Circ |         | •          | NS OF  | F 2D FI      | LTERS           | ·     | 118<br>118<br>120<br>122<br>123<br>125<br>131 |

| 4-1<br>4-2<br>4-3<br>4-3.1<br>4-3.2<br>4-3.3<br>4-4 | RATES Introduction . The 2-D Semi-S A Switched-Cap Design o Realization Bank Out Conclusion .  CONCLUSION | ystolic Real<br>acitor Real<br>f Line Deli<br>on of PE in<br>tput Summ | . dization ization ay . i SC Circ |         | •          | NS OF  | F 2D FI      | LTERS           | ·     | 118<br>118<br>120<br>122<br>123<br>125<br>131 |

<del>-</del>--

#### LIST OF FIGURES

| Figure 1-1  | The basic elements for signal processing                          | •         | . 6  |

|-------------|-------------------------------------------------------------------|-----------|------|

| Figure 1-2  | Input and output masks for 2nd order filter                       |           | . 7  |

| Figure 1-3  | A direct form realization                                         | •         | . 9  |

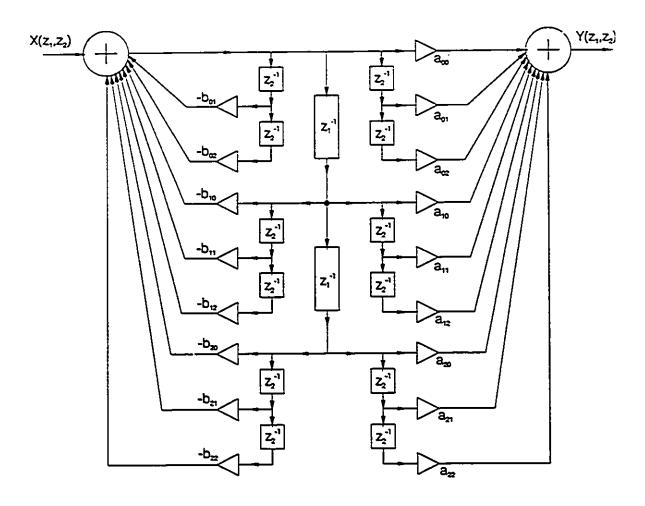

| Figure 1-4  | A direct form 2-D Canonic realization (2 x 2) case type I         | •         | . 10 |

| Figure 1-5  | An alternate direct form 2-D Canonic realization (2 x 2) case     | e type II | . 11 |

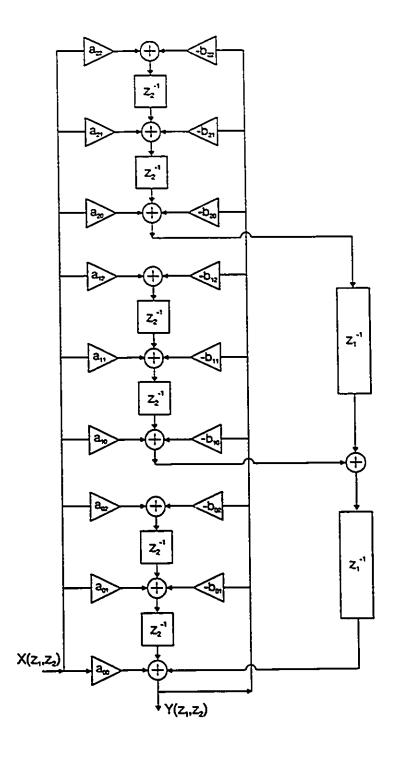

| Figure 1-6  | Realization of 5 x 5 FIR filter example                           |           |      |

|             | - High Speed Delayed Multipath 2-D                                | •         | . 16 |

| Figure 1-7  | Realization of the general sub-block $A_{ii}(z_1^{-2}, z_2^{-1})$ |           | . 17 |

| Figure 1-8  | Systolic implementation of polynomial evaluation                  | •         | . 19 |

| Figure 1-9  | 2-D systolic architecture (Sid-Ahmed [12])                        |           | . 21 |

| Figure 1-10 | 2-D systolic architectures given in [14]                          | •         | . 23 |

| Figure 2-1  | Partial realization of $z_2^{-1} Y_i(z_1, z_2)$                   | •         | . 29 |

| Figure 2-2  | Processing element (PE)                                           | •         | . 29 |

| Figure 2-3  | Realization of $M \times N$ IIR semi-systolic filter              | •         | . 30 |

| Figure 2-4  | A 1-D realization                                                 | •         | . 33 |

| Figure 2-5  | "Coefficient" function realizations                               | •         | . 34 |

| Figure 2-6  | 2 x 2 semi-systolic filter structure for prototype                | •         | . 36 |

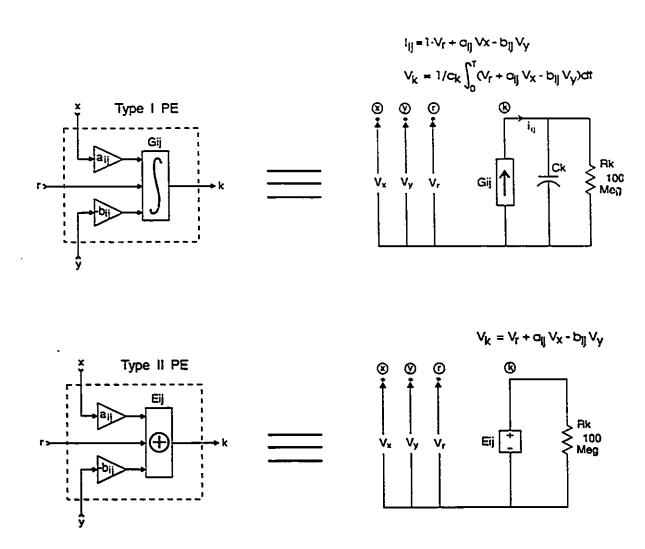

| Figure 2-7  | The two types of PE for use in practical hardware prototype       |           | . 37 |

| Figure 2-8  | Block diagram of CCD type 1H line delay                           | •         | . 39 |

| Figure 2-9  | Block diagram of CCD321 IC                                        | •         | . 40 |

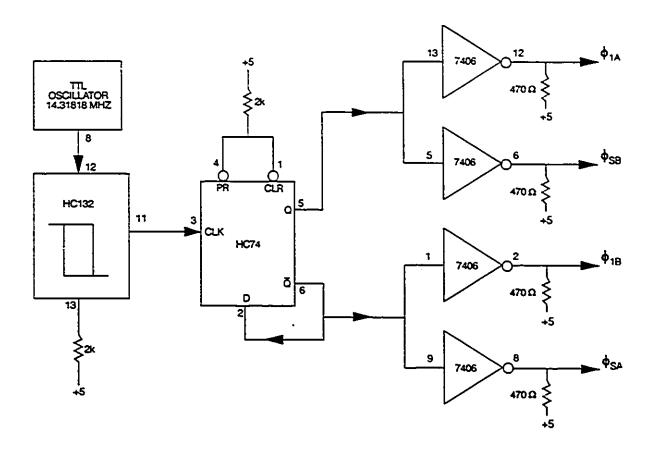

| Figure 2-10 | Clock driver circuit for multiplex CCD                            | •         | . 45 |

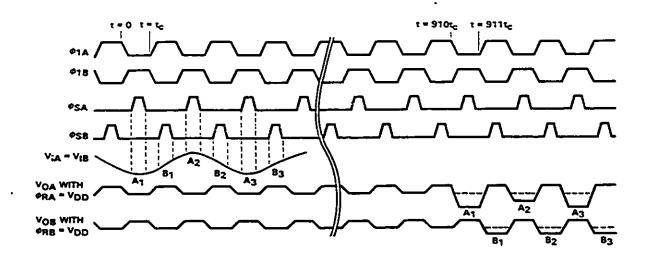

| Figure 2-11 | Timing diagram for the CCD IC in the multiplexed mode.            | •         | . 46 |

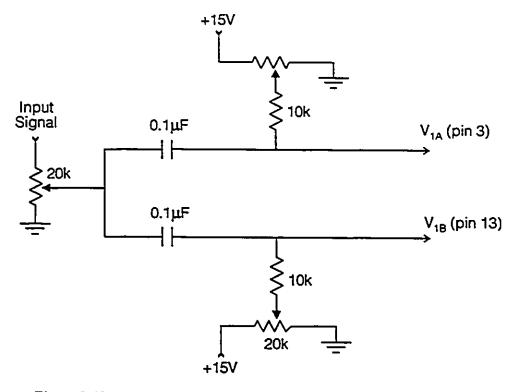

| Figure 2-12 | Input coupling circuit for multiplexed CCD                        | •         | . 49 |

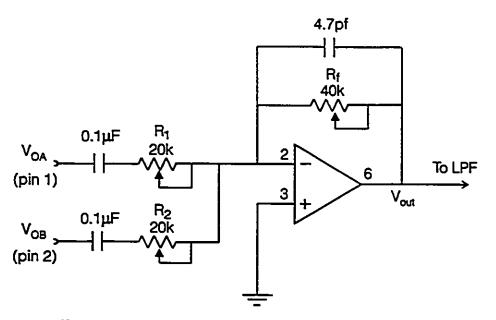

| Figure 2-13 | Output coupling circuit for multiplexed CCD                       |           | . 49 |

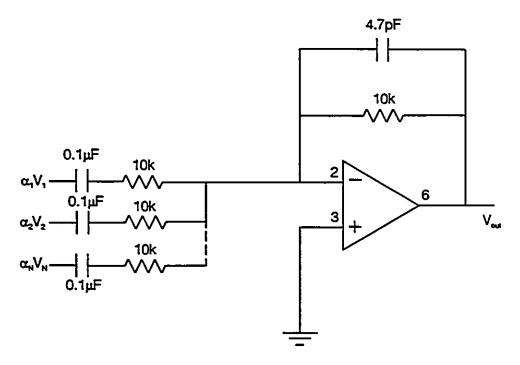

| Figure 2-14 | Low Pass Filter Removes CCD clock feedthrough .                   | •         | . 50 |

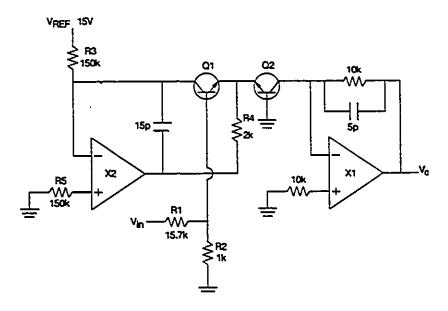

| Figure 2-15 | <del>-</del>                                                      |           | . 51 |

| Figure 2-16 | Homomorphic Filter                                                | •         | . 55 |

| Figure 2-17 | Cross-section of circularly symmetric 2-D Butterworth filter      | function  |      |

| J           | used in homomorphic filtering. $D(u,v)$ is the distance from      |           | . 55 |

| Figure 2-18 |                                                                   |           | . 56 |

| Figure 2-19 |                                                                   | •         | . 57 |

| Figure 2-20 | PE realization in analog form                                     | •         | . 59 |

| Figure 2-21 | SPICE model for the PE of Figure 2-20                             | •         | . 60 |

| Figure 2-22 | SPICE netlist for single PE simulation using idealized op-ar      | np model  | . 61 |

| Figure 2-23 |                                                                   | •         | . 65 |

| Figure 2-24 | <u> </u>                                                          | ro-model  | . 66 |

| Figure 2-25 | <u> </u>                                                          |           | . 67 |

| Figure 2-26 |                                                                   | •         | . 70 |

| Figure 2-27 | · · · · · · · · · · · · · · · · · · ·                             | ire 2-26  | . 71 |

| Figure 2-28 |                                                                   | •         | . 72 |

| Figure 2-29 |                                                                   | •         |      |

| 0           | semi-systolic filter structure                                    |           | . 75 |

| Figure 2-30 |                                                                   | •         | . 81 |

| -5          | • • • • • • • • • • • • • • • • • • •                             |           |      |

|   |             |                                                                 |       |   | VIII |

|---|-------------|-----------------------------------------------------------------|-------|---|------|

| F | igure 2-31  | High-speed antilog circuit                                      |       | • | . 81 |

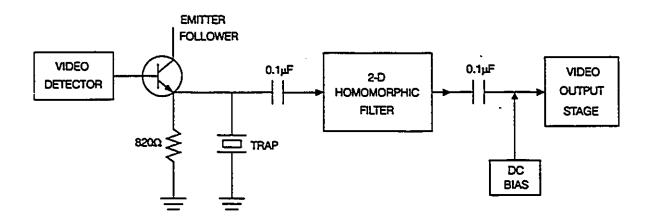

|   | igure 2-32  | Insertion of filter prototype into TV receiver circuitry        | •     | • | . 82 |

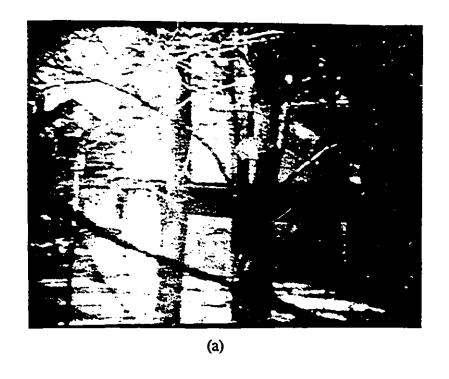

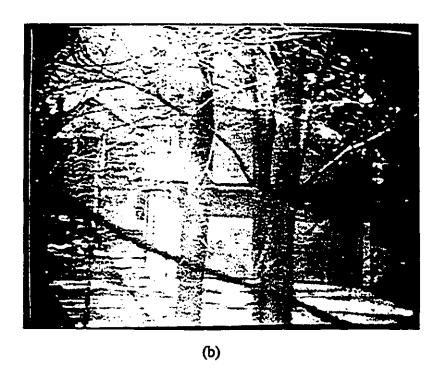

|   | igure 2-33  | (a) Original broadcast TV image. (b) Image homomorphic          | ally  |   |      |

| • | .gu.e 2 55  | filtered by prototype                                           |       |   | . 83 |

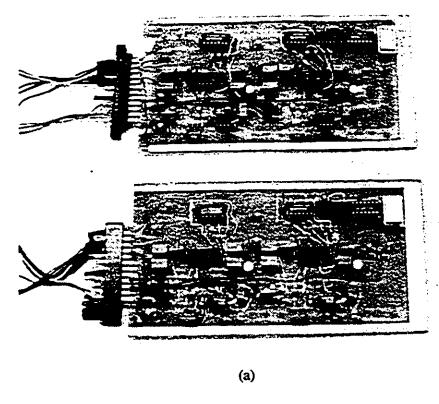

| F | igure 2-34  | (a) Line delays on dual delay CCD boards.                       |       |   |      |

| • | 150.023     | (b) Homomorphic filter prototype                                | •     | • | . 84 |

| F | igure 2-35  | Cost of realization - digital vs. analog components.            | •     |   | . 86 |

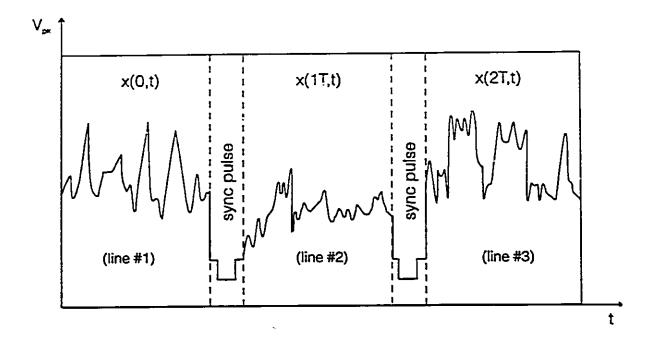

|   | igure 3-1   | Raster scanned signal as a 2-D semi-discrete-time signal        | •     | • | . 89 |

|   | igure 3-2   | A 2-D analog filter realization                                 |       | • | . 91 |

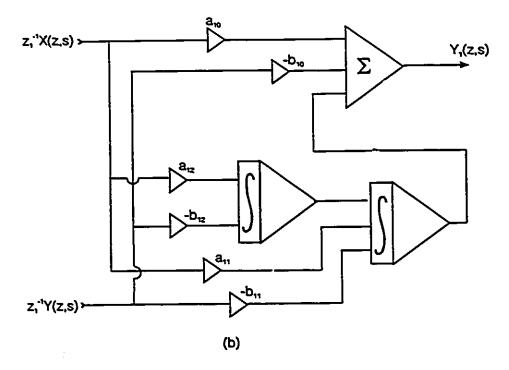

|   | igure 3-3   | 2-D recursive 1 x 1 filter realization.                         | •     | • | . 95 |

|   | igure 3-4   | Fast Inverter                                                   | _     | • | . 98 |

|   | igure 3-5   | Fast summing amplifier                                          | •     | • | . 98 |

|   | igure 3-6   | Fast integrator.                                                | •     | • | . 99 |

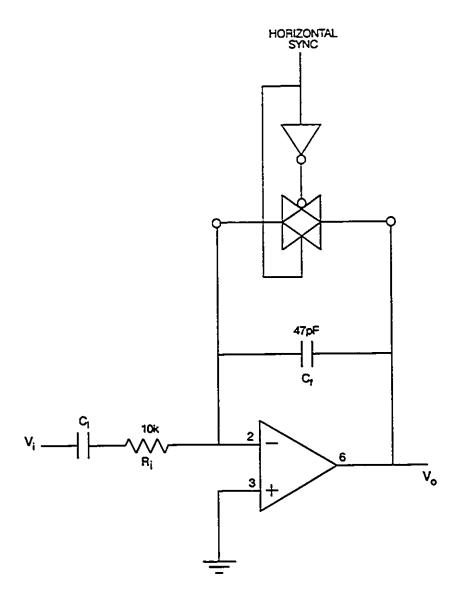

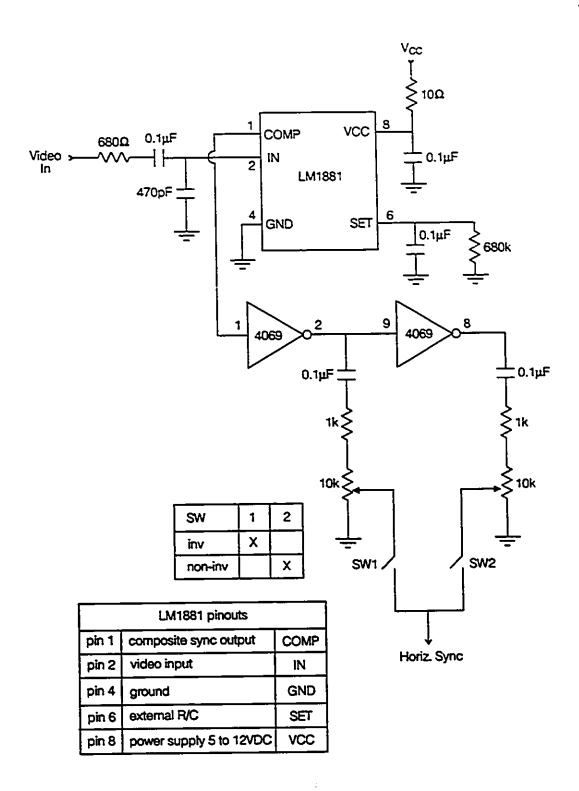

|   | igure 3-7   | Sync separator circuit                                          | •     | • | 100  |

|   | igure 3-8   | SPICE model of the 2 x 2 semi-systolic structure based or       | n the |   |      |

|   | -3          | 2-D hybrid transfer function                                    | •     |   | 105  |

| F | igure 3-9   | Function block SPICE models for PE types I and II               |       | • | 106  |

|   | igure 3-10  | SPICE netlist for simulation of 2-D IIR semi-systolic           |       |   |      |

|   | J           | hybrid filter structure                                         | •     | • | 107  |

| F | igure 3-11  | SPICE PE (type I) simulation model - 2-D hybrid filter          | •     | • | 110  |

|   | igure 3-12  | SPICE PE (type I) netlist                                       |       | • | 111  |

|   | igure 3-13  | 2-D hybrid analog filter prototype (photo)                      | •     | • | 113  |

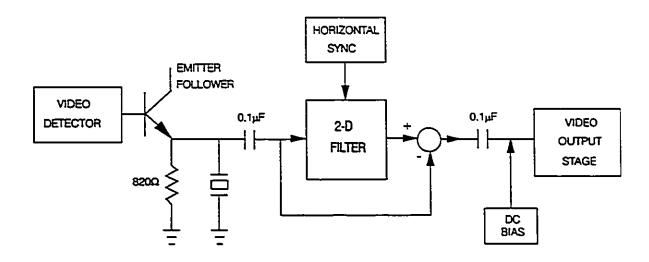

|   | igure 3-14  | Insertion of 2-D hybrid analog filter prototype into            |       |   |      |

|   | Ü           | TV luminance channel                                            | •     | • | 114  |

| F | igure 3-15  | Image filtered with 2-D hybrid analog filter prototype          | •     | • | 115  |

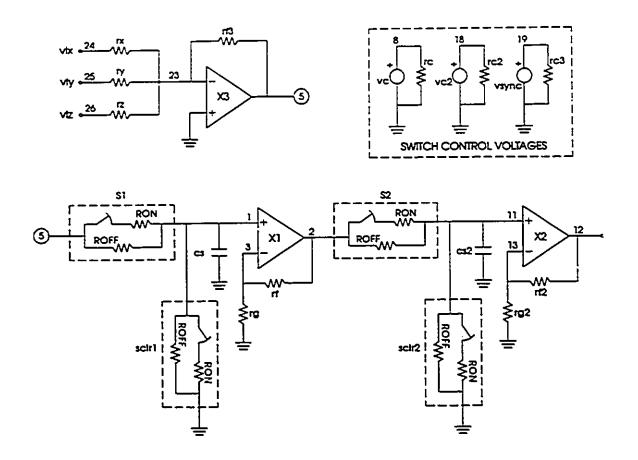

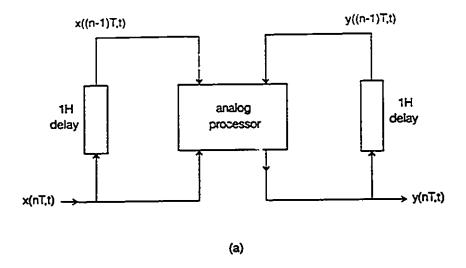

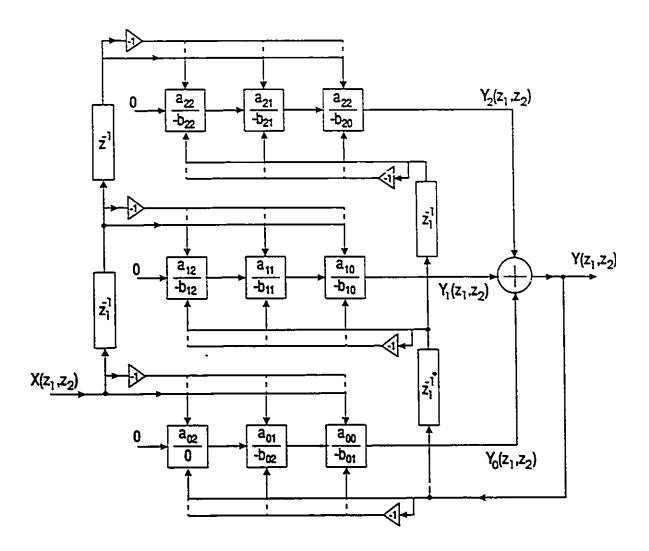

| F | igure 4-1   | Block diagram representation of a 2-D semi-systolic struc       | ture  |   |      |

|   |             | $(M \times N = 2 \times 2) \qquad . \qquad . \qquad . \qquad .$ | •     | • | 121  |

| F | igure 4-2   | PE symbol and its block diagram realization .                   | •     | • | 121  |

| F | igure 4-3   | Serial-Parallel-Serial configuration for 1H line delay          | •     | • | 124  |

| F | igure 4-4 🔤 | Analog feedback-readout capacitor memory for use in             |       |   |      |

|   |             | SPS type 1H line delay                                          | •     | • | 124  |

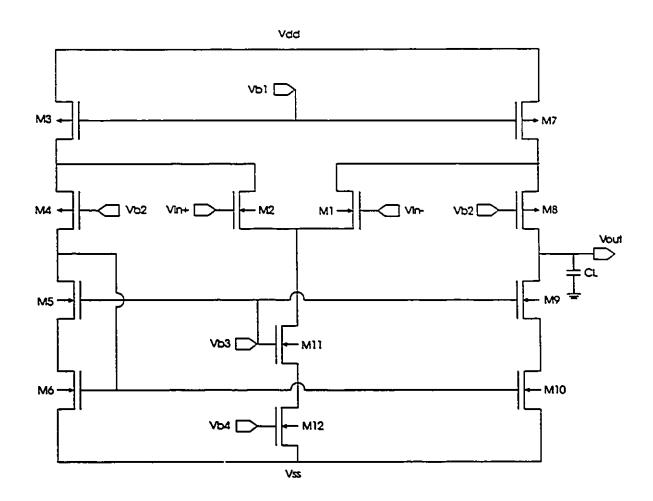

| F | igure 4-5   | A CMOS folded-cascode one stage op-amp                          | •     | • | 126  |

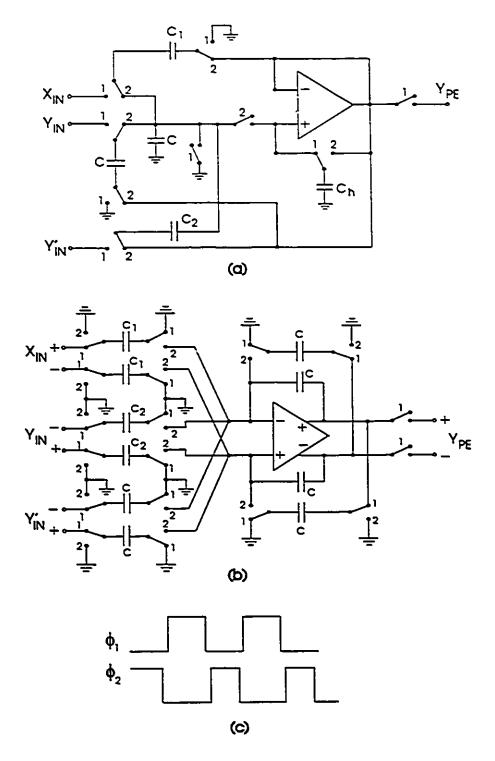

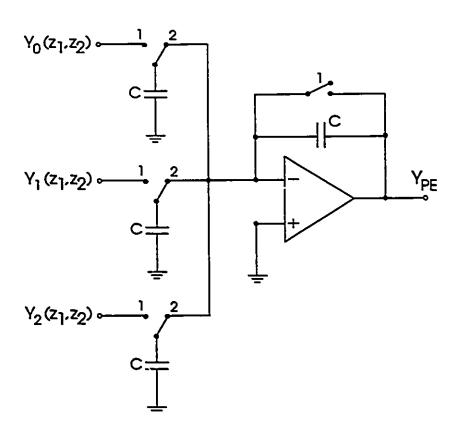

|   | igure 4-6   | SC PE realization                                               | •     | • | 128  |

|   | igure 4-7   | 2 x 2 semi-systolic structure with dual broadcast lines         | •     | • | 130  |

|   | ioure 4-8   | Switched-capacitor addition of partial results (2 x 2 case)     |       |   | 131  |

`..

--

#### INTRODUCTION

#### 1-1 BACKGROUND

In the development of new receivers for television, more advanced signal processing techniques will be implemented in the circuitry of the video processing section. It has been proposed that such advanced video signal processing can be carried out by high-speed two-dimensional (2-D) spatial filtering or by so-called motion adaptive temporal filtering [1] Newer receivers will display pictures that have higher pixel resolution. For what has been termed High Definition Television (HDTV), if the processing is done in *real-time*, that is, at the same rate as the effective sampling rate of the picture, processing rates in excess of 40 million pixels/sec would be required (e.g. 1000 lines/field x 50 fields/sec, 5:3 aspect ratio, interlaced).

In the past analog signal processing techniques have been based on one-dimensional time domain approaches implemented as simple Finite Impulse Response (FIR) signal processing structures. These have been quite limited as to the type of signal processing and enhancement operations that could be performed by the characteristic type of apparatus resulting from that approach.

More sophisticated signal processing is possible by means of the direct application of techniques for filtering 2-D data, known from the field of Mathematical Image Processing

Theory. Various techniques for the enhancement of digital images are usually implemented by

programming a general purpose computer to operate on stored digitized images off-line. These 2-D filtering techniques can be implemented in real-time by means of dedicated hardware [2]. Due to hardware constraints, conventional designs of dedicated 2-D filters have favored FIR filters even though IIR (Infinite Impulse Response) filters are known to be more efficient allowing lower order realizations than their FIR counterparts.

Considerations of hardware complexity, physical size of apparatus, power consumption, and economical manufacture are all of vital importance in any practical signal processing apparatus intended for use in consumer products.

The present thesis introduces dedicated hardware for real-time 2-D filtering which is based on a semi-systolic analog structure realization. The hardware realizations considered are based directly on the 2-D digital transfer function  $H(z_1,z_2)$ , and 2-D hybrid transfer function H(z,s) and are economical and efficient. Both IIR and FIR filtering structures can be realized with the approaches considered and high real-time rates can be attained through the use of analog components that have inherently small delay times. The development of systolic filtering architectures offers advantages for VLSI implementation such as modularity, regularity, and high parallelism. Even greater amenability to VLSI implementation along with high accuracy are obtained through the application of switched-capacitor circuit techniques to these architectures.

Recently, motion adaptive digital filters have been proposed for use in high-definition television video signal processing. They require delays of one or more field periods, such delays being accomplished by means of frame stores. Since pixels in separate fields are combined, this type of signal processing is referred to as temporal filtering [1] and can only be

performed on those pixels for which no motion in the scene of the picture being displayed has occurred between fields.

The approaches considered in the present thesis do not require analog to digital (A/D) and digital to analog (D/A) converters, often used in conjunction with analog pre-filters and post-filters, to convert video signal data from analog raster scanned form to sampled digital data for processing; nor do they require expensive frame stores or motion detection circuitry.

Other methods of performing real-time 2-D signal processing have been based on elaborate algorithms such as the Burt Pyramid [3] which separates an image into a number of 2-D spatial frequency bandpass images. This method, although capable of real-time operation, has the disadvantage of greater complexity and correspondingly higher cost, relative to the methods considered in the present dissertation, due to the need to process multiple bands and to generate a set of component images. When this approach is applied using digital hardware, a large amount of circuitry is required along with the need for A/D, and D/A converters.

#### 1-2 LITERATURE SURVEY

In this chapter we introduce the basic concepts of 2-D filter realization from a literature survey.

#### 1-2.1 FUNDAMENTAL CONCEPTS

A 2-D FIR (finite impulse response) filter of general order  $M \times N$  is given by the transfer function

$$H(z_1, z_2) = \sum_{i=0}^{M} \sum_{j=0}^{N} a_{ij} z_1^{-i} z_2^{-j}$$

(1-1)

where  $\{\{a_{ij}\}, \{b_{ij}\}\}\$  are the filter coefficients, and

$$H(z_1, z_2) = \frac{Y(z_1, z_2)}{X(z_1, z_2)} \tag{1-2}$$

is the ratio of output to input in the z-domain. If the upper limits of the summations in equation (1-1) are both equal to N, then the input and output data are square arrays.

Throughout this paper, the z-transform of a 2-D sequence x(m,n) is defined by

$$X(z_1, z_2) = \sum_{m=-\infty}^{\infty} \sum_{n=-\infty}^{\infty} x(m, n) z_1^m z_2^n$$

(1-3)

A 2-D IIR (infinite impulse response) filter of order  $M \times N$  has the transfer function

$$H(z_1, z_2) = \frac{Y(z_1, z_2)}{X(z_1, z_2)} = \frac{\sum_{i=0}^{M} \sum_{j=0}^{N} a_{ij} z_1^{-i} z_2^{-j}}{\sum_{i=0}^{M} \sum_{j=0}^{N} b_{ij} z_1^{-i} z_2^{-j}} + \sum_{i=0}^{M} \sum_{j=0}^{N} b_{ij} z_1^{-i} z_2^{-j}}$$

$$(1-4)$$

The recursive equation governing the relationship of the input x to the output y is given

by

$$y(m,n) = \sum_{i=0}^{M} \sum_{j=0}^{N} \alpha_{ij} x(m-i,n-j) - \sum_{i=0}^{M} \sum_{j=0}^{N} b_{ij} y(m-i,n-j)$$

$$i+j\neq 0$$

(1-5)

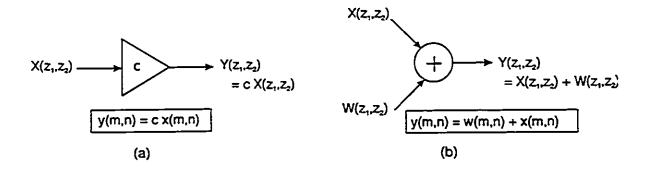

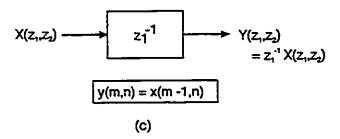

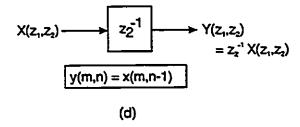

A 2-D filter configuration can be conveniently represented in a block-diagram form, the basic elements of which are the constant multipliers and adders (similar to the 1-D case), and two distinct types of delay elements with transfer functions  $z_1^{-1}$  and  $z_2^{-1}$ , respectively. These are depicted in Figure 1-1. Figure 1-2 illustrates the nature of the 2-D filtering process as governed by equation (1-5) for the case N=M=2. The input mask  $a_{ij}$  is superimposed on the input image and the addition of the product between the mask and the underlying samples gives the 2-D convolution. The output mask  $b_{ij}$  is similar to the input except for the missing element in correspondence to the output sample to be computed.

Figure 1-1

The basic elements for signal processing

- (a) multiplication by a scalar

- (b) addition

- (c) line delay

- (d) sample (pixel) delay

Figure 1-2

Input and output masks for 2nd order filter

#### 1-2.2 DIRECT REALIZATIONS

A direct realization of an IIR filter from the transfer function follows from the algorithm given by Shanks et al. [4]. There it is shown that equation (1-4) can be written as

$$Y(z_1,z_2) = \left[\sum_{i=0}^{M} \sum_{j=0}^{N} a_{ij} z_1^{-i} z_2^{-j}\right] X(z_1,z_2)$$

$$-\left[\sum_{\substack{i=0\\i+j\neq 0}}^{M}\sum_{j=0}^{N}b_{ij}z_{1}^{-i}z_{2}^{-j}\right]Y(z_{1},z_{2})$$

(1-6)

An example of the direct form realization for the 2 x 2 case is shown in Figure 1-3.

Another direct realization is the 2-D Canonic form (Figure 1-4), which was first introduced in the literature by Mitra et al. [5]. An alternate 2-D Canonic form which is referred to here as type II is shown in Figure 1-5. These structures require only two line delays (denoted  $z_1^{-1}$ ) for a 2 x 2 filter.

Figure 1-3

A direct form realization

Figure 1-4  $A \ direct \ form \ 2-D \ Canonic \ realization \ (2 \times 2) \ case \ - \ type \ I$

## 1-2.3 REALIZATION FROM CONTINUED AND PARTIAL FRACTION EXPANSION

In the field of 1-D signal processing, continued fraction and partial fraction expansion realizations are well known. In some instances, it is possible to extend these realizations to the 2-D case, as discussed in [5] and [6,7]. Both of these approaches are limited due to the fact that an arbitrary transfer function of a 2-D recursive filter cannot be realized, but certain restrictions apply. A continued fraction form requires a number of strong relationships to be satisfied among the design coefficients. Also a given continued fraction expansion must be checked for existence [5]. A partial fraction expansion will exist for the case of a denominator separable 2-D digital filter transfer function (of order  $M \times N$ ):

$$H(z_1, z_2) = \frac{Y(z_1, z_2)}{Q_1(z_1)} = \frac{\sum_{i=0}^{M} \sum_{j=0}^{M} a_{ij} z_1^{-i} z_2^{-j}}{\sum_{i=0}^{M} q_{1i} z_1^{-i} \sum_{i=0}^{M} q_{2j} z_2^{-j}}$$

(1-7)

However, in general, 2-D systems have no partial fraction expansion since the fundamental theorem of algebra does not apply as in the 1-D case.

#### 1-2.4 ARCHITECTURES FOR 2-D FILTERING

A number of realization structures appearing in the literature are described as "architectures" because they are optimal in terms of some desired properties such as processing speed, efficiency, and modularity.

### 1-2.4.1 HIGH SPEED DELAYED MULTIPATH 2-D DIGITAL FILTERING

This type of structure is a delayed multipath realization for 2-D recursive (and non-recursive) filters due to Kwan and Hirano [8]. This work overcomes the disadvantages of those techniques which involve the application of the decomposition theorems to the 2-D transfer function as in [9], and those using LU triangular decomposition of the matrix coefficients of the 2-D polynomials of the transfer function [10].

In the implementation of these structures (given in [8]) so-called N1-path structures are used to implement the sub-blocks. The multiplex switching which is used in the implementation of the sub-blocks is not strictly necessary and unnecessarily complicates the discussion. Thus we will continue to view realizations only in terms of the fundamental blocks as given in Section 1-2.1, i.e. adders, multipliers, and delays. The method can be used to implement FIR or IIR 2-D filters, so we can discuss the implementation of IIR filters with the FIR being a specific case in which the denominator of the transfer function is equal to one (no poles).

Consider again the transfer function of a 2-D IIR digital filter (equation (1-4). In general, it can be decomposed in terms of sub-blocks  $A_{ij}$ ,  $B_{ij}$  as follows:

$$H(z_1, z_2) = \frac{\sum_{j=0}^{N_2-1} z_2^{-jL_2} \sum_{i=0}^{N_1-1} z_1^{-i} A_{ij}(z_1^{-N_1}, z_2^{-1})}{1 + \sum_{j=0}^{\overline{N_2}-1} z_2^{-j\overline{L_2}} \sum_{i=0}^{\overline{N_1}-1} z_1^{-i} B_{ij}(z_1^{-\overline{N_1}}, z_2^{-1})}$$

(1-8)

where

$$A_{ij}(z_{1}^{-N_{1}}, z_{2}^{-1}) = \sum_{k=0}^{L_{1}-1} \sum_{l=0}^{L_{1}-1} a(kN_{1} + i, l + jL_{2})z_{1}^{-kN_{1}}z_{2}^{-l}$$

$$B_{ij}(z_{1}^{-N_{1}}, z_{2}^{-1}) = \sum_{k=0}^{L_{1}-1} \sum_{l=0}^{L_{1}-1} b(k\overline{N_{1}} + i, l + j\overline{L_{2}})z_{1}^{-k\overline{N_{1}}}z_{2}^{-l}$$

$$M_{i} + 1 = N_{i} \times L_{i} \text{ for } i = 1, 2$$

$$\overline{M_{i}} + 1 = \overline{N_{i}} \times \overline{L_{i}} \text{ for } i = 1, 2$$

$$1 \leq N_{2} \leq M_{2} + 1$$

$$1 \leq \overline{N_{2}} \leq \overline{M_{2}} + 1$$

$$1 < N_{1}; 1 < L$$

$$1 < \overline{N_{1}}; 1 < \overline{L_{1}}$$

$$1 < \overline{N_{1}}; 1 < \overline{L_{1}}$$

Let us develop the realization of a 5 x 5 FIR filter by this method (as an example).

If we choose  $N_2=3$ ,  $N_1=2$ ,  $L_2=2$ ,  $L_1=3$ , then (1-8) (with denominator = 1) becomes

$$H(z_{1}, z_{2}) = \sum_{j=0}^{2} z_{2}^{-2j} \sum_{i=0}^{1} z_{1}^{-i} A_{ij}(z_{1}^{-2}, z_{2}^{-1})$$

$$= \left[ A_{00}(z_{1}^{-2}, z_{2}^{-1}) + A_{10}(z_{1}^{-2}, z_{2}^{-1}) \right] + z_{2}^{-2} \left[ A_{01}(z_{1}^{-2}, z_{2}^{-1}) + A_{11}(z_{1}^{-2}, z_{2}^{-1}) \right]$$

$$+ z_{2}^{-4} \left[ A_{02}(z_{1}^{-2}, z_{2}^{-1}) + A_{12}(z_{1}^{-2}, z_{2}^{-1}) \right]$$

$$(1-10)$$

where each sub-block  $A_{ij}$  is given by

$$A_{ij} = \sum_{k=0}^{2} \sum_{l=0}^{1} a(2k+i, l+2j) z_{1}^{-2k} z_{2}^{-l}$$

$$= \sum_{k=0}^{2} z_{1}^{-2k} \sum_{l=0}^{1} a(2k+i, l+2j) z_{2}^{-l}$$

(1-11)

for example,

$$A_{02} = (a_{04} + a_{05}z_2^{-1}) + z_2^{-2}(a_{24} + a_{25}z_2^{-1}) + z_2^{-4}(a_{44} + a_{45}z_2^{-1})$$

(1-12)

The block diagram realization of (1-10) is shown in Figure 1-6, while the realization of the general sub-block  $A_{ij}(z_1^{-2}, z_2^{-1})$  is shown in Figure 1-7.

Figure 1-6

Realization of 5 x 5 FIR filter example — High Speed Delayed Multipath 2-D

#### 1-2.4.2 2-D SYSTOLIC REALIZATIONS

Due to the recent advances in VLSI technology, it has become highly desirable to develop digital filter realizations in such a way that the repetitive use of common structures (i.e. modules) is maximized and the number of "random" connections is minimized in order to reduce the design effort and create producible integrated circuits. Systolic structures also have a speed advantage over other known forms of realization, due to the high degree of parallelism.

Kung [11] has given the following definition of a systolic system: " A systolic system is a network of processors that rhythmically compute and pass data through the system." Systolic arrays may be thought of as networks of (ideally) locally interconnected processing elements (PE's) in which each PE regularly "pumps" data in and out, each time performing some short computation involving the data input to the PE and local variables associated with storage within the PE, in order that a regular flow of data is kept up in the network." In general, systolic array processing, has applications to many computationally intensive problems. The wide range of applications includes not only signal and image processing, and matrix arithmetic, which involve numeric computations, but even includes symbolic tasks such as searching and sorting, graph theoretical algorithms, and relational database processing.

As an introduction to the method of systolic array computation, let us consider a simple example: Suppose we are given the following polynomial

$$P(x) = C_m x^m + C_{m-1} x^{m-1} + \dots + C_0$$

(1-13)

which is to be evaluated at points  $x_i$ , in the interval [1,n]. Using Horner's rule, the formula for P(x) becomes

$$P(x) = (\cdots((C_m x + C_{m-1})x + \cdots + C_1)x + C_0$$

(1-14)

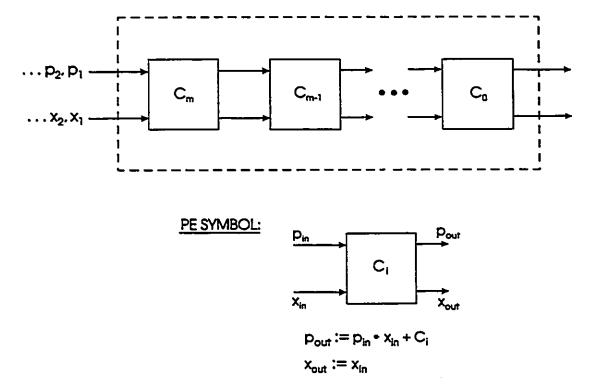

A possible systolic implementation is shown in Figure 1-8. The coefficients are stored in individual "cells" or processing elements (PE's). (We can think of the coefficients as the *local variables* of the computation.) The  $x_i$  (inputs) and  $p_i$  (partial results) data "flow" through the PE's. On every clock cycle, each PE receives as inputs  $x_i$  and  $p_{in}$ , multiplies them and adds its internal coefficient  $C_i$ , producing an output  $p_{out}$ , while passing through  $x_i$  unchanged. Each result  $P(x_i)$  appears at the output (the rightmost PE's) m clock cycles after  $x_i$  is input at the leftmost PE.

Figure 1-8

Systolic implementation of polynomial evaluation

We see from this example, that a systolic array processor, unlike a von Neumann type machine, does not require a data item to be retrieved from a central memory store every time it is used. Thus a systolic array processor is said to have *low external memory bandwidth*.

Systolic processing offers many additional advantages. The modularity of the design, involving only a few simple PE types, used repetitively, as well as the local pattern of interconnection between PE's, simplifies circuit layout, and is cost-effective. The low fanout in a systolic array allows the output of signal line drivers to be independent of the number of cells in the array. Moreover, systolic architectures can be readily scaled up to handle larger problems, a property of considerable importance in the case of implementing filters of arbitrary order.

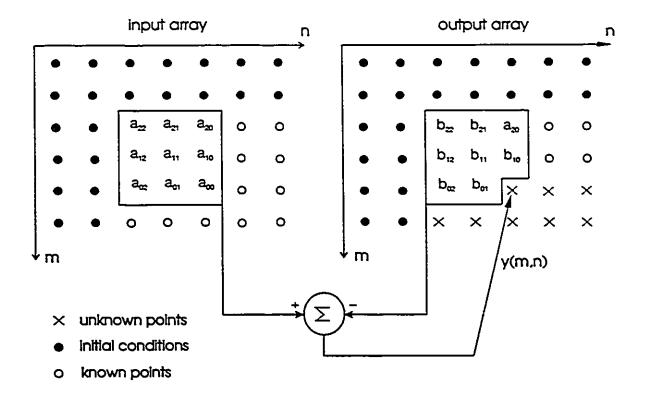

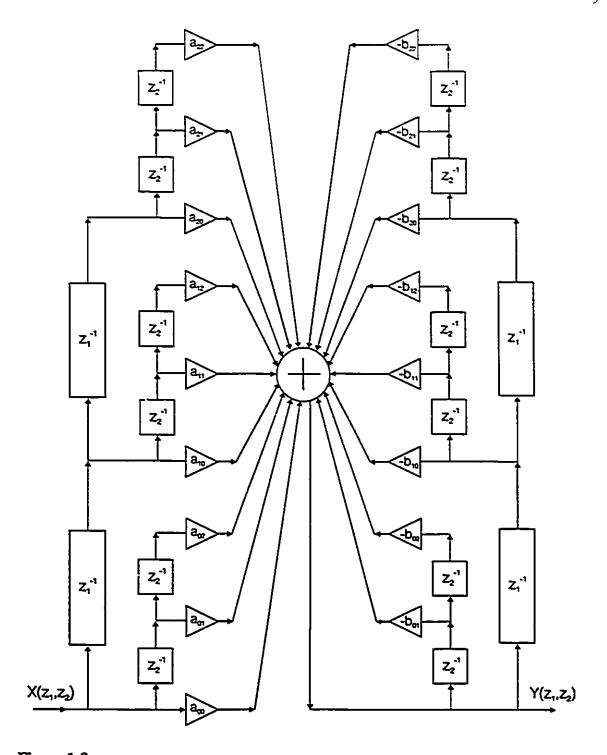

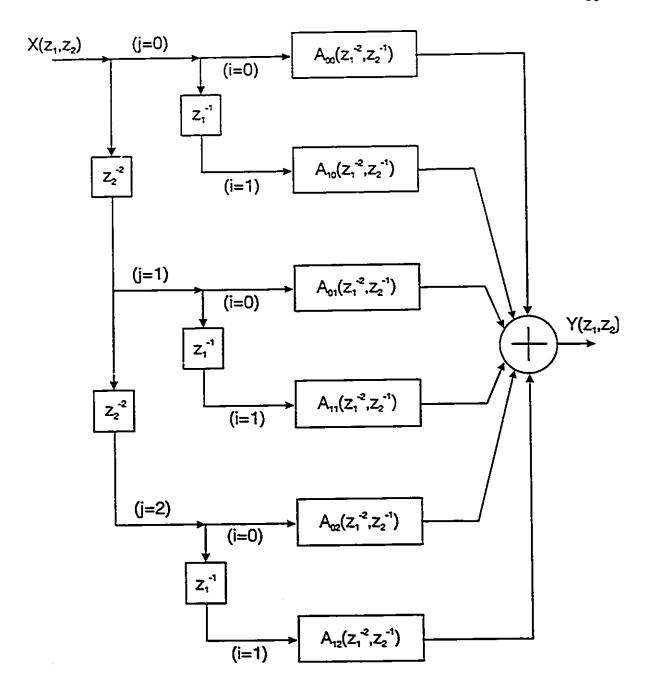

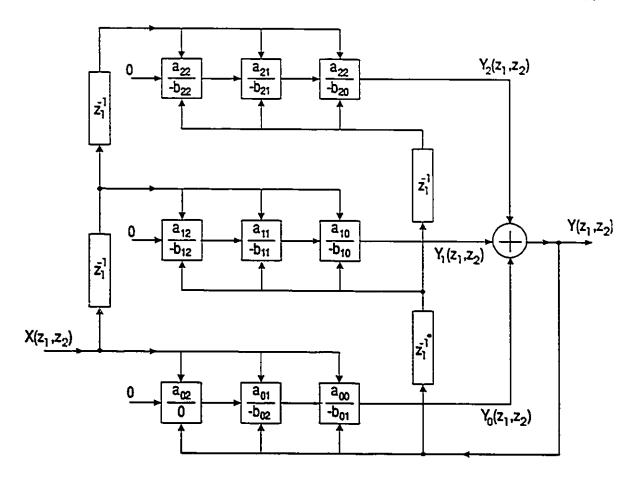

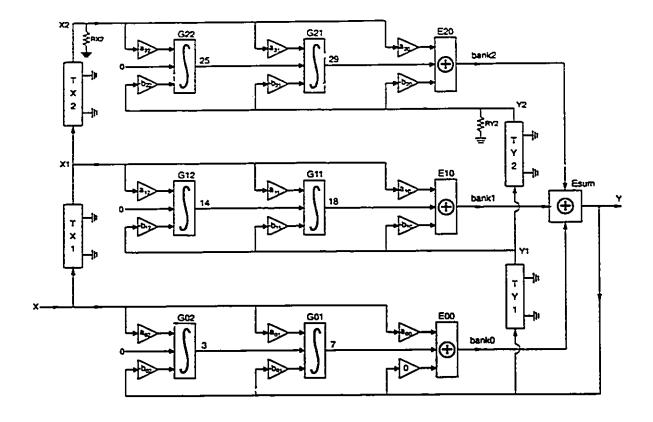

A representative example of a systolic architecture that can implement either IIR or FIR filters and which makes use of a feature known as "broadcasting" i.e. data is distributed to several PE's in parallel via a single take-off point, is the one developed by Sid-Ahmed in [12, 13]. The Sid-Ahmed structure, which can be realized directly in terms of the transfer function coefficients, is shown in Figure 1-9. A detailed derivation of this structure is given in Chapter 2. Note that in this figure one of the line delays is denoted by  $z_1^{-1*}$  (with an asterisk), due to the fact that the line delay period is shortened by one sample time. This is sometimes alternatively denoted  $z_1^{-1} z_2$ .

Figure 1-9

2-D systolic architecture (Sid-Ahmed [12])

Other systolic architectures for 2-D filtering are described in the literature. In [14] two other architectures are presented, which are both based on the same type of PE as [12]. These are shown in Figure 1-10. In general, systolic architectures will differ in:

- 1) Number of adders and multipliers needed

- 2) Critical path length

- 3) Number of storage elements,  $z_1^{-1}$  (line delay),  $z_2^{-1}$  (sample delay)

- 4) Speed-up factor (SUF)

and

5) latency.

For real-time image processing it is highly desirable for a 2-D filter architecture to have a short critical path length. The critical path is the longest delay-free arithmetic path, i.e. the signal path with the longest arithmetic operation time, leading from the output of any delay element or the system input to the input of any delay element or the system output. A short critical path length allows a systolic filter to operate at a high clock rate, and thus a high real-time throughput rate. In general, the minimum achievable path length for a 2-D filter is 1-multiply and 1-add time (1m-1a). Assuming two-input additions, the critical path length of the architectures shown in Figure 1-10 is  $T_m + 2T_a$ , (where  $T_m$ ,  $T_a$  are multiplication and addition times respectively) and is

for the architecture in Figure 1-9. The situation improves in the case of analog component realization of the latter architecture, in which multi-input additions can be done.

Figure 1-10

2-D systolic architectures given in [14]

The SUF is a measure used to compare the speed efficiencies of systolic arrays. It is defined [15] as

$$SUF = \frac{Processing Time in a PE}{Processing Time in the Array Processor}$$

(1-16)

For the purposes of comparison it is usually assumed that all adders are two operand adders.

Using this assumption we would find that the structures in Figure 1-10 both have SUF=1.0, while that of Figure 1-9 has an SUF given by

$$SUF = \frac{T_m + T_\sigma}{\max\{(T_m + T_\sigma), T_\sigma[\log_2(N+1)]\}}$$

(1-17)

This penalty in SUF, incurred by the latter, can be avoided in the case of analog component realization utilizing multi-input adders, as will be seen in Chapter 2.

Latency is defined as the time interval separating the appearance of an input sample on the input port from the appearance of the corresponding output sample at the output port. The architectures shown in Figures 1-9 and 1-10 all have a latency of one sample period.

# REALIZATION OF 2-D IIR FILTERS USING SAMPLE-AND-HOLD TECHNIQUES

#### 2-1 INTRODUCTION

In this chapter we introduce systolic realization of 2-D systolic filters for real time applications. The structures which we will consider can implement either IIR or FIR filters.

Since the FIR realizations follow directly as special cases of the IIR realizations we consider only the latter. The structures presented here make use of a feature known as "broadcasting" i.e. data is distributed to several PE's in parallel via a single take-off point. These structures also can be realized directly in terms of the transfer function coefficients as opposed to the local state space approach [16]. The hardware development and SPICE simulation of structures based on the semi-systolic architecture proposed by Sid-Ahmed [13] are presented.

This development culminates in the production of a hardware prototype that has been applied to the real time filtering of video rate broadcast images in a representative application, namely that of the non-linear homomorphic filtering approach of Oppenheim et al. [18].

In addition to hardware development and prototyping, a new approach to SPICE simulation of discrete time filtering based on functional block simulation [19] is introduced.

This approach exploits the modularity of systolic structures to reduce the complexity of the simulation process. Hence a direct simulation with actual 2-D data input can readily be done in

the time domain, eliminating the need to introduce z-domain equivalent circuits as has been done for 1-D filter simulation in [20].

In general, a 2-D recursive digital filter transfer function of order M x N is given by

$$H(z_1, z_2) = \frac{Y(z_1, z_2)}{X(z_1, z_2)} = \frac{\sum_{i=0}^{M} \sum_{j=0}^{N} a_{ij} z_1^{-i} z_2^{-j}}{\sum_{i=0}^{M} \sum_{j=0}^{N} b_{ij} z_1^{-i} z_2^{-j}}$$

$$1 + \sum_{i=0}^{M} \sum_{j=0}^{N} b_{ij} z_1^{-i} z_2^{-j}$$

$$i + j \neq 0$$

(2-1)

where  $\{a_{ij}\}$  and  $\{b_{ij}\}$  are filter coefficients obtained from a design procedure that determines the coefficients according to some given criteria to approximate the desired frequency response of  $H(z_1,z_2)$  (i.e. high-pass, low-pass, etc.).

Corresponding to equation (2-1) in the time domain is the so called recursive equation which relates the output sample of the filter y(m,n) to the input sample x(m,n) occurring at the same point in time.

$$y(m,n) = \sum_{i=0}^{M} \sum_{j=0}^{N} a_{ij} x(m-i,n-j) - \sum_{i=0}^{M} \sum_{j=0}^{N} b_{ij} y(m-i,n-j)$$

$$(2-2)$$

Here we have made the assumption of a causal system so that the output signal y(m,n) is written as a function of only the present and past values of the input and output signals x(m,n), y(m,n) respectively. We can write equation (2-2) in the z-domain as

$$Y(z_1, z_2) = \sum_{i=0}^{M} \sum_{j=0}^{N} \alpha_{ij} X(z_1, z_2) z_1^{-i} z_2^{-j} - \sum_{i=0}^{M} \sum_{j=0}^{N} b_{ij} Y(z_1, z_2) z_1^{-i} z_2^{-j}$$

$$i+j\neq 0$$

(2-3)

Multiplying both sides of this equation by  $z_2^{-1}$  (thus introducing one pixel of latency in the output) and rearranging yields

$$z_2^{-1}Y(z_1, z_2) = \sum_{i=0}^{M} z_2^{-1}Y_i(z_1, z_2)$$

(2-4)

where

$$z_{2}^{-1}Y_{0}(z_{1}, z_{2}) = z_{2}^{-1}\{[a_{00}X(z_{1}, z_{2}) + z_{2}^{-1}([a_{01}X(z_{1}, z_{2}) - b_{01}Y(z_{1}, z_{2})] + z_{2}^{-1}([a_{02}X(z_{1}, z_{2}) - b_{02}Y(z_{1}, z_{2})] + z_{2}^{-1}(\cdots + z_{2}^{-1}([a_{0j}X(z_{1}, z_{2}) - b_{0j}Y(z_{1}, z_{2})] + z_{2}^{-1}(\cdots + z_{2}^{-1}([a_{0N}X(z_{1}, z_{2}) - b_{0N}Y(z_{1}, z_{2})] \cdots)\}$$

$$(2-5)$$

and

$$z_{2}^{-1}Y_{i}(z_{1},z_{2}) = z_{2}^{-1} \{ [a_{i0}X(z_{1},z_{2})z_{1}^{-i} - b_{i0}Y(z_{1},z_{2})z_{1}^{-i}]$$

$$+z_{2}^{-1}([a_{i1}X(z_{1},z_{2})z_{1}^{-i} - b_{i1}Y(z_{1},z_{2})z_{1}^{-i}]$$

$$+z_{2}^{-1}([a_{i2}X(z_{1},z_{2})z_{1}^{-i} - b_{i2}Y(z_{1},z_{2})z_{1}^{-i}]$$

$$+z_{2}^{-1}(\cdots$$

$$+z_{2}^{-1}([a_{ij}X(z_{1},z_{2})z_{1}^{-i} - b_{ij}Y(z_{1},z_{2})z_{1}^{-i}]$$

$$+z_{2}^{-1}(\cdots$$

$$+z_{2}^{-1}([a_{iN}X(z_{1},z_{2})z_{1}^{-i} - b_{iN}Y(z_{1},z_{2})z_{1}^{-i}]\cdots) \}$$

$$(2-6)$$

for  $i=1, \ldots, M$

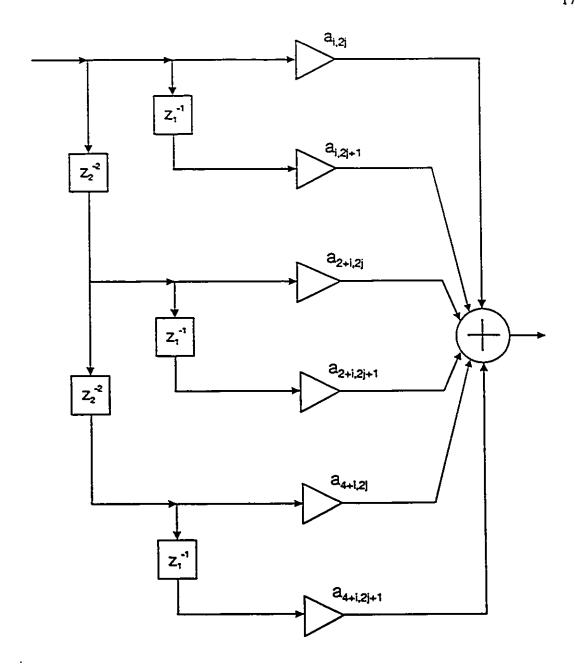

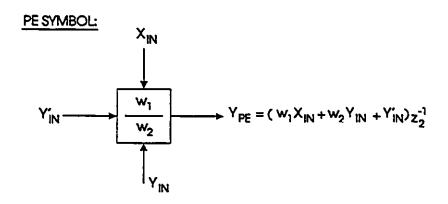

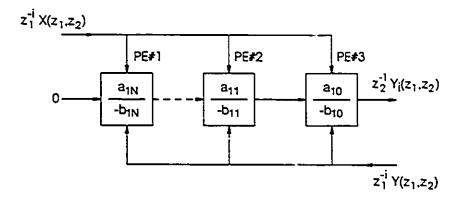

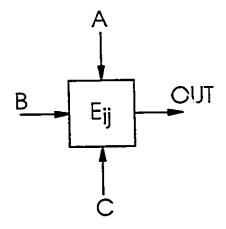

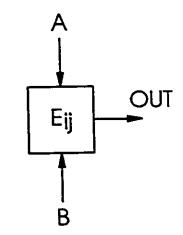

The realization of the partial result  $z_2^{-1}Y_1(z_1,z_2)$  based on equation (2-6) is shown in Figure 2-1. Shown below in this figure is the general block diagram symbol for a processing element (PE).

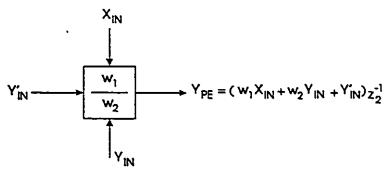

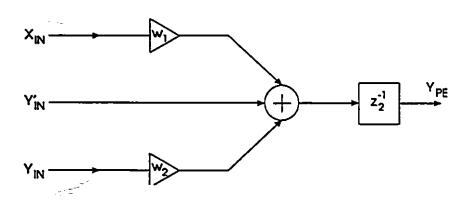

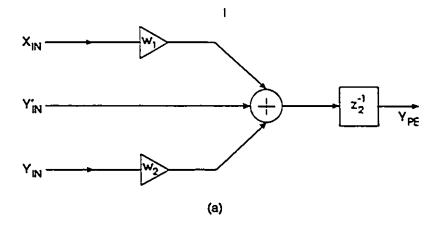

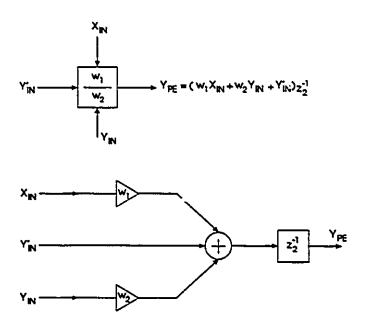

Figure 2-2 shows each PE consisting of two coefficient multipliers, an adder, and a pixel delay, connected as shown. Note that  $w_1$  and  $w_2$  correspond to some specific filter design coefficients in the set  $\{\{a_u\}, \{b_u\}\}$  that are required in a particular PE.

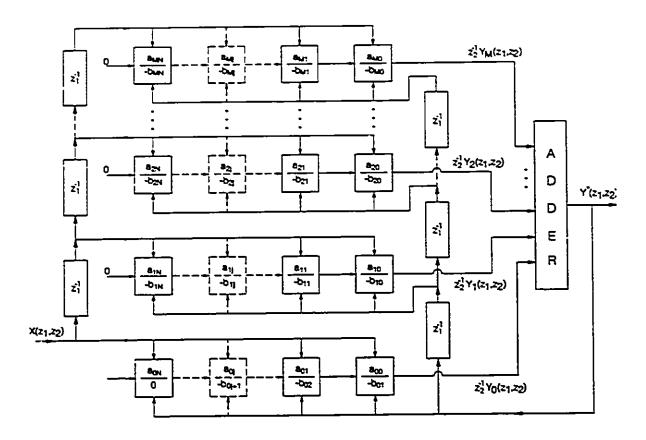

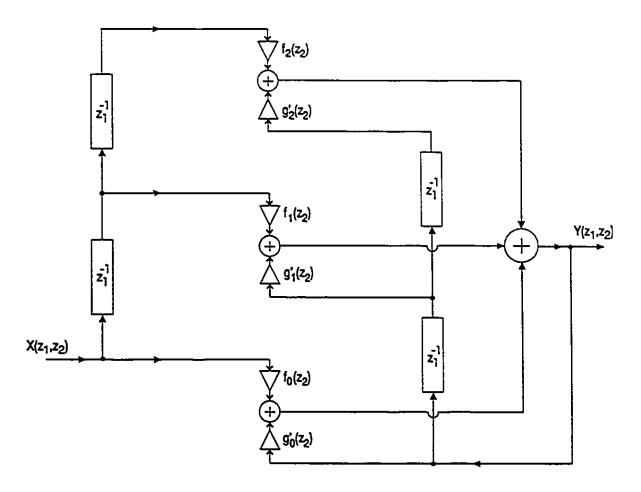

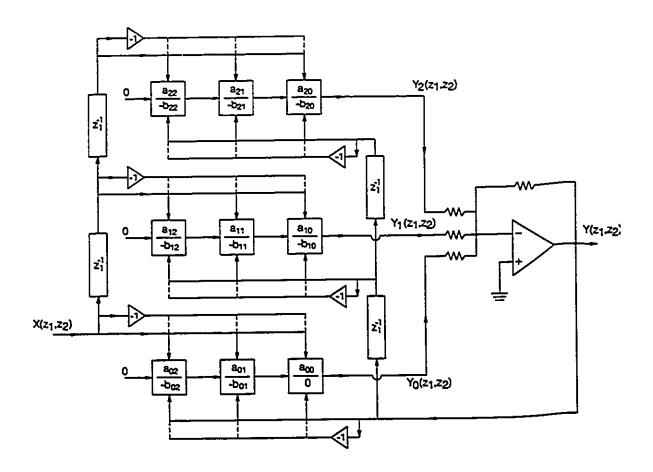

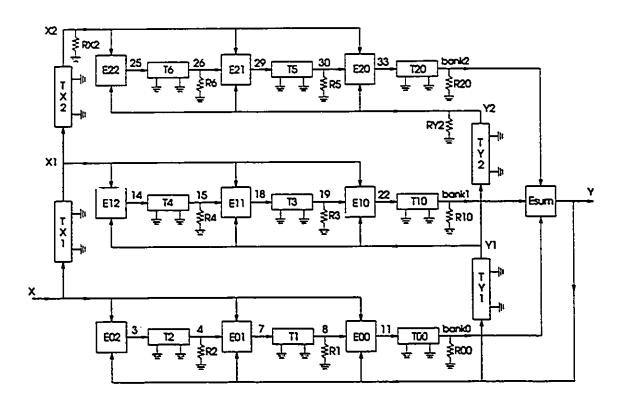

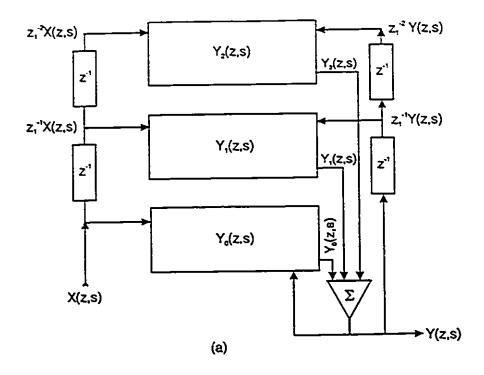

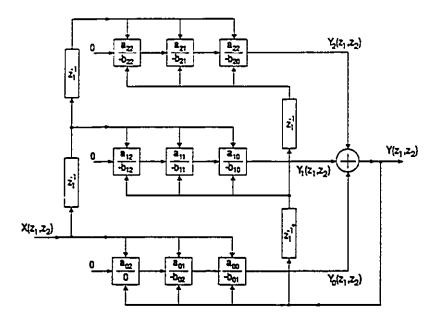

The overall 2-D semi-systolic filter structure of order  $M \times N$  based on equations (2-4), (2-5), and (2-6) is realized as shown in Figure 2-3.

\_

In Figure 2-3, the output signal of the structure  $Y(z_1,z_2)$  has been denoted with an asterisk because the output signal is produced with one data sample (or pixel time) of latency and is actually  $z_2^{-1}Y(z_1,z_2)$  which corresponds to y(m,n-1) in the time domain rather than y(m,n). To remove the effects of this latency on the feedback, the first line delay in the feedback path must, in practice, be shortened by one pixel (sample) time and is thus denoted  $z_1^{-1}$ . Also, because a latent (by one pixel time) signal is fed back, to the lowermost bank of PE's, the "b" coefficients occur there in the order 0,  $-b_{02}$ ,  $-b_{01}$ , from left to right. In this figure,  $z_1^{-1}$  is used to represent a row delay, which in the case of a raster scanned image is a delay of one line scanning period (63.5 $\mu$ s in the NTSC television standard).

=

Figure 2-1

Partial realization of  $z_2^{-1}Y(z_1,z_2)$

Figure 2-2

Processing element (PE)

Figure 2-3 Realization of  $M \times N$  IIR semi-systolic filter

= 100

We can alternatively derive the 2-D semi-systolic structure of Figure 2-3, without using Horner's rule, by employing a modified version of the method proposed in [21].

Consider again the transfer function as a 2-D linear, causal shift-invariant recursive discrete-time filter (equation 2-1) for the case M=N=2. We can rewrite this as follows:

$$H(z_1, z_2) = \frac{Y(z_1, z_2)}{X(z_1, z_2)} = \frac{\sum_{i=0}^{2} f_i(z_2) z_1^{-i}}{\sum_{i=0}^{2} g_i(z_2) z_1^{-i}}$$

(2-7)

where

$$f_i(z_2) = \sum_{j=0}^{2} a_{ij} z_2^{-j}$$

(2-8)

and

$$g_i(z_2) = \sum_{j=0}^2 b_{ij} z_2^{-j}$$

We can now think of the 2-D transfer function as being a 1-D transfer function in which the coefficients  $f_i(z_2)$ ,  $g_i(z_2)$  are not constant but instead functions of  $z_2$ . Without loss of generality, we can assume that  $b_{00}=1$ , (as we have been doing so far). Accordingly, let

$$g'_{i}(z_{2}) = \sum_{j=0}^{2} b_{ij} z_{2}^{-j}$$

for  $i = 1, 2$

and

$$g_0'(z_2) = \sum_{i=1}^2 b_{0i} z_2^{-i}$$

(2-9)

in equation (2-7) above so that

$$H(z_1, z_2) = \frac{Y(z_1, z_2)}{X(z_1, z_2)} = \frac{\sum_{i=0}^{2} f_i(z_2) z_1^{-i}}{1 + \sum_{i=0}^{2} g_i'(z_2) z_1^{-i}}$$

(2-10)

Thus we obtain the 2-D difference equation

$$Y(z_1, z_2) = \sum_{i=0}^{2} f_i(z_2) z_1^{-i} X(z_1, z_2) - \sum_{i=0}^{2} g_i'(z_2) z_1^{-i} Y(z_1, z_2)$$

(2-11)

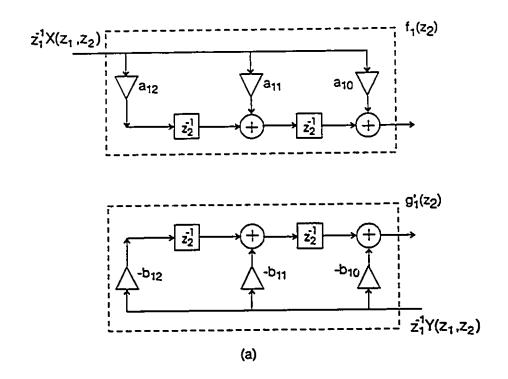

A 1-D realization based on equation (2-11) above is shown in Figure 2-4. In order to obtain a 2-D realization it remains to develop realizations of the "coefficient" functions,  $f_i$ ,  $g'_i$ . This has been done for  $f_1$  and  $g_1'$  in Figure 2-5(a). The other  $f_i$ 's and  $g_i$ 's are similarly realized. Note that the realizations of  $f_1$  ( $z_2$ ) and  $g_1'$ ( $z_2$ ) can be combined into one block, by means of block diagram transformations, as shown in Figure 2-5(b). A grouping of elements to be regarded as a PE is indicated by the dashed line in this figure.

As it now stands, the realization of Figure 2-6 to be presented in Section 2-2.1, has been derived. An extra delay block may be added to the last adder of Figure 2-5(b), to obtain full modularity so that all PE's are identical, resulting in the structure of Figure 2-3, for the 2 x 2 case. However, as before, this results in a latency of one pixel delay in the output and necessitates a rearrangement of the  $b_{0j}$  coefficients in the lowermost bank of PE's...

Figure 2-4

A 1-D realization

Figure 2-5

"Coefficient" function realizations

- (a) Realizations of  $f_1(z_2)$  and  $g_1'(z_2)$ (b) Realizations of (a) combined

## 2-2 DETAILS OF HARDWARE DESIGN WITH APPLICATION TO HOMOMORPHIC FILTERING

#### 2-2.1 2-D SEMI-SYSTOLIC FILTER

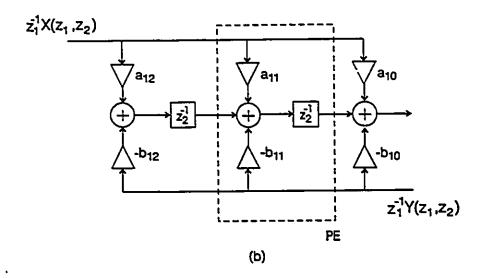

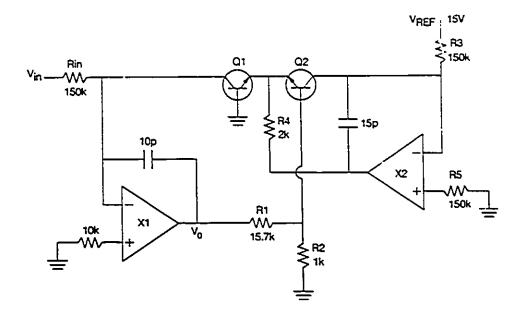

The realization as described in [13] requires line delays of differing lengths. For practical implementation using standard commercially available components, the structure described in Figure 2-3 was modified to use two types of PE instead of only one type throughout and the resulting revised structure is shown in Figure 2-6 (2 x 2 case). Type I PE's are used everywhere except at the end of each bank of PE's, where a type II PE is used instead. Both PE types are shown in Figure 2-7. Note that the type II PE is a modified version of the type I PE in which the pixel delay element denoted  $z_2^{-1}$  is excluded. Having two types of PE in the structure allows the use of standard length line delays. Since the end of stage PE's do not contain storage elements, the latency of one pixel time in processing is removed, so that the feedback connections to the lowermost bank of PE's (i.e. the bank whose PE's contain the local variables  $b_{01}$ ,  $b_{02}$ ) are different.

Another change which was made for greater ease of construction with off-the-shelf components is the introduction of dual broadcast data lines, allowing either non-inverted or inverted data to be sent to each PE. (Note that in the literature on systolic structures, lines through which PE's receive the same data in parallel are called broadcast lines).

Given the high degree of modularity in systolic structures, a practical hardware realization of the structure will result if hardware is designed for the PE's and line delays (and adder for partial results).

Figure 2-6

$2 \times 2$  semi-systolic filter structure for prototype

Figure 2-7

The two types of PE for use in practical hardware prototype.

- (a) Type I PE

- (b) Type II PE

### 2-2.2 DESIGN OF 1H DELAY LINE

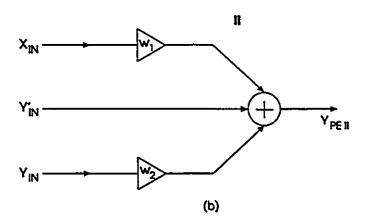

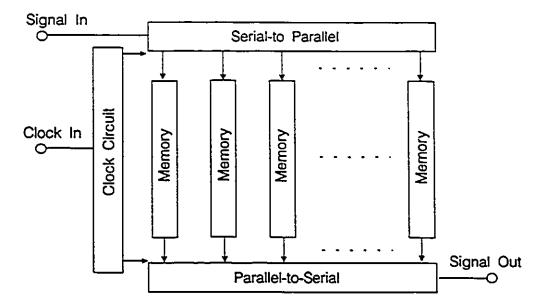

As is seen in Figure 2-6, a 2 x 2 IIR filter structure requires four line delay elements, which are denoted  $z_i^{-1}$  in the z-domain. When processing a raster scanned signal, these line delays correspond to one horizontal line scanning period (1H) which is 63.5 $\mu$ s in the NTSC system. A 1H delay was designed using an electronic charge-coupled device (CCD) type analog shift register as shown in the block diagram of Figure 2-8. The device used was the Fairchild-Weston CCD321, which is intended specifically for NTSC applications [22]. The CCD device has an insertion loss of 0 dB compared to >>6 dB for glass block devices. Glass block devices have the disadvantage of requiring the modulation of a carrier due to bandwidth limitations. The delay time of analog signals through the CCD is precisely controlled by clock signals, which are two-phase symmetrical square wave signals derived from a crystal oscillator signal by means of clock driver circuits.

The type of clock driver circuits used will be a function of the type of CCD chosen and are typically based on TTL or CMOS family integrated circuit devices. For the Fairchild-Weston CCD321, which has a charge injection port at its input and a sample-and-hold circuit in its output amplifier section, the two-phase system of clocks is applied to the device to effect charge injection at the input as well as interstage charge transport and clocking of the internal sample-and-hold circuit.

A sample-and-hold device in the output stage of a CCD offers the advantage of reducing clock frequency feedthrough components in the output signal. Any of these undesirable frequency components that remain in the output may be further suppressed by a 5 MHz low-pass filter circuit.

Figure 2-8

Block diagram of CCD type 1H line delay

Figure 2-9

Block Diagram of CCD321 IC

(continued next page)

|                                     | PIN NAMES                                |

|-------------------------------------|------------------------------------------|

| ф <sub>ід</sub> , ф <sub>ів</sub>   | Analog Shift Register Transport Clocks   |

| $\phi_{\text{SA}},\phi_{\text{SB}}$ | Input Sampling Clocks                    |

| $\phi_{ra}, \phi_{rb}$              | Output Sample and Hold Clocks            |

| $V_2$                               | Analog Shift Register DC transport Phase |

| $V_{1A}, V_{1B}$                    | Analog Inputs                            |

| $V_{RA}, V_{RB}$                    | Analog Reference Inputs                  |

| VOAN VOB                            | Analog Outputs                           |

| V <sub>DD</sub>                     | Output Drain                             |

| V <sub>GG</sub>                     | Signal Ground                            |

| V <sub>ss</sub>                     | Substrate Ground                         |

Figure 2-9 (continued)

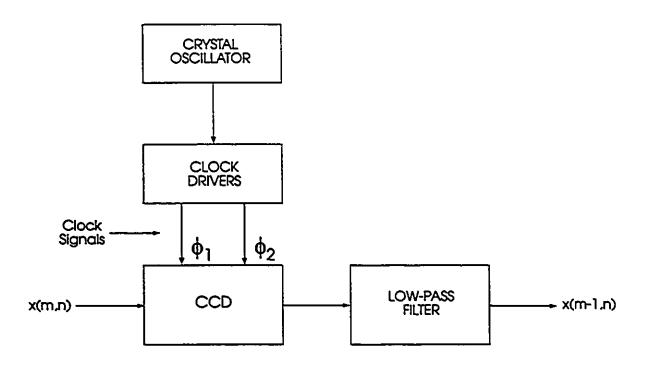

#### 2-2.2.1 THE CCD IC

The block diagram of the CCD 321 IC is shown in Figure 2-9. (A legend of pin names is also given.) It contains two identical 455 bit analog shift registers A and B. (In the literature it is conventional to refer to each register stage as a "bit" whether the samples are analog or digital.) Each of the shift registers A (or B respectively) has a charge injection port and an output amplifier.

#### i) Charge Injection Port

A charge packet, linearly dependent on the voltage at the input  $V_I$ , with respect to the reference voltage  $V_R$  is injected into the analog shift register. Charge packet injection occurs with each activation of the sampling clock  $\phi_{SA}$ .

#### ii) 455 Bit Analog Shift Register

Charge packets arriving at the injection port are transported successively from one bit to the next. A shift occurs for each cycle of the transport clock  $\phi_1$ . Note that channels A and B have independent transport clocks  $\phi_{1A}$  and  $\phi_{1B}$ . For a given clock frequency f, a charge packet arriving at the injection port will reach the output amplifier after a delay time T, where T = 455/f.

#### iii) Output Amplifier

Each output amplifier consists of three source follower stages with constant current source bias. A sample and hold transistor is located between the second and third stage of the amplifier. The sample and hold transistor is clocked by  $\phi_R$  to obtain a continuous output

waveform  $V_{OA}$  which is a delayed version of the input waveform (insertion loss is 0 dB).  $V_{OB}$  will contain sampling clock feedthrough that can be removed by low-pass filtering.

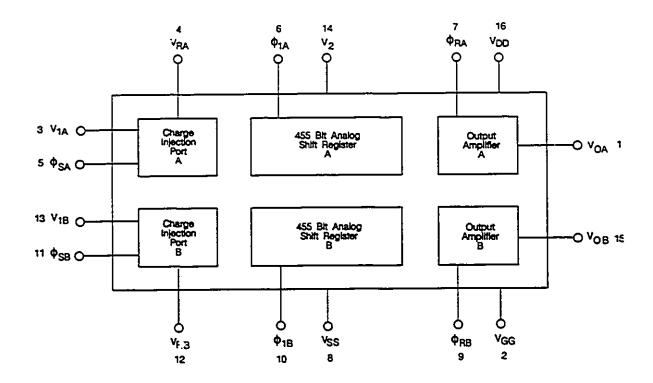

#### 2-2.2.2 MULTIPLEXED VS. SERIAL MODE OPERATION

To provide a 1H delay with 910 sample resolution, the two 455 bit shift registers can be cascaded with each register operated at the same clock frequency f. In this case

$$T = 1H \text{ period} = 63.5 \mu s = 910 / f.$$

Thus serial mode requires a 14.31818 MHz clock.

Alternatively a 910 sample resolution 1H delay can be obtained by multiplexed mode operation. Two 455 bit shift registers are connected in parallel. Alternate samples of the common input are carried by registers A and B, and combined at the output. Multiplex mode requires a clock frequency

$$f = 455 / 63.5 \mu s = 7.159 \text{ MHz}$$

but has an effective sampling rate of 14.31818 MHz.

Since each clock input is a 30pF load, the performance of the clock driver circuits is less critical for multiplex mode. Also layout and shielding requirements to contain the high frequency harmonic radiation caused by clock driver switching are eased. In the present design multiplex mode was used.

#### 2-2.2.3 CLOCK DRIVER CIRCUIT

The clock driver circuitry of Figure 2-10 was designed to provide the waveforms needed for multiplexed mode operation, given in the timing diagram of Figure 2-11. The clock drivers

provide two-phase symmetrical waveforms to the CCDs at an amplitude of 15Vpk at 7.159Mhz. (Note that  $\Phi_{SA}$  and  $\Phi_{SB}$  are drawn with less than 50% duty cycle in Figure 2-11, however a 50% duty cycle will suffice.) The crystal oscillator produces a square wave at TTL levels, which is buffered and then divided by two at the D flip-flop where the Q and  $\overline{Q}$  outputs provide antiphase signals. Each of these signals is in turn converted to a 15Vpk level by 7406 type open collector inverters with 470  $\Omega$ , 1/4W pull-up resistors. Rise and fall times are in the order of 10ns. If rise and fall times are made too fast, negative transients below ground may cause charge injection from the substrate to the shift registers. This injection can be eliminated with a negative bias on  $V_{SS}$  (-2.0 to -5.0V) with respect to signal ground,  $V_{GG}$ .

Figure 2-10

Clock driver circuit for multiplex CCD

Figure 2-11

Timing diagram for the CCD IC in the multiplexed mode

#### 2-2.2.4 INPUT COUPLING CIRCUIT AND BIASING

As indicated in Figure 2-12, inputs to the CCD are attenuated to a level of 400 - 500 mVpk and AC coupled. (Inputs must be less than 1V pk-pk for distortionless operation.)

The DC bias level at an input is established by a resistive divider (approx. 1.5 VDC). The reference voltage inputs  $V_{RA}$  and  $V_{RB}$  are set to DC levels by the same type of resistive divider (approx. 4.5 VDC).

Since signal charge injection is proportional to the difference between  $V_1$  and  $V_R$ , adjustment of either  $V_1$  or  $V_R$  is necessary to assure proper operation.

#### 2-2.2.5 OUTPUT COUPLING CIRCUIT

This circuit recombines the multiplexed outputs into one signal. Outputs  $V_{OA}$  and  $V_{OB}$  are AC coupled to the summing node of a summing amplifier (Figure 2-13). The amplifier shown is a high speed operational amplifier (LM318). A variable amount of gain is provided by adjusting  $R_f$ . This compensates for the attenuation introduced by the input coupling circuit.  $R_2$  and  $R_1$  must be as closely matched as possible so that equal gain is given to each CCD output.

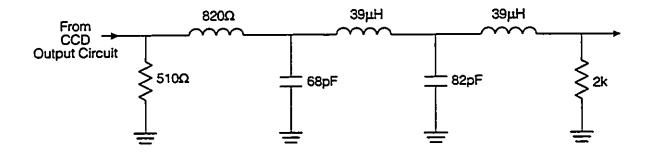

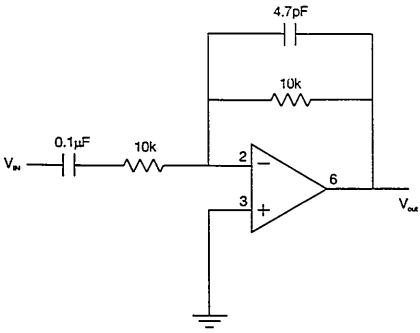

## 2-2.2.6 LOW PASS FILTER

An optional low pass filter with a zero in its frequency response at 14.3 MHz may be used to remove any clock signal component remaining in the summed output. The -2 IB point of this filter is chosen to be somewhat above the highest video frequency to ensure that its presence causes no amplitude or phase changes within the video bandwidth. An example of

such a filter designed with discrete components is shown in Figure 2-14. The 39µH inductors can be obtained in packages comparable in size to a 1/4 W carbon composition resistor. (LC filters are commonly used in video circuitry and are practical because of the small size of the inductors required at video frequencies.) In the case in which sampled data signals are being processed the optional LC filter is not required in the CCD circuitry and low pass filtering may be done exclusively at the filter output.

Figure 2-12

Input Coupling Circuit for Multiplex CCD

Figure 2-13

Output Coupling Circuit for Multiplexed CCD

Figure 2-14

Low Pass Filter - Removes CCD clock feedthrough

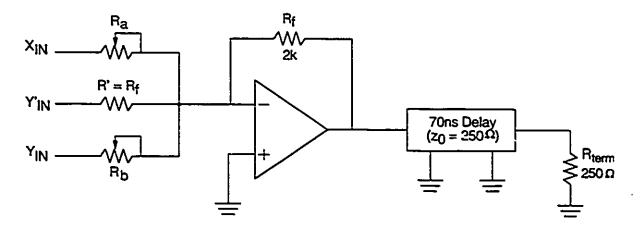

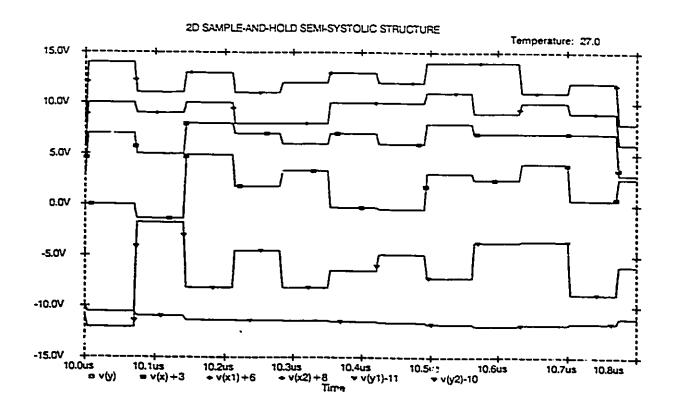

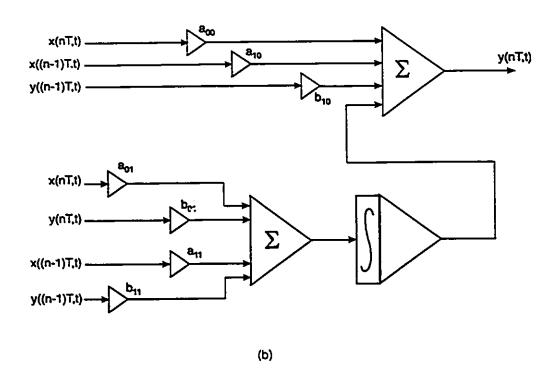

#### 2-2.3 DESIGN OF PE

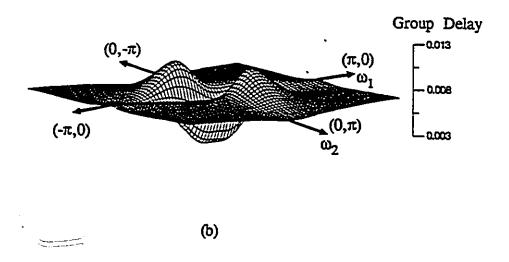

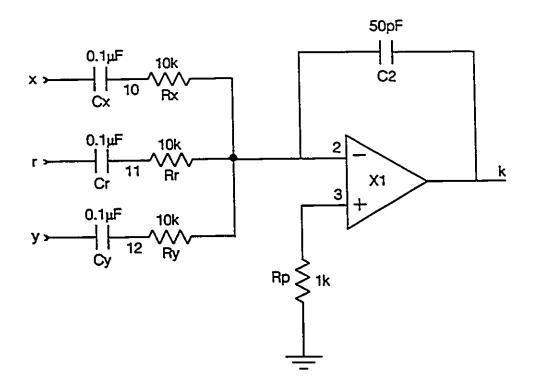

Type I and type II PE's, as defined in Figure 2-7, were constructed using high-speed op-amp circuits. This was done for the type I PE as shown in Figure 2-15. The op-amp is configured as an inverting weighted summer and drives a passive delay line with resistive termination. The circuitry for a type II PE is the same as for a type I PE except that it consists solely of the inverting summer op-amp circuit excluding the delay line.

With reference to Fig. 2-10, the summing amplifier configuration produces the sum  $(-R_f/R_a)X_{IN} + (-R_f/R_a)Y_{IN} - Y'_{IN}$ . Comparing with Figure 2-7,  $w_1 = (-R_f/R_a)$  and  $w_2 = (-R_f/R_a)$ . For greater ease in setting coefficient values in the experimental prototype,  $R_a$  and  $R_b$  are variable resistors.

Figure 2-15

Op-amp circuit for PE (type I shown)

The op-amp used in the PE's of the prototype is an EL2020C (Elantec). This is a high-speed monolithic (50MHz - 3 dB bandwidth) current feedback type op-amp, specifically

designed for video and other applications that require high slew rates, fast settling times and low power consumption. In contrast with conventional op-amps, those such as the EL2020C that use the current feedback topology provide nearly constant bandwidth and settling time over a wide range of closed-loop voltage gains [23,24,25]. Higher performance (200 MHz - 3 dB bandwidth)) current feedback op-amps specifically designed for HDTV and other comparable high-speed applications such as the EL400 (Elantec) are available in an 8 pin mini-DIP package that is pinout compatible with the EL2020C. These higher performance op-amps could be used instead of the EL2020C in Figure 2-15 for HDTV application.

A passive delay line is used to implement a pixel delay (denoted  $z_2^{-1}$  in the z-domain). In the time domain, a signal x(m,n) is delayed by one pixel time resulting in a delayed version of the signal x(m,n-1). The passive delay line used in the PE's of the prototype is a type 1514-70D (Data Delay Devices). Lumped constant delay lines of this type are widely used in a number of electronic applications [26]. They are generally designed using low-pass LC filters as basic units cascaded in stages having linear phase characteristics overall. The type 1514-70D delay line has a delay time  $T_d$ =70ns and a characteristic impedance  $z_0$ =250 $\Omega$  and accordingly is terminated in a 250 $\Omega$  resistor. This delay line is available in a four pin SIP package that does not take up much circuit board space. Lumped constant delay lines with a clock input and sample-and-hold output are available in 8 pin DIP packages (e.g. Reticon 5100 series) and can be used instead if desired. In the 2 x 2 filter prototype the delay lines used were found adequate to establish an accurate 70ns pixel delay. (The pixel delay time is 70ns for NTSC.)

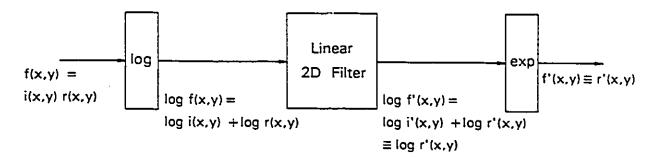

#### 2-3 HOMOMORPHIC FILTERING

An image f(x,y) is defined as a two-dimensional light intensity function of spatial coordinates (x,y). In the illumination-reflectance model of an image, the illumination component i(x,y) due to the amount of source light incident on the scene being viewed and the reflectance component r(x,y) due to light reflected by objects in the scene are considered to vary independently, so that the image is formed multiplicatively, f(x,y) being expressed by f(x,y)=i(x,y) r(x,y) (2-12)

Illumination is directly responsible for the dynamic range achieved by the pixels of an image while contrast is a function of the reflectance.

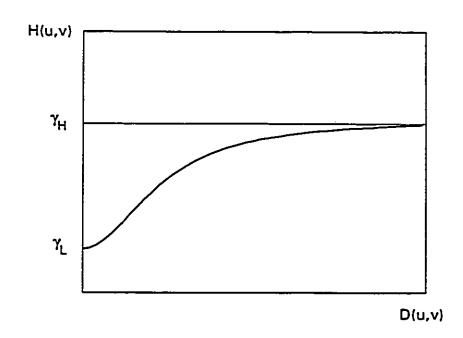

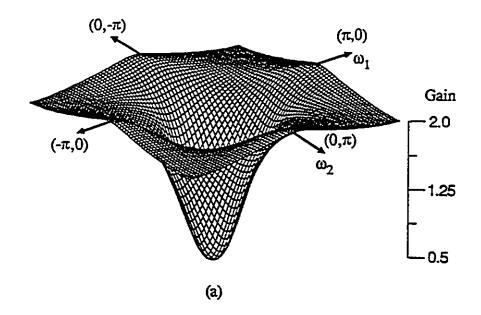

By means of homomorphic filtering, [18], as depicted in the block diagram of Figure 2-16, it is possible to process the illumination and reflectance components of an image separately. In this scheme, input data is logarithmically converted prior to performing a linear filtering operation (usually high pass filtering) and the result is converted back to the linear scale. In the present work the linear operation selected is a 2-D high frequency emphasis Butterworth (near linear phase) recursive filter of order 2 x 2. A cross-sectional plot of the 2-D magnitude response of this function is shown in Figure 2-17. Magnitude and group delay responses of the designed 2-D filter are plotted in Figure 2-18, while Figure 2-19 gives the coefficients of the designed filter. Group delay is essentially constant considering the scale used in the drawing.

To a first approximation we can assume as in [18] that the illumination component contains mostly low frequencies in its logarithm and that the logarithm of the reflectance component contains mostly high frequencies. Choosing the parameters  $\gamma_L$  and  $\gamma_H$  so that

$\gamma_L$ =0.5 and  $\gamma_H$ =2, for the Butterworth filter function will tend to attenuate the low frequencies and amplify the high frequencies. This results in an enhancement of the reflectance components, which represent the objects in the scene, and attenuation of the illumination component, which represents the light distribution. The net result is a clearer image.

Figure 2-16

Homomorphic Filter

Figure 2-17

Cross-section of a circularly symmetric 2-D Butterworth filter function used in homomorphic filtering. D(u,v) is the distance from the origin

Figure 2-18

Magnitude and group delay response - designed 2-D filter

- (a) Magnitude response

- (b) Group delays:  $\tau_1$ ,  $\tau_2$  (both identical)

$$(a_{ij}) = \begin{bmatrix} -0.09347 & -0.07165 & -0.04295 \\ -0.07165 & 1.79010 & -0.87585 \\ -0.04295 & -0.87585 & 0.46525 \end{bmatrix}$$

$$(b_{ij}) = \begin{bmatrix} 1.0 & -0.45083 & -0.00833 \\ -0.45083 & 0.26831 & 0.00681 \\ -0.00833 & 0.00681 & 0.00292 \end{bmatrix}$$

Figure 2-19

Filter coefficients - designed 2-D filter

# 2-4 SPICE SIMULATION OF THE 2-D SEMI-SYSTOLIC FILTER STRUCTURE

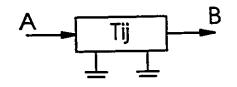

In this section, we present a simulation of the 2-D semi-systolic analog filter structure realization presented in Section 2-1. The particular version of SPICE being used herein is Microsim PSPICE [27].

#### 2-4.1 SPICE MODELLING OF A SINGLE PE

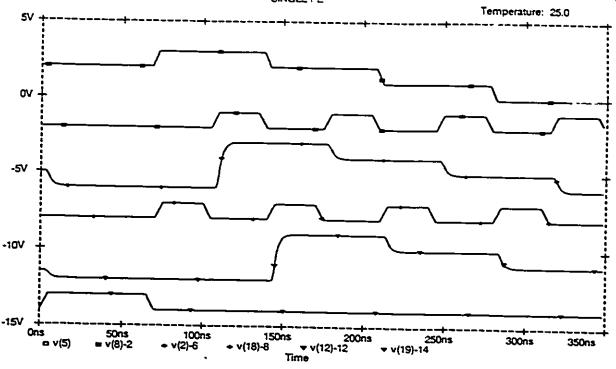

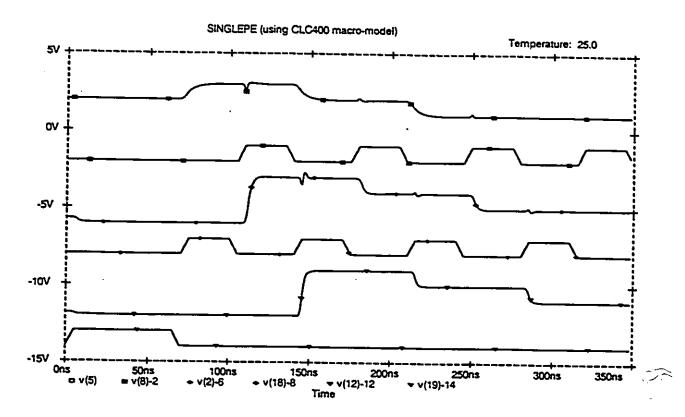

The method of filter realization given in [13] results in a modular structure (Figure 2-3) in which all PE's are identical. The fixed coefficient PE realization in analog form, as given in [13], is shown in Figure 2-20. A SPICE simulation model of this PE circuitry is shown in Figure 2-21 and its corresponding netlist is shown in Figure 2-22. (The latter figure does not show the parasitic capacitances included in the netlist so as not to clutter the diagram.)

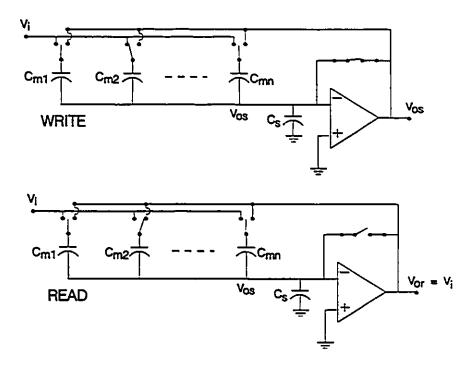

Each PE generates a weighted sum of inputs which is delayed by one sampling clock period. With reference to the SPICE netlist in Figure 2-22, the subcircuit call to x3 introduces an op-amp inverting summer configuration with input resistors rx, ry, rz and feedback resistor rf3. Signals are input to the PE at nodes 24, 25, 26 and the (inverted) summed output appears at node 5. Independent sources vix, viy and viz are driving waveforms to test the simulated single PE. The summed output at node 5 is delayed by one sampling clock period by means of the circuitry connected between nodes 5 and 12. The op-amp circuit associated with subcircuit x1 and external components rf and rg buffers the voltage signal held on capacitor cs. Similarly the signal from cs2 is buffered by the op-amp circuit associated with x2. S1 and S2 are series sampling switches for capacitors cs and cs2