### University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2005

## Novel arithmetic implementations using cellular neural network arrays.

Youssef Ibrahim University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Ibrahim, Youssef, "Novel arithmetic implementations using cellular neural network arrays." (2005). *Electronic Theses and Dissertations*. 2878. https://scholar.uwindsor.ca/etd/2878

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# UM®

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

### Novel Arithmetic Implementations Using Cellular Neural Network Arrays

by

**Youssef Ibrahim**

A Dissertation

Submitted to the Faculty of Graduate Studies and Research through the Department of Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at the University of Windsor

> Windsor, Ontario, Canada 2005

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

.

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence ISBN: Our file Notre retérence ISBN:

#### NOTICE: .

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadiennesur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manguant.

#### 1032587

#### © 2005 Youssef Ibrahim

All Rights Reserved. No part of this document may be reproduced, stored or otherwise retained in a retrieval system or transmitted in any form, on any medium or by any means without the prior written permission of the author

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

### Abstract

The primary goal of this research is to explore the use of arrays of analog self-synchronized cells - the cellular neural network (CNN) paradigm - in the implementation of novel digital arithmetic architectures. In exploring this paradigm we also discover that the implementation of these CNN arrays produces very low system noise; that is, noise generated by the rapid switching of current through power supply die connections - so called di/dt noise. With the migration to sub 100 nanometer process technology, signal integrity is becoming a critical issue when integrating analog and digital components onto the same chip, and so the CNN architectural paradigm offers a potential solution to this problem. A typical example is the replacement of conventional digital circuitry adjacent to sensitive bio-sensors in a SoC Bio-Platform. The focus of this research is therefore to discover novel approaches to building low-noise digital arithmetic circuits using analog cellular neural networks, essentially implementing asynchronous digital logic but with the same circuit components as used in analog circuit design.

We address our exploration by first improving upon previous research into CNN binary arithmetic arrays. The second phase of our research introduces a logical extension of the binary arithmetic method to implement binary signed-digit (BSD) arithmetic. To this end, a new class of CNNs that has three stable states is introduced, and is used to implement arithmetic circuits that use binary inputs and outputs but internally uses the BSD number representation. Finally, we develop CNN arrays for a 2-dimensional number representation (the Double-base Number System - DBNS). A novel adder architecture is described in detail, that performs the addition as well as reducing the representation for further processing; the design incorporates an innovative self-programmable array. Extensive simulations have shown that our new architectures can reduce system noise by almost 70dB and crosstalk by more than 23dB over standard digital implementations.

To: My parents,

·

my wife, Eman,

and my daughter, Lauren

### Acknowledgments

I would like to acknowledge all the people who assisted and supported me over the years of my graduate study at the University of Windsor. Although this thesis prominently bears my name, it would not have been possible without their contribution.

I would like to express my gratitude to my advisors, Dr. G.A. Jullien and Dr. W.C. Miller for providing guidance and support. Aside from keeping me on track, they have also allowed me the freedom to pursue research at my own pace. I would like to extend thanks to the members of my committee, Dr. N. Yazdi, Dr. A. Ngom, Dr. C. Chen, and Prof. M. Ahmadi whose insightful comments and helpful suggestions have improved this thesis. I am also grateful to Dr. R. Muscedere who helped me use system-level CAD tools.

I am indebted to the RCIM lab manager Mr. Till Kuendiger who was always there whenever I needed help. I appreciate my colleagues in the RCIM research group, my friends in all other research groups, and the entire Electrical and Computer Engineering staff. They were a constant source of encouragement and optimism over the years.

I would like to acknowledge financial support from the Natural Sciences and Engineering Research Council of Canada, the Micronet Network of Centres of Excellence, and Gennum Corporation. Furthermore, I am obliged to CMC Microsystems (formerly The Canadian Microelectronics Corporation) for providing design tools, workstations and fabrication services.

Finally, I would like to thank my parents, Salah and Nadia, for their never-fading love and encouragement. I am also grateful to my surrogate parents, Larry and Doreen Cheshire, and to my surrogate parents-in-law, Joseph and Betty Tomc, for their love and assistance during my stay in Windsor. I am indebted to my church family at Campbell Baptist Church for their moral support throughout this research project. I am very grateful to my wife, Eman, and my daughter, Lauren, for their love, inspiration, and understanding through the very difficult moments in my studies.

### **Table of Contents**

| Abstract                 |                                                                                                                                  | iv     |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------|--|

| Dedication               |                                                                                                                                  | v      |  |

| Acknowledgm              | ents                                                                                                                             | vi     |  |

| List of Figures          | 5                                                                                                                                | x      |  |

| List of Tables           |                                                                                                                                  | xiii   |  |

| List of Symbol           | ls                                                                                                                               | xiv    |  |

| List of Abbrev           | List of Abbreviations xvii                                                                                                       |        |  |

| Chapter 1                | Introduction                                                                                                                     | 1      |  |

| 1.1<br>1.2<br>1.3<br>1.4 | Low-noise - motivation<br>Substrate Noise<br>CNN-based Arithmetic Circuits - Rationale<br>Existing CNN-based Arithmetic Circuits | 3<br>8 |  |

| 1.5<br>1.6<br>1.7        | CNN-based Arithmetic Circuits Design Goals<br>Thesis Overview<br>Thesis Organization                                             | 14     |  |

| Chapter 2                | Cellular Neural Networks: An Overview                                                                                            | 16     |  |

| 2.1<br>2.2<br>2.3        | CNN History and Applications<br>CNN Structures<br>CNN Cell Architecture                                                          | 18     |  |

|           | 2.4      | CNN Dv    | namics                                                 | 22  |

|-----------|----------|-----------|--------------------------------------------------------|-----|

|           | <i>~</i> | 2.4.1     | Modes of Operation                                     |     |

|           |          | 2.4.2     | Network Convergence                                    |     |

|           | 2.5      |           | y                                                      |     |

|           | 2.5      | Samma     | y                                                      | 27  |

| Chapter 3 | Bin Bin  | nary Arit | hmetic Using CNNs                                      | 25  |

|           | 3.1      | The Bina  | ary Number System: Overview                            | 26  |

|           |          | 3.1.1     | Definition                                             | 26  |

|           |          | 3.1.2     | Binary Addition                                        | 26  |

|           | 3.2      | Designin  | ng a 1-bit Binary Full Adder Using CNN (CNNBFA)        | 28  |

|           |          | 3.2.1     | CNNBFA Templates Design                                |     |

|           |          | 3.2.2     | CNNBFA CMOS Basic Building Blocks                      | 30  |

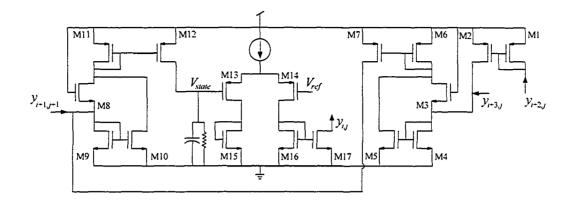

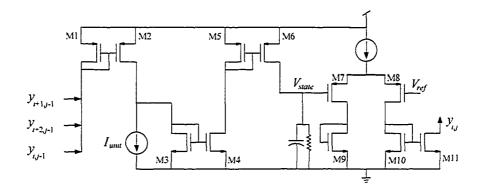

|           |          | 3.2.3     | CNNBFA CMOS Implementation                             | 34  |

|           |          | 3.2.4     | CNNBFA Hspice Simulation                               | 36  |

|           | 3.3      | CNNBF.    | A Design Scalability                                   |     |

|           |          | 3.3.1     | A 32-bit CNN-based Binary Adder                        | 38  |

|           |          | 3.3.2     | Impact of the CNN-based Binary Adder on Substrate No   | ise |

|           |          |           |                                                        | 39  |

|           | 3.4      | CNNBF.    | A Design Compatibility                                 | 42  |

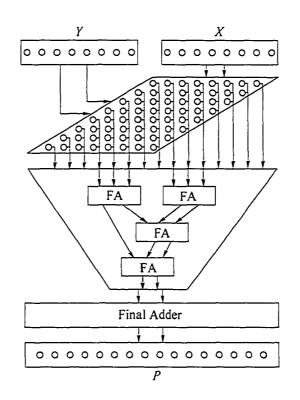

|           |          | 3.4.1     | A 32x32-bit CNN-based Binary Multiplier                |     |

|           |          | 3.4.2     | Impact of the CNN-based Binary Multiplier on Substrate | 2   |

|           |          |           | Noise                                                  | 44  |

|           | 3.5      | Summar    | y of CNN-based Binary Arithmetic                       | 45  |

| Chapter 4 | l Bi     | nary Sigr | ned-Digit Arithmetic Using CNNs                        | 47  |

|           | 4.1      | Introduc  | tion                                                   | 48  |

|           | 4.2      |           | ary Signed-Digit Number System: Overview               |     |

|           |          | 4.2.1     | Definition                                             |     |

|           |          | 4.2.2     | BSD Addition                                           | 51  |

|           | 4.3      | Designii  | ng a 1-digit BSD Full Adder Using CNN (CNNBSDFA)       | 54  |

|           |          | 4.3.1     | A 3-State CNN Cell.                                    |     |

|           |          | 4.3.2     | CNNBSDFA Templates Design                              |     |

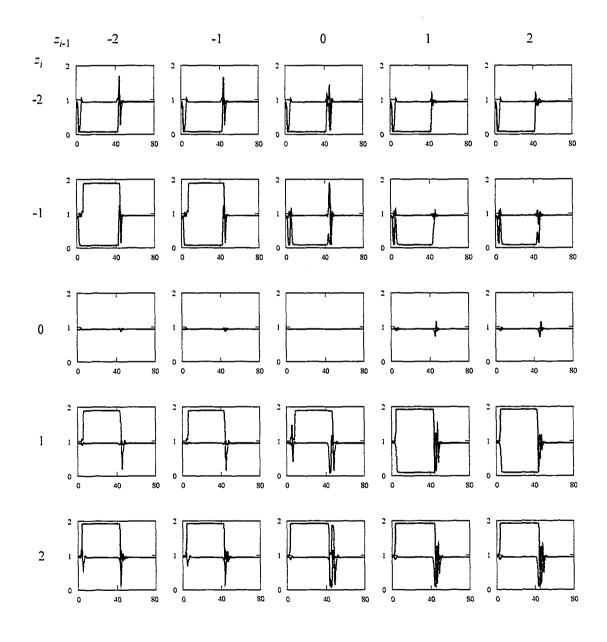

|           |          | 4.3.3     | CNNBSDFA Hspice Simulation                             |     |

|           | 4.4      |           | DFA Design Scalability                                 |     |

|           | - •      | 4.4.1     | A 32-digit CNN-based BSD Adder                         |     |

|           |          | 4.4.2     | Impact of the CNN-based BSD Adder on Substrate Nois    |     |

|           |          |           |                                                        |     |

| 62        |

|-----------|

| Noise63   |

| 65        |

| 67        |

| ate Noise |

| 68        |

| 69        |

|           |

| Chapter 5 D    | ouble-Ba   | se Number System Arithmetic Using CNNs             | 71    |

|----------------|------------|----------------------------------------------------|-------|

| 5.1            | Introduc   | ction                                              | 72    |

| 5.2            | The Do     | uble-Base Number System: Overview                  | 73    |

|                | 5.2.1      | Definition                                         |       |

|                | 5.2.2      | DBNS Addition                                      | 75    |

|                | 5.2.3      | Reduction to Addition-Ready Representation         | 77    |

| 5.3            | Designi    | ng a 1-bit DBNS Adder Unit Using CNN (CNNDBNSA)    | U)79  |

|                | 5.3.1      | CNNDBNSAU Templates Design                         |       |

|                | 5.3.2      | Dealing with Special Cases of DBNS-maps            | 81    |

|                | 5.3.3      | CNNDBNSAU CMOS Implementation                      |       |

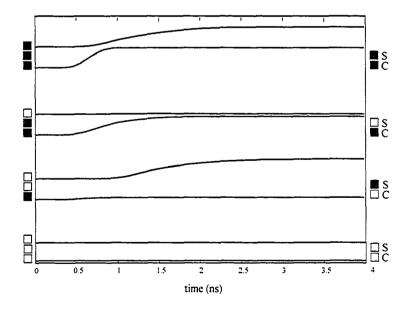

|                | 5.3.4      | CNNDBNSAU Hspice Simulation                        |       |

| 5.4            | CNNDI      | 3NSAU Design Scalability                           |       |

|                | 5.4.1      | A 20x20 CNN-based DBNS Adder                       |       |

|                | 5.4.2      | Constraints on the CNN-based DBNS Adder to be Self | -Pro- |

|                |            | grammable                                          | 94    |

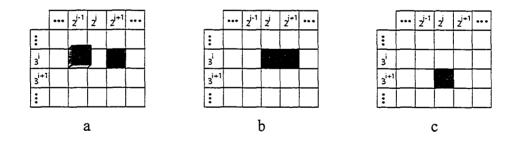

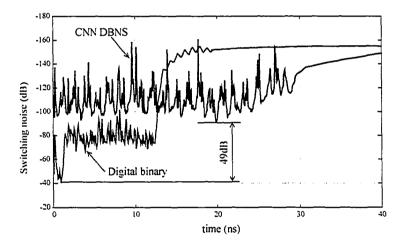

|                | 5.4.3      | Impact of the CNN-based DBNS Adder on Substrate N  | loise |

|                |            | -                                                  | 97    |

| 5.5            | Summa      | ry of CNN-based DBNS Arithmetic                    |       |

| Chapter 6 C    | Conclusior | 15                                                 | 100   |

| 6.1            | Summa      | ry and Contributions                               | 100   |

| 6.2            | Conclus    | sions                                              | 107   |

| 6.3            | Suggest    | tions for Future Work                              | 108   |

| REFERENCES     | 5          |                                                    | 110   |

| Vita Auctoris. | ••••       |                                                    | 126   |

### **List of Figures**

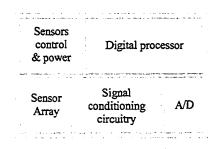

| Figure 1.1  | Simplified block diagram of a bio-sensor SoC chip.                                                                                              | 2   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

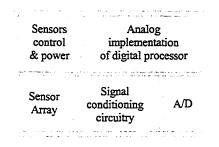

| Figure 1.2  | Reducing system noise in the bio-sensor with smooth analog transitions.                                                                         | 3   |

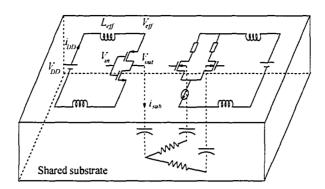

| Figure 1.3  | Lumped model of the substrate coupling                                                                                                          | 4   |

| Figure 1.4  | Hspice simulation of a standard digital inverter.                                                                                               |     |

| Figure 1.5  | Hspice simulation of $di / dt$ for a digital inverter and a CNN cell                                                                            | 9   |

| Figure 1.6  | Hspice simulation of $dv/dt$ for a digital inverter and a CNN cell                                                                              | .10 |

| Figure 1.7  | Hspice simulation of a CNN cell output voltage for different time                                                                               |     |

|             | constants                                                                                                                                       |     |

| Figure 1.8  | The flat binary adder                                                                                                                           |     |

| Figure 1.9  | MATLAB simulation of the recursive binary adder                                                                                                 | .13 |

| Figure 2.1  | Examples of rectangular and hexagonal CNN grids with neighborhood of size 1. Light grey cells belong to the neighborhood of the dark grey cell. |     |

| Figure 2.2  | CNN cell activation function.                                                                                                                   |     |

| Figure 2.3  | A block diagram representation of a CNN cell                                                                                                    |     |

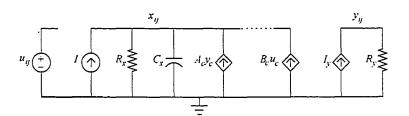

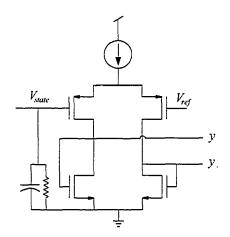

| Figure 2.4  | Schematic of an electrical implementation of a CNN cell                                                                                         | .22 |

| Figure 3.1  | An example of binary addition.                                                                                                                  |     |

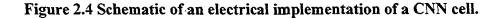

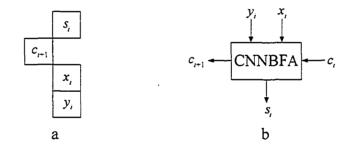

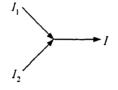

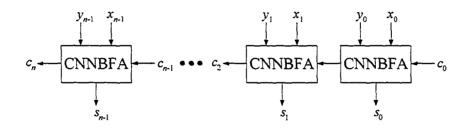

| Figure 3.2  | Block diagram of a binary adder: (a) 1-bit full adder, (b) <i>n</i> -bit binary adder.                                                          | .28 |

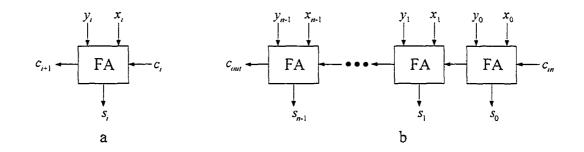

| Figure 3.3  | Representation of the CNN-based 1-bit full adder: (a) CNN grid, (b) blo diagram.                                                                |     |

| Figure 3.4  | Schematic of a current-mode summing node.                                                                                                       |     |

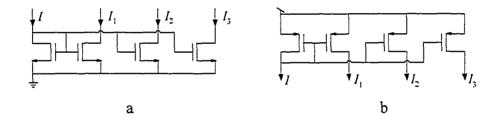

| Figure 3.5  | Schematic of current sources: (a) nMOS current source, (b) pMOS current source.                                                                 |     |

| Figure 3.6  | Schematic of simple current mirrors: (a) nMOS current mirror, pMOS current mirror.                                                              | .32 |

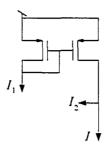

| Figure 3.7  | Schematic of a subtractor                                                                                                                       | .33 |

| Figure 3.8  | Schematic of absolute function                                                                                                                  | .33 |

| Figure 3.9  | Schematic of basic CNN cell.                                                                                                                    | .34 |

| Figure 3.10 | Schematic of the CNNBFA sum cell with connections to neighbors                                                                                  |     |

| Figure 3.11 | Schematic of the CNNBFA carry cell with connections to neighbors                                                               | .36 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.12 | Hspice simulation of the CNNBFA.                                                                                               | .37 |

| Figure 3.13 | Block diagram of an <i>n</i> -bit CNN-based binary adder.                                                                      | .38 |

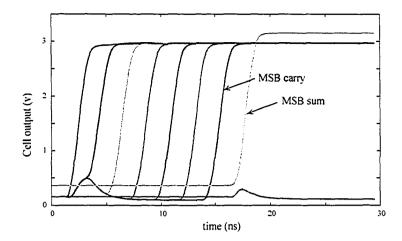

| Figure 3.14 | Hspice simulation of an 8-bit section of the 32-bit CNN-based binary adder                                                     | .39 |

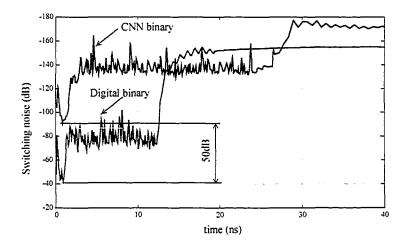

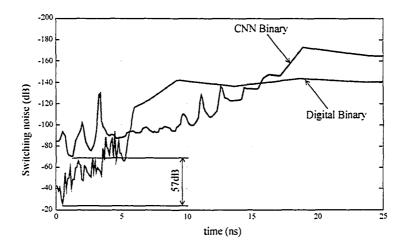

| Figure 3.15 | Switching noise of the CNN-based and standard digital 32-bit binary adders.                                                    | .41 |

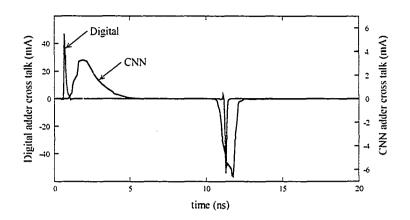

| Figure 3.16 | Cross talk noise of the CNN-based and standard digital 32-bit binary adders.                                                   | .42 |

| Figure 3.17 | Block diagram of a carry-save tree multiplier.                                                                                 | .43 |

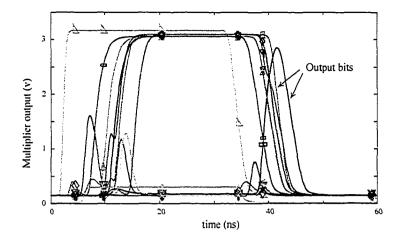

| Figure 3.18 | Hspice simulation of a section of the 32x32-bit CNN-based binary multiplier.                                                   |     |

| Figure 3.19 | Switching noise of the CNN-based and standard digital 32x32-bit binary multipliers.                                            |     |

| Figure 4.1  | An example of BSD addition                                                                                                     | 52  |

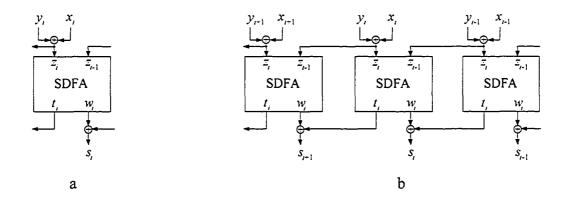

| Figure 4.2  | Block diagram of a BSD adder: (a) 1-digit BSD adder, (b) <i>n</i> -digit BSD adder.                                            | 53  |

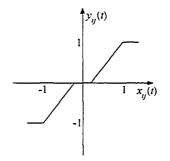

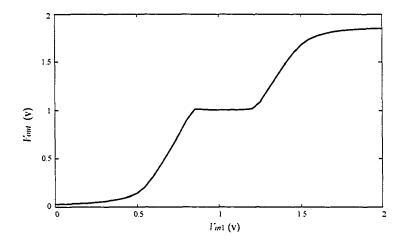

| Figure 4.3  | The required CNN cell activation function                                                                                      |     |

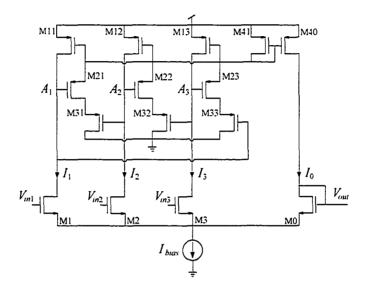

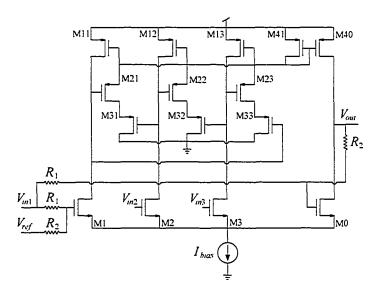

| Figure 4.4  | Schematic of the 3-input median extractor.                                                                                     | 56  |

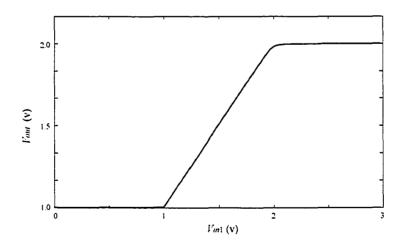

| Figure 4.5  | Transfer characteristics of the 3-input median extractor.                                                                      | 56  |

| Figure 4.6  | Schematic of the 3-state circuit                                                                                               | 57  |

| Figure 4.7  | Transfer characteristics of the 3-state CNN cell                                                                               | 58  |

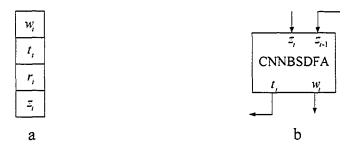

| Figure 4.8  | Representation of the CNN-based 1-digit SD adder: (a) CNN grid, (b) block diagram.                                             | 59  |

| Figure 4.9  | Hspice simulation of the CNNBSDFA.                                                                                             | 61  |

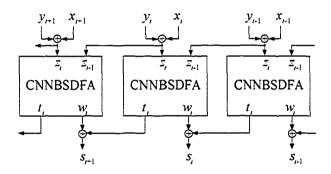

| Figure 4.10 | Block diagram of an n-digit CNN-based BSD adder                                                                                | 62  |

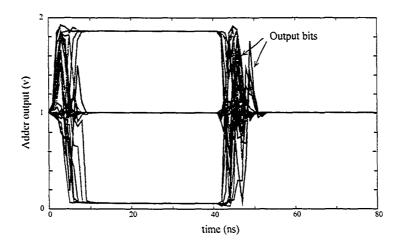

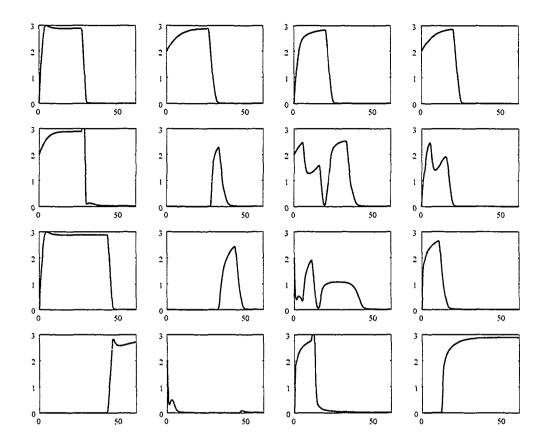

| Figure 4.11 | Hspice simulation of a section of the 32-digit CNN-based BSD adder                                                             | 63  |

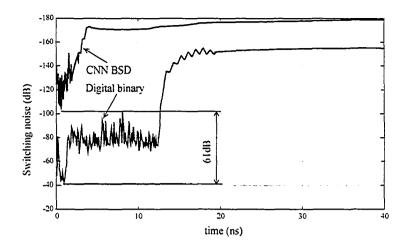

| Figure 4.12 | Switching noise of the CNN-based 32-digit BSD adder and 32-bit stands digital binary adder.                                    |     |

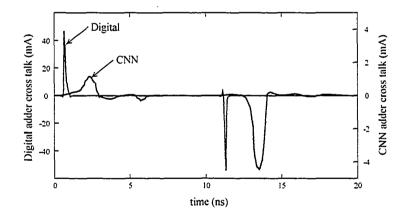

| Figure 4.13 | Cross talk of the CNN-based 32-digit BSD adder and 32-bit standard digital binary adder.                                       | 64  |

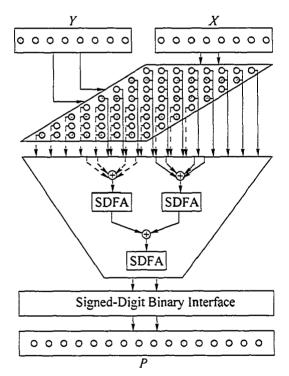

| Figure 4.14 | Block diagram of the BSD multiplier.                                                                                           | 66  |

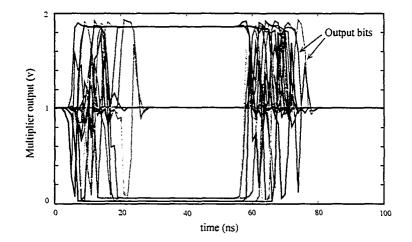

| Figure 4.15 | Hspice simulation of an 8-digit section of the 32x32-digit CNN-based<br>BSD multiplier. The output is in BSD representation.   |     |

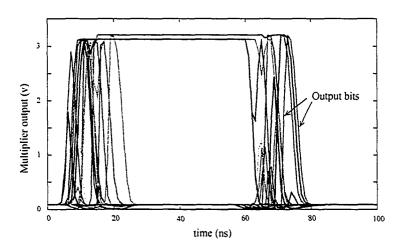

| Figure 4.16 | Hspice simulation of an 8-digit section of the 32x32-digit CNN-based<br>BSD multiplier. The output is in binary representation |     |

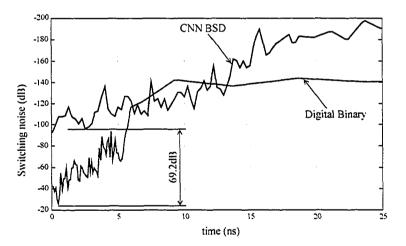

| Figure 4.17 | Switching noise of the CNN-based BSD and standard digital 32x32-bit binary multipliers.                                        |     |

| Figure 5.1  | Different representations of 108 in the DBNS                                                                                   |     |

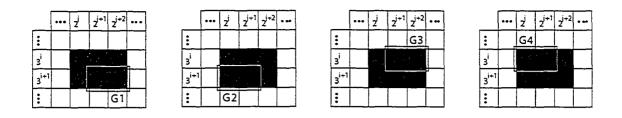

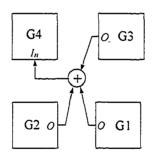

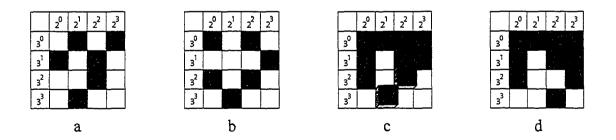

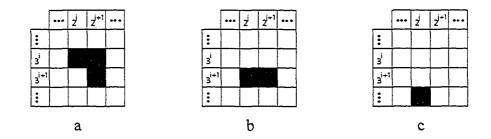

| Figure 5.2  | Graphical representation of the overlaying rule: (a) initial map, (b) final map.                                               | I   |

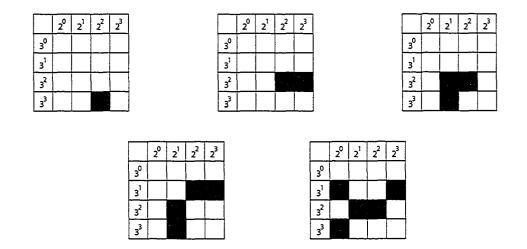

| Figure 5.3  | Addition in DBNS: (a) $X$ , (b) $Y$ , (c) map obtained by overlaying, (d) $Z$ after applying the overlaying rule.              |     |

.

| Figure 5.4  | Graphical representation of the reduction rule: (a) initial map, (b) final map.                                                                                                 | .78 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

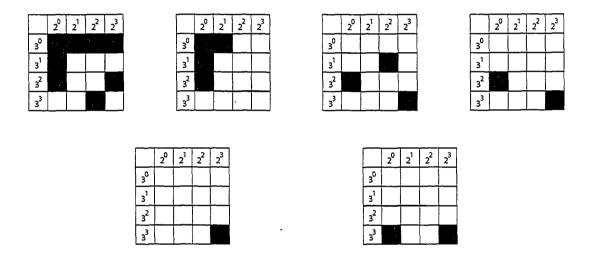

| Figure 5.5  | Non-zero digit reduction of Z: (a) initial map, (b) intermediate map, (c) final map.                                                                                            | .78 |

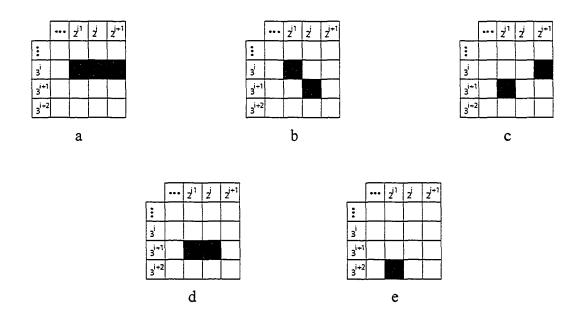

| Figure 5.6  | An example of simultaneous reductions: (a) initial map, (b) and (c) corresolutions, (d) and (e) wrong output                                                                    |     |

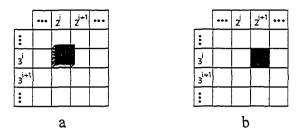

| Figure 5.7  | Two possible simultaneous applications of Eqn. (5.4) to the same cell                                                                                                           | .83 |

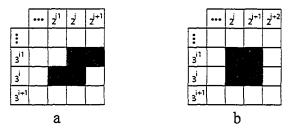

| Figure 5.8  | An example of the order of reduction: (a) initial map, (b) <i>j</i> in ascending order, (c) <i>j</i> in descending order.                                                       | .85 |

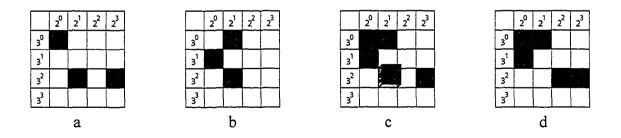

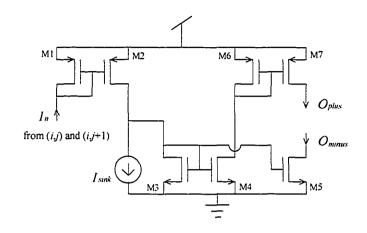

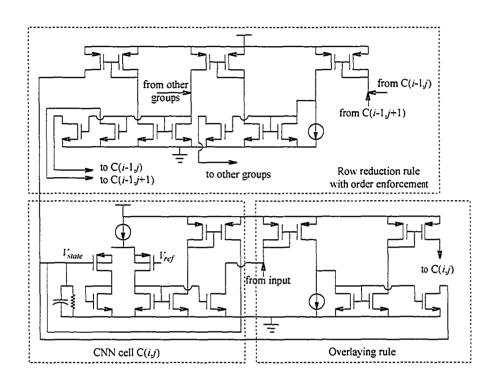

| Figure 5.9  | Schematic of the reduction rule.                                                                                                                                                | .87 |

| Figure 5.10 | Connection to participating cells.                                                                                                                                              | .87 |

| Figure 5.11 | A situation where the row reduction rule can be applied to four different groups of cells.                                                                                      |     |

| Figure 5.12 | Connection between groups of cells.                                                                                                                                             | .88 |

| Figure 5.13 | CNNDBNS adder cell schematic                                                                                                                                                    | .89 |

| Figure 5.14 | Hspice simulation of the CNNDBNSAU: (a) only the row reduction rule applicable, (b) both the row and overlaying reduction rules are applicable.                                 | le  |

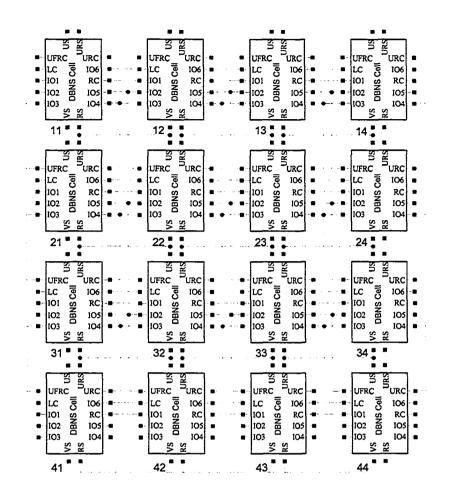

| Figure 5.15 | Schematic of a 4x4 section of the CNN-based DBNS adder                                                                                                                          |     |

| Figure 5.16 | An example of addition using the CNN-DBNS adder: (a) X, (b) Y, (c)<br>Overlaying X and Y, (d) Z after time T.                                                                   | 92  |

| Figure 5.17 | Non-zero digit reduction of Z. Starting from left to right, each map is obtained from the previous map after a time T                                                           | .93 |

| Figure 5.18 | Hspice simulation of a 4x4 section of the CNN-based DBNS adder                                                                                                                  | .94 |

| Figure 5.19 | An example of a reduction rule followed by a reduction rule: (a) initial map, (b) map after the first reduction rule, (c) map after the second reduction rule.                  | .95 |

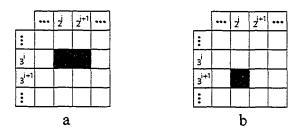

| Figure 5.20 | An example of a carry propagation rule followed by a reduction rule: (a initial map, (b) map after applying the overlaying rule, (c) map after applying the row reduction rule. | )   |

| Figure 5.21 | Switching noise of the CNN-based 20x20 DBNS adder and 32-bit standard digital binary adder                                                                                      | 97  |

| Figure 5.22 | Cross talk of the CNN-based 20x20 DBNS adder and 32-bit standard digital binary adder.                                                                                          | 98  |

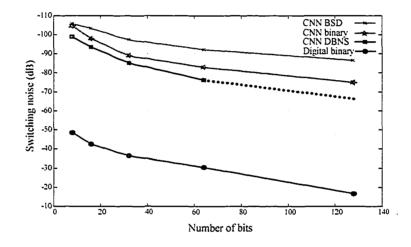

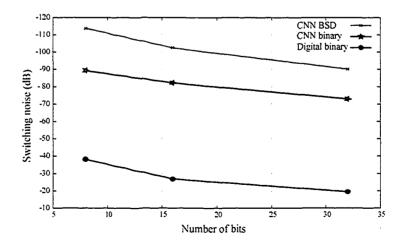

| Figure 6.1  | Switching noise of different adders vs. adder size                                                                                                                              | 106 |

| Figure 6.2  | Switching noise of different multipliers vs. multiplier size                                                                                                                    |     |

| Figure 6.3  | Cross talk of different adders designs                                                                                                                                          | 107 |

### **List of Tables**

| Table 3.1 | Truth table of a 1-bit binary full adder.             | 37  |

|-----------|-------------------------------------------------------|-----|

| Table 4.1 | Truth table of BSD addition (* represents don't care) | 60  |

| Table 5.1 | Truth table of DBNS adder unit.                       | 90  |

| Table 6.1 | Summary of design specifications.                     | 105 |

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

### **List of Symbols**

| Δ                  | Delta operator                                                           |

|--------------------|--------------------------------------------------------------------------|

| ρ                  | Substrate resistivity                                                    |

| 3                  | Substrate permittivity                                                   |

| α                  | Self-feedback current coefficient                                        |

| ī                  | Integer digit -1                                                         |

| 2                  | Integer digit -2                                                         |

| $\pi(i)$           | Permutation <i>i</i>                                                     |

| $\bar{x}_i$        | Two's complement of digit at position $i$ of operand $X$                 |

| Г                  | Number of full adder levels in binary reduction tree                     |

| μ                  | Micron                                                                   |

| A <sub>c</sub>     | Output feedback template                                                 |

| A <sub>ij:kl</sub> | Element $kl$ of the output feedback template $A$ for the CNN cell C(i,j) |

| B <sub>c</sub>     | Input control template                                                   |

| С                  | Carry out of an addition                                                 |

| C(i,j)             | CNN cell at position (i,j)                                               |

| Ceff               | Effective parasitic capacitance                                          |

| c <sub>i</sub>     | Digit at position $i$ of the carry in/out $C$                            |

| C <sub>x</sub>     | Input capacitance of a CNN cell                                          |

| Ι                  | Bias of a CNN cell                                                       |

| In <sub>i</sub>    | Input <i>i</i> to median extractor                                       |

|                    |                                                                          |

| i <sub>sub</sub>   | Substrate current                                                        |

|--------------------|--------------------------------------------------------------------------|

| I <sub>unit</sub>  | Unit current                                                             |

| I <sub>VDD</sub>   | Instantaneous supply current                                             |

| $I_x(i,j)$         | DBNS representation of operand $X$                                       |

| $I_y$              | Output current of a CNN cell                                             |

| $I_{\gamma}(i,j)$  | DBNS representation of operand Y                                         |

| I_(i,j)            | DBNS representation of sum out $Z$                                       |

| k                  | Average number of nonzero digits                                         |

| L                  | Transistor length                                                        |

| L                  | Digit set of the binary signed digit                                     |

| L <sub>eff</sub>   | Effective parasitic inductance                                           |

| m                  | Milli                                                                    |

| m                  | Meter                                                                    |

| M                  | Number of rows in a CNN grid                                             |

| m <sub>i</sub>     | Scaling factor of a current mirror                                       |

| n                  | Nano                                                                     |

| n                  | Number of digits in a number                                             |

| Ν                  | Number of columns in a CNN grid                                          |

| N(i,j)             | Neighborhood of CNN cell C(i,j)                                          |

| 0 <sub>minus</sub> | Negative output current of reduction rule                                |

| 0 <sub>plus</sub>  | Positive output current of reduction rule                                |

| р                  | Pico                                                                     |

| Р                  | Product of multiplication                                                |

| $p_{i.j}$          | Partial product of digit $i$ of operand $X$ and digit $j$ of operand $Y$ |

| $P_{j}$            | Product of operand $X$ and digit at position $j$ of operand $Y$          |

| q(r,t)             | Transient charge density                                                 |

| r                  | Radius of the CNN neighborhood                                           |

| R <sub>i</sub>     | Resistor i                                                               |

| $R_x$              | Input resistance of a CNN cell                                           |

| $R_y$              | Output resistance of a CNN cell                                          |

| S                  | Sum out of an addition                                                   |

| s <sub>i</sub>     | Digit at position <i>i</i> of the sum out S                              |

| Т                  | Time constant of a CNN cell                                              |

| T <sub>delay</sub> | Maximum delay of DBNS adder                                              |

| -                  |                                                                          |

Transfer digit at position i $t_i$ Input to CNN cell C(i,j)  $u_{ii}$ V(r,t)Transient voltage vector Bias voltage V<sub>bias</sub>  $V_{DD}$ Power supply voltage  $V_{eff}$ Effective voltage on chip Vin Input voltage Vout Output voltage V<sub>ref</sub> Reference voltage V<sub>state</sub> State voltage of a CNN cell W Transistor width Intermediate sum at position *i* w; Х An operand to an arithmetic operation Digit at position i of the operand X $x_i$ Digit in position (i,j) in a DBNS number  $x_{i,j}$ State voltage of CNN cell C(i,j)  $x_{ij}$ Y An operand to an arithmetic operation Digit at position i of the operand YУi Output voltage of CNN cell C(i,j)  $y_{ii}$ Ζ Instantaneous sum out Digit at position i of the instantaneous sum out Z $\overline{z}_{i}$

### List of Abbreviations

| 2D        | Two dimensional                                  |

|-----------|--------------------------------------------------|

| A/D       | Analog-to-digital                                |

| ARDBNR    | Addition-ready double-base number representation |

| BC        | Before Christ                                    |

| BSD       | Binary signed-digit                              |

| BSDNS     | Binary signed-digit number system                |

| CDBNS     | Canonic double-base number system                |

| CD-ROM    | Compact disk-Read only memory                    |

| CMOS      | Complementary metal-oxide semiconductor          |

| CNN       | Cellular neural network                          |

| CNNBFA    | CNN-based binary full adder                      |

| CNNBSDFA  | CNN-based signed-digit full adder                |

| CNNDBNSAU | CNN-based double-base adder unit                 |

| CNN-UM    | Cellular neural network universal machine        |

| CSD       | Canonic signed-digit                             |

| CT-CNN    | Continuous time CNN                              |

| DBNS      | Double-base number system                        |

| DC        | Direct current                                   |

| DSN       | Digital switching noise                          |

| DSP       | Digital signal processing                        |

| DT-CNN    | Discrete time CNN                                |

| ECC       | Elliptic curve cryptography                      |

| FA        | Full adder                                       |

|           |                                                  |

| FIR    | Finite impulse response                           |

|--------|---------------------------------------------------|

| FLP    | Floating-point                                    |

| IC     | Integrated circuit                                |

| IDBNS  | Index calculus double-base number system          |

| IEEE   | Institute of Electrical and Electronics Engineers |

| IIR    | Infinite impulse response                         |

| JSF    | Joint sparse form                                 |

| LNS    | Logarithmic number system                         |

| LSB    | Least significant bit                             |

| MAC    | Multiply-accumulate                               |

| MAF    | Multiplication-add fused                          |

| MCM    | Multiple constant multiplication                  |

| MDLNS  | Multidimensional logarithmic number system        |

| MSB    | Most significant bit                              |

| NCDBNR | Near-canonic double-base number representation    |

| NN     | Neural network                                    |

| PS     | Porous silicon                                    |

| RF     | Radio frequency                                   |

| SD     | Signed-digit                                      |

| SDFA   | Signed-digit full adder                           |

| SDNS   | Signed-digit number system                        |

| SoC    | System-on-a-chip                                  |

| SOI    | Silicon-on-insulator                              |

| SSN    | Simultaneous switching noise                      |

| TFSOI  | Thin-film silicon-on-insulator                    |

| VCCS   | Voltage controlled current source                 |

| VLSI   | Very large scale integrated (or integration)      |

|        |                                                   |

•

### Chapter 1 Introduction

The objective of this research project is to develop novel arithmetic circuit structures using arrays of analog networks and the cellular neural network paradigm. The motivation behind this work contains both an exploration of this novel concept to a variety of arithmetic techniques and a more practical investigation into the use of these networks for implementing arithmetic circuits that produce very low di/dt noise as explained in Section 1.1. The digital switching noise and cross talk problems are defined in Section 1.2. A review of the research literature that addresses the noise problem is also presented in this section. Reasons to use the CNN paradigm are discussed in Section 1.3 and the state-of-the-art CNN-based binary adders are presented in Section 1.4. The design goals of the arithmetic circuits are introduced in Section 1.5. The thesis is outlined in Section 1.6 and Section 1.7.

### 1.1 Low-noise - motivation

The migration to sub 100 nanometer process technologies and the advances in fabrication processes have allowed the packing of ever increasing complex functionality into fewer chips on circuit boards by the use of massive integration of circuitry onto single silicon die using system-on-a-chip (SoC) tools and technologies. Despite the impressive reductions in area and cost, signal integrity remains a critical issue when integrating analog and digital components onto the same chip; for example digital circuitry adjacent to sensitive bio-sensors in a SoC Bio-Platform as depicted in Figure 1.1. One of the parasitic effects that adversely influences signal integrity is digital switching noise (DSN) produced by the supply current drawn by fast switching digital components. This noise propagates across the common Si substrate and can easily corrupt sensitive analog signals. Noise can also couple to the substrate capacitively, a phenomenon known as crosstalk. The noise problem is amplified as operating frequencies increase and feature sizes decrease; being primarily responsible for inexplicable design failure and poor yields of mixed-signal SoC designs [1].

Figure 1.1 Simplified block diagram of a bio-sensor SoC chip.

The work presented in this thesis couples different digital number representations with low precision simple current-mode analog components in a novel way that combines the computational capability of analog circuits and noise immunity of digital components. In essence, we are building digital arithmetic circuits but using analog components to replace uncontrolled digital transitions (produced by the digital processor of Figure 1.1) with smooth analog transitions as illustrated in Figure 1.2. Digital arithmetic is converted into a problem of processing 2-D binary/ternary images and novel CNN structures are designed to manipulate these images to perform the required arithmetic task.

Figure 1.2 Reducing system noise in the bio-sensor with smooth analog transitions.

#### **1.2** Substrate Noise

Digital switching noise is one of the major sources of trouble in a typical mixed-signal VLSI circuit design. When many static gates change state together, they draw a large cumulative current from the power supply. Due to the self-inductance of the off-chip bonding wires and package pins and the on-chip parasitic inductance inherent to the power supply rails, as shown in Figure 1.3, the fast current surges result in voltage fluctuations in the power distribution network [2]. The effective supply voltage on chip is given by the following equation:

$$V_{eff} = V_{DD} - L_{eff} \frac{dI_{V_{DD}}}{dt}$$

(1.1)

The second term on the right hand side of Eqn. (1.1) is referred to as digital switching noise (DSN), simultaneous switching noise (SSN), inductive—Ldi/dt—noise, or  $\Delta I$ . A fraction of this noise is invariably injected into the substrate.

Figure 1.3 Lumped model of the substrate coupling.

The presence of parasitic capacitance between the transistors and the silicon substrate contributes significantly to the problem. When digital circuits switch, they inject current into the substrate via these capacitances. The amount of injected current is directly proportional to the slew rate of the switching voltage and the lumped parasitic capacitance according to Eqn. (1.2); this will be referred to as "cross-talk noise".

$$i_{sub} = C_{eff} \frac{dV_{out}}{dt}$$

(1.2)

Therefore, substrate noise increases as the operating frequency increases. Moreover, the scaling down of feature sizes increases the total capacitance associated with the internal circuitry [3]. With the number of transistors on a chip expected to reach over 600 million by 2009 [4], the amount of injected noise increases dramatically.

The common substrate on which both digital and analog circuits are embedded serves as a resistor network which can be modelled using a simplified form of Maxwell's equations [1]:

$$\frac{1}{\rho}\nabla^2 V(r,t) + \varepsilon \frac{\partial}{\partial t} (\nabla^2 V(r,t)) = -\frac{\partial}{\partial t} q(r,t)$$

(1.3)

Introduction

4

where  $\rho$  is the resistivity and  $\varepsilon$  the permittivity of the uniformly-doped semiconductor. V(r, t) is the transient voltage vector and  $\frac{\partial}{\partial t}q(r, t)$  is the rate of generation of charge per unit volume at location r = (x, y, z) on the substrate. Consequently, voltage variations around the injected points propagate in the substrate and also potential gradients arise due to the resistive nature of the substrate. Assuming a 3-D semi-infinite substrate that goes to infinity in all but one of the six spatial directions, the solution to Eqn. (1.3) in the Laplace domain for the voltage at any point on the substrate,  $V_2$  due to a current,  $i_1$  injected into the substrate a distance r away, is:

$$V_2(s) = \frac{\rho}{2\pi r} \cdot \frac{i_1(s)}{s(\rho \cdot \varepsilon) + 1} \tag{1.4}$$

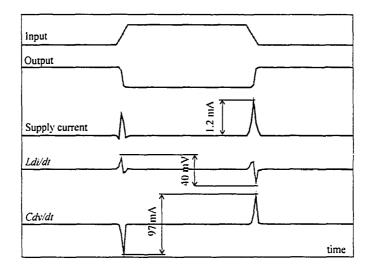

The time variant substrate voltages are sensed by MOSFETs through the body effect and transferred to signal paths in consequence of current fluctuations or gain mismatches in analog circuits. On the other hand, sub-threshold current increase due to the body bias change may degrade digital signal integrity seriously and thus cause dynamic operation failures [5]. On-chip DSN can also create delay uncertainty since the power supply level temporally changes the local drive current [6]. Furthermore, logic malfunctions may be created and excess power may be dissipated due to faulty switching if the power supply fluctuations are sufficiently large [7][8]. Predicting how and when this will happen is a difficult problem, since it is highly dependent on the specific layout and process technology used. Therefore, it is crucial in today's sub 100 nanometer technology to reduce the peak value of dynamic current provided by the supply source  $i_{DD}$ , that is proportional to the carrier injection into the substrate [9]. Moreover, by monitoring the instantaneous power supply current, designers can determine a time window for the worstcase substrate current injection [1]. For example, Figure 1.4 shows the Hspice simulation of a standard digital inverter in 0.35µm CMOS technology during one period of excitation. The simulation also illustrates the instantaneous power supply current drawn by the inverter, digital switching noise, and cross talk noise.

Figure 1.4 Hspice simulation of a standard digital inverter.

The rapidly growing SoC market presents an urgent need for highly effective solutions for the substrate noise problem. Research in this area can be broadly classified into three main categories: Process fabrication techniques, physical design and layout techniques, and innovative digital circuit design techniques.

**Process fabrication techniques:** The goal of process technologists, regarding the noise problem, is to prevent the substrate from working as a noise-coupling path by increasing its resistance, ultimately to infinity. They employ a number of expensive techniques to control the substrate noise problem. One technique employs a deep trench (through-the-wafer) of porous Si (PS) to provide radio frequency (RF) isolation in Si between noise generating and noise sensing circuits [10]. Traditional guard-rings [11][12] have very limited effectiveness in suppressing the underlying substrate noise due to the fact that they are very shallow structures on the wafer surface. However, a Faraday cage consisting of a ring of high-aspect ratio substrate vias encircling noisy or sensitive circuits results in improved performance [13]. A popular technique involves creating a deep N-well structure where active devices are insulated from the substrate by a buried implant layer [12]. Experimental results indicated that an improvement of 25-30dB can be achieved by applying a relatively low-fluence proton bombardment on the isolation-intended region

Introduction

Substrate Noise

[14]. The expensive option based on silicon-on-insulator (SOI) wafers assures full DC isolation; however, it fails to maintain its advantage in the high frequency AC regime [15]. Still another technique is to deploy more costly thin-film silicon-on-insulator (TFSOI) technology where p+ substrate contact rings are used to improve the cross-talk isolation [16][17]. These techniques can help improve the intrinsic noise immunity of SoC devices, but have limited effectiveness at elevated frequencies. Thus, although the use of one or more of these fabrication techniques can reduce substrate noise, process remedies alone are insufficient to ensure a design's immunity to substrate noise coupling [18].

Physical design and layout techniques. Physical design techniques and layout concerning noise immunity primarily aim to reduce the parasitic inductance associated with the power supply network and package pins, minimize the parasitic capacitance between transistors and the substrate, and attenuate noise coupling from one area on a chip to another. It is common practise among analog designers to use separate supplies for digital and analog sections of the chip to isolate the sensitive analog components from noise introduced on the digital supplies [19]. The same technique is useful to isolate different sensitive blocks. Dividing a chip into sections with different substrate grounds will mitigate noise coupling [20]. Researchers have also found that using multiple digital and analog pins can achieve the largest noise reduction. Decreasing the value of the inductance of the bonding wire widens the bottleneck which reduces ground noise [2]. Proper choice of substrate contact geometry and placement plays a major rule in substrate noise distribution [21] and a careful design of power lines geometry and supply network distribution can greatly reduce parasitic inductance [22]. While relative placement of the logic and analog blocks affects the amount of noise coupling [19], analog layout techniques such as mirror symmetry and common-centroid geometries increases noise immunity of analog circuitry [9]. Adding a dedicated backplane substrate contact can substantially drain injected noise [23]. A first and excellent experimental study on the impact of physical design on substrate coupling noise is presented in [24] and a wealth of industry examples to highlight isolation impacts of technology can be found in [25].

Digital design techniques. Regardless of measures taken to minimize noise coupling from digital sections to analog sections on a chip, digital circuitry can still produce significant transient noise. For example, the Ldi/dt noise is estimated to reach 0.35 volt in 0.1 µm CMOS technology with 1.2 volt power supply [26]. This peak noise seriously degrades signal integrity and can easily cause dynamic operation failure. Therefore minimizing on-chip noise is an important element in the effort to improve a design's noise immunity in high performance mixed-signal integrated circuits. Some techniques have been reported that can reduce the effect of DSN. Adding decoupling capacitance can reduce the amount of noise created by supplying local charge for nearby switching and thus lowering the peak current drawn across the package inductance [27]. Building a simple RC filter can leak out DSN with selected frequency roll-off [28]. A negative feedback loop can also be formed by sampling the noise and re-injecting it into the substrate with inverted phase. This inverted noise can reduce the substrate noise for low frequency operations [29]. Using divided switches with current control can also reduce switching noise by controlling the current slope [30]. A number of low-switching-noise digital CMOS families have also been reported: current steering logic [31], folded sourcecoupled logic [32], NMOS current-balanced logic [33], and cellular neural networks [34][35]. However, static power consumption is the main penalty of such structures. Furthermore, some actions at the system level can be taken to minimize switching activities, for instance alternative architectural allocation and scheduling [9], reducing switching activity by pin swapping [36], and the right choice of the clocking scheme [37].

### **1.3** CNN-based Arithmetic Circuits - Rationale

Among all of the above methods, the use of cellular neural networks is quite interesting for several reasons:

- uses analog circuit blocks with inherently lower system noise,

- additional noise reduction due to the asynchronous nature of the CNN arrays,

- noise reduction is independent of the traditional noise reduction methods (e.g., guard rings) and thus can be used in combination with them, and

• the regular structure of the arrays and locality of connections makes it an excellent choice for VLSI implementation.

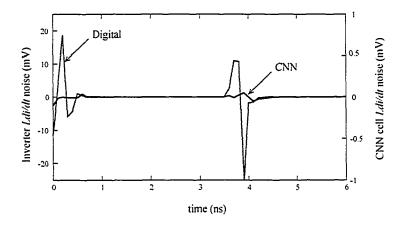

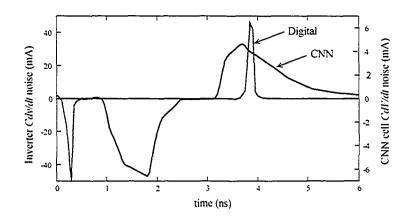

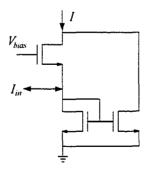

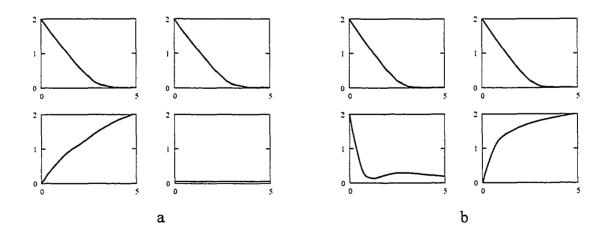

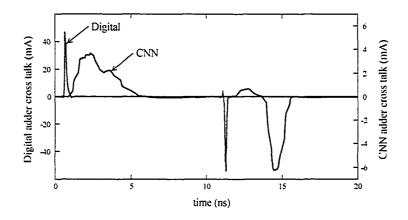

CNN arrays inherently reduce system noise because their current-mode structures operate with almost constant supply current, thus reducing variation in supply current and, hence, switching noise. Moreover, the nodes are built with analog building blocks and effectively provide controlled slewing. In digital logic, by contrast, the output of logic gates switch rapidly between logic states; this switching rate of change being independent of the clock rate of the input logic signals. To illustrate this idea, Hspice simulations of instantaneous values of Ldi/dt and Cdv/dt from a standard CMOS static digital inverter are compared to those from a CNN cell (which can be used as an inverter by forcing its operation in the saturation mode and using the negative output of the cell) in Figure 1.5 and Figure 1.6 respectively. A parasitic inductance of 1nH is used to calculate the DSN while a parasitic capacitance of 2pF is used in Eqn. (1.2). The CNN circuit clearly significantly suppresses the noise in both cases. The advantage of using CNN arrays becomes greater as the circuit size increases.

Figure 1.5 Hspice simulation of di/dt for a digital inverter and a CNN cell.

Figure 1.6 Hspice simulation of dv/dt for a digital inverter and a CNN cell.

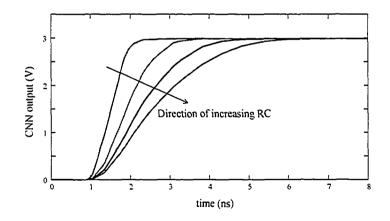

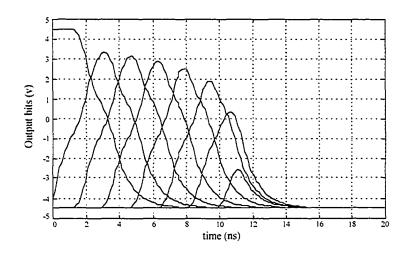

In addition, CNN arrays permit a direct trade off between speed and cross talk (see Section 2.3 for details). By increasing the integration time constant, the slope of the output voltage is decreased and, hence, cross talk. Figure 1.7 shows Hspice simulations of the output voltage of a CNN for different time constants.

Figure 1.7 Hspice simulation of a CNN cell output voltage for different time constants.

### **1.4 Existing CNN-based Arithmetic Circuits**

Two CNN-based binary adders, the flat adder and the recursive adder, were previously introduced in [34] and [35] respectively. In the flat structure, the addition of two *N*-bit binary numbers  $A = a_N a_{N-1} \dots a_2 a_1$  and  $B = b_N b_{N-1} \dots b_2 b_1$  is performed through successive conversion of the given addition operation to another equivalent addition using the rules:

$$c_{i}^{1} = \begin{cases} 0 & i = 1 \\ a_{i-1} \wedge b_{i-1} & 2 \le i \le N+1 \end{cases}$$

(1.5)

$$d_i^1 = \begin{cases} a_i \oplus b_i & N \le i \le 1\\ 0 & i = N+1 \end{cases}$$

(1.6)

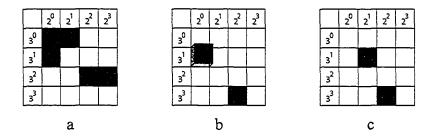

As a result of each conversion step, one digit of the result is obtained and, in the worst case, the complete result is obtained in N + 1 steps. Implementing this algorithm in CNN required assigning a row of N + 1 cells for each original operand. Considering that in the worst case N + 1 steps are needed to complete the addition, the network consisted of 2(N + 1) rows. However, as addition proceeds, more digits of the first operand become zero and more digits of the second operand attain final value. Therefore, cells corresponding to these digits are not required in the CNN implementation. The optimized network structure consists of N(N + 1) cells as shown in Figure 1.8 for the addition of two 4-bit numbers. Two major drawbacks of this design are the huge silicon area required, that increases with  $o(n^2)$ , and consequently large power consumption.

| 1 |   |   |            |    | Co         |

|---|---|---|------------|----|------------|

| 0 |   |   |            |    |            |

| 1 | 0 |   |            |    | S4         |

| 1 | 0 |   |            |    |            |

| 0 | 0 | 0 |            |    | S3         |

| 0 | 1 | 0 |            |    |            |

| 0 | 1 | 0 | 0          |    | S2         |

| 0 | 0 | 1 | 0          |    |            |

|   | 1 | 1 | 0          | 1  | <b>S</b> 1 |

|   | ा | 0 | 1,         | E. | Α          |

|   | 0 | 1 | <b>1</b> 0 | 0  | В          |

Figure 1.8 The flat binary adder.

To save on silicon area, the author implemented a recursive adder in [35] that requires four rows of N + 1 cells. In this structure, the information is allowed to flow from the first two rows back to the last two rows. Unlike the flat structure which performs quite robustly for a wide range of template values, this parameter here should be chosen carefully to avoid divergence due to a potential race problem. The structure also lacks speed and stability due to the recursive operation as shown in the simulation of Figure 1.9. As addition proceeds, the height of the generated carries gradually falls. This indicates that the adder will eventually diverge from correct sum outputs for large operands. To alleviate this problem, the author suggested applying a positive velocity vector across the array from the LSB to the MSB. This was implemented by decreasing the value of the self-feedback factor  $\alpha$  by 0.05 per bit position. This fine-tuning method can work with MATLAB simulation as variables can be decremented virtually by any small value. However, its realization is almost impossible because the analog designer is restricted by the physical constraints imposed by the technology being used.

Figure 1.9 MATLAB simulation of the recursive binary adder.

Our research work builds on the previous work introduced in [34] and [35] by providing a novel systematic paradigm for implementing digital arithmetic circuits using analog CNN. The design methodology presented in the following chapters takes into consideration the pitfalls of the previous designs and ensures convergence of the network while optimizes its speed, silicon area, and power consumption.

### **1.5** CNN-based Arithmetic Circuits Design Goals

There are three major design goals that need to be fulfilled for a practical and successful design of a CNN-based arithmetic circuit: Convergence, scalability, and compatibility. The first design goal corresponds to the continuous output feedback nature of the CNN while the other two design goals come from the wide spectrum of applications using arithmetic circuits and a wealth of arithmetic circuit designs available in the literature.

1. Convergence: This requirement ensures that the developed CNN-based arithmetic circuits, after transient time, will always approach one of the stable equilibrium points, as will be discussed in Section 2.4.2.

- 2. Scalability: Precision required for arithmetic circuits varies by function. Consider multiplication as an example. At the low end, 8 bit words are used, as is the case in image compression algorithms, or 16 bits in more precise DSP tasks. At the high end, the word lengths in the IEEE double precision floating point standard are 53 bit and 64 bit. The scalability requirement ensures that arithmetic circuits with arbitrary sizes can be developed to meet the needs of specific applications.

- 3. Compatibility: The enormous collection of arithmetic circuit designs available in the literature places a stringent demand on new designs to provide backward compatibility. Instead of re-inventing the wheel, this requirement guarantees that the developed CNN-based arithmetic circuits can be used as embedded components in existing, more complex circuit structures without the need to re-design the whole circuit.

#### **1.6 Thesis Overview**

This research work explores the implementation of arithmetic circuits using arrays of analog circuits and the CNN computing paradigm, and also addresses mixed-signal applications where the presence of digital switching noise is a major problem. We thus describe a general technique for building low-noise digital arithmetic circuits using analog cellular neural networks, essentially implementing asynchronous digital logic with analog circuits. Each node in our asynchronous architectures uses controlled current sources driving into capacitors; providing both low current and voltage time derivatives ( $\delta i / \delta t$ and  $\delta v / \delta t$ ) and, as a result, reducing both instantaneous and time-averaged system and cross talk noise. In our approach, nonlinear templates are employed to perform the required arithmetic task without decomposing the arithmetic operation into primitive linear templates. Utilizing nonlinear templates facilitates performing medium complexity arithmetic operations with three major advantages. 1) Considerable reduction in processing time; since the arithmetic task is performed using one nonlinear template, the time needed to load/unload different templates with their inputs and initial conditions is eliminated. 2) Simplification of the circuit; this is because the control logic traditionally required to control template operations is no longer needed. 3) Decrease in power consumption; this result comes straightforwardly from the fact that power consumption is directly related to processing time. Therefore, reducing processing time translates into lower power consumption. Moreover, removing the control logic from the circuit structure reduces power consumption further by the amount needed by the control logic.

To demonstrate the effectiveness of our methodology, we have designed and simulated CNN arrays for arithmetic operations using binary, binary signed-digit, and double-base number systems. First, we re-defined the arithmetic task in the given number system using continuous functions which are mapped into nonlinear templates. We then designed and simulated a CMOS circuit implementation of the arithmetic operation. We have demonstrated that the designed structures, regardless of the number system being used, are quite modular which enables the accurate evaluation of the performance of larger networks. We have also presented other novel contributions including the introduction of a new class of CNN featuring a 3-state transfer characteristics and an innovative self-programmable array using a novel feedback connection between groups of cells. Finally, we have analyzed the performance of the designed circuits in terms of power consumption, delay, and area. We have finally illustrated the efficiency of our designs to suppress noise by comparing them to standard digital implementations.

#### **1.7 Thesis Organization**

The thesis is organized as follows. Chapter 2 provides the basic theory of CNN arrays required to understand the work presented in subsequent chapters. Chapter 3 to Chapter 5 introduce general procedures to develop arithmetic circuits for the three number systems described in Section 1.6. Each chapter analyzes the corresponding arithmetic operations, defines the required templates, and provides Hspice simulations to demonstrate convergence of the designed circuits. We also present the designs of multi-bit adders and multipliers to illustrate the scalability and compatibility of each algorithm in more useful arithmetic tasks. Each chapter also examines the impact of the corresponding design on system noise using extensive Hspice simulations. Finally, Chapter 6 summarizes the work and provides a detailed comparison of the performance of each design in terms of noise, area, delay, and power consumption. Chapter 6 also presents the final conclusions.

# Chapter 2

Cellular Neural Networks: An Overview

Cellular Neural Network (CNN) arrays represent a massively parallel asynchronous computing paradigm that is a hybrid of Cellular Automata (CA) and Artificial Neural Networks (ANNs). CNN arrays take advantage of both worlds: their local connectedness makes the arrays well suited for VLSI implementation, and, similar to ANNs, they provide a natural parallel processing paradigm. The CNN regular grid-like structure also makes it a good candidate for online solutions of systems of first order non-linear differential equations. CNNs represent an analog nonlinear dynamic system operating in continuous or discrete time. When considered as a system, a CNN is characterized by the fact that information is directly exchanged just between neighboring neurons. Of course, this characteristic does not prevent the capability of obtaining global processing. Cells that are not in the immediate neighborhood have an indirect effect because of the propagation effects of the dynamics of the network. By exploiting locality of connections, electronic IC and optical or electro-optical implementations become feasible, even for large nets, which is the main advantage of CNNs over ANNs. Since the research work presented in this thesis is built on CNN arrays, the purpose of this chapter is to acquaint the reader with basic CNN theory needed for subsequent chapters. A brief history of CNNs and the scope of applications is given in Section 2.1. The spatial layout and restrictions on connections between neighboring cells are described in Section 2.2. In Section 2.3, mathematical equations defining the behavior of a CNN cell are reviewed and a general circuit architecture of a CNN is given. The dynamics of CNNs is discussed in Section 2.4, and modes of operation and notes on CNN stability are also presented.

## 2.1 CNN History and Applications

Since their introduction in 1988 by Chua and Yang [38][39], Cellular Neural Networks have attracted considerable attention. They are well suited for image processing applications, because of their two-dimensional structure and local interconnections, which are typical characteristics of many image processing algorithms [40]-[42]. Enormous advances have been made by many researchers in this field [43]. While software prototypes prove the potential of CNN [44]-[46], a great deal of research has also been reported in hardware implementations which can be used for real-time applications. These implementations include transconductance-mode based processing elements [47], switched-current signal processing elements [48], discrete-time implementations [49][50], current-mode implementation [50][51] and more [52]-[54]. The first CNN realizations were designed to perform one specific function in image processing or classification, such as edge detection [40], connected component detection [55], noise removal [39], or hole filling [56]. More complex image processing functions are also reported including image and video compression [57]-[60], image rotation [61]-[62], nonlinear image filtering [63]-[66], image enhancement [67]-[69], image restoration and reconstruction [70]-[72], image segmentation [73]-[75], pattern matching and classification [76]-[78], and character/face recognition [79]-[81]. CNN arrays have also been applied to a wide variety of important tasks in robot navigation [82]-[84], motion detection and estimation [85]-[88], defect inspection [89]-[92], satellite communication and secure transmission systems [93]-[97], analysis of brain electrical activity in epilepsy [98]-[100], cryptography [101], bionic eyeglasses [102]-[103], and solving partial differential equations and optimization problems [104]-[107], just to mention a few. More recently, researchers investigated programmable CNNs to provide flexibility in implementing analog parallel array

processors [53],[108]. In other work, the slope and the threshold of the activation function has also been made tunable [109]-[110]. Because of the thresholded activation function at the output of the CNN structure, many image processing applications have traditionally been based on black and white images even though CNN arrays, by their nature, are analog, continuous processing systems. However, grey/color based applications have recently started to emerge [61], [66], [111]-[113]. From a hardware point of view, the local connectivity of the CNN array lends itself to practical VLSI implementations. The addition of logic functions results in a programmable analog/logic array computer capable of performing algorithms that combine the strengths of analog template processing and logic operations [41],[114]. In fact, CNN arrays sets the platform for a new algorithmic style based on the spatio-temporal properties of the array. The key elementary instruction is a spatio-temporal transient generated by a two dimensional nonlinear dynamic processor array. This basic instruction resembles the typical convolutional operator used in image processing applications.

## 2.2 CNN Structures

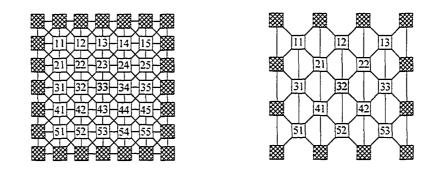

The CNN is intrinsically defined spatially; generally only 1- or 2-dimensional space is considered, so that the CNN can be realized physically. The most common types of CNN can be characterized as a 2-D planar array of dynamic cells (neurons) with rectangular, triangular or hexagonal geometry. Any cell on the  $i^{th}$  row and  $j^{th}$  column, C(i,j), is connected only to cells within a small neighborhood, denoted as N(i,j). For hardware implementations, and due to the wiring complexity involved, most often neighborhoods are of radius 1; although, for software simulations, a radius of 3 or more has been reported. As an example, Figure 2.1 shows two different CNN grids with a neighborhood of radius 1. Note that in this figure, each cell in the rectangular grid is connected to the inputs and outputs of 9 cells, including to itself, while cells in the hexagonal grid are connected to the inputs and outputs of 7 cells for the same radius.

Figure 2.1 Examples of rectangular and hexagonal CNN grids with neighborhood of size 1. Light grey cells belong to the neighborhood of the dark grey cell.

In a CNN, cells may be all identical or they can belong to a few different types as is the case for biological neurons. The interconnection strengths or connection weights are usually spatially invariant. However, more than one connection network may also be present, with a different neighborhood size to permit short range interactions and subsystem connections. To ensure that the cells on the perimeter of the CNN grid achieve proper convergence, dummy border cells (hatched cells in Figure 2.1) are added on the border of the processing array to simulate interaction with imaginary cells outside the CNN grid. The size of the dummy border depends on the neighborhood radius. For example, for a rectangular array with a neighborhood of radius 1, the width of the dummy border would be 1 cell as depicted in Figure 2.1. A dummy cell outputs a constant voltage that a properly converged computing cell would produce if it were in its place. A dummy cell would also receive an input signal voltage as if it were a member of the array. Therefore, a cell on the perimeter of the CNN array uses the input signal voltage and dynamic output voltage of neighboring cells as well as the static output and signal voltages of the dummy cells to arrive at the proper final state. The border cells are treated as members of the array for initialization purposes and template implementation, but are not considered in the final state analysis.

All cells in the CNN operate in parallel and when one computing cell is allocated to each pixel in the 2D input signal, the CNN achieves very high signal processing speeds. Although the cells are only locally connected, the network is able to perform global

operations on the 2-D inputs. This is possible because the missing global connections are replaced by a time-multiplexing of the connections and the time-propagation of the information through the network from cell to cell.

### 2.3 CNN Cell Architecture

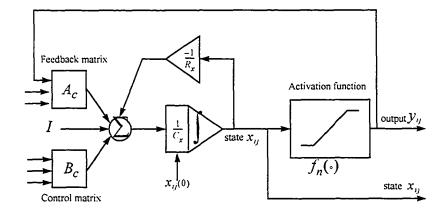

CNN cells are multiple input - single output nonlinear processors that consist of linear and nonlinear circuit elements. Each cell is characterized by an internal state variable  $x_{ij}$ , that is bounded for all time t > 0. Every cell also has a constant external input  $u_{ij}$  and output  $y_{ij}$ . The evolution and dynamics of the state of cell *ij* is described by the first order nonlinear differential equation:

$$C_{x}\dot{x}_{ij}(t) = -\frac{1}{R_{x}}x_{ij}(t) + \sum_{c \in N_{ij}}A_{c} \cdot y_{c}(t) + \sum_{c \in N_{ij}}B_{c} \cdot u_{c}(t) + I$$

(2.1)

and output function:

$$y_{ij}(t) = \frac{1}{2}(|x_{ij}(t) + 1| - |x_{ij}(t) - 1|)$$

(2.2)

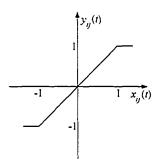

where I is a local value called the bias, and  $N_{ij}$  is the r-neighborhood of the cell C(i,j) which contains all cells within a radius r. The output nonlinearity  $f(x_{ij})$  is a piecewise linear function; f is linear in the unit range [-1,1], and outside the unit range the output saturates to +1 for positive state values and to -1 for negative state values, as shown in Figure 2.2.  $A_c$  and  $B_c$  are two generic parametric functionals. The  $A_c$  template connections represents the inter-cell connection weights and provides an output feedback mechanism. The  $B_c$  template connections in turn represents connections to the input and serves as an input control mechanism. Specific entry values of the bias term and the feedback and control templates are application dependent and, most often, are identical for all cells (so called cloning templates). The constant bias, I, and the cloning templates determine the transient behavior of the cellular nonlinear network.

Cellular Neural Networks: An Overview

20

Figure 2.2 CNN cell activation function.

The solution to this system of equations is the classical exponential function of a first order system. The maximum convergence rate of a cell is determined by the integration time constant  $C_x R_x$ . Therefore the speed of the CNN array can be controlled by adjusting this value. This property is crucial in controlling the cross talk (see Section 1.3).

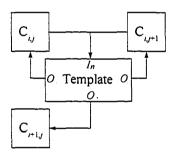

In Figure 2.3, a block diagram that implements Eqn. (2.1) is represented. The cell sums the incoming signal from the neighbors, itself, and the constant bias of the *I* template and integrates them to compute its internal state. The cell also sends two signals to each of its neighbors: one signal is its output multiplied by a weight from the  $A_c$  template; the second signal is its input multiplied by a weight from the  $B_c$  template.

Figure 2.3 A block diagram representation of a CNN cell.