# University of Windsor

# Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

1981

# PROCESSOR ARCHITECTURES FOR FAST COMPUTATION OF MULTI-DIMENSIONAL UNITARY TRANSFORMS.

HARI K. NAGPAL University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

## **Recommended Citation**

NAGPAL, HARI K., "PROCESSOR ARCHITECTURES FOR FAST COMPUTATION OF MULTI-DIMENSIONAL UNITARY TRANSFORMS." (1981). *Electronic Theses and Dissertations*. 3199. https://scholar.uwindsor.ca/etd/3199

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

National Library of Canada Collections Development Branch

Cahadian Theses on Microfiche Service Bibliothèque nationale du Canada Direction du développement des collections

Service des thèses canadiennes sur microfiche

NOTICE

**AVIS**

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us a poor photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30. Please read the authorization forms which accompany this thesis.

THIS DISSERTATION

HAS BEEN MICROFILMED

EXACTLY AS RECEIVED

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

, S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de mauvaise qualité.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30. Veuillez prendre connaissance des formules d'autorisation qui accompagnent cette thèse.

LA THÈSE A ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS RECUE

Ţ

PROCESSOR ARCHITECTURES FOR FAST

COMPUTATION OF MULTI-DIMENSIONAL

UNITARY TRANSFORMS

• ъу

A Dissertation

Submitted to the Faculty of Graduate Studies

through the Department of Electrical Engineering

in partial fulfillment of the requirements

for the Degree of Doctor of Philosophy at the

University of Windsor

Windsor, Ontario, Canada

## ABSTRACT

This work presents the development of new algorithms and special purpose sequential processor architectures for the computation of a class of one-, two- and multi-dimensional unitary transforms.

In particular, a technique is presented) to factorize the transformation matrices of a class of multi-dimensional unitary transforms, having separable kernels, into products of sparse matrices. These sparse matrices consist of Kronecker products of factors of the one-dimensional transformation matrix. Such factorizations result in fast algorithms for the computation of a variety of multi-dimensional unitary transforms including Fourier, Walsh-Hadamard and generalized Walsh transforms. It is shown that the u-dimensional Fourier and generalized Walsh transforms can be implemented with a u-dimensional radix-r butterfly operation requiring considerably fewer complex multiplications than the conventional implementation using a one-dimensional radix-r butterfly operation.

Residue number principles and techniques are applied to develop novel special purpose sequential processor architectures for the computation of one-dimensional discrete Fourier and Walsh-Hadamard transforms and convolutions in real-time. The residue number system (RNS) based implementations yield a significant improvement in processing speed over the conventional realizations

using the binary number system.

As an illustration of the factorization techniques developed in this work, novel sequential architectures of RNS-based fast Fourier, Walsh-Hadamard and generalized Walsh transform processors for real-time processing of two-dimensional signals are presented. These sequential processor architectures are capable of processing large bandwidth (> 5 M.Hz) input sequences.

The application of the proposed FFT processors for the realtime computation of two-dimensional convolutions is also investigated.

A special memory structure to support two-dimensional convolution operations is presented and it is shown that the two-dimensional FFT processor architecture proposed in this work requires less hardware than the conventional implementations. The FFT algorithms and processor architectures are verified by computer simulation.

## ACKNOWLEDGEMENTS

I would like to express my sincere thanks and appreciation to my supervisors, Dr. J.J. Soltis and Dr. G.A. Jullien, for their invaluable advice, help and constant encouragement throughout the progress of this research. The valuable advice of Dr. W.C. Miller and other faculty members is gratefully acknowledged. In addition, the help of many of the graduate students and Mr. J. Novasad is sincerely appreciated.

To my parents and brothers, I extend my sincerest thanks and gratitude. Without their help and inspiration, this work would not nave started.

Thanks are also due to Mrs. Marion Campeau for her diligence in typing this thesis.

# TABLE OF CONTENTS

|                       |                                                                 | Page |

|-----------------------|-----------------------------------------------------------------|------|

| ABSTRACT              |                                                                 | (I)  |

| ACKNOWLEDGEMENTS      |                                                                 | (iii |

| TABLE OF CONTENTS     |                                                                 | (iv) |

| LIST OF FIGURES       |                                                                 | (vii |

| LIST OF SYMBOLS       |                                                                 | (1x) |

| LIST OF APPENDICES    |                                                                 | (xiv |

| CHAPTER 1 <u>INTR</u> | ODUCTION .                                                      | ` 1  |

| 1.1                   | Unitary Transform Implementation                                | 4    |

| 1.2                   | Objective and Outline of the Research                           | 11   |

| 1.3                   | Thesis Organization                                             | 13   |

| CHAPTER 2 ONE         | DIMENSIONAL UNITARY TRANSFORM ALGORITHMS                        | 15   |

| 2.1                   | Introduction                                                    | 15   |

| . 2.2                 | One-Dimensional Unitary Transforms                              | 16   |

| 2.3                   | One-Dimensional Discrete Fourier Transform Implementation       | 19   |

|                       | 2.3.1 One-Dimensional OIOO FFT Algorithm and its Implementation | . 24 |

| 2.4                   | One-Dimensional Walsh-Hadamard Transform and its Implementation | 32   |

|                       | 2.4.1 Dyadic-Ordered Fast WHT Algorithm and its Implementation  | 33   |

| 2.5                   | Residue Number System                                           | 37   |

| •                     | 2.5.1 Residue Number System Concepts                            | 38   |

| 2.6                   | Summary                                                         | 44   |

| CHAPTÉR 3 | RESIDUE NUMBER SYSTEM BASED ONE-DIMENSIONAL                                       | 45  |

|-----------|-----------------------------------------------------------------------------------|-----|

|           | PROCESSOR ARCHITECTURES                                                           |     |

|           | 3.1 Introduction                                                                  | 45  |

| <b>.</b>  | 3.2 An RNS-Based Butterfly Unit's Architecture                                    | 46  |

|           | 3.3 A One-Dimensional RNS-Based FFT Processor Architecture                        | 54  |

|           | 3.3.1 System Organization of a RNS-Based FFT Processor                            | 58  |

| •         | 3.4 Processor Organization to Obtain the DFT of Smaller Sequences                 | 62  |

|           | 3.5 Processor Organization to Compute 1-D Convolutions of Real-Valued Sequences   | 69  |

| <i>;</i>  | 3.6 A One-Dimensional Walsh-Hadamard Transform Processor Architecture             | 75  |

| •         | 3.7 Summary                                                                       | 78  |

|           |                                                                                   |     |

| CHAPTER 4 | MULTI-DIMENSIONAL ALGORITHMS AND PROCESSOR                                        | 80  |

| · · ·     | ARCHITECTURES FOR COMPUTING A CLASS OF UNITARY                                    |     |

|           | TRANSFORMS                                                                        |     |

| i         | 4.1 Introduction                                                                  | 80  |

|           | 4.2 Multi-Dimensional Unitary Transforms                                          | 81  |

|           | 4.2.1 Multi-Dimensional Unitary Transform Algorithms                              | 86  |

|           | 4.2.2 Multi-Dimensional Discrete Fourier Transform                                | 90  |

|           | .4.2.3 Two-Dimensional FFT Processor<br>Organization                              | 96  |

| •         | 4.2.4 RNS-Based 2-D FFT Processor Organization                                    | 107 |

| ·         | 4.2.5 Multi-Dimensional Generalized Walsh and Walsh-Hadamard Transform Algorithms | 110 |

|           | 4.2.6 Other Multi-Dimensional Unitary Transform Algorithms                        | 115 |

|           | 4.3 Summary                                                                       | 116 |

|     | CHAPTER   | 5           | HIGH | SPEED CONVOLUTION                                     | ,      | \ <del>1</del> 18 |

|-----|-----------|-------------|------|-------------------------------------------------------|--------|-------------------|

|     |           | •           | 5.1  | Introduction                                          | 4      | ง<br>_ 118        |

| •   |           |             | 5.2  | Two-Dimensional Convolution Using a 2-D FFT Processor | (      | 119               |

|     | •         |             | 5.3  | 2-D Convolution Using 1-D FFT Processor               | $\sim$ | 131               |

|     | •         | -           | 5.4  | 2-D Convolution Using NTTs                            | ۸~     | 138               |

|     | •         |             | 5.5  | Summery                                               |        | .140              |

|     |           |             |      |                                                       |        |                   |

| •   | · >-      | `           |      | •                                                     | . •    | •                 |

|     | CHAPTER   | <b>)</b> 6: | HARD | WARE REQUIREMENT AND SIMULATION OF THE                |        | 142               |

| •   |           | r           | FFT  | PROCESSOR DESIGNS                                     |        |                   |

|     | •         |             | 6.1  | Introduction                                          |        | 142               |

|     |           |             | 6.2  | Hardware Requirements                                 | • •    | 143               |

|     | •         |             | 6.3  | Simulation of the FFT Processor Designs               |        | 147               |

| `   | •         |             | 6.4  | Summary                                               |        | 154               |

|     |           |             |      |                                                       |        | •                 |

|     | •         |             | •    |                                                       |        |                   |

|     | CHAPTER   | 7           | CONC | LUSIONS                                               | •      | 157               |

|     | ·         |             |      |                                                       | c      | •                 |

| RE  | FERENCES  |             |      |                                                       | •      | 161               |

|     |           |             |      |                                                       |        |                   |

| .AP | PENDICES  | •           |      |                                                       |        | 166               |

|     |           |             |      | _ 🖈                                                   |        |                   |

| VI  | TA AUCTOR | IS          |      |                                                       |        | 181               |

# LIST OF FIGURES

| Figure      |                                                                                                                      | Page |

|-------------|----------------------------------------------------------------------------------------------------------------------|------|

| 2.1         | (8x8) Transformation Matrices of (a) DFT (b) WHT (c) HT                                                              | : 20 |

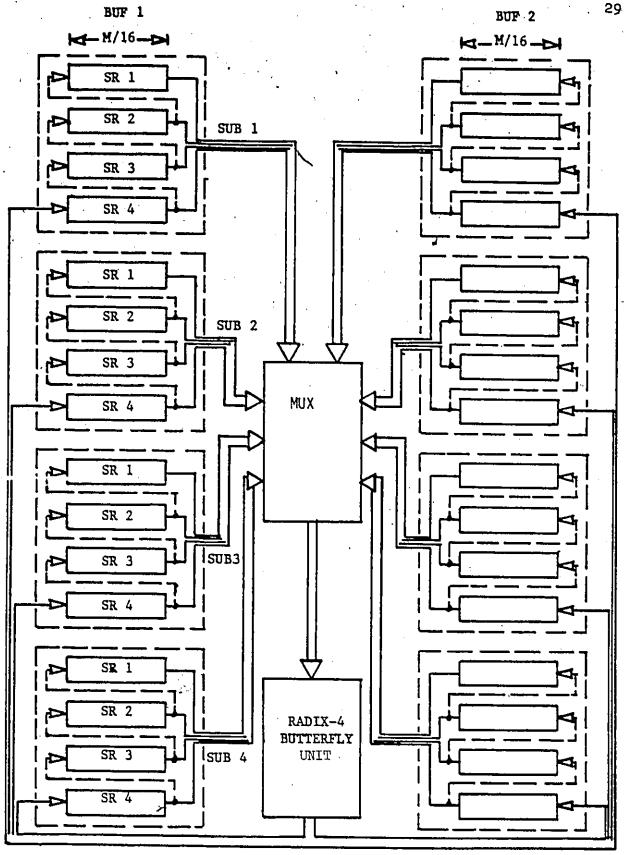

| 2.2         | Memory Organization of the 1-D FFT Processor                                                                         | 29   |

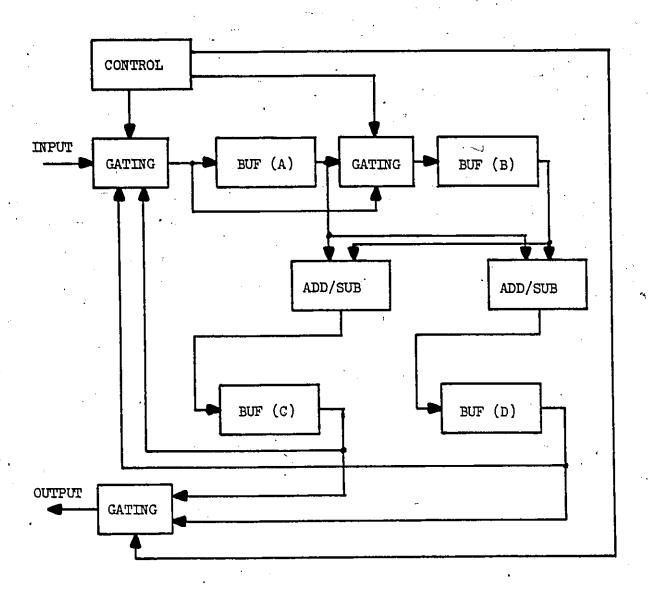

| 2.3         | A Sequential WHT Processor                                                                                           | 36   |

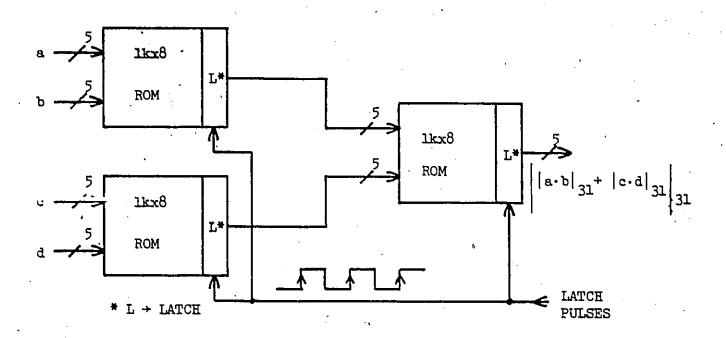

| 2.4         | A Pipelined ROM Array                                                                                                | 142  |

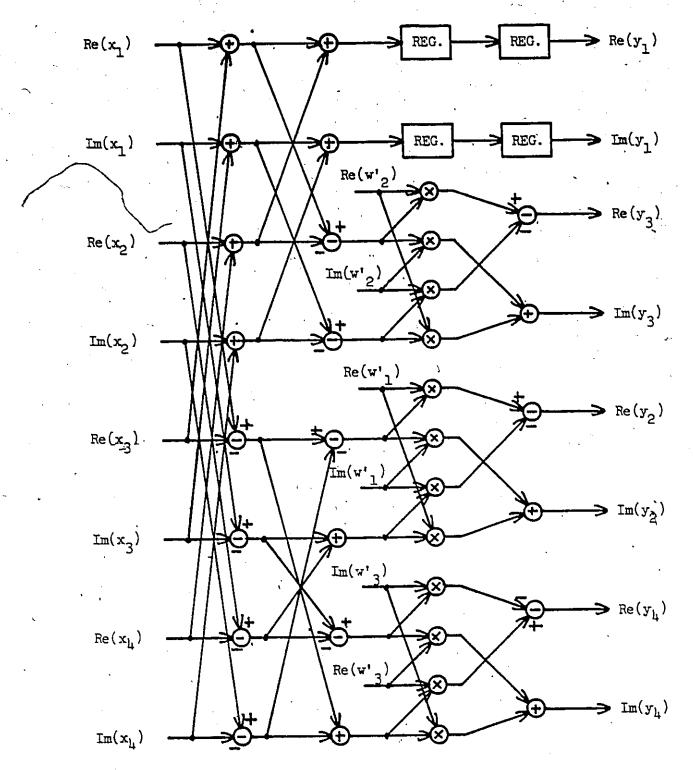

| 3.1         | A Simplified Block Diagram of a RNS-Based Butterfly Unit for the Modulus m                                           | 49   |

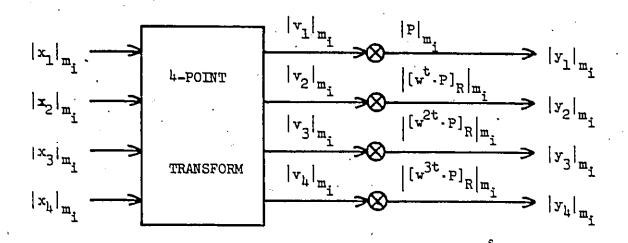

| 3.2         | A ROM Implementation of the Radix-4 Butterfly Unit for the Modulus m;                                                | 50   |

| 3.3         | Original Scaling Algorithm for N = 6 and s = 3                                                                       | 53   |

| 3.4         | ROMs Storing the Twiddle Factors for a Radix-4 FFT Processor                                                         | 55   |

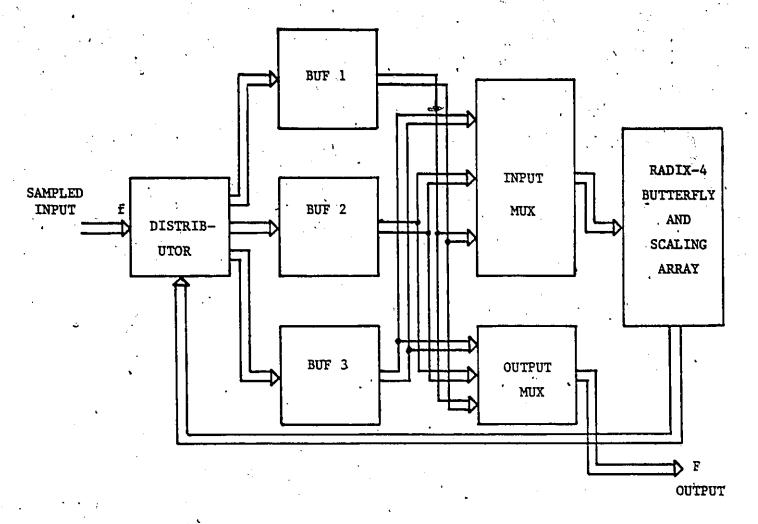

| 3.5(a)      | Organization of a RNS-based 1-D FFT Processor                                                                        | 57   |

| (b)         | Interconnections of SUBs of BUF1 to Form Shift-Register of Size N                                                    | 57   |

| 3.6         | Buffer Allocation for Real-Time Computation of a Transform When the Number of Stages in the FFT are (a) even (b) odd | · 59 |

| <b>3.</b> 7 | System Organization of a RNS-Based 1-D Radix-4 FFT Processor                                                         | . 60 |

| 3.8         | FFT Processor Configuration for Processing Smaller Sequences                                                         | 68   |

| 3.9         | Input Buffer Configuration for Smaller Sequences                                                                     | 68   |

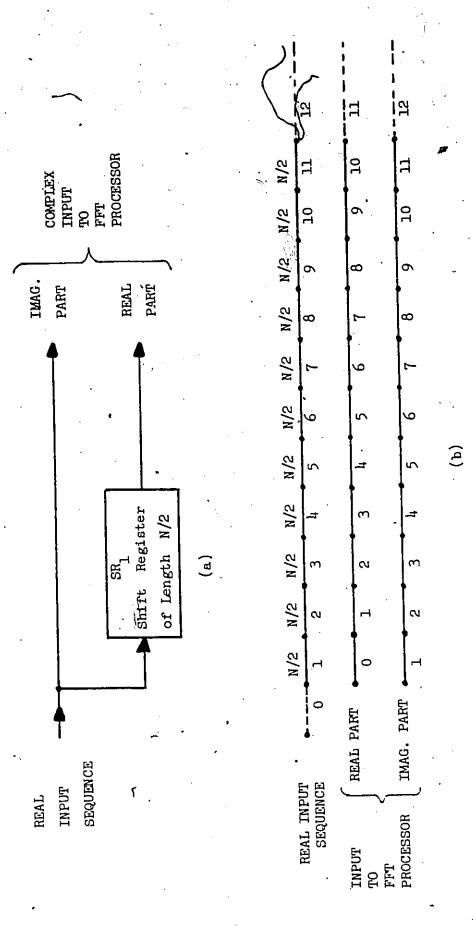

| 3.10(a)     | Generation of Complex Input to FFT Processor                                                                         | . 72 |

| (b)         | Timing Diagram                                                                                                       | 72   |

| figure        |                                                                                                                                                     | Page  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|

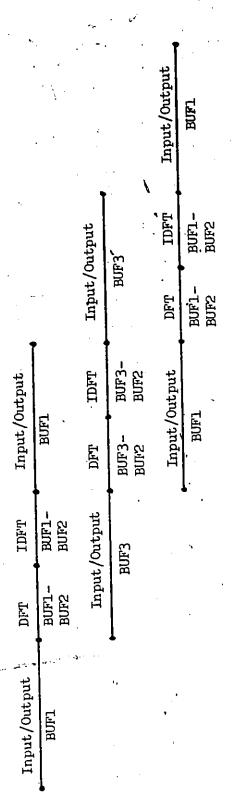

| 3.11          | FFT Processor Buffer Allocation for Sectioned Convolutions                                                                                          | 74 =  |

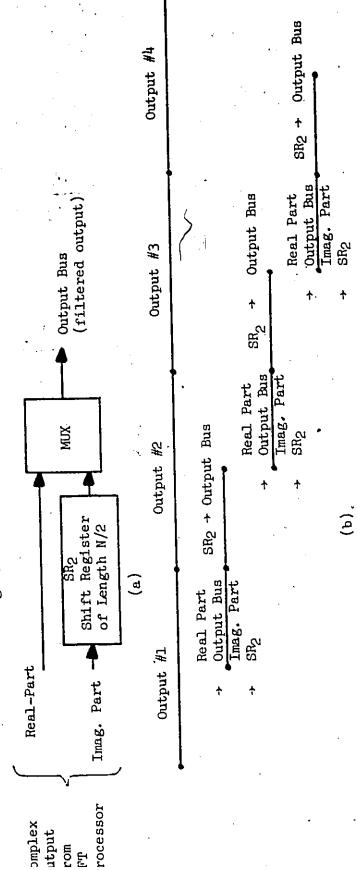

| 3.12(a)       | Generation of Real-Output Sequence from the Complex FFT Processor Output                                                                            | 74    |

| ' <b>(</b> b) | Timing Diagram                                                                                                                                      | 74    |

| 4.1           | A 2-D Sequence                                                                                                                                      | 93    |

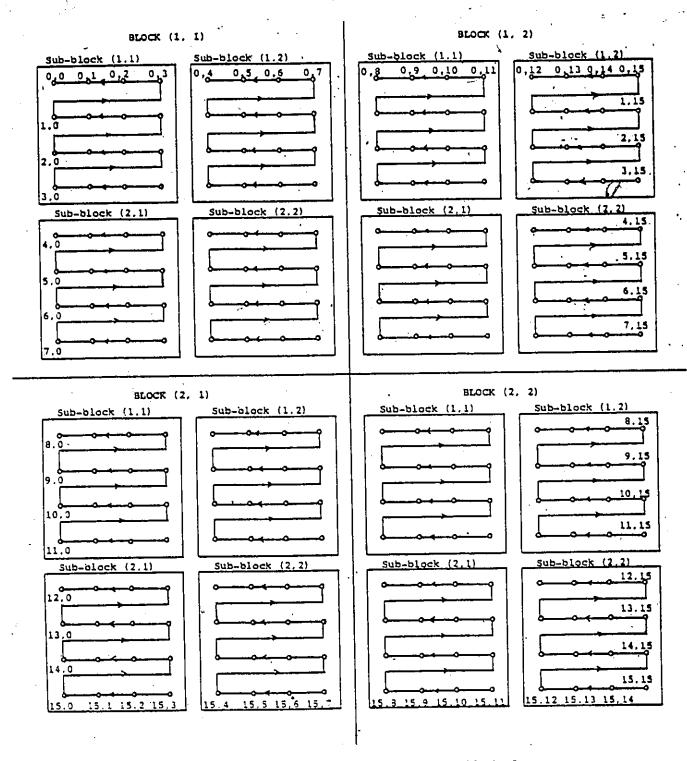

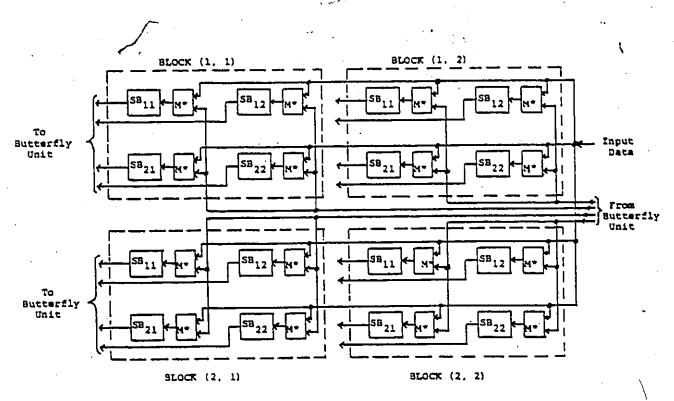

| 4.2           | Partitioning of (16x16) Array into Sub-Blocks                                                                                                       | . 97  |

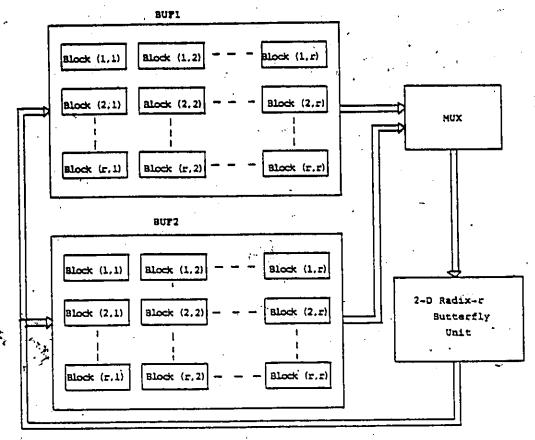

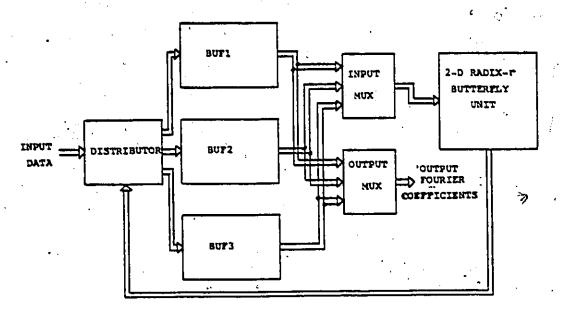

| 4.3(a)        | 2-D Radix-r Processor Organization                                                                                                                  | 99    |

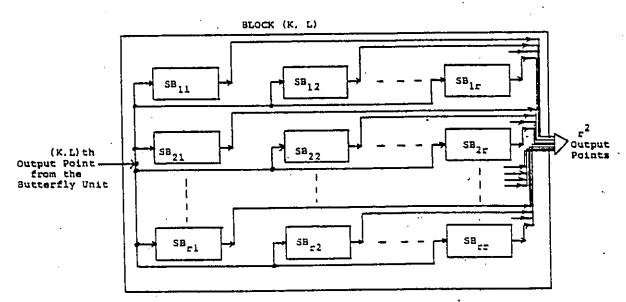

| (b) ·         | Sub-Division of a Block into Sub-Blocks                                                                                                             | 99    |

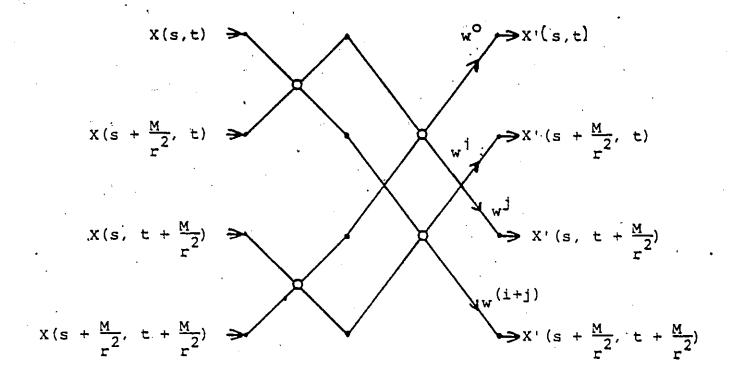

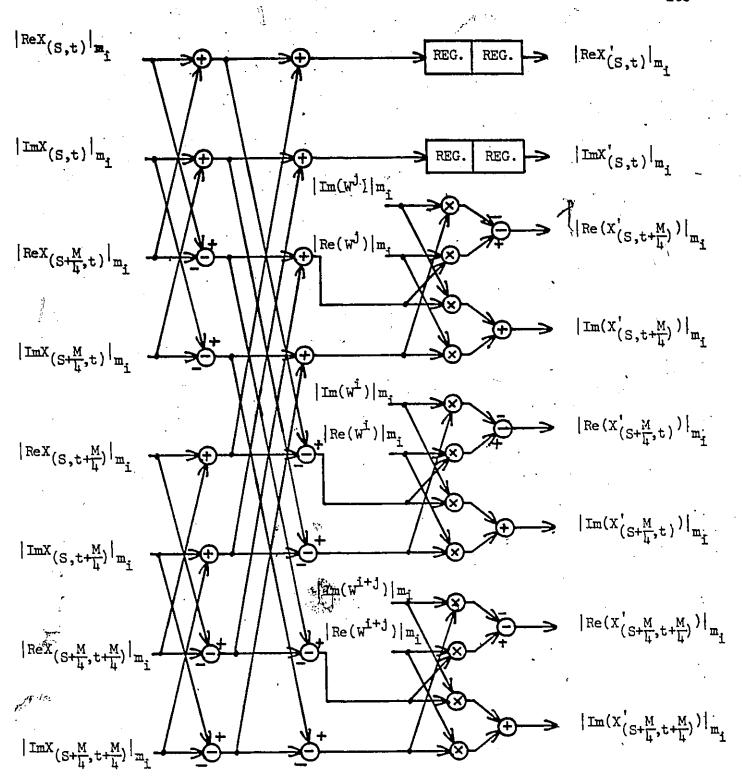

| 4.4           | A 2-D Radix-2 Butterfly Operation                                                                                                                   | 103   |

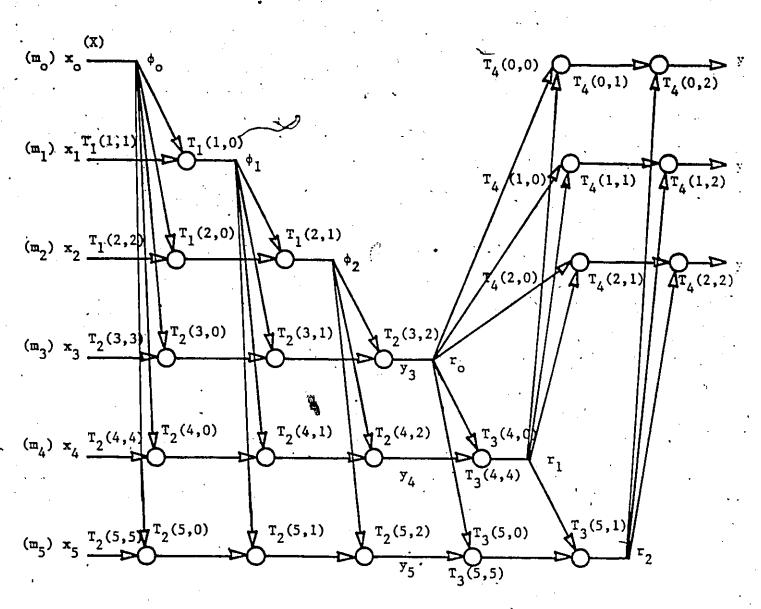

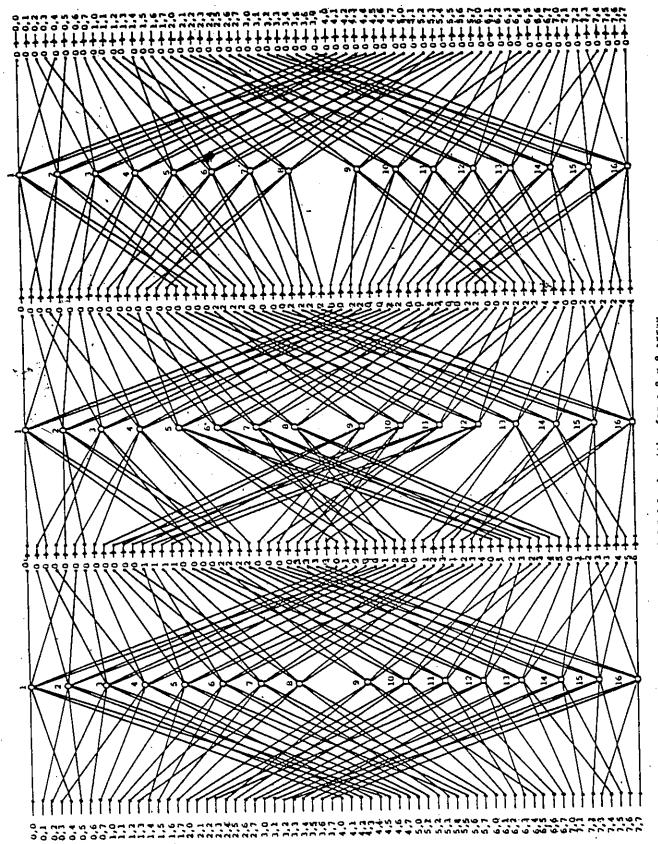

| 4.5           | Flow Graph of 2-D Radix-2 0100 Algorithm for a (8x8) Array                                                                                          | 105   |

| 4.6(a)        | FFT Processor Organization for Real-Time I/O                                                                                                        | 106   |

| (p)           | A Real-Time Buffer Organization for a 2-D Radix-2;<br>FFT Processor                                                                                 | 106   |

| 4.7           | A RNS-Based 2-D Radix-2 Butterfly Structure                                                                                                         | 108   |

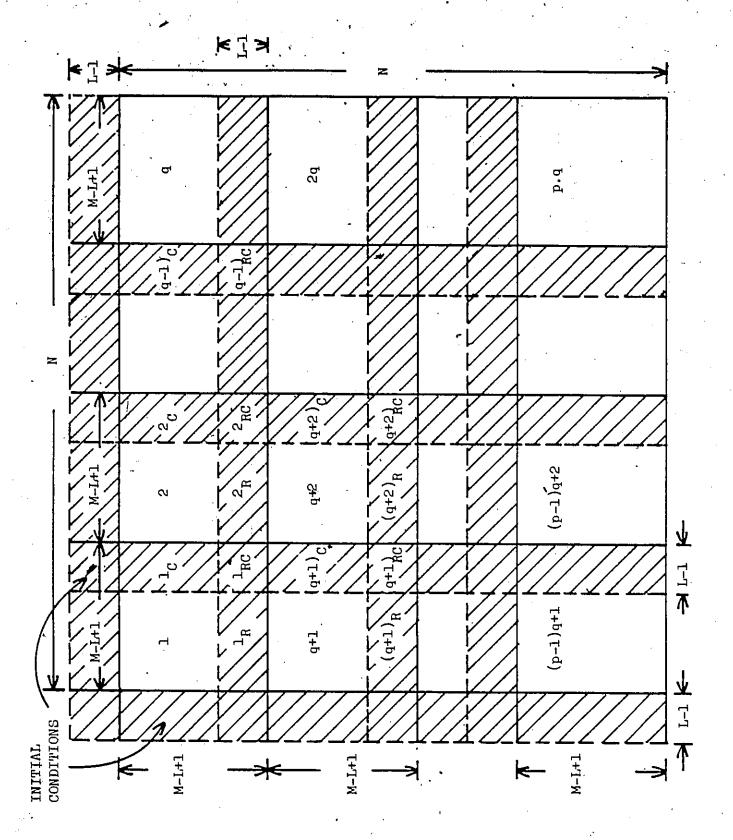

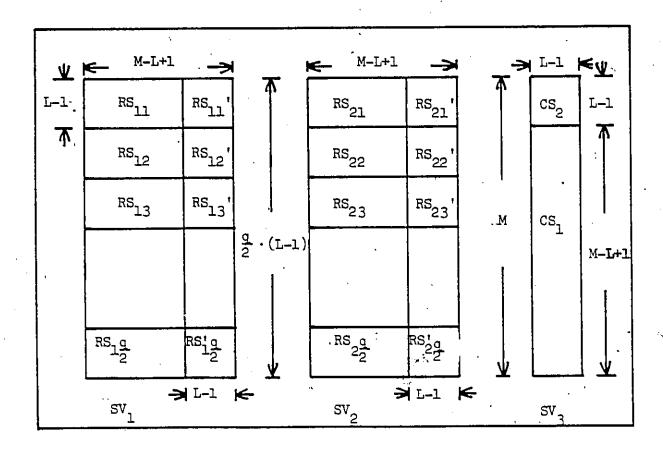

| 5.1           | Sections of an (NxN) Matrix                                                                                                                         | 122   |

| 5.2(a)        | Input Data Memory Sections                                                                                                                          | 123   |

| (b)           | Save Memory Sections                                                                                                                                | 123   |

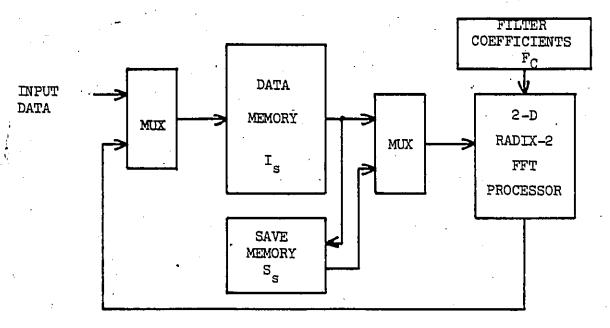

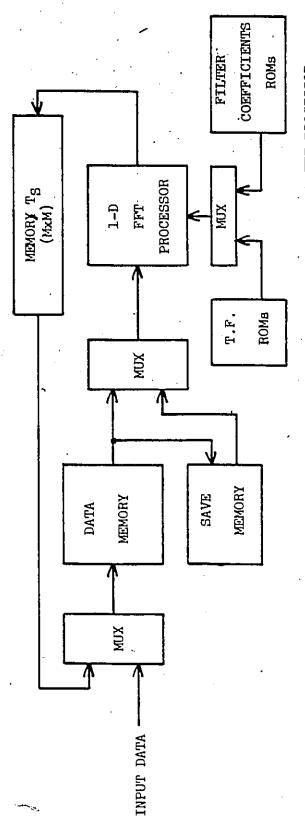

| 5.3           | A 2-D Radix-2 Convolver Organization                                                                                                                | 125   |

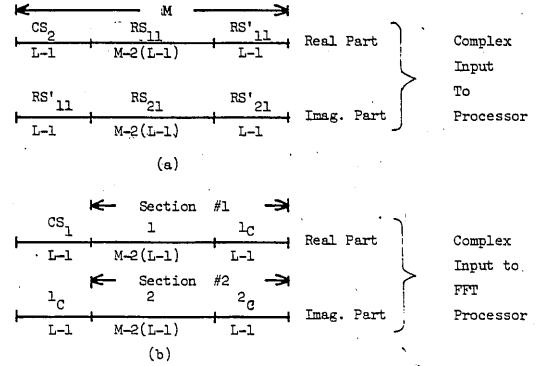

| 5.4           | Formation of Complex Input to the FFT Processor for Simultaneous Processing of Two Data Sections                                                    | 125   |

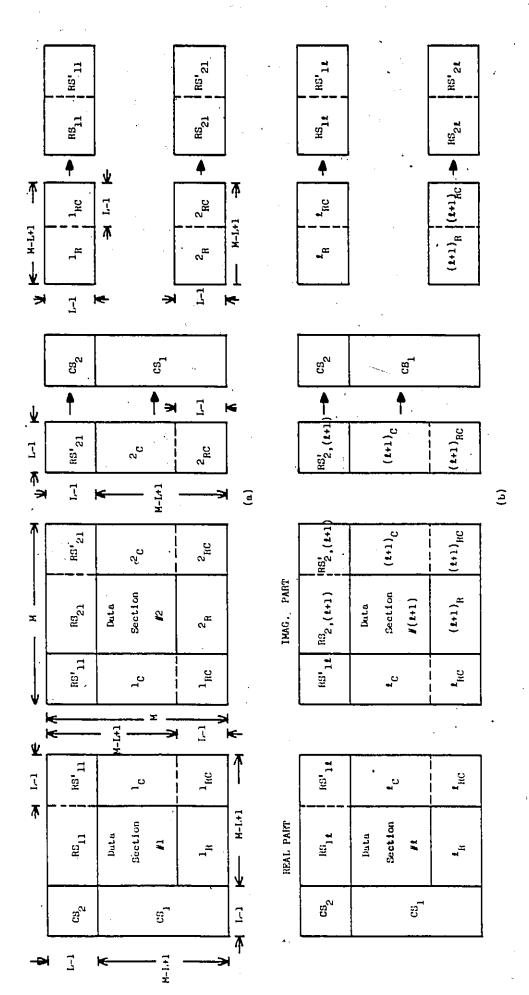

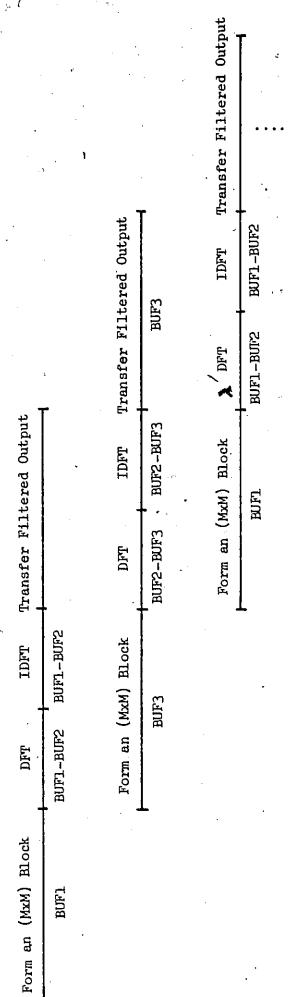

| 5.5           | Formation of an (MxM) Block Using Data Accessed from (a) The Data Sections 1 and 2 (b) The Data Sections 1 and (l+1), and the Save Memory Sections. | , 126 |

| 5.6           | FFT Processor Buffer Allocation and Timing Diagram for Processing Successive Data Sections.                                                         | 128   |

| Figure  |                                                                                                                              | Page |

|---------|------------------------------------------------------------------------------------------------------------------------------|------|

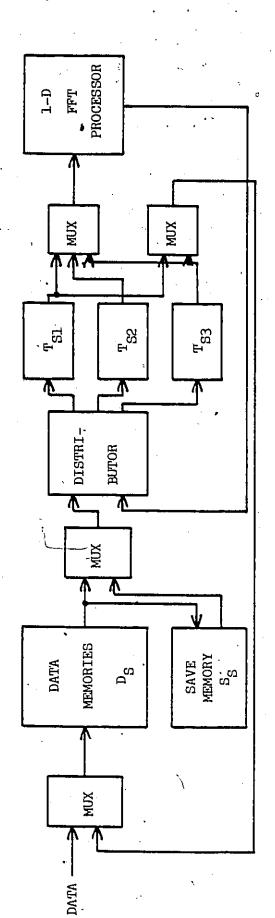

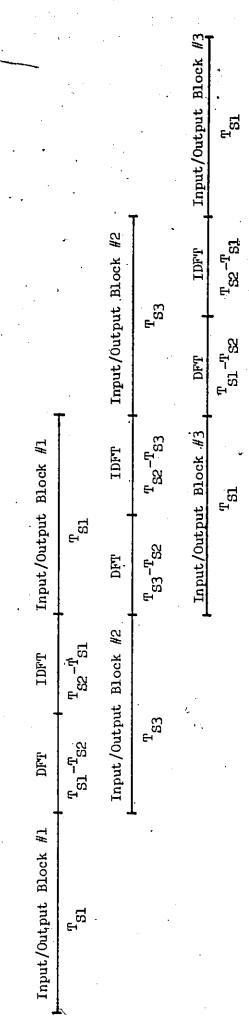

| 5.7     | A 2-D Convolver Organization Using 1-D FFT Processor                                                                         | 132  |

| 5.8     | A 2-D Convolver Organization Using 1-D FFT Processor<br>With 3 External Memories                                             | 136  |

| 5.9     | Allocation of Memories TS <sub>1</sub> , TS <sub>2</sub> and TS <sub>3</sub> for Continuous Operation of a 1-D FFT Processor | 136  |

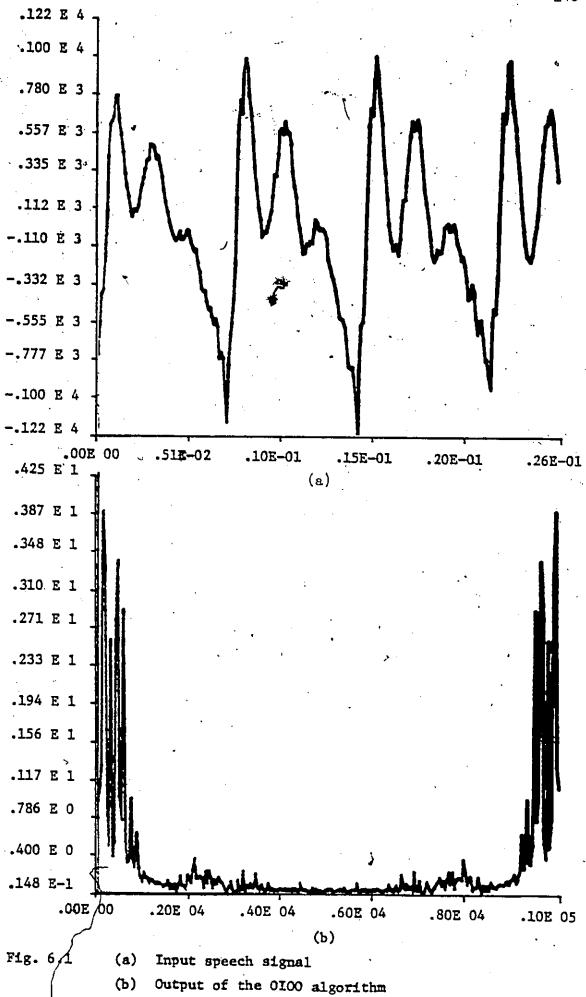

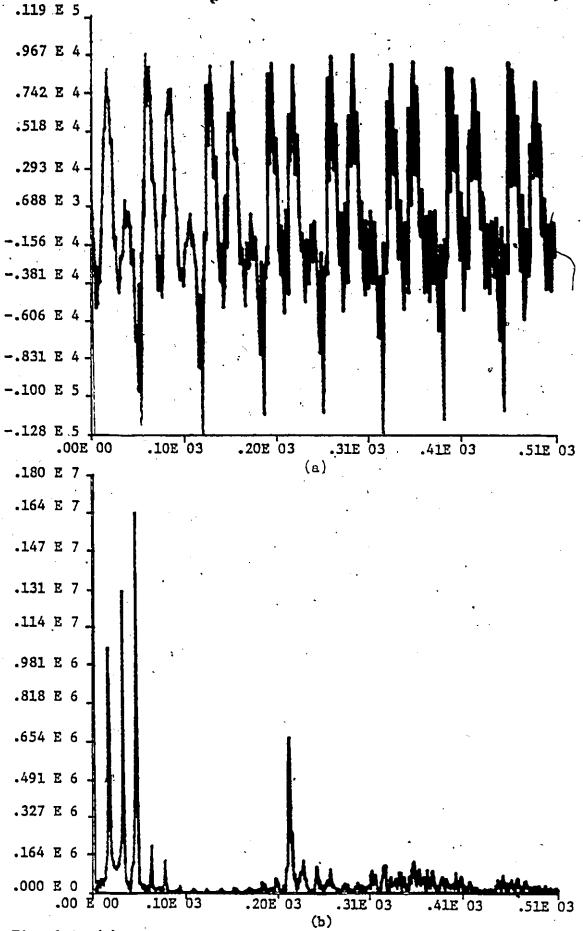

| 6.1(a)  | Input Speech Signal                                                                                                          | 148  |

| (p)     | Output of the OIOO FFT Algorithm                                                                                             | 148  |

| (c,)    | Output of the Standard DIT FFT Algorithm                                                                                     | 149, |

| (a)     | Error' Between the Outputs Generated by the OIOO and DIT FFT Algorithms                                                      | 149  |

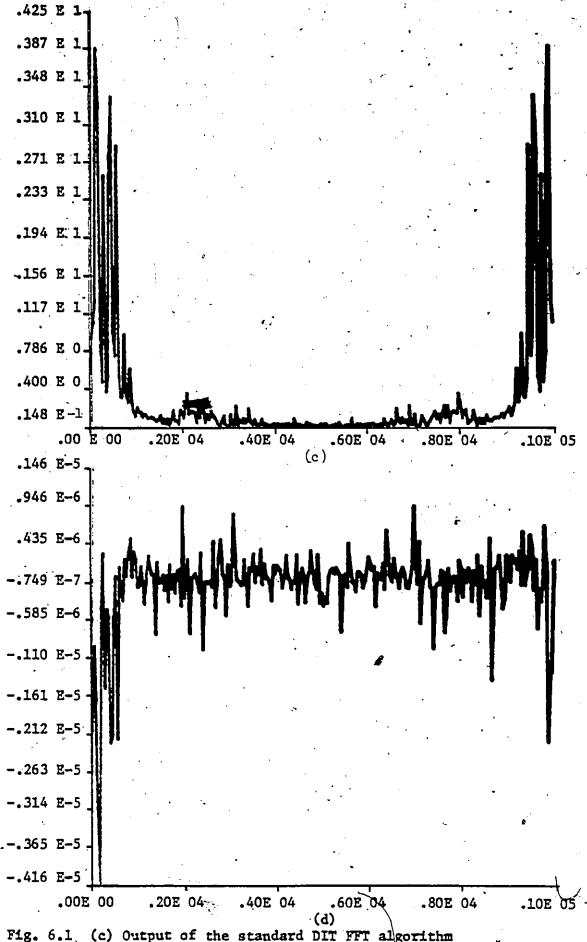

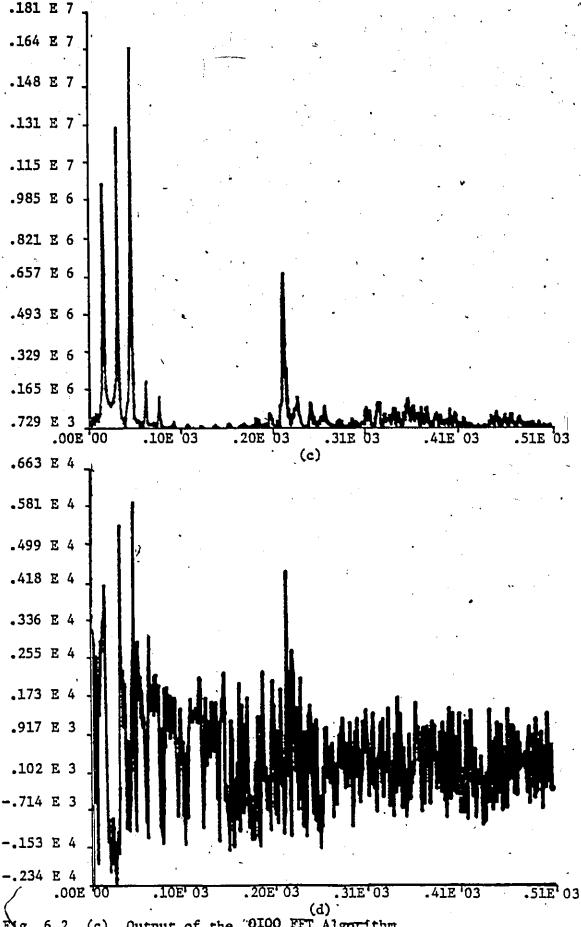

| 6.2(a)  | Input Speech Signal                                                                                                          | 152  |

| (ъ)     | Output of the EFT Processor Simulator                                                                                        | 152  |

| (c)     | Output of the OIOO FFT Algorithm                                                                                             | 153  |

| (a)     | Error Between the Outputs Generated by the Simulator and the OIOO FFT Algorithm                                              | 153  |

| 6.3(a). | Input Image                                                                                                                  | 155  |

| (b)     | Filtered Image Using the 2-D Radix-2 FFT Processor/<br>Convoler                                                              | 155  |

| (c)     | Filtered Image Using the Conventional Technique of Computing the 1-D DFT Along the Rows and then Along                       | `155 |

#### LIST OF TABLES

| <u> </u> |                                                                                                                                            | Page |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1      | Comparison of FFT Realizations                                                                                                             | 6    |

| 6.1      | Package Requirement for the Implementation of a 1-D Radix-4 1024-point FFT Processor/Convolver for a 6 Moduli RNS with 3 Scaling Moduli    | 144  |

| 6.2      | Package Requirement for the Implementation of a 2-D Radix-2 (64x64)-point FFT Processor/Convolver for a 6 Moduli RNS with 3 Scaling Moduli | 146  |

# LIST OF SYMBOLS

|                                    |                                             |                  |                 | . •  |

|------------------------------------|---------------------------------------------|------------------|-----------------|------|

| , 1-D \                            | One-dimensional                             |                  |                 | •    |

| 2-D                                | Two-dimensional                             |                  |                 |      |

| u-D                                | u-dimensional                               | <i>r</i>         |                 | •    |

| $\mathbf{D}_{\mathbf{k}}$          | Quasi-diagonal Matrix multiplication by the |                  |                 | •    |

| <b>f</b> , ,                       | Vector containing the                       | input of a Unit  | tary Transforma | tion |

| f <sub>i</sub> -                   | Vector containing the Unitary Transform     | input to the it  | th stage of a   |      |

| F                                  | Vector containing the                       | output of the l  | OFT ·           | ٠    |

| $\mathbf{I}_{\mathbf{k}}$          | Identity Matrix of size                     | ze (kxk)         |                 |      |

| p                                  | Vector containing the                       | transformed sec  | quence          |      |

| p <sub>i</sub> (r)                 | Base-r permutation ope                      | erator of the i  | th stage        |      |

| P .                                | Integer conversion fac                      | etor             |                 |      |

| $P_{N}$                            | Base-2 perfect shuffle                      | e operator of s  | ize (NxN)       |      |

| $P_{\mathbf{M}}^{(\mathbf{r})}$    | Base-r perfect shuffle                      | e operator of s  | ize (MxM)       |      |

| r                                  | Radix of the FFT algor                      | rithm            | • ' (           | ,    |

| r                                  | ith residue of a number                     | er modulo m      |                 |      |

| R <sub>m</sub> (r)                 | Multi-dimensional r-po<br>mth stage         | oint transform   | operator for th | æ    |

| s(r),s(r),                         | Radix-r transform open                      | rator            | •               |      |

| s <sub>m</sub>                     | Radix-r transform open                      | rator for the m  | th stage        |      |

| T                                  | Multi-dimensional unit                      | tary transform   | matrix          |      |

| $\mathtt{T}_{\mathbf{M}}^{^{(i)}}$ | Unitary transformation                      | n matrix of size | e (MxM)         |      |

| T <sub>M</sub> i                      | One-dimensional unitary transformation matrix of a multi-dimensional transform in the ith dimension |

|---------------------------------------|-----------------------------------------------------------------------------------------------------|

| u                                     | Dimension of an multi-dimensional array                                                             |

|                                       | e-J <sup>2π</sup> /M                                                                                |

| (r)<br><sup>u</sup> m                 | Base-r twiddle factor operator for the mth stage                                                    |

| βį                                    | ith factor of a unitary transformation matrix                                                       |

| ψm,                                   | Multi-dimensional base-r twiddle factor operator for the mth stage                                  |

| T                                     | Access-time of a buffer/ROM                                                                         |

| G*                                    | Complex conjugate of the matrix G                                                                   |

| $\llbracket \cdot  floor  bracket$    | Transpose of the matrix enclosed                                                                    |

| $[\cdot]_{\mathfrak{k}_{\mathbf{k}}}$ | 2, kth element of the matrix enclosed                                                               |

| $\lceil \cdot  ceil_R$                | The closest integer to the term enclosed                                                            |

| [·] <sup>© n</sup>                    | Kronecker nth power of the matrix enclosed                                                          |

| A ⊗ B                                 | Kronecker product of the matrices A and B                                                           |

| $ \mathbf{x} _{\mathbf{m_i}}$         | The residue of x modulo m.                                                                          |

|                                       | Multiplicative Inverse of m modulo m.                                                               |

| {a <sub>i</sub> }                     | Set containing the elements a                                                                       |

| Re(x)                                 | Real-part of the complex number x                                                                   |

| Im(x)                                 | Imaginary-part of the complex number x                                                              |

| BUF, BUFF                             | Memory buffer                                                                                       |

| $(H_{N})_{h}$                         | Natural-order WHT transformation matrix of size (NxN)                                               |

| (H <sub>N</sub> ) <sub>d</sub>        | Dyadic-ordered WHT transformation matrix of size (NxN)                                              |

| MUX                                   | Multiplexer unit                                                                                    |

RNS Residue Number System

ROM Read-Only Memory

SUB Memory Sub-buffer

SR Shift Register

# LIST OF APPENDICES

| • | 100 |

|---|-----|

|   |     |

|   | 166 |

APPENDIX A Computer Programs for the Verification of the 2-D Radix-2 0100 FFT Algorithm and the 2-D Convolver Architecture

#### CHAPTER 1

#### INTRODUCTION

In recent years there has been a growing interest in the study of unitary transforms in the area of one- and two- dimensional digital signal processing. Major applications of such transforms include image processing, speech processing, feature selection in pattern recognition, data compression and generalized spectral analysis. For example, the high frequency terms of the Fourier transform of an image give an indication of the amplitude and orientation of the edges within an image. Other applications are in transform coding in which a bandwidth reduction is achieved by discarding or grossly quantizing low-magnitude transform coefficients.

A discrete unitary transform is characterized by a unitary matrix of such that  $G \cdot [G^*]^T = I$  where \* denotes a complex conjugate,  $[\cdot]^T$  denotes a transpose and I is the identify matrix of the same order as G, say N. The computation of the transform of an input vector, f, of dimension N can be written as a matrix vector multiplication  $G \cdot f$ , which usually requires  $N^2$  operations where an operation is defined as a multiplication and an addition. In 1958 Good [1] proposed a technique to factorize the matrix, G, into a set of sparce matrices, each expressing a stage of computation. In 1965 Cooley and Tukey [2] used the approach followed

by Good and developed the Fast Fourier Transform (FFT) algorithm to compute the discrete Fourier Transform (DFT). In general, the FFT algorithm resulted in the computation of the DFT in (N·r:log N) operations as compared to N<sup>2</sup> operations required for the direct implementation. Recently, the matrix factorization approach described by Good has also been applied to develop fast algorithms for the computation of Hadamard [3], Walsh [4]; Haar [5], generalized Walsh [6], generalized Hear [6] and a more general class of orthogonal These algorithms also achieve a computational transforms, [7]. saving which is of the same order as that of the DFT. Two new algorithms (prime factor FFT and Winograd Fourier transform algorithms [9],[10]) to compute the DFT have also been proposed recently, which achieve further savings in the computation by computing the DFT via convolution using number theoretic concepts.

Many of the fast algorithms, reported in the literature, deal with one-dimensional transforms. Multi-dimensional unitary transforms are generally computed by taking one-dimensional transforms, utilizing fast one-dimensional unitary transform algorithms, along all dimensions, successively. The processing speed of the multi-dimensional unitary transform algorithms depends on the efficiency of the one-dimensional unitary transform algorithm employed. In [1] Good also proposed techniques to factorize the multi-dimensional transformation matrix into a set of sparse matrices containing elements of the one-dimensional transformation matrix. There is no evidence that this technique of

factorization of a multi-dimensional transformation matrix has been used to develop fast algorithms for the computation of multi-dimensional unitary transforms. Recently, Arambepola and Rayner [34] described a FFT algorithm for the computation of multi-dimensional DFT's which achieves a savings of more than 25% in the number of multiplications over the conventional FFT algorithms. The fast algorithms for the computation of other multi-dimensional unitary transforms are not well developed in the literature.

The principal objective of this research work is to develop twoand multi-dimensional unitary transform algorithms which are well

adapted for implementation by a special purpose processor for realtime\* processing of two and multi-dimensional signals. In

this work, we extend the idea of matrix factorization, proposed by

Good [1] to explore further the redundancy available in the transformation

matrices of many unitary transforms and present a unified approach to

the development of fast algorithms for a class of unitary transforms.

Based on this approach we present the development of fast algorithms for

a number of unitary transforms for real-time digital signal and image

processing applications. Before presenting the approach followed for

the implementation of the proposed algorithms and other objectives of

this work we give a brief survey of the various special purpose processor

architectures, proposed in the literature, for the implementation of

unitary transform algorithms.

By real-time we mean that the processor accepts the input data and generates the output data at the same sampling rate, continuously. The processing delay between an input sequence and the corresponding output is ignored.

# 1.1 UNITARY TRANSFORM IMPLEMENTATIONS

Since the DFT is an important transform in most digital signal processing applications, the FFT algorithm has been explored A detailed derivation of the FFT algorithms can be found in [7] and [23]. In general, there are two basic versions of the FFT algorithm, namely, the decimation-in-time (DIT) and the decimation-in-frequency (DIF) algorithm [23]. Both of the two versions have various structures which require ordered or digit reversed input and generate digit reversed or ordered output. An FFT algorithm computes the DFT of an N-point sequence for N = r, in log\_N stages and there are  $\frac{N}{r}$  radix-r butterfly operations in each stage. A radix-r butterfly operation consists of an r-point DFT operation on a set of r data points and multiplication of the r input data points or the result of r-point DFT operation by a set of complex coefficient known as twiddle factors [23]. A radix-2 implementation has the simplest structure but the efficiency of computation is improved by employing a higher radix FFT algorithm [26].

A general purpose processor is normally provided with a real adder, a real multiplier and memory having a word length of one data point. The software implementation of the FFT algorithm on such a processor requires 28 memory cycles [23] to perform a radix-2 butterfly operation. Since there are N/2 log<sub>2</sub>N butterfly operations, the total time required to compute an N-point DFT is given by 14 · T · N · log<sub>2</sub>N where T is the memory access time. This computation time does not

include the software overhead required to computé the data and twiddle factor addresses. Also, additional time is required to digit reverse the input or output sequence.

To achieve higher processing speeds most of the research effort on the hardware implementation of special purpose FFT processors has been concentrated on the development of

- (1) faster and new adder and multiplier structures [19],[27],[28];

- (2) Butterfly units with overlapped memory and arithmetic cycles and pipelined arithmetic operations [20],[23],[29];

- (3) memory structures to access multiple words simultaneously to reduce memory access time and to simplify the generation of data and twiddle factor addresses [11]-[27].

The structure of the FFT algorithm has also been exploited to perform multiple butterfly operations simultaneously [16]-[18],[30].

Based on the number of Butterfly units employed by a FFT processor, Bergland [30] divided the hardware implementation of the FFT algorithm into four categories, namely, the sequential, cascade and parallel iterative processors and the array analyzer. Table 1.1 shows some of the features of the four different realizations. The sequential realization is simplest to implement but the slowest of the four implementations. The cost of the third and fourth implementation is very high, which limits their applications. For high speed applications many forms of cascade processors have been proposed in the literature [11],[16]-[18],[20],[24]. Pease [16] and Gold [20] proposed the use

TABLE 1.1

# COMPARISON OF FFT REALIZATIONS

|    | D 31-15               | Butterfly     | Butterfly<br>Perform | Operations ned In               | Execution     |  |

|----|-----------------------|---------------|----------------------|---------------------------------|---------------|--|

|    | Realization           | units         | units Parallel       |                                 | Time T        |  |

| 'I | Sequential            | 1             | 1                    | <u>N</u> - m                    | T* <u>N</u> m |  |

| 2  | Cascade               | m .           | m                    | $\frac{\mathtt{N}}{\mathtt{r}}$ | T·T           |  |

| 3  | Parallel<br>Iterative | . <u>N</u>    | n<br>r               | m                               | T-m           |  |

| 14 | Array<br>Analyzer     | , m. <u>n</u> | m. n.                | 1                               | T ,           |  |

N = number of point in input sequence -

m = log\_N (number of stages)

\*T is the time required to perform a Butterfly operation

'

and includes the time required to generate data and twiddle

factor addresses.

of serial memories to eliminate the calculation of memory addresses at each stage of the FFT algorithm. Whelchel [11] also proposed the use of serial memories for a high-radix cascade processor. Since the cost of a cascade processor is proportional to the number of Butterfly units employed, Corinthios [12]-[15] proposed the use of serial memories for the implementation of a sequential processor for moderate cost and medium speed applications. Also the proposed memory organization yielded the output Fourier coefficients in a properly ascending order without the need for pre- or post-ordering of the data.

The redundancy in the transformation matrix of Hadamard, Walsh, Haar, generalized Walsh, Cosine and many other unitary transforms has also been exploited to develop the corresponding fast algorithms.

Similar to the development of the FFT processor proposed in [13], Corinthios [22] proposed the organization of a Walsh-Hadamard transform processor. The only difference between the two processors is that they specify a different permutation of the imtermediate results and there are no multiplications by the twiddle factors in the Walsh-Hadamard transform processor. In [5] Ahmed has proposed a Cooley-Tukey-type algorithm to compute the Haar transform and thus the Haar transform can be computed in a modified form of the FFT processor. The fast algorithms to compute generalized Walsh [6], Cosine [31] and many other unitary transforms [5],[31],[32] have structures which are similar to the FFT algorithm.

Multi-dimensional unitary transforms are generally computed by

taking one-dimensional unitary transform along all the dimensions, successively [31]-[34]. In applications, such as image processing and seismic data processing, the volume of data handling is quite large and some form of bulk storage must be used to store the input and output data. In earlier computers the size of available fast access memory was limited to only a few columns (or rows) of the two-dimensional data to be transformed. Singleton [35] and Hunt [36] have discussed techniques to transform a large matrix of data stored in an external bulk store with limited amount of high speed memory. Since these methods required transposition of the matrix after the column (or row) transforms, Anderson [37] proposed a modification of the Cooley-Tukey algorithm to avoid matrix transposition and to reduce the associated input/output operations.

Software implementation of the multi-dimensional transforms on a general purpose processor with auxiliary storage results in very slow processing speeds. Recent advances in semi-conductor memory have resulted in the development of high density and low cost memory packages and it is now possible to provide large amounts of fast access storage at a reasonable cost. A large improvement in the computation time of multi-dimensional transforms has also been obtained by the use of special purpose one-dimensional transform processors or general purpose array processors [38]. For very high speed applications, such as real-time transmission of pictures at video rates and real-time filtering of images and robotics, special purpose processors must be developed to cope with the large volume of data.

Joshi, McDonald et al. [21] have proposed a high speed multiprocessor architecture suitable for realizing a 512x512 point FFT in under 1/30 of a second. This processor has been realized with 16 one-dimensional Butterfly units and a number of memory units.

In the above discussion on the implementation of the unitary transform it was implied that all the compututations are performed using the binary number system (fixed point or floating point). Recently, the residue number system (RNS) has received considerable attention for the implementation of digital signal processing elements [39]+[44]. The use of RNS techniques has been proposed for the implementation of recursive and non-recursive filters [39], [42], [43] DFT [40], [41] and Number theoretic transforms [25]. The unique advantage of the RNS, as compared to the binary number system, is that the binary operations of addition, subtraction and multiplication can be performed using a number of independent and parallel paths. Addition and subtraction have no inter-digit carries or borrows and multiplication does not need the generation of partial products, thus resulting in fast operating speed. Also these operations may be performed at very high speed by the use of ROMs to provide parallel arrays of look-up tables [39].

From this discussion on the implementation of one- and multidimensional unitary transforms the conclusion that emerges is that a general purpose processor is incapable of satisfying the very high throughput rate requirement of many real-time applications and thus a special purpose processor must be realized. In order to design a special purpose processor one must consider various options and examine the tradeoffs that must be made. The architecture of a special purpose processor is usually dictated by the performance and cost requirements. Due to the inherent structural properties of the various unitary transform algorithms, a special purpose processor can be designed with increasing degrees of parallelism, performance and cost. Out of the four catagories of the FFT processors, discussed earlier, a casgade architecture satisfies the processing speed requirement of most of the real-time applications and a number of different cascade processors have been proposed in the literature. Sequential architectures have normally been considered for medium speed applications because of the limited computational power. A significant improvement in the processing speed of a sequential processor has been obtained by employing various pipelining techniques in the design of the arithmetic unit and special memory structures. The major factor which limits the processing speed of , a sequential processor is the speed limitations associated with the binary multiplications. Although various hardware units are commercially available, higher speed can only be obtained at higher cost and complexity. Fortunately, the residue number system can be used to overcome some of the problems associated with the binary number system.

Another objective of this work is to explore the application of residue number techniques to the implementation of unitary

transforms by a special purpose sequential processor for real-time digital signal and image processing. Although we have already given a preview of the objective of this work, we restate it again for clarity.

# 1.2 OBJECTIVE AND OUTLINE OF THE RESEARCH

The principal objective of this research is to explore further the redundancy available in the transformation matrix of one- and multi-dimensional unitary transforms and to propose special purpose processor architectures for real-time processing of one- and multidimensional signals. Because of the recent advances in memory technology and the development of high speed, high density and inexpensive memory IC's, it is becoming more and more attractive to trade logic gates for memory packages, we explore the use of RNS techniques to the implementation of high speed processors. the ROM oriented implementation of a RNS-based Butterfly unit allows pipelining of the basic arithmetic operations within the Butterfly unit, it is believed that a special memory architecture, combined with a single Butterfly unit, will alleviate the processing speed Ximitation of a sequential processor and thus the throughput rate requirement (>5 M. samples/sec.) of many real-time applications can be satisfied with a sequential processor.

Based on the above philosophy, this work concentrates on the development of multi-dimensional unitary transform algorithms that are well adapted for implementation by the parallel architectures of an

RNS-based special purpose sequential processor, and also result in a simple memory architecture to allow full utilization of the Butterfly unit.

As a starting point, we explore the nature of one-dimensional unitary transforms for which a number of fast algorithms have been proposed in the literature. In particular, we consider the memory structures for the implementation of the RNS-based one-dimensional FFT and fast Walsh-Hadamard transform processors. We show that a significant improvement in processing speed can be obtained with the use of RNS techniques. We also propose the FFT processor architectures for the implementation of one-dimensional convolution and to compute the DFT of multiple sequences in real-time. In the case of Walsh-Hadamard transforms (WHT) we show that the proposed FFT processor architecture can also be used to compute the WHT with a significant improvement in processing speed.

For the implementation of multi-dimensional unitary transforms, we present a technique to factorize the transformation matrices of a class of multi-dimensional unitary transforms into products of sparse matrices. Such factorizations result in fast unitary transform algorithms and yield processor structures which are similar to the one-dimensional processor organizations. As an illustration of the above technique, the architectures of the FFT and WHT processors for real-time processing of two-dimensional signals is presented. Similar to the one-dimensional algorithms, multi-dimensional FFT algorithms compute a DFT in log M stages, where M = r, but employ a multi-

dimensional radix-r butterfly operation and achieve a considerable saving in the number of multiplications over the conventional implementations.

Since the FFT algorithm is extensively used to perform convolutions, we also show the development of a special memory architecture required to support the implementation of two-dimensional convolutions. These convolver organizations are shown to be suitable for the computation of convolutions using Number theoretic transforms defined over complex residue rings.

## 1.3 THESIS ORGANIZATION

In Chapter 2, a review of the basic structure of the one-dimensional unitary transformation matrices and their associated fast algorithms is provided. Special emphasis is placed on the factorization techniques used to develop one-dimensional FFT and WHT algorithms as these are used to develop fast algorithms for the multi-dimensional unitary transforms. The RNS and its basic properties are also reviewed.

Chapter 3 covers the development of the RNS-based one-dimensional FFT and WHT processors and convolvers. An algorithm and the resulting processor architecture for processing data from a number of independent channels are also developed.

In Chapter 4, fast algorithms based on the Kronecker product factorization of the multi-dimensional unitary transformation matrix are developed. These algorithms are applied to develop RNS-based processor architectures for the implementation of two-dimensional DFT,

WHT and generalized Walsh transforms. Processor architectures for real-time computation of the two-dimensional DFT, WHT and generalized Walsh transform are also presented.

Chapter 5 covers the implementation of two-dimensional convolution using the one- and two-dimensional FFT processors developed in Chapter 3 and 4. Special memory organizations for the implementation of two-dimensional convolutions are also proposed. On the basis of cost to performance ratio, a comparison of the two convolver architectures realized using one- and two-dimensional FFT processors, respectively, is presented. A comparison of the convolver organizations realized via FFT and NTT defined over complex residue rings is also presented.

In Chapter 6, an approximate number of commerically available IC packages required to implement one- and two-dimensional RNS-based FFT processors and convolvers is given. The results obtained via simulation of the proposed FFT processors and convolvers are compared with the results obtained via the implementation of the standard FFT and convolution algorithms.

Chapter 7 summarizes the conclusions resulting from this research.

#### CHAPTER 2

# ONE-DIMENSIONAL UNITARY TRANSFORM ALGORITHMS

# 2.1 INTRODUCTION

In the past, the computation of a unitary transform of an N-point sequence required N<sup>2</sup> operations and proved very time consuming and uneconomical. Since the development of the fast Fourier transform algorithm by Cooley and Tukey [2] in 1965, a significant amount of research effort has been directed towards finding efficient algorithms for the implementation of unitary transforms [1]-[10]. The underlying principle for efficient implementation of unitary transforms is the utilization of the high degree of redundancy in the transform matrix description (transformation matrix). If the redundancy in a transformation matrix can be eliminated by matrix factorization, then a more efficient way of implementation is available. The technique of factorization of a unitary transformation matrix into products of sparse matrices was first described by Good [1] in 1958 and resulted in the development of fast Fourier [2], Hadamard [3], Walsh [4], Haar [5], generalized Walsh [6], generalized Haar [6] and a more general class of ... othogonal transform [7] algorithms.

As indicated in the last Chapter, software implementation of the unitary transforms on a general purpose processor result in relatively slow processing speed. For a large class of applications which have an inherent large bandwidth real-time constraint or have a large amount of

data, speed becomes very important and several special purpose unitary transform processors have been proposed in the literature [11]-[25]. The requirement of high processing speed necessitates the search for available algorithms or the development of new algorithms that are well adapted for a parallel processor architecture. The problem of designing a special purpose processor is thus analogous to the problem in computer architecture in which we seek a proper match between the implemented algorithm and the various resources of a processor. this work we follow both of the above approaches; that is we search for algorithms already proposed in the literature and we also propose new algorithms that are well adapted for implementation by a special In this Chapter we review the basic concepts of processor. unitary transforms and the techniques used to develop fast unitary transforms algorithms. We also describe some of the algorithms and processor architectures, proposed in the literature, which are suitable for implementation by a special purpose processor. In the following chapters we propose extensions of the published algorithms and processor architectures and also present development of new algorithms and the resulting processor architectures for real-time processing of two-dimensional signals.

# 2.2 ONE-DIMENSIONAL UNITARY TRANSFORMS

The one-dimensional forward unitary transform of an N-point sequence f(n), n=0,1,...,N-1 is defined as

$$p(m) = \sum_{n=0}^{N-1} f(n) g(n,m); m=0,1,...,N-1$$

(2.1)

٠ - ټو

where p(m) is the transformed sequence and g(n,m) is the forward transformation kernel. Similarly, the inverse unitary transform of the sequence p(m) is given by the relation

$$f(n) = \sum_{m=0}^{N-1} p(m) h(n,m); n=0,1,...,N-1$$

(2.2)

where h(n,m) denotes the inverse transformation kernel. The transform pair defined in equation (2.1) and (2.2) is unitary if the transformation kernels g(n,m) and h(n,m) satisfy the following orthonormality conditions:

$$\sum_{m=0}^{N-1} g(n,m) \cdot g^*(j,m) = \delta(n-j)$$

(2.3a)

$$\sum_{m=0}^{N-1} h(n,m) \cdot h^*(j.m) = \delta(n-j)$$

(2.3b)

$$\sum_{n=0}^{N-1} g(n,m) \cdot g^*(n,k) = \delta(m-k)$$

(2.3e)

$$\sum_{n=0}^{N-1} h(n,m) \cdot h^*(n,k) = \delta(m-k)$$

(2.3d)

where  $g^*(x)$  denotes the complex conjugate of g(x) and  $\delta(x)$  is the Kronecker delta. Based on the set's of orthogonal functions such as exponential, Walsh and Haar, a number of discrete unitary transforms, namely, discrete Fourier transform (DFT), Walsh-Hadamard transform (WHT), Haar (HT), discrete Cosine transform (DCT), generalized transform (GT) and generalized Walsh transform (GWT), have been defined in the literature [6], [7], [31], [32].

In the development of fast algorithms for the computation of a unitary transform, it is useful to express equations (2.1) and (2.2)

in vector notation. Let p and f be vector representations of the sequences p(n), f(n), n=0,1,...,N-1, i.e.

$$p = [p(0), p(1), ..., p(N-1)]^{T}; f = [f(0), f(1), ..., f(N-1)]^{T}$$

where  $[x]^T$  denotes the transpose of [x]. Then in the vector representation equations (2.1) and (2.2) can be written as

$$p = Gf (2.4)$$

and

$$f = Hp$$

(2.5)

where G and H are the forward and inverse transformation matrices of size (NxN), respectively, and the elements of G and H are given by  $G_{n,m} = g(m,n)$  and  $H_{n,m} = h(n,m)$ . Since equations (2.4) and (2.5) define a transform pair  $H = G^{-1}$ , and for a unitary transform  $G^{-1} = [G^*]^T = H$ , hence the transformation matrices G and H are unitary. For some unitary transforms, the transformation matrix G is real and the unitary transforms are known as orthogonal transforms. For such transforms  $H = G^{-1} = G^T$ .

In the vector representation of a unitary transform, the rows of its transformation matrix may be obtained by sampling the set of orthogonal functions defining the unitary transform. Also, in terms of the vector respresentation, the transformation matrices of a unitary transform satisfy the following orthonormality conditions which are equivalent to the conditions given by (2.3):

$$[G^*]^T \cdot G = G \cdot [G^*]^T = I_M$$

(2.6a)

$$[H^*]^T \cdot H = H \cdot [H^*]^T = I_N$$

(2.6b)

where  $I_N$  denotes the identity matrix of size (NxN). Examples of the transformation matrices defining the DFT, WHT and HT are shown in Fig. 2.1, for N = 8, where W =  $e^{-j2\Pi/N}$ . These matrices may be obtained by sampling the sets of complex exponential, Walsh and Haar functions at N equidistant points. A detailed procedure for the generation of transformation matrices for a large class of unitary transforms may be found in the references [7], [31] and [32].

operations. As mentioned earlier, an efficient way of computing a unitary transform may be obtained if the transformation matrix defining the transform can be factored into a product of a set of sparse matrices.

For a number of unitary transforms such a factorization, and the resulting fast algorithms, has been proposed in the literature [1]-[27], [30]-[38]. Since the discrete Fourier and Walsh-Hadamard transforms are most often used in digital signal and image processing, we will concentrate on the factorization of DFT and WHT transformation matrices and the processor architectures implementing the corresponding fast algorithms. The factorization techniques discussed here can be extended easily to other unitary transforms.

# 2.3 ONE-DIMENSIONAL DISCRETE FOURIER TRANSFORM IMPLEMENTATION

In 1965, Cooley and Tukey [2] applied the matrix factorization technique proposed by Good [1] to compute the DFT of an N-point sequence for  $N=2^{\ell}$ , which resulted in a fast algorithm to compute the DFT in  $N\log_2 N$  operations instead of the originally required  $N^2$  operations.

Fig. 2.1 8x8 TRANSFORMATION MATRICES OF (a) DFT (b) WHT (c) HT

Since then, many variations of this basic algorithm have been proposed; all variations being termed Fast Fourier transforms (FFT) algorithms [23]. Although all of the FFT algorithms available in literature can be implemented on a general purpose processor as software or firmware routines, the throughput rate obtainable from this type of implementation is sufficient only for non real-time applications. A moderate increase in processing speed has been obtained by the use of a combination of a general purpose computer and an array processor [38] where the array processor performs the arithmetic operations, specified by the FFT algorithm, in its high speed arithmetic unit. Due to the constraints imposed by the internal architecture of most of the commercially available array processors, these processors are unable to perform arithmetic operations on multiple data items simultaneously and thus cannot satisfy the throughput rate requirement of many real-time applications. Hence, for high processing speed, we must investigate various special purpose processor architectures which are more suitable for parallel processing. Since the objective of this work is the development of algorithms that are well adaptable for implementation by the parallel machine architecture of a special purpose processor, we will discuss some of the algorithms, proposed in the literature, which are better suited for parallel processing.

In 1968, Pease [16] discribed a variation of the Cooley-Tukey FFT algorithm in which he first partitioned the DFT transformation matrix and then factored it in terms of arithmetic and permutation operators.

In a manner similar to the Cooley-Tukey algorithm, Pease's factorization

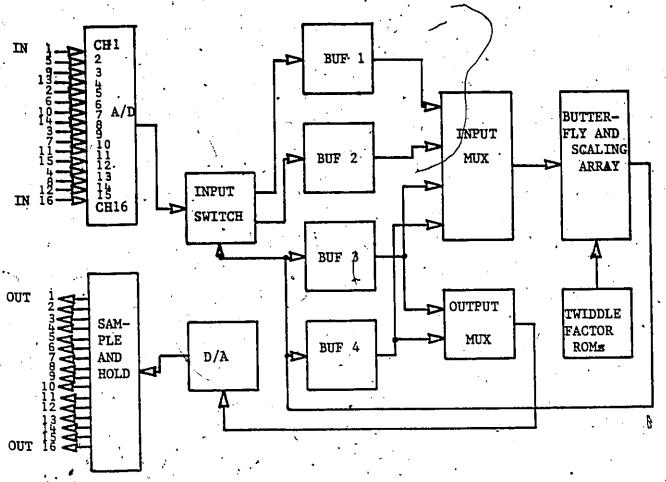

specified an 1-stage algorithm for N = 2", but in Pease's factorization each stage consisted of a constant permutation of the input data elements and the arithmetic operator specified operations of addition and subtraction on pairs of successive data elements. Pease also suggested the implementation of this algorithm on a cascade/parallel iterative type of processor where the permutation operation is performed by a hardwired shift network. In 1969, Pease [17] suggested another architecture where he emphasized the utilitization of relatively slow memories and a number of arithmetic units operating in parallel. Whelchel and Guinn [11] used the matrix factorization techniques suggested by Pease and proposed the implementation of a radix-4 cascade processor utilizing serial shift registers for high-speed digital Similar cascade/pipeline architectures using serial memories were also proposed by Groginsky and Works [18] and Gold and Bailly [20]. These architectures used less amounts of memory than required by the organization proposed in [11], but were more suitable for simultaneous processing of data from a number of input channels.

All the above mentioned implementations of the FFT algorithm require a number of arithmetic units and generate the Fourier coefficients in a digit-reversed order. For applications which call for an ordered output, a pre-shuffling or post-ordering of the data is required which results in a reduced throughput rate. Corinthios [12]-[15] used the matrix factorization techniques suggested by Pease [16] and proposed a number of algorithms that are well suited for implementation by a serial sequential processor. Also, these algorithms absorb the post-

ordering operations within the permutation operations of each stage and the Fourier coefficients are generated in the natural ascending order without any loss in processing speed. A processor architecture implementing these algorithms and using serial memories is described in [15].

Although the cascade/pipeline FFT processor architectures proposed by Pease, Groginsky and Works, and Gold and Bailly satisfy the processing speed requirement of most of the real-time signal processing applications, the cost of these processors is proportional to the number of arithmetic units they employ. In this work we will show that, with the use of high density, high speed and low cost commercially are memory packages, the throughput rate obtainable from a serial sequential FFT processor architecture, that is well matched to the implemented algorithm, is comparable to the throughput rate obtainable from a cascade/pipeline architecture. We will also show that the architecture of a sequential processor is also adaptable to process two-dimensional signals in real-time.

Since, the FFT algorithms proposed by Corinthios [13], [14] result in a serial sequential hardwired processors having simplified control functions for the generation of data and twiddle factor addresses, we choose the Ordered-input Ordered-output (OIOO) FFT algorithm as the basis of our further investigation. Another advantage of this algorithm is that it generates the Fourier coefficients in a properly ascending order without pre-ordering of the input data. Since OIOO FFT algorithm

also leads to the development of a high speed two-dimensional FFT processor, we describe this algorithm in detail.

## 2.3.1 One-Dimensional (1-D) OIOO FFT Algorithm and its

### Implementation

The DFT of an M-point sequence f(n) is defined over the field of complex numbers as

$$F(k) = \sum_{k=0}^{M-1} f(n) W^{k}; \quad k, k = 0,1,...,M-1$$

(2.7)

where  $W=e^{-j2\pi/M}$  is the Mth root of unity over the field. This can also be written in the matrix form of equation (2.4) as

$$F = T_{M} f$$

(2.8)

where  $\mathbf{T}_{\underline{\mathbf{M}}}$  is the MxM DFT transformation matrix and the elements of  $\mathbf{T}_{\underline{\mathbf{M}}}$  are given by

$$\left[\mathbf{T}_{\mathbf{M}}\right]_{\mathbf{k},\mathbf{k}} = \mathbf{W}^{\mathbf{k}\mathbf{k}} \tag{2.9}$$

To simplify notation, we preserve only the exponent of W, that is we write k in place of W. Then  $T_M$  can be written as

The matrix  $T_M$  can be expressed in terms of a permutation matrix  $P_M^{(r)}$  and  $T_M$  as

$$T_{M} = P_{M}^{(r)} T_{M}^{t} \tag{2.11}$$

or

$$T_{M}' = [P_{M}^{(r)}]^{-1} T_{M}$$

(2.12)

where  $P_{M}^{(r)}$  is the ideal shuffle base-r permutation operator which is defined by its operation on a vector of dimension M, where M/r=q is an integer, by the relation

$$P_{M}^{(r)} \cdot [x_{0}, x_{1}, x_{2}, \dots, x_{M-1}]^{T}$$

$$= [x_0, x_q, x_{2q}, \dots, x_1, x_{q+1}, x_{2q+1}, \dots, x_2, x_{q+2}, x_{2q+2}, \dots, x_{M-1}]^T$$

(2.13)

When M is a composite number, i.e.  $M = r^n$ , Corinthios [14] has shown that the matrix  $T_M'$  cam be partitioned into  $(r \times r)$  square sub-matrices, each of dimension M/r, and factored into a product of matrices including a matrix  $T_{M/r}$ .  $T_{M/r}$  iteself can then be partitioned and factored in terms of  $T_{M/r}$ . If this process is iterated n times we obtain a complete factorization of  $T_M$ . The result of the ith iteration can be written as

$$T_{M/k} = P_{M/k}^{(r)} (T_{M/rk} \otimes I_r) D_{M/k}^{(r)} (T_{M/rk} \otimes T_r)$$

(2.14)

where  $k = r^{i}$ , the symbol  $\otimes$  stands for the Kronecker product of matrices [16] and

$$D_{M/k} = \text{quasi-diag} (I_{M/rk}, I_k, L_{2k}, ..., L_{(r-1)k})$$

$$L_{m} = diag (0, m, 2m, ..., (M/rk-1)m)$$

(2.15)

$$T_{r} = \begin{bmatrix} 0 & 0 & 0 & 0 & & & & 0 \\ 0 & M/r & 2M/r & 3M/r & & & & & (r-1)M/r \\ 0 & 2M/r & 4M/r & 6M/r & & & & 2(r-1)M/r \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & &$$

and  $\mathbf{I}_k$  is the identity matrix of dimension k. Using (2.14) and replacing in turn every matrix  $\mathbf{T}_{\mathrm{M/k}}$  by its factors in terms of  $\mathbf{T}_{\mathrm{M/rk}}$  a complete factorization of  $\mathbf{T}_{\mathrm{M}}$  is obtained and can be written as

$$T_{M} = \prod_{m=1}^{n} \mu_{m}^{(r)} s_{m}^{(r)}$$

(2.17)

where  $\mu_{m}^{(\mathbf{r})}$  is a twiddle operator specifying multiplications by the twiddle factors and is given by

$$\mu_{\hat{i}}^{(r)} = (I_{r}^{n-i} \cdot \otimes D_{r}^{(r)}); i=2,3,...,n$$

(2.18)

$s_{\underline{m}}^{(r)}$  is an r-point transform operator given by

$$s_{m-1}^{(r)} = s^{(r)} p_m^{(r)}; m=2,3,...,n$$

(2.19a)

with

$$(s_n^{(r)}) = s_n^{(r)} = (I_{M/r} \otimes T_r)$$

(2.19b)

where p<sub>i</sub>(r) is a permutation operator defined by

$$p_{i}^{(r)} = (I_{r}^{n-i} \otimes P_{ri}^{(r)})$$

(2.20)

and

$$p_1 = \mu_1 = I_N \tag{2.21}$$

Also

$$s_{m-1}^{(r)} = p_m^{(r)} s_m^{(r)}; m=2,3,...,n$$

(2.22)

where

$$s^{(r)} = (I_{M/r^2} \otimes T_r \otimes I_r)$$

(2.23)

Substituting equation (2.17) into (2.8) we get

$$F = \{ \prod_{m=1}^{n} \mu_{m}^{(r)} s_{m}^{(r)} \} f$$

(2.24)

or

$$F = \{\mu_1^{(r)} \ s_1^{(r)} \ \mu_2^{(r)} \ s_2^{(r)} \ \mu_3^{(r)} \ s_3^{(r)} \ \dots \ \mu_n^{(r)} \ s_n^{(r)} \} f$$

Equation (2.24) simply states that the computation of F may be divided into n stages where each stage performs the computation specified by the operators  $\mu_m^{(r)} s_m^{(r)}$ . The operators of any stage operate on the output of the previous stage and operators  $\mu_n^{(r)} s_n^{(r)}$  of the first stage operate on the input vector f.

For the intermediate stages the computation specified by the operators  $\mu_{\bf i}^{({\bf r})}~s_{\bf i}^{({\bf r})}$  can be written as

$$\mu_{i}^{(r)} s_{i}^{(r)} = \mu_{i}^{(r)} p_{i+1}^{(r)} s_{i}^{(r)} = (I_{r^{n-i}} \otimes D_{r^{i}})(I_{r^{n-i-1}} \otimes P_{r^{i+1}})$$

$$(2.25)$$

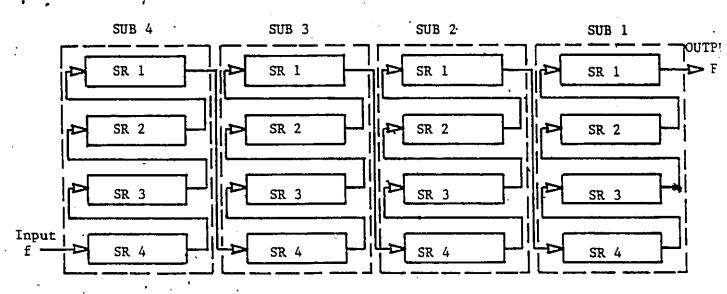

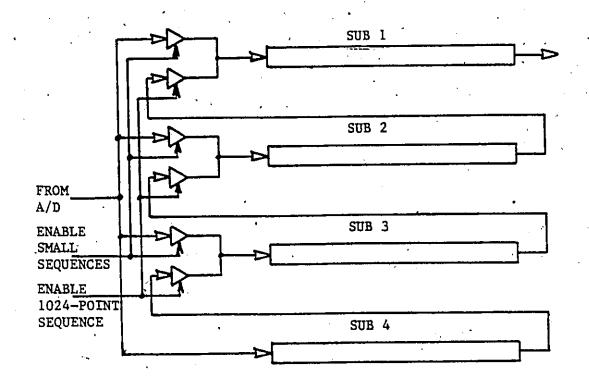

If we look at the expanded form of the operator  $s^{(r)}$ , we find that this operator always operates on data points which are  $M/r^2$  words apart. An address separation of  $M/r^2$  between the data points can be easily obtained if the memory storing the M points is split into  $r^2$  serial sub-memories where each sub-memory stores  $M/r^2$  data words. Thus, when the data from the sub-memories is accessed sequentially, the difference in their address is always  $M/r^2$ . A sequential memory organization, which allows both the addressing structure specified by  $s^{(r)}$ , and permutation specified by  $p^{(r)}_{i+1}$ , is shown in Fig. 2.2 for r=4.

The memory structure of Fig. 2.2 consists of two memory buffers BUF1 and BUF2, each storing M data words. Each buffer is divided into r sub-buffers (SUB) where each SUB consists of r shift registers (SR) with a storage capacity of M/r<sup>2</sup> data words. The SRs in each SUB can be connected in series to form a SUB of size M/r, and also the SUBs within BUF1 or BUF2 may be connected in series to form a shift register of size M. During the FFT computation, BUF1 and BUF2 are used to access data for the butterfly operation and to store the results alternatively, i.e. when BUF1 stores the data for input to the Butterfly unit, BUF2 stores the output of the Butterfly unit. The multiplexer (MUX) is used to select between BUF1 and BUF2 for data input to the

Fig. 2.2 Memory Organisation of the 1-D FFT Processor

Butterfly unit.

To implement the operations specified by s(r), we simply select a SUB and the data at top of the SRs of the selected SUB forms the After the data is accepted by the input to the Butterfly unit. Butterfly unit, each SR in the selected SUB is shifted right by one position so that the next data set becomes available at the output of the SRs. A SUB within a buffer is selected on a rotating basis, starting with SUBl, i.e. the selection of the SUBs always follows the order SUB1 - SUB2 - SUB3 - SUB4 - SUB1 ..... butterflies for which a SUB is selected depends upon the operators s<sup>(r)</sup>, and p<sub>i+1</sub> and hence the FFT stage. For the jth FFT stage the permutation is specified by the operator  $p_{n-(j-2)}^{(r)}$  (the indexing of the FFT stage is opposite to the ordering of the stage operators) and we perform r<sup>1-2</sup> sequential accesses from one SUB before selecting the next SUB. An additional base-r perfect shuffle operation is required to implement the operations specified by the operators s(r), which can easily be achieved while storing the output of the Butterfly unit into the buffer used for storing the output. cannect the SRs in each SUB of the output buffer in series and the r output points from the Butterfly unit are shifted into the SUBs, one At the end of a stage, the output buffer will point in each SUB. store the input data for the next stage.

The operations specified by  $\mu_i^{(r)}$  are performed within the Butterfly unit. Since  $\mu_i^{(r)} = (I_{rn-i} \otimes D_{ri})$  is a diagonal operator, it simply

specifies multiplication of the output of r-point transform with the twiddle factors. We can store all the required twiddle factors in ROMs and the ROM addresses can be generated by evaluating equation (2.15).

From equation (2.24) we see that the operations for the first FFT stage are specified by the operator  $s_n^{(r)} = s^{(r)}$  (not by  $s^{(r)}$ ) and specifies that the r-point transform operator be applied to data points separated by M/r points. This can be achieved when the SRs in each SUB of the buffer containing the input vector f are connected in series. The r points taken from the top SR of each SUB then forms the input to the Butterfly unit. Throughout the first FFT stage, all CUBS of the input buffer supply data to the Butterfly unit. The output buffer configuration remains the same as discussed earlier.

It may be noted that  $\mu_1^{(\mathbf{r})} = I_N$  and thus for the last FFT stage the twiddle factors are unity. At the end of the last stage the output buffer will store the vector F in a natural sequential order.

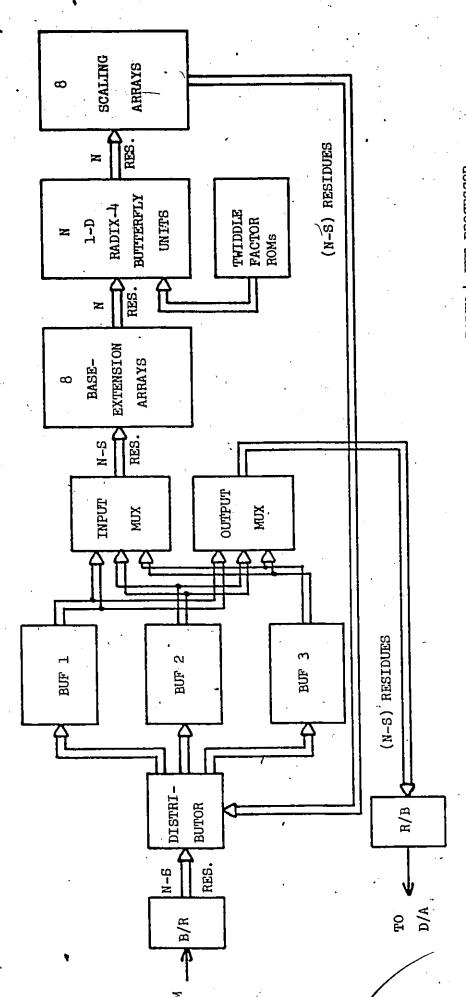

In [15], Corinthios et al. proposed a radix—4 processor architecture, implementing the above 0I00 algorithm, for digital spectral analysis.

This processor incorporated the basic organization of Fig. 2.2 as the central part and an input and an output buffer for real-time processing of input data and the computation of average power spectra.

The Butterfly unit of this processor used a very complex three-dimensional multiplier architecture with a dynamic range of 21 bits. This organization of the FFT processor resulted in a real-time processing speed of 1.6

million samples/second. In the next chapter we will present an extension of the above processor architecture to obtain throughput rates of over 10 million samples/second.

#### 2.4 ONE-DIMENSIONAL WALSH-HADAMARD TRANSFORM AND ITS IMPLEMENTATION

The development of the FFT algorithm, to compute the DFT, by Cooley and Tukey [2] led to the development of many other unitary transforms having applications in the areas of digital signal processing, image processing and pattern recognition. In 1968, Whelchel and Guinn [3] introduced the Hadamard transform for signal representation and classifications which is based on the Hadamard matrix. Two variations of the Hadamard transform based on different ordering of the Walsh functions have also been proposed [7]. These different transforms are commonly known as Walsh-Hadamard transforms (WHT). This class of transforms has also been extended to a much larger class of orthogonal transforms known as generalized Walsh transforms [6]. In this section we will give a brief description of the techniques used to factorize the Walsh-Hadamard transformation matrix resulting in fast algorithms for its implementation. In the next two chapters we will show that the one- and two-dimensional FFT processor architecture are also suitable to compute the WHT and generalized Walsh transforms in real-time.

Fino and Algazi [4] and Geadah and Corînthios [22] have described techniques to factorize the transformation matrices of various ordering of the WHT. In [4] Fino showed that the various ordering of the WHT can be expressed as a product of perfect shuffle operators and the

WHT transformation matrix in natural ordering. Geadah [22] used the factorization techniques similar to those used in the development of OTOO FFT algorithm of section 2.3.1 and suggested a wired-in serial processor architecture for its implementation where a permutation stage is performed after a stage of additions and subtractions. In this section we describe briefly the factorization of the WHT transformation matrix proposed by Geadah [22], and in the next chapter we will show that the permutation and computational stages of the dyadic-ordered WHT can be merged into a single stage which results in a higher processing speed than that obtainable from the processor architecture described in [22].

## 2.4.1 Dyadic-Ordered Fast WHT Algorithm and its Implementation

The algorithms for the computation of various ordering of WHT are based on the Hadamard matrix. A Hadamard matrix of order N can be obtained by the following recursive relation:

$$(H_N)_h = (H_{N/2})_h \otimes H_2$$

(2.26)

where  $(H_N)_h$  is a Hadamard or natural-order WHT transformation matrix and  $H_2$  is the core matrix of order 2 which is the lowest order Hadamard matrix:

$$H_2 = \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix} \tag{2.27}$$

By using the relation given by (2.26) recursively we can write

$$(H_{N})_{h} = [H_{2}] \otimes \log_{2} N$$

(2.28)

where  $[\cdot]^{\otimes n}$  indicates n successive Kronecker products. In [22] Geadah has shown that the Dyadic-ordered WHT transformation matrix  $(H_N)_d$  can be written in terms of  $(H_N)_h$  as