#### University of Windsor

### Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2004

#### IP protection for DSP algorithms' FPGA implementation.

Wei Dai University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Dai, Wei, "IP protection for DSP algorithms' FPGA implementation." (2004). *Electronic Theses and Dissertations*. 2517.

https://scholar.uwindsor.ca/etd/2517

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# IP Protection for DSP Algorithms' FPGA Implementation

by

Wei Dai

A Thesis

Submitted to the Faculty of Graduate Studies and Research

Through the Department of Electrical and Computer Engineering

In Partial Fulfillment of the Requirements for

The Degree of Master of Applied Science at the

University of Windsor

Windsor, Ontario, Canada August 2004

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-96386-1 Our file Notre référence ISBN: 0-612-96386-1

The author has granted a nonexclusive license allowing the Library and Archives Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

exclusive permettant à la

Bibliothèque et Archives Canada de

reproduire, prêter, distribuer ou

vendre des copies de cette thèse sous

la forme de microfiche/film, de

reproduction sur papier ou sur format

électronique.

L'auteur a accordé une licence non

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# Canadä

1008405

#### © 2004 Wei Dai

All Rights Reserved. No Part of this document may be reproduced, stored or otherwise retained in a retrieval system or transmitted in any form, on any medium or by any means without the prior written permission of the author.

## Abstract

With today's system-on-chip (SOC) technology, we are able to design larger and more complicated application-specific integrated circuits (ASICs) and field programmable gate array (FPGA) in shorter time period. The key point of the success of SOC technology is the reuse of intellectual property (IP) cores. Consequently the copyright protection for these IP cores becomes the major concern for the development pace of SOC technology.

Watermarking technology has been proved to be an effective way of copyright protection. In this thesis, the author presents two new watermarking algorithms respectively at algorithm level and FPGA layout level. The simulations and implementation results show that the new proposals have much less design and hardware implementation overheads, lower watermark embedding and extraction cost, as well as higher security strength, compared to the previously proposed methods.

# Acknowledgements

Here I would like to give my sincere thanks to everyone who has help me for the successful completion of this thesis.

Firstly I would like to thank my co-supervisors, Dr.H.K.Kwan and Dr.H.Wu. Dr.H.K.Kwan has rich experience in DSP algorithm development as well as FPGA implementation. He gives me detail guidance of the research direction. Dr.H.Wu shares his strong experience in data hiding and data encryption during my research procedure. He helps me to select the thesis topic, supervises me through the thesis writing procedure and gives a lot of valuable suggestions.

Thanks also go to the committee members, Dr.K.Tepe and Dr.H.Hu, for their helpful advice to improve this thesis.

Finally, I also thank my friends in VLSI lab for their kind help.

# Table of Contents

| Abstract      | •••••••••••••••••••••••••••••••••••••••                          | i    |

|---------------|------------------------------------------------------------------|------|

| Acknowledg    | gements                                                          |      |

| List of Figur | res                                                              | viii |

| List of Table | es                                                               | i    |

| List of Abbi  | reviations                                                       | X    |

| Chapter 1     | Introduction                                                     |      |

| 1.1.          | Research Motivations                                             | 1    |

| 1.2.          | The Organization of Thesis                                       | 2    |

| Chapter 2     | Review of Watermarking Technology                                | 3    |

| 2.1.          | Watermarking Technology Basics                                   |      |

| 2.2.          | ASIC and FPGA Watermarking Technology                            |      |

| 2.3.          | Filter Watermarking Schemes                                      |      |

| 2.4.          | FPGA Watermarking Schemes                                        |      |

| 2.5.          | ASIC Watermarking Schemes                                        |      |

| 2.6.          | Attack Methods Targeting IP Protection Routine with Watermarking |      |

| 2.7.          | Importance of Developing New Watermarking Schemes for DSP        | _    |

|               | Algorithms' FPGA Implementation                                  |      |

| Chapter 3     | FIR Filter Coefficient Modification Watermarking                 | 25   |

| 3.1.          | Watermarking Scheme                                              | 25   |

| 3.2.          | Simulation of Coefficients' LSB Watermarking                     |      |

| 3.3.          | Watermarking Performance Analysis                                |      |

| Chapter 4     | Watermarking Through FPGA Cell Location Constrain                | 31   |

| 4.1.          | Watermarking Scheme                                              |      |

| 4.2.          | FPGA cells' location Watermarking Simulation Procedures and Re   |      |

| 4.3.          | Watermarking Simulations for Other FPGA IPs                      |      |

| 4.4.          | Detail Watermarking Steps for Implementation Optimization        | 51   |

| 4.5.          | Watermarking Performance Analysis                                | 55   |

| Chapter 5     | Summary of Contributions and Possible Future Work                | 60   |

| Appendix A | Timing Report for FIR Filter's Original Implementation              | 63 |

|------------|---------------------------------------------------------------------|----|

| Appendix B | Timing Report for FIR Filter's Implementation with 8-bit Watermark. | 67 |

| Appendix C | Place and Route Report of FIR Filter Before Watermarking            | 71 |

| Appendix D | Place and Route Report of FIR Filter with 8-bit Watermark           | 73 |

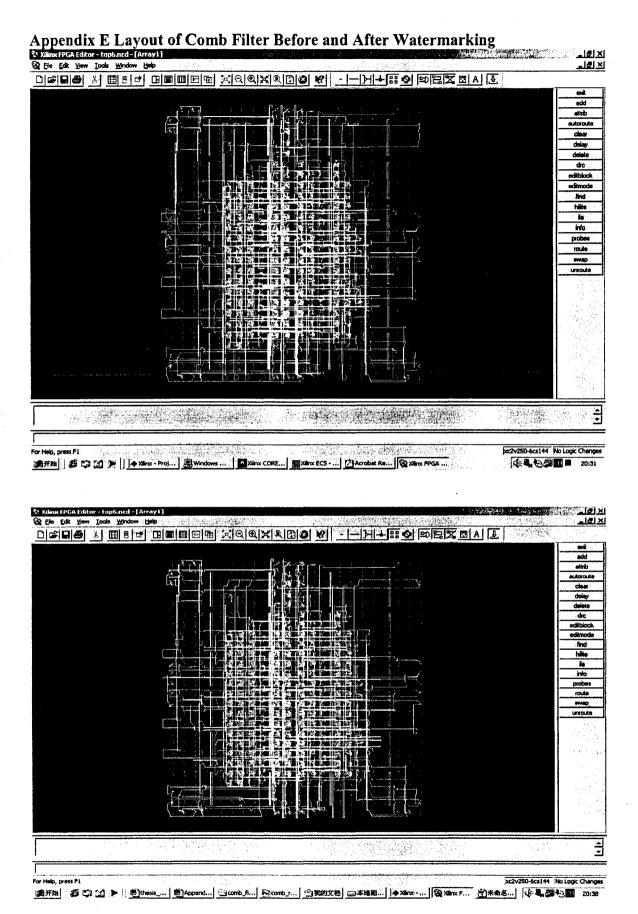

| Appendix E | Layout of Comb Filter Before and After Watermarking                 | 75 |

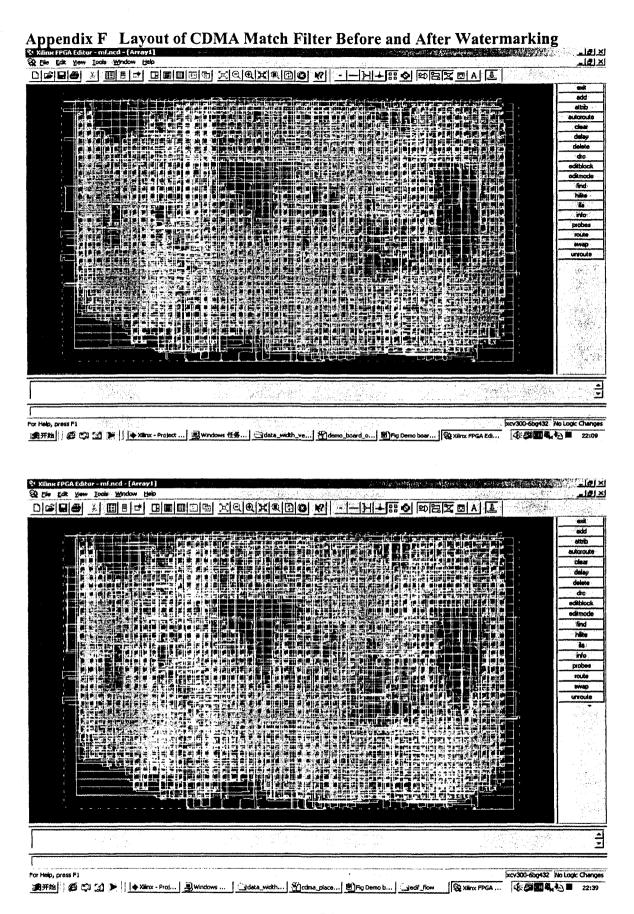

| Appendix F | Layout of CDMA Match Filter Before and After Watermarking           | 76 |

| Appendix G | Layout of DCT Before and After Watermarking                         | 77 |

# List Of Figures

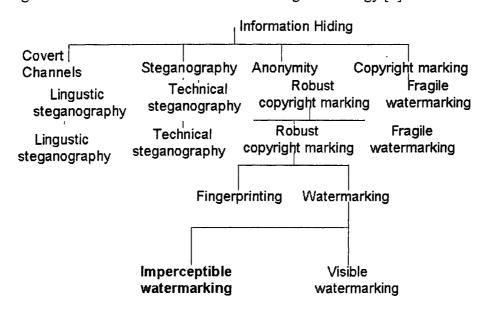

| Figure 1 Classification of Information Hiding Technology                           | 4    |

|------------------------------------------------------------------------------------|------|

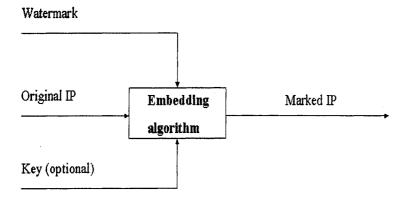

| Figure 2 Watermark Embedding Scheme                                                |      |

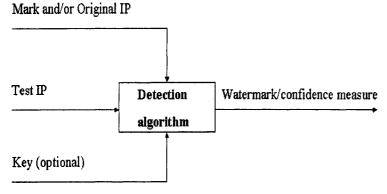

| Figure 3 Watermark Extraction Scheme.                                              |      |

| Figure 4 SOC Design Flow and Different Forms of IP Blocks                          |      |

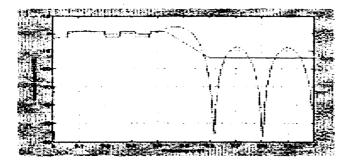

| Figure 5 The Magnitude Response of the Filter with 7-Bit Watermark                 |      |

| Figure 6 Filter Equal Function Replacement                                         |      |

| Figure 7 Who Have Sold the FPGAs to Our Enemy?                                     |      |

| Figure 8 FIR Filter's Magnitude Response Before and After Watermarking,            |      |

| 16-bit Coefficients                                                                | 27   |

| Figure 9 FPGA Layout with 48*16 Slices Array                                       |      |

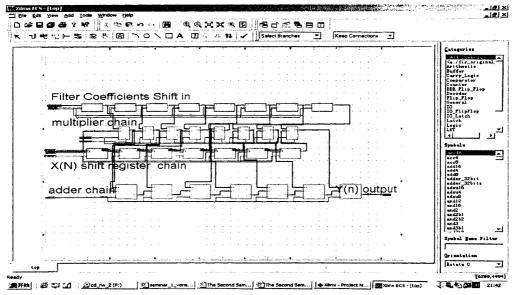

| Figure 10 FIR Filter's Schematic Diagram                                           |      |

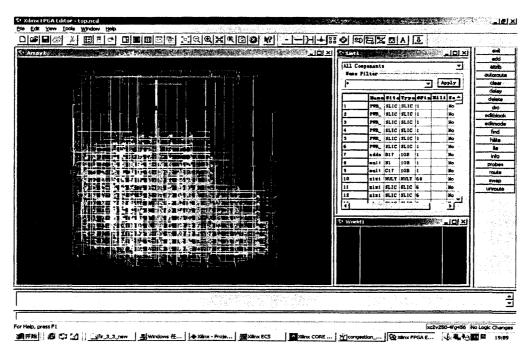

| Figure 11 Original Layout of the FIR Filter, Virtex-II Device                      |      |

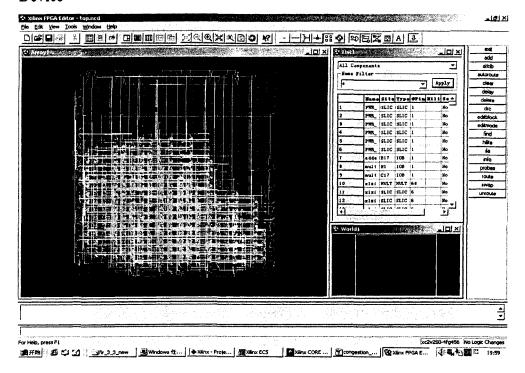

| Figure 12 Watermarked Layout of the FIR Filter, 8-bit Watermark,                   |      |

| Virtex-II Device                                                                   | 39   |

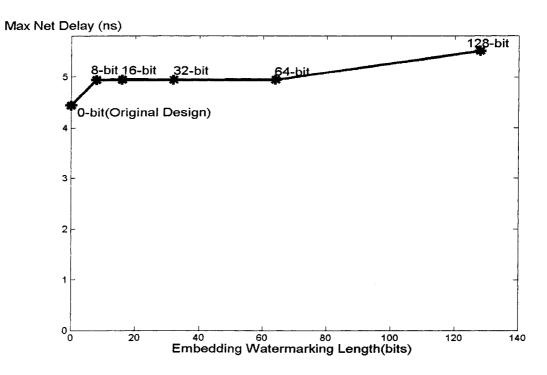

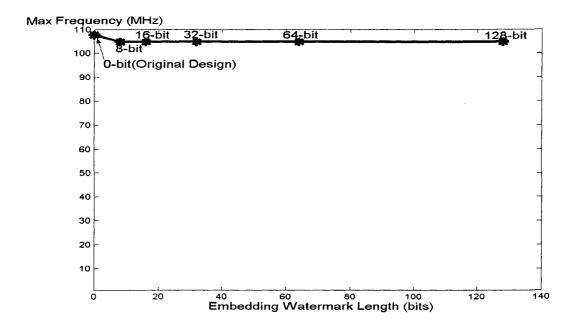

| Figure 13 FIR Filter Watermark Length & Max Net Delay Relation                     |      |

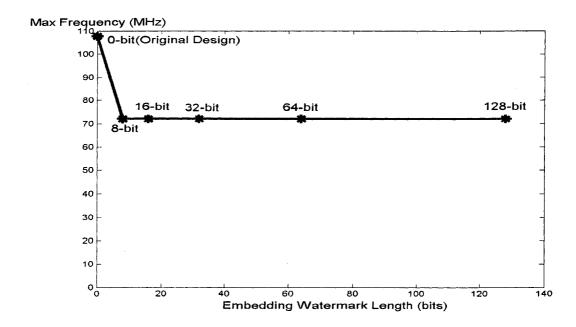

| Figure 14 FIR Filter Embedding Watermark Length and Maxim Frequency Relation       |      |

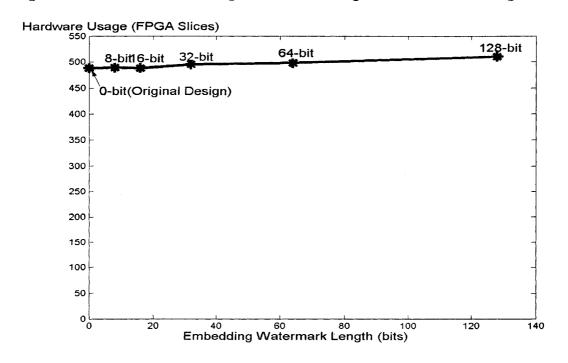

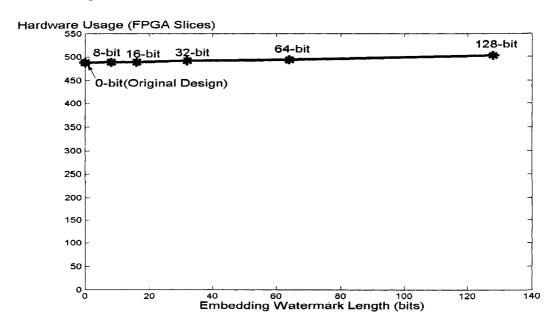

| Figure 15 FIR Filter Embedding Watermark Length and Hardware Usage Relation        | 43   |

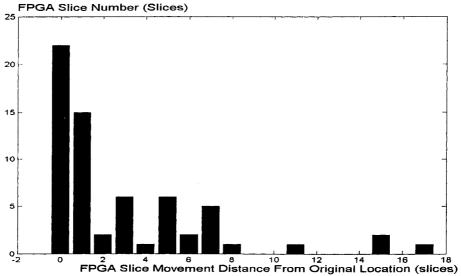

| Figure 16 FIR Filter Cell Movement Distance Distribution, 128-bit Watermark        |      |

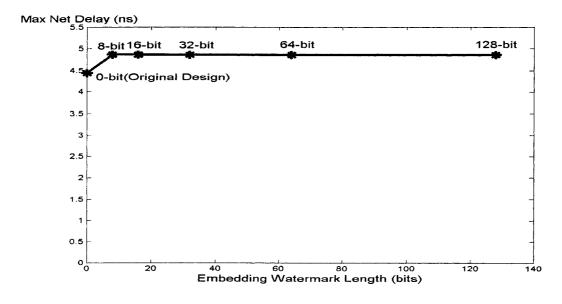

| Figure 17 FIR Filter Watermark Length & Max Net Delay Relation, Reverse Sequence   | e.45 |

| Figure 18 FIR Filter Embedding Watermark Length and Max Frequency Relation,        |      |

| Reverse Sequence                                                                   | 46   |

| Figure 19 FIR Filter Embedding Watermark Length and Hardware Usage Relation,       |      |

| Reverse Sequence                                                                   | 46   |

| Figure 20 FIR Filter Cell Movement Distance Distribution, 128-bit watermark, Rever | se   |

| Sequence                                                                           | 47   |

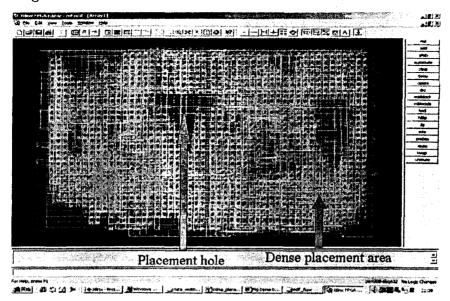

| Figure 21 Holes and Dense Placement Areas of CDMA Match Filter                     | 52   |

| Figure 22 FPGA Cell Selection Strategy                                             |      |

| Figure 23 FIR Filter Placement Diagram with Pre-solidified Layout Modules          | 54   |

# List Of Tables

| Table 1 FIR Filter Coefficients' LSB Watermarking Scheme.                          | 25   |

|------------------------------------------------------------------------------------|------|

| Table 2 Comparisons between Filter Coefficient Modification Watermarking and Cu    |      |

| Watermarking Schemes                                                               | 29   |

| Table 3 FPGA Cell Location Watermarking                                            | 32   |

| Table 4 FIR Filter Cell Location Watermarking, 8-bit, Virtex-II Device             |      |

| Table 5 FIR Filter Cell Location Watermarking, 8-bit, Virtex II-PRO Device         |      |

| Table 6 FIR Filter Cell Location Watermarking, 8-bit to 128-bit, Virtex-II Device  | 41   |

| Table 7 FIR Filter Cell Location Watermarking, 8-bit to 128-bit, Virtex-II Device, |      |

| Reverse Sequence                                                                   | 45   |

| Table 8 Comb Filter Watermarking, 8-bit Watermark                                  | 48   |

| Table 9 CDMA Match Filter Watermarking, 8-bit Watermark                            |      |

| Table 10 DCT Watermarking, 8-bit Watermark                                         |      |

| Table 11 Direct Waveform Synthesizer Watermarking, 8-bit Watermark                 |      |

| Table 12 Board Interface Circuit Watermarking, 8-bit Watermark                     |      |

| Table 13 Comparisons Between FPGA Cell Location Watermarking and State-of-art      |      |

| FPGA/ASIC Implementation Watermarking Methods                                      | . 58 |

# List Of Abbreviations

| ASIC | Application-Specific Integrated Circuit                          |

|------|------------------------------------------------------------------|

| CDMA | Code Division Multiple Access                                    |

| CLB  | Configurable logic block                                         |

| DCT  | Discrete Cosine Transform                                        |

| DSP  | Digital Signal Processing                                        |

| FIR  | Finite Impulse Response                                          |

| FPGA | Field Programmable Gate Array                                    |

| LUT  | Look-up Table                                                    |

| IP   | Intellectual Property                                            |

| IPP  | Intellectual Property Protection                                 |

| PCB  | Printed Circuit Board                                            |

| RAM  | Random Access Memory                                             |

| ROM  | Read Only Memory                                                 |

| SOC  | System On Chip                                                   |

| VHDL | Very-high-speed Integrated Circuit Hardware Description Language |

| VLSI | Very Large Scale Integration                                     |

# Chapter 1: Introduction

#### 1.1. Research Motivations

In the past decade there has been an explosion in the use and distribution of digital contents such as music, movies, electronic books, software, etc, over Internet. Electronic commerce applications and online services have also grown rapidly. But at the same time, digital products and services providers concern themselves about the unrestricted duplication and dissemination of copyrighted materials [1][2]. For example, the lack of effective protection methods for copyright content was the main reason for the delayed introduction of Digital Video Disks (DVDs) [1]. Two complementary technologies have been developed as countermeasures against copyright violation, one is encryption and the other is watermarking [1].

More recently, watermarking has been shown as an effective way to protect intellectual property (IP) of hardware design. In the past few years, the system-on-chip (SOC) technology has made it possible and efficient to design complicated DSP ASICs and FPGAs. The main reason of the success of the SOC technology is the reuse of IP cells. The copyright protection for the IP cells becomes a vital issue for further development of the SOC technology. Encryption technology can provide copyright protection during the transmission of the IP cells from the vendor to the customer. It is obvious that encryption is not enough for the complete IP protection since there is no protection for the IP cells at the customer's end after the customer receives and decrypts the encrypted IP cells. Watermarking technology has been used to complement encryption by embedding a piece of secret information into the original data to generate the watermarked data. It is assumed that the watermarked data still keep their proper content or function and this secret information cannot be removed from the watermarked data without damaging the proper content/function of the data.

Several watermarking schemes for DSP algorithms and/or their ASIC/FPGA designs have been presented since late 1990's [3][4][5][6][7][8][9][[10][11]. However, many of the watermarking schemes have been shown not secure by recent proposals of attacking schemes [8] and not efficient due to large overheads and performance degradation [3][[9][10][11]. Many IP vendors do not use any watermarking scheme and are still trying to find an efficient enough watermarking scheme to be used for the customer's end. Market leaders of ASIC CAD tool and IP providers like Cadence and Synopsys have built focusing ASIC IP's watermarking technology research teams on [4][12][13][14][15][16].

Two pieces of research work have been proposed in this thesis. Firstly, we apply the method of modifying the least significant bit (LSB) to FIR filter and some other DSP algorithms. The simulation results show that the watermarked filter/DSP algorithms have very low magnitude distortion. Secondly, a novel watermarking scheme at FPGA layout layer is proposed. It provides IP protection for FPGA design by utilizing the location information of the used FPGA cells. Compared to the previous methods for FPGA, the proposed watermarking scheme has extremely low overheads and high security strength.

# 1.2. The Organization of Thesis

There are five chapters in this thesis. In Chapter 1, the motivation of developing new DSP algorithms' FPGA watermarking scheme is given. Chapter 2 introduces watermarking technology, watermarking application fields and requirements, current ASIC/FPGA as well as DSP algorithms' watermarking technologies. Chapter 3 presents the filter coefficients' LSB watermarking scheme. Chapter 4 proposes the FPGA cell locations' watermarking scheme. Several FPGA IPs, like FIR filter, comb filter, Code Division Multiple Access (CDMA) match filter, discrete cosine transform (DCT) IPs are used to verify the performance of watermarking scheme. The comparisons between the FPGA cell location modification watermarking scheme and the current available DSP algorithms as well as ASIC/FPGA watermarking schemes are also given in chapter 4. Conclusions are drawn in chapter 5 based on the simulation and analysis presented in the previous chapters. Several possible future work directions are also mentioned.

# Chapter 2: Review of Watermarking Technology

In this chapter, we introduce the concepts of watermarking and information hiding technologies. Then the application fields and general requirements for watermarking technology are discussed. Finally, a review of the current ASIC/FPGA as well as DSP algorithms' watermarking schemes is given. A few watermarking attack methods are also introduced.

## 2.1. Watermarking Technology Basics

#### 2.1.1. Current Copyright Protection Technologies

Great effort has been made for copyright protection in the past years. We have seen some legislation act like Digital Millennium Copyright Act, which was effective on October 28,1998, in U.S.A [1]. The European Union is also preparing similar intellectual property rights protection for digital multimedia products [1]. To provide copyright protection for digital data, two complemented methods have been developed: *encryption* and *watermarking*.

Encryption technology can be used to protect digital data during the transmission from the sender to the receiver. After the receiver has obtained the encrypted data and decrypted it, the decrypted data is no longer protected. Unauthorized copies may be made from the decrypted data. For example, after downloading the music files from the Internet, the customer can use the given key to decrypt the music files and make copies by himself, and then gives them to his friends. The encryption technology cannot protect the copyright anymore [1].

Watermarking techniques can be used to complement encryption by embedding secret information, which is imperceptible to the receiver, called watermark, into the original

data. Watermark is a piece of information embedded within other objects that shows the identity of copyright owner. Watermarks tell us who is the owner of the IP for the object [1][2]. Watermarking is an old technology that has been used for centuries. This technology was firstly developed to protect valuable paper documentations, like bank notes, commercial contracts as well as cash. In this thesis, the discussion of watermarking technology will be limited to the digital watermarking field. For example, if a customer violates copyright protection by making illegal copies of a watermarked image and freely distributing them among his friends, then the original copyright owner can suit this customer and show the copyright information embedded in the image as the watermark in the court [1][2].

#### 2.1.2. Watermarking as a Sub-field of Information Hiding

Figure 1 Classification of Information Hiding Technology [2]

Information hiding includes covert channels, steganography, anonymity and copyright marking, see Figure 1. Covert Channels means the hidden secret channels used by two parties for communication. Anonymity is the technology that investigates the hiding of information sender's true name. Steganography means hiding information in other information. This is the technology to conceal the existence of information within other data [2]. Steganography is different from Cryptography. Cryptography is the technology

to protect the content of messages. People use encryption algorithms to encrypt data and use decryption algorithms to decrypt the encrypted data [2].

We can see there are two subsets under copyright marking, one is robust copyright marking and the other is fragile watermarking. *Robust copyright watermark* is the watermark that is infeasible to be removed or modified without destroying the object at the same time [2].

Fragile watermark is the watermark that will be destroyed as soon as the object is modified too much [2]. We can see that the watermarking technology belongs to robust copyright marking. Watermarking is the technology or procedure to embed a digital watermark into a digital IP and detect/extract it from the digital IP that has been watermarked [2].

Fingerprinting technology also belongs to robust copyright marking. Fingerprint is the serial number information hidden in the original data. Fingerprinting is the technology or procedure to embed fingerprint into the original digital IP and detect/extract it from the digital IP that has been fingerprinted [2]. Fingerprints can enable the intellectual property owners to identify which customer broke his license agreement and supplied the property to unauthorized third parties [2].

This thesis focuses on the imperceptible watermarking method since imperceptible watermark will arouse less suspicion and attacks. Until recently, information hiding technology received much less attention from the research community and industry than cryptography (encryption belongs to cryptography). But this condition has changed. The first academic conference on the watermarking subject was organized in 1996 [2]. The main driving strength is concern over copyright protection. Law enforcement and counter intelligence agencies are also very interested in understanding these technologies so as to detect and trace hidden copyright and serial number information [2]. In this area rapid strides are being made constantly but general theories are still very tentative.

Copyright marking, as opposed to Steganography, has some additional requirement of robustness against possible attacks. Copyright marks can be either visible or invisible,

depending on the specific application case. But most of the literature has focused on invisible (or transparent) digital watermarks that have wider applications [2]. Watermarking in paper is a very old anti-counterfeiting technology; more recent innovations include special ultraviolet (UV) fluorescent inks used in printing traveler's cheques. In this paper, the discussion will focus on digital watermarking techniques.

#### 2.1.3. Watermarking Application Fields

The watermarking technology can be used for the following purposes:

Copyright Protection: The owner can embed a watermark with copyright information in the original data. Under the condition that there is any copyright argument or copyright violation, the original owner can show the copyright information within the watermark to the judge at court [1][2].

Fingerprinting: The copyright owner or IP vender also can embed different watermarks called fingerprints in the copies submitted to different customers. So they can trace the source of illegal copies [1][3][5]. For example, the music publisher can embed different serial number to the CDs that will be sold by different retail agents in different countries. If the music publisher finds some illegal copies of the CD products, the publisher can trace the source of the illegal copy by extracting the watermark.

Copy Protection: The watermark information can stop the copy procedure during unauthorized copy. For example, for some software, there are copy protection codes embedded. When the customer try to make illegal copies, these copy protection bits will make the computer to stop execute the copy instructions [1].

Authentication: Fragile watermarks (watermarks that will be modified or removed without difficulty with the modification of the original data) can be used to check the authenticity of the data. The author of the electronic books can embed large amount of fragile watermarks into the whole electronic book. So if some of the watermarks have been removed, that means some sections of the books have been alternated [1].

#### 2.1.4. Watermarking Embedding and Extraction Schemes

The watermarking procedure is to add watermark that contains copyright information into the original data by using watermark embedding algorithms. The embedded data are the message that one wishes to send secretly. Sometimes secret or public keys are also used to encrypt the original copyright information. The key is used to control the hiding processing so as to restrict detection and/or recovery of the embedded data to parties who know it [2]. After applying the watermarking algorithm we will have the marked data with watermark inside.

Figure 2 Watermark Embedding scheme [2]

Figure 3 Watermark Extraction Scheme [2]

In Figure 3, the watermark inside the IP will be extracted. Let us use the digital photo image as an example. The watermark extraction procedure is to use the watermark and the original image, as well as the image that will be tested. After comparing the original image and the image under test, we can find the watermark inside the tested image, which is the copyright confidence. Other watermark extraction methods are similar to this scheme.

#### 2.1.5. General Watermarking Requirements

A few general requirements for a watermarking scheme have been proposed [1][2][3][4]:

Perceptual Transparency: A watermark is imperceptible if humans cannot distinguish the original data and the data with watermark. Since by comparing the original data and the watermarked data, people can easily find the difference, that is the watermark, we should assume that the customer does not have access to the original data [1].

Payload of the Watermark: This is the amount of the information that can be stored in a watermark. For specific data object, if we can embed more information into the original data, we say this watermark-embedding scheme has higher payload. A good watermark-embedding scheme should provide high payload [1].

Robustness: This refers to the difficulty to remove/modify the watermark without degrading or changing the original data. To remove the watermark, the potential attacker should firstly try to find the watermark. If the watermark is very hard to find, very hard to forgery and very hard to remove, we say that this kind of watermarking scheme has good robustness [1][2][3]. To remove or modify the watermark must require the knowledge of a secret, like the secret key value, the watermarking procedure and watermarking algorithm details. The watermark should survive all attacks that do not degrade the IP's perceived quality. Some attacks include re-sampling, re-quantization, dithering, compression and the combination of them.

Security: The security of watermarking scheme means the watermarking scheme's ability against watermark detection/forgery/modification. We should assume that the method to encrypt and watermark the data is known to the public and the security must lie in the choice of a key [1].

*Independency:* If multiple marks are inserted in a single object, then they should not interfere each other.

Most watermarking applications have a sharp tradeoff between robustness and watermark embedding efficiency. This make a single watermarking scheme meeting the requirements of all applications to be difficult [2]. At the other side, most real case applications do not require all of the properties for general watermarking schemes.

### 2.2.ASIC and FPGA Watermarking Technology

#### 2.2.1. Where We Need to Add Watermark

Figure 4 SOC Design Flow and Different Forms of IP Blocks [17]

# System Level Design(Co-design Level) Algorithmic Design System Level Model System Level Model Software Specification Hardware Specification Coding RTL Model(Soft IP) Sate Model(Firm IP) Layout(Hard IP)

SOC Design Flow and Different Forms of IP Blocks

A watermark can be added at different levels such as algorithm level, architecture level, register level, layout level, etc. At a lower level, payload is usually higher. A watermark can be added at multiple levels to make an attack even harder.

Figure 4 shows the current SOC design flow and different types of IP blocks that need to be protected. For each level, there should be different copyright protection schemes. For watermarking technology, the watermarking schemes of these IPs locating at different levels are also different. The watermark embedded at the higher level will be carried to the lower levels. For example, if we add watermark to the RTL model (soft IP), the watermark will be carried to the lower levels, like gate level and layout level. This is the reason we prefer to add watermark to the design level as high as possible. The reason is if any attacker wants to remove the watermark and get the high level design, he needs to remove the watermark embedded at each lower level, if the attacker can only access the lowest level of IPs.

The watermark embedded at higher level is often easy to be identified and removed, if the IP is provided with high-level form modules. Human beings normally will feel much easier to understand high-level design data. For example, the attacker will feel more comfortable to understand the structure of the software program written in C or Java, comparing to the layout data of all binary format (FPGA bit-stream programming data or ASIC layout data).

#### 2.2.2. The Importance of ASIC/FPGA IP Watermarking

The fast development of system-on-chip technology increases the importance of IP reuse. Now we can integrate the complete system on a single silicon chip that has all the functions of those chips on a printed board produced several years ago. Reusable virtual components or IP blocks are most effective for the purpose of reducing design cycle time, as well as decreasing design risk. IP owners want to make sure that their IP products will not be illegally redistributed. Consumers also want to make sure that the IPs they buy are legitimate. FPGAs become good candidates for fast-to-market products like DSP cores for wireless communication and computer network applications. Distribution of the IP cores through the Internet is the commercial fact but it also increases the risk of IPs being stolen and forgery [17]. The IP provider can use some technologies like JAVA applets and JHDL to protect their IPs during the evaluation of the IPs by potential customers. Based on the JHDL design tool, these JAVA applets allow structure viewing, circuit simulation and netlist generation for some cases. Applets can be customized to provide varying levels of visibility and functionality [18].

Watermark technology is also needed for AISC/FPGA co-design and co-verification, which means from the right beginning there should be considerations for the integration of different types of design blocks (including software codes, digital blocks, analog blocks, as well as IPs with the form of Very-high-speed Integrated Circuit Hardware Description Language (VHDL)/Verilog source code, black box schematic block or layout hard blocks) [17][19]. There should be copyright protection schemes for all these kinds of design IPs.

IP vendors can protect their copyright by encrypting their source codes (VHDL/Verilog) when these codes are sent to the buyers. These modules can be loaded into authorized simulators or synthesis tools without making the source code visible to the system designer who uses the IP blocks. In this case, the CAD tool maintains the safety of the copyright. But in practice, this protection is often broken with attacking the CAD tool (simulators, synthesis tool) directly. We need to find extra methods to protect the design IPs. Watermarking technology has shown its ability for ASIC/FPGA IP protection.

The methods of watermarking for digital images, music and video are quite different from the methods to protect DSP algorithms and ASIC/FPGA designs. The research about the DSP algorithm and ASIC/FPGA watermarking just began several years ago and still is a relatively new area. But we can see this area begin attract more researchers and some market leader ASIC/FPGA design software companies like Cadence that also begins to support such kind of research activities.

#### 2.2.3. ASIC/FPGA Watermarking Evaluation Criteria

Watermarking is a process that hides or embeds data into a design IP that can help deter theft and counterfeiting. The watermark serves as evidence of ownership. A complete ASIC/FPGA IP protection scheme based on watermarking consists of two phases: watermark synthesis and watermark detection [4][12].

The *synthesis* phase is fully characterized by [4]:

- (a) Algorithms translating design features onto a unique watermark

- (b) Tr: the worst case time required to forge and/delete the watermark

- (c) Pu: the odds that a design carries an unintended watermark in part or in its totality.

The detection phase is characterized by [4]:

- (d) Pm: the probability of a detection miss

- (e) Pf=Pu: the probability of a false alarm.

Typical specification of a complete IP protection scheme could be [4]:

Tr >= 2 years, Pu=Pf <= 1E-30 Pm <= 1E-6

To evaluate certain ASIC/FPGA and DSP algorithms' watermarking scheme, some major factors need to be considered. The following factors have combined the requirements presented in [4][12] as well as the general requirements for watermarking schemes [1][2]. These evaluation criteria will be used in the following chapters.

Embedding Efficiency: This item shows the watermarking schemes' efficiency. For example for the same filter, watermarking scheme A can embed maximum 8-bit information and watermarking scheme B can embed 16-bit information, we say watermarking scheme B has better embedding efficiency.

Embedding Cost: This item reflects the effect of the watermarking procedure on the original ASIC/FPGA or DSP algorithm. If the watermarking scheme introduces comparatively small timing delay increase, hardware cost increase, algorithm complexity and/or software computational time's increase, we say this scheme has low embedding cost.

Design Overhead: This item shows the extra time for the design with watermarking steps. If the watermarking steps will add small extra design time, we say this watermarking scheme has low design overhead.

Extraction Cost: This one is related to the difficulty, complicity, as well as the time of watermark extraction. If the extraction procedure needs less effort, for example, does not need complicate test equipments, people having strong electronics background or extra software, we will say this scheme's watermark extraction cost is low.

Extraction Miss Probability: This is the probability that a watermark cannot be extracted. This item equals to Pm.

*Probability of Coincidence*: This item shows the probability that one watermarked IP will carry the whole or partial watermark as another IP that has not been watermarked. The smaller this number, the better. Normally this number should be less than 1E-30 for copyright protection applications. This item equals to Pu and Pf.

Security Strength: This item shows the watermarking scheme's ability against potential attacker's attempt of detecting, counterfeiting and remove of the watermark. The higher the ability, the better the security strength. Also the more transparent the watermark, the better the security strength. The value of Tr is one of the indications of this specification.

Applied Area: This item is related to the application fields of the watermarking scheme. Some watermark schemes can be used for ASICs' IP protection, others are for FPGAs only. Some are for digital designs and others are for analog designs. The wider the applied area, the better the watermarking schemes.

## 2.3. Filter Watermarking Schemes

The following three filter watermarking schemes have been proposed: filter magnitude modification, filter tap's equal-replacement and windowing function watermarking. In this section, the watermarking procedures and the major properties of these three schemes are mentioned.

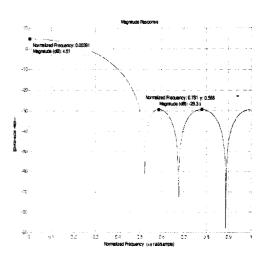

#### 2.3.1. Filter Magnitude Modification [9]:

Firstly, the designer separates the filter stop or pass-band to several equal width zones (i.e., seven zones). Then he modifies the filter magnitude response according to the watermark bits. If the bit is 1, he will decrease the filter magnitude response by x dB (here x is a small number like 0.1). If the bit is 0, he will increase the filter magnitude response by x dB. After that, he uses the modified filter magnitude response as the design constrains input to the design tool. Finally he obtains the filter coefficients. Now the filter's magnitude response decided by the new coefficients will contain the watermark information that is 7-bit as 0110101.

Figure 5 The Magnitude Response of the Filter with 7-bit Watermark [9]:

Watermarking performance analysis for filter magnitude modification scheme:

The embedding efficiency is less than 8 bit/31taps=0.258 bit/tap. The authors do not give out clear number of the maxim number of watermark bits, which can be hidden into the filter's magnitude response. But the authors do mention that for the hiding of 7-bit watermark, the 31-tap filter is not long enough in terms of filter tap number. The filter with 41-taps can be used to embed such 7-bit watermarks. Since the authors divide the filter's pass band's magnitude response and modify the magnitude response, the filter's order may increase. But the authors of [9] do not mention other simulation results with more watermarking bits, the author of this thesis can not exactly evaluate the relation between the watermark length and the filter's order, as well as the hardware cost increase. There is 7% hardware increase for the embedding of 7-bit watermark at algorithm level only.

From [9], the designer needs to re-design the filter for embedding the watermark. So the design overhead is high. The authors of this paper do not mention the watermark extraction flow. It seems that we can plot out the filter's magnitude response and check the magnitude response, then find the watermark bits related to the magnitude ripples. And if the original filter already has magnitude ripples in pass-band, it will be more difficult to extract the watermark from its magnitude response.

The authors of paper [9] do not provide any information about the possible attack mode analysis and security strength analysis. The filter performance degradation is related to the filter magnitude change value. If the filter magnitude change decreases, the filter performance degradation will decrease, but the filter taps number will increase. This scheme adds watermark at algorithm level, the highest level for filter design, so it is hard to be removed from lower level of filter's implementation, like logic, layout or circuit level. This watermarking scheme increases the complexity of filter design. It also increases the order of the filer, since we introduce new ripple constrains to the filter magnitude response, As a result, the hardware cost increases by +7%.

#### 2.3.2. Filter Tap's Equal Function Replacement Method [9]

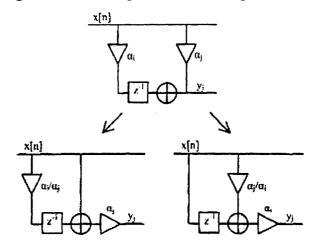

The designer firstly designs the filter with the original performance specification then he replaces the filter taps by using equal filter structure replacement. There are three equal function filter structures, A, B and C. When the watermarking bit is 0, the designer will use B to implement this tap. When the watermarking bit is 1, the designer will use C to implement this tap. When there is no watermark to be embedded, the designer will keep on using A.

Figure 6 Filter Equal Function Replacement [9]

Watermarking performance analysis:

Since the author can use one tap to embed one bit of watermark information, the embedding efficiency is 1 bit/tap. After watermarking, the hardware area increases by 29%, which is primarily due to a higher internal word length. The higher word length is the result of dividing coefficients introduced by equal filter tap function replacements. The increase of hardware area will also increase the power consumption of the filter, since we increase the amount of operations introduced by dividing operations. The design of the filter with watermark needs to replace the standard filter taps with equal functional tap module. This introduces the non-regularity for the filter's hardware design and will increase the time and effort of VHDL coding.

The authors of the paper do not mention the details of how to extract the watermark. The extraction of the watermark needs the extractor to review the filter's implementation layout or logic circuit design or VHDL/Verilog source code, extract the logic functions of

the filter and extract the watermark according to the equal function replacement watermarking rules. This will require considerable time and effort. The probability of coincidence of this kind will be zero if only the author of that paper uses this watermarking method. Since the tap structure of the filters will be all the same if the filter is designed in traditional way.

The authors do not mention the security strength of this method. Layout reverse engineering may be able to remove this kind of watermark, as long as the layout processing technology is visible by the attacker (normally 0.5um or wider metal wire width). This method can be applied to both ASIC and FPGA design. There is no filter response performance degradation, since the authors use equal functional module to do the replacement.

This scheme makes watermarking at algorithm level, so it is hard to remove at the lower levels and there is no degradation of filter response performance. But this method increases hardware cost dramatically by +29. It also makes the filter structure to be not uniform and increases the design time for implementation on ASIC or FPGA.

#### 2.3.3. Windowing Function Watermarking [10][11]

Suppose W(n) is the original windowing function, where  $1 \le n \le N$ .

Firstly the designer adds random noise to W(n) to obtain Wm(n):

$Wm(n)=W(n)+a * r(n),1 \le N$ . Here a is a small number like 0.0001. Then the designer adds watermarking bits c (n) to Wm (n):

$$Wc (n) = \begin{bmatrix} Wm (n), & 1 <= n <= i-1 \\ Wm (n) + b*c(n-i+1), & i <= n <= i+P-1 \\ Wm (n), & i+P <= n <= N/2 \\ -Wc(N+1-n), & N/2+1 <= n <= N. \end{bmatrix}$$

The designer will let b=0.0001. The starting bit of the P-bit watermark code sequence c (n-i+1) is bit i of Wm (n). The sequence Wc (n), n=1,N, is the new window function which contains the watermark information.

Watermarking Performance Analysis:

For a classical windowing function with length n, we can embed n bits of watermark information, so the embedding efficiency is 1 bit/tap. Since the embedding cost is just to add random noise sequence as well as watermark bits to the original windowing function, the embedding procedure is simple and fast at software computational level. The embedding cost is low. There is no design overhead for this method. Since the watermark is added to the windowing function after it has been designed.

The authors do not mention the details of watermark extraction flow. But we can see that the watermark can be extracted by comparing (subtraction operation) the watermarked windowing function with the original windowing function. Then by subtracting the random noise sequence, we can extract the watermark. To do this is simple and fast at software level. The extraction cost is low. The length of the watermark decides the probability of coincidence. For the watermark with length n, it equals to  $1/(2^n)$ .

The authors do not provide detail information about the application fields. But if this method is only carried at algorithm level, the attacker may be able to add extra random noise to the windowing function and remove the watermark. So the security strength is low. Since this method is developed specifically for windowing function, it can be applied to windowing function or similar structure functions. The authors do not mention this method can be applied to other DSP algorithms' ASIC/FPGA implementation or not.

There will be some degree of performance degradation, which is caused by the modification of the windowing function. The degradation is decided by the comparative ratio of the windowing function's modification value and the original function value. This method embeds watermark at algorithm level that is hard to remove at a lower levels. Its watermarking scheme is simple and direct. But this method increases design complexity and the security strength is low.

### 2.4. FPGA Watermarking Schemes

In this section, two kinds of FPGA watermarking schemes are described. The first one uses FPGA spare LUTs to embed watermarking information and the second one is to manipulate the FPGA bit-stream programming data directly.

#### 2.4.1.FPGA Fingerprinting by Using Spare LUTs (look-up-table)

This method for watermarking FPGA uses the unused lookup table (LUT) bits to encode the signature bits. In order to further hide the signature, the constrained configurable logic blocks (CLBs) are incorporated into the design with unused interconnections and neighboring CLB inputs. Each unused LUT bit can be used to encode one bit of the mark. The inputs of the marked CLB are taken from the passing signals in adjacent routing channels and outputs are routed to neighboring don't care inputs. Upon inspection, it is not apparent which CLB has been marked [5][6][20][21].

#### Watermarking Performance Analysis:

From the embedding method, every LUT (look-up-table) can be used to embed 16 bits of watermark [21], so the embedding efficiency is 16 bit/LUT. When the FPGA device has two LUTs in one FPGA slice, the embedding efficiency equals to 32 bit/slice. The embedding cost for this method is not too large. For embedding 7 bits of watermark, the hardware usage increase is less than 1%. [5] The author does not mention the timing delay change before and after watermarking.

To use this method, the designer needs to assign the locations of the unused LUTs, then place and route the original design around these watermarked unused LUTs. The authors of [5] provide the extraction procedure information. The watermark extractor needs to find the locations of the watermarked LUTs and read out the contents of these LUTs. The length of the watermark decides the probability of coincidence. If the length of the embedded watermark is m, the probability of coincidence is  $1/(2^m)$ .

The authors of paper[5] do not give out the analysis of possible attack methods and the security strength of this method. Another paper [8] points out that one attack method

could be used to successfully detect the watermark embedded in this way. Since this watermarking method uses unused LUTs to embed the watermark, there will be no logic change connections between these LUTs and the original logic design. So the attacker may be able to scan the logic changes happening inside the FPGA and separate the unused LUTs whose output has no effected on the logic changes of other parts. Since there is available attach scheme to break this kind of watermarking, new FPGA watermarking method need to be developed.

#### 2.4.2. FPGA Programming Bit-stream Data Watermarking [3]

This FPGA watermarking method involves substituting watermark bits for some of the bits in the configuration bit stream that control multiplexers for the unused CLB outputs. This method involves the modification of the FPGA bit stream programming data. But in practice, this kind of knowledge is not open to the FPGA design engineers. So the application area of this scheme is limited.

## 2.5. ASIC Watermarking Schemes

In this section, several ASIC watermarking methods are mentioned. Compared with FPGA watermarking technology, there are more papers about ASIC watermarking methods. ASIC watermarking methods at different design stages like logic synthesis, gate level and layout level have been proposed.

#### 2.5.1. Finger-marking by Transistor Finger W/L (width/length) Watermarking

In paper [3], the author presents a method called finger marking. It can be applied for integrated circuit design at the physical (layout) design level. The watermark is embedded in the transistor layout, making this method applicable to digital, analog and mixed-signal SOC (system-on-chip) designs [3]. The transistors in the circuit design are uniquely ordered based on their connectivity. The random bit-stream is then embedded into the transistor geometries to serve as an indelible mark in the circuit. If the value of the bit-stream bit is 0, the designer then uses even number of transistor fingers. For example: for a N-transistor with design specification of W/L=300um/5um, he uses 2 parallel

150um/5um fingers. If the value of the bit-stream bit is 1, the designer uses odd number of transistor fingers. For example, for a N-transistor with design specification of W/L=300um/5um, he uses 3 parallel 100um/5um fingers.

This method can be applied to analog circuit design and easy to be understood by the designer. But this watermarking scheme increases the design effort to implement the layout. It is easy to be removed by layout reverse engineering. The reason is that for analogy design, the layout processing technology is much bigger than pure digital designs. It makes it easier for the attacker to observe the layout by optical devices (micorscope, for example). We can extract the circuit diagram from the layout then re-arrange the finger configurations to remove the watermarking information. But this kind of reverse engineering need at nearly the same time to re-design the layout. So this method still has its value.

#### 2.5.2. Hierarchical Watermarking

Charbon [13][14][15] presents a hierarchical watermarking technique for ASIC designs. It involves the unique mapping of design topological information onto a sequence of symbols called a topological signature. His method has limited applicability in designs that use more than just standard cells and lacks robustness analysis[4][12]. Charbon and Torunoglu also present the watermarking technology of sequential functions [22]. This method will impose a digital watermark on the state transition graph of the synchronous circuits [22][23].

#### 2.5.3. Protocols for IP Protection

Protocols for IP protection have also been developed for hiding data at the combinational logic's behavioral synthesis level [16]. This approach involves embedding a watermark as a set of design constrains. The synthesis tool results in solution satisfying both the original design specifications and the additional set of constrains. Constraint-based techniques have been proposed for watermarking at different stages of the VLSI (very large scale integration) design process. This method can be used well for pure-digital layouts, but need to be complemented with another scheme when applied for SOC (for

example, digital-analog-mixed-signal) design. Watermarking protocols added at ASIC layout place and route stage has also been developed [7].

# 2.6. Attack Methods Targeting IP Protection Routines with Watermarking

Several attack methods have been mentioned by different authors [8][17].

An attack method called logic redundancy detection uses logic scan method to scans the logic transitions happening inside the ASIC or FPGA and try to find the redundancy in the design. Then the attacker may be able to locate and remove the redundant logics and the watermark that is implemented by using these redundant logics [8]. Another attack method is finite state machine reduction. This method is trying to reduce the unused transitions in the state machine transitions that have been used to embed watermark [17].

The hardware remove method will physically remove the FPGA and ASIC chip that contains watermark. No existing watermarking scheme can avoid this kind of attack. But this method also makes the attacker away from the usage of the IP. So the copyright protection purpose also has been realized [17].

Other attack methods include encryption system attacks. This one is the attack of the DES and AES cryptographic algorithms. This method is a big challenge of the security of many watermarking schemes. The designer needs to keep an eye on the most advanced technology of encryption. And the attack for ASIC logic synthesis level watermarking tries to extract the logic synthesis constrains that contain watermark information. ASIC layout level reverse engineering is to recover the original circuit design by photographing the layout, then carry human or computer vision detection for layout to logic extraction.

# 2.7. Importance of Developing New Watermarking Schemes for DSP Algorithms' FPGA Implementation

The author selects the DSP algorithm's FPGA implementation's watermarking as the topic

of the thesis. The reason is the DSP algorithm's FPGA implementations are widely used for the consumer electronics as well as telecommunication applications. And the protection of this kind of IPs is important. To show the importance of the FPGA watermarking technology, two real scenarios are used to show its application for FPGA based IPs' fingerprinting and watermarking.

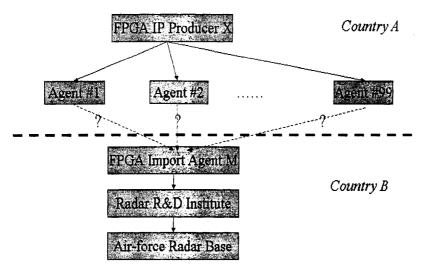

Scenario One: Who Have Sold the FPGA Chips to Our Enemy? Figure 7 Who Have Sold the FPGAs to Our Enemy?

In this scenario, FPGA IP producer X in country A produces FPGA chips and develops high performance DSP IP soft cores. This company also sells FGPAs with DSP IP cores implemented inside. Company X sells their products through 99 retail agents. The customer officers of country A find some mail packages that contained company X's FPGA products. These mail packages are mailed to the electronics retail agent M in country B. But the names and addresses of the sender are false. FBI officers do not find any valuable human being's fingerprints of the sender, except those fingerprints of the post officers'. So the question here is: How the FBI officer can identify which sales agent has involved into the illegal export of the FPGAs? Is there any technology that can make this task much easier?

FPGA watermarking technology is one of the good candidates that can be used to fingerprint the FPGAs. For this kind of applications, the watermark is used as fingerprints

to identify different objects. For our example, there are 99 retail agents and we need at lest 99 different fingerprints to identify all the sales agents. So we need 8-bit watermark length, since 2's power 8 is 128. The idea is each sales agent will receive different watermarks that have been embedded into the FPGAs containing DSP IP cores. Although the functions of these FPGAs are the exactly the same, the watermark is different. And all the watermarks have been documented by company X. In this way, the FBI officer will feel easy to trace the source of the illegal exported FPGAs, by contacting company X and extracting the watermark inside the FPGAs. In chapter 4, the author's implementation results of such kind of 8-bit watermark into some real world DSP IPs are presented. The simulations are used to verify the effect of watermark embedding. The simulation results are encouraging.

#### Scenario Two: Is Mr. Z the DSP IP Thief?

Mr. Z is the technician who works for company X that produces FPGAs and DSP IP cores. Mr. Z's job is to program the FPGA chips with the programming data that is stored in the PC. Mr. Z has ability to read and copy the data. Some sales persons of company X report that another company, company Y, also sales the similar products. So the managers of company X want to know weather Mr. Z has sold the FPGA programming data to company Y. If it is true, how can company X suite Mr. Z, as well as company Y in the court? What kind of evidence will help company X to win the case? Insiders make many high-tech IP stealing cases; the law procedures for these cases are normally long and complicated, partly due to the high-tech background. This makes the suite process time and money consuming.

So is there any technology that will simplify the situation and help to protect the right of the original IP copyright owner? As mentioned in chapter one, watermarking technology can also be used for copyright information embedding. The watermark length of this kind of application will sometime be longer than the watermark's length for fingerprinting usages. For this case, we need 128-bit watermark, to provide strong enough witness for copyright provident. In chapter 4, the simulation results of embedding this kind of 128-bit watermark are presented.

From the review of the current available DSP algorithms' and FPGA implementation watermarking schemes, the area of watermarking for DSP algorithms is relatively new. Although some people have done a lot of innovative work in this area, the proposals they have mentioned still have space for improvement, and the application fields of those watermarking schemes need to be extended. DSP algorithms' FPGA implementation is today's hot-point in the consumer electronics market. FPGAs can provide hardware based fully parallel data processing ability, which makes the FPGAs good candidates for ultrahigh speed and high volume throughout DSP applications, like wireless applications, wide band network, etc.

The filter magnitude modification scheme will introduce 7% hardware increase. The filter taps' equal replacement also have 29% hardware increase after watermarking. And the windowing function' watermarking scheme may be broken by adding false watermark at algorithm level. The current available FPGA watermarking methods also have some limitations. The look-up-table (LUT) watermarking scheme has been broken and the FPGA bit stream modification scheme is not fit for those engineers who do not have knowledge of the format of FPGA bit-stream data. The FPGA producers also announce that they will not expose such bit-stream format information to the public, for confidential reason and IP protection considerations. So to develop new and better watermarking schemes that can protect DSP algorithms' FPGA implementation becomes important.

In chapter 3, the FIR filter coefficients' modification watermarking scheme will be presented. The idea to modify the original image bitmap data and windowing function coefficients has been proposed by several papers [1][10][11]. The author of this thesis extends the application area of this idea to filter and other DSP algorithms. By embedding the coefficients into ASIC and FPGA hardware level, the security strength of watermarking scheme has been increased. In chapter 4, the watermarking through FPGA cell locations' constrain is introduced. This is an innovative watermarking scheme that works at FPGA layout level. This scheme uses the unique layout structure of FPGA to embed watermark information into the FPGA cells' layout coordinates.

# Chapter 3: FIR Filter Coefficient Modification Watermarking

## 3.1. Watermarking Scheme

For the filter coefficients' LSB watermarking scheme, a designer who is responsible for the watermark embedding firstly needs to have the filter's coefficients' file. The designer will use the watermark bits to replace the filter coefficients' LSBs. After embedding of the watermark, the designer needs to run simulation of the filter with the watermarked coefficients. If the simulation results are acceptable, the designer will save the filter's coefficients to a new file and the watermarking flow ends here. For the watermark extraction, the designer needs to read out the filter's coefficients, find the watermark locations and extract their LSBs. After that, he can obtain the watermark bit sequence.

Let a FIR filter design be given by:

Y(k)=A0\*x(k)+A1\*x(k-1)+.....+An-1\*x(k-N-1), where k=0,1,.....,N-1.

Here A0, A1,....., An-1 are filter coefficients. A watermark, for instance, is 10001010.

Watermark embedding process is to replace the filter coefficients' LSBs with the watermark bits. Table 1 shows the procedure of watermark embedding by replacing filer coefficients' LSBs.

Table 1 FIR Filter Coefficients' LSB Watermarking Scheme

| Original Filter Coefficients | Modified Filter Coefficients    | Watermark bits |

|------------------------------|---------------------------------|----------------|

| A0: 1111-1111-1100-0100      | A0: 1111-1111-1100-0101         | 1              |

| A1: 1111-1111-0100-1101      | A1: 1111-1111-0100-110 <b>0</b> | 0              |

| A2: 1111-1111-1010-1001      | A2: 1111-1111-1010-1000         | 0              |

| A3: 0000-0000-1110-1010      | A3: 0000-0000-1110-101 <b>0</b> | 0              |

| A4: 0000-0011-0111-1000      | A4: 0000-0011-0111-1001         | 1              |

| A5: 0000-1000-1101-1111      | A5: 0000-1000-1101-1110         | 0              |

| A6: 0000-0001-1111-1010      | A6: 0000-0001-1111-1011         | 1              |

| A7: 1111-1110-0101-0110      | A7: 1111-1110-0101-011 <b>0</b> | 0              |

The watermark embedding flow of filter coefficient modification is concluded in the following paragraph:

### Schemel.a: Watermark Embedding by Filter Coefficients' Modification

Input: Filter design specifications, watermark bits that need to be embedded

Output: Watermarked filter design

Step 1.Design filter by using filter design specifications.

Step 2:Obtain digitized filter coefficients with specific word length.

Step 3: Modify filter's coefficients' LSBs according to watermark bits

Step 4:Use the modified filter coefficients as the simulation inputs of the filter design tool.

Verify weather the filter's response satisfies the design specification or not.

4.1. If yes, output the watermarked filter's coefficients, stop the procedure.

4.2. If no, check weather we can increase the filter's coefficients or not.

4.2.1.If yes, go to Step 2.

4.2.2.If no, stop the procedure.

The watermark extraction procedure is as following: The watermark extractor first reads out the filter's coefficients and get the LSBs of the coefficients. The binary sequence of the filter coefficients' LSBs is the watermark information. For the improvement of the watermark scheme's security, the filter's coefficients need to be solidified into FPGA hardware by using ROM (read only memory) programming or hard-wiring (connect the signal lines with power or ground). So the designer needs to either read out the filter's coefficients from the ROM or find the internal hard-wired signals' value that are used as filter's coefficients. The following scheme shows the watermark extraction procedures.

# Schemel.b: Watermark Extraction for Filter Coefficients' Modification

Input: Filter coefficients (binary format), watermark bits that need to be verified

Output: Embedded watermark/copyright confidence

Step 1. Extract the filter coefficients LSBs.

Step 2:Read out the LSBs within the specific range where the watermark supposed to be added.

Step 3:Compare the LSBs read from the filter coefficients with the original watermark bits, check how many bits match and get their match rate.

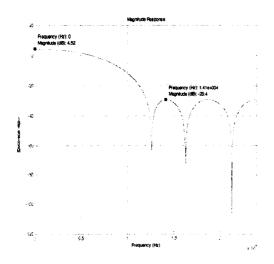

# 3.2. Simulation of Coefficients' LSB Watermarking

To evaluate the effectiveness of proposal one, FIR filter LSBs' watermarking, the author makes the simulation to check the filter performance degradation after watermarking. Commercial filter design and simulation tool is used to carry the simulation. Here are the filter's original design specifications:

Direct form II transposed equal ripple low pass FIR filter

Order: 8

Fs: 48 KHz

Fpass: 9.6 KHz

Fstop: 12 KHz

Wpass: 1 dB

Wstop: 20 dB

The Matlab FDA (Filter Design and Analysis) tool is used to design the original filter and create the filter magnitude response before and after the watermarking. By reading out the magnitude response after watermarking, the difference of Wpass and Wstop of the filter before and after watermarking are less than 0.1 dB.

Figure 8 FIR Filter's Magnitude Response Before (Left) and After Watermarking (Right), 16-bit Coefficients

From the simulation results, we can see that FIR filter coefficients' LSB watermarking method will introduce some degree of performance degradation. The author also carries the simulation for the watermarking of the same FIR filter with 8-bit coefficients. But the simulation results show that the magnitude distortion is too large and unacceptable. So for 8-bit coefficients case, the LSB watermarking scheme introduces too large magnitude response change.16-bit watermarking case works well, with quite small magnitude response degradation. Coefficients' LSB watermarking method can also be extended to other DSP algorithms that have a sequence of parameters.

# 3.3. Watermarking Performance Analysis

To evaluate the watermarking scheme's performance for proposal one, the author uses the evaluation items that have been introduced in chapter 2. The evaluation results will also be used for the summarizations that are made at the end of this chapter.

Embedding Efficiency: 1 bit/tap. From the watermarking method, we can embed one bit of information with each filter coefficient. The maxim number of watermarking bits that can be embedded to the filter's coefficients is equal to the number of the filter's taps.

Embedding Cost: The embedding procedure is simple and direct. The designer can modify the filter's coefficients' LSBs by using normal text editors, like notepad or so. There is no hardware or timing punishment for this method.

Design Overhead: There is no design overhead for the filter design itself. The watermark is added after the filter design has been finished. But the designer who embeds the watermark needs to run simulation after watermarking to verify the filter's performance degradation is acceptable or not.

Extraction Cost: The extraction procedure is direct and simple. People just need to read out the filter's coefficients' LSBs and get the watermark bit sequence.

Probability of Coincidence (Pu): If we use all available coefficients' LSB for watermarking, the probability of coincidence equals to 1/(2^n), where n is the number of filter taps. For the 8-bit watermark and 8-tap filter case, this number equals to 1/256. For 128-bit watermark, this number equals to 3.4E-38.

Security Strength: For those DSP algorithms whose coefficients have been programmed into non-erasable memory (ROM) or implemented through hard wiring, this method provides very strong security strength. The attacker will have no way to remove the watermark embedded inside the coefficients' LSBs unless he removes the ASIC or FPGA chip.

Applied Area: This method can be applied to filter algorithms, as well as DSP algorithms' ASIC/FPGA implementation that have sequential parameters. The filter coefficients or other parameters should be solidified into the hardware.

Filter Performance Degradation: The filter performance degradation is decided by the filter coefficients' word-length. For 16-bit FIR filter case, the magnitude degradation is less than 0.1dB.

Probability of Detection Miss (Pm): From the watermark detection procedure, we can see that the probability of a detection miss is 0. The extractor can always successfully extract the watermark information by reading out the filter's coefficients' LSBs.

Table 2 Comparisons between Filter Coefficient Modification Watermarking and Current Filter Watermarking Schemes

|                | Magnitude    | Tap's Equal | Windowing    | Filter Coefficient |

|----------------|--------------|-------------|--------------|--------------------|

|                | Modification | Replacement | Function     | Modification       |

|                |              |             | Watermarking | Watermarking       |

| Filter         | Medium       | Small       | Small        | Small              |

| Performance    |              |             |              |                    |

| Degradation    |              |             |              |                    |

| Hardware       | +7%          | +29%        | N/A          | 0%                 |

| Usage Increase |              |             |              |                    |

| Design         | High         | Medium      | Low          | Low                |

| Overhead       |              |             |              |                    |

| Extraction     | Low          | Medium      | Low          | Medium             |

| Cost           |              |             |              |                    |

| Probability of | Low          | Low         | Low          | Low                |

| Coincidence    |              |             |              |                    |

| Security       | Medium       | Medium      | Low          | High               |

The proposed filter coefficient's modification watermarking scheme shows better performance than other current available filter watermarking schemes with most performance items. The filter's hardware usage increase is 0% and is the major strong point for this new proposal. The design overhead is also low due to little additional design effort required for watermark embedding. The probability of coincidence is low due to the large amount of watermark information that can be embedded inside the filter's coefficients. The security strength is quite high because of the hardware solidation of the watermark information, so to remove the watermark is physically impossible. All in all, the proposed filter coefficients' modification watermarking scheme shows good watermarking performance and has good potential for practical DSP algorithms' watermarking.

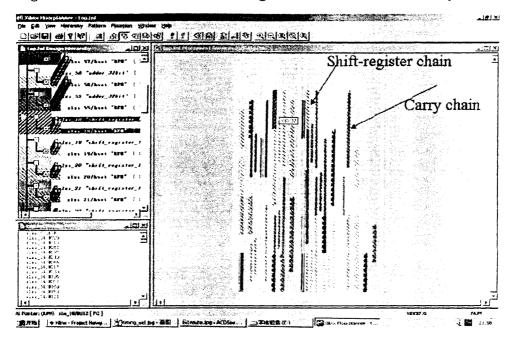

# Chapter 4: Watermarking Through FPGA Cell Location Constrain

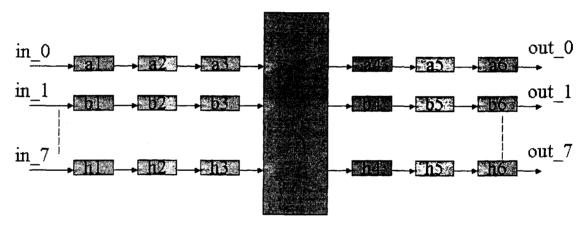

The FPGA cell location constrain watermarking scheme uses the FPGA cells' x and y coordinates to embed the watermark information. This method belongs to the physical constrain watermarking method. By doing so, each selected FPGA layout cell for watermarking can embed 2 bits of information. Several real world IPs like FIR filter, CDMA match filter, discrete cosine transform (DCT) are used to embed 8-bit watermark. The simulation results are used to verify the watermarking performance. Varied length watermark embedding are carried for the FIR filter to study the relationship between design overhead and watermark length.

# 4.1. Watermarking Scheme

The watermarking flow for this scheme is firstly set up some kind of watermark embedding rules. Then the designer needs to select the FPGA layout cells that will be used for watermarking. After that, the designer makes the original implementation of the IP without watermarking. After this step, the selected FPGA cells will be moved according to the watermarking rules. And the FPGA implementation procedure will be carried again with these new layout location constrains. The finished layout of the FPGA will contain the watermark information that the designer has embedded by constraining the cells' layout locations.

Let a FIR filter design be given by:

Y(k)=A0\*X(k)+A1\*X(k-1)+....+An-1\*X(k-N-1), where k=0,1,...N-1.

Suppose we need to embed a watermark consists of 8 bits as 10001010. Let the RAM (random access memory) cells to store Ai be RAM\_i, i=0,1,...,7. A RAM cell in FPGA layout can be identified by its coordinates (x, y). The watermark embedding rules are described as following:

If the bits are 00, we choose both x and y as even.

If the bits are 01, we choose x as even and y as odd.

If the bits are 10, we choose x as odd and y as even.

If the bits are 11, we choose both x and y as odd.

Table 3 shows the procedure of embedding watermark to RAM cells' location coordinates.

**Table 3 FPGA Cell Location Watermarking**

| RAM_i for Storing Ai | Watermarking Bits | New Location of the     |

|----------------------|-------------------|-------------------------|

|                      |                   | Chosen RAM Cell: (x, y) |

| RAM_0                | 1                 | (1,4)                   |

|                      | 0                 |                         |

| RAM_1                | 0                 | (4,4)                   |

|                      | 0                 |                         |

| RAM_2                | 1                 | (3,2)                   |

|                      | 0                 |                         |

| RAM_3                | 1                 | (3,0)                   |

|                      | 0                 |                         |

Figure 9 FPGA Layout with 48\*16 Slices Array

For FPGA devices, the whole layout is divided into certain number of slices. (see figure 9) There are route path between slices. Each slice has some kind of logic resources, like 16-bit RAMs, look-up tables, D-type flip-flops and so on. Different types of FPGA devices will have different number of slices available, as well as the logic cells' type and amount within each slice. For watermarking purpose, we can use the logic cells like 16-bit RAM, D-type flip-flop or other kind of logic cells to embed the watermark information. The selection of the cells should satisfy that each cell used for watermarking does not occupy more than one FPGA slice.

## Scheme 2.a. Watermark Embedding Flow of FPGA Cell Location Modification

Input: Original FPGA logic and layout design and design specifications, watermark bits need to be embedded

Output: Watermarked FPGA layout design

Step 1.Try to find FPGA layout RAM cells that have sequential relations from the logic view.

- 1.1.If we can find, from these RAM layout cells,

- 1.1.1.Try to find layout cells that occupy less than 1/4 FPGA slices. If we can find them, go to step 2.

- 1.1.2.Try to find layout cells that occupy less than or equal 1 FPGA slices. If we can find them, go to step 2.

If we cannot, stop the procedure.

- 1.2. If we cannot, stop the procedure.

- Step 2. Select layout cells locating at loose place and route area.

- 2.1.From the cells we find in step 1,try to find those cells locating at unused place and route areas.

- 2.1.1.If we can find them, go to step 3.

- 2.1.2.If we cannot, go to step 2.2.

- 2.2.From the cells we find in step 1,try to find those cells locating at loose place and route areas.

- 2.2.1. If we can find them, go to step 3.

- 2.2.2. If we cannot, use the cells we find in step 1 and go to step 3.

- Step 3. From the layout cells we find in step 2, select layout cells locating at parallel logic paths.

- 3.1. If we can find them, go to step 4.

- 3.2. If we cannot, use the cells we find in step 2 and go to step 4.

- Step 4.From the layout cells we find in step 3, select layout cells locating at non-critical logic paths.

- 4.1.If we can find them, go to step 5.

- 4.2. If we cannot, use the layout cells we find in step 3 and go to step 5.

- Step 5.For every selected watermarking cell, try to find new location for re-locating that satisfies watermarking bit and watermarking rules.

- 5.1. Try to find spare layout slice within one slice distance.

- 5.1.1.If we can find it, move the layout cell to the new location. Go to step 6.

- 5.1.2.If we cannot, try to find spare layout slice within two slices distance.

If we can find it, move the layout cell to the new location. Go to step 6.

- 5.1.n.If we cannot, try to find spare layout slice within n slices distance. Here n is the largest slice number of possible movement.

If we can find it, move the layout cell to the new location. Go to step 6.

- 5.2.If we cannot find it, try to swap this layout cell with another layout cell that is not selected as watermarking cell and within one slice location.

- 5.2.1. If we can find it, move the layout cell to the new location. Go to step 6.

- 5.2.2.If we cannot, try to find such layout cell within two slices distance.

If we can find it, move the layout cell to the new location. Go to step 6.