#### University of Windsor

# Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

1993

# BiCMOS implementation on DSP arithmetic blocks.

Henry Hin Hai. Chan University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Chan, Henry Hin Hai., "BiCMOS implementation on DSP arithmetic blocks." (1993). *Electronic Theses and Dissertations*. 1295.

https://scholar.uwindsor.ca/etd/1295

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontano K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Oritario) K1A 0N4

Your fam Loren reference

Cur he Note elerence

#### NOTICE

# The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

**AVIS**

La qualité de cette microforme

If pages are missing, contact the university which granted the degree.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments. La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# **Canadä**

# BICMOS IMPLEMENTATION ON DSP ARITHMETIC BLOCKS

by

Henry Hin Hai Chan

#### A Thesis

Submitted to the Faculty of Graduate Studies through the Department of Electrical Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada April, 1993

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Figure flags - Linters restatement of

Our file. Notice reference

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-83059-X

|                                               | . 1             |                                                    | .                 | $O_{1a}$                                      |                      |                                         |                          |

|-----------------------------------------------|-----------------|----------------------------------------------------|-------------------|-----------------------------------------------|----------------------|-----------------------------------------|--------------------------|

| Name                                          | <u> </u>        | earn Him                                           | 1-1a.             | Lhan                                          |                      |                                         |                          |

| Directorion Abstract                          | s International | is arranged by broad                               | , general sub     | pject categories. Please                      | select the or        | ne subject which mo                     | ost                      |

| nearly describes the                          | content of you  | ir dissertation. Enter the                         | e correspond      | ling four-digit code in                       | the spaces p         | rovided.                                |                          |

| •                                             | 11. 00          | B. CMOS                                            | / <del>}</del>    | <del></del>                                   | ĺ                    | 0544                                    | I I.N I.I                |

|                                               | V               | 5. (MO)                                            | Ticith            | ritic UTOCK                                   | ١                    |                                         | OIVII                    |

| <u>=                                    </u>  |                 | SUBJECT TE                                         | RM                | , (                                           | •                    | SUBJECT CODE                            |                          |

|                                               | تحرب ر          | Andread Council                                    | المندين كالم      | والعنا كالمرسوا                               | T. 60                |                                         |                          |

| Subject Categories                            | 5               |                                                    |                   | $\mathcal{G}$                                 | - Ci                 |                                         |                          |

| •                                             |                 |                                                    |                   |                                               | _                    |                                         |                          |

| THE HUMAN                                     | ITIES AN        | D SOCIAL SCIE                                      | NCE5              |                                               |                      |                                         |                          |

| COMMUNICATIONS AND                            | THE ARTS        | Psychology                                         | 0525              | PHILOSOPHY, RELIGION                          | AND                  |                                         | 0579                     |

| Architecture                                  | 0729            | Reading                                            | 0535              | THEOLOGY                                      |                      |                                         | 0581<br>0582             |

| Art History                                   | 03//            | Religious<br>Sciences                              |                   | Philosophy<br>Religion                        | 0422                 | Block                                   | 0328                     |

| Dance                                         | 03/8            | Secondary                                          | 0533              | General                                       | 0318                 | African                                 | 0331<br>and Oceania 0332 |

| Fine Arts                                     | 0357            | Social Sciences<br>Socialogy of                    | 0340              | Biblical Studies<br>Clargy                    | 0321                 | Canadian                                | 0334                     |

| lournalism                                    | 0391            | Special                                            | 0529              | History of                                    | 0.320                | European                                | 0335                     |

| Library Science                               | 0399            | Technology                                         | 0710              | Philosophy of<br>Theology                     | 0322<br>0469         | Middle Eastern .                        | 0333                     |

| Music                                         | 0413            | Tests and Measurements Vocational                  | ,0288             |                                               |                      | United States<br>History of Science     | 0337                     |

| Speech Communication<br>Theater               | 0465            |                                                    |                   | SOCIAL SCIENCES American Studies              | 0323                 | Low                                     | 0398                     |

|                                               |                 | LANGUAGE, LITERATURE                               | AND               | Anthropology                                  |                      | Political Science<br>General            | 0615                     |

| General                                       | 0515            | LINGUISTICS                                        |                   | Archoeology<br>Cultural                       | 0324                 | International Lav                       | w and                    |

| Administration                                | 0514            | Language<br>General                                | 0679              | Physical                                      | 0327                 | Relations                               | 0616<br>ation0617        |

| Adult and Continuing                          | 0516            | Ancient<br>Linguistics                             | 0289              | Business Administration General               |                      | Recreation                              | 0814                     |

| Agricultural                                  | 0273            | Modern                                             | 0291              | Accounting                                    | 0272                 | Social Work<br>Sociology                |                          |

| Bilingual and Multicultural Business          | 0282            | Literature<br>General                              | 0401              | Bonking                                       |                      | General                                 | 0626                     |

| Community College                             | 0275            | Classical                                          | 0294              | Marketing<br>Canadian Studies                 | 0338                 | Criminology and                         | d Penology 0627<br>0938  |

| Curriculum and Instruction<br>Early Childhood | 0518            | Comparative<br>Medieval                            | 0295              | Canadian Studies<br>Economics                 | 0385                 | Ethnic and Raci                         | 0938<br>ol Studies 0631  |

| Elementary                                    | 0524            | Modern                                             | 0298              | General                                       | 0501                 | Individual and F                        |                          |

| Finance                                       | 0519            | African                                            | 0316              | Agricultural                                  | 0503                 | Industrial and La                       | abor                     |

| Health                                        | 0680            | Asion                                              | 0305              | Finance                                       | 0508                 | Relations                               | 0629<br>al Walfare 0630  |

| Higher                                        | 0520            | Canadian (English)<br>Canadian (French)<br>English | 0352              | History                                       | 0509                 | Social Structure                        | and                      |

| Home Economics                                | 0278            | English                                            | 0593              | Theory                                        | 0511                 | Development                             |                          |

| Industrial<br>Language and Literature .       | 0279            | Germanic<br>Latin American                         |                   | Folklore<br>Geography                         | 0358                 | Transpondition                          | 0709                     |

| Mathematics                                   | 0280            | Middle Eastern                                     | 0315              | Gerontology                                   | 0351                 | Urban and Regiona                       |                          |

| MusicPhilosophy of                            | 0998            | Romance                                            | 0313              | History<br>General                            | 0578                 | *************************************** |                          |

| Physical                                      | 0523            | Signif Blig that thiobs                            |                   |                                               |                      |                                         |                          |

|                                               |                 |                                                    |                   |                                               |                      |                                         |                          |

| THE CCIENC                                    | EC AND          | ENGINEERIN                                         | ic                |                                               |                      |                                         |                          |

| THE SCIENC                                    | ES ARD          | ERGUNEERIN                                         |                   |                                               |                      |                                         |                          |

| BIOLOGICAL SCIENCES                           |                 | Geodesy                                            | 0370              | Speech Pathology                              |                      | Engineering                             | 0537                     |

| Agriculture<br>General                        | 0473            | Geology<br>Geoplysics                              | 0373              | Toxicology<br>Home Economics                  | 0386                 | Aerospace                               | 0537                     |

| Agronomy                                      | 0285            | Hydrology                                          | 0388              | PHYSICAL SCIENCES                             |                      | Agricultural                            | 0539<br>0540             |

| Animal Culture and Nutrition                  | 0475            | Mirreralogy                                        | 0345              |                                               |                      | Biomedical                              | 0541                     |

| Animal Pathology                              | 0476            | Paleoecology                                       | 0426              | Pure Sciences<br>Chemistry                    |                      | Chemical                                | 0542<br>0543             |

| Food Science and                              | 0359            | Paleontology<br>Paleozoology                       | 0985              | General                                       | 0485                 | Electronics and                         | Electrical 0544_         |

| Technology<br>Forestry and Wildlife           | 0478            | Polynology<br>Physical Geography                   | 0427              | Agricultural<br>Analytical                    | 0486                 | Heat and Them                           | noctynamics0348          |

| Plant Culture<br>Plant Pathology              |                 | Physical Geography<br>Physical Oceanography        | 0368              | Biochemistry                                  | 0487                 | Industrial                              | 0545                     |

| Plant Physiology                              | 0817            | HEALTH AND ENVIRONM                                |                   | Inorganic<br>Nuclear                          | 0738                 | Marine                                  | 0547<br>co0794           |

| Range Management Wood Technology              | 0777            | SCIENCES                                           | IENIAL            | Organic                                       | 0490                 | Mechanical                              | 0548                     |

| Riotogy                                       |                 | Environmental Sciences                             | 0768              | Pharmaceutical<br>Physical                    | 0491                 | Metallurgy                              | 0743                     |

| General                                       | 0306<br>0287    | Health Sciences                                    | 0544              | Polymer                                       | 0495                 | Nuclear                                 | 0551<br>0552             |

| Biostatistics                                 | 0308            | General<br>Audiology                               | 0300              | Radiation                                     | 0/34                 | Pockoging                               | 0549                     |

| Botany                                        | 0309            | Chemotherapy                                       | 0992              | Physics                                       |                      | Sanitary and M                          | 0765<br>Junicipal0554    |

| Ecology                                       | 0329            | Dentistry                                          | 0350              | General<br>Acoustics                          | 0986                 | System Science                          | 0790                     |

| Entomology                                    | 0353            | Hospital Management<br>Human Development           | 0769              | Astronomy and                                 |                      | Operations Resear                       | 0428<br>ch0796           |

| Limnology<br>Microbiology                     | 0793            | trumon Development                                 | 0758              | Astrophysics<br>Atmospheric Science           | 9090                 | Plastics Technology                     | /0 <u>79</u> 5           |

| Microbiology<br>Molecular                     | 0410<br>0307    | Immunology<br>Medicine and Surgery                 | 0564              | Atomic                                        | 0748                 | <del>-</del> -                          | 0994                     |

| Neuroscience                                  | 0317            | Mental Health<br>Nursing                           |                   | Electronics and Elect<br>Elementary Particles | tricity0007<br>. and | <b>SACHOTOGA</b>                        | 0/01                     |

| Oceanography<br>Physiology                    | 0416            |                                                    |                   | High Energy                                   | 0798                 | Behavioral                              | 0621                     |

| Registron                                     | 0821            | Obstetrics and Gynec<br>Occupational Health        | ology 0380<br>and | Fluid and Plasma<br>Molecular                 | 0759                 | Clinical                                | 0622                     |

| Veterinary Science<br>Zoology                 | 0778            | Therapy<br>Ophtholmology                           | 0354              | Nuclear                                       | 0610                 | Developmental<br>Experimental           | 0620<br>0623             |

| Ricobusics                                    |                 | Ophtholmology                                      | 0381<br>0571      | Optics<br>Radiation                           |                      | Industrial                              | 0424                     |

| General                                       | 0786            | Pathology<br>Pharmacology                          | 0419              | Solid State                                   | 0611                 | Physiological                           | 0625<br>0989<br>0349     |

|                                               |                 | Pharmocy<br>Physical Therapy                       |                   | Statistics                                    | 0463                 | Psychobiology                           | 0349                     |

| EARTH SCIENCES Biogeochemistry                | 0425            | Public Health                                      | 0573              | Applied Sciences Applied Mechanics            | 0344                 | raycnomemos                             | 0632<br>0451             |

| Geochemistry                                  | 0996            | Radiology                                          | 0574              | Computer Science                              | 0984                 |                                         | <b>A</b>                 |

|                                               |                 |                                                    |                   |                                               |                      |                                         | ₩.                       |

# Henry Hin Hai Chan 1993

© All Rights Reserved

#### **ABSTRACT**

This thesis presents an improved VLSI architecture to perform different arithmetic operations, multiplication, division and square rooting, along with addition and subtraction. The architecture is highly regular, requires only three control bits to choose among five different operations. Through the use of a redundant binary number system and pipelining, the execution time for each operation is identical and is independent of the wordsize of the array. Moreover, the improved architecture is capable of being implemented using the dynamic switching tree technique. Finally, the improved architecture has been designed utilizing a 0.8 micron BiCMOS technology and has a throughput rate of 100 Megasamples per second for each operation.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere thanks and appreciation to Dr. G.A. Jullien and Dr. W.C. Miller for their tremendous support and guidance throughout the progress of this theis. I would like to give my special thanks to Bruce Erickson for his help and experiences. Thanks also go to Andy Hung, Raymond Lei, Sam Lai and H.M. Chan for their help and stay at school during night time. Special thanks must be given to Teresa Chan for her understanding, patience and support during the writing process. Last but far from least, I would like to thank my parents and my brother, Mr. & Mrs. Tsang and Peter Tsang, for without them none of this would be possible.

# TABLE OF CONTENTS

| ABSTRACT    |                                                      | IV   |

|-------------|------------------------------------------------------|------|

| ACKNOWLE    | DGEMENTS                                             | v    |

| LIST OF FIG | URES                                                 | ix   |

| LIST OF TAE | BLES                                                 | xiii |

| CHAPTER 1   |                                                      |      |

| INTRO       | DDUCTION                                             | 1    |

| 1.1         | Introduction                                         | 1    |

| 1.2         | Organization Of Thesis                               | 2    |

| CHAPTER 2   |                                                      |      |

| REDU        | NDANT NUMBER SYSTEMS AND ALGORITHMS                  | 4    |

| 2.1         | Introduction                                         | 4    |

| 2.2         | Signed Digit Number Representation[6]                | 5    |

|             | 2.2.1 Signed Binary Number Representation            | 7    |

|             | 2.2.2 Redundant Binary Adder                         | 8    |

|             | 2.2.2 Modified Redundant Binary Adder                | 9    |

|             | 2.2.3 (+,-) Scheme SBNR Adder                        | 16   |

|             | 2.2.4 Conversion Between Redundant Binary And Binary |      |

|             | Numbers                                              | 17   |

|             | 2.2.5 Redundancy Overflow                            | 20   |

| 2.3         | Redundant Computer Arithmetic                        | 20   |

|             | 2.3.1 Division                                       | 21   |

|             | 2.3.2 Square Root                                    | 23   |

|             | 2.3.3 Multiplication                                 |      |

| 2.4         | Summary                                              | 28   |

## **CHAPTER 3**

| VLSI A    | ARCHITECTURES FOR ARITHMETIC OPERATIONS   | 30 |

|-----------|-------------------------------------------|----|

| 3.1       | Introduction                              | 30 |

| 3.2       | Bit-Level Systolic Array                  | 31 |

| 3.3       | Add-Shift-Extract Configuration           | 33 |

| 3.4       | The Unified Algorithm                     | 34 |

|           | 3.4.1 Rationale For Redundant Arithmetic  | 35 |

|           | 3.4.2 Unified Algorithm                   | 37 |

| 3.5       | Original Architecture                     | 38 |

|           | 3.5.1 Redundant Addition                  | 39 |

|           | 3.5.2 Architecture                        | 41 |

| 3.6       | Improved Architecture                     | 47 |

|           | 3.6.1 The Unified Algorithm               | 48 |

|           | 3.6.2 Redundant Addition                  | 50 |

|           | 3.6.3 Architecture                        | 52 |

| 3.7       | Comparisons                               | 60 |

| 3.8       | Dynamic Switching Tree                    | 61 |

| 3.9       | Summary                                   | 62 |

| CHAPTER 4 |                                           |    |

| VERI      | LOG MODELING AND VLSI IMPLEMENTATIONS     | 63 |

| 4.1       | Introduction                              | 63 |

| 4.2       | Designing With Verilog                    | 63 |

|           | 4.2.1 Behavioral Modeling Of Architecture | 64 |

|           | 4.2.2 Mixed Structural And Behavioral     | 70 |

| 4.3       | Structural Architecture                   | 71 |

| 4.4       | Hspice Simulation                         | 74 |

| 4.5       | Summary                                   | 78 |

#### **CHAPTER 5**

| CONCL         | USIONS AND FU               | TURE DIRECTIONS                                  | 79            |

|---------------|-----------------------------|--------------------------------------------------|---------------|

| 5.1           | onclusions                  |                                                  | 79            |

| 5.2 F         | uture Direction             | ns                                               | 81            |

| REFERENCES    |                             |                                                  | 82            |

| APPENDIX A    | BEHAVIORAL M                | MODEL OF IMPROVED ARCHITEC                       | CTURE 85      |

| APPENDIX B    | SBNR-BINARY                 | CONVERTER AND ITS OUTPUT                         | 96            |

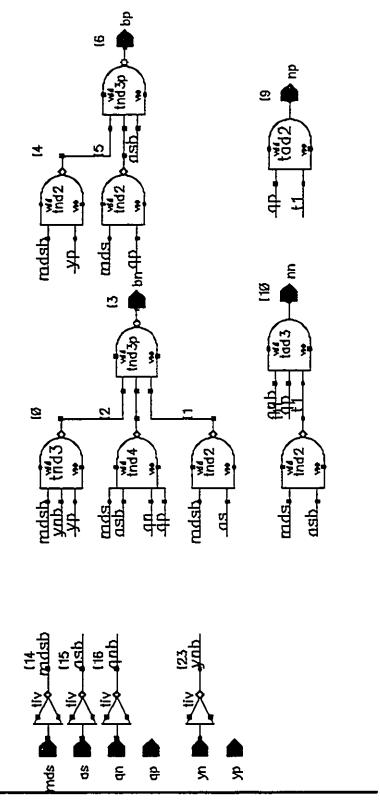

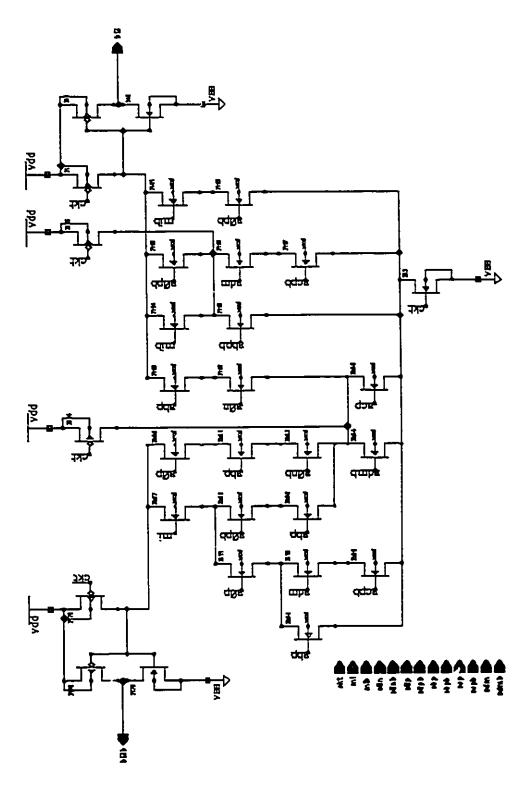

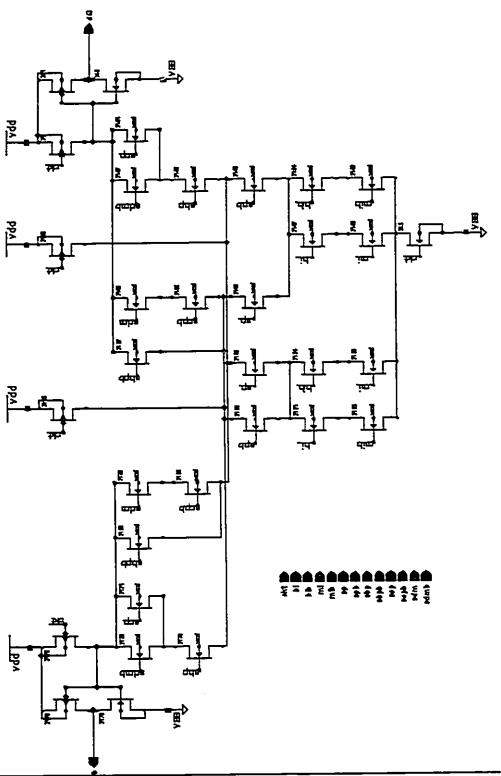

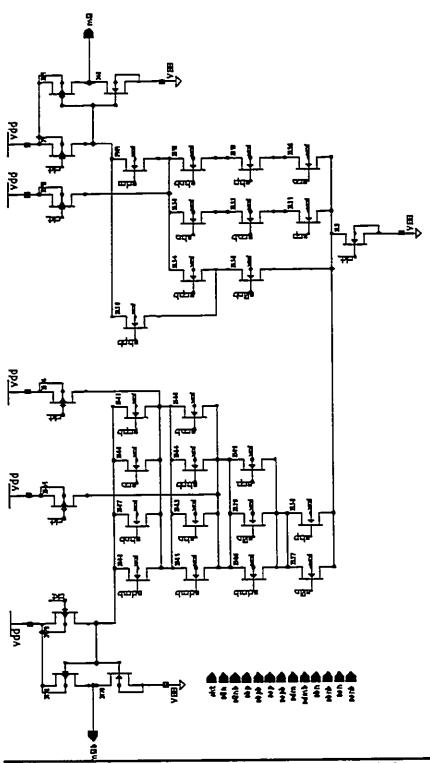

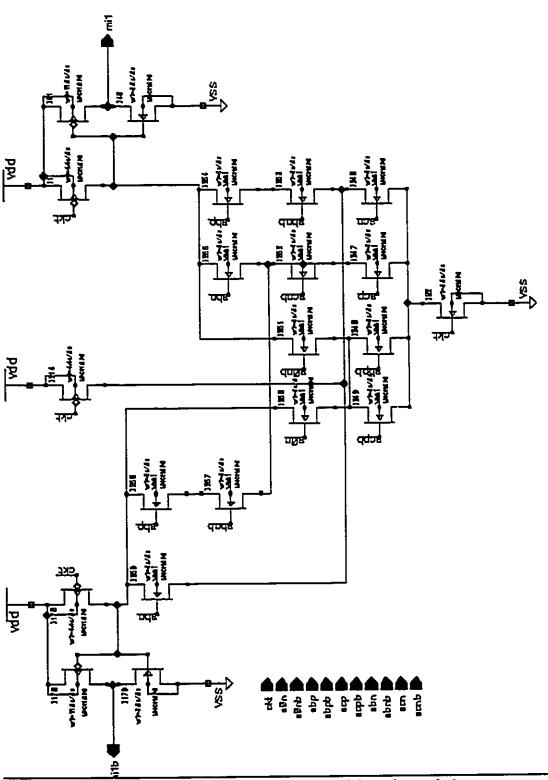

| APPENDIX C    |                             | AGRAMS OF IMPROVED ARCHI<br>ARCHITECTURE         | TECTURE       |

| APPENDIX D    | MASK LAYOUT<br>ORIGINAL ARC | OF IMPROVED ARCHITECTURE                         | : AND<br>129  |

| APPENDIX E    | VERILOG NETL                | IST OF IMPROVED ARCHITECTU                       | JRE 132       |

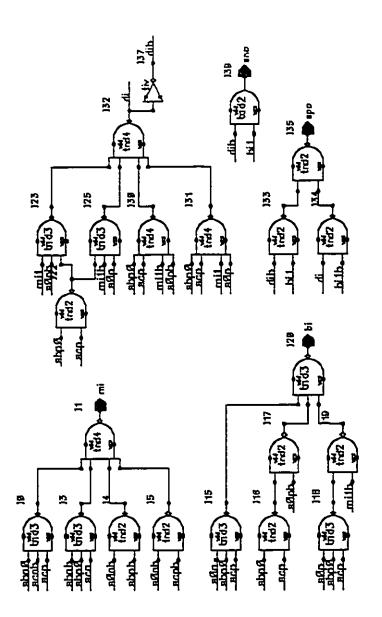

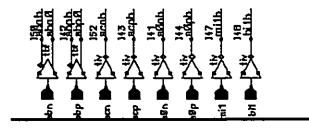

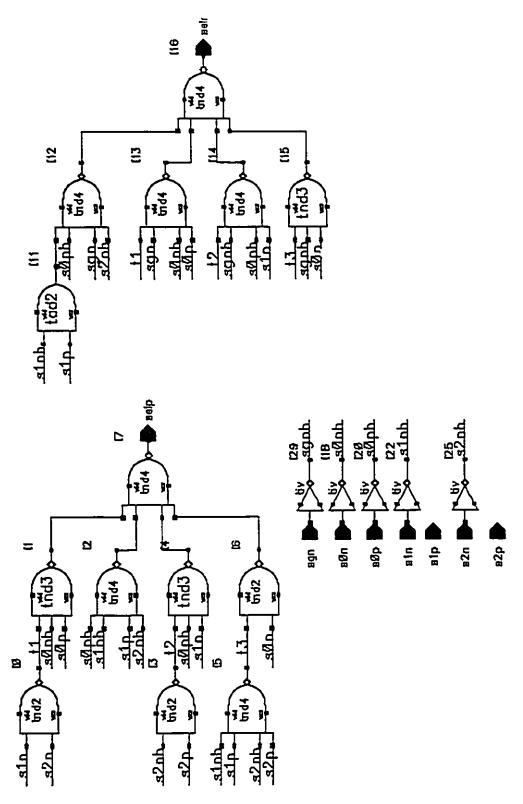

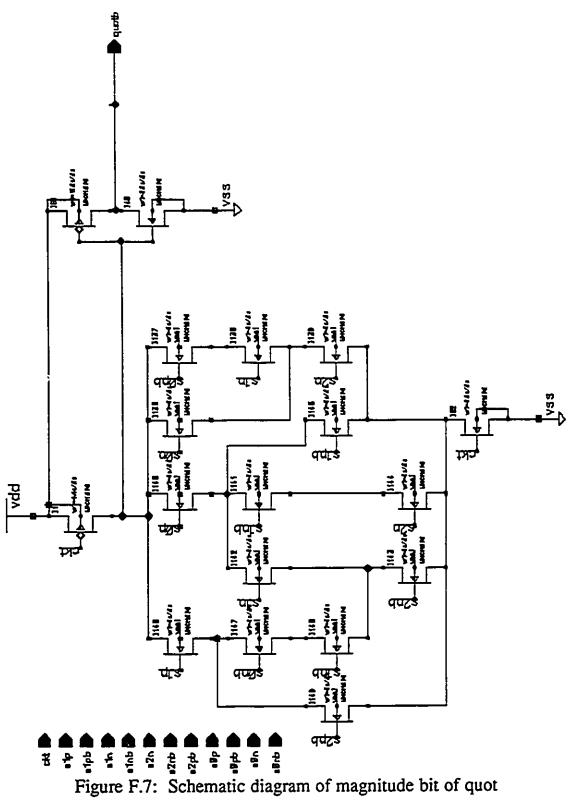

| APPENDIX F    |                             | AGRAM OF IMPROVED ARCHITI<br>IING TREE TECHNIQUE | ECTURE<br>140 |

| Vita Auctoris |                             |                                                  | 150           |

# LIST OF FIGURES

| <b>ว</b> 1 | Classical addition with carry propagation                              | 6  |

|------------|------------------------------------------------------------------------|----|

| 2.1        |                                                                        | 9  |

| 2.2        | Redundant binary adder                                                 |    |

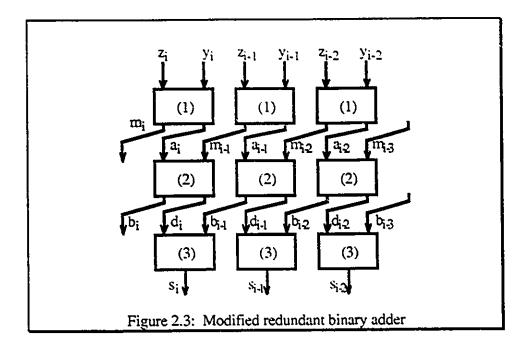

| 2.3        | Modified redundant binary adder                                        | 10 |

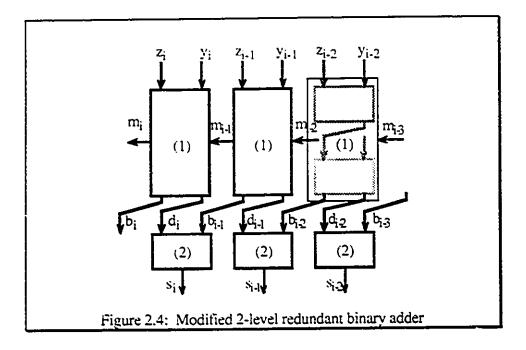

| 2.4        | Modified 2-level redundant binary adder                                | 11 |

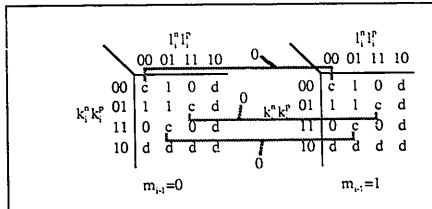

| 2.5        | Karnaugh maps for m; for the redundant adder with format 2             | 14 |

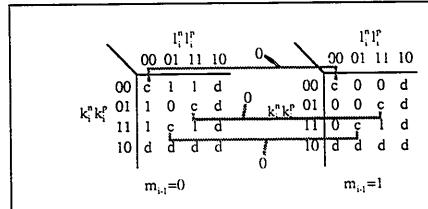

| 2.6        | Karnaugh maps for b <sub>i</sub> for the redundant adder with format 2 | 14 |

| 2.7        | Karnaugh maps for $d_i$ for the redundant adder with format 2          | 14 |

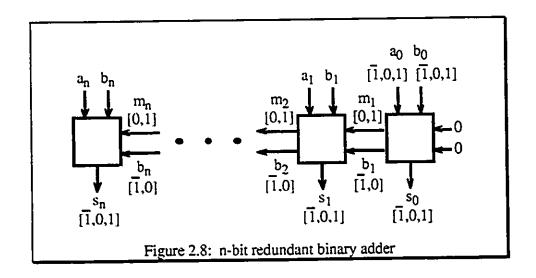

| 2.8        | n-bit redundant binary adder                                           | 15 |

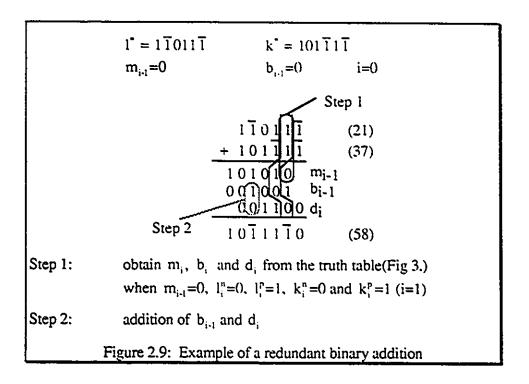

| 2.9        | Example of a redundant binary addition                                 | 16 |

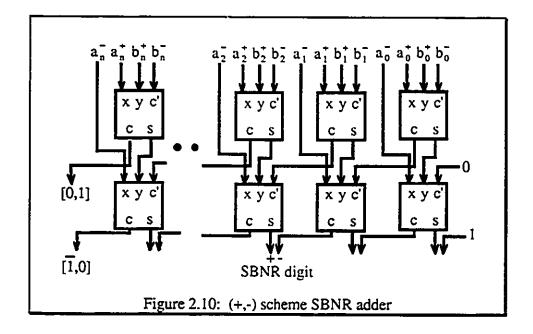

| 2.10       | (+,-) scheme SBNR adder                                                | 16 |

| 2.11       | Example on SBNR-binary conversion                                      | 17 |

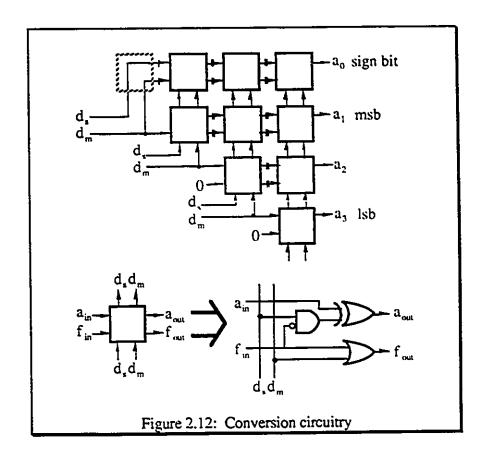

| 2.12       | Conversion circuitry                                                   | 18 |

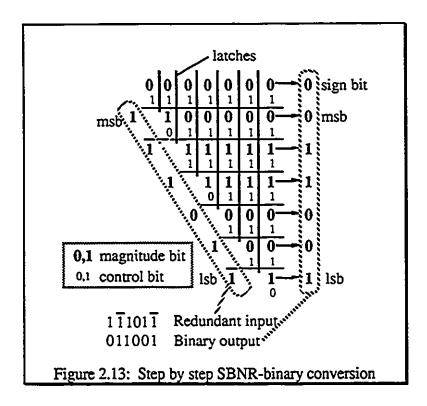

| 2.13       | Step by step SBNR-binary conversion                                    | 19 |

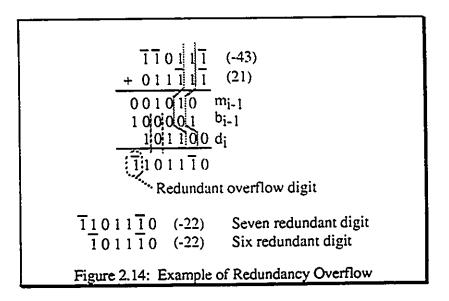

| 2.14       | Example of Redundancy Overflow                                         | 20 |

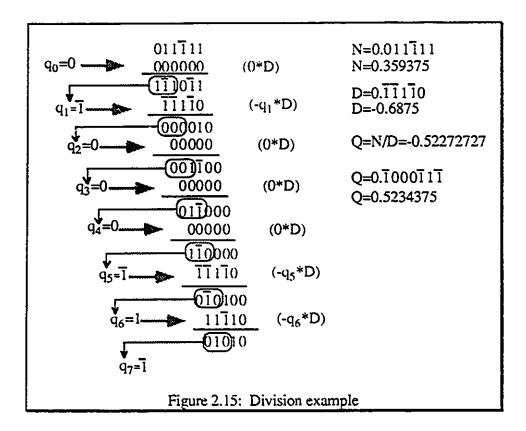

| 2.15       | Example on division                                                    | 23 |

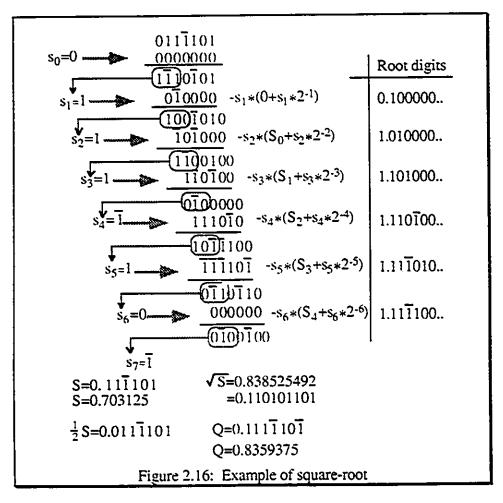

| 2.16       | Example of square-root                                                 | 25 |

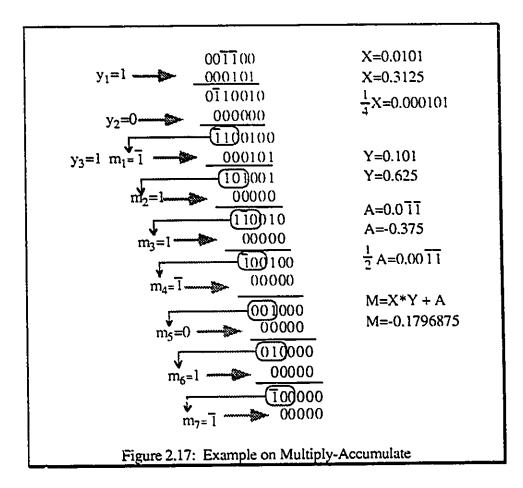

| 2.17       | Example on Multiply-Accumulat                                          | 28 |

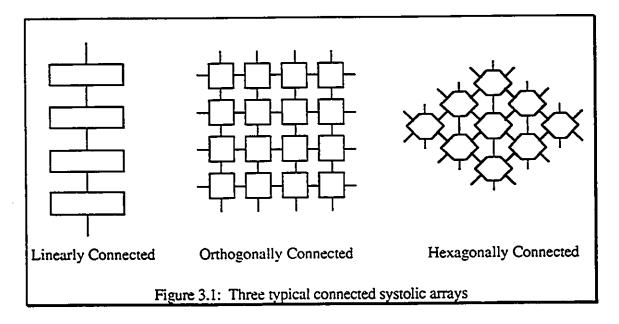

| 3.1        | Three typical connected systolic arrays                                | 31 |

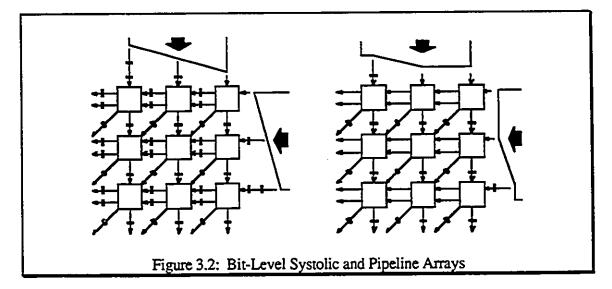

| 3.2        | Bit-Level Systolic and Pipeline Arrays                                 | 32 |

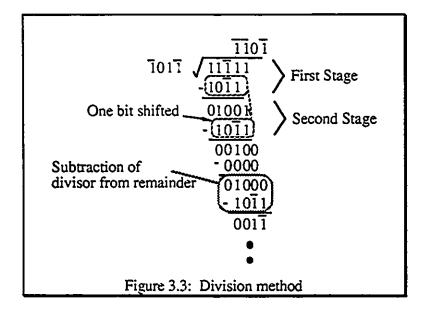

| 3.3        | Division method                                                        | 33 |

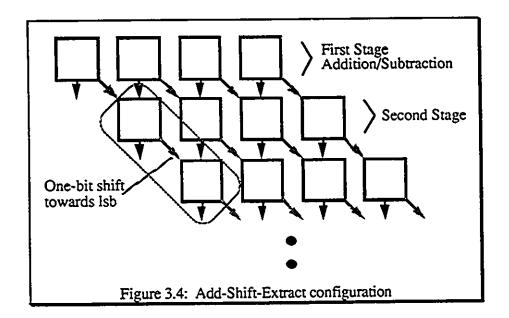

| 3.4        | Add-Shift-Extract configuration                                        | 34 |

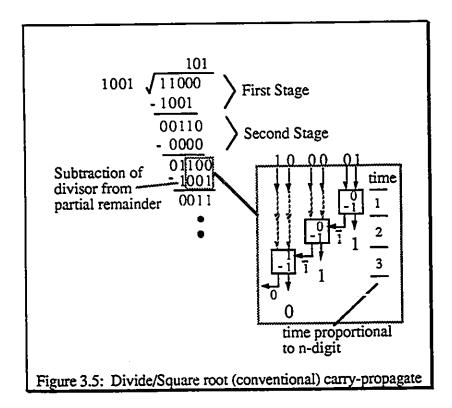

| 3.5        | Divide/Square root (conventional) carry-propagate                      | 3: |

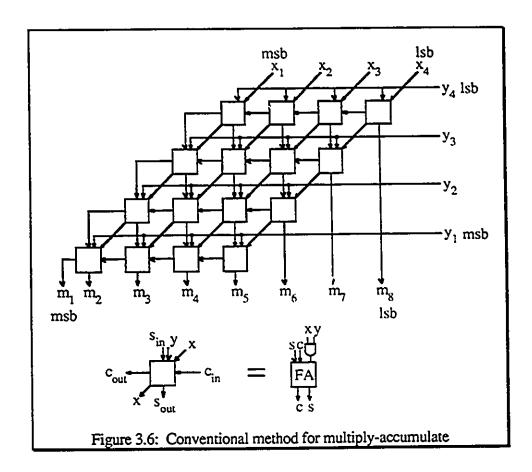

| 3.6        | Conventional method for multiply-accumulate                            | 36 |

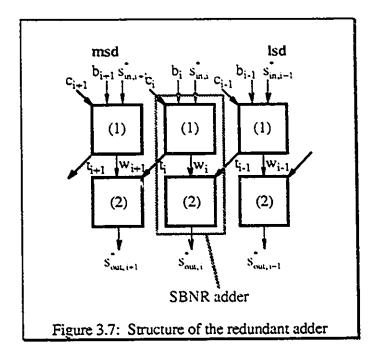

| 3.7        | Structure of the redundant adder                                       | 40 |

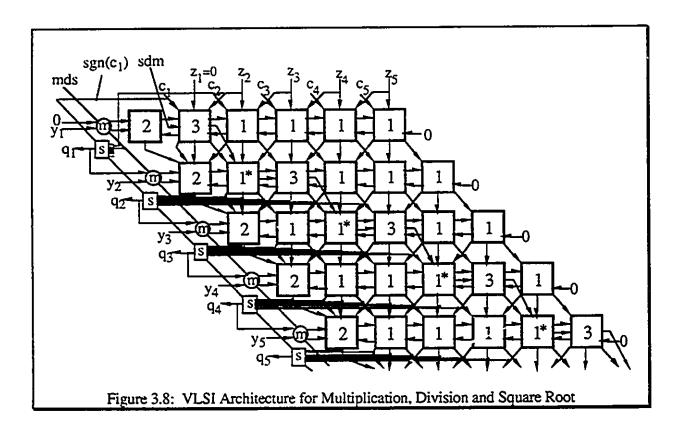

| 3.8        | VI.SI Architecture for Multiplication, Division and Square Root        | 4  |

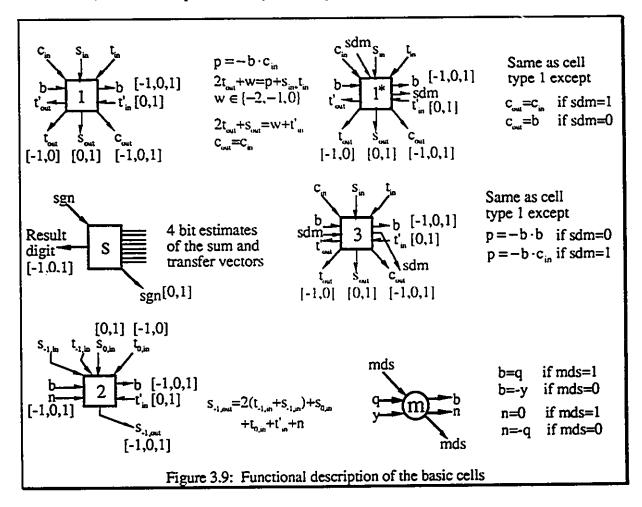

| 3.9  | Functional description of the basic cells                                                     | 42 |

|------|-----------------------------------------------------------------------------------------------|----|

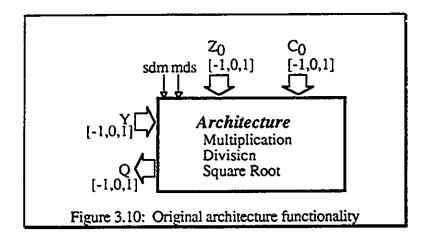

| 3.10 | Original architecture functionality                                                           | 43 |

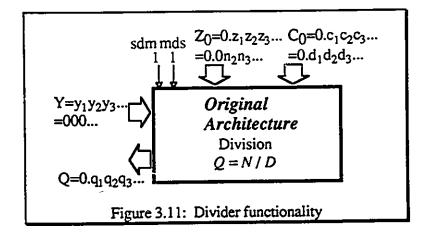

| 3.11 | Divider functionality                                                                         | 44 |

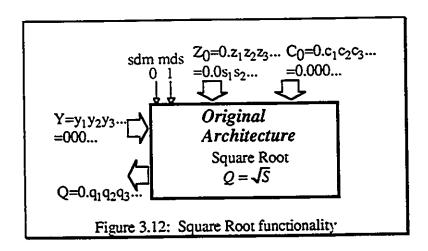

| 3.12 | Square Root functionality                                                                     | 45 |

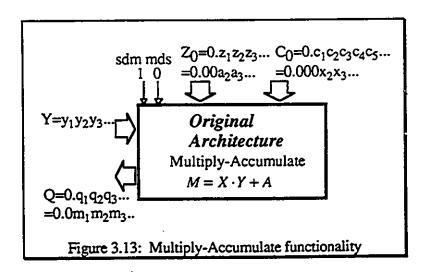

| 3.13 | Multiply-Accumulate functionality                                                             | 46 |

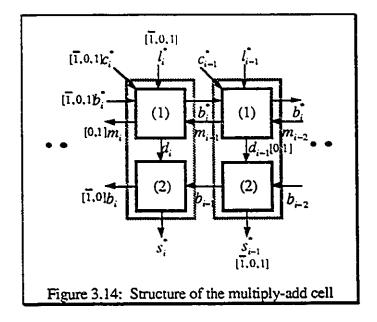

| 3.14 | Structure of the multiply-add cell                                                            | 52 |

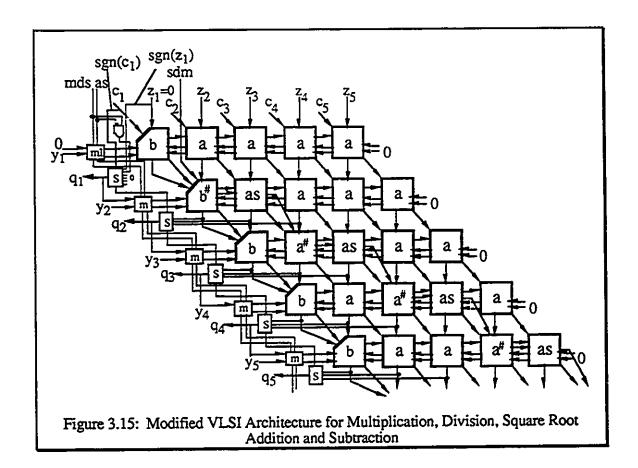

| 3.15 | Modified VLSI Architecture for Multiplication, Division, Square Root Addition and Subtraction | 52 |

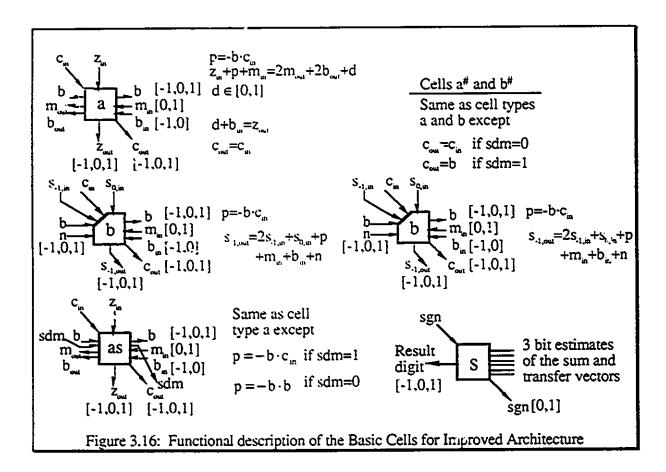

| 3.16 | Functional description of the Basic Cells for Improved Architecture                           | 53 |

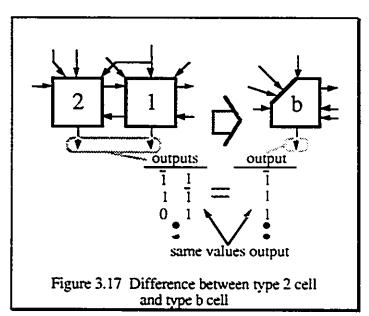

| 3.17 | Difference between type 2 cell and type b cell                                                | 55 |

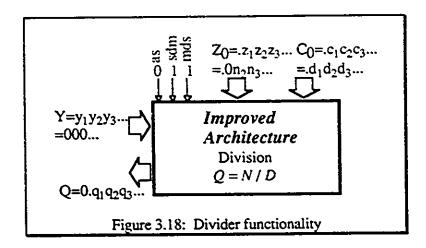

| 3.18 | Divider functionality                                                                         | 56 |

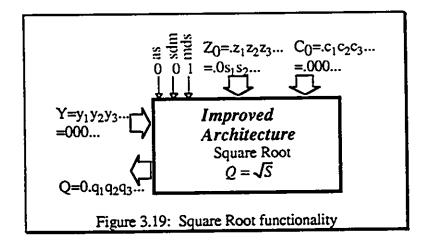

| 3.19 | Square Root functionality                                                                     | 56 |

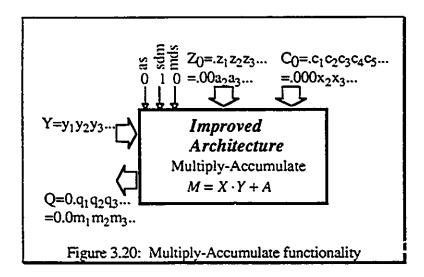

| 3.20 | Multiply-Accumulate functionality                                                             | 57 |

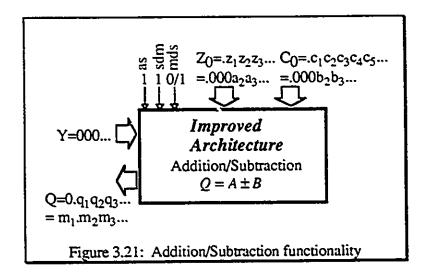

| 3.21 | Addition/Subtraction functionality                                                            | 58 |

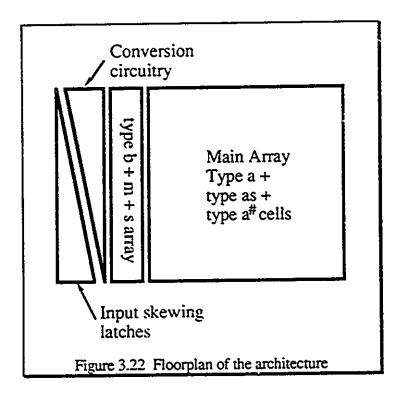

| 3.22 | Floorplan of the architecture                                                                 | 59 |

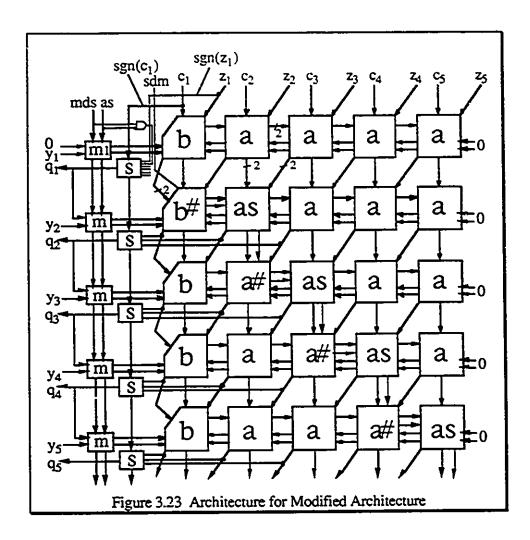

| 3.23 | Architecture for Modified Architecture                                                        | 60 |

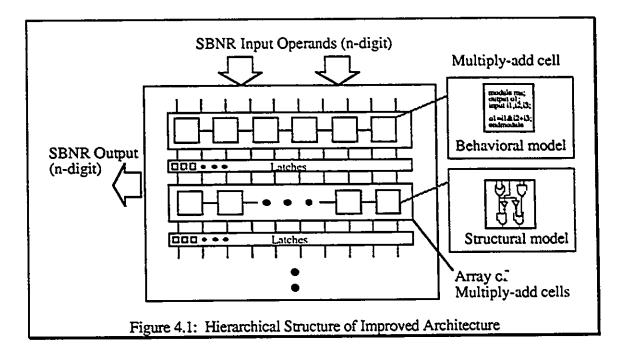

| 4.1  | Hierarchical Structure of Improved Architectur                                                | 64 |

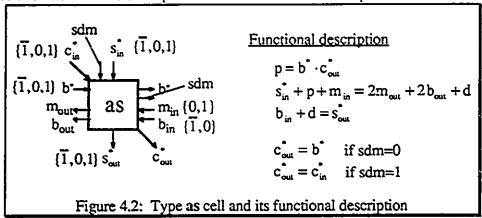

| 4.2  | Type as cell and its functional description                                                   | 65 |

| 4.3  | Verilog behavioral description for type as cell                                               | 65 |

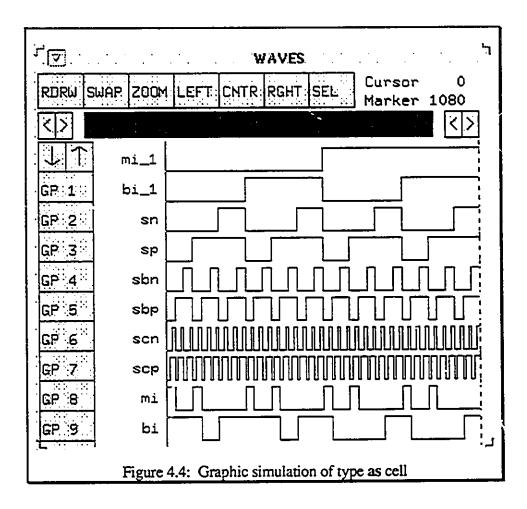

| 4.4  | Graphic simulation of type as cell                                                            | 66 |

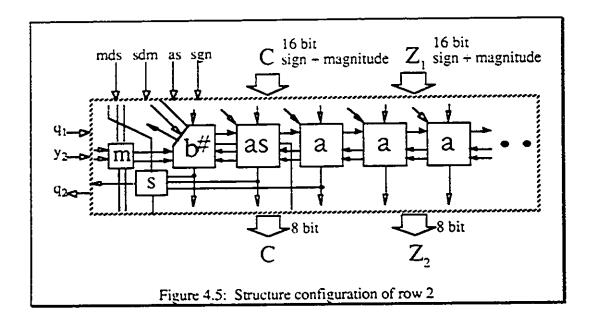

| 4.5  | Structure configuration of row 2                                                              | 67 |

| 4.6  | Behavioral description of row 2                                                               | 67 |

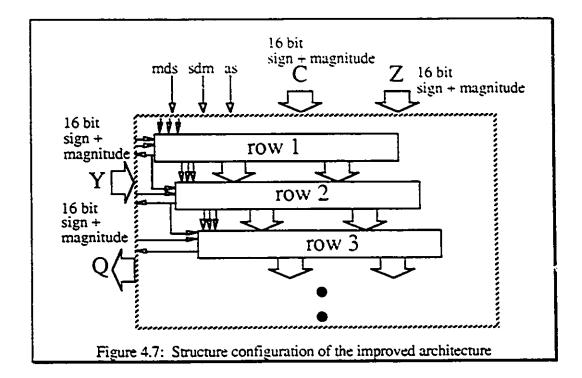

| 4.7  | Structure configuration of the improved architecture                                          | 68 |

| 4.8  | Behavioral description of the improved architecture                                           | 69 |

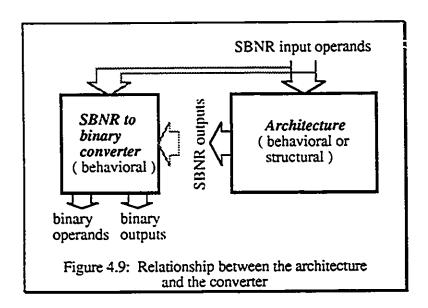

| 4.9  | Relationship between the architecture and the converter                                       | 69 |

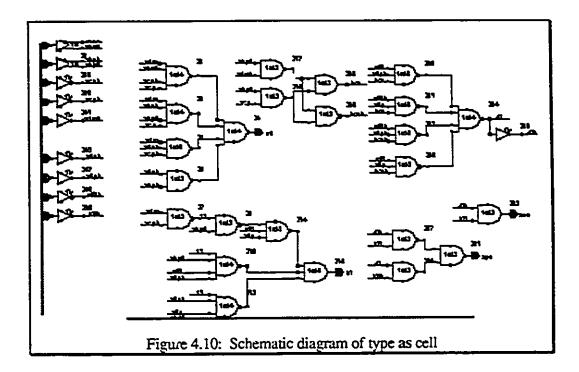

| 4.10 | Schematic diagram of type as cell                                                             | 70 |

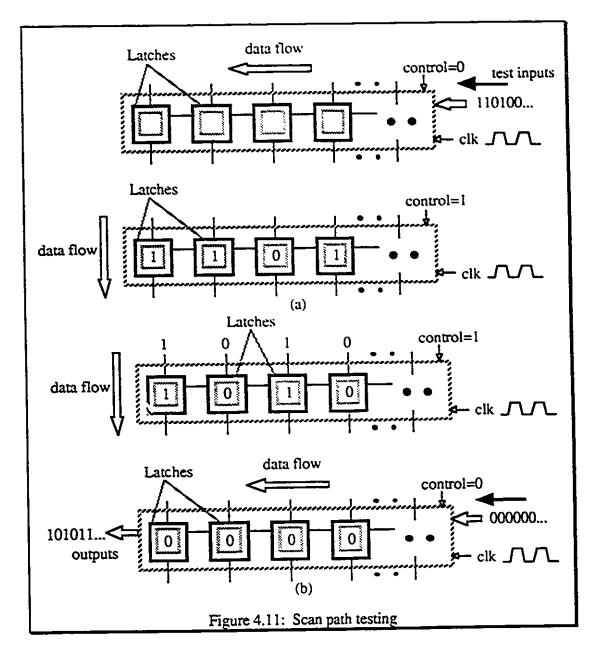

| 4.11 | Scan path testing                                                                             | 72 |

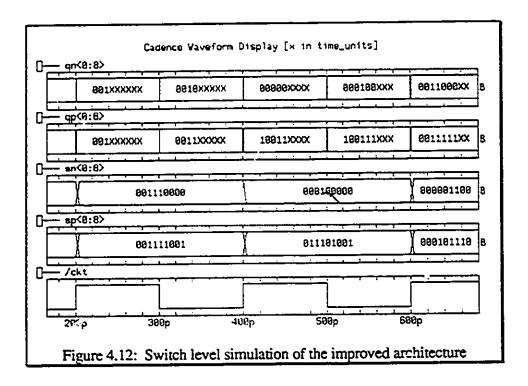

| 4.12 | Switch level simulation of the improved architecture                                          | 73 |

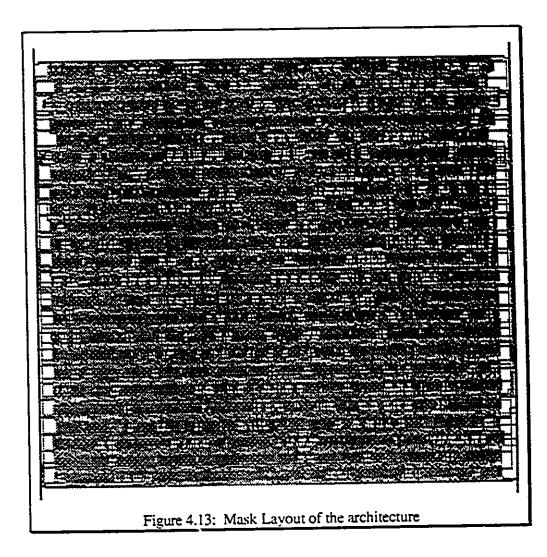

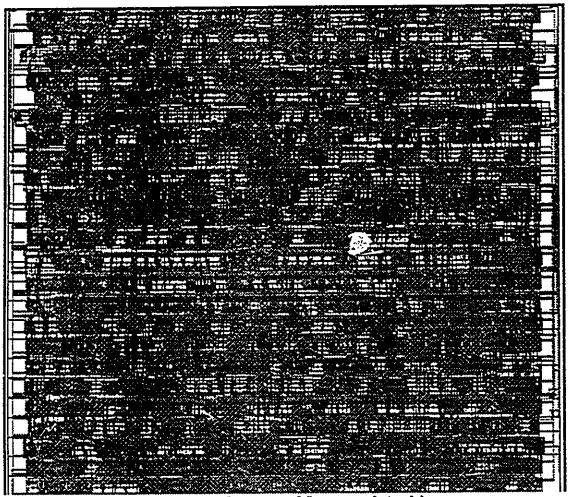

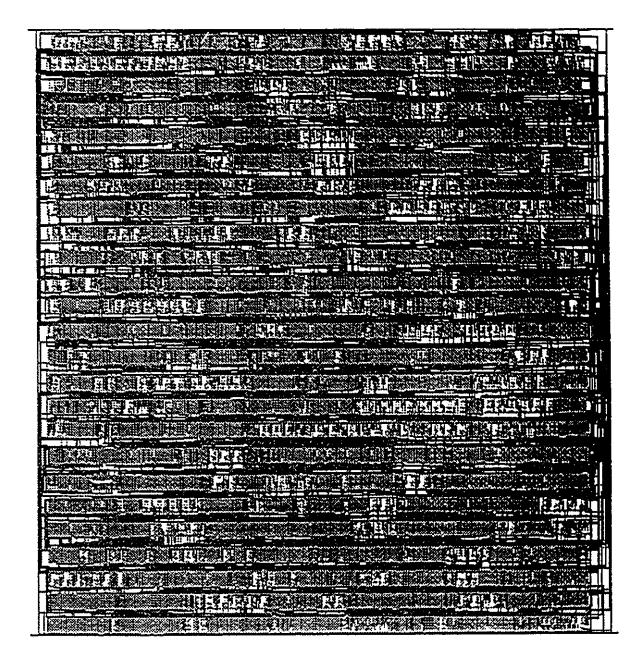

| 4.13 | Mask Layout of the architecture                        | 74  |

|------|--------------------------------------------------------|-----|

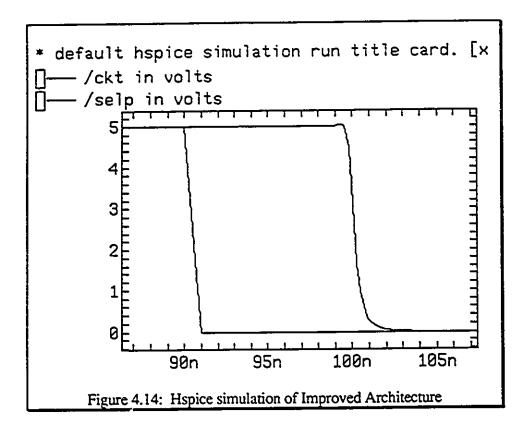

| 4.14 | Hspice simulation of Improved Architecture             | 75  |

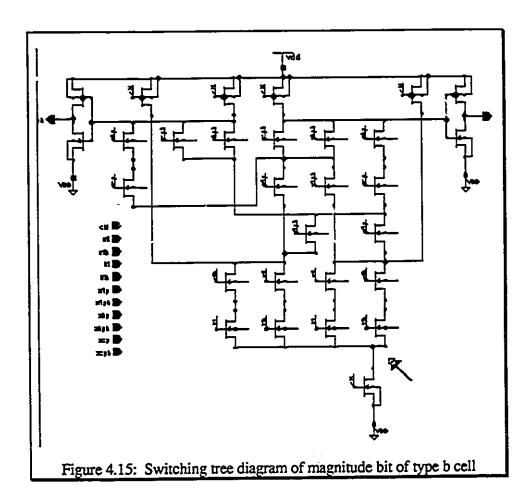

| 4.15 | Switching tree diagram of magnitude bit of type b cell | 76  |

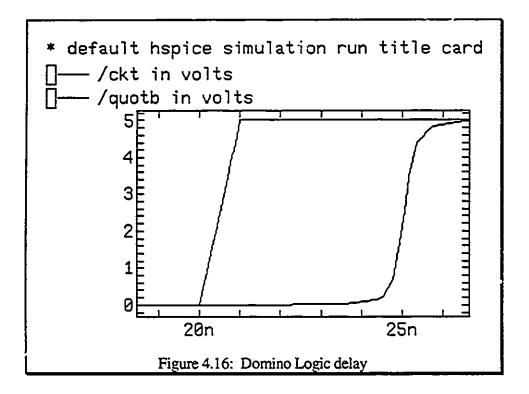

| 4.16 | Domino Logic delay                                     | 77  |

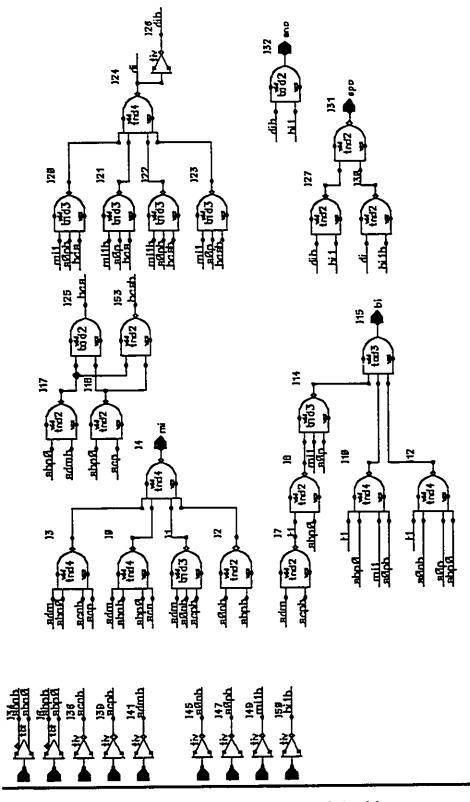

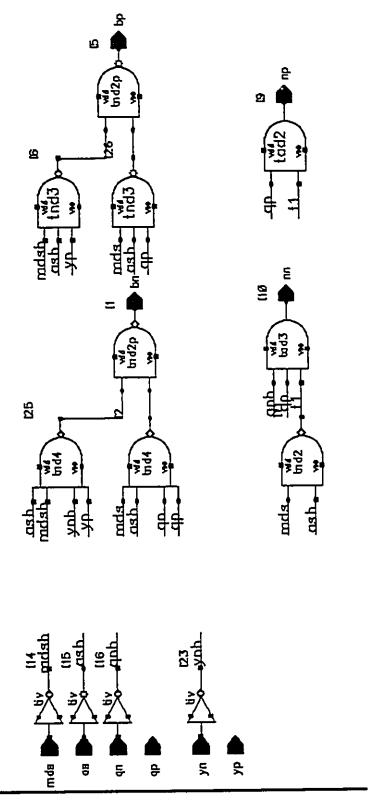

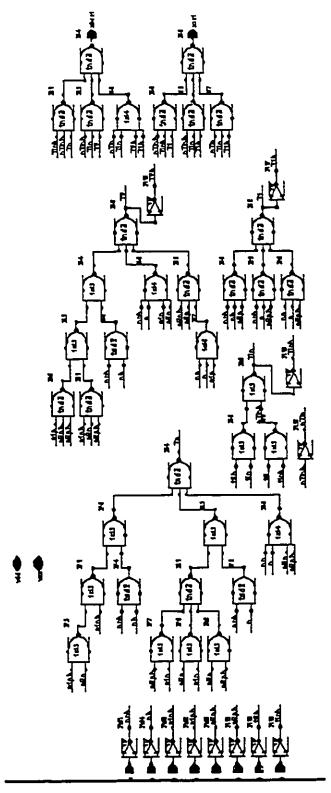

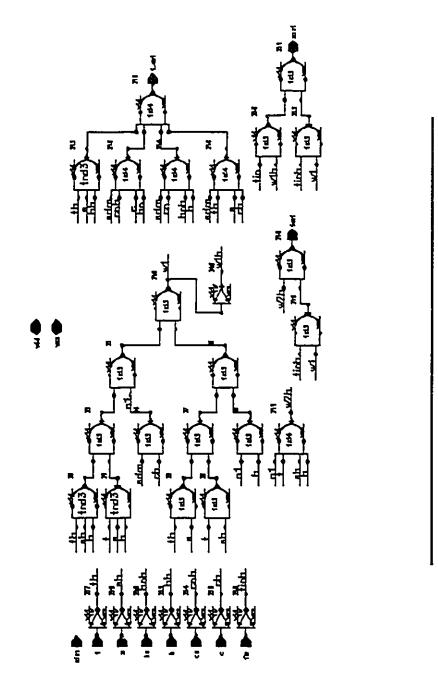

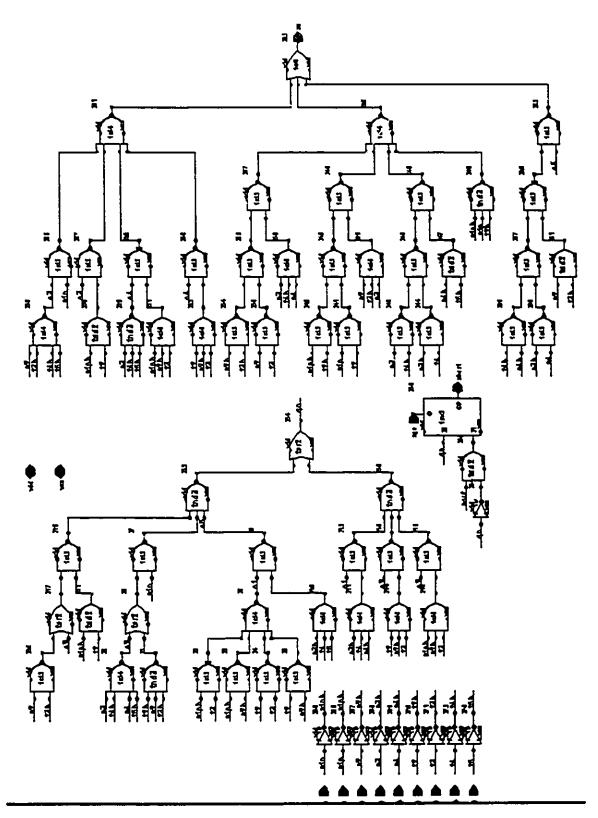

| C.1  | Type a cell of Improved Architecture                   | 116 |

| C.2  | Type as cell of Improved Architecture                  | 117 |

| C.3  | Type b cell of Improved Archtiecture                   | 118 |

| C.4  | Type s cell of Improved Architecture                   | 119 |

| C.5  | Type m cell of Improved Architecture                   | 120 |

| C.6  | Type m1 cell of Improved Architecture                  | 121 |

| C.7  | Type a# cell of Improved Architecture                  | 122 |

| C.8  | Type 1 cell of Original Architecture                   | 123 |

| C.9  | Type 1* cell of Original Architecture                  | 124 |

| C.10 | Type 2 cell of Original Architecture                   | 125 |

| C.11 | Type 3 cell of Orignal Architecture                    | 126 |

| C.12 | Type s cell of Original Architecture                   | 127 |

| C.13 | Type m cell of Original Architecture                   | 128 |

| D.1  | Mask Layout of Improved Architecture                   | 130 |

| D.2  | Mask Layout of Original Architecture                   | 131 |

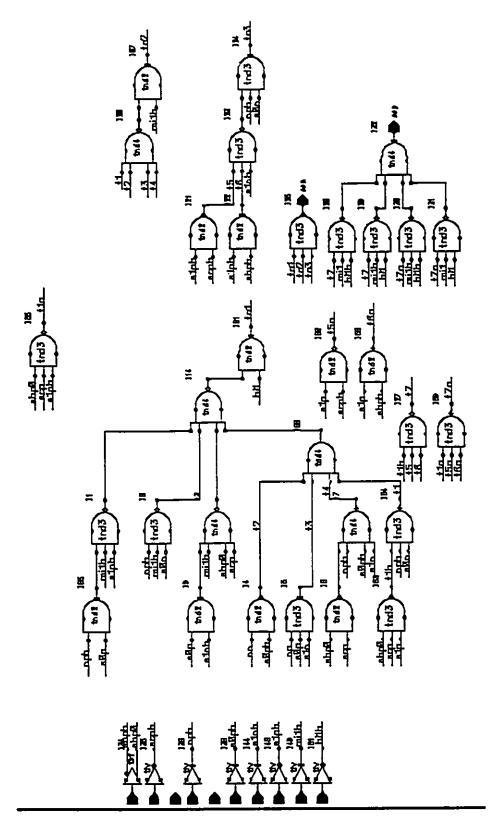

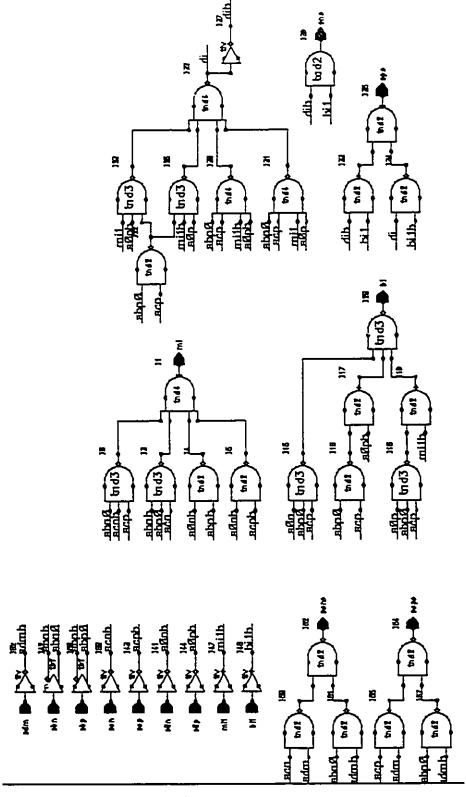

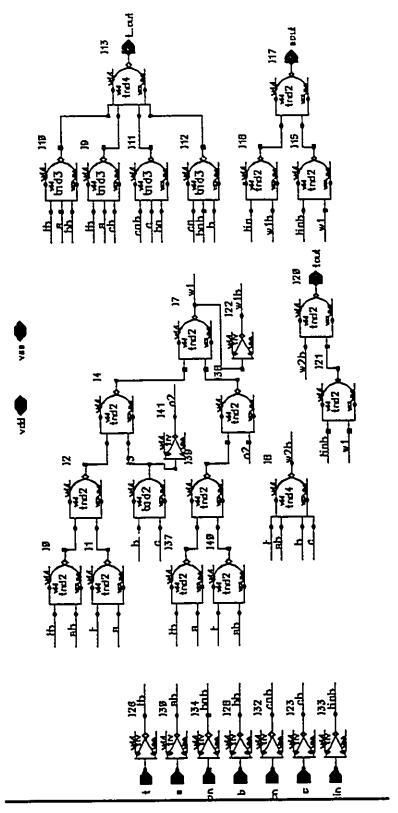

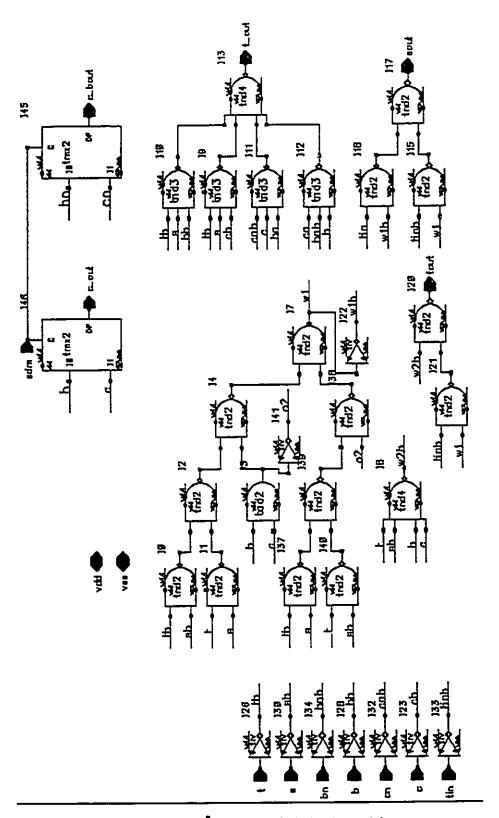

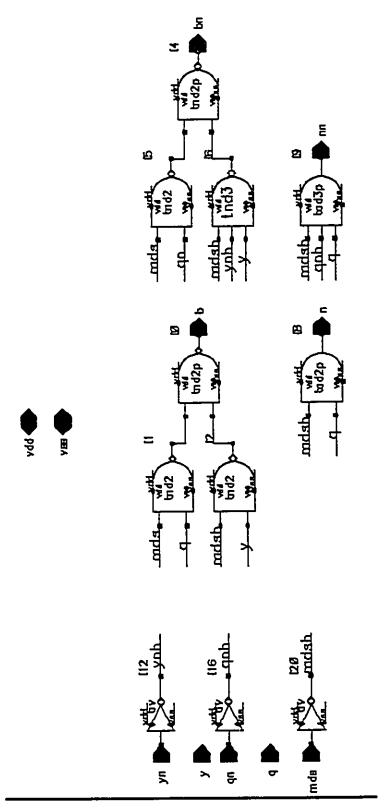

| F.1  | Schematic diagram of function bi_3                     | 141 |

| F.2  | Schematic diagram of function di_3                     | 142 |

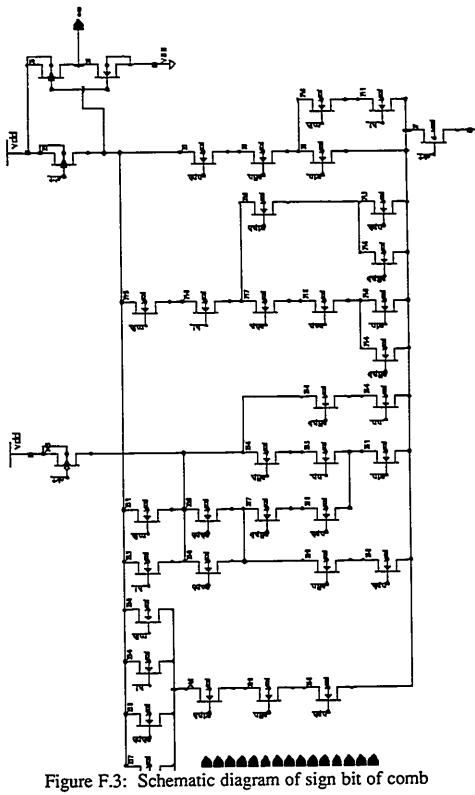

| F.3  | Schematic diagram of sign bit of comb                  | 143 |

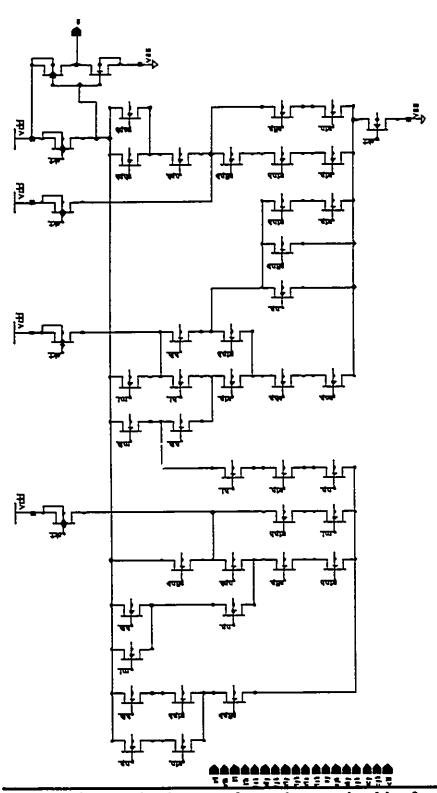

| F.4  | Schematic diagram of complement sign bit of comb       | 144 |

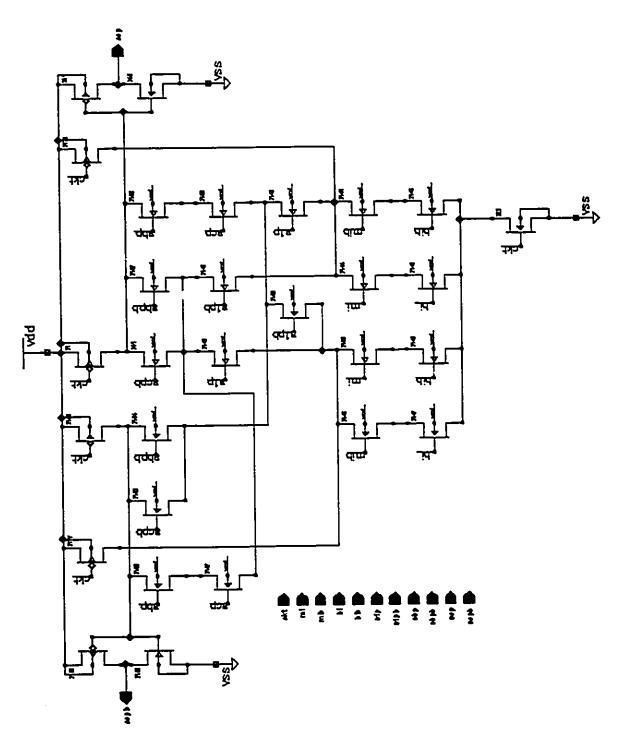

| F.5  | Schematic diagram of magnitude bit of comb             | 145 |

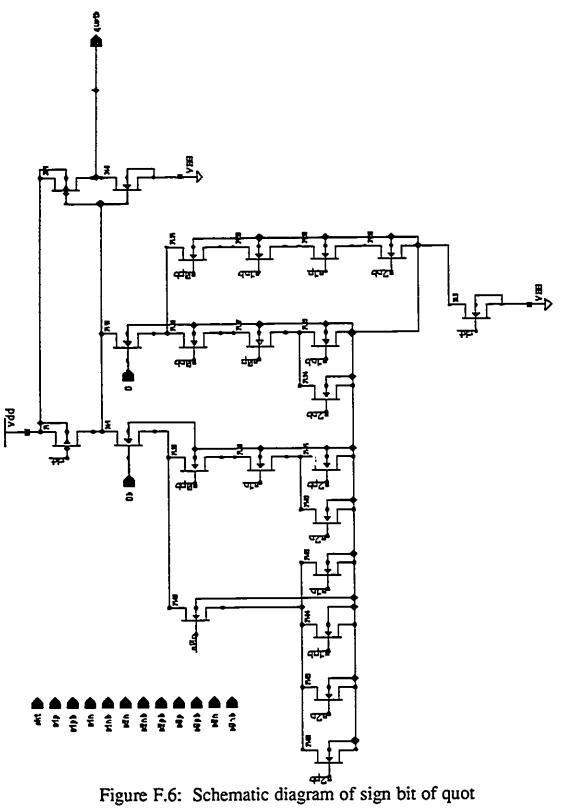

| F.6  | Schematic diagram of sign bit of quot                  | 146 |

| F.7  | Schematic diagram of magnitude bit of quot             | 147 |

| F.8  | Schematic diagram of function mi_3                     | 148 |

# LIST OF TABLES

| 2.1  | Encoding schemes of SBNR digits                                              | 7  |

|------|------------------------------------------------------------------------------|----|

| 2.2  | Nine distinct formats of representing a redundant binary digit with two bits | 12 |

| 2.3  | Truth Table for the combined block of format 2                               | 13 |

| 2.4  | Format of root digit extractors                                              | 25 |

| 2.5  | Ranges of the operands                                                       | 26 |

| 3.1  | Definition of recurrence parameters                                          | 38 |

| 3.2  | Ranges of Operands                                                           | 38 |

| 3.3  | Initial values of the parameters                                             | 38 |

| 3.4  | Encoded scheme for original architecture                                     | 39 |

| 3.5  | Values for interim transfer and interim sum                                  | 40 |

| 3.6  | Values of Transfer and Sum digit                                             | 41 |

| 3.7  | Selection function for Original Architecutre                                 | 42 |

| 3.8  | Control bits of the original architecture                                    | 43 |

| 3.9  | Definition of recurrence parameters for Improved Archtiecture                | 48 |

| 3.10 | Initial values of the parameters for Improved Architecture                   | 49 |

| 3.11 | Ranges of Operands for Improved Architecture                                 | 49 |

| 3.12 | Definition of result digits                                                  | 50 |

| 3.13 | Second stage of multiply-add cell                                            | 51 |

| 3.14 | Control bits of the Improved Architecture                                    | 54 |

| 3.15 | Comparisons between two architectures                                        | 61 |

| 3.16 | Comparisons of two architecture under switching tree technique               | 62 |

| 4.1  | Comparison of timing delays                                                  | 75 |

| 4.2  | Comparison between two Architectures                                         | 76 |

# Chapter 1

#### INTRODUCTION

#### 1.1 INTRODUCTION

In digital signal processing (DSP), there is a well established need for high renformance implementations of the basic arithmetic operations. All DSP systems require fast multiply and add/subtract operations while the more complex systems have a requirement for division and square root. It is evident that the speed of the basic arithmetic operations has considerable consequences on the performance of current DSP systems. With the rapid growth of integrated circuit technology, complex DSP systems which were prohibitively expensive in hardware terms, are usually implemented on a single chip. Furthermore, many arithmetic accelerating schemes (e.g. redundant number systems) are taking this advantage to improve the performance of current arithmetic algorithms.

Several architectures which share hardware to perform multiplication, division and square root have been proposed [1] [2] [3]. The architecture described by Kamal [1], exhibits regularity and local communication. However, its throughput rate is wordlength dependent and severely limited by carry propagate arithmetic. A similar array architecture was proposed by Agrawal [2]. The carry-save method is engaged instead of the carry propagate arithmetic. However, the result digits are in conventional binary form and result in lengthy communication paths for long wordlengths. The bit-serial architectures described by Zurawski and Gosling [3] and Ercegovac and Lang [4] do not address any

regularity and local communications which are suited for VLSI implementation. Additionally, relatively complex control is required and the throughputs are dependent on the wordlength.

The VLSI architecture proposed by McCanny and McQuillan [5] is capable of performing combined multiply-accumulate, division and square root operations at a very high throughput rate by employing pipelining and redundant arithmetic system. Moreover, the architecture is highly regular, requires minimal control and can be reconfigured on every cycle. The execution time for each operation is the same and the throughput rate is independent of the wordsize of the array. The focus of this thesis is to implement an improved architecture which has a better performance, and utilizes less number of standard cells than the previous architecture. This improved architecture employs many of the characteristics from the original architecture, including regularity, equal execution time for each operation, and precision independent throughput and simple control. Furthermore, add and subtract operations are combined with the existing operations on the improved architecture. The final VLSI implementation utilizes 0.8µm BiCMOS technology, one of the most advance technologies available nowadays.

# 1.2 ORGANIZATION OF THESIS

This thesis consists of five chapters. The first chapter serves to briefly present the contents and then to lay out the structure of the remaining chapters. Chapter 2, is divided into two sections. The first section is devoted to a review of Signed Digit Number Representation (SDNR) [6], in particular, the Signed Binary Number Representation (SBNR) [7]. Different radix-2 redundant adders are also discussed. In the second part of the chapter, multiply, division and square root algorithms which employ the redundant arithmetic system are briefly discussed through the use of examples.

Chapter 1 Introduction 3

In Chapter 3, a unified algorithm to perform multiply, divide and square root operations and VLSI architecture to implement the algorithm purposed by McCanny and McQuillan [5] are discussed in detail. Based on the original architecture, an improved architecture is proposed in this chapter. Comparisons between two architectures are made in terms of the number of standard cells required and performance.

Chapter 4 briefly describes the Hardware Description Language (HDL), Verilog, which used to describe the function of the architectures and perform the switch-level simulation. VLSI implementation of the architectures are presented in this chapter.

The final chapter, Chapter 5, concludes the work with a summary and few suggestions are also made to give direction to future research in this area.

# Chapter 2

REDUNDANT

NUMBER SYSTEMS

AND ALGORITHMS

#### 2.1 INTRODUCTION

Over the years, the demand for higher performance and higher functionality VLSI processors has increased substantially. Therefore, there is also need to improve the performance, area, efficiency, and functionality of the arithmetic units contained within these VLSI processors. The basic arithmetic function, addition, is often implemented by using the ripple carry adder, which uses a minimum number of gates, but forces a long delay in producing the sum since the carry must be propagated through the entire number. Several methods are described in the literature [8] [9] that overcome the problem generated by carry propagation. One of the techniques is to introduce redundancy into the number systems to accelerate arithmetic operations. Redundancy can also provide structural flexibility to these number systems. This chapter will be divided into two main sections. The first section deals with the general concept of Signed Digit Number Representation (SDNR) [6], which is the basic fundation of the SBNR adder. The first section will also examine the general characteristic properties of signed-binary number. Methods for redundant addition will be discussed through the use of examples. The second section of this chapter will deal with the algorithms that are used as the basis of the work. This section will discuss the division, square root and multiply algorithms.

#### 2.2 SIGNED DIGIT NUMBER REPRESENTATION[6]

The Signed Digit Number Representation (SDNR) was originally proposed by Avizienis to eliminate carry propagation chains in operations such as addition, subtraction, multiplication and division. Signed-digit numbers differ from conventional numbers in that the individual digit comprising a number allows both positive and negative digit values and since the individual digit contains all the sign information, there is no need for an explicit mechanism (such as 2's complement) to handle the overall sign of a number. For example, in a radix-2 SDNR, the individual digit may assume values 1, 0 or -1 (denoted by  $\overline{1}$ ). Signed-digit representations are redundant, that is, each radix r digit  $z_i$  assumes more than r different values. In conventional (non-redundant) number representation, only r values of a digit (0, 1, ..., r-1) are allowed. In signed-digit (redundant) number representation, the value a (where a is the maximum digit magnitude) is chosen from the following range:

$$-(r-1) \le a \le r-1$$

for radix r (2.1)

The smallest set of digits is termed the minimally redundant set and contains at least r+1 values (where r is the radix). The largest set of digits is termed the maximally redundant set and contains at most 2r-1 values. For example, in higher radices, there is some choice available in the digit set that can be chosen; symmetric digit sets for radix-4 can be chosen as either  $\{\overline{2},...2\}$  or  $\{\overline{3},....3\}$ . The other reason that signed-digit numbers are termed as redundant is that any given algebraic value may have several possible representations. For example, value 13 may be represented several ways in radix-2 SDNR as 1101, or  $111\overline{1}$ , or  $100\overline{1}\overline{1}$ , etc. The characteristic properties of signed-digit representations are listed below.

1. The algebraic value Z of the number z composed of n+m+1 digits  $(z_n \cdots z_1 z_0 z_{-1} \cdots z_{-m})$  is given by the conventional expression:

$$Z = \sum_{i=0}^{-m} z_i r^i \qquad \text{where radix r is a positive integer}$$

(2.2)

- 2. The algebraic value Z=0 has a unique representation, if and only if all  $z_i=0$ .

- 3. The sign of the algebraic value Z is given by the sign of the most significant (left most) nonzero digit.

- 4. To form the representation of the additive inverse -Z, the sign of every nonzero digit  $z_i$  is changed individually.

- 5. The addition and subtraction of two signed-digit operands Z and Y satisfies  $s_i = f(z_i, y_i, z_{i-1}, y_{i-1}, z_{i-2}, y_{i-2}) \ \forall i$ , where  $s_i$  are digits in the representation of the sum or difference  $s_i = z_i \pm y_i$ . In other words,  $s_i$  is a function of the sum or difference of three adjacent operands.

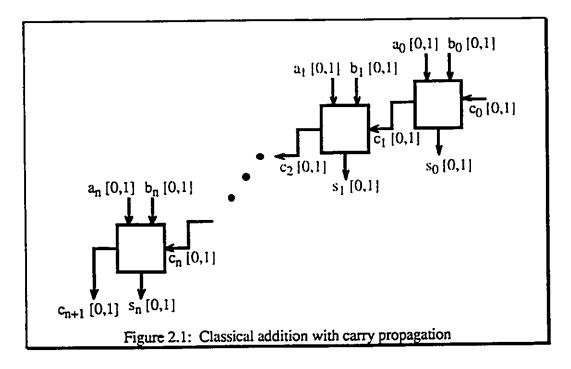

In a conventional binary number system, the addition of two binary numbers requires a computation time at least proportional to the logarithm of the wordlength of the operands, because of carry propagation from Least-Significant Bit (LSB) through Most-Significant Bit (MSB). This is usually the bottleneck for speed improvement in digital integrated systems. The addition of two binary numbers is sketched in Figure 2.1.

As the global delay of the adder depends on the carry delay, the basic full adder cell is optimized regarding this criterion. Redundancy in a number system allows methods of addition to be devised in which each digit of the result is a function only of the digits in a few adjacent positions of the operands and does not depend on the other digits in any way. Thus the features of redundancy in a number system has several important consequences. It allows parallel arithmetic operations to be performed completely without full carry propagation from the Least-Significant Bit (LSB) through to the Most-Significant Bit (MSB). Thus the time required for an operation such as parallel addition or subtraction is constant and does not dependent on the wordlength. In other words, it provides flexibility to the structure of the arithmetic units. A corollary of this is that it is possible to pipeline such an adder so that it operates from the most significant digit first.

# 2.2.1 SIGNED BINARY NUMBER REPRESENTATION

Of particular interest in this thesis is the Radix-2 SDNR known as the Signed Binary Number Representation (SBNR) which has a digit set  $\{\overline{1},0,1\}$ . Each SBNR digit requires a two bit representation implying a multiplicity of possible encoding schemes. Two encoding schemes which are particularly useful are the sign-and-magnitude and the (+,-) schemes which are defined in Table 2.1.

| Digit<br>d*                       | sign-and-magnitude<br>d <sub>s</sub> d <sub>m</sub> | (+,-)<br>d+ d- |

|-----------------------------------|-----------------------------------------------------|----------------|

| 0                                 | 0 0                                                 | 0 1            |

| 1                                 | 0 1                                                 | 1 1            |

| -1                                | 1 1                                                 | 0 0            |

| 0 or d (d doesn't exist in (+,-)) | 1 0                                                 | 1 0            |

Table 2.1: Encoding schemes of SBNR digits

Note: d: don't care

In the sign-and-magnitude scheme, the SBNR digits are coded as the sign and magnitude bits, that is  $d^* = (d_s, d_m)$ . In the (+,-) scheme, an SBNR digit is coded as  $d^* = (d^+, d^-)$  where  $d^* = d^+ + (d^- - 1)$ . The  $d^+$  bit is coded such that  $d^+ = 0$  implies 0 and  $d^+ = 1$  implies 1, while the  $d^-$  bit is coded such that  $d^- = 0$  implies -1 and  $d^- = 1$  implies 0. An important property of the (+,-) scheme is that the SBNR adders can be constructed from simple binary full adders. The structure of the (+,-) scheme adders will be discussed later in this section.

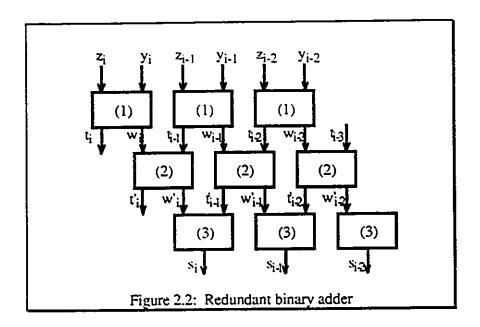

# 2.2.2 REDUNDANT BINARY ADDER

A redundant binary or SBNR adder in which all digit sets are  $\{\overline{1},0,1\}$  was first discussed by Avizienis[6]. He showed that the parallel addition or subtraction dictates a three level structure. The result digit  $s_i$  depends only on the three adjacent operands  $z_{i-2}, y_{i-2}, z_{i-1}, y_{i-1}, z_i$  and  $y_i$ . The operation of the redundant binary adder is described by the following equations(2.3a - 2.3c):

$$z_i + y_i = 2t_i + w_i (2.3a)$$

$$w_i + t_{i-1} = 2t'_i + w'_i (2.3b)$$

$$s_i = w'_{i+1} + t'_{i-1} (2.3c)$$

where  $z_i$  and  $y_i$  are the operands,  $w_i$  and  $w'_i$  are defined as intermediate sum digits,  $t_i$  and  $t'_i$  are the transfer digits, and  $s_i$  is the sum digit. The term transfer digit is used here instead of the commonly used terms "carry" or "borrow" for two reasons. First, the transfer digit may assume both positive and negative values in either addition or subtraction. Second, unlike the "carry" or "borrow" of conventional addition or subtraction, the transfer digit is never propagated past the first adder position on the left. The structure of the adder is shown in Figure 2.2. The sum of operands is realized in three steps. In the first step,  $t_i$  is 1 whenever  $z_i + y_i > 1$ . In the second step, transfer digit  $t'_i$  is 1 only if  $t_i + w_i = 2$ . This ensures that  $t_i$  and  $t'_i$  cannot be equal to +1 or -1 at the same time. At the last step, the sum digit,  $s_i$ , is simply obtained by the free addition of transfer digit  $t'_{i-1}$  from the adjacent digit and sum digit  $w'_i$ .

# 2.2.2 MODIFIED REDUNDANT BINARY ADDER

Based on the concept introduced by Avizienis, the logic design and implementation of redundant binary adders have been investigated by several other authors[10] [11] [5]. Here, only the logic design by Robertson [10] will be discussed. The logic design will be used as the basic foundation in the improved arithmetic architecture in the following chapter.

The logic design introduced by Robertson [10] is very similar to the design by Avizienis [6], but with the combination of the first two stages, it results in a relatively simple logic design compared to the previous one. The redundant binary adder constructed with two inputs and one output, in the digit set  $\{\overline{1},0,1\}$ . The structure of the adder is shown in Figure 2.3, and the operation of the redundant binary adder is shown in eqn. 2.4:

$$l_i^* + k_i^* = 2m_{i+1} + a_i^* (2.4a)$$

$$a_i^* + m_{i-1} = 2b_{i+1} + d_i (2.4b)$$

$$s_i^* = d_i + b_{i-1}$$

(2.4c)

At ith position, inputs  $l_i^*$ ,  $k_i^*$  are the operands of the adder/subtractor structure, and with output operates at one non-redundant  $m_{i+1}$  and one redundant digit  $a_i^*$  (an asterisk beside a symbol denotes a redundant binary digit chosen from digit set  $\{\overline{1},0,1\}$ ). The sum of  $l_i^*$  and  $k_i^*$  equals  $(2m_{i+1} + a_i^*)$  (2.4a) must be chosen from one of the following combinations (2.5a) - 2.5c):

$$m_{i+1} \in \{\overline{1}, 0\}, \ a_i^* \in \{0, 1, 2\}$$

(2.5a)

$$m_{i+1} \in \{0,1\}, \ a_i^* \in \{\overline{2},\overline{1},0\}$$

(2.5b)

$$2m_{i+1} \in \{\overline{1},1\}, \ a_i^* \in \{\overline{1},0,1\}$$

(2.5c)

Combining the first two levels of the original structure does result in a relatively simple logic design. With the combination of the first two stages, the format of transfer digit ai no longer needs to be considered. For the symmetric adder, the algebraic relationships are listed below and Figure 2.4 [10] depicts the operations shown below:

$$d_i + b_i = s_i^*$$

for the final block (2.6)

$$d_i + b_i = s_i^* \qquad \text{for the final block}$$

(2.6)

$$l_i^* + k_i^* + m_{i-1} = 2m_i + 2b_i + d_i \qquad \text{for the combined block}$$

(2.7)

In spite of equations 2.6 and 2.7,  $m_i$  can be made independent of  $m_{i-1}$ . The final result digit  $s_i^*$  is still a function only of the digits in three adjacent digital positions of the operands. The chosen sets for  $m_i$ ,  $h_i$ ,  $d_i$  are  $\{0,1\}$ ,  $\{\overline{1},0\}$ ,  $\{0,1\}$  respectively. Before proceeding further, one has to fix the binary representation for the redundant binary digit set  $\{\overline{1},0,1\}$ . The term redundant is used here because there exists more than one way to represent a redundant binary number by using the two-bit binary number. Robertson has shown that there exists only nine distinct ways, under permutation and negation, of representing three values  $\overline{1}$ , 0 and 1 from the redundant digit set with a two-bit binary number. The nine formats are shown in Table 2.2. Since it is sometimes necessary to feed the output of the redundant adder as an operand to the input of the next redundant adder, the result digit  $s_i^*$  should have the same binary representation as the operand digits  $t_i^*$  and  $t_i^*$ .

| S <sub>i</sub> <sup>n</sup> | Sip | 1 | 2 | 3  | 4 | 5  | 6        | 7 | 8 | 9 |

|-----------------------------|-----|---|---|----|---|----|----------|---|---|---|

| 0                           | 0   | 0 | 0 | () | 0 | d  | 0        | 0 | l | ī |

| 0                           | 1   | 1 | 1 | l  | 1 | 1  | 1        | 1 | 1 | l |

| 1                           | 0   | ī | d | 0  | ī | 0  | 1        | ī | 0 | 0 |

| 1_                          | 1   | 0 | ī | ī_ | d | 1_ | <u>ī</u> | ī | ī | 1 |

Table 2.2: Nine distinct formats of representing a redundant binary digit with two bits

Note:  $s_i^* = [s_i^n, s_i^n]$ , d: don't care and  $\overline{1}$ : -1

Some rather interesting details are encountered in the design of this redundant binary adder. From equation 2.7, whenever  $(l_i^* + k_i^* + m_{i-1})$  is algebraically 0 or 1,  $-b_i$  and  $m_i$  can be both 0 or both 1. This results in the introduction of "Coupled don't care" cases in the truth table. Table 2.3 shows the truth table for the combined block of the redundant binary adder using format 2 from Table 2.2.  $l_i^*$ ,  $k_i^*$  and  $s_i^*$  are represented by pairs of bits  $(l_i^n, l_i^p)$ ,  $(k_i^n, k_i^p)$  and  $(s_i^n, s_i^p)$  respectively. The horizontal pairs of c's across  $b_i$  and  $m_i$  are the "coupled don't cares". A horizontal pair of c's can be both 0 or both 1.

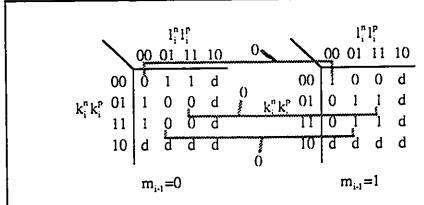

The complexity introduced by the "coupled don't cares" is greatly reduced by the important constraints that the transfers  $b_i$  and  $m_i$  be non-propagating. This means that  $m_i$  must be independent of  $m_{i-1}$  from the adjacent unit. Therefore, in Table 2.3, the "coupled don't cares" for minterms 1, 4, 19 and 28 must have the values 1, 1, 0, and 0 respectively. This requires the upper 16 function values of  $m_i$  to match the lower 16 function values of  $m_i$ . With four minterms of "coupled don't cares" being fixed, there remain only six "coupled don't cares" of the values of  $m_i$  needed to fill the table. Figure 2.5 shows the Karnaugh maps for  $m_i$  from Table 2.3. Similar karnaugh maps for  $b_i$  and  $d_i$  are shown in Figure 2.6 and Figure 2.7 respectively.

|    | m <sub>i-1</sub> | $l_i^n$ | $l_i^p$ | k, | k,ª | value | m,    | b <sub>i</sub> | d, |

|----|------------------|---------|---------|----|-----|-------|-------|----------------|----|

| 0  | 0                | 0       | 0       | 0  | 0   | 0     | С     | c              | 0  |

| 1  | 0                | 0       | 0       | 0  | 1   | 1     | c(1)  | c (1)          | 1  |

| 2  | 0                | 0       | 0       | 1  | 0   | d     | d     | d              | d  |

| 3  | 0                | 0       | 0       | 1  | 1   | ī     | 0     | 1              | 1  |

| 4  | 0                | 0       | l       | 0  | 0   | 1     | c (1) | c (1)          | 1  |

| 5  | 0                | 0       | i       | 0  | 1   | 2     | 1     | 0              | 0  |

| 6  | 0                | 0       | 1       | 1  | 0   | d     | d     | d              | d  |

| 7  | 0                | 0       | 1       | 1  | 1   | 0     | С     | c              | 0  |

| 8  | 0                | 1       | 0       | 0  | 0   | d     | d     | d              | d  |

| 9  | 0                | 1       | 0       | 0  | 1   | d     | d     | d              | d  |

| 10 | 0                | 1       | 0       | 1  | 0   | d     | d     | d              | đ  |

| 11 | 0                | 1       | 0       | 1  | 1   | d     | d     | d              | d  |

| 12 | 0                | 1       | 1       | 0  | 0   | 1     | 0     | 1              | 1  |

| 13 | 0                | 1       | 1       | 0  | 1   | 0     | С     | С              | 0  |

| 14 | 0                | 1       | 1       | 1  | 0   | d     | d     | ď              | d  |

| 15 | 0                | 1       | 1       | 1  | 1   | 2     | 0     | 1              | 0  |

| 16 | 1                | 0       | 0       | 0  | 0   | 1     | С     | c              | 1  |

| 17 | 1                | 0       | 0       | 0  | ī   | 2     | 1     | 0              | 0  |

| 18 | 1                | 0       | 0       | i  | 0   | d     | d     | d              | d  |

| 19 | 1                | 0       | 0       | 1  | 1   | 0     | c (0) | c (0)          | 0  |

| 20 | 1                | 0       | 1       | 0  | 0   | 2     | 1     | 0              | 0  |

| 21 | 1                | 0       | 1       | 0  | 1   | 3     | 1     | 0              | 1  |

| 22 | ı                | 0       | 1       | 1  | 0   | d     | d     | d              | d  |

| 23 | 1                | 0       | 1       | 1  | 1   | l     | С     | С              | 1  |

| 24 | 1                | 1       | 0       | 0  | 0   | d     | d     | d              | d  |

| 25 | 1                | 1       | 0       | 0  | 1   | d     | d     | d              | d  |

| 26 | 1                | I       | 0       | 1  | 0   | d     | d     | d              | d  |

| 27 | 1                | 1       | 0       | 1  | 1   | d     | d     | d              | d  |

| 28 | 1                | 1       | 1       | 0  | 0   | 0     | c (0) | c (0)          | 0  |

| 29 | 1                | 1       | 1       | () | 1   | ī     | c     | С              | 1  |

| 30 | 1                | 1       | 1       | 1  | 0   | d     | d     | d              | d  |

| 31 | 1                | 1       | 1       | 1  | 1   | 1     | 0     | 1              | 1  |

Table 2.3: Truth Table for the combined block of format 2

Figure 2.5: Karnaugh maps for m, for the redundant adder with format 2

Figure 2.6: Karnaugh maps for b, for the redundant adder with format 2

Figure 2.7: Karnaugh maps for d<sub>i</sub> for the redundant adder with format 2

With the introduction of "coupled don't cares", the logical design of the redundant binary adder will yield a simpler structure. The boolean functions of the redundant binary adder of format 2 are listed below:

$$\begin{aligned} d_{i} &= m_{i-1} \oplus l_{i}^{p} \oplus k_{i}^{p} & d_{i} \in \{0,1\} \\ m_{i} &= \overline{l_{i}^{n}} \overline{k_{i}^{n}} (l_{i}^{p} \vee k_{i}^{p}) & m_{i} \in \{0,1\} \\ b_{i} &= \overline{m_{i-1}} \overline{l_{i}^{p}} k_{i}^{p} \vee \overline{m_{i-1}} l_{i}^{p} \overline{k_{i}^{p}} \vee l_{i}^{n} k_{i}^{n} & b_{i} \in \{\overline{1},0\} \\ s_{i}^{n} &= \overline{d_{i}} b_{i} & (2.6\text{d}) \\ s_{i}^{p} &= d_{i} \oplus b_{i} & s_{i}^{*} \in \{\overline{1},0,1\} & (2.6\text{e}) \end{aligned}$$

The other formats for the redundant binary adder will not be discussed here as they were fully studied by Robertson [10]. The structure of the redundant binary adder is regular. It provides flexibility to the structure of the adder, in other words, the wordlength of the operands can be expanded easily without changing the addition time. This feature of the redundant binary adder is shown in Figure 2.8. And this particular feature is illustrated with an example on redundant binary addition as shown in Figure 2.9. This redundant binary adder structure will be used as the basis of the work in the following chapter.

## 2.2.3 (+,-) SCHEME SBNR ADDER

As mentioned earlier in the section, (+,-) coding scheme SBNR adders [12] can be constructed from simple binary full adders. The circuit to add two SBNR operands  $a=(a^+,a^-)$  and  $b=(b^+,b^-)$  is shown in Figure 2.10 [12].

# 2.2.4 CONVERSION BETWEEN REDUNDANT BINARY AND BINARY NUMBERS

An n-bit unsigned binary number  $[x_{n-1}x_{n-2}...x_0]_2(x_i \in \{0,1\})$  and an n-digit redundant binary number  $[x_{n-1}x_{n-2}...x_0]_{SD2}(x_i \in \{\overline{1},0,1\})$  have the same value  $\sum_{i=0}^{n-1}x_i2^i$ , since the value of binary number  $\{0,1\}$  is a sub-set of the redundant binary number  $\{\overline{1},0,1\}$ . Therefore, no computation is required to convert an unsigned binary number into an equivalent redundant binary integer.

A coi.version from an n-digit redundant binary number  $X=[x_{n-1}x_{n-2}...x_0]_{SD2}(x_i \in \{\overline{1},0,1\})$  into the equivalent binary number  $Y=[y_{n-1}y_{n-2}...y_0]_2(y_i \in \{0,1\})$  has to be performed, because the binary system is the standard representation used externally in most systems. The result, Y, is generated by subtracting  $X^-$  from  $X^+$ , where  $X^-$  and  $X^+$  are n-bit unsigned binary integers formed from the positive digits and the negative digits in X respectively. This conversion can be performed easily by the following equation (2.7):

$$Y(=\sum_{i=0}^{n-1}y_i2^i)=X^*(=\sum_{i=0,x_i=1}^{n-1}x_i2^i)-X^*(=\sum_{i=0,x_i=1}^{n-1}x_i2^i)$$

(2.7)

$$X = 1\overline{1}101\overline{1} (25)$$

$X = 1\overline{1}101\overline{1} (25)$

$X = 1\overline{1}101\overline{1} (25)$

$X = 101010 (42)$

$X = 101010 (42)$

$X = 010001 (17)$

$X = 101010 (17)$

The conversion can be performed in a computation time proportional to  $\log_2 n$  by means of a carry look ahead adder. The number of computation elements of a carry look ahead adder is proportional to n.

Although this approach achieves the desired objective, the subtractor increases the delay through the chip. Therefore, an alternative scheme is needed which carries out the conversion while the data are being deskewed, and without affecting the latency. The 'on-the-fly' conversion was first proposed by Ercegovac and Lang [13] [14] and a modified version was later proposed by Knowles and McWhirter [15]. The conversion circuitry is siewn in Figure 2.12, and the corresponding equations describing the conversion circuitry are:

If

$$f_{i(in)} = 1$$

:  $a_{i(out)} = a_{i(in)}$ ;  $f_{i(out)} = 1$  (2.8)

If

$$f_{i(in)} = 0$$

:  $a_{i(out)} = \begin{cases} a_{i(in)} & \text{if } d_j = 0, 1 \\ \hline a_{i(in)} & \text{if } d_j = \overline{1} \end{cases}$ ;  $f_{i(out)} = \begin{cases} 0 & \text{if } d_j = 0 \\ 1 & \text{if } d_j = \overline{1}, 1 \end{cases}$  (2.9)

The operation of the array is explained in terms of columns of cells. As each digit can affect those of higher significance, each digit is broadcast back up to the relevant column. The estimate is represented by a-lines in each column. These bits are clocked across the array together with the control bit f. This control bit is initially set to 0. Whenever a nonzero digit appears at a lower significance, determining the value of the a-bits above it in the column, all the f-bits in these cells are set to 1. When the f-bit equals to 1, the estimate value of a cannot be altered. This ensures that a lower digit only affects the bits in an MSB direction up to the next 1, but not any higher significance bits. If the next lower significance is zero, then both value of f and a are unchanged. In any case,  $|d_i|$  is appended to  $a_{i-1}$ . An example of the step by step conversion is given in Figure 2.13.

# 2.2.5 REDUNDANCY OVERFLOW

One problem that arises with the SBNR is redundancy overflow. Redundancy overflow occurs when a SBNR number occupies more than the minimum number of signed digit positions. In other words, alternative representations of that number exist. For example, adding a zero to an n digit SBNR operand can yield an n+1 digit result, but it is obvious that an n digit result is sufficient. However, it is possible to compress the result back to an n digit word. In some cases, redundancy overflow can be accommodated by increasing the wordlength to n+1 digits or by extending the degree of redundancy occupied by the MSD, that is increasing the digit range of the MSD. An example of redundancy overflow in addition is shown in Figure 2.14.

# 2.3 REDUNDANT COMPUTER ARITHMETIC

Since the inception of computers, much effort has been expended in search of fast arithmetic techniques. These fast arithmetic techniques have been put into compact high-speed circuits as the computation units in various VLSI systems for real-time applications. One of the speed-up techniques is to introduce redundancy in the implementation of

computer arithmetic. The judicious application of redundancy to the systems can increase the speed of operations and provide structural flexibility. Three algorithms that employ redundancy will be studied in the following sections. They are division, multiplication and square-root. Methods of operation will be discussed through the use of examples.

#### 2.3.1 Division

Division is one of the most complex basic binary arithmetic operations. Several algorithms for fast computation of division of binary numbers have been proposed in the literature. They can be broadly classified into restoring and non-restoring algorithms. The restoring algorithm is another name for the pencil and paper division method that is usually taught in grade school. The restoring method of division requires the subtraction of the right shifted divisor from the scaled remainder at each step. If the partial remainder is negative, a quotient bit '0' is selected as the quotient bit and the original remainder is restored as the new remainder. Otherwise, a'l' is selected as the quotient bit and the partial remainder is the new remainder. In any case, the divisor is right shifted one position. In the non-restoring algorithm, both addition and subtraction are used to avoid the restoring step when the partial remainder yields a negative number. Each step of the non-restoring division method requires the right shifted divisor to be either added to or subtracted from the scaled remainder depending on whether the quotient bit generated in the preceding row was a '0' or a '1' respectively. The introduction of redundancy into the algorithm can speed up the computation time. First, less time is needed to form the partial remainder since the carry propagation is limited. Also, with the quotient digit represented by redundancy resulting in a comparison between the partial remainder and the divisor need not be at the full precision. The most well-known non-restoring with redundancy method is the SRT division[16] [17]. SRT division originated from three initial proposers; D. W.

Sweeney of IBM, J. E. Robertson of the University of Illinois and K. D. Tocher of Imperial College. The first letter of each of their last names forms the acronym.

Performing division requires making a choice of quotient digits starting with the most significant, and proceeding to the least significant digits. A quotient digit is determined by estimating the partial remainder at each stage. The value of the quotient digit is chosen from the redundant digit set  $\{\overline{1},0,1\}$ . The complete quotient is accumulated by the following equation:

$$Q = \sum_{i=0}^{n-1} q_i r^{-i}$$

(2.10)

r: radix

n: number of quotient digits calculated

Q: Accumulated quotient result

q.: quotient digit

The quotient digit chosen at each stage in the division determines the operation of computing the next partial remainder according to the equation:

$$R_{i+1} = rR_i - Dq_i (2.11)$$

r: radix

R<sub>i</sub>: partial remainder at stage i

D: Divisor

q<sub>i</sub>: quotient digit

The dividend is initialized with  $rR_0$ . In this method, the divisor and dividend must be normalized to the same binary range, and the valid quotient digits are in the set  $\{-p,...,0,...,p\}$  where p is restricted to be in the range of  $\frac{r}{2} \le p \le r-1$  according to Atkins [37].

With redundancy introduced into the SRT division, each quotient digit need only use an approximation of the partial remainder, because small errors may be corrected with less significant quotient bits of the opposite sign. Since an approximation of the partial remainder is needed for the quotient bit selection, only a small number of the most significant bits need to be examined, and it can be proved that it is only necessary to examine 3 MSD's of the partial remainder [18]. A division example is shown in Figure 2.15.

# 2.3.2 Square Root

Various rapid square-rooting algorithms, based on the classical non-restoring method, are described by Metze [19] and Oklobdzija [20]. Metze's binary algorithms also give the square-root value in the notation with the digits -1, 0, 1. They are specially fitted

to obtain the result with the minimal possible number of non-zero digits. Algorithms described in [20] also cover non-binary number notations and take into account a bigger number of various digits of the redundant notations of the square root.

Classical binary non-restoring square-rooting is very similar to classical binary non-restoring division method. In both cases, numbers are subtracted or added in successive process steps to decrease the successive partial remainders. The main difference among them is the way that these subtracted or added numbers are formed. But despite this difference, many division methods, being modifications of the classical non-restoring division, can be respectively adapted and used as square-rooting methods. Therefore, the concept of redundancy in division can be applied to the square-rooting method in a similar manner. As in the division method, the square-rooting method is accelerated by decreasing the time to form a partial remainder. In addition, only part of the partial remainder is needed to examine for the root digit extraction. The algorithm described by Majerski [21] is described in this section.

The  $R_j$  is the radicand and assumed to be in the range  $\frac{1}{4} \le R < 1$ , and consequently the square root S is normalized:  $\frac{1}{2} \le S < 1$ . The accuracy of the partial root,  $S_j$ , at the jth step is given by:

$$\left| \sqrt{R_{j}} - S_{j} \right| < 2^{-j}$$

(2.12)

The scaled remainder at the jth step can be defined as follows:

$$Z_{i} = 2^{j}(R - S_{i}^{2})$$

(2.13)

Therefore, the recurrence for computing successive remainders is:

$$Z_i = 2Z_{j-1} - s_j(2S_{j-1} + s_j 2^{-j})$$

where j=1,2,3,..n (2.14)

At the j-1th step,  $s_j$ , the root digit will be determined according to some criterion and the partial remainder  $Z_j$  is formed by the equation specified above. The term in brackets

defines the root digit extractor. The initial remainder  $Z_0$ , is set to the radicand R and the initial estimate of the square root is  $S_1 = \frac{1}{2}$ . The successive root digit extractors are in the form specified by Table 2.4 given below:

| Step | Root digit extractors                                           |

|------|-----------------------------------------------------------------|

| j=1  | 0.s <sub>1</sub> 0000                                           |

| j=2  | s <sub>1</sub> .0s <sub>2</sub> 000                             |

| j=3  | s <sub>1</sub> .s <sub>2</sub> 0s <sub>3</sub> 00               |

| j=4  | s <sub>1</sub> .s <sub>2</sub> s <sub>3</sub> 0s <sub>4</sub> 0 |

Table 2.4: Format of root digit extractors

A complete example is given below in Figure 2.16 to illustrate the procedures:

# 2.3.3 Multiplication

Multiplication is one of the vital computer arithmetic operations in many digital applications such as digital signal processing, process control and computer graphics. High-speed multipliers are essential in real time signal processing systems providing filtering, correlation, and range measurement. As a result, various high-speed multipliers have been proposed and designed on a single-chip LSI [11] [22].

In practice, there are three common multiplier schemes: array multiplier, redundant binary tree, and Wallace tree[23]. The shift-add algorithm is a familiar multiplication method. Parallel multipliers based on this algorithm have been widely used, i.e. the array multiplier. Again, employing redundancy into the multiplication can speed up the computation time, since the partial product is formed independently of the wordlength. Based on the shift-add algorithm, Ercegovac [13] proposed a similar algorithm to perform the multiply-accumulate operation. The general multiply and add operation can be expressed as:

$$M = X \cdot Y + A \tag{2.15}$$

Here, it is assumed that the multiplicand, X, is known at full precision at the start of computation, whereas the multiplier Y and the addend A are assumed to be available in a digit-by-digit manner. For simplicity, it is assumed that all the operands are in the range specified by Table 2.5.

| Operands       | Ranges                              |

|----------------|-------------------------------------|

| Multiplicand X | $\frac{1}{4} \le  X  < \frac{1}{2}$ |

| Multiplier Y   | $\frac{1}{2} \le  Y  < 1$           |

| Addend A       | $\frac{1}{4} \le  A  < \frac{1}{2}$ |