#### University of Windsor

### Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2005

# The design of an asynchronous BCJR/MAP convolutional channel decoder.

Kristofer Patrick Perta *University of Windsor*

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Perta, Kristofer Patrick, "The design of an asynchronous BCJR/MAP convolutional channel decoder." (2005). *Electronic Theses and Dissertations*. 3820.

https://scholar.uwindsor.ca/etd/3820

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# **NOTE TO USERS**

This reproduction is the best copy available.

# The Design of an Asynchronous BCJR/MAP Convolutional Channel Decoder

by

#### Kristofer Patrick Perta

#### A Thesis

Submitted to the Faculty of Graduate Studies and Research through the Department of Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada 2004

Library and Archives Canada Bibliothèque et Archives Canada

Published Heritage Branch

Direction du Patrimoine de l'édition

395 Wellington Street Ottawa ON K1A 0N4 Canada 395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-494-00498-3 Our file Notre référence ISBN: 0-494-00498-3

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### © 2004 Kristofer Patrick Perta

All Rights Reserved. No Part of this document may be reproduced, stored or otherwise retained in a retreival system or transmitted in any form, on any medium by any means without prior written permission of the author.

#### The Design of an Asynchronous BCJR/MAP Convolutional Channel Decoder

by

Kristofer Patrick Perta

#### APPROVED BY:

Dr. R. Lashkari, External Examiner

Department of Industrial and Manufacturing Systems Engineering

Dr. H. Wu, Internal Reader

Department of Electrical and Computer Engineering

Dr. K. Tepe, Supervisor

Department of Electrical and Computer Engineering

Dr. B. Shahrrava, Chair Department of Electrical and Computer Engineering

December 17, 2004

## Abstract

The digital design alternative to the everyday synchronous circuit design paradigm is the asynchronous model. Asynchronous circuits are also known as handshaking circuits and they may prove to be a feasible design alternative in the modern digital Very Large Scale Integration (VLSI) design environment. Asynchronous circuits and systems offer the possibility of lower system power requirements, reduced noise, elimination of clock skew and many other benefits.

Channel coding is a useful means of eliminating erroneous transmission due to the communication channel's physical limits. Convolutional coding has come to the forefront of channel coding discussions due to the usefulness of turbo codes.

The niche market for turbo codes have typically been in satellite communication. The usefulness of turbo codes are now expanding into the next generation of handheld communication products. It is probable that the turbo coding scheme will reside in the next cellular phone one purchases [1].

Turbo coding uses two BCJR decoders in its implementation. The BCJR decoding algorithm was named after its creators Bahl, Cocke, Jelinek, and Raviv (BCJR). The BCJR algorithm is sometimes known as a Maximum Priori Posteriori (MAP) algorithm. This means a very large part of the turbo coding research will encompass the BCJR/MAP decoder and its optimization for size, power and performance.

An investigation into the design of a BCJR/MAP convolutional channel decoder will

be introduced. This will encompass the use and synthesis of an asynchronous Hardware Definition Language (HDL) called Balsa. The design will be carried through to the gate implementation level. Proper gate level analysis will identify the key metrics that will determine the feasibility of an asynchronous design of that of the everyday clocked paradigm.

# Acknowledgments

There are many people I would like to offer thanks and appreciation. The many people that have helped me along the way have proven to be titanic and priceless.

First and foremost, I would like to thank my advisor for truly caring and making these 2 years fly by. Dr. Tepe's expert guidance and colossal technical expertise paved the way for a truly enriched and pleasant graduate program.

I like to extend my thanks to the RCIM group, especially Till Kuendiger for his endless patience and tremendous expertise. I would also like to offer thanks to my committee members, Dr. Huapeng Wu and Dr. Reza Lashkari for their patience and guidance.

To my friends, especially my University of Windsor fellow alumni, Pedram Mokrian, Mike Howard, Alan Soltis, Collin Hayes, Marianne Dent, Colleen Middaugh and Rita Turchi. I would like to say thanks for helping in every conceivable way and giving me great advice.

I'd like to give a warm thanks to my family for putting up with me for the past 2 years and motivating me to get things done.

# Contents

| A  | bstra  | ıct    |                                                  | iv   |

|----|--------|--------|--------------------------------------------------|------|

| A  | ckno   | wledgr | nents                                            | vi   |

| Li | st of  | Figur  | es                                               | xi   |

| Li | ist of | Table  | s                                                | xiii |

| 1  | Inti   | oduct  | ion                                              | 1    |

|    | 1.1    | Async  | chronous Circuits And Systems                    | 1    |

|    |        | 1.1.1  | Fundamental Asynchronous Concepts                | 2    |

|    |        | 1.1.2  | Benefits Of Asynchronous Systems                 | 3    |

|    |        | 1.1.3  | Recent Developments In Asynchronous Applications | 4    |

|    | 1.2    | Chan   | nel Coding                                       | 5    |

|    |        | 1.2.1  | Basic Concepts                                   | 5    |

|    |        | 1.2.2  | Channel Coding Techniques                        | 7    |

| 2  | Asy    | nchro  | nous Circuits And Systems                        | 8    |

|    | 2.1    | Introd | luction                                          | 8    |

|    | 2.2    | Bundl  | led Data (BD) Or Single Rail (SR) Protocols      | . 8  |

|    |        | 2.2.1  | 4 Phase Bundled Data Protocol (4PBDP)            | 9    |

|    |        | 2.2.2  | 2 Phase Bundled Data Protocol (2PBDP)            | 10   |

|    | 2.3    | Dual 1 | Rail Protocols (DRP)                             | 12   |

|    |        |        |                                                  |      |

|   |      | 2.3.1-4 Phase Dual Rail Protocol (4PDRP) Or 1-of-2 RTZ Protocol $$ | 13 |

|---|------|--------------------------------------------------------------------|----|

|   |      | 2.3.2 2 Phase Dual Rail Protocol Or 1-of-2 NRTZ Protocol           | 13 |

|   | 2.4  | Discussion On Protocol Choice                                      | 14 |

|   | 2.5  | Muller Basics                                                      | 18 |

|   |      | 2.5.1 The Muller C-Element                                         | 18 |

|   |      | 2.5.2 The Muller Pipeline (MP)                                     | 20 |

| 3 | Con  | volutional Codes (CC)                                              | 23 |

|   | 3.1  | ,                                                                  | 23 |

|   | 3.2  |                                                                    | 23 |

|   | 3.3  |                                                                    | 27 |

|   | 3.4  |                                                                    | 28 |

|   | 3.5  |                                                                    | 30 |

|   | 3.6  | Viterbi Algorithm                                                  | 31 |

|   | 3.7  | BCJR/MAP                                                           | 34 |

|   |      | 3.7.1 Forward Recursion                                            | 36 |

|   |      | 3.7.2 Backward Recursion                                           | 38 |

|   |      | 3.7.3 State Transition Matrix                                      | 39 |

|   |      | 3.7.4 APPs Of The Symbols                                          | 40 |

| 4 | Vite | erbi Decoder Using Asynchronous Techniques                         | 43 |

|   | 4.1  | Introduction                                                       | 43 |

|   | 4.2  | Basic Building Block Concepts                                      | 43 |

|   | 4.3  | System Overview                                                    | 44 |

|   | 4.4  | System Parameters                                                  | 45 |

|   | 4.5  | Conclusions                                                        | 46 |

| 5 | Des  | igning The BCJR/MAP Decoder                                        | 47 |

|   | 5.1  | ,                                                                  | 47 |

|   | 5.2  | Design Flow                                                        | 47 |

|   |      | 5.2.1 High Level Languages And Tools                               | 47 |

|   |      |                                                                    |    |

viii

|    |       | 5.2.2   | CSP Vs. HDL                                              | 48 |

|----|-------|---------|----------------------------------------------------------|----|

|    |       | 5.2.3   | Balsa: Asynchronous Hardware Language And Synthesis Tool | 49 |

|    |       | 5.2.4   | Feasibility Design Flow                                  | 52 |

|    | 5.3   | The A   | synchronous BCJR/MAP Decoder                             | 53 |

|    |       | 5.3.1   | System Constraints                                       | 53 |

|    |       | 5.3.2   | The Log-MAP Algorithm And Max-Log-MAP Algorithm          | 55 |

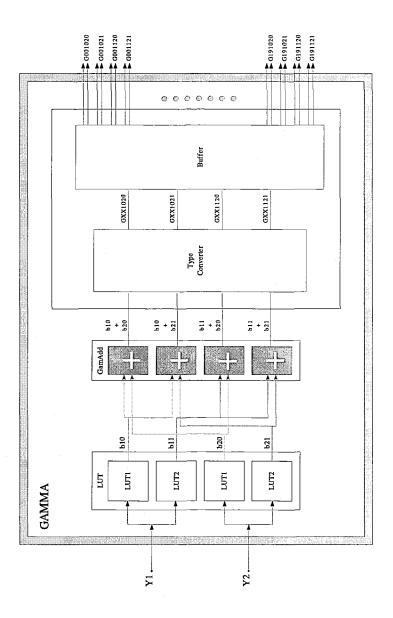

|    |       | 5.3.3   | Gamma Architecture                                       | 55 |

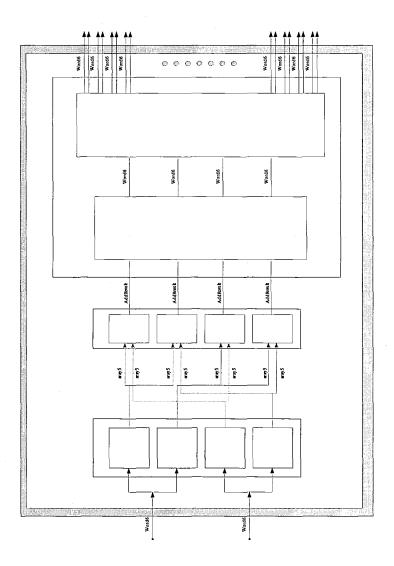

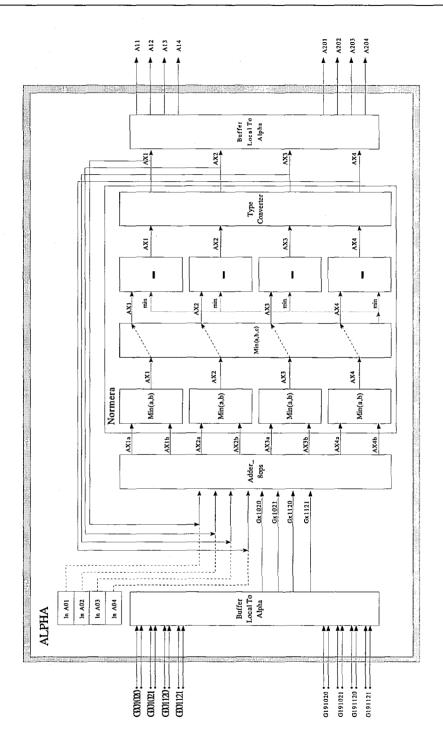

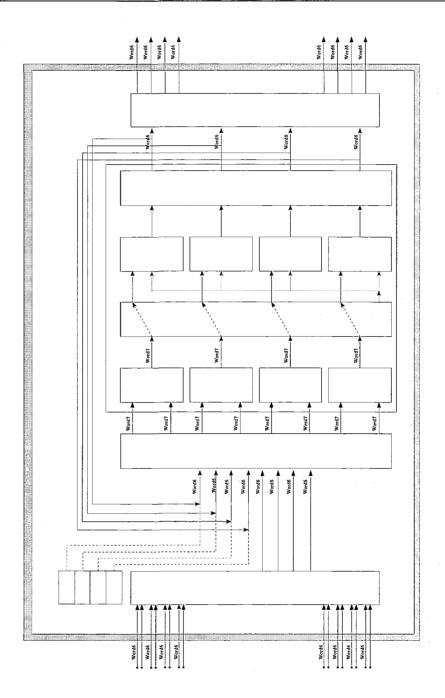

|    |       | 5.3.4   | Alpha Architecture                                       | 57 |

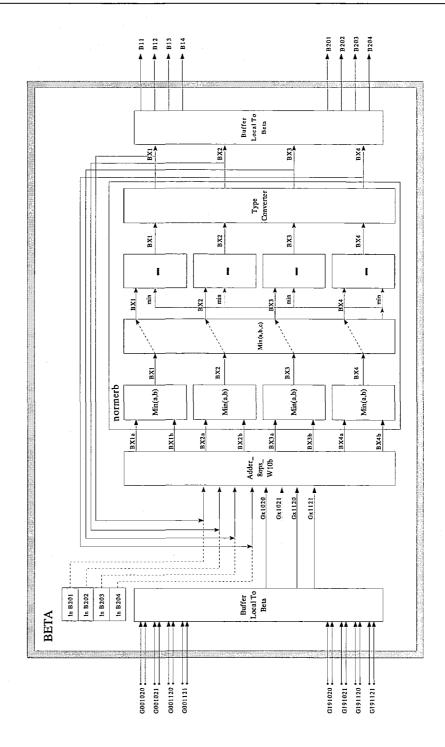

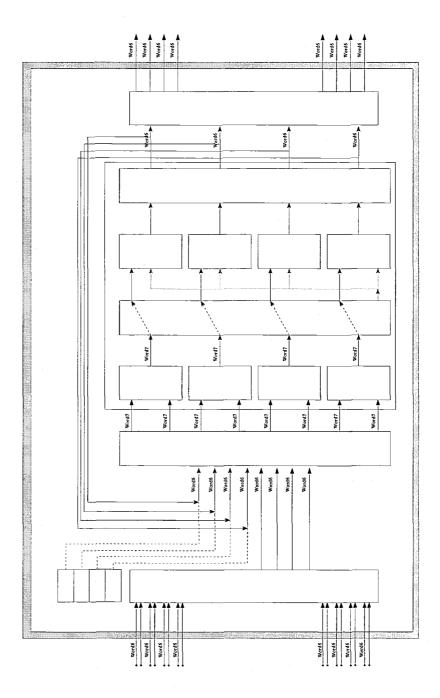

|    |       | 5.3.5   | Beta Architecture                                        | 65 |

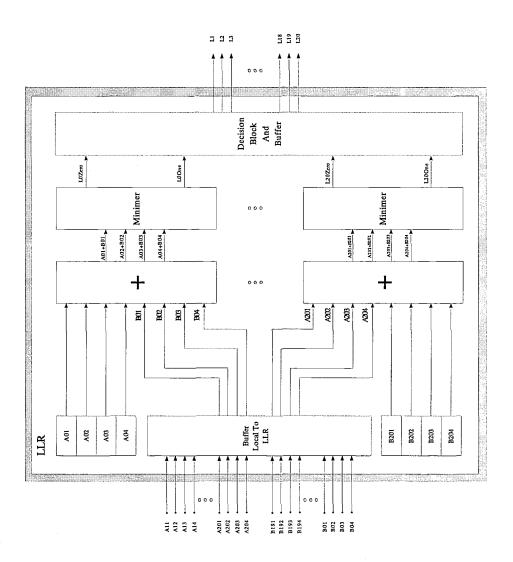

|    |       | 5.3.6   | LLR Architecture                                         | 69 |

|    |       | 5.3.7   | Normalization And The Positive Domain                    | 73 |

| 6  | Sim   | ulation | Architecture and Simulation Results                      | 75 |

|    | 6.1   | Softwa  | re Tools - Verilog, Synopsys and MatLab                  | 75 |

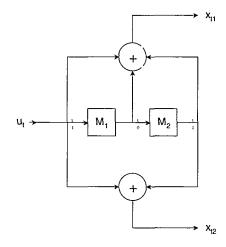

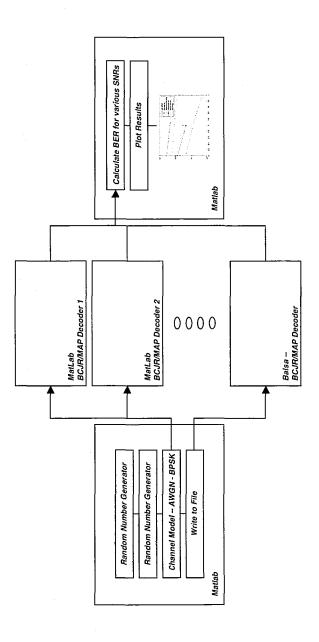

|    | 6.2   | MatLa   | b Simulation Architecture                                | 76 |

|    | 6.3   | Synops  | sys Synthesis Simulation Results                         | 79 |

|    |       | 6.3.1   | Problems Encountered And Possible Remedies               | 84 |

|    |       | 6.3.2   | Future Work                                              | 84 |

| 7  | Sun   | nmary   | Of Contributions and Conclusion                          | 86 |

|    | 7.1   | Asyncl  | nronous VLSI                                             | 86 |

|    | 7.2   | Simula  | tion Architecture                                        | 87 |

|    | 7.3   | BCJR    | MAP Channel Decoding                                     | 87 |

|    | 7.4   | Conclu  | sion                                                     | 87 |

| Re | efere | nces    |                                                          | 88 |

| A  | List  | of Ab   | breviations                                              | 91 |

| В  | Mat   | lab Co  | ode - see enclosed CD                                    | 94 |

| C  | Bals  | sa Cod  | e - see enclosed CD                                      | 95 |

| D            | Balsa To Verilog Netlist Mapping Files:                               |    |

|--------------|-----------------------------------------------------------------------|----|

|              | For TSCM 0.18 micron, Single Poly, Six Metal, Salicide CMOS Process - |    |

|              | see enclosed CD                                                       | 96 |

| ${f E}$      | Verilog Code - see enclosed CD                                        | 97 |

| $\mathbf{F}$ | Synopsys Area, Power And Timing Report Files - see enclosed CD        | 98 |

| V]           | TA AUCTORIS                                                           | 99 |

# List of Figures

| 1.1  | Synchronous Circuit [2]                                              | 2   |

|------|----------------------------------------------------------------------|-----|

| 1.2  | Asynchronous Circuit [3]                                             | 3   |

| 1.3  | Basic Digital Communication System                                   | 6   |

| 2.1  | Bundled Data Channel                                                 | 9   |

| 2.2  | 4-Phase Bundled Data Protocol (4PBDP)                                | 10  |

| 2.3  | Transition Signaling Paradigm [13]                                   | ,11 |

| 2.4  | 2-Phase Bundled Data Protocol (2PBDP)                                | 12  |

| 2.5  | 4-Phase Dual Rail Protocol                                           | 14  |

| 2.6  | 2-Phase Dual Rail Protocol For A 2-Bit Wide Channel                  | 15  |

| 2.7  | 2 Phase, 4 Phase (Push) And 4 Phase (Pull) Protocols                 | 16  |

| 2.8  | Binput Handshake Channel                                             | 17  |

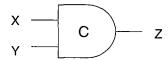

| 2.9  | The C-Element (Denoted By A 'C') And The 'OR' Element Schematic      | 19  |

| 2.10 | Behavior Of C-Element With Inverter [13]                             | 20  |

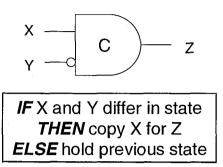

| 2.11 | The Muller Pipeline                                                  | 22  |

| 3.1  | (7,5) Convolutional Encoder With $R_c = \frac{1}{2}$ And $L = 3$ [9] | 24  |

| 3.2  | Finite State Machine (FSM) For (7,5) Encoder [9]                     | 24  |

| 3.3  | Trellis Diagram For The (7,5) Encoder [9]                            | 25  |

| 3.4  | Recursive Systematic Convolutional (RSC) Encoder [17] $\dots \dots$  | 27  |

| 3.5  | Binary Symmetric Channel (BSC) And Binary Erasure Channel (BEC) [9]  | 29  |

| 3.6  | Additive White Gaussian Noise (AWGN) Channel [9]                     | 29  |

| 3.7  | Sample Encoder Output Values With Corresponding Channel Error             | 31 |

|------|---------------------------------------------------------------------------|----|

| 3.8  | Viterbi Algorithm Decoding The Sample Encoder Output Values               | 32 |

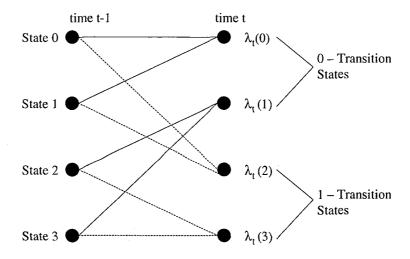

| 3.9  | System Diagram Of The BCJR/MAP Decoding Algorithm                         | 37 |

| 3.10 | Transitions For NRC codes [9]                                             | 41 |

| 4.1  | Viterbi Decoder Using Asynchronous Techniques - System Level [12, 8]      | 44 |

| 5.1  | Balsa Asynchronous Design Flow [19]                                       | 50 |

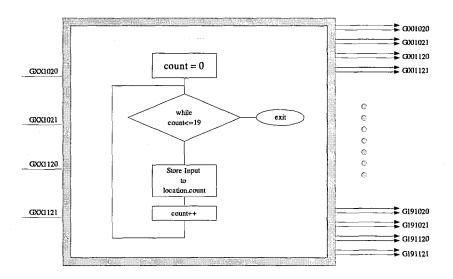

| 5.2  | Gate-Level and Handshake Component Level Of A Modulo-10 Counter [19]      | 51 |

| 5.3  | The Feasibility Asynchronous Design Flow (For The Area And Power Metrics) | 52 |

| 5.4  | Gamma Architecture                                                        | 58 |

| 5.5  | Gamma Architecture - Data Type Structures                                 | 59 |

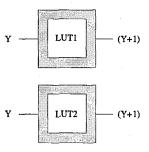

| 5.6  | Gamma Sub-System Architecture - LUT                                       | 60 |

| 5.7  | Gamma Sub-System Architecture - Buffer                                    | 60 |

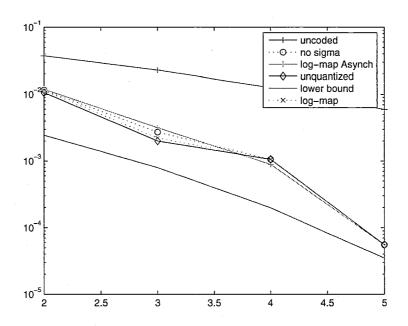

| 5.8  | 1000 Blocks Transmitted Per dB Level - BER Vs. SNR                        | 61 |

| 5.9  | Alpha Architecture                                                        | 62 |

| 5.10 | Alpha Architecture - Data Type Structures                                 | 63 |

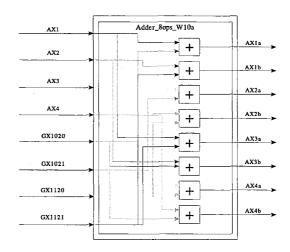

| 5.11 | Alpha Sub-System Architecture - Adder                                     | 64 |

| 5.12 | Alpha Sub-System Architecture - Subtractor                                | 64 |

| 5.13 | Beta Architecture                                                         | 66 |

| 5.14 | Alpha Architecture - Data Type Structures                                 | 67 |

| 5.15 | LLR Architecture                                                          | 70 |

| 5.16 | LLR Architecture - Data Type Structures                                   | 71 |

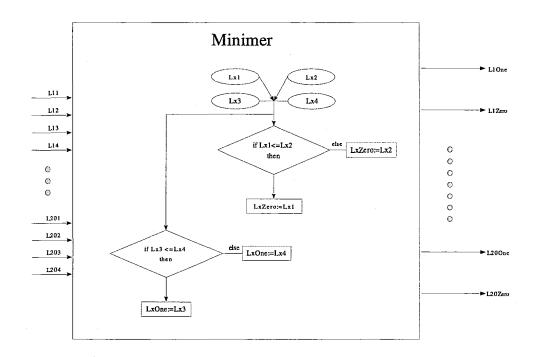

| 5.17 | LLR Sub-System Architecture - Minimer                                     | 72 |

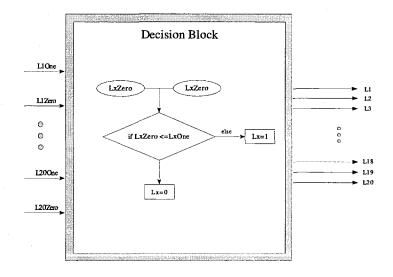

| 5.18 | Alpha Sub-System Architecture - Decision Block                            | 72 |

| 6.1  | 1000 Blocks Transmitted Per dB Level - BER Vs. SNR - Invalid Balsa Design | 77 |

| 6.2  | MatLab System Simulation Architecture                                     | 78 |

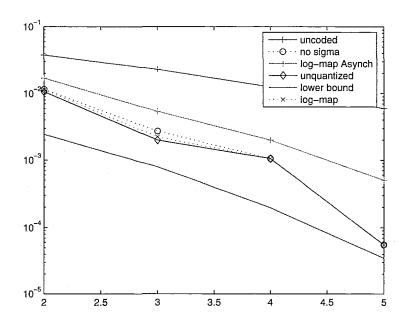

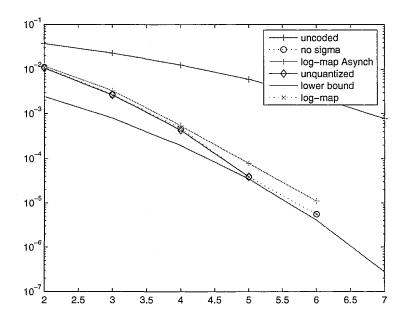

| 6.3  | 10000 Blocks Transmitted Per dB Level - BER Vs. SNR - trunc_5bit Design   | 80 |

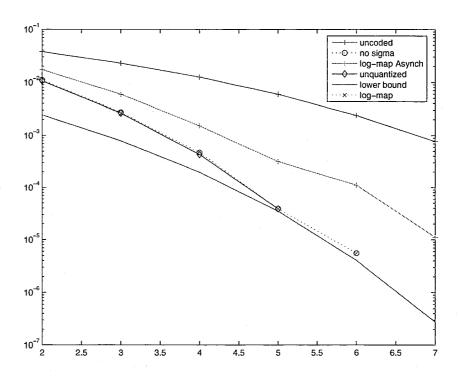

| 6.4  | 10000 Blocks Transmitted Per dB Level - BER Vs. SNR - trunc 4bit Design   | 81 |

# List of Tables

| 2.1 | 1-bit Channel - Encoding Chart                        | 13 |

|-----|-------------------------------------------------------|----|

| 2.2 | Comparison Of Protocols [14]                          | 17 |

| 2.3 | C-Element Truth Table                                 | 18 |

| 2.4 | 'OR' Truth Table                                      | 19 |

| 5.1 | Asynchronous BCJR/MAP System Constraints              | 54 |

| 6.1 | breeze-cost Estimates For Area (Units Are Normalized) | 80 |

| 6.2 | Area, Power And Timing Values                         | 82 |

| 6.3 | Comparison To Synchronous MAP Decoder Designs         | 83 |

# Chapter 1

## Introduction

#### 1.1 Asynchronous Circuits And Systems

The digital VLSI designers are faced with many challenges. Some of the biggest challenges they face include [2]:

- Lowering power consumption

- Addressing clock skew issues

- Decreasing noise

- Increasing performance

These challenges have been in existence for some time. They will become increasingly prevalent in future digital VLSI designs due to scaling issues with technology. There are additional concerns that need to be addressed; however, the issues stated above, are staples in the designer's healthy diet of problems.

To overcome these current obstacles, temporary fixes that simply patch up the greater need for a concise solution are currently employed. The many advantages that asynchronous

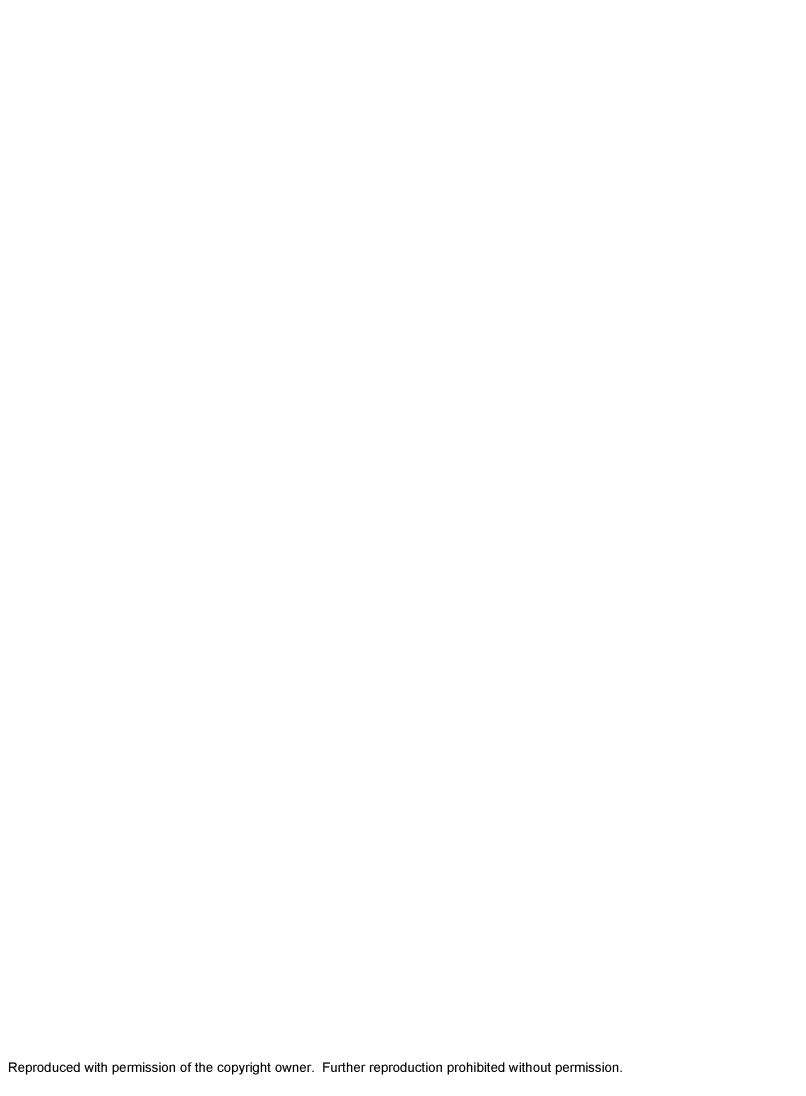

Figure 1.1: Synchronous Circuit [2]

circuits and systems have, e.g., lower power and noise systems than in synchronous systems, are an attractive alternative and the key to the reduction of VLSI design problems.

#### 1.1.1 Fundamental Asynchronous Concepts

To understand the fundamental concepts of asynchronous circuits and systems, one must first examine a synchronous circuit shown in Figure 1.1.

The synchronous circuit works in the following way [2]:

- 1. The current state is stored in an array of registers.

- 2. The next state is then computed from the current state and the input to the combinational logic circuit.

- 3. When the clock makes a transition from low to high, registers are enabled and the next state gets copied into the register. Thus, becoming the next state.

An important note to make is that the clock period depends on the length of time that the combinational logic circuit takes to compute the input and deliver an output.

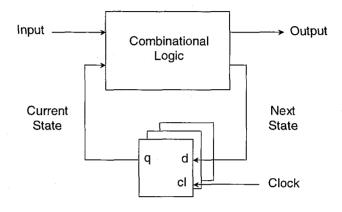

Figure 1.2: Asynchronous Circuit [3]

In an asynchronous system, instead of having a clock as the main synchronizer, coordination is accomplished through the use of acknowledge (ack) and request (req) signals. This is also known as handshake signaling.

In the asynchronous system in Figure 1.2, each stage of the system contains a register and control circuitry. The control circuit communicates with the preceding and succeeding stages by handshake signaling. This in turn controls the state of the registers, i.e., transparent (open) or opaque (closed), which allows the input to pass towards the next register and so forth [2]. The different protocols will be discussed in the next chapter.

#### 1.1.2 Benefits Of Asynchronous Systems

Asynchronous Systems (AS) offer many advantages over the common clocked Synchronous System (SS) design. According to [4], these advantages are as follows, but not limited to:

1. Elimination of Clock Skew - With the need for larger, more complex integrated systems, the synchronization of the clock's arrival time, at different areas of the circuit, is increasingly more difficult to achieve. AS utilizes handshaking protocols to achieve

the synchronization needed within its circuitry, thus eliminating the clock.

- 2. Average Case Performance SS performance is dictated by worst-case condition.

AS performance is dictated by average case conditions, which may lead to increases in performance.

- 3. Adaptivity to Processing and Environmental Variations SS have their clock rate set to allow for correct operation under some allowed variation. AS operate under all variations and simply speed up or slow down as necessary.

- 4. Component Modularity and Reuse AS have no need to synchronize with a global clock, therefore simple system integration with other sub-systems and reuse are simpler than with SS.

- 5. Lower System Power Requirements Additional clock networks are not needed in AS. 15-45 % of electrical power consumed by a SS chip must be devoted to the clock network [5]. There is no waste of energy during spurious transitions, reducing global dynamic power consumption.

- 6. Reduced Noise Activity is uncorrelated in AS, resulting in a more distributed noise spectrum and lower peak noise values.

#### 1.1.3 Recent Developments In Asynchronous Applications

There are many facets that encompass asynchronous circuit design. However, the idea that asynchronous circuits alone are going to revolutionize VLSI design is a false presumption.

The amalgamation of the asynchronous and synchronous conceptual frameworks will offer promising solutions such as Central Processing Units (CPU) that are synchronous internally, yet communicate asynchronously with memory [6].

An important advantage that AS have is their ability to be modular, meaning that they are easily incorporated into other synchronous or asynchronous systems. Commercially, this has been shown with the use of asynchronous circuits in the UltraSPARC IIIi synchronous processor at Sun Microsystems [7].

In the field of communications, Brackenbury et al. [8] have proposed that asynchronous techniques can be used in VLSI implementations of communication systems yielding lower power consumption, specifically the Viterbi decoder. Their design yields 23-29 % less area than a selection of other synchronous implementations with the same design parameters which use the same fabrication process and cell library.

#### 1.2 Channel Coding

In a communication system, the aim is to transmit information from a source to a target. A communication engineer faces many challenges. According to [9], these challenges are as follows, but not limited to:

- Thermal noise

- Changes in signal power

- Short losses of signal power (Erasure)

To tackle these challenges a useful tool is channel coding. When performing channel coding in a communication system, redundant information is introduced into the original signal. This redundancy, at the receiving end, can aid in recovering the original signal that may have been corrupted during transmission.

#### 1.2.1 Basic Concepts

C.E. Shannon [9] demonstrated that channel coding helps realize "reliable" communication over noisy channels. Many landmark achievements have been proposed and used, for instance Convolutional Coding (CC). CC is an error correction channel coding technique that differs from the block coding technique. In block coding, the data stream is divided into a number of blocks and each block is encoded into a code word. In CC, the entire data stream is encoded into a code word.

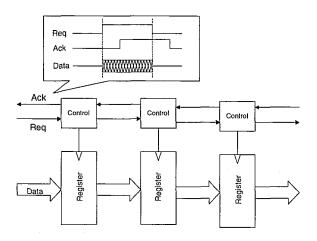

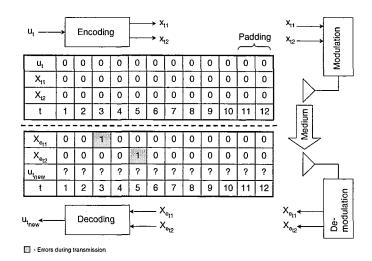

Figure 1.3: Basic Digital Communication System

Coding is a two part process, which involves the encoding of the original information and then followed by decoding at the receiving end. Figure 1.3 shows the system diagram of a basic digital communication system [9].

First, the source produces a message, a digital signal, which will be transmitted to a particular target. If the source produces an analog signal, that signal needs to be made digital.

The source encoder removes most redundancies from the message. This is done so that the efficiency of the overall system increases.

The channel encoder inserts redundancies in a controlled manner so that at the receiver, the system can correct or detect any errors that may have been introduced by the channel or the receiver's front end.

The modulator gives the coded information a new form so that it has the best chance to pass through the channel with as little error as possible.

After passing through the channel, the demodulator, channel decoder and source decoder reverse the original operation of their equivalent partner to produce the original message.

#### 1.2.2 Channel Coding Techniques

With channel coding, the main source of importance lies with the decoder. This is because the decoder is more complex than the encoder. The research that has been done has largely comprised the decoder.

There are many different types of decoding algorithms that are used for convolutional codes. The most popular are the Viterbi Algorithm (VA) and BCJR/MAP. The Viterbi is a maximum-likelihood decoding algorithm [9]. The BCJR is known as a symbol-by-symbol 'Maximum A Posteriori' (MAP) algorithm. The main reason that we use the BCJR/MAP is because it can calculate soft information for the output symbols, which is used in iterative decoding schemes like Turbo Codes [9], [1].

As mentioned earlier, Brackenbury et al. [8] have proposed that asynchronous techniques can be used with application to VLSI implementations of communication systems, specifically the Viterbi decoder.

Applying asynchronous techniques, as previously mentioned, can conceivably advance or offer a feasible design alternative where synchronous techniques cannot. Asynchronous techniques, as seen in [8], can offer the potential for lower power systems.

The natural extension of the work done at the University of Manchester with the asynchronous decoder is to apply asynchronous techniques to other decoding algorithms such as the BCJR/MAP. This thesis investigates the design of an asynchronous convolutional decoder using the BCJR/MAP algorithm.

# Chapter 2

# Asynchronous Circuits And Systems

#### 2.1 Introduction

To fully understand asynchronous circuitry, the different types of protocols and building blocks used must be examined.

The following chapter examines the various types of protocols used and the building blocks required for the implementation of these protocols. This chapter will assist in the knowledge required to understand asynchronous circuits and systems.

### 2.2 Bundled Data (BD) Or Single Rail (SR) Protocols

The two main protocols in asynchronous circuits and systems are the Bundled Data Protocol (BDP) and the Dual Rail Protocol (DRP) [3].

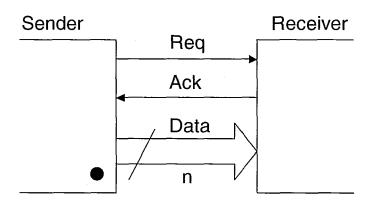

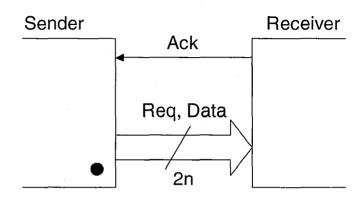

The BDPs, in different literature, are sometimes known as the Single Rail Protocols (SRP). These terms refer to the separate single req and ack wires that are bundled together with the data signals, see Figure 2.1.

The dot in Figure 2.1 denotes the active side of communication. The receiver does not have a dot because it is passive, i.e., only responds (ack) when communicated to (req). This

Figure 2.1: Bundled Data Channel

type of communication channel is called a push channel. The 'n' denotes the number of data bits.

In push channels, data is always valid before the request signal is put high (for 4-phase) or put into a different Boolean state (for 2-phase). The 4 and 2 phase protocols make up the BD and SR protocol.

#### 2.2.1 4 Phase Bundled Data Protocol (4PBDP)

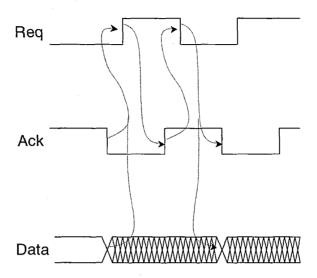

The 4-Phase Bundled Data Protocol (4PBDP) or in other texts the Return to Zero Bundled Data Protocol (RTZBDP), works using the following steps [3], see Figure 2.2:

- 1. The sender supplies data on the data line and sets the request line high. When the request line is put high, constant valid data must be provided on the data line.

- 2. The receiver then absorbs the valid data and sets the acknowledge signal high.

- 3. The sender then responds to the receiver by putting the request line low. When the request line is low, the data on the data line is no longer valid.

9

Figure 2.2: 4-Phase Bundled Data Protocol (4PBDP)

4. The receiver acknowledges the sender by putting the acknowledge line low. After the acknowledge line is low the sender can then start the process again.

The advantage of the 4PBDP is its familiarity to most designers. The disadvantage is that the protocol makes use of the Return To Zero (RTZ) behaviour, which wastes time and energy, i.e. Extra transitions to RTZ in each communication cycle will consume more power and time rather than the Non Return To Zero (NRTZ) behaviour.

The way a certain asynchronous system 'responds to events' is a complex issue. This means, that saying at the beginning of a design that protocol A is better than protocol B because A usually is quicker, may not be true or a realistic assumption.

Note: Depending on the convention of the designer, the circuit's handshaking may be initialized on a rising or falling edge.

#### 2.2.2 2 Phase Bundled Data Protocol (2PBDP)

The 2-Phase Bundled Data Protocol (2PBDP) [3] or in other texts the Non Return To Zero Bundled Data Protocol (NRTZBDP) is different than the 4PBDP in that it uses the NRTZ

Figure 2.3: Transition Signaling Paradigm [13]

#### behaviour.

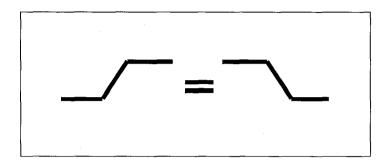

The 2PBDP also uses a different signaling paradigm called transition signaling or event signaling. Normally when circuits are enabled, an adjustment to the Boolean level is how the circuit interprets active or not active.

In the transition signaling paradigm, the circuit is enabled through a transition from '0 to 1' or '1 to 0', see Figure 2.3. The Boolean level in transition signaling is not important; the event or transition is the relevant measurement.

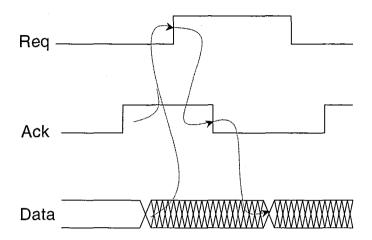

The 2PBDP works using the following steps, see Figure 2.4:

- 1. The receiver sends a transition (in the first case from '0 to 1') on the acknowledge line to signal that it is ready to receive data. The transition on the acknowledge line is also used to signal to the sender that the receiver is done with the previous cycle's data.

- 2. The sender then puts new valid data on the data line and sends a transition on the request line to indicate that valid data is present. Then the process starts anew.

11

Figure 2.4: 2-Phase Bundled Data Protocol (2PBDP)

Note: When the communication starts again, the transitions will not be going from '0 to 1' as mentioned. The next cycle will always produce an opposite transition, e.g., from '1 to 0' if the communication starts from '0 to 1'. This opposite direction in the transition is irrelevant in the transition paradigm because a transition from '0 to 1' holds the same meaning as a transition from '1 to 0'.

### 2.3 Dual Rail Protocols (DRP)

In the BD [3] convention, there exists a need for delay matching. This delay matching is needed so that the order of the signals' events on the sender's end is preserved on the receiver's end. This is done so that valid data is always produced when needed.

There exists another protocol that is insensitive to delays; this protocol is the Dual Rail Protocol (DRP). It contains two main protocols called the 4-phase and 2-phase DRPs.

The '1-of-2' name refers to the protocols use of 2 wires to encode 1-bit of data information.

Table 2.1: 1-bit Channel - Encoding Chart

| For n=1   | d.t | d.f |

|-----------|-----|-----|

| Empty     | 0   | 0   |

| Valid '0' | 0   | 0   |

| Valid '1' | 0   | 0   |

| Not Used  | 0   | 0   |

#### 2.3.1 4 Phase Dual Rail Protocol (4PDRP) Or 1-of-2 RTZ Protocol

The 4-Phase Dual Rail Protocol (4PDRP) [3], also known as the 1-of-2 RTZ protocol is very similar to the 4PBDP except that the request signal is encoded into the data signals. The protocol uses two wires per bit of information, d; one wire d.t. is used to transmit a Boolean logic '1' (true) and one wire d.f. is used to transmit a Boolean logic '0' (false). Once, again 'n' refers to the number of information bits, see Table 2.1.

This method of communication is robust since the communication of the sender and receiver can be done reliably, regardless of delays. Hence, the protocol is 'delay insensitive'.

The 4PBDP works in the following way, see Figure 2.5:

- 1. The sender supplies a valid codeword, which is also a request put into the high level.

- 2. The receiver absorbs the valid codeword and sets acknowledge high.

- 3. The sender then responds to the acknowledge by supplying an empty codeword.

- 4. The receiver then sets acknowledge low. After the acknowledge line is low, the process can start over again.

#### 2.3.2 2 Phase Dual Rail Protocol Or 1-of-2 NRTZ Protocol

The 2-Phase Dual Rail Protocol (2PDRP) otherwise known as the 1-of-2 NRTZ protocol encodes the data signals in the request signals. It also uses 2 wires {d.t, d,f} per bit. The

Figure 2.5: 4-Phase Dual Rail Protocol

information is encoded as transitions (events) as discussed in Section 2.2.2. Unlike the 4-phase system in Section 2.2.1, there is no empty value. Valid information is acknowledged, followed by another valid messaged and then the process continues. Figure 2.6 demonstrates a 2-bit wide channel using the 2PDRP.

#### 2.4 Discussion On Protocol Choice

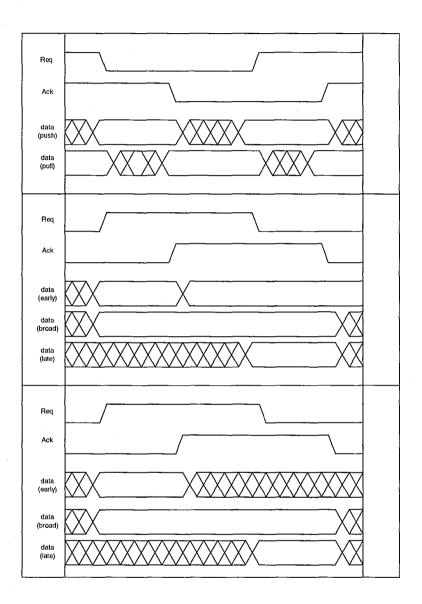

The previous sections have outlined the main protocols used to design asynchronous circuits. However, these 4 protocols can be combined to offer a plethora of protocol possibilities. In addition, the dual rail protocol can be further manipulated to offer extra encoding per bit of information, e.g., 4 wires to encode 1-bit of data, known as 1-of-4.

To give a general idea of the many possibilities of protocols used to design asynchronous circuits, the other channel types used must be briefly mentioned. Thus far, the 'push' channel was the only channel discussed.

In fact, there are 3 other channels used. The 'nonput' channel, is a channel that passes no data between channels. It is simply used as a coordinating link, i.e: req, ack and data

Figure 2.6: 2-Phase Dual Rail Protocol For A 2-Bit Wide Channel

link.

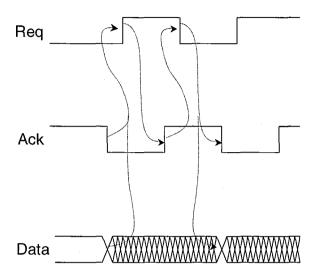

The 'pull' channel is the opposite of the push channel in that the receiver is the active party in the initiation of communication and the sender is the passive member. Figure 2.7 shows the different data validity schemes for the different types of channels.

The 'biput' channel is where the data is passed in both direction along with the acknowledge and request signals, see Figure 2.8.

The choice of protocol offers different features that may or may not suit the needs of the application. The protocol is an important choice and one that will influence the applications behaviour.

In [14], a comparison on asynchronous design styles were presented. They compared the 2PBDP, 2PDRP, 4PDRP, 1-of-4 RTZ and 1-of-4 NRTZ.

The comparison study yielded interesting results with respect to the potential for the 1-of-4 protocol. However, a general view of all protocols is outlined, which tends to show that the 2PBDP is a very reliable protocol with respect to area and power, see Table 2.2.

The 2PBDP offers a potential increase in circuit speed and decrease in area (wires/bit)

Figure 2.7: 2 Phase, 4 Phase (Push) And 4 Phase (Pull) Protocols

Figure 2.8: Binput Handshake Channel

Table 2.2: Comparison Of Protocols [14]

|               | Area (wires/bit) | Energy (transitions/bit) |  |

|---------------|------------------|--------------------------|--|

| 2PBDP         | 1                | 1/2 (avg.)               |  |

| 2PDRP         | 2                | 1                        |  |

| 4PDRP         | 2                | 1                        |  |

| 1-of-4 (RTZ)  | 2                | 1                        |  |

| 1-of-4 (NRTZ) | 2                | 1/2 (avg.)               |  |

Table 2.3: C-Element Truth Table

| X | Y | Z                       |

|---|---|-------------------------|

| 0 | 0 | 0                       |

| 0 | 1 | Retain previous Z value |

| 1 | 0 | Retain previous Z value |

| 1 | 1 | 1                       |

and energy (transitions/bit). This increase in speed and decrease in energy and area costs is directly correlated to the NRTZ behaviour that the 'transition signaling' paradigm offers.

The downfall to the 2PBDP is the overhead required to implement the delay matching circuitry and the extra level of complexity of transition signaling circuitry. However, the speed gained in using the 2PBDP would be a beneficial due to the computationally heavy nature of the BCJR/MAP algorithm. This will be investigated in later chapters.

#### 2.5 Muller Basics

Muller [15] invented the Muller C-Element in 1959. It is the most often used primitive in asynchronous circuit implementations. The Muller pipeline, which is used in most asynchronous protocol implementations, is the backbone for handshaking circuitry [3].

#### 2.5.1 The Muller C-Element

In asynchronous circuits, signals are required to be valid at all times. Indication and acknowledgment plays an important role in the design of these circuits. This means that every signal transition has a meaning and that hazards and races should be avoided [3].

The C-Element primitive is better suited to these types of constraints. The C-Element is a state holding element that acts as an 'OR' element for events. Unlike the 'OR' element, the C-Element can represent an acknowledgment when both inputs are '1' or '0', see Figure 2.9, Table 2.3 and Table 2.4.

Figure 2.9: The C-Element (Denoted By A 'C') And The 'OR' Element Schematic

Table 2.4: 'OR' Truth Table

| X  | Y | Z |

|----|---|---|

| 0  | 0 | 0 |

| 0_ | 1 | 1 |

| 1  | 0 | 1 |

| 1  | 1 | 1 |

Figure 2.10: Behavior Of C-Element With Inverter [13]

## 2.5.2 The Muller Pipeline (MP)

In most asynchronous protocols, when analyzing the circuit implementation, the backbone that is always present is that of the MP. The MP is built from C-Elements and inverters. The MP is the structure that controls the handshaking in asynchronous circuits.

To understand the concept of the MP [3], the MP must be first put in its initial state. The initial state of all C-Elements are X='0' and Y='1', therefore Z='0'.

When an inverter (denoted by a circle) is placed on the input of the C-Element, it works in the following way, see Figure 2.10.

Network A, in Figure 2.11, is ready to send data to the MP. It sends a constant '1' on the req(in) line. This then starts a ripple effect through the MP. Note: The initial state of all C-Elements are X='0' and Y='1', therefore Z='0'.

Examining 'node 1', we see that after A has sent a '1', the value at 'node 1' will become a '1'. This changes the Req signal heading to the 2nd C-Element. This also sends an ack signal back to A.

'Node 2', then changes to a '1' bringing the value at 'node 3' to '1'. This has no effect on first C-Element. The first C-Element is now in a ready state. The '1' from the Req(in) line, propagates through all the C-Elements and puts each C-Element in a ready state (X='1', Y='1' and Z='1' (previous state)).

Once all C-Elements are in the ready state, the system can either send a constant '0' or '1' on the req(in) line. This '0' or '1' will propagate through the MP as did the first request of '1'. The MP acts as a flow through First-In First-Out (FIFO) circuit.

In an abstract way, the MP can be thought of as a wave. Where the wave carries a '1' through the MP or a '0'.

There are few other points that should be mentioned about the MP. Data doesn't necessarily have to flow from A to B. The symmetry of the MP makes the MP bi-directional. The complexity from A to B is the same from B to A. Therefore, communication can start from either 'A to B' or 'B to A'.

The MP also can be used for 2-phase or 4-phase protocols. The only difference between the two protocols is how the designer interprets the signals.

Figure 2.11: The Muller Pipeline

# Chapter 3

# Convolutional Codes (CC)

## 3.1 Introduction

P. Elias [9] proposed CC in 1954. CC is an error correction channel coding scheme that is the alternative to block codes.

As previously mentioned, in block coding, a data stream is broken up into separate blocks of information and then each block is encoded into an n-bit codeword. CC differs from block coding in that they encode the complete data stream into a single codeword [10].

There are several types of decoding algorithms used for CC. This chapter will focus on the Viterbi Algorithm and the BCJR/MAP algorithm.

# 3.2 Encoding

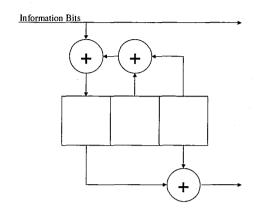

Before the decoding algorithms are discussed, the encoding process must be examined. In CC, encoding is accomplished through shift registers and adders ('XOR' elements), see Figure 3.1.

The rate or ratio  $(R_c)$  of source bits (k) to code bits (n) is known as the code rate.

Figure 3.1: (7,5) Convolutional Encoder With  $R_c=\frac{1}{2}$  And L=3 [9]

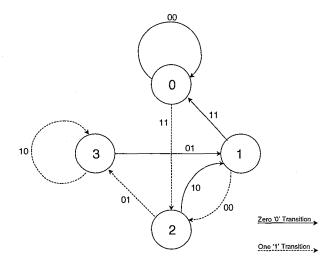

Figure 3.2: Finite State Machine (FSM) For (7,5) Encoder [9]

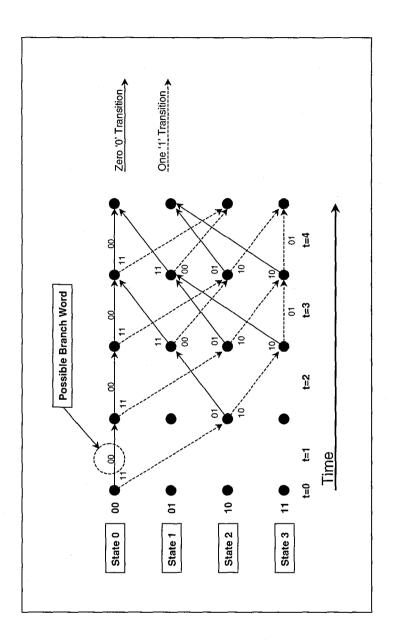

Figure 3.3: Trellis Diagram For The (7,5) Encoder [9]

The constraint length (L) is defined as M+1, where M is the number of Memory elements needed. The memory describes how many bits in the input sequence will affect the output sequence at a time. The generator sequence can be thought of how the actual wiring of the encoder is carried out, i.e., where a binary '1' mean there exists a connection and a binary '0' represents an absence of a connection. The standard for the sequence is usually represented by the octal number system, e.g.,  $(7,5)_8 = (111,101)_2$ . Figure 3.1 shows a (7,5) convolutional encoder with  $R_c = \frac{1}{2}$  and L = 3.

The encoder, before the source bits of information enter it, is filled with zeros, i.e., the all-zero state. This brings the encoder to an initial state, this process is sometimes known as 'padding the systems with zeros', 'flushing' or 'trellis termination'. This 'flushing' makes the decoding process easier but causes rate loss. The process is satisfactory for long block lengths but for relatively short block lengths, the loss is unacceptable and causes degradation to the system's performance.

'Flushing' works in the following way; the information bits are entered, k bits at a time. The corresponding code bits are then transmitted over the channel. This process continues and when all sets of k bits are sent, the encoder is sent zeros to put the encoder in the all-zero state. Then the system is ready for the next transmission. The amount of zeros needed for padding is k(L-1). For the (7,5) encoder example, the systems needs k(L-1) = 1(3-1) = 2 'zeros'.

For convolutional encoding, there are two main types of encoders. They are the Recursive Systematic Convolutional (RSC) see Figure 3.4 and Non-Recursive Convolutional (NRC) encoders see Figure 3.1. In a turbo encoder, typically we would find 2 NRC encoders. The NRC encoders are used due to their advantage in performance at low Signal To Noise Ratio (SNR) values in the communication channel. [16]. However, in terms of a standalone BCJR/MAP decoder, using one type of encoder over another does not matter in terms of performance.

RSC encoders are different than NRC encoders due to the feedback nature in their shift registers implementations, see Figure 3.4. NRC encoders are implemented as Finite Impulse Response (FIR) Filters, however, RSC are implemented as Infinite Impulse Response (IIR)

Figure 3.4: Recursive Systematic Convolutional (RSC) Encoder [17]

filters. For the sake of simplicity with this project, a NRC encoder was utilized. This has ramifications when the Log Likelihood Ratio (LLR) calculation is executed in the decoder, i.e., more storage and additions are needed with the RSC implemention because all three metrics (alpha,beta and gamma) are needed for the LLR calculation unlike the NRC implementation were only two metrics are needed (alpha and beta). Therefore, an NRC code implementation will more than likely have smaller area and lower power consumption than RSC without the expense of performance.

The convolutional encoder can be presented in various forms, e.g., functional diagram shown in Figure 3.1, finite state diagram shown in Figure 3.2 and the trellis diagram shown in Figure 3.3.

# 3.3 Decoding

Decoding is the reverse act of encoding. Decoding compared to encoding is more complex in terms of the amount of computation and memory requirements needed. There are two types of decoding frameworks, known as hard and soft decision decoding.

Hard-decision decoding is the process of using two quantized levels from the demodulator as the symbols used for comparison methods. In hard decision decoding, the quantized levels are binary values of '0' and '1'. Soft-decision decoding uses more than two quantized levels and this yields better performance. Hard-decision decoding produces an extra 2 to 3 dB performance loss over that of soft-decision decoding [11].

# 3.4 Channel Model

Before the decoding algorithms are demonstrated, the channel model used must be first discussed. A channel is the medium that "transfers or stores information" that is used in a communication cycle [9]. The physical medium can be wire, e.g., twisted pair communication, air (wireless), glass (fibre-optic), etc.

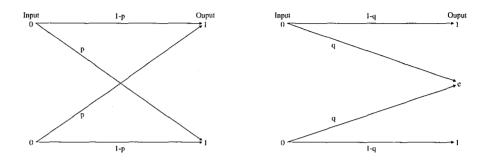

In this study, the modulator, channel and demodulator make up the channel model. There are three important channel models used. They are the Binary Symmetric Channel (BSC) and Binary Erasure Channel (BEC) which are forms of the Discrete Memoryless Channel (DMC), see Figure 3.5 and Figure 3.5. The channel model used in this thesis is the Additive White Gaussian Noise (AWGN) Channel which is a type of discrete-time channel characterized by a set of probability density functions, see Figure 3.6.

The input,  $X = \{0, 1\}$ , to a channel in a digital communication system is a sequence of binary numbers. The output,  $Y = \{0, 1\}$ , is also a sequence of binary numbers. Suppose the channel introduces "statically independent errors" in the transmitted binary sequence with the average probability p.

Therefore,

$$Pr(Y = 0 \mid X = 1) = Pr(Y = 1 \mid X = 0) = p$$

(3.1)

$$Pr(Y = 1 \mid X = 1) = Pr(Y = 0 \mid X = 0) = p - 1$$

(3.2)

Thus, the BSC is obtained, see Figure 3.5.

Another DMC is the BEC, with inputs, X = 0, 1, and outputs, Y = 0, e, 1, where e is an 'erasure', meaning the channel cannot decide if the output is a '1' or a '0', see Figure 3.5.

Figure 3.5: Binary Symmetric Channel (BSC) And Binary Erasure Channel (BEC) [9]

Figure 3.6: Additive White Gaussian Noise (AWGN) Channel [9]

As mentioned, the AWGN channel is the channel model used in this thesis. It is shown in Figure 3.6. This channel model includes the "output alphabet equal to the entire real line",  $Y = \{-\infty, \infty\}$ , and the "input alphabet has a finite number of symbols",  $X = \{x_1, x_2, \dots, x_{t-1}\}$ . The AWGN channel is characterized by the following probability density function,

$$p(y \mid X = x_i) = \text{ where } i = 1, 2, \dots, l - 1$$

(3.3)

The channel equation is as follows,

$$Y = X + N \tag{3.4}$$

where N is a zero mean Gaussian random variable with variance  $\sigma^2$  and  $X = x_i$  where i = 1, 2, ..., l - 1. The probability distribution function of Y with a given X is Gaussian with mean  $x_i$  and variance  $\sigma^2$ . Then,

$$p(y \mid X = x_i) = \frac{1}{\sqrt{2\pi}\sigma} e^{-(y-x_i)^2/2\sigma^2}$$

(3.5)

Therefore, for a given input sequence,  $x_{t,i}$ , of symbols, n, where t = 1, 2, ..., n and  $x_{t,i} \in X$ , the output sequence for a time, t, is given by the following equation,

$$y_t = x_{t,i} + n_t \tag{3.6}$$

The condition of the channel when memoryless can be expressed as,

$$Pr(y_1, y_2, ..., y_n \mid X = x_{1,t}, ..., X) = \prod_{t=1}^{n} Pr(y_t \mid X = x_{t,t})$$

$$= \left(\frac{1}{2\pi\sigma^2}\right) \exp\left\{-\frac{1}{2\sigma^2} \sum_{t=1}^{n} (y_t - x_{t,t})^2\right\}$$

(3.7)

The channel also, in our case, depends on the modulation used. This thesis uses the Binary Phase Shift Keying (BPSK) modulation technique. This means that any level value of '0' gets mapped to '-1' and any level value of '1' gets mapped to '1'.

# 3.5 Sample Values

Section 3.6 will use Figure 3.7 to obtain encoder output with corresponding channel errors, which is the input to the decoder after demodulation.

Note: Channel errors in Figure 3.7 are highlighted in red.

Figure 3.7: Sample Encoder Output Values With Corresponding Channel Error

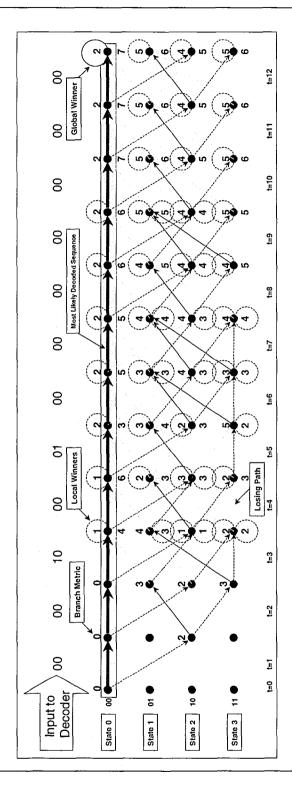

# 3.6 Viterbi Algorithm

The Viterbi is a maximum-likelihood decoding algorithm [9]. Figure 3.8 shows how an example of the Viterbi Algorithm works. The bold line along the top is the final most likely decoded sequence, all '0' transitions, which is the correct decoded sequence from the sample. The lightly coloured lines are the lines during the algorithm in which we eliminate as being not a likely transition. The circled numbers signify the local winner. The final circled number at the top right signifies the global winner.

In its simplest form, a specific sequence is chosen as the most likely sequence if the likelihood of that sequence is larger than the likelihood of all other possible sequences.

The algorithm uses the following computational properties to find the most likely sequence:

- Branch Word or Label: Is the encoder output due to the transition of an encoder state to another, see Figure 3.8.

- Branch Metric: Is the distance between the sequence received and the possible branch

Figure 3.8: Viterbi Algorithm Decoding The Sample Encoder Output Values

word. For hard-decision decoding, it is usually Hamming distance and Euclidean distance for soft-decision decoding. Hamming Distance between two code words,  $c_i$  and  $c_j$ , is the number of components that the two words differ from each other. Hamming distance is denoted by  $d(c_i, c_j) = d_{ij}^H$ . Euclidean distance,  $d_{ij}^E$  can be expressed in terms of Hamming distance,

$$\left(d_{ij}^E\right)^2 = 4d_{ij}^H \mathcal{E} \tag{3.8}$$

where  $\mathcal{E}$  is the signal energy [17]

- Path Metric: Is the summation of branch metrics.

- *Trellis*: Is the basis for a visual and structural representation of the calculations that need to be carried out for the algorithm. The trellis shows the states or nodes of the encoder at different moments in time.

Now that the structural metrics have been defined, the following steps make up the Viterbi algorithm:

- 1. The path metrics must be found for every path at each node. This is done by summing the correct branch metric to the related survived path metric.

- 2. The two paths, there will be two paths for the K=3 case, that enter each node or state must be compared. The path with the smallest path metric is selected. This path is the survivor path metric. This step needs to be performed in parallel for 2K-1 states.

- 3. This procedure needs to be repeated until the end of the trellis is reached.

When the end of the trellis is reached, one will notice that all paths merge into a common state (if your system is padded or flushed). This means that only one path survives. If you trace-back that path, you can obtain the most likely original signal.

The depth of trellis in practice is five times the constrain length. There is no performance increase if you deepen the trellis. However, the depth is dependant on the rate of the encoder.

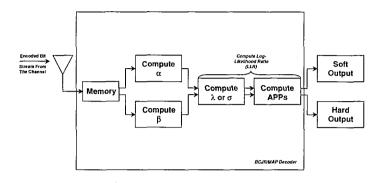

# 3.7 BCJR/MAP

Bahl et al. [24], first published the BCJR algorithm otherwise known as the 'symbol by symbol' Maximum A Priori (MAP) algorithm, in 1974 [24]. This algorithm was put aside for decoding convolutional codes due to its inherent complexity. However, the BCJR/MAP algorithm gained a second wind with the introduction of Turbo Codes. The main reason to use this algorithm is that it produces soft likelihood value of symbols on the output.

"The BCJR/MAP is an optimum decoding algorithm used to minimize the symbol error rate for the terminated convolutional codes. The BCJR/MAP estimates the A Posterior Probability (APP) of the states and the state transitions of a convolutional code and then the APPs of the symbols. [9]"

The BCJR/MAP algorithm, though complex, is very similar to the Viterbi algorithm. As mentioned above, the Viterbi, in its simplest form, chooses the most likely sequence as the final decoded sequence. This is done through several computational steps in a forward motion (left to right) through the trellis.

Like the Viterbi Algorithm, the BCJR/MAP algorithm search Forward and Backwards (FB) through the trellis for a 'received channel sequence' defined by  $Y_1^L = \{Y_1, Y_2, ..., Y_L\}$  created by a 'channel input sequence' (encoder)  $X_1^L = \{X_1, X_2, ..., X_L\}$ . The BCJR/MAP is otherwise known as the FB algorithm. Depending on the channel model,  $Y_t = (y_{t,1}, y_{t,2}, ..., y_{t,n})$  and  $X_t = (x_{t,1}, x_{t,2}, ..., x_{t,n})$  for a 1/n code and  $x_{t,i}$  and  $y_{t,i}$ , i = 1, 2, ..., n. In this thesis, we use AWGN with BPSK, therefore  $x_{t,i} \in \{-1,1\}$  and  $y_{t,i} \in \{-\infty,\infty\}$ . This FB recursion will produce state probabilities defined as  $\alpha_t(\cdot)$ .

To produce the state probabilities or the state transitions 3 different values are needed:

- The forward recursion probability function,  $\alpha(\cdot)$ .

- The backward recursion probability function,  $\beta(\cdot)$ .

- The state transition matrix,  $\Gamma(m', m)$ .

The forward recursion is defined as the joint probability that the state of the system is m at time t,  $S_t = m$ , and the received channel sequence from time 1 to t is  $Y_1^t$ ,

$$\alpha_t(m) = Pr\left\{S_t = m; Y_1^t\right\} \tag{3.9}$$

The backward recursion is defined as the probability that the received channel sequence from time t+1 to L is  $Y_{t+1}^L$ , given that the state m at time t is  $S_t=m$ . Then,

$$\beta_t(m) = Pr\left\{Y_{t+1}^L \mid S_t = m\right\} \tag{3.10}$$

The state transition probability matrix is defined as the conditional probability that the state m at time t is  $S_t = m$  and the received channel sequence at time t is  $Y_t$ , while being at the state m' at time t - 1,  $S_{t-1} = m'$ . Then,

$$\Gamma(m', m) = Pr\{S_t = m; Y_t \mid S_{t-1} = m'\}$$

(3.11)

The next step involves estimating the APPs of the states and the state transitions for the received channel sequence. They are defined as follows,

$$Pr\left\{S_{t} = m \mid Y_{1}^{L}\right\} = \frac{Pr\left\{S_{t} = m; Y_{1}^{L}\right\}}{Pr\left\{Y_{1}^{L}\right\}}$$

(3.12)

and

$$Pr\left\{S_{t}=m; S_{t-1}=m' \mid Y_{1}^{L}\right\} = \frac{Pr\left\{S_{t}=m; S_{t-1}=m'; Y_{1}^{L}\right\}}{Pr\left\{Y_{1}^{L}\right\}}$$

(3.13)

The received sequence probability,  $P\left(Y_1^L\right)$ , is constant during calculation, then the joint probabilities of the states and the received channel sequence denoted as  $\lambda\left(m\right)$ , and the joint probability of the state transitions and the received channel sequence denoted as  $\lambda\left(m\right)$  can be calculated. They are defined as followed,

$$\lambda_t(m) = Pr\left\{S_t = m; Y_1^L\right\} \tag{3.14}$$

and

$$\sigma_t(m',m) = Pr\left\{S_{t-1} = m'; S_t = m; Y_1^L\right\}$$

(3.15)

Mathematically,  $\lambda_t(m)$  and  $\sigma_t(m', m)$  can be expressed as  $\alpha(m)$ ,  $\beta(m)$  and  $\Gamma(m', m)$ . By using Markov and DMC properties [9] for the derivations,

$$\lambda_{t}(m) = Pr\left\{S_{t} = m; Y_{1}^{L}\right\} \cdot Pr\left\{Y_{t+1}^{L} \mid S_{t} = m; Y_{1}^{t}\right\}$$

$$\lambda_{t}(m) = \alpha(m) \cdot Pr\left\{Y_{t+1}^{L} \mid S_{t} = m\right\}$$

$$\lambda_{t}(m) = \alpha(m) \cdot \beta(m)$$

(3.16)

and

$$\sigma_{t}(m',m) = Pr\{S_{t-1} = m'; Y_{1}^{t-1}\} \cdot Pr\{S_{t} = m; Y_{t} \mid S_{t-1} = m'\} \cdot Pr\{Y_{t+1}^{L} \mid S_{t} = m\}$$

$$\sigma_{t}(m',m) = \alpha_{t-1}(m') \cdot \Gamma_{t}(m',m) \cdot \beta_{t}(m)$$

(3.17)

When  $\lambda_t(m)$  or  $\sigma_t(m, m')$  are found, the APPs of the data symbols can be calculated. Figure 3.9 shows the system diagram and the basic building blocks of the BCJR/MAP decoding system.

#### 3.7.1 Forward Recursion

The forward recursion probability function,  $\alpha(\cdot)$ , is the sum of all probabilities of the state m for the received channel sequence from time 1 to t. It is described as follows,

$$\alpha(m) = Pr\left\{S_t = m; Y_1^t\right\} = \sum_{m'}^{2^{K-1}-1} Pr\left\{S_{t-1} = m'; S_t = m; Y_1^t\right\}$$

(3.18)

Figure 3.9: System Diagram Of The BCJR/MAP Decoding Algorithm

Rewriting equation 3.18 using the Markov chain and the DMC properties, the equation becomes,

$$\alpha(m) = \sum_{m'}^{2^{K-1}-1} Pr\left\{S_{t-1} = m'; Y_1^{t-1}\right\} \cdot Pr\left\{S_t = m; Y_t \mid S_{t-1} = m'\right\}$$

$$\alpha(m) = \sum_{m'}^{2^{K-1}-1} \alpha_{t-1}\left(m'\right) \cdot \Gamma\left(m', m\right) \text{ for } t = 1, 2, \dots, L$$

(3.19)

Now using vector notation, we can take  $\alpha_t$  as an N tuple row vector with the  $m^{th}$  entry being the probability of being in the  $m^{th}$  state at time t, where N is the number of states for memory, M, then,  $N = 2^M$ . Therefore, equation 3.19 is a row vector multiplied with a matrix. Note, the bold character refers to a matrix. Therefore,

$$\alpha_t = \alpha_{t-1} \cdot \Gamma_t \tag{3.20}$$

$\alpha_t(m)$  requires normalization during each iteration to prevent underflow, since  $Pr\left\{Y_1^L\right\}$  is not used in the calculation. Then, the normalized forward recursion,  $\bar{\alpha}_t(m)$ , is,

$$\bar{\alpha}_t(m) = \frac{\alpha_t(m)}{\sum_{m'=0}^{N-1} \alpha_t(m')}$$

(3.21)

The forward recursion expressed with normalization is as follows,

$$\alpha_t(m) = \sum_{m'=0}^{N-1} \bar{\alpha}_{t-1}(m') \cdot \Gamma_t(m', m)$$

(3.22)

$\alpha_0$ , the initial conditions, can be determined by analyzing the starting state of the encoder. When the encoder starts at state m, then  $\alpha_0 = (0, \dots, 1, \dots, 0)$  where the  $m^t h$  entry is 1.

#### 3.7.2 Backward Recursion

Using the same procedure as in the forward recursion, the backward probability function can be obtain,  $\beta_t(m)$ . Therefore,

$$\beta_t(m) = Pr\left\{Y_{t+1}^L \mid S_t = m\right\} = \sum_{m'=0}^{N-1} Pr\left\{S_{t+1} = m'; Y_{t+1}^L \mid S_t = m\right\}$$

(3.23)

Rewriting equation 3.23 using the Markov chain and the DMC properties, the equation becomes,

$$\beta_{t}(m) = \sum_{m'=0}^{N-1} Pr\left\{Y_{t+2}^{L} \mid S_{t+1} = m'\right\} \cdot Pr\left\{S_{t+1} = m'; S_{t} = m\right\}$$

$$\beta_{t}(m) = \sum_{m'=0}^{N-1} \beta_{t+1}(m') \cdot \Gamma_{t+1}(m, m') \text{ for } t = 1, 2, \dots, L-1$$

(3.24)

Using vector notation, equation 3.24 becomes,

$$\beta_{t-1} = \Gamma_t \cdot \beta_t \tag{3.25}$$

Due to the previous subsections reasons, the backward recursion needs normalization, which is as follows,

$$\bar{\beta}_{t}(m) = \frac{\beta_{t}(m)}{\sum_{m'=0}^{N-1} \beta_{t}(m')}$$

(3.26)

The backward recursion in terms of the normalized values is then,

$$\beta_{t}(m) = \sum_{m'=0}^{N-1} \bar{\beta}_{t+1}(m') \cdot \Gamma_{t+1}(m, m')$$

(3.27)

If the final state is know and it is m or the encoder is 'terminated', then  $\beta_L$ , the initial conditions, are  $(0, \ldots, 1, \ldots, 0)$  where 1 is the  $m^{th}$  entry.

#### 3.7.3 State Transition Matrix

An NxN matrix, where N is the number of states in the code, is known as the transition matrix,  $\Gamma(m', m)$ , and is defined as follows,

$$\Gamma(m', m) = Pr\{S_t = m; Y_t \mid S_{t-1} = m'\}$$

(3.28)

Applying Bayes' rule we can show the following,

$$\Gamma(m', m) = \sum_{U} Pr\{U_t \mid S_t = m; S_{t-1} = m'\} \cdot Pr\{S_t = m \mid S_{t-1} = m'\} \cdot Pr\{Y_t \mid X_t\}$$

(3.29)

To describe equation 3.29, it's individual pieces can be broken up and analyzed:

- $Pr\{U_t \mid S_t = m; S_{t-1} = m'\}$ : This value is either 0 or 1. A 1/n rate convolutional code contains two transitions from each state for a binary input  $U_t$ , e.g., transition 1 and transition 0.

- Pr {S<sub>t</sub> = m | S<sub>t-1</sub> = m'}: These are the APPs of the symbols at time t. The encoder input symbol probabilities are the same as the state transition probabilities. With turbo coding, i.e., iterative coding, the soft symbol information given by another decoder will be used in place of this term for the later iterations. The first iteration uses 0.5 for all symbols, given that the decoder has no priori probabilities of the symbols. The BCJR/MAP decoder that has been designed will be a standalone decoder. Therefore, 0.5 should be used for all symbols, however, it has been concluded through experimentation that we can neglect these APPs without any loss to performance see Section 5.3.1.

- $Pr\{Y_t \mid X_t\}$ : This value depends on the channel property. Since, the AWGN channel with BPSK will be used, for a rate 1/n code, the AWGN channel with a single side power spectrum density value of  $N_o/2$  gives,

$$Pr\left\{Y_{t} \mid X_{t}\right\} = \left(\frac{1}{\pi N_{o}}\right)^{n/2} \exp\left(-\frac{1}{N_{o}} \sum_{i=1}^{n} (y_{t,i} - x_{t,i})^{2}\right)$$

(3.30)

where  $x_{t,i} \in \{-1,1\}$  and recall that in BPSK, bit level 0 is mapped to -1 and 1 is mapped to 1.

## 3.7.4 APPs Of The Symbols

Once  $\Gamma_t(m', m)$ ,  $\alpha_t(m)$ ,  $\beta_t(m)$  are calculated it relatively simple to calculate  $\lambda_t(m)$  defined as the joint probabilities of the states and the received channel sequence, and  $\sigma_t(m', m)$ , either one of the following equations are used to find the APPs of the symbols,

$$\lambda_t(m) = \alpha_t(m) \cdot \beta_t(m) \tag{3.31}$$

Figure 3.10: Transitions For NRC codes [9]

$$\sigma_{t}\left(m',m\right) = \alpha_{t-1}\left(m'\right) \cdot \Gamma_{t}\left(m'\right) \cdot \beta_{t}\left(m\right) \tag{3.32}$$

$\lambda_t(m)$  is typically used for NRC codes because each state can be either 'reached' by 1 or 0, but not both, unlike  $\sigma_t(m',m)$ .  $\sigma_t(m',m)$  is typically used for RSC codes because each state can be 'reached' by both 1 or 0 transitions, see Figure 3.10.

The following equations show the remainder of the calculations needed,

$$Pr_{APP}\left[u_{t}=1\right] = \frac{\sum_{m \in A} \lambda_{t}\left(m\right)}{\sum_{m \in All \ states} \lambda_{t}}$$

(3.33)

where A is all '1' transition states and

$$Pr_{APP}\left[u_{t}=1\right] = \frac{\sum_{(m',m)\in B} \sigma_{t}\left(m',m\right)}{\sum_{(m',m)\in All\ branches} \sigma_{t}\left(m',m\right)}$$

(3.34)

where B is all '1' transition branches. The APPs of symbol '-1' at time t for a given received channel sequence is

$$Pr_{APP}[u_t = -1] = 1 - Pr_{APP}[u_t = 1]$$

(3.35)

By choosing the APP with the largest value, the decoder can give hard outputs which are estimations of the input symbols, denoted  $\hat{u}_t \in \{-1,1\}$ . Therefore, the decision rule is,

$$\hat{u}_t = \begin{cases} 1 & \text{if } Pr_{APP} [u_t = 1] \ge Pr_{APP} [u_t = -1] \\ -1 & \text{if } Pr_{APP} [u_t = 1] < Pr_{APP} [u_t = -1] \end{cases}$$

(3.36)

Equations 3.33 - 3.36 are based on the AWGN channel with BPSK.

# Chapter 4

# $egin{aligned} Viter bi \ Decoder \ Using \ Asynchronous \ Techniques \end{aligned}$

### 4.1 Introduction

The asynchronous paradigm can conceivably provide viable advantages to the problems caused by synchronous design. Applying asynchronous techniques, as seen in [8, 12] can offer the potential for lower power systems. The natural extension of the Amulet Group's (University of Manchester) paper is to apply asynchronous techniques to the BCJR/MAP algorithm. This chapter briefly introduces the ideas concerned with the asynchronous Viterbi decoder from [8, 12], as to better describe an asynchronous BCJR/MAP decoder.

# 4.2 Basic Building Block Concepts

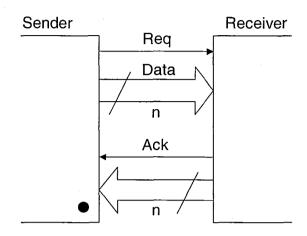

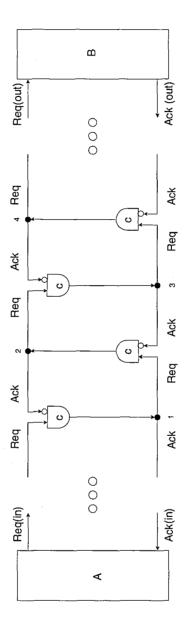

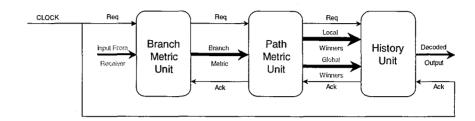

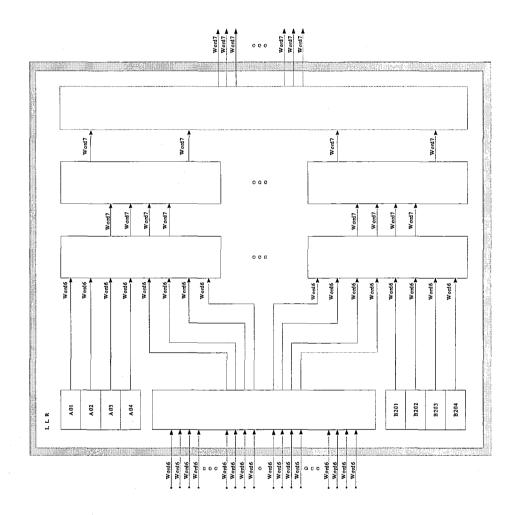

The Amulet Group divided up the design into three main sub-systems shown in Figure 4.1:

- 1. Branch Metric Unit (BMU)

- 2. Path Metric Unit (PMU)

Figure 4.1: Viterbi Decoder Using Asynchronous Techniques - System Level [12, 8]

#### 3. History Unit (HU)

The HU is sometimes called the Survival Metric Unit (SMU) in synchronous systems.

In Figure 4.1, the thick lines are the data signals and the thin lines are the handshaking control signals. The system's first request line and last acknowledge line is connected to a clock. This clock is solely to synchronize with an external synchronous systems' clock.

# 4.3 System Overview

The BMU takes the inputs from the receiver and calculates the distance between the received bits and the four ideal symbols (ideal branch words) that could have been transmitted, i.e., branch metric calculations. These weights are the inputs to the PMU.

Holding node weights, the PMU calculates the node plus branch weights, selecting the lower overall metric as the next metric for a node in a specific time period. The calculated node weights are then fed back into the PMU for the next calculation. The PMU also holds a bit of data for whether or not the winner was on the upper or lower branch entering the node.

For each time slot, the local winner information is inputted to the HU. The global winner, the state with the lowest node weight, is also passed on to the HU. This is done so that there is a known starting point when tracing back through the trellis history to find the most correct decoded sequence.

The HU, using the global and local node weights, reconstructs the trellis. It also traces back to find the path (most correct decoded sequence) from the global winner node to the local winner node in the oldest timeslot.

# 4.4 System Parameters

The system described used 4PBDP. The received bits to the decoder were soft coded; three bits were used to represent values. The system constrain length was 7. That means that there were 64 nodes/states and 128 paths or branches.

The system receives and decodes at a rate of  $\frac{1}{2}$ , however, other data rates are obtained by omitting some of the encoded symbols sent. Therefore, code rates of  $\frac{2}{3}, \frac{3}{4}, \frac{5}{6}$  and  $\frac{7}{8}$  can be obtained. As the code rate increases, less redundancy is included in the transmitted data signal, which results in increases in error rate from the decoder. The  $\frac{1}{2}$  rate encoder has the most error-free output.

The system operates on a 90 MHz clock. This clock is used by all code rates, and the code rate defines two important ideas. First, the code rate defines the number of input bits to the number of transmitted encoded characters, which are the inputs to the decoder. Second, it specifies the ratio of the number of clocks containing encoded information and to the number of clock cycles. As an example, a  $\frac{3}{4}$  rate means that three input bits result in four output transmitted characters and that there are three clocks out of four that contain encoded information. Therefore, in a  $\frac{3}{4}$  rate code, every fourth clock cycle contains no

encoded information (Block-Valid Low). So a 90 MHz clock rate using a  $\frac{1}{2}$  rate encoder produces valid encoded information on every other clock cycle and yields a data rate of  $\frac{1}{2} \times 90 = 45$   $\frac{Msymbols}{sec}$ .

#### 4.5 Conclusions

The Viterbi decoder described in [3, 8] was compared in [12]. In many asynchronous designs, their synchronous counterpart cannot be directly translated into the asynchronous conceptual framework. This resulted in a design that was conceived from first principles and caused the designers to completely rethink how to implement the decoder.

The designers compared their design to the standard Viterbi decoder and the other decoders in the Power Reduction for System Technologies (PREST) project. The designers claim that the "power consumption was approximately an order of magnitude less than that of the other novel designs, and twice that again less than the reference design (when decoding an uncorrupted bit stream)".

The authors only mentioned that since the design is asynchronous, that low Electro Magnetic (EM) emissions would be desirable for a communication-related circuit.

The most promising aspect that was observed was that of the exploitation in the HU. Asynchronous designs most significant assets; doing nothing when nothing useful needs to be done was visibly shown in the power results. Since this is true when good channel conditions exist, this in no way impeded the system when the condition didn't exist. This aspect is the most difficult to achieve in a synchronous design.

The architecture used both high-speed serial operation (in the PMU) and lower speeds in the parallel operation (in the HU). These two architectures were used when seen to be most appropriate. The variety of architectures would have been difficult to achieve in a synchronous design due to the synchronization of different clocks.

# Chapter 5

# Designing The BCJR/MAP Decoder

### 5.1 Introduction

This chapter will introduce Balsa which is a Hardware Definition Language (HDL) used for asynchronous circuits and systems and a quick tool to assess the feasibility of an asynchronous design over a synchronous design.

The design constraints along with the cost saving design feature will be discussed.

# 5.2 Design Flow

### 5.2.1 High Level Languages And Tools

Asynchronous circuits are highly concurrent and the communication between modules is based on handshake channels. Therefore, a hardware language for the description of asynchronous circuits needs to incorporate these two characteristics.

The Communicating Sequential Processes (CSP) language [3] meets these constraints and contains the following characteristics:

#### 1. Concurrent processes

- 2. Sequential and concurrent composition of statements within a process

- 3. Synchronous message passing over point to point channels (supported by primitives such as 'send', 'receive' and possibly 'probe')

CSP languages designed specifically for designing asynchronous circuits are:

- 1. Tangram, developed by Phillips and not available in the public domain

- 2. Balsa, developed by the University of Manchester and available in the public domain

#### 5.2.2 CSP Vs. HDL

The CSP language [3] is not a standardized language as are other Hardware Definition Languages (HDL) such as Very High Speed Integrated Circuit Hardware Description Language (VHDL) or Verilog.

For instance, VHDL can be used to design asynchronous circuits, however, there are some disadvantages, such as:

- VHDL lack primitives to implement the synchronous message passing needed by asynchronous circuits. It is possible to write low level code that implements the handshaking, however, it is undesirable to mix low level details into code whose purpose is to capture the high-level behaviour of the circuit.

- 2. VHDL lacks the statement level concurrency within a process.

VHDL does have advantages to its use, such as:

- VHDL is well supported by existing Computer Aided Design (CAD) tool frameworks

that provide simulators, pre-designed modules, mixed-mode simulation and tools for

synthesis, layout and the back annotation of timing information.

- 2. The same simulator and test bench can be used throughout the entire design process form the first high-level specification to the final implementation in some target technology, i.e., standard cell layout.

- 3. It is possible to perform mixed mode simulation where some entities are modelled using behavioural specification and other are implemented using the components of the target technology.

- 4. Many real world systems include both synchronous and asynchronous subsystems and such hybrids systems can be modelled without any problems in VHDL.

Although, VHDL does have some excellent advantages, in terms of the study at hand. A CSP language offers immediate results. Balsa, a framework for synthesizing asynchronous hardware systems and a language for describing such systems will be the tool of choice for this study.

## 5.2.3 Balsa: Asynchronous Hardware Language And Synthesis Tool

Asynchronous circuits, at a hardware level, are complex systems that have not been addressed by industry standard Electronic Design and Automation (EDA) tools and companies. EDA tools are lacking and this is a sentiment expressed by Ian Sutherland, vice president, fellow and asynchronous expert at Sun Microsystems Laboratories [18].

VHDL and Verilog, industry standard hardware description languages, lack the needed "concurrency and platform for handshaking channels" [3] that are required by asynchronous systems. The problem is that the majority of tools are manufactured for the clocked design paradigm.

A recent free tool from the University of Manchester, one of the academic leaders in asynchronous design, is Balsa. Balsa is both a "framework for synthesis of asynchronous hardware systems and a language for describing such systems" [3]. Balsa uses the adopted approach of proprietary languages like Tangram, "syntax-directed compilation into communication handshaking components" [3]. This means that there is direct 'one-to-one' mapping between language and direct handshaking circuits produced.

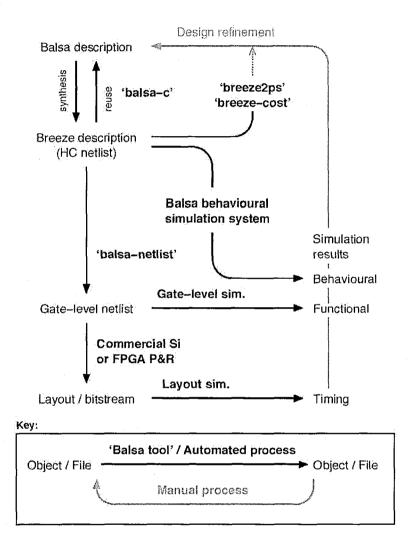

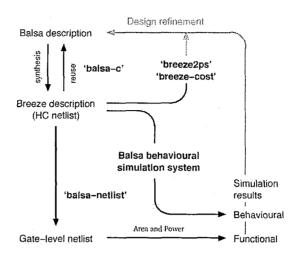

Figure 5.1 details the design flow for a digital asynchronous circuit using Balsa version 3.4.1.

The Balsa circuit description is compiled using the balsa-c program to an intermediate

Figure 5.1: Balsa Asynchronous Design Flow [19]

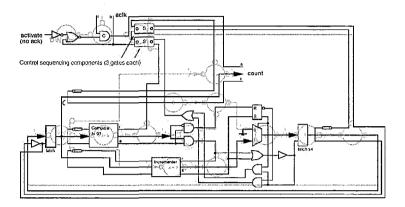

Figure 5.2: Gate-Level and Handshake Component Level Of A Modulo-10 Counter [19]

file type, called the breeze description. The breeze description is a network arrangement of a finite set of Handshake Components (HC) (45). The HC are connected across channels were the handshake signaling occurs. Figure 5.2 demonstrates a gate-level modulo-10 counter with the underlining handshake circuitry underneath drawn in light grey.

The majority of the tools in the Balsa package deal with the manipulation of the breeze files. The breeze files can be used by 'back-end' tools for different protocol implementations, however, the breeze files contain procedures and type definitions passed on from Balsa source files allowing breeze to be used as the package description format for Balsa. breeze-sim provides the behavioural simulation package for source level debugging, visualization of the channel activity at the handshake circuit level and it provides conventional waveform traces that can be viewed using GTKWave. GTKWave is a waveform viewer. The eventual target CAD package can be used to perform more accurate simulations and eventual physical layout.