#### University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

1993

# Dynamic logic synthesis with application to selftimed pipelines.

Hong Ming. Chan University of Windsor

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### **Recommended** Citation

Chan, Hong Ming., "Dynamic logic synthesis with application to self-timed pipelines." (1993). *Electronic Theses and Dissertations*. Paper 1795.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

National Library of Canada

Acquisitions and Bibliographic Services Branch

NOTICE

395 Weilington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontano) K1A 0N4

Your Net - Votre reference

Our life - Notre reférence

#### AVIS

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments. La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# Canadä

#### DYNAMIC LOGIC SYNTHESIS WITH APPLICATION TO SELF-TIMED PIPELINES

by

Hong Ming Chan

A Thesis Submitted to the Faculty of Graduate Studies through the Department of Electrical Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada

1992

National Library of Canada

Acquisitions and Bibliographic Services Branch Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395 Wellington Street Ottawa, Ontario K1A 0N4 395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file - bothe manner

Our life Note telefence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-83061-1

Name <u>Hong Ming</u>, <u>Chan</u> Dissertation Abstracts International is arranged by broad, general subject categories. Please select the one subject which most nearly describes the content of your dissertation. Enter the corresponding four-digit code in the spaces provided.

SUBJECT TERM

#### **Subject Categories**

#### THE HUMANITIES AND SOCIAL SCIENCES

| COMMUNICATIONS AND THE A | RTS   |

|--------------------------|-------|

| Architecture             | .0729 |

| Art History              | 0377  |

| Cinemo                   | .0900 |

| Donce                    | .0378 |

| Fine Arts                |       |

| Information Science      | 0723  |

| Journalism               | .0391 |

| Library Science          | 0399  |

| Mass Communications      | 0708  |

| Music                    |       |

| Speech Communication     | 0459  |

| Thursday                 | 0465  |

#### EDUCATION

| General                                                             | .0515   |

|---------------------------------------------------------------------|---------|

| Administration                                                      | .0514   |

| Adult and Continuing                                                | .0516   |

| Anticultural                                                        | .0517   |

| Ari                                                                 | .0273   |

| Bilinguat and Multicultural                                         | .0282   |

| Business                                                            | .0688   |

| Art<br>Bilingual and Multicultural<br>Business<br>Community College | .0275   |

| Controlium and instruction                                          | . VI 41 |

| Early Childhood                                                     | .0518   |

| Elementary                                                          | .0524   |

| Finance                                                             | .0277   |

| Finance<br>Guidance and Counseling                                  | .0519   |

| 210CHM                                                              | .0080   |

| Higher                                                              | .0745   |

| History of                                                          | 0520    |

| Home Economics                                                      | .02/8   |

| Industrial                                                          | .0521   |

| Language and Literature                                             | .0279   |

| Mathematics                                                         | .0280   |

| Music                                                               | .0522   |

| Philosophy of                                                       | .0998   |

| Physical                                                            | .0523   |

| Psychology                              | 0525   |

|-----------------------------------------|--------|

| Reading                                 | . 0535 |

| Religious                               | . 0527 |

| Sciences                                | 0714   |

| Secondary                               | 0533   |

| Secondary<br>Social Sciences            | 0534   |

| Sociology of                            | 0340   |

| Special                                 | 0529   |

| Teacher Training                        | 0530   |

| Technology                              | 0710   |

| Tests and Measurements                  | 0288   |

| Vocational                              | 0747   |

| *************************************** |        |

#### LANGUAGE, LITERATURE AND

LINGUISTICS

| 0679   |

|--------|

| 0289   |

|        |

| 0290   |

| 0291   |

|        |

| 0401   |

| 0294   |

| .0295  |

| 0297   |

|        |

| 0298   |

| 0316   |

| . 0591 |

| 0305   |

| . 0352 |

| 0355   |

| 0502   |

| 0593   |

| .0311  |

| 0312   |

| 0315   |

| 0313   |

| .0314  |

|        |

| PHILOSOPHY, RELIGION AND THEOLOGY                                                                                               |                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Philosophy                                                                                                                      | .0422                                                                                  |

| Roligion<br>General<br>Biblical Studies<br>Clergy<br>History of<br>Philosophy of<br>Theology                                    | .0318<br>.0321<br>.0319<br>.0320<br>.0322                                              |

| SOCIAL SCIENCES                                                                                                                 |                                                                                        |

| American Studies                                                                                                                | .0323                                                                                  |

| Anthropology<br>Archoeology<br>Cultural<br>Physical<br>Business Administration                                                  | .0326                                                                                  |

| General<br>Accounting<br>Banking<br>Management                                                                                  | .0310<br>.0272<br>.0770<br>.0454                                                       |

| Marketing<br>Canadian Studies                                                                                                   | .0338                                                                                  |

| Economics<br>Agricultural<br>Commerce-Business<br>Finance<br>History<br>Labor<br>Theory<br>Folklore<br>Geography<br>Gerontology | .0501<br>.0503<br>.0505<br>.0508<br>.0509<br>.0510<br>.0511<br>.0358<br>.0366<br>.0351 |

| General                                                                                                                         | .0578                                                                                  |

| Canadian 033<br>European 033<br>Latin American 033<br>Middle Eastern 033<br>Uniterl States 033<br>History of Science 035<br>Law 035<br>Political Science 045<br>Law 035<br>Political Science 045<br>International Law and Relations 040<br>Recreation 040<br>Social Work 044<br>Sociology 04<br>Ceneral 044<br>Sociology 04<br>Ceneral 044<br>Sociology 04<br>Ceneral 044<br>Sociology 04<br>Ceneral 044<br>Sociology 04<br>Ceneral 044<br>Sociology 04<br>Ceneral 044<br>Demography 099<br>Ethnic and Rocial Studies 045<br>Individual and Family 046<br>Industrial and Labor Relations 045<br>Public and Social Welfare 045<br>Social Structure and Development 077<br>Theore and Methods 03 | 1581<br>1582<br>1328<br>1331<br>1332 | Ancient<br>Medieval<br>Modern<br>Black<br>African<br>Asia, Austrolia and Oceania                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Latin American                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 334                                  | European                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| History of Science                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 100                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| History of Science                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 337                                  | United States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Coc                                  | HISPOY OF SCIENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Relations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1370                                 | Polnical Science                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Relations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 815                                  | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Recreation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 616                                  | Relations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Sociology<br>General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <u>617</u>                           | Public Administration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Sociology<br>General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1452                                 | Social Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Individual and Family<br>Studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                      | 2000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Individual and Family<br>Studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1620<br>1477                         | Crimicalony and Penalogy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Individual and Family<br>Studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>7938</b>                          | Demography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Relations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>3628</b>                          | Studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Relations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                      | Industrial and Labor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Social Structure and<br>Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2629<br>1470                         | Relations<br>Public and Social Walferra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      | Social Stauchure and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Transportation 07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0700                                 | Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1344                                 | Transportation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Transportation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      | and the second s |

| Women's Studies04:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1999                                 | Urban and Regional Planning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

054

SUBJECT CODE

4

ΛŀΙ

#### THE SCIENCES AND ENGINEERING

| Agriculture                            |       |

|----------------------------------------|-------|

| General                                | 0473  |

| According                              | 0285  |

| Agronomy<br>Animal Culture and         |       |

| Nutrition                              | 0475  |

| A - ' al Dathalam.                     | 0474  |

| Animal Pathology<br>Food Science and   |       |

| rood Science and                       | 0260  |

| Technology<br>Forestry and Wildlife    |       |

| Forestry and wildline                  |       |

| Plant Culture                          |       |

| Plant Pathology                        |       |

| Plant Physiology<br>Range Management   |       |

| Kange Management                       |       |

| Wood Technology                        |       |

| Biology                                | 000/  |

| General                                |       |

| Analomy                                |       |

| Biostatistics                          |       |

| Botany                                 |       |

| <u>Coll</u>                            |       |

| Ecology                                |       |

| Entomology                             | 0353  |

| Genetics                               |       |

| unnology                               |       |

| Microbiology                           |       |

| Limnology<br>Microbiology<br>Molecular |       |

| Neuroscience                           |       |

| Oceanography                           |       |

| Physiology                             |       |

| Rodiction                              |       |

| Veterinary Science                     |       |

| Zoology                                |       |

| Biophysics                             | A76 / |

| General                                |       |

| Medicol                                | 0760  |

| EARTH SCIENCES                         |       |

|                                        | 0/06  |

| Biogeochemistry                        |       |

| Geodesy<br>Geology<br>Geophysics<br>Hydrology<br>Mineralogy<br>Paleobolany                                                                                                                                                                                                                   | 0372<br>0373<br>0388<br>0411<br>0345                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Paleoecology<br>Paleozoology<br>Paleozoology<br>Palynology<br>Physical Geography<br>Physical Oceanography                                                                                                                                                                                    | 0418                                                                                                         |

| HEALTH AND ENVIRONMENTA<br>SCIENCES                                                                                                                                                                                                                                                          | uL.                                                                                                          |

| Environmental Sciences                                                                                                                                                                                                                                                                       | 0768                                                                                                         |

| Health Sciences<br>General<br>Audiology<br>Chemotherapy<br>Dentistry<br>Education<br>Hospital Management<br>Human Development<br>Immunology<br>Medicine and Surgery<br>Medicine and Surgery<br>Mental Health<br>Nursing<br>Nutrition<br>Obstetrics and Gynecology<br>Occupational Health and | 0300<br>0992<br>0567<br>0350<br>0769<br>0769<br>0982<br>0982<br>0564<br>0347<br>0569<br>0569<br>0570<br>0380 |

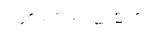

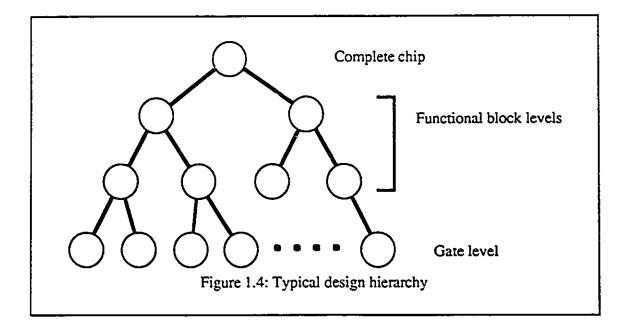

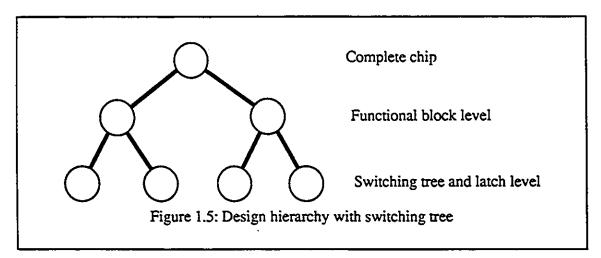

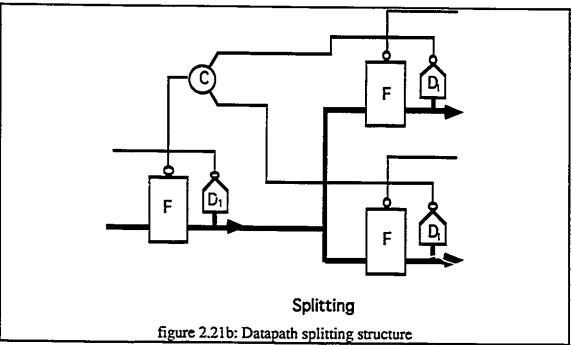

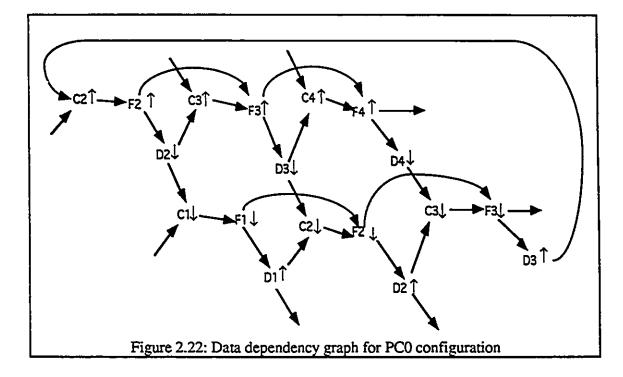

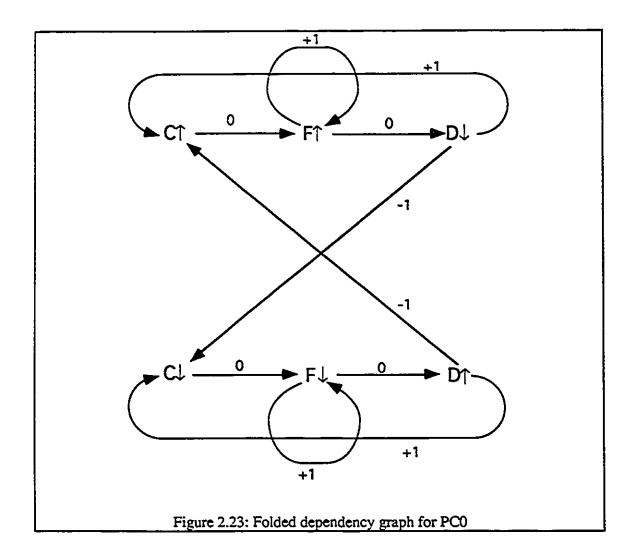

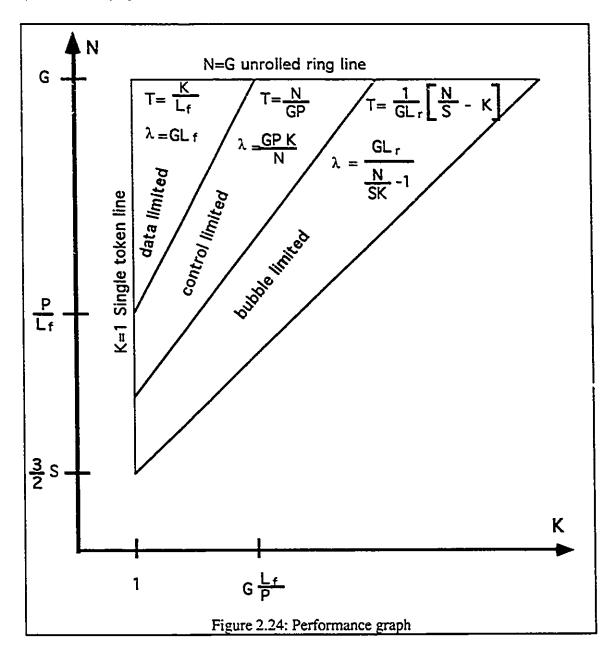

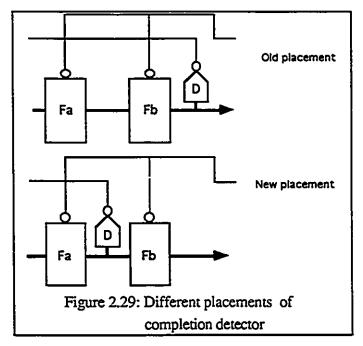

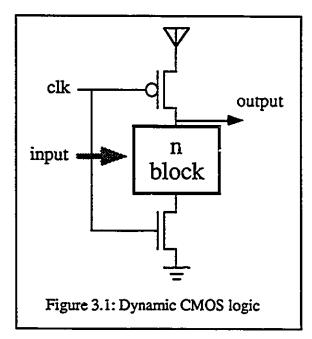

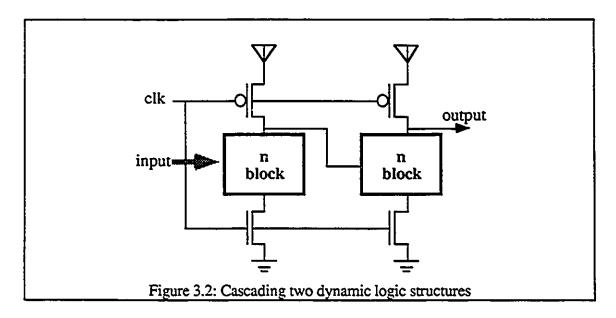

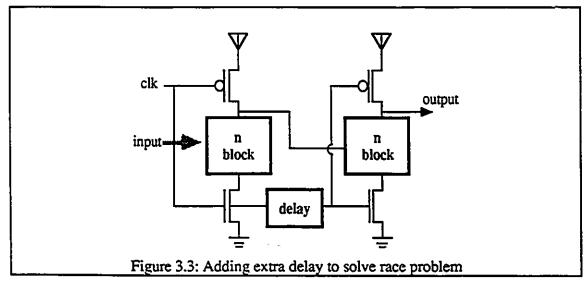

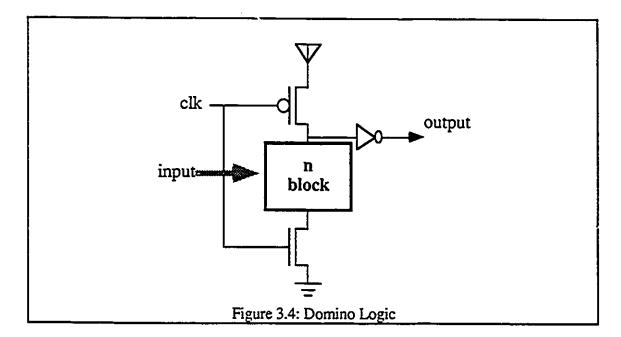

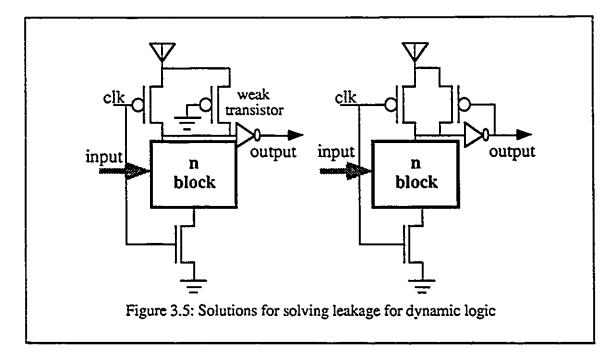

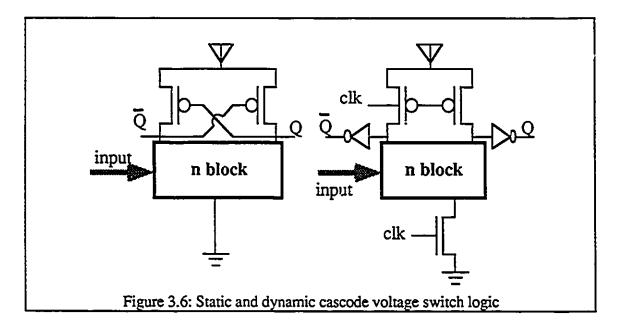

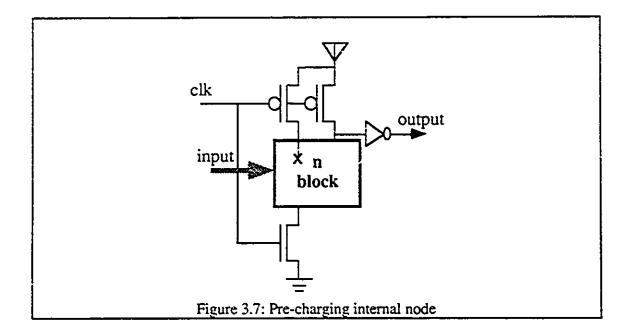

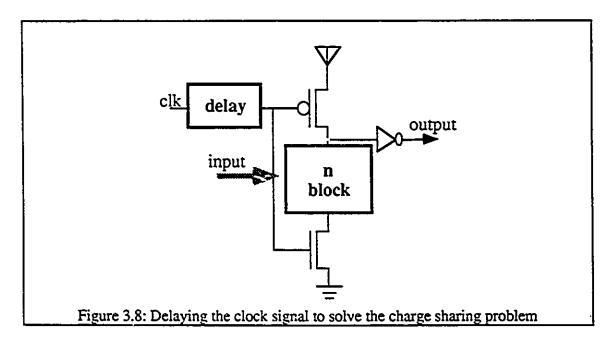

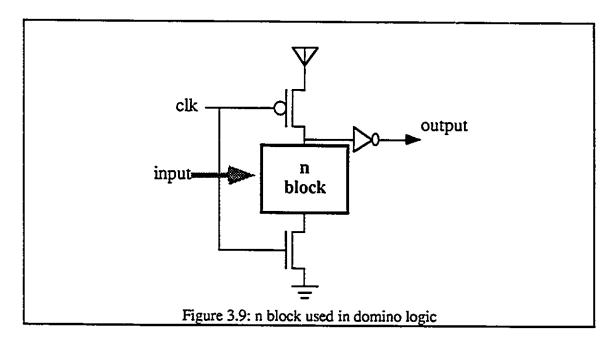

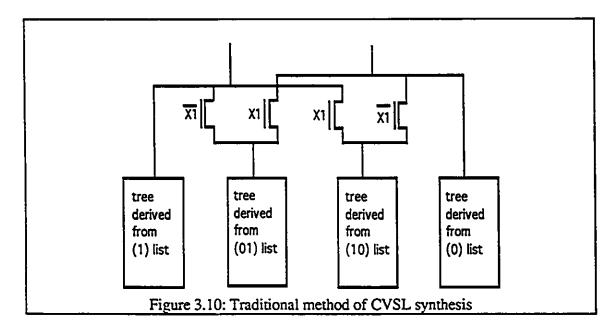

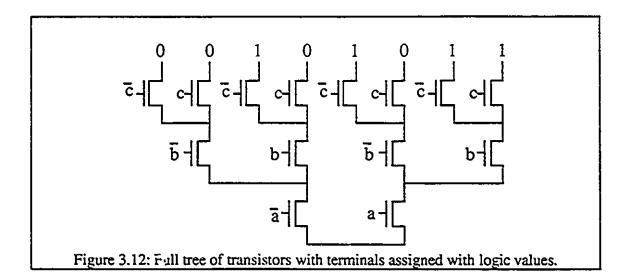

| Therapy<br>Ophtholmology<br>Pathology<br>Pharmocy<br>Physical Therapy<br>Physical Therapy<br>Public Health<br>Radiology<br>Recreation                                                                                                                                                        | 0354<br>0381<br>0571<br>0419<br>0572<br>0382<br>0573<br>0574                                                 |