# University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

2003

# A 2-digit multidimensional logarithmic number system filterbank processor for a digital hearing aid.

Hongbo (Jennifer). Li *University of Windsor*

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### Recommended Citation

Li, Hongbo (Jennifer)., "A 2-digit multidimensional logarithmic number system filterbank processor for a digital hearing aid." (2003). *Electronic Theses and Dissertations.* Paper 515.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

## A 2-Digit Multidimensional Logarithmic Number System Filterbank Processor for a Digital Hearing Aid

by

#### Hongbo (Jennifer) Li

#### A Thesis

Submitted to the Faculty of Graduate Studies and Research through the Department of Electrical and Computer Engineering in partial fulfillment of the requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada 2003

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisisitons et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-82885-9 Our file Notre référence ISBN: 0-612-82885-9

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

#### © 2003 Hongbo (Jennifer) Li

All Rights Reserved. No part of this document may be reproduced, stored or otherwise retained in a retrieval system or transmitted in any form, on any medium or by any means without the prior written permission of the author.

### **Abstract**

This thesis addresses the design, implementation, and evaluation of a filterbank for digital hearing aids using a Multidimensional Logarithmic Number System (MDLNS). Hearing loss is a function of both frequency and input level. In a typical digital hearing instrument, the hearing loss compensation is performed by separating the incoming sound into several frequency bands which are then compressed to allow the amplification of low level signals while maintaining the amplitude of high level signals.

The demands of low power consumption and small size have led to a number of advances in algorithms, semiconductor technologies and system architectures for completely-incanal (CIC) hearing aid device. Based on research for digital hearing aids that started in the early 1990's, we have developed a new number system (MDLNS) and associated architecture that benefit the digital hearing aid processor in both of these requirements. Although the LNS has been previously considered for digital hearing aid processors, this thesis presents an exploration of the MDLNS for digital hearing aid circuitry. As with the LNS, the MDLNS provides a reduction in the size of the number representation, but the MDLNS promises a lower cost (*area.power*) implementation of the arithmetic operations required in both the linear and non-linear domains of filtering and compression. In this thesis we discuss an application of the MDLNS on the construction of a finite impulse response FIR filterbank, a major component of digital hearing aid processors. The MDLNS filterbank processor chip was fabricated using a 0.18 micron CMOS technology.

After evaluating the MDLNS filterbank and the two state-of-the-art filterbanks using classic binary implementation, we found power, area, and performance of the MDLNS filterbank processor showed competitive results compared to those binary filterbank processors.

To my parents who taught me not to fear failure, the determination to succeed and the courage to try. To my husband Norman and my son Barton for their support.

### Acknowledgments

I would like to express my deepest thanks and appreciation to my supervisor Dr. G. A. Jullien for his continuous guidance, support and encouragement and for bringing this challenging project to my attention. I am grateful to Gennum Corp. for providing funding.

I would also like to thank my committee members Dr. Majid Ahmadi, Dr. Vassil Dimitrov, Dr. R. G. Gaspar and Dr. Chunhong Chen for their interest and invaluable comments.

Finally, I would like to express my thanks to Roberto Muscedere for his aid with HDLs, Cadence tools and helping in producing the MDLNS filterbank microchip.

The CAD tools used in the project were provided though CMC.

## **Table of Contents**

|               | gments                                |     |

|---------------|---------------------------------------|-----|

| List of Sym   | bols                                  | X   |

| List of Abbi  | reviations                            | xi  |

| List of Figu  | res                                   | xii |

| List of Table | es                                    | xv  |

| Chapter 1     | Introduction                          | 1   |

| 1.1           | Introduction                          | 1   |

| 1.2           | Human Hearing                         |     |

|               | 1.2.1 Dynamic Range                   |     |

|               | 1.2.2 Frequency Range                 |     |

| 1.3           | Hearing Loss                          |     |

|               | 1.3.1 Conductive Hearing Loss         |     |

|               | 1.3.2 Sensorineural Hearing Loss      | 6   |

| 1.4           | Hearing Instrument Types              | 10  |

| 1.5           | Hearing Instrument Technologies       | 12  |

| 1.6           | MDLNS                                 | 16  |

| 1.7           | Thesis Organization                   |     |

| Chapter 2     | MDLNS Background Theory               | 20  |

| 2.1           | Introduction                          | 20  |

| 2.2           | Representation                        | 21  |

| 2.3           | Input Data Mapping                    | 24  |

|               | 2.3.1 Error-Free Representations      |     |

|               | 2.3.2 Non Error-Free Representations  | 28  |

|               | 2.3.3 Mathematical Operations         | 29  |

| 2.4           | Hardware Complexity                   | 32  |

|               | 2.4.1 Single Digit Computational Unit |     |

|               | 2.4.2 n-digit Computational Unit      | 33  |

| 2.4.3         | MDLNS Complexity Comparison           | 34  |

| Chapter 3     | Digital Filterbank Algorithms         | 36  |

| 2.1        |                                                       | 26  |

|------------|-------------------------------------------------------|-----|

| 3.1        | Introduction                                          |     |

| 3.2        | Design Constraints                                    |     |

| 3.3        | IFIR Filterbank Algorithm Design                      |     |

|            | 3.3.1 Introduction                                    |     |

|            | 3.3.3 Complementary halfband linear-phase FIR filters |     |

|            | 3.3.4 Prototype filter $H1(z)$                        |     |

|            | 3.3.5 Sub-filterbanks <i>Hs</i> 1 and <i>Hs</i> 2     |     |

|            | 3.3.6 IFIR filterbank with 60 dB noise level          |     |

| 3.4        | DFT Filterbank Algorithm                              | 46  |

|            | 3.4.1 Oversampled WOLA Filterbank [22]                | 48  |

|            | 3.4.2 Prototype Nyquist Eigenfilter                   | 50  |

| 3.5        | MDLNS 8 Parallel FIR Filters                          | 52  |

|            | 3.5.1 MDLNS Filterbank Algorithm Design               |     |

|            | 3.5.2 Coefficient MDLNS Mapping                       |     |

| 3.5.3      | Conclusions                                           |     |

| Chapter 4  | Filterbank Processor Architectures                    | 59  |

| 4.1        | IFIR Filterbank Architecture                          | 59  |

| 4.2        | DFT Filterbank Architecture [24]                      | 61  |

| 4.3        | MDLNS Filterbank Architecture                         | 63  |

|            | 4.3.1 Improved MDLNS Architecture                     |     |

| 4.3.2      | Results and Conclusions                               | 66  |

| Chapter 5  | Physical Implementation of Filterbank Processor       | 67  |

| 5.1        | Introduction                                          |     |

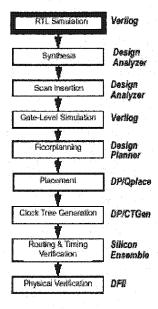

| 5.2        | Design Flow                                           | 68  |

|            | 5.2.1 RTL Simulation                                  | 69  |

|            | 5.2.2 Logic Synthesis                                 |     |

|            | 5.2.3 Gate-Level Simulation                           |     |

|            | 5.2.4 Floorplanning and Timing-Driven Placement       |     |

|            | 5.2.5 Clock Tree Generation                           |     |

|            | 5.2.7 Routing                                         |     |

|            | 5.2.8 Post-Layout Static Timing Analysis              |     |

|            | 5.2.9 Physical Verification (DRC & LVS)               |     |

| 5.3        | MDLNS Filterbank Processor Chip                       |     |

| Chapter 6  | MDLNS Filterbank Processor Analysis and Comparison    | 82  |

| 6.1        | Introduction                                          |     |

| 6.2        | Quantization Noise Comparison                         |     |

| 6.3        | Area Comparison                                       |     |

| 6.4        | Power Comparison Power Comparison                     |     |

|            | Conclusion and Future Works                           |     |

| Chapter 7  |                                                       |     |

| 7.1        | Conclusion                                            |     |

| 7.2        | Contributions                                         |     |

| 7.3        | Suggestions for Future Work                           | 100 |

| REFERENC   | CES                                                   | 101 |

| Appendix A | Matlab Code for Filterbanks                           | 104 |

| A.1        | Introduction                                          |     |

|            | And OddetOil                                          |     |

| Matlab Code for DFT Filterbank                         | 104                                                                                                                                                                                                                                                |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Eight 60 dB Parallel FIR Filters                       | 107                                                                                                                                                                                                                                                |

| Verilog Code for MDLNS Filterbank                      | 120                                                                                                                                                                                                                                                |

| Testbench.v                                            | 120                                                                                                                                                                                                                                                |

| parameters.v                                           | 122                                                                                                                                                                                                                                                |

| chipfilterbank.v                                       | 123                                                                                                                                                                                                                                                |

| Binary to MDLNS converter                              | 145                                                                                                                                                                                                                                                |

| Matlab Code for MDLNS and Binary Filterbank Comparison | 161                                                                                                                                                                                                                                                |

| MDLNS Filterbank Chip Testing                          | 167                                                                                                                                                                                                                                                |

| Test Overview                                          | 167                                                                                                                                                                                                                                                |

| Test Procedure                                         | 169                                                                                                                                                                                                                                                |

|                                                        | Eight 60 dB Parallel FIR Filters  Verilog Code for MDLNS Filterbank  Testbench.v  parameters.v  chipfilterbank.v  Binary to MDLNS converter  Matlab Code for MDLNS and Binary Filterbank Comparison  MDLNS Filterbank Chip Testing.  Test Overview |

# **List of Symbols**

| m | mantissa                                     |  |  |

|---|----------------------------------------------|--|--|

| r | base or radix                                |  |  |

| Φ | Look-up table operator for MDLNS addition    |  |  |

| Ψ | Look-up table operator for MDLNS subtraction |  |  |

| t | MDLNS ternary exponent                       |  |  |

| b | MDLNS binary exponent                        |  |  |

### **List of Abbreviations**

ASIC Application Specific Integrated Circuits

CAD Computer Aided Design

CMC Canadian Microelectronics Corporation

CMOS Complementary Metal-Oxide Semiconductor

CT-GEN Clock Tree Generator

dB Decibels

DEF Design Exchange Format

DRC Design Rule Check

FIR Finite Impulse Response

HDL Hardware Description Language

IC Integrated Circuit

LEF Library Exchange Format

LNS Logarithmic Number System

LVS Layout Versus Schematic

MAC Multiply Accumulate

MDLNS Multi-dimensional Logarithmic Number System

RAM Random Access Memory

RC Resistance and Capacities

ROM Read Only Memory

RTL Register Transfer Level

# **List of Figures**

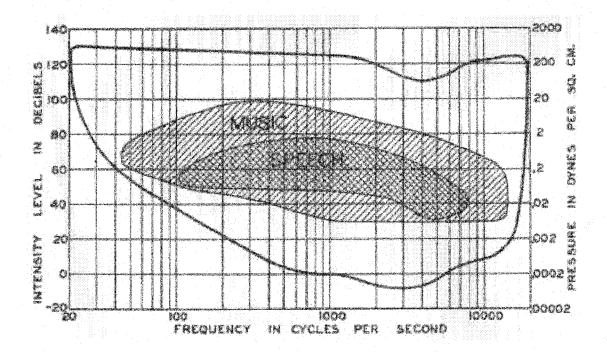

| Figure 1.1  | Frequency and intensity ranges of speech and music                   | 5  |

|-------------|----------------------------------------------------------------------|----|

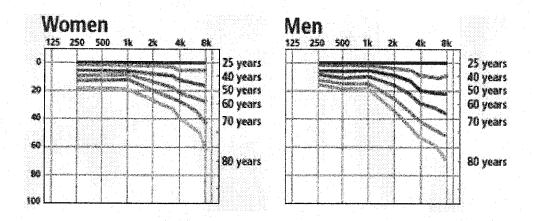

| Figure 1.2  | Age-induced hearing loss                                             | 7  |

| Figure 1.3  | Noise induced hearing loss                                           | 8  |

| Figure 1.4  | Ski-slope hearing loss                                               | 9  |

| Figure 1.5  | (left) Meniere's Disease (low_frequency loss), right: Trauma         |    |

|             | (mid_frequency loss)                                                 |    |

| Figure 1.6  | BTE type of hearing aid                                              |    |

| Figure 1.7  | ITE type of hearing aid                                              |    |

| Figure 1.8  | ITC type of hearing aid                                              | 11 |

| Figure 1.9  | CIC Hearing instrument placement                                     | 12 |

| Figure 1.10 | Digital hearing instrument structure [1]                             | 14 |

| Figure 1.11 | An example of the DSP part of the hearing aid block diagram          | 14 |

| Figure 1.12 | Compressive amplification                                            | 16 |

| Figure 1.13 | Signal-to-quantization noise ratio vs. input level                   | 18 |

| Figure 1.14 | Filter coefficient distribution.                                     | 19 |

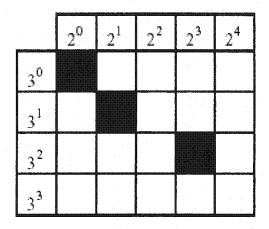

| Figure 2.1  | A 2-digit DBNS representation of 79                                  | 25 |

| Figure 2.2  | A 2DLNS representation of 7.25                                       | 26 |

| Figure 2.3  | Absolute error (>0.5) for different second bases                     | 28 |

| Figure 2.4  | 1-digit MDLNS inner product computation unit                         | 32 |

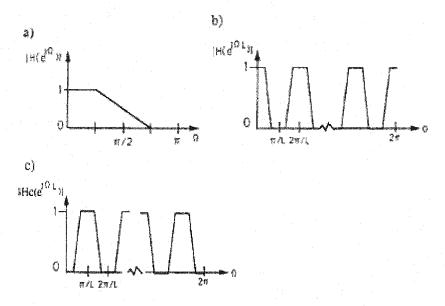

| Figure 3.1  | a) Lowpass modelfilter b) Interpolated model filter c) Complementary |    |

|             | interpolated model filter                                            | 40 |

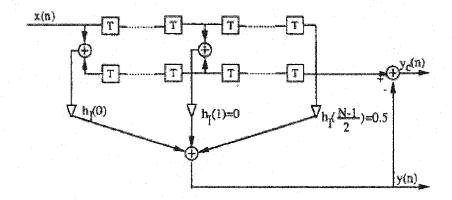

| Figure 3.2  | Realization of an interpolated complementary linear-phase FIR filter | 41 |

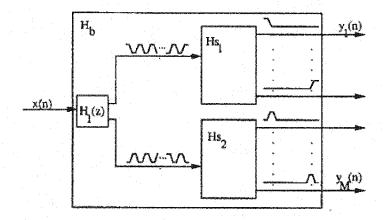

| Figure 3.3  | Filterbank structure with prototype filter and subfilterbank         | 42 |

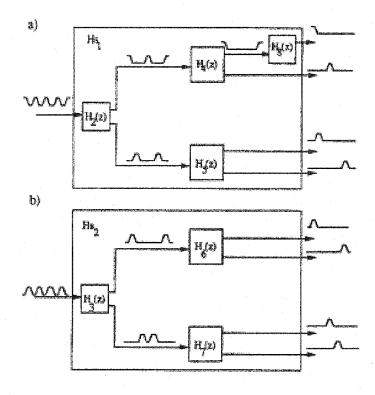

| Figure 3.4  | a) Sub-filterbank Hs1 b) Sub-filterbank Hs2                          | 43 |

| Figure 3.5  | IFIR filterbank structure.                                           | 44 |

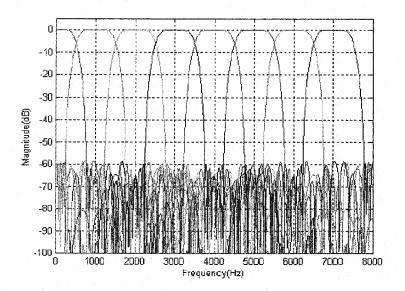

| Figure 3.6  | Magnitude response of 60 dB IFIR filterbank                          | 45 |

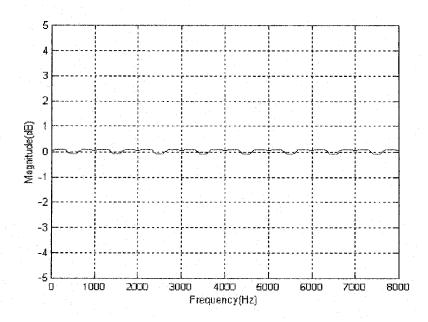

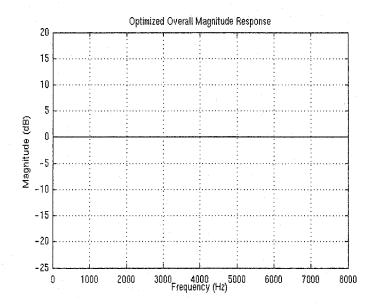

| Figure 3.7  | Maximally flat overall magnitude response of 60 dB IFIR filterbank   | 45 |

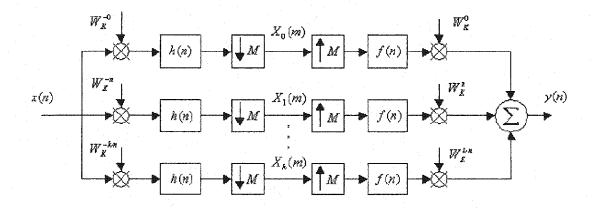

| Figure 3.8  | Complex modulator model of the DFT filterbank                        | 47 |

|             |                                                                      |    |

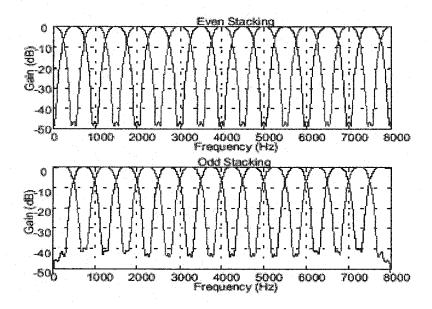

| Figure 3.9  | Frequency response of DFT filterbank channels for odd and even chann                    |    |  |  |

|-------------|-----------------------------------------------------------------------------------------|----|--|--|

|             | stacking arrangements                                                                   |    |  |  |

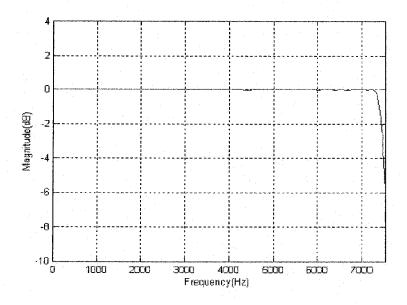

| Figure 3.10 | Overall magnitude response of the DFT filter bank                                       |    |  |  |

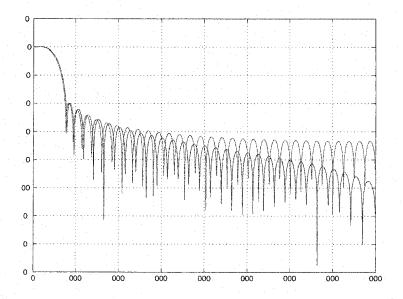

| Figure 3.11 | Frequency response of Eigenfilter and Kaiser Window FIR Filter                          |    |  |  |

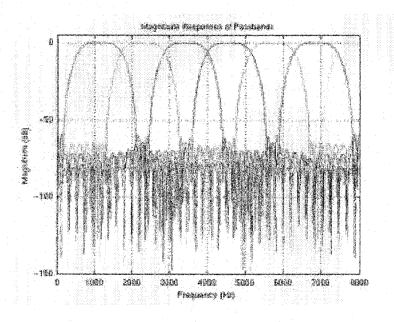

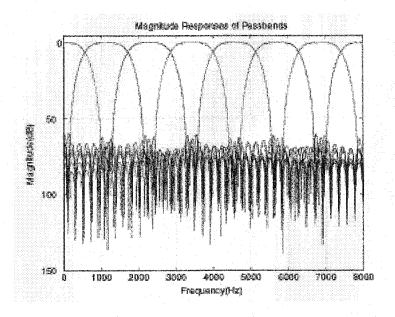

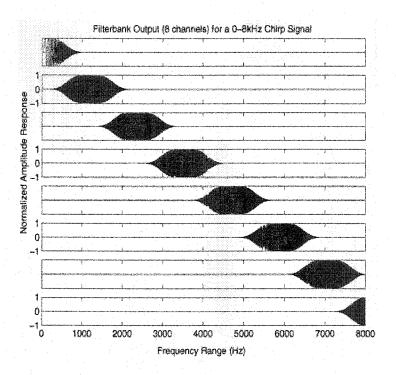

| Figure 3.12 | Magnitude response of 8 parallel filters                                                |    |  |  |

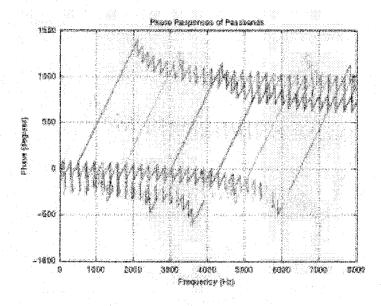

| Figure 3.13 | Phase response of the 8 parallel FIR filter                                             | 54 |  |  |

| Figure 3.14 | Overall magnitude response of 8 parallel filters                                        |    |  |  |

| Figure 3.15 | Magnitude response of MDLNS filterbank(5bit 3bit,5bit 3bit)                             |    |  |  |

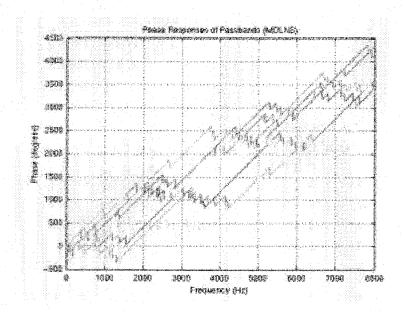

| Figure 3.16 | Phase response of MDLNS filterbank                                                      | 57 |  |  |

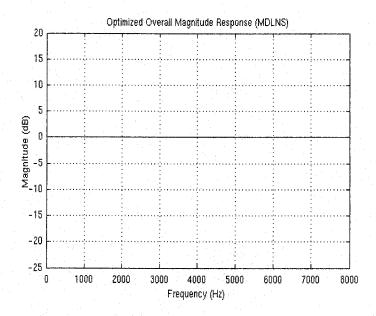

| Figure 3.17 | Flat overall magnitude response of MDLNS filterbank                                     |    |  |  |

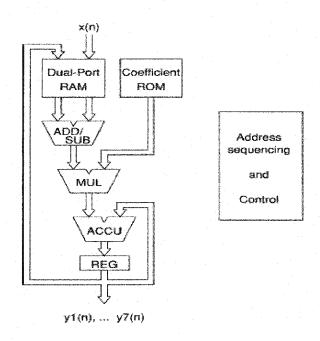

| Figure 4.1  | IFIR Filterbank Architecture.                                                           | 60 |  |  |

| Figure 4.2  | The address sequence for filter H7 (indicating the address pairs for the dual-port RAM) |    |  |  |

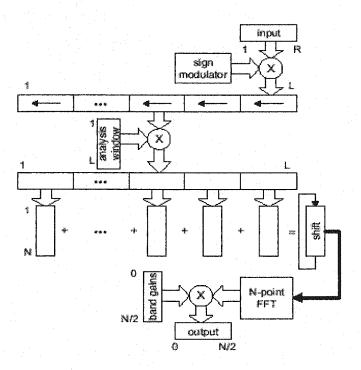

| Figure 4.3  | WOLF DFT analysis processing                                                            |    |  |  |

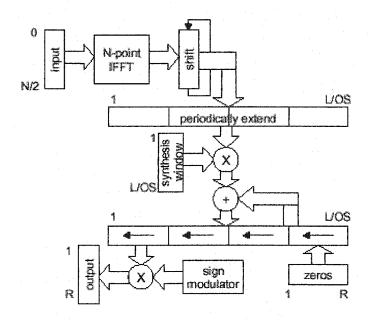

| Figure 4.4  | WOLA DFT filterbank synthesis processing                                                |    |  |  |

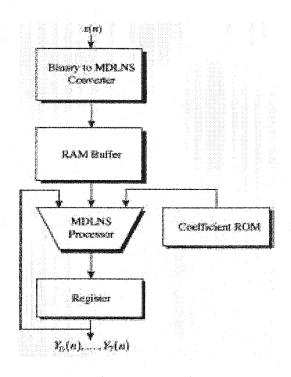

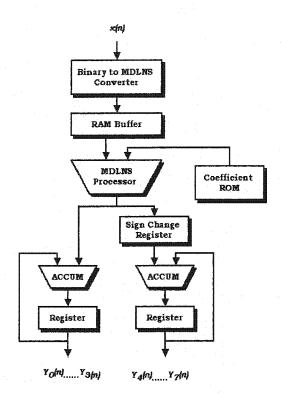

| Figure 4.5  | 8-bank 2-DLNS filter architecture                                                       |    |  |  |

| Figure 4.6  | Improved MDLNS processor                                                                |    |  |  |

| Figure 5.1  | Digital ASIC Design Method                                                              |    |  |  |

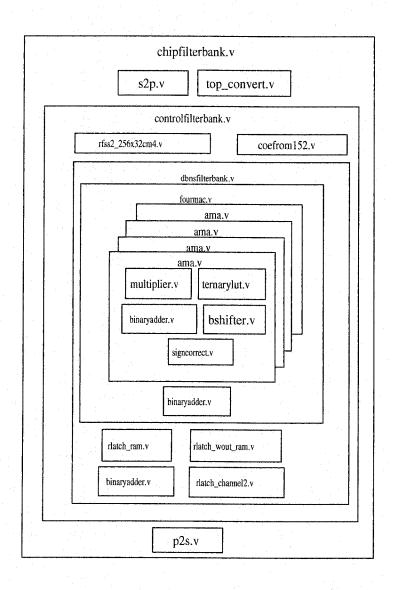

| Figure 5.2  | Hierarchal diagram for HDL description of a MDNS filterbank                             |    |  |  |

| Figure 5.3  | Verilog simulation of the entire MDLNS filterbank                                       |    |  |  |

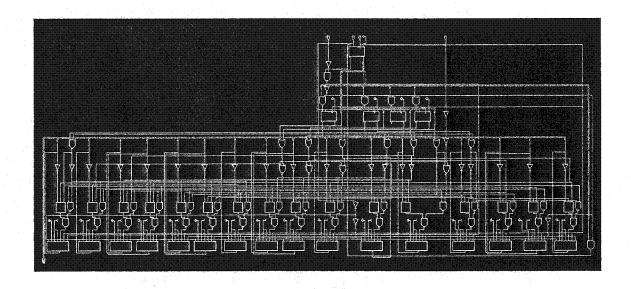

| Figure 5.4  | Gate level input data serial to parallel converter block (128 cells)                    |    |  |  |

| Figure 5.5  | Gate level binary to MDLNS converter block (762 cells)                                  | 74 |  |  |

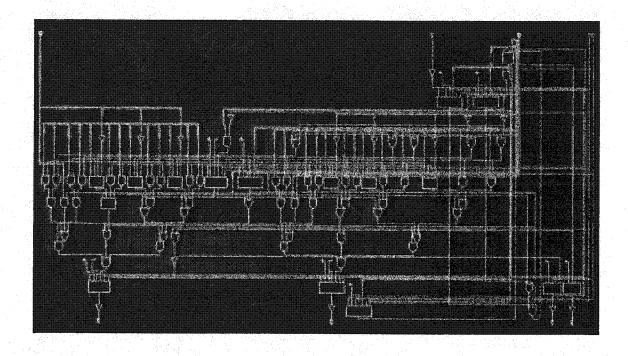

| Figure 5.6  | Gate level MDLNS filterbank block (1883 cells)                                          | 75 |  |  |

| Figure 5.7  | Gate level output data parallel to serial converter block (69 cells)                    | 76 |  |  |

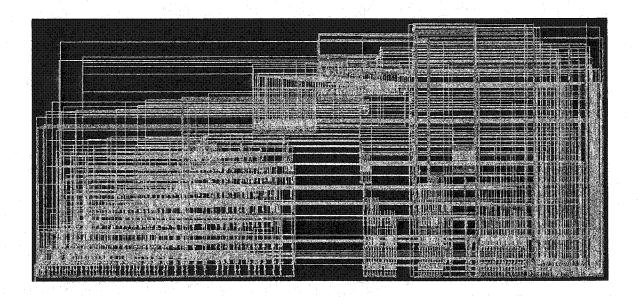

| Figure 5.8  | Design of MDLNS filterbank processor after placement                                    | 77 |  |  |

| Figure 5.9  | Design of MDLNS filterbank processor after CTGen                                        |    |  |  |

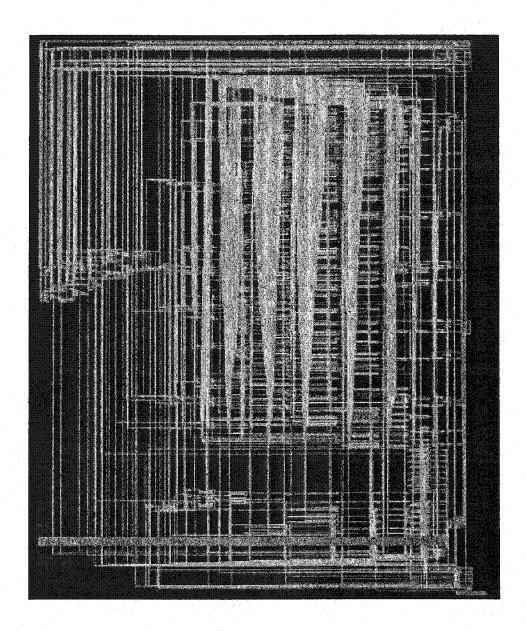

| Figure 5.10 | Design of MDLNS filterbank processor after routing                                      | 79 |  |  |

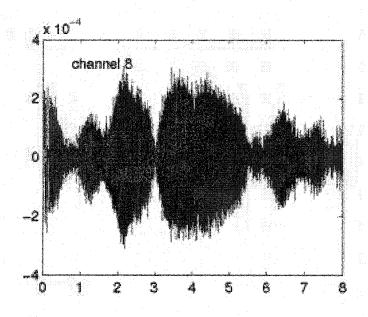

| Figure 5.11 | Block graph of MDLNS filterbank chip                                                    | 80 |  |  |

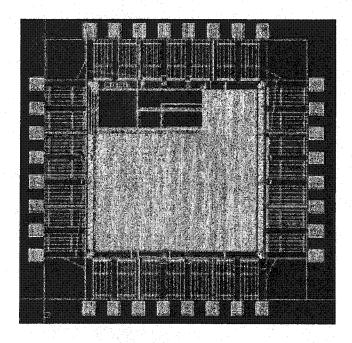

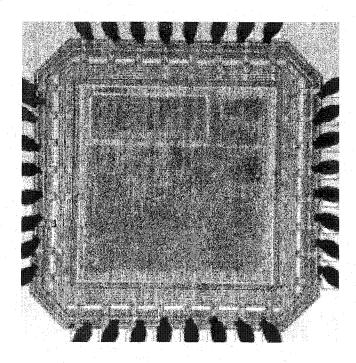

| Figure 5.12 | Layout of the MDLNS filterbank chip                                                     | 81 |  |  |

| Figure 5.13 | Micrograph of the fabricated MDLNS filterbank processor chip                            | 81 |  |  |

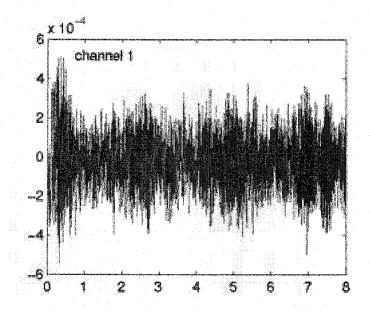

| Figure 6.1  | Quantization noise of 16 bit binary system: channel one                                 | 83 |  |  |

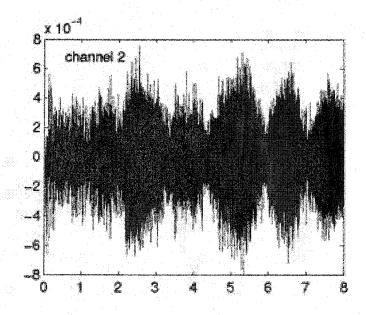

| Figure 6.2  |                                                                                         |    |  |  |

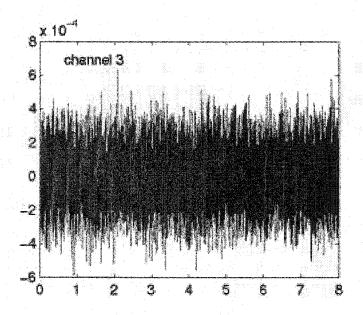

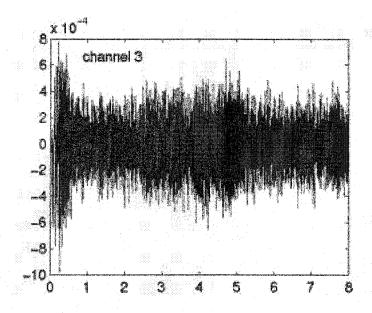

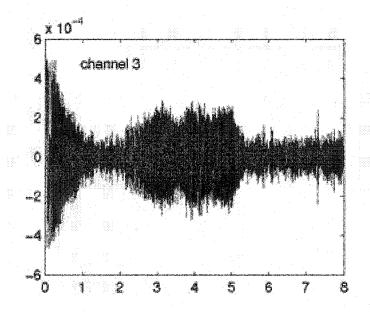

| Figure 6.3  | Quantization noise of 16 bit binary system: channel 3                                   | 84 |  |  |

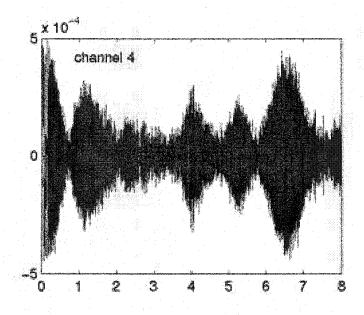

| Figure 6.4  | Quantization noise of 16 bit binary system: channel 4                                   | 84 |  |  |

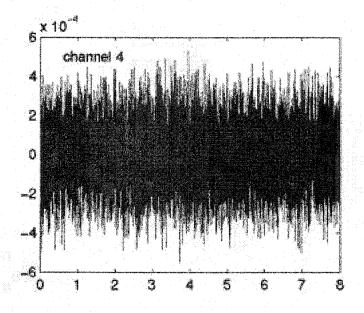

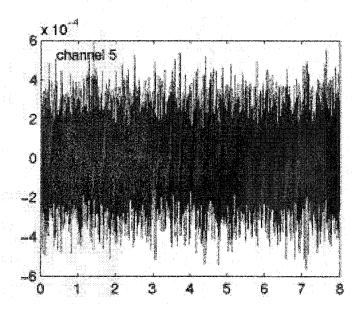

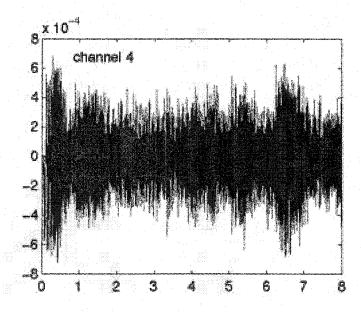

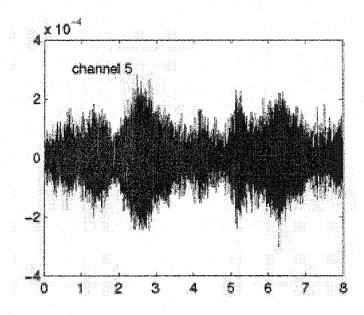

| Figure 6.5  | Quantization noise of 16 bit binary system: channel 5                                   | 85 |  |  |

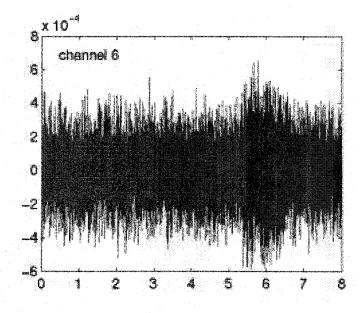

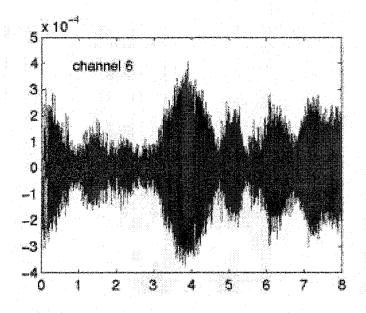

| Figure 6.6  | Quantization noise of 16 bit binary system: channel 6                                   | 85 |  |  |

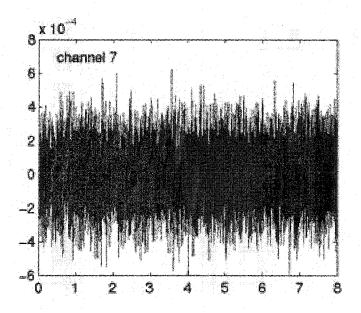

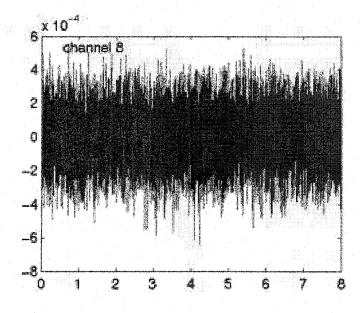

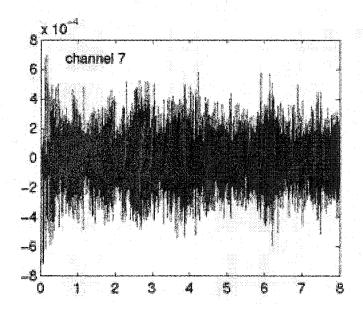

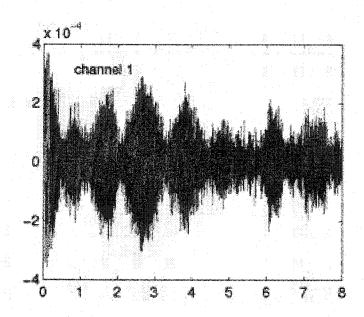

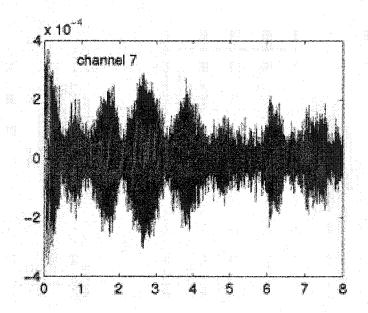

| Figure 6.7  | Quantization noise of 16 bit binary system: channel 7                                   | 86 |  |  |

| Figure 6.8  | Quantization noise of 16 bit binary system: channel 8                                   | 86 |  |  |

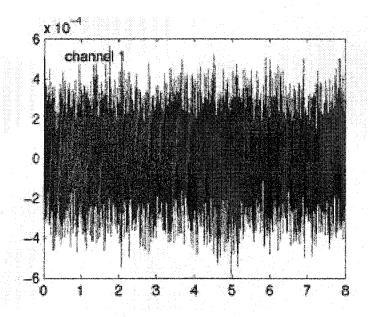

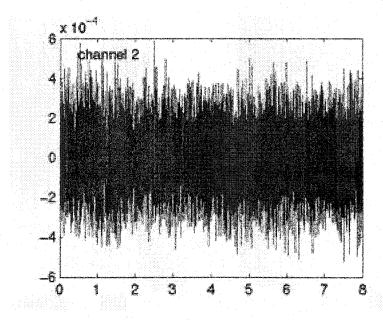

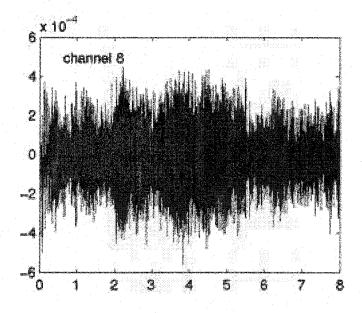

| Figure 6.9  | Quantization noise of MDLNS filterbank channel 1 (input 5 4 5 4)                        |    |  |  |

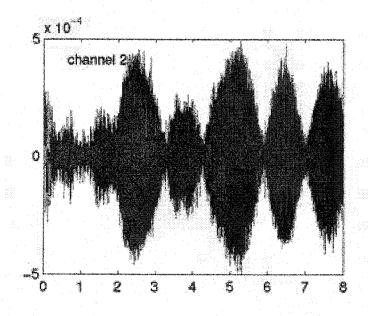

| Figure 6.10 | Quantization noise of MDLNS filterbank channel 2 (input 5 4 5 4)                        | 87 |  |  |

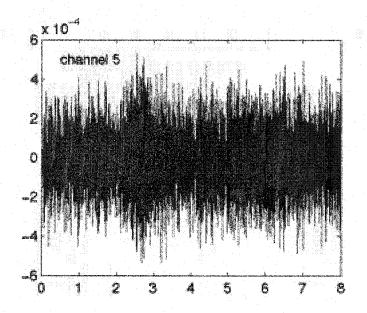

| Figure 6.11 | Quantization noise of MDLNS filterbank channel 3 (input 5 4 5 4)                        | 88 |  |  |

| Figure 6.12 | Quantization noise of MDLNS filterbank channel 4 (input 5 4 5 4) | 88  |

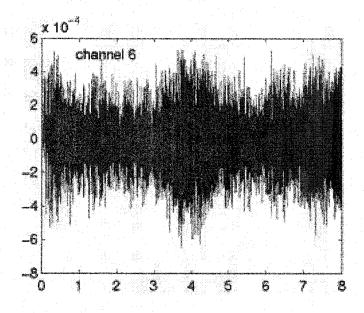

|-------------|------------------------------------------------------------------|-----|

| Figure 6.13 | Quantization noise of MDLNS filterbank channel 5 (input 5 4 5 4) | 89  |

| Figure 6.14 | Quantization noise of MDLNS filterbank channel 6 (input 5 4 5 4) | 89  |

| Figure 6.15 | Quantization noise of MDLNS filterbank channel 7 (input 5 4 5 4) | 90  |

| Figure 6.16 | Quantization noise of MDLNS filterbank channel 8 (input 5 4 5 4) | 90  |

| Figure 6.17 | Quantization noise of MDLNS filterbank channel 1 (input 5 5 5 5) | 91  |

| Figure 6.18 | Quantization noise of MDLNS filterbank channel 2 (input 5 5 5 5) | 91  |

| Figure 6.19 | Quantization noise of MDLNS filterbank channel 3 (input 5 5 5 5) | 92  |

| Figure 6.20 | Quantization noise of MDLNS filterbank channel 4 (input 5 5 5 5) | 92  |

| Figure 6.21 | Quantization noise of MDLNS filterbank channel 5 (input 5 5 5 5) | 93  |

| Figure 6.22 | Quantization noise of MDLNS filterbank channel 6 (input 5 5 5 5) | 93  |

| Figure 6.23 | Quantization noise of MDLNS filterbank channel 7 (input 5 5 5 5) | 94  |

| Figure 6.24 | Quantization noise of MDLNS filterbank channel 8 (input 5 5 5 5) |     |

| Figure 6.25 | Micrograph of the IFIR chip                                      | 96  |

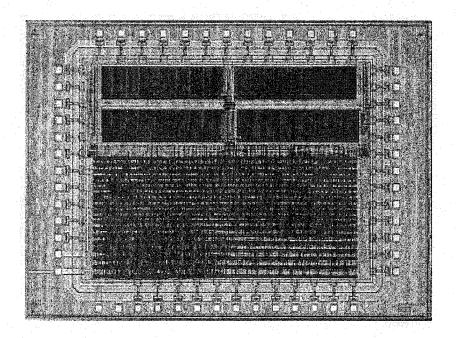

| Figure D.1  | Overview of the test setup                                       |     |

| Figure D.2  | Testing lab for MDLNS Filterbank Processor Chip                  |     |

| Figure D.3  | List of hardware connections                                     | 171 |

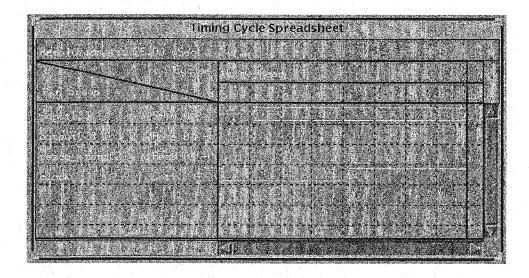

| Figure D.4  | Timing cycle of MDLNS filterbank chip testing                    | 172 |

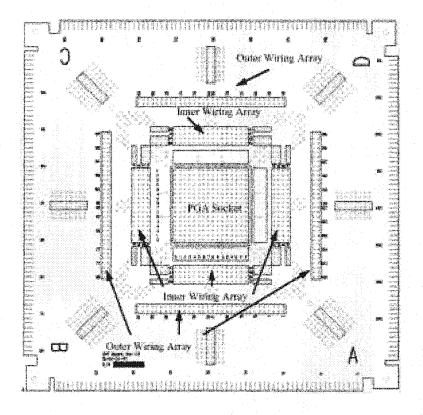

| Figure D.5  | Device Under Test Board                                          | 173 |

| Figure D.6  | Testing chip and DUT board                                       | 174 |

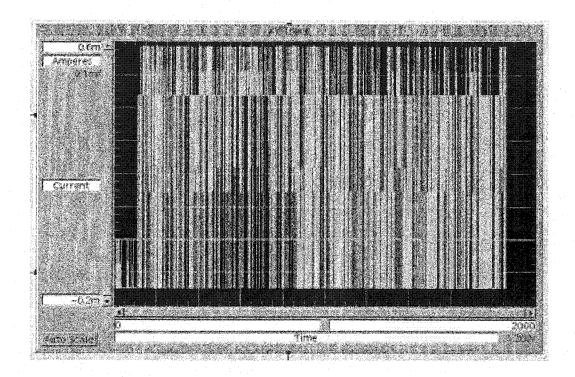

| Figure D.7  | Current measurement interconnections                             | 176 |

| Figure D.8  | Current of power supply display                                  | 176 |

### **List of Tables**

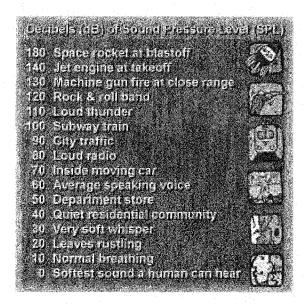

| Table 1.1 | Sound examples for dynamic range of human hearing             | 3   |

|-----------|---------------------------------------------------------------|-----|

| Table 1.2 | Octave bands of human hearing and their characteristics       |     |

| Table 1.3 | Hearing loss degrees and their effects                        |     |

| Table 2.1 | Classical LNS and 2D LNS Comparison                           | 35  |

| Table 3.1 | IFIR filterbank coefficients not equal to zero                | 42  |

| Table 6.1 | Synospys Power Compiler results of MDLNS filterbank processor | 97  |

| Table D.1 | pin-to-pod mapping                                            | 174 |

# Chapter 1

#### Introduction

#### 1.1 Introduction

In this thesis, research on current digital filterbank algorithms, architectures, and hardware implementation for CIC (completely in the canal) digital hearing instruments is carried out. The design and implementation of a filterbank for digital hearing aids using the Multidimensional Logarithmic Number System (MDLNS) is carried out.

The history of hearing instruments can be traced from the 19th century on, but it is known that Greeks used shells and Romans had bronze funnels as hearing instruments. In 1800 the first hearing instrument company, which was manufacturing tubes and trumpets as hearing instruments, was established. In the mid 1890's the first patent for an electrical hearing aid was filed but the invention never reached production. 1899 was the year that the first commercially manufactured hearing aid, Akoullalion, made of carbon, was produced. The first vacuum tube hearing aid, which was very heavy and worn on the body, was patented in 1921. It consisted of a microphone, an earphone, an amplifier and two batteries, which would last only one day. With the commercial introduction of transistor technology, after 1953, the size of the hearing aids

became much smaller and their capabilities were increased. In 1970 the first hybrid hearing aids, which had analog and digital circuitry were manufactured. In 1988 many programmable hearing aids were introduced; they used analog circuitry, which was programmed, digitally, with computers. In 1996 the first behind the ear 100% digital hearing instrument was manufactured [1].

### 1.2 Human Hearing

#### 1.2.1 Dynamic Range

The dynamic range of human hearing is defined as the difference between the audible weakest sound and the highest comfortable level, where discomfort starts. The nominal threshold of hearing ( $P_0$ ) at 1kHz is measured as  $2 \cdot 10^{-5}$  Pa. In order to derive the intensity of this pressure, we first define acoustic resistance. Acoustic resistance, r, varies with temperature because of its dependence on the density of air,  $\rho$ , and the speed of sound, s, according to Eqn. (1.1). At 0 °C the acoustic resistance is 428 Rayls,

$$r = \rho \cdot s \tag{1.1}$$

whereas at room temperature it is reduced to 415 Rayls. To achieve a standard, the intensity threshold,  $I_0$ , at room temperature, is derived:

$$I_0 = (P_0)^2/r = (2 \cdot 10^{-5})^2/415 = 0.964 \cdot 10^{-12} \approx 10^{-12} Watts/m^2$$

(1.2)

10<sup>-12</sup> Watts/m<sup>2</sup> is defined as the weakest audible sound intensity level at 1kHz. The intensity or pressure of a sound signal is defined as the ratio of its value to these threshold values. The sound pressure level (SPL) and sound intensity level (IL) equations are:

$$SPL = 20 \cdot \ln(p/p_0)$$

$IL = 10 \cdot \ln(I/I_0)$  (1.3)

Introduction Human Hearing 2

The dynamic range of human hearing is accepted as from 0 dB SPL  $(2 \cdot 10^{-5} \text{ Pa})$  to 120 dB SPL (20 Pa). Over 120 dB SPL sound causes discomfort and damage in our ear [1]. Table 1.1 shows some example sounds with their SPL and intensity values.

Actually human hearing is not only intensity dependent. The weakest audible sound intensity differs according to the frequency of that sound. For example, the weakest audible sound at 10 kHz is 20 dB SPL but the weakest audible sound at 100 Hz is 40 dB SPL [1].

Table 1.1 Sound examples for dynamic range of human hearing

#### 1.2.2 Frequency Range

The frequency range of human hearing is generally accepted to be 20 Hz to 20 kHz. The cochlea splits the sound signal approximately into octave bands (a factor of two increase in frequency), thus human hearing covers approximately 10 octaves. The bands and their characteristics are given in Table 1.2 [1]. Each octave gives different characteristics to the sound signal. Because of the logarithmic frequency distribution of human hearing, the bandwidths of octave bands are increasing along the frequency axis. This shows that different, but equal amount of, audio information is located between 20 Hz - 40 Hz and 10

Introduction Human Hearing 3

kHz- 20 kHz. Therefore if we omit the 10 th octave of the sound signal, the signal will still carry 90% of its information [1].

| Octave | Frequency Range |                                                                                                  |

|--------|-----------------|--------------------------------------------------------------------------------------------------|

| 1st    | 20-40 Hz        | Low Bass - These frequencies add fullness, power                                                 |

| 2nd    | 40-80 Hz        | and boom to sound. Lowest notes of bass, piano and tuba fall into this category.                 |

| 3rd    | 80-160 Hz       | Upper Bass - These frequencies provide a balance                                                 |

|        |                 | in the structure of sound. Without them, sound is                                                |

| 4th    | 160-320 Hz      | thin. The lower tones of the cello, trombone and rhythm sections produce sounds in this range.   |

| 5th    | 320-640 Hz      | Midrange - Sounds get their intensity from this                                                  |

| 6th    | 640-1280 Hz     | range of frequencies. Fundamentals and lower harmonics of most sound sources fall into this cat- |

| 7th    | 1280-2560 Hz    | egory.                                                                                           |

| 8th    | 2560-5120 Hz    | Upper Midrange - Humans hear this range of fre-                                                  |

|        |                 | quencies best. 3000-3500 Hz contains informa-                                                    |

|        |                 | tion, which improves the intelligibility of speech                                               |

|        |                 | and lyrics. If this band is incorrectly processed,                                               |

|        |                 | sound becomes unpleasant. Frequencies above                                                      |

|        |                 | 3500 Hz give sound realism and clarity. Listeners                                                |

|        |                 | perceive sound in this section of the octave (and                                                |

|        |                 | up to about 6000 Hz in the 9th octave) as being                                                  |

|        |                 | close. Thus, 3500-6000 Hz is known as the pres-                                                  |

|        |                 | ence range.                                                                                      |

| 9th    | 5120-10240 Hz   | Treble - Frequencies in this range give sound                                                    |

| 10th   | 10240-20480 Hz  | sparkle and brilliance. Most humans do not hear much beyond 16000 Hz                             |

Table 1.2 Octave bands of human hearing and their characteristics

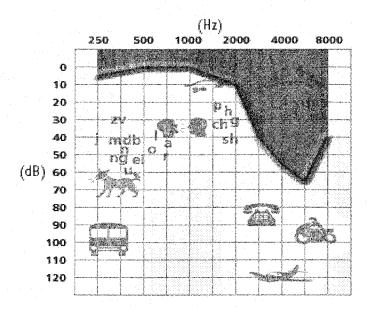

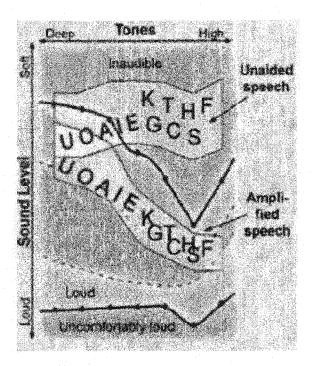

Male speech lies between 100 Hz and 8 kHz, whereas the harmonics of female speech can reach up to 10 kHz. The frequency and dynamic ranges of speech and music are plotted in Figure 1.1 [1]. The solid line shows the border of normal hearing. We observe that human speech can be totally extracted if the original signal is low-pass filtered up to 8 kHz. On the other hand music covers a wider frequency band than does speech [1].

Introduction Human Hearing 4

Figure 1.1 Frequency and intensity ranges of speech and music

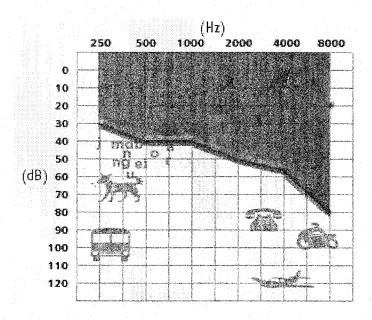

The letters shown in the figure below symbolize sounds in our language. They are spread across frequencies and intensities. The consonants are critical for speech understanding. Note how they are centered in the high frequency area where most hearing losses occur [3].

### 1.3 Hearing Loss

The intricate structure of the human ear can be damaged by different sources. The degrees of hearing losses and their effects are given in Table 1.3 [1]. Hearing Loss is generally separated into two categories: 'Conductive Hearing Loss' and 'Sensorineural Hearing Loss'.

Introduction Hearing Loss 5

Table 1.3 Hearing loss degrees and their effects

| LOSS         | CLASSIFICATION               | EFFECTS                                |

|--------------|------------------------------|----------------------------------------|

| 0-15 dB SPL  | Norman hearing               |                                        |

| 16-25 dB SPL | Borderline normal (children) | <del>-</del>                           |

| 15-25 dB SPL | Slight                       | Minimal difficulty with soft speech    |

| 25-40 dB SPL | Mild                         | Difficulty with soft speech            |

| 40-45 dB SPL | Moderate                     | Frequent difficulty with normal speech |

| 46-70 dB SPL | Moderate-severe              | Occasional difficulty with loud speech |

| 71-90 dB SPL | Severe                       | Frequent difficulty with loud speech   |

| >91          | Profound                     | Near total loss of hearing             |

#### 1.3.1 Conductive Hearing Loss

Conductive hearing loss is caused by damage to, or a malfunction of, the outer and middle ear. The reasons for this loss include: abnormality of the outer ear, ossicular discontinuity, middle ear infection, otosclerosis, perforated eardrum, earwax. It is because of the fact that the inner ear is functioning properly, that conductive hearing losses can be treated either medically or surgically [3].

#### 1.3.2 Sensorineural Hearing Loss

This type of hearing loss covers disorders of the inner ear and the auditory neural system. Commonly the problem is due to the damage of the haircells inside the cochlea. The hearing can diminish gradually or suddenly (as with a trauma). The result is permanent hearing loss, which can not be cured with medicine or by surgery [1]. 80% of the patients who are suffering from hearing loss have sensorineural loss. Therefore, hearing instrument designers focus on this portion of hearing loss.

#### Causes and characteristics of sensorineural hearing loss [3]

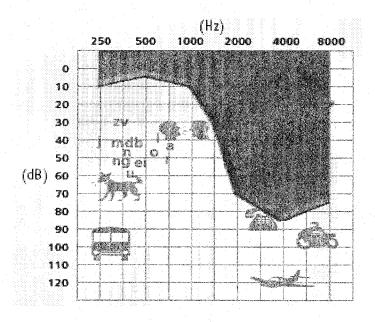

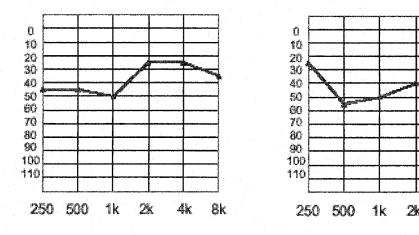

Aged induced - or presbycusis: All human beings suffer a loss of hearing as part of the aging process. Gradual deterioration of hair cells in the inner ear can lead to a significant hearing loss. All frequencies may be affected, but it is mainly the loss of the high frequency area that results in difficulty in understanding speech, as shown in Figure 1.2. It also shows us that aging causes more hearing loss for males than for females.

Figure 1.2 Age-induced hearing loss

Introduction Hearing Loss 7

#### Noise induced hearing loss:

An acoustic trauma or having been subjected to excessive noise for extended periods of time causes 'noise induced' hearing loss. These patients will loose some high frequency sounds as shown in Figure 1.3, but it is primarily the loss of hearing sensitivity that makes listening difficult in heavy background noise.

Figure 1.3 Noise induced hearing loss

#### Ski-slop hearing loss:

The causes of this type of hearing loss are one or more of the following: acoustic trauma, extended periods of time spent in excessive noise, lack of oxygen during birth, virus infection, genetic defects, a severe side effect of medication. A ski-slope hearing loss is often a combination of loss of inner and outer hair cells. The effect is a significant loss of high frequency sounds as shown in Figure 1.4.

8k

Figure 1.4 Ski-slope hearing loss

Meniere's Disease represents a typical low-frequency hearing impairment. Trauma can also causes mid-frequency loss, as shown in Figure 1.5 [2].

Figure 1.5 (left) Meniere's Disease (low\_frequency loss), right: Trauma (mid\_frequency loss)

Introduction Hearing Loss 9

### 1.4 Hearing Instrument Types

Hearing instruments can be grouped, according to their sizes, into four categories: BTE (behind the ear), ITE (in the ear), ITC (in the canal) and CIC (completely in the canal) [1].

**BTE** (**Behind the ear**): These hearing instruments rest behind the earlobe and connected to the ear by a custom earmold. Their location allows a relaxation in their size constraint. Therefore circuits allowing more gain can be used. BTE instruments can be used to correct a wide range of hearing losses from mild to profound.

Figure 1.6 BTE type of hearing aid [3]

ITE (In the ear): These instruments fit in the bowl of the ear and are visible in the ear. They are also powerful based on their size and can be used for hearing losses from mild to severe.

Figure 1.7 ITE type of hearing aid [3]

ITC (In the canal): These hearing instruments are located further into the canal than the ITE types, but are still visible. They can be used for hearing losses from mild to moderate.

Figure 1.8 ITC type of hearing aid [3]

CIC (completely in the canal): These instruments go very deep inside the ear canal and are almost invisible as shown in Figure 1.9. Therefore they provide more comfort and cosmetic value. Because of the closer proximity to the eardrum and the resonance characteristic of the ear canal, less power is required to provide equal amounts of amplification compared to the other instrument types. The other hearing instruments also have the 'occlusion effect', which refers to the sensation of "talking in a barrel". This is greatly reduced or eliminated with CIC hearing aids. Another advantage is reduced wind noise [1].

Figure 1.9 CIC Hearing instrument placement

### 1.5 Hearing Instrument Technologies

For persons with sensorineural hearing losses it is necessary that the frequency response is optimally fitted into their residual hearing area, and that the fitting is valid under various conditions, such as a change in input level. Hearing instruments ideally optimize speech intelligibility for the listener, while maintaining user comfort. In recent years, there has been a transition, in the design of hearing instruments, from analog technology to digital technology. In general, we can identify three major types of hearing instruments [1]:

Analog Hearing Instruments: This type of hearing instrument is also referred to as a conventional hearing instrument. The instrument comprises a microphone, an amplifier unit, a loudspeaker and a battery. The circuitry used in these hearing instruments is totally analog. There are several drawbacks to the use of analog technology, including difficulty in obtaining high resolution in the frequency domain; analog hearing aids usually have a maximum of two frequency channels. The instruments are adjusted manually through

trimmer potentiometers; this adjustment is not accurate and can drift. These instruments generally apply only linear amplification.

**Programmable Hearing Instruments**: This type of hearing instruments is based on analog circuitry, where a memory module replaces the potentiometers. The memory module can be a RAM or EEPROM, which is accessed through an external microprocessor. They are basically analog hearing aids, whose control is improved through digital technology. Even if the patients hearing changes they can be reprogrammed instead of having to obtain a completely new instrument. Compression is achieved through sound-level dependent amplification.

Both analog and hybrid hearing aids, with only low order filtering possibilities, exhibit difficulties in obtaining appropriate corrective frequency responses.

Digital Hearing Instruments: These instruments convert the analog signal, received from the microphone, to a digital data stream, and process the signal with DSP (digital signal processing) algorithms. The output is converted again to an analog signal, which drives the loudspeaker. In the signal processing part, the sound is split into multichannels, where the frequency shaping of the sound signal is performed according to the patient's audiogram. Nonlinear amplification parameters are set once and the algorithm adjusts itself according to the intensity level of the input sound. Besides compression algorithms, speech enhancement algorithms are also used. These allows better overall sound quality and compensation of loudness growth. More sophisticated signal processing, such as adaptive noise cancellation and acoustical feedback cancellation, will be simplified by using digital processing.

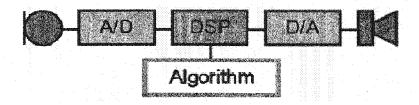

Figure 1.10 Digital hearing instrument structure [1]

Figure 1.11 An example of the DSP part of the hearing aid block diagram

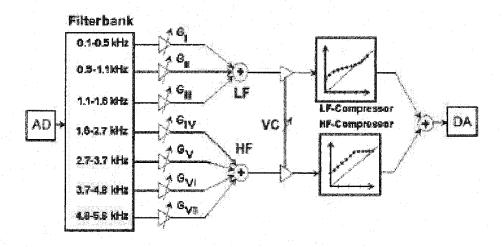

As shown in Figure 1.11, the DSP block contains a filterbank and compression blocks.

#### **Filterbank**

As plotted and tabulated in Section 1.3.2 sensorineural hearing loss can exhibit different types of frequency characteristics. The reason for this is based on the fact that the cochlea operates as a filterbank and damage to the organ of corti, sensing a specific band, results in narrowband hearing loss. Therefore, the hearing instrument should provide high frequency resolution in order to compensate properly. Considering that the bandwidth of a telephone line is between 200 Hz and 3.2 kHz, a frequency range up to 8 kHz would cover almost the entire speech components and most of the music components, as demonstrated in Figure 1.1. In terms of an octave scale, 90% of the sound information would be covered [1].

Digital filterbanks can be used to obtain an arbitrary magnitude response with exact linear phase. This provides considerable flexibility and ease whereby the characteristics of a digital filter can be instantaneously adjusted [13].

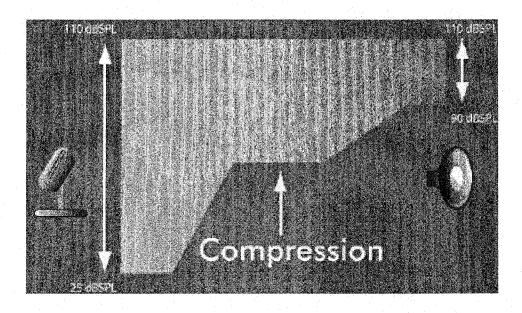

#### Compression

Because of the dynamic range reduction and rapid loudness growth, linear amplification can not be applied to hearing instrument sound signals. This would amplify soft signals to the audible range but loud signals would be amplified to the uncomfortable range. Therefore, modern hearing instruments apply compressive amplification, which maps the speech signal into the dynamic range of the hearing impaired person. This is demonstrated in Figure 1.12 [1].

Figure 1.12 Compressive amplification

Low power and small size are two important constraints for a digital hearing aid. A hearing aid is required to run on a single cell zinc-air battery ( $V_{supply}=1V$ ) for a minimum of one week; thus, the maximum power consumption should be less than 1mA @ 1V = 1mW. The maximum dimensions for a CIC hearing are: length < 3mm, width <5mm, height < 2 mm [4]; a hearing aid integrated circuit should clearly fit into these dimensions, which constrains the sophistication of the processing circuitry, based on the fabrication technology.

The filterbank is a core part of current digital hearing aids and constitutes about half of the signal processing circuitry [14]. In this research we focus on the filterbank design and implementation.

#### 1.6 MDLNS

As mentioned previously, the hearing loss compensation in a typical digital hearing instrument, is performed by separating the input signal into multiple frequency bands which are then compressed to allow the amplification of low level signals while maintaining the amplitude of high level signals. We thus require a processor that is able to

both perform linear processing (band separation), and non-linear processing for signal compression. In order to be able to adequately represent the very low level signals, that are subject to the maximum amplification in the processor, very large word-lengths are required, and floating point representation is quite usual in this regard [11]. To be practically usable in a completely-in-canal (CIC) device, the digital circuitry needs to fulfill the joint requirements of low power consumption and small size. The Multidimensional Logarithmic Number System (MDLNS) is a recently developed number system [5] that appears to be a good candidate for implementing hearing instrument processors. Although the LNS has been previously considered for digital hearing aid circuitry. As with the LNS, the MDLNS provides a reduction in the size of the number representation, but the MDLNS promises a lower cost (area×power) implementation of the arithmetic operations required in both the linear and non-linear domains of filtering and compression. In this research we apply the MDLNS to the construction of a finite impulse response (FIR) filterbank for digital hearing instruments.

We use the MDLNS representation for the filterbank design in order to both reduce the size of the number representation and to allow a relatively low cost implementation of the operations of multiplication. This number representation uses both a one and two digit MDLNS where the digits are represented by the indices of their bases. This provides a logarithmic type of representation with the added advantage of allowing orthogonal implementations of the index computation on each base.

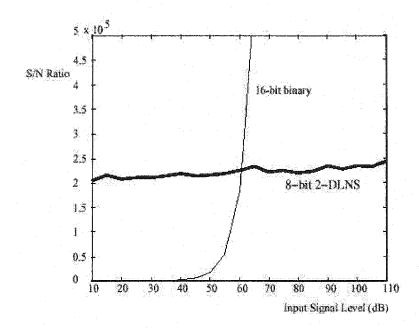

In the MDLNS domain (as with logarithmic arithmetic with a radix of 2) we can more accurately represent smaller values compared to an integer binary representation, and the percentage error normalized to the signal magnitude remains quite constant. Figure 1.13 shows the signal-to-quantization noise ratio vs. input level of an input signal quantized to a single-digit 8-bit MDLNS and an equivalent 16-bit binary representation. The MDLNS representation provides a constant S/N ratio throughout the range of inputs, while the binary S/N ratio drops with input level. The MDLNS has a superior S/N ratio below 60 dB, the sound level of an average conversation;

Figure 1.13 Signal-to-quantization noise ratio vs. input level

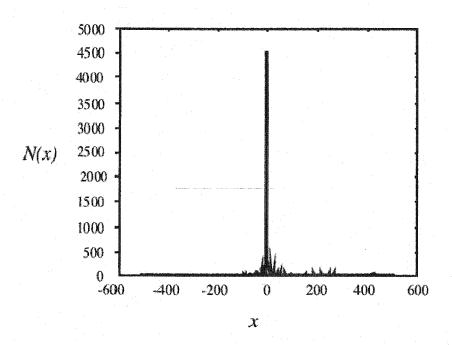

Figure 1.14 shows the distribution of filter coefficients from a study of 200 different designs using 9-bit quantization on the coefficients [5]. The distribution clearly shows that the density of filter coefficients is a Gaussian-like function centered on zero. Such a coefficient distribution is better represented by a logarithmic-like number system, such as the MDLNS, rather than a classical positional number representation (such as binary) [5]. So both input data and coefficients of digital filterbank are better represented by MDLNS than by a fixed-point binary representation.

Figure 1.14 Filter coefficient distribution

### 1.7 Thesis Organization

This thesis is organized into seven chapters and four appendices. The first chapter (this chapter) is an introduction. Chapter 2 covers MDLNS background theory both in terms of the representation and the arithmetic. Chapter 2 also provides a comparison between the MDLNS and LNS number systems. Chapter 3 discusses current digital filterbank algorithms and a new MDLNS filterbank algorithm. Chapter 4 presents architectures of three filterbanks. Chapter 5 provides verification of the MDLNS filterbank architecture through the simulation of a microchip of an 8-band filter at a hardware description language level. Chapter 6 provides some comparisons between the new designs and recently published designs; the comparisons include noise, area and power dissipation. Chapter 7 presents conclusions and potential future work.

Introduction Thesis Organization 19

# Chapter 2

# MDLNS Background Theory

#### 2.1 Introduction

The logarithmic number system (LNS) is an alternative to the classical binary representation and it has been the subject of some investigation [5], particularly in the field of digital signal processing (DSP), where the computation of inner (dot) products is a major computational step. In the LNS, multiplication and division are easy operations, whereas addition and subtraction are difficult operations, traditionally implemented by using large ROM arrays. Inner products computed in DSP algorithms are often between a predetermined set of coefficients (e.g., FIR filters or discrete transform basis functions) and integer data. For fixed point binary implementations, the uniform quantization properties (a constant error bound over all mapped input values) are perfectly matched to the mapping of most input data (the mapping of input data for non-linear hearing instrument processing is a counter-example), but often the predetermined coefficients are better suited to a non-uniform quantization mapping. A study of a large number of filter designs reveals a histogram that benefits from the quantization associated with a logarithmic mapping [5]. A logarithmic-like representation, multi-dimensional number system (MDLNS), was recently introduced [6] that promises

implementation improvements over the LNS while maintaining a logarithmic quantization distribution [5].

# 2.2 Representation

The MDLNS representation of a number differs somewhat from the traditional fixed radix form of representation. In a fixed radix positional system, a number is represented in the form:

$$\chi = \sum_{i=0}^{N} m_i r^i \tag{2.1}$$

where  $m \in \{0, 1, ..., r-1\}$ , i is an integer and r is the radix. For example in the decimal system r = 10, and in the binary system r = 2.

In the Logarithmic Number System (LNS)a number is represented by:

$$x = s_i 2^{a_i} \tag{2.2}$$

where  $a_i$  is an arbitrary real number.

We can build upon some well-established results on s-integers before defining a multidimensional logarithmic number system [5]. We start with two basic definitions.

<u>Definition 1</u>: An *s*-integer is a number whose largest prime factor does not exceed the *s*-th prime number.

For example, non-negative powers of two are 1-integers, numbers of the form  $2^a 3^b$ , a, b -non-negative integers, are 2-integers and so on.

MDLNS Background Theory Representation 21

<u>Definition 2</u>: Modified 2-integers are numbers of the form  $2^a p^b$ , p - odd prime.

Note that we do not impose restrictions on the sign of a and b in Definition 2.

<u>Definition 3</u>: A representation of the real number, x, in the form:

$$x = \sum_{i=1}^{n} s_{i} \prod_{j=1}^{b} p_{i}^{e_{j}^{(i)}}$$

(2.3)

where  $s_i \in \{-1, 0, 1\}$  and  $p_j, e_j^{(i)}$  are integers, is called a multidimensional *n*-digit logarithmic (MDLNS) representation of x. b is the number of bases used (at least two, the first one, that is,  $p_{I_j}$  will always be assumed to be 2. The next two definitions are special cases of Definition 3.

<u>Definition 4</u>: An approximation of a real number x as a signed modified 2-integer  $s2^ap^b$ , is called a two-dimensional logarithmic representation of x.

<u>Definition 5</u>: An approximation of a real number x as a sum of signed modified 2-integers  $\sum_{i=1}^{n} s_i 2^{a_i} p^{b_i}$  is called an n-digit two-dimensional logarithmic representation of x (2DLNS). The binary number system to be a subset of MDLNS if  $b_i = 0$  for all i. If p=3

then  $x = \sum_{i=1}^{n} s_i 2^{a_i} 3^{b_i}$ . In this form the number is represented by the sign and the exponents.

The exponent on the base of 2 is called the binary exponent, and the exponent on the base of 3 is called the ternary exponent. we will use a triple  $\{s_i, b_i, t_i\}$  to represent x. If we fix the binary and ternary exponent to a signed, fixed length representation, we can represent any real number to arbitrary precision. We use this kind of 2DLNS representation as an example to illustrate some characters of MDLNS.

MDLNS Background Theory Representation 22

For single-digit representation of the form:

$$y = s2^b 3^t \tag{2.4}$$

where  $s_i \in \{-1, 0, 1\}$  and b, t are signed integers. In this case we have the following theorem [9].

Theorem 1: For every  $\varepsilon > 0$  and every non-negative real number x, there exist a pair of integers a and b, such that the following inequality holds:

$$\left|x - 2^{a} 3^{b}\right| < \varepsilon \tag{2.5}$$

We may therefore approximate, to arbitrary precision, every real number with the triple  $\{s,$ b, t. We may look at this representation as a two-dimensional generalization of the binary logarithmic number representation. The important advantage of this generalization is that the binary and ternary exponents are operated on independently from each other, with an attendant reduction in complexity of the implementation hardware. As an example, a VLSI architecture for inner product computation with the MDLNS proposed in [9][7], has an area complexity dependent entirely on the dynamic range of the ternary exponents. Providing that the range of the ternary exponent is smaller than the LNS dynamic range for equivalent precision, then we have the potential for a large reduction in the MDLNS hardware compared to that required by the LNS. We can capitalize on this potential improvement by placing design constraints on the ternary exponent size. For example, if we want to represent digital filter coefficients in the MDLNS, then we can design the coefficients in such a way that the ternary exponent is minimized; an integer programming task [5]. Although this approach is sound, and can produce modest improvements, generalizing the representation to multi-dimensions and/or multiple digits has the potential to bring about very large reductions in hardware complexity of DSP implementations.

It is important to note that an extension of the classical LNS to a multi-digit (or multi-component) representation does not provide any inherent advantages in terms of complexity reduction. We can show this for the special 2-digit 2-dimensional case with the following two theorems.

Theorem 2: Let x be an integer with the following 2-digit 2-base logarithmic approximation  $x \approx s_1 2^{a1} p^{b1} + s_2 2^{a2} p^{b2}$ . Then for  $\left| x - \left( s_1 2^{a1} p^{b1} + s_2 2^{a2} p^{b2} \right) \right| < 0.5$ , the dynamic range of  $a_1, b_1, a_2, b_2$  is  $0.5 \cdot \log(x) + o(\log x)$ .

<u>Theorem 3</u>: Let *x* be an integer with a 2-component LNS representation

$$x \approx s_1 2^{l_1} + s_2 2^{l_2} (2.6)$$

Then for  $|x - (s_1 2^{l_1} + s_2 2^{l_2})| < 0.5$  the dynamic range of  $l_1, l_2$  is  $\log(x) + o(\log x)$ .

Our conjecture is that both theorems are generalizable to n-digits. We can see from Theorems 2 and 3, that the dynamic range of the exponents is reduced by a factor of 2 for the 2DLNS, but for the 2-component LNS system there is no reduction at all. Since we will demonstrate that hardware complexity for the MDLNS is exponentially dependent on the size of the second base(s) exponent, we clearly have a potential for quite considerable hardware reduction providing that the following inequality is met:  $max(|b_1|,|b_2|) < max(|l_1|,|l_2|)$  [5].

# 2.3 Input Data Mapping

We will start this section using an example of a linear representation using the Double-Base Number System [9], DBNS, from which the MDLNS was developed.

Figure 2.1 A 2-digit DBNS representation of 79

Figure 2.1 shows one of the possible mappings of 79 into the DBNS. The black squares represent the location of a digit. The digits used are  $2^{0}3^{0}+2^{1}3^{1}+2^{3}3^{2}=1+6+72=79$ . The white squares represent the '0' digits and the black squares represent the '1' digits. From Figure 2.1 the DBNS is clearly a very sparse representation.

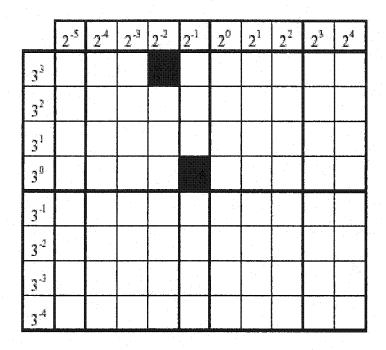

If negative exponents are used, the representation of real numbers, with arbitrary precision, can be obtained with single digits; in general, however, we can use more than one digit. Figure 2.2 shows the representation of the real number 7.25 using two digits  $2^{-2}3^3 + 2^{-1}3^0 = 63.75 + 0.5 = 7.25$ , and an expanded table using signed indices.

From our earlier definition of an MDLNS representation, we see that Figure 2.2 represents 7.25 using a 2-digit 2DLNS representation (1,-2,3), (1,-1,0) with bases 2 and 3. Note our short-hand for the digit as triples (*sign*, *binary exponent*, *ternary exponent*).

MDLNS Background Theory Input Data Mapping 25

Figure 2.2 A 2DLNS representation of 7.25

Clearly only a small number of digits are required to represent a number in the 2DLNS. For example, the number 103 can represented, approximately, by the two 2DLNS digits (1,-24,18), (1,19,-8) and 2315 can be represented, exactly, by the two digits (1,0,7), (1,7,0). Since the MDLNS is a redundant number system, most numbers will have more than one representation. For example 4.25 has 3 error free two digit MDLNS representations, while 7.25 has a single unique, error free, two digit MDLNS representation. It is provable that every real MDLNS representations, but realistically the majority will have at most 4 or 5 error free representations. This redundancy can be useful in allowing you to choose the best possible representation for your application [10].

# **2.3.1** Error-Free Representations

As stated in the introduction, most often in DSP applications the input data has to be converted from analog to a fixed point binary value with a uniform quantization error bound. Mapping to integers has a quantization error bounded by 0.5 for all converted values. For a classical LNS representation (and also a 1-digit MDLNS representation) we

MDLNS Background Theory Input Data Mapping 26

do not have this uniform quantization accuracy so we have to choose a sufficient number of bits so that we will be able to maintain this conversion accuracy for the larger data values. In the multi-digit MDLNS we can mitigate this quantization problem; in fact, we can find certain MDLNS representations that are completely error free! [5]

Consider the case of the two odd prime bases, (3, 5).

A representation of a real number into forms given in Definition 3 to 5 is called error-free if there is zero approximation error. The next three theorems and one conjecture have provided new results about the error-free two-dimensional logarithmic representation of numbers [5].

Theorem 4: Every real number, x, may have at most 91 different error-free 2-digit two-dimensional logarithmic representations.

<u>Theorem 5</u>: The smallest positive integer with no error-free 2-digit two-dimensional LNS representation in the case of odd base three is 103.

<u>Theorem 6</u>: The smaller positive integer with no error-free 2-digit two-dimensional logarithmic representation in the case of odd base five is 43.

The following conjecture is based on extensive numerical calculations.

Conjecture 1: The smallest positive integer with no error-free 3-digit two-dimensional logarithmic representation in the case of odd base three is 4985.

It is important to note that such results will be available (and different) for every particular set of bases that we choose. In this case (that is, a 3-digit two-dimensional logarithmic representation with odd base three) we see that a 12-bit error-free mapping is available; a useful dynamic range for many DSP applications.

#### 2.3.2 Non Error-Free Representations

Clearly, error-free representations are special cases of the MDLNS, but the extra degree of freedom provided by the use of multiple digits can mitigate the non-uniform quantization properties of the classical LNS [5].

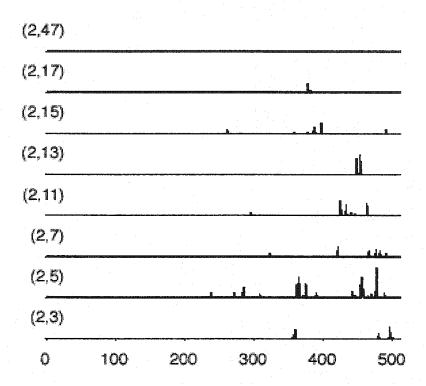

Figure 2.3 Absolute error (>0.5) for different second bases

To illustrate this, we present numerical results for mapping 10-bit signed binary input data to the 2-digit 2-D LNS where we treat the second base as a parameter. In order to demonstrate the ability to closely match input data with very small exponents, we have restricted the second base exponent to 3-bits. We are allowing the binary exponent to be somewhat larger, namely 6-bits, but, as we will see in the next section, this has very little bearing on the overall complexity of the inner product implementation (i.e., the hardware complexity is mainly driven by the dynamic range of the second exponents). As stated above, we require quantization errors to be <0.5 in order to match a binary representation. Figure 2.3 shows the results for parameters in the set {3,5,7,11,13,15,17,47}. The scale

for each graph is between 0.5 and 1 for the absolute error. There are two observations: 1) there are very few values in any of the results where the error exceeds 0.5; 2) there appears to be no correlation between the density of errors >0.5 and the value of the second base.

For a second-base of 47 we find no errors that exceed 0.5, whereas for *integer* bases below this value we find some error. Of course, we could speculate on the use of real numbers rather than integers for the second base, and we have some recent evidence that we can indeed reduce the absolute error below 0.5 for small real numbers in the some range.

To compare these results with an implementation using a classical LNS representation, we need to determine the number of bits of the logarithm to produce an absolute error of <0.5. A previous study has found that we require n+3 bits for the logarithm in order to achieve this accuracy for an n-bit positive number [12]. If we assume that the hardware complexity of the classical LNS representation is driven by the number of bits in the logarithm, then we can see a potential for enormous reduction in the implementation complexity of the 2-digit 2-D LNS versus the classical LNS [5].

### 2.3.3 Mathematical Operations

An 2DLNS representation provides a triple,  $\{s_i, b_i, t_i\}$ , for each digit, where  $s_i$  is the sign bit and  $b_i$ ,  $t_i$  are the exponents of the binary and non-binary bases. Thus a number, x, can be represented as given in Eqn. (2.7).

$$x = \sum_{i=1}^{n} s_i 2^{b_i} 3^{t_i} \tag{2.7}$$

#### **Multiplication and Division**

MDLNS multiplication and division are the simplest of the arithmetic operations. The equations for multiplication and division, given a single digit 2DLNS representation of  $x = (s_x, b_x, t_x)$  and  $y = (s_y, b_y, t_y)$ , are [9]:

$$x \cdot y = (s_x s_y, b_x + b_y, t_x + t_y)$$

(2.8)

$$x/y = (s_x s_y, b_x - b_y, t_x - t_y)$$

(2.9)

Eqn. (2.8) and Eqn. (2.9) show that single digit 2DLNS multiplication can be implemented in hardware using two independent binary adders and simple logic for the sign correction. As we start to add digits to the representation we will face the equivalent of implementing multiplication with the addition of partial products. A 2-digit representation will produce four independent partial products that will have to be added, and since addition is an expensive operation we have to deal with this in a special way. In this thesis we will use a multiplier accumulator structure that eliminates much of the complexity of performing addition within the 2DLNS representation. Multi-digit arithmetic is briefly dealt with later in this section.

#### **Addition and Subtraction**

Unfortunately, as with logarithms, addition and subtraction operations are not as simple as multiplication and division operations. Addition and subtraction must be handled through a set of identities and look-up tables. The identities are [9]:

$$2^{a}3^{b} + 2^{c}3^{d} = 2^{a}3^{b}(1 + 2^{c-a}3^{d-b})$$

$$\approx 2^{a}3^{b}\Phi(c-a, d-b)$$

(2.10)

$$2^{a}3^{b}-2^{c}3^{d} = 2^{a}3^{b}(1-2^{c-a}3^{d-b})$$

$$\approx 2^{a}3^{b}\Psi(c-a,d-b)$$

(2.11)

The operators  $\Phi$  and  $\Psi$  are lookup tables that store the precomputed values of:

$$\Phi(x, y) = 1 + 2^x 3^y \approx 2^\alpha 3^\beta$$

(2.12)

$$\Psi(x, y) = 1 - 2^x 3^y \approx 2^{\gamma} 3^{\delta}$$

(2.13)

The use of large look-up tables, implemented through the use of ROMs, for the evaluation of addition and subtraction operations is the traditional approach in systems such as the

Logarithmic Number System [10]. This technique is only feasible for very small ranges of 2DLNS numbers. It is more practical to convert the 2DLNS numbers to binary and perform the addition and subtraction using binary representation.

The conversions from 2DLNS to binary will still require a look-up table, but one that is much smaller than required for handling 2DLNS addition and subtraction. The look-up table is used to convert the second base portion of the 2DLNS number into a binary representation. Therefore the size of the look-up table is dependent on the number of bits used to represent the second base exponent.

#### **Multi-digit MDLNS Arithmetic**

Multi-digit MDLNS arithmetic is simply an extension of the single digit MDLNS arithmetic, and is necessary when numbers are represented by more than one MDLNS digit. When performing a computation using multi-digit MDLNS each digit can be treated as an independent MDLNS number and the operations handled separately. For example, if X and Y are 2 digit MDLNS numbers such that  $X = x_1 + x_2$  and  $Y = x_1 + x_2$  then:

$$X \cdot Y = (x_1 + x_2)(y_1 + y_2) = x_1 y_1 + x_1 y_2 + x_2 y_1 + x_2 y_2 \tag{2.14}$$

where  $x_i$  and  $y_i$  are single digit MDLNS numbers.

Eqn. (2.15) is an example of 2 digit MDLNS multiplication of 27 and 23

$$(2^{2}3^{2} - 2^{0}3^{2}) \cdot (2^{5}3^{0} - 2^{0}3^{2})$$

$$= 2^{2}3^{2} \cdot 2^{5}3^{0} - 2^{2}3^{2} \cdot 2^{0}3^{2} - 2^{0}3^{2} \cdot 2^{5}3^{0} + 2^{0}3^{2} \cdot 2^{0}3^{2}$$

$$= 2^{2+5}3^{2+0} - 2^{2+0}3^{2+2} - 2^{0+5}3^{2+0} + 2^{0+0}3^{2+2}$$

$$= 2^{7}3^{2} - 2^{2}3^{4} - 2^{5}3^{2} + 2^{0}3^{4}$$

$$= (1152)_{10} - (324)_{10} - (288)_{10} + (81)_{10}$$

$$= (621)_{10}$$

(2.15)

The independence of the arithmetic operations is very important, as it allows for parallel architectures. Furthermore, these parallel structures can be asynchronously clocked, reducing the power requirement of the circuit [10].

# 2.4 Hardware Complexity

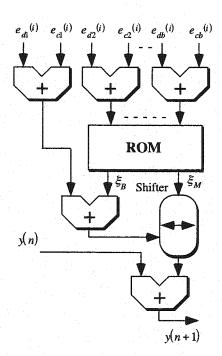

In order to provide complexity results for the MDLNS inner product computation unit, we expand on the inner product processor architecture initially developed for the 1-Digit 2-D LNS [9]. The processor can be used in a filterbank for 1-D convolution.

### 2.4.1 Single Digit Computational Unit

Figure 2.4 shows the structure of the proposed single-digit computation unit (CU). Since we do not require to retain the MDLNS representation of the accumulated output, and also since the CU is feedforward, we can use the MDLNS domain for the coefficient multiplication and a binary representation for the accumulated output.

Figure 2.4 1-digit MDLNS inner product computation unit

The multiplication is performed by parallel small adders for each of the data and coefficient base exponents. The addition output for each of the *b*-1 odd bases is concatenated into an address for a lookup table (ROM). This table produces an equivalent floating point value for the product of the odd bases raised to the exponent sum, as shown below:

$$\prod_{j=2}^{b} p_{j}^{(e_{dj}^{(i)} + e_{cj}^{(i)})} \approx 2^{\xi_{B}} \cdot \xi_{M}$$

(2.16)

We note that since the size of the exponents of each odd base in an MDLNS representation (where there are at least 2-digits and 2 bases) can be very small (<4 bits), then the maximum address input to the ROM is given by 4(b-1) bits. This is an 8-bit address table for a 3-D LNS. The shifter in the floating point to binary (2's complement) conversion part of the unit also handles the sign of the product (not shown in Figure 2.4 for brevity).

For large dimensional LNS, we can also consider the use of unity approximants to reduce the output of each odd-base adder to the number of bits of the input exponents (or even less if we are willing to accept the increased mapping error). This reduction process stores a small number of unity approximants that can be added in parallel to the output of the odd-base adders. The reduced input to the ROM is selected from these parallel results. The ROM input address size is now reduced by (b-1) bits. This is a subject of current research work and will not be explored further here. For the complexity analysis in Section 2.4.3., we will assume the structure of Figure 2.4 [5].

### 2.4.2 n-digit Computational Unit

The n-digit computational unit is a simple parallel extension of the 1-digit unit. Each of the units computes the binary output for one of the digit combinations. As an example, consider multiplying an accumulating sequence, y, with a coefficient, x,  $z = x \cdot y$ , where:

$$y = \sum_{i=1}^{2} s_{i}^{[y]} \prod_{j=1}^{2} p_{j}^{e_{j}^{[y](i)}}; \qquad x = \sum_{i=1}^{2} s_{i}^{[x]} \prod_{j=1}^{2} p_{j}^{e_{j}^{[x](i)}}$$

We can perform this with 4 parallel 1-digit units, where the (u, v) unit computes:

$$z_{u,v} = s_u^{[y]} \cdot s_v^{[x]} \prod_{j=1}^2 p_j^{(e_j^{[y](u)} + e_j^{[x](v)})}$$

(2.17)

Clearly there are  $n^2$  such units in an *n*-digit MDLNS. The parallel outputs are summed using an adder tree [5].

### 2.4.3 MDLNS Complexity Comparison

In terms of complexity comparison with the classical LNS, we need to compare each system based on the same quantization properties.

This will require a knowledge of the change in the size of the odd-base exponents as a function of dimensionality and number of digits. At the moment this appears to be a rather intractable task and so we have to resort to exhaustive search analysis. Here we report the results from 10 and 12-bit unsigned binary dynamic range (these are taken from typical video filter requirements). From Section 2.3.2., we obtain the number of bits for the classical LNS as n +3 shows these results.

Our assumption in Table 2.1 is that the ROM size dominates the hardware complexity. For the classical LNS and 1-digit 2D LNS, this is a valid assumption. For the 2-digit LNS the ROM size is very small and the other components in the architecture will undoubtedly be important in the overall complexity. Even so, it is clear that there is a very substantial reduction in the hardware complexity for the 2-digit case. We are currently performing a comparison analysis for a much larger set of digits and dimensions. Our initial findings point to the number of digits as being the primary contributor to the hardware savings [5].

Table 2.1 Classical LNS and 2D LNS Comparison

| Binary<br>Dynamic<br>Range | LNS | 1-digit 2D<br>LNS               | 2-digit 2D<br>LNS                         |

|----------------------------|-----|---------------------------------|-------------------------------------------|

| 10-bits                    | 8K  | 1K(10bit odd-<br>base exponent) | 64 words (4-bit<br>ternary expo-<br>nent) |

| 12-bits                    | 32K | 4K (12-bit odd-base exponent)   | 128 words (5-<br>bit ternary<br>exponent) |

# Chapter 3

# Digital Filterbank Algorithms

## 3.1 Introduction

There are five major forms of digital filterbanks that we compare here: QMF, Wavelet, Interpolated FIR (IFIR), DFT modulated, Parallel FIR. The first two banks are rejected based on the fact that the magnitude responses of the extended QMF bank and wavelet filter bank do not meet our frequency resolution criteria for hearing aids. The wavelet filter bank also does not allow perfect reconstruction [1].

This chapter covers the remaining three forms of digital hearing aid filterbank algorithm: Interpolated FIR (IFIR) filterbank, DFT modulated filterbank and parallel FIR MDLNS filterbank.

# 3.2 Design Constraints

The performance of a filterbank determines the frequency resolution of the instrument and the gain limits in each frequency band. The constraints listed at the end of the first chapter for the hearing instrument design are also the constraints for the digital filterbank design. The impacts of these constraints on digital filterbank design are explained in this section.

Frequency Range: It is shown in the first chapter that the frequency range of human hearing is from 20 Hz to 20 kHz. Because of the octave band characteristic of human hearing, good quality sound can still be achieved with half the frequency range coverage. In filter bank designs, 16 kHz is taken as sampling frequency. Because of the fact that spectrum coverage of a system is half of its sampling frequency, up to 8 kHz of the input sound signal is processed. This will cover the first nine octaves in Table 1.2 [1]

Number of Channels: Another important constraint is the frequency resolution. The monitoring of hearing loss is done through the generation of audiograms, which record measurements at eight different frequencies. Therefore 8 channels is an acceptable resolution for hearing instruments with more resolution at lower frequencies because of the octave characteristic of human hearing [1].

Stopband Attenuation: The stopband attenuation in each channel determines the gain range of the hearing instrument, and at least 50 dB of gain adjustment in each bank are required. The order of the filter is proportional to stopband and passband attenuation. When the order of the filter increases, the group delay and implementation cost increases. Therefore the tradeoff between these parameters should be well adjusted to achieve an optimum design [1].

*linear phase:* In a compression system, gain changes are dynamic. This may cause anomalies in the overall frequency response if phase differences exist between adjacent bands. To avoid these undesirable frequency response notches or peaks at the band edges (which frequently occur in analog systems), it is necessary to constrain the filter channel impulse responses to be linear phase and of equal delay.

**Power Consumption**: The power consumption is one of the most important constraints in filter bank design for hearing instruments. To achieve long battery life the circuitry inside the instrument should consume minimum power.

The most power consuming arithmetic unit in a VLSI implementation is multiplication [1] and the number of multiplications should be kept as small as possible. Besides the multiplication per unit time (MPU), addition per unit time (APU) is another important parameter to estimate the power consumption of the filterbank design [1].

Size: The research on filterbank design is for CIC model hearing instruments. Therefore the size of the filterbank structure should be kept as small as possible. This implies the use of minimum number of digital elements in filterbank structure, which also effects the power consumption.

# 3.3 IFIR Filterbank Algorithm Design

#### 3.3.1 Introduction

This filterbank employs linear phase interpolated FIR filters and their complement. Properties of these filters and filter bank design procedure are explained in this section.