#### University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

1999

# Testing asynchronous logic circuits from transistor networks to gate-level designs.

Kaamran. Raahemifar University of Windsor

Follow this and additional works at: http://scholar.uwindsor.ca/etd

#### **Recommended** Citation

Raahemifar, Kaamran., "Testing asynchronous logic circuits from transistor networks to gate-level designs." (1999). *Electronic Theses and Dissertations*. Paper 3735.

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

UMI®

•

# Testing Asynchronous Logic Circuits from Transistor Networks to Gate-Level Designs

by

#### Kaamran Raahemifar

**A** Dissertation

presented to the College of Graduate Studies and Research through Electrical Engineering in partial fulfilment of the requirements for the degree of Doctor of Philosophy at

the University of Windsor

Windsor, Ontario, Canada, 1999

©Kaamran Raahemifar 1999

#### National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérence

Our file Notre rélérence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-52440-X

# Canadä

I hereby declare that I am the sole author of this thesis.

I authorize the University of Windsor to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize the University of Windsor to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research. The University of Windsor requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

#### Abstract

This dissertation is concerned with testing of asynchronous circuits. Asynchronous circuits are attracting increasing interest for future generations of highspeed low-power logic circuits because they facilitate concurrent computation, offer average-case performance and better technology migration potential, and eliminate clock skew.

The research reported in this dissertation is a comprehensive study of testing asynchronous circuits using design-for-testability (DFT) techniques and test generation algorithms.

In the first part of the study we propose an on-line DFT technique for detecting short defects (or  $I_{DDQ}$  faults), which create a low-resistance path between the supply lines. It is shown that  $I_{DDQ}$  testing, delay testing, and stuck-open testing are necessary in order to achieve a high defect coverage. The second DFT technique presented in this part is a novel circuit for concurrently detecting delay faults and stuck-open faults. In the proposed DFT techniques, in particular, fault detection in CMOS logic family is investigated.

The second half of this study attempts to derive test sequences for sequential circuits. First, initialization phase is studied. Initialization is the process of driving the state signals in the circuit to known states. This dissertation presents an initialization technique for non-initializable asynchronous sequential circuits.

Finally, we proceed by generating test sequences for asynchronous sequential circuits. We assume the presence of all multiple faults of all multiplicities. No faulty machines are generated during these procedures and we do not resort to their explicit enumeration.

#### Acknowledgements

I would like to express my thanks and gratitude to my supervisor, Professor M. Ahmadi. This work would not have been possible without his continuous support and encouragement.

I am thankful to the members of my defense committee, Professors Michael Miller, William C. Miller, Reza Lashkari, and J. J. Soltis for their valuable comments. I am grateful to Prof. Graham. A. Jullien for his constructive questions and comments. I would also like to thank all my colleagues and friends for their support and useful discussions, in particular, S. Hessabi, M. Shams, and S. Sadeghi-Emamchaie for their valuable consultations, and Phil Regier for his kind assisstance.

Finally, and most of all, I am thankful to my wife for her constant provision of love, friendship, and moral support from which I drew the strength to persevere with this project.

### **Dedications**

To Saeedeh, my wife, and Keyan, my son, who – more than I – endured the hardships of this work.

### Contents

| 1 | Intr | oduction                                     | 1  |

|---|------|----------------------------------------------|----|

|   | 1.1  | Testing Asynchronous Circuits                | 5  |

| 2 | Des  | ign Overview                                 | 9  |

|   | 2.1  | Levels of Abstraction                        | 9  |

|   | 2.2  | PUPD BiCMOS Logic Gates                      | 12 |

|   | 2.3  | Categories of Digital Circuits               | 14 |

|   | 2.4  | Asynchronous Design                          | 20 |

|   |      | 2.4.1 Basic Asynchronous Element: An Example | 22 |

|   |      | 2.4.2 Micropipelines                         | 24 |

|   | 2.5  | Chronology                                   | 27 |

| 3 | Test | ting Overview                                | 33 |

|   | 3.1  | Defects and Faults                           | 34 |

|   |      | 3.1.1 Types of Testing                       | 36 |

|   | 3.2  | Fault Modeling                               | 36 |

|   |     | 3.2.1   | Types of Faults                                 | 36 |

|---|-----|---------|-------------------------------------------------|----|

|   |     | 3.2.2   | Levels of Faults                                | 39 |

|   |     | 3.2.3   | Fault Models                                    | 40 |

|   | 3.3 | Test (  | Generation Algorithm                            | 46 |

|   |     | 3.3.1   | Fault Simulation                                | 47 |

|   |     | 3.3.2   | $\mathcal{NP}$ -Completeness                    | 49 |

|   |     | 3.3.3   | Initialization                                  | 54 |

|   |     | 3.3.4   | Testing Classical Asynchronous Circuits         | 56 |

|   |     | 3.3.5   | Self-Checking circuits                          | 56 |

|   |     | 3.3.6   | Testing Quasi-Delay-Insensitive (QDI) circuits  | 57 |

|   | 3.4 | Desigr  | n-for-Testability                               | 59 |

|   |     | 3.4.1   | Design-for-Testability of CMOS/BiCMOS Circuits  | 62 |

|   |     | 3.4.2   | Design-For-Testability of Asynchronous Circuits | 73 |

| 4 |     | q Fault | ts in Asynchronous Circuits                     | 83 |

|   | 4.1 | Typica  | al Examples                                     | 85 |

|   | 4.2 | Fault   | Characterization                                | 86 |

|   |     | 4.2.1   | Defect Modeling                                 | 86 |

|   |     | 4.2.2   | Conventional BiCMOS NAND Gate                   | 87 |

|   |     | 4.2.3   | BiNMOS NAND Gate                                | 90 |

|   |     | 4.2.4   | Full-Swing BiCMOS NAND Gate                     | 91 |

|   |     | 4.2.5   | CMOS NAND Gate                                  | 91 |

|   |     |         |                                                 |    |

|   |      | 4.2.6 Analysis of Results                                       |

|---|------|-----------------------------------------------------------------|

|   |      | 4.2.7 General Fault Characterization: A proof                   |

|   | 4.3  | DFT Technique                                                   |

|   | 4.4  | Medium Size Logic Circuits                                      |

|   | 4.5  | Conclusions                                                     |

| 5 | Del  | ay Faults in Asynchronous Circuits 118                          |

|   | 5.1  | Delay Faults in BiCMOS Circuits                                 |

|   | 5.2  | Proposed DFT Technique for Delay Fault Detection                |

|   | 5.3  | Detecting Stuck-Open Faults                                     |

|   |      | 5.3.1 Proposed DFT Technique for Stuck-open Fault Detection 129 |

|   | 5.4  | Fully Testable CMOS Designs                                     |

|   | 5.5  | <b>Evaluation</b>                                               |

|   |      | 5.5.1 Delay Fault Testing                                       |

|   |      | 5.5.2 Stuck-Open Faults                                         |

|   | 5.6  | Generation of $\Phi_1$                                          |

|   | 5.7  | Faults on $\Phi_1$ and $\Phi_2$                                 |

|   | 5.8  | Medium Size Logic Circuits                                      |

|   | 5.9  | <b>Conclusions</b>                                              |

| 6 | Init | ialization 151                                                  |

|   | 6.1  | Introduction                                                    |

|   | 6.2 | Background                                 | 155 |

|---|-----|--------------------------------------------|-----|

|   | 6.3 | The Proposed Initialization Technique      | 157 |

|   | 6.4 | An Example                                 | 160 |

|   | 6.5 | Advantages                                 | 163 |

|   | 6.6 | Medium Size Circuits                       | 164 |

|   | 6.7 | Conclusion                                 | 165 |

| 7 | Asy | nchronous Sequential Circuit Testing       | 166 |

|   | 7.1 | Introduction                               | 166 |

|   | 7.2 | Definitions                                | 169 |

|   |     | 7.2.1 Components                           | 170 |

|   |     | 7.2.2 Red & Green Edges                    | 170 |

|   | 7.3 | Assumptions                                | 172 |

|   | 7.4 | Redundancy                                 | 175 |

|   | 7.5 | Network Model                              | 178 |

|   |     | 7.5.1 Minimal Feedback Set                 | 178 |

|   | 7.6 | The Behavioral Model for Testability (BMT) | 182 |

|   |     | 7.6.1 An Example                           | 183 |

|   | 7.7 | The BMT Correct Behaviors                  | 188 |

|   |     | 7.7.1 Selection Rules                      | 188 |

|   | 7.8 | Redundancy                                 | 189 |

|   |     | 7.8.1 State-Holding Component              | 193 |

|   | 7.9                                                                                                   | Linking Test Sequences Together                       | 193                                          |

|---|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------|

|   | 7.10                                                                                                  | Computational Cost                                    | 196                                          |

|   | 7.11                                                                                                  | Rationale                                             | 197                                          |

|   | 7.12                                                                                                  | Important Results                                     | 201                                          |

|   | 7.13                                                                                                  | Benchmark Circuits                                    | 204                                          |

|   | 7.14                                                                                                  | Summary                                               | 207                                          |

| 8 | Sun                                                                                                   | amary and Future Work                                 | 209                                          |

|   | 8.1                                                                                                   | Summary                                               | 209                                          |

|   | 8.2                                                                                                   | Future Directions                                     | 212                                          |

| A | HSI                                                                                                   | PICE Device Model Parameters                          | 215                                          |

|   |                                                                                                       |                                                       |                                              |

| в | АТ                                                                                                    | ypical HSPICE Simulation                              | 219                                          |

| B |                                                                                                       | ypical HSPICE Simulation       2         HSPICE files |                                              |

| B | B.1                                                                                                   | HSPICE files                                          |                                              |

|   | В.1<br><b>Еха</b>                                                                                     | HSPICE files                                          | 220<br>227                                   |

|   | B.1<br><b>Exa</b><br>C.1                                                                              | HSPICE files                                          | 220<br>227<br>227                            |

|   | <ul><li>B.1</li><li>Exa</li><li>C.1</li><li>C.2</li></ul>                                             | HSPICE files                                          | 220<br>227<br>227<br>227                     |

|   | <ul> <li>B.1</li> <li>Exa</li> <li>C.1</li> <li>C.2</li> <li>C.3</li> </ul>                           | HSPICE files                                          | 220<br>227<br>227<br>227                     |

|   | <ul> <li>B.1</li> <li>Exa</li> <li>C.1</li> <li>C.2</li> <li>C.3</li> <li>C.4</li> </ul>              | HSPICE files                                          | 2220<br>2227<br>2227<br>2227<br>231<br>234   |

|   | <ul> <li>B.1</li> <li>Exa</li> <li>C.1</li> <li>C.2</li> <li>C.3</li> <li>C.4</li> <li>C.5</li> </ul> | HSPICE files                                          | 2220<br>2227<br>2227<br>2231<br>2334<br>2339 |

#### Bibliography

245

## List of Tables

| 3.1 | Causes of observed errors                                             | 35           |

|-----|-----------------------------------------------------------------------|--------------|

| 3.2 | Types of testing                                                      | 37           |

| 3.3 | Fault characterization of the conventional BiCMOS NAND gate $\ . \ .$ | 45           |

| 4.1 | Fault characterization of the conventional BiCMOS NAND gate           | 90           |

| 4.2 | Fault characterization of the BiNMOS NAND gate                        | 91           |

| 4.3 | Fault characterization of the full-swing BiCMOS NAND gate $\ldots$ .  | 92           |

| 4.4 | Fault characterization of the CMOS NAND gate                          | 92           |

| 4.5 | Fault distribution for BiCMOS/CMOS NAND gates                         | 93           |

| 4.6 | Fault detection comparison for 4 structures                           | 111          |

| 4.7 | Fault detection comparison for four MSI structures                    | 116          |

| 5.1 | CMOS functional behaviors                                             | 132          |

| 5.2 | CMOS functional behaviors                                             | 1 <b>3</b> 5 |

| 5.3 | Effects of the DFT technique for delay/stuck-open fault detection on  |              |

|     | the circuit parameters                                                | 143          |

| 5.4 | Fault detection comparison for four MSI structures                    | 147          |

| 5.5 | Fault detection comparison for four MSI structures                                    | 148 |

|-----|---------------------------------------------------------------------------------------|-----|

| 6.1 | Initializability Results                                                              | 164 |

| C.1 | Single stuck-at faults in the majority C-element and their test sequences. $\ldots$ . | 228 |

| C.2 | Single stuck-at faults in the Wuu's C-element and their test sequences.               | 230 |

| C.3 | Single stuck-at faults in the Mayevsky's C-element and their test sequences           | 233 |

| C.4 | Single stuck-at faults in the Bartkey's C-element and their test sequences            | 238 |

# List of Figures

| 2.1  | General structure of a complex BiCMOS logic gate            | 13 |

|------|-------------------------------------------------------------|----|

| 2.2  | Conventional BiCMOS NAND gate                               | 13 |

| 2.3  | Digital circuits                                            | 14 |

| 2.4  | Typical synchronous sequential circuit structure            | 15 |

| 2.5  | Typical classical asynchronous sequential circuit structure | 16 |

| 2.6  | Handshaking Protocols                                       | 18 |

| 2.7  | Data transfer in handshaking protocols                      | 19 |

| 2.8  | Representations of JOIN                                     | 23 |

| 2.9  | Specification of the C-element                              | 23 |

| 2.10 | Control and computational parts in Micropipeline structure  | 25 |

| 3.1  | Open defect in a CMOS NOR gate                              | 40 |

| 3.2  | Line stuck-at faults                                        | 41 |

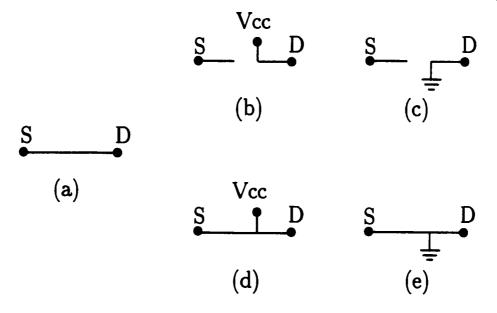

| 3.3  | Transistor stuck-at faults                                  | 43 |

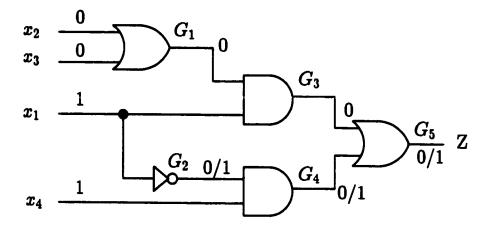

| 3.4  | A sample gate-level representation                          | 48 |

| 3.5  | Partitioning                                                | 60 |

| 3.6  | Built-in Current Testing Circuit                                | 63  |

|------|-----------------------------------------------------------------|-----|

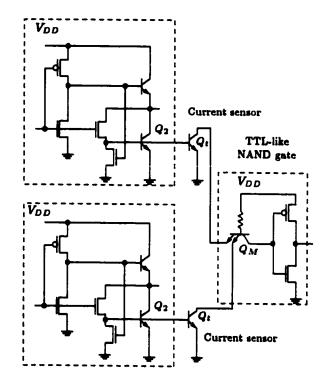

| 3.7  | IDDQ testable CMOS gates proposed in literature                 | 64  |

| 3.8  | Built-in Current Testing Circuit                                | 66  |

| 3.9  | Two-pattern test                                                | 67  |

| 3.10 | Delay test invalidation by dynamic hazard                       | 68  |

| 3.11 | DFT technique proposed in [64]                                  | 68  |

| 3.12 | Delay testing circuit presented in [58]                         | 69  |

| 3.13 | Testable CMOS gates proposed in literature                      | 70  |

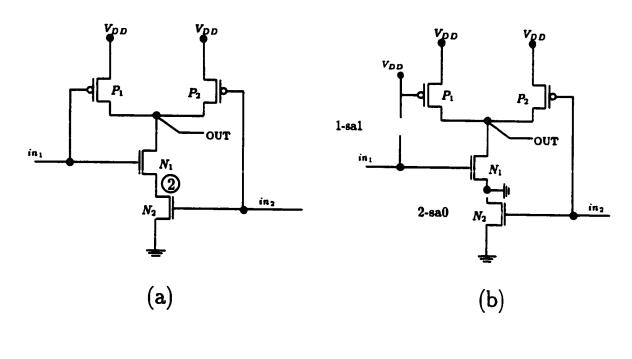

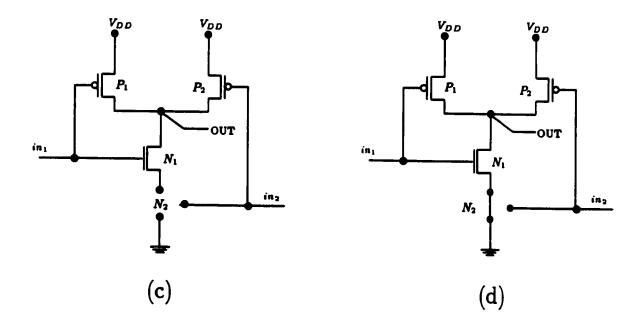

| 3.14 | Modified circuit for detecting stuck-open faults                | 72  |

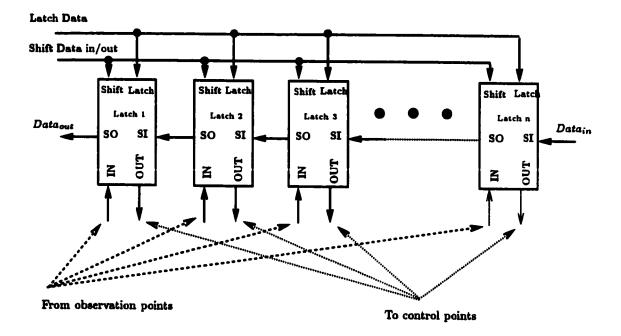

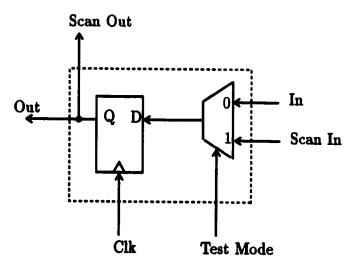

| 3.15 | General scan-path technique                                     | 75  |

| 3.16 | Scan-path technique using circuit latches                       | 75  |

| 3.17 | Polarity-hold shift register latch                              | 77  |

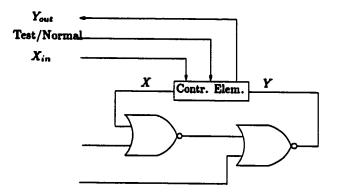

| 3.18 | Scan-path testing technique for micropipelines                  | 80  |

| 4.1  | Conventional BiCMOS NAND gate                                   | 86  |

| 4.2  | BiNMOS NAND gate                                                | 86  |

| 4.3  | Full-swing BiCMOS NAND gate                                     | 86  |

| 4.4  | CMOS NAND gate                                                  | 86  |

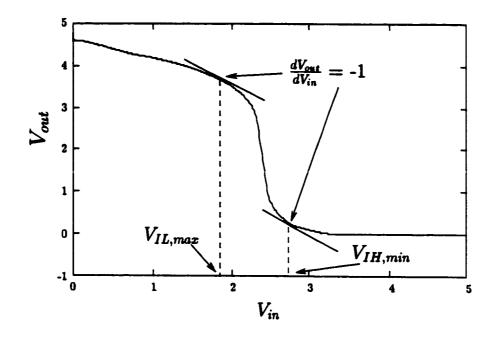

| 4.5  | DC transfer function of BiCMOS NAND gate                        | 88  |

| 4.6  | Different paths in inverter circuit                             | 95  |

| 4.7  | Introducing virtual GND for detecting shorts                    | 105 |

| 4.8  | Conventional BiCMOS NAND gate, modified for detecting bridgings | 106 |

| 4.9        | Detection of an $I_{DDQ}$ fault in the modified BiCMOS NAND 107                |

|------------|--------------------------------------------------------------------------------|

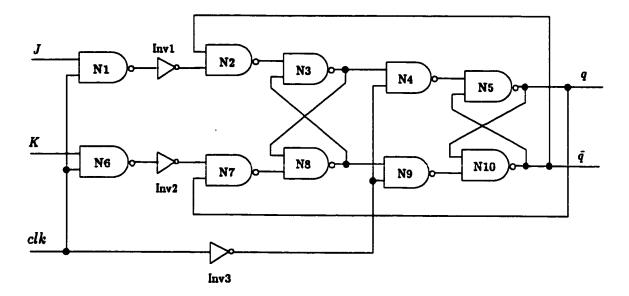

| 4.10       | JK flip-flop                                                                   |

| 5.1        | Different appearances of delay fault                                           |

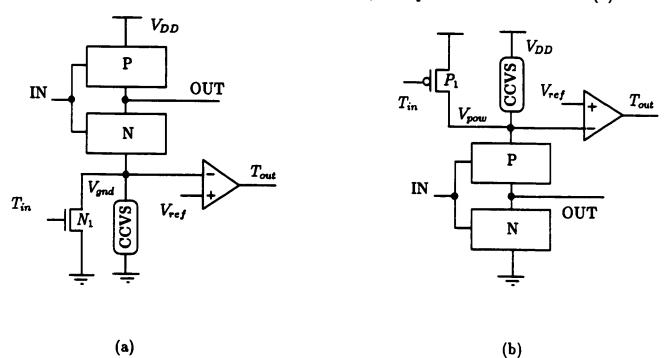

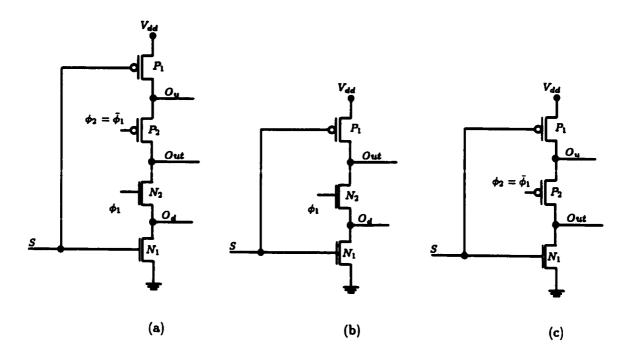

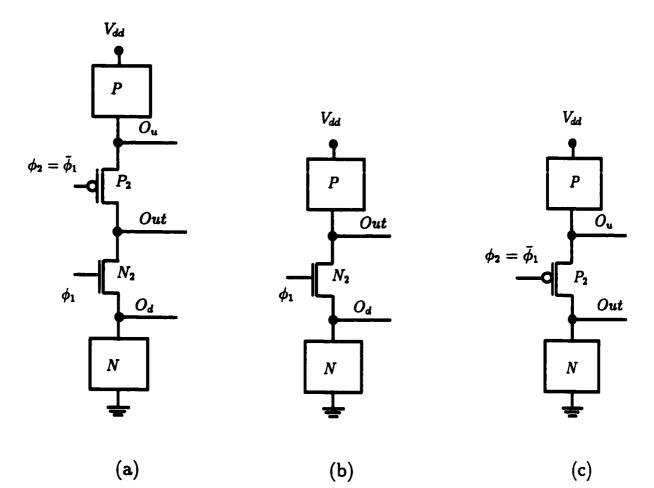

| 5.2        | Proposed concurrent checkers for delay faults                                  |

| 5.3        | Concurrent checkers for delay faults                                           |

| 5.4        | Proposed concurrent stuck-open detector                                        |

| 5.5        | Proposed fully testable CMOS design                                            |

| 5.6        | Alternative solutions for current sensor                                       |

| 5.7        | Delay fault detection using the concurrent checker                             |

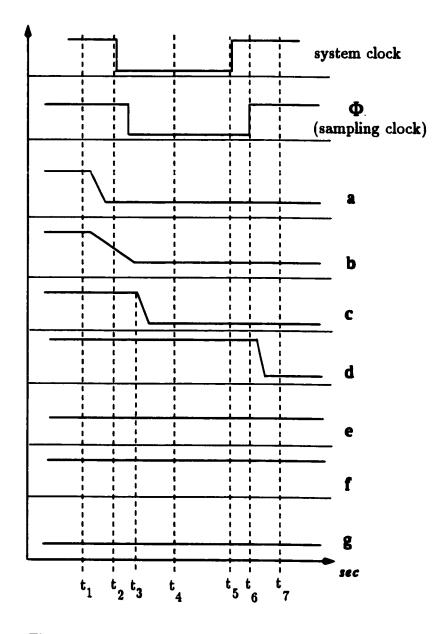

| 5.8        | Detecting delay fault (type "c") using the concurrent checker 138              |

| 5.9        | Stuck-open fault detection using the proposed BIST technique 140               |

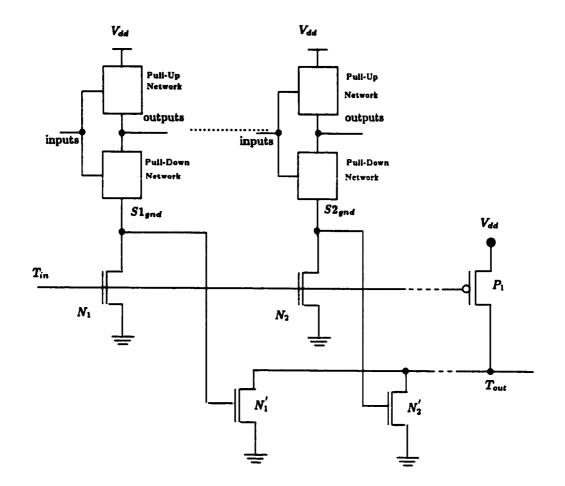

| 5.10       | Controlling signals in Asynchronous circuits                                   |

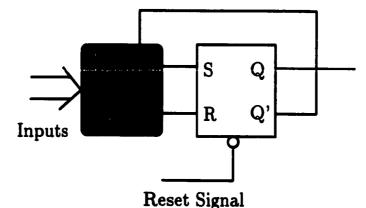

| 6.1        | Typical reset techniques: (a) Externally, (b) Internally 152                   |

| <b>6.2</b> | An example where reset signal may fail                                         |

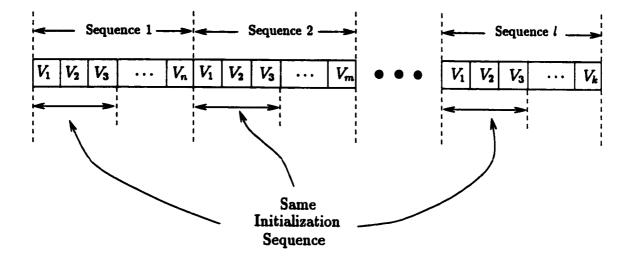

| 6.3        | A typical test vector set                                                      |

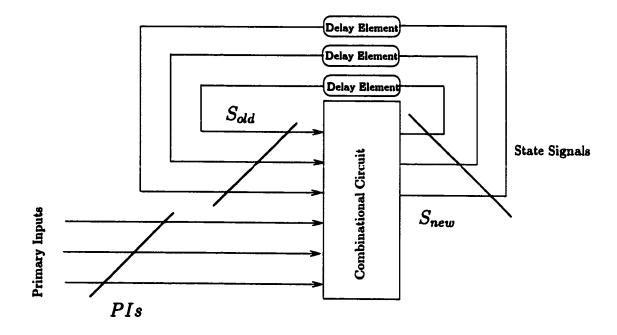

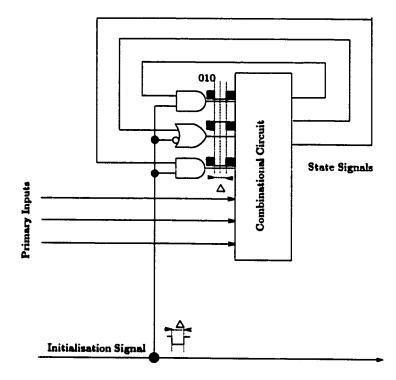

| 6.4        | Typical classical asynchronous sequential circuit structure 156                |

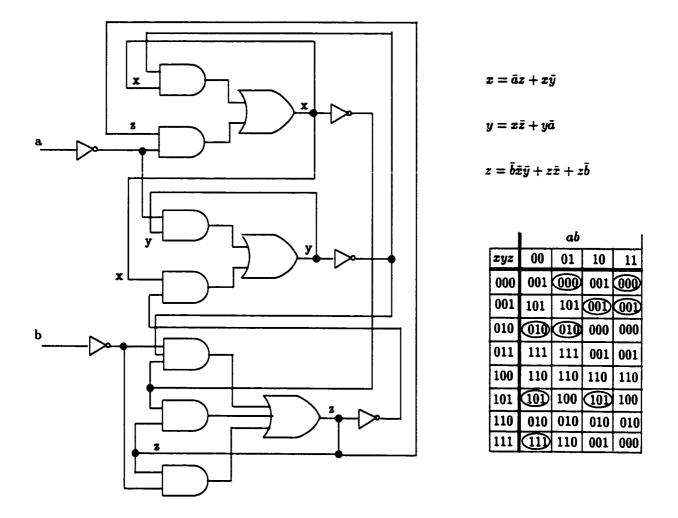

| 6.5        | Original logic circuit along with its flow table and its Boolean functions.157 |

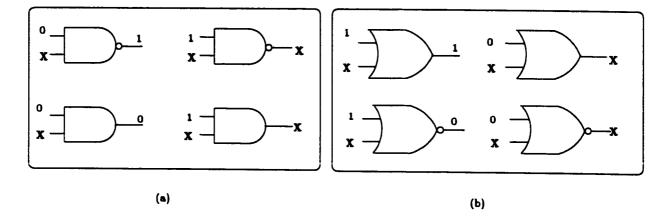

| 6.6        | Initializing a node to one or zero using a) AND/NAND, or b) OR/NOR.159         |

| 6.7        | DFT: The proposed initialization technique                                     |

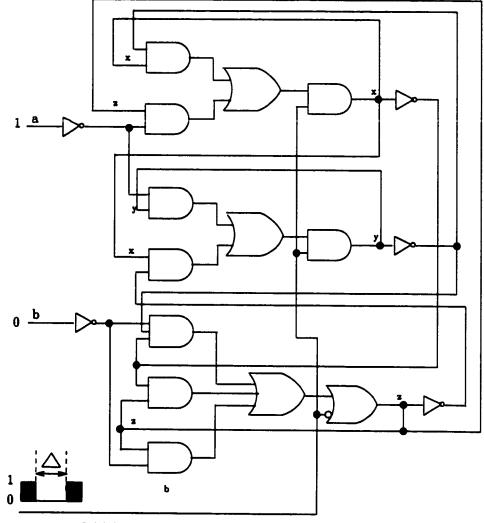

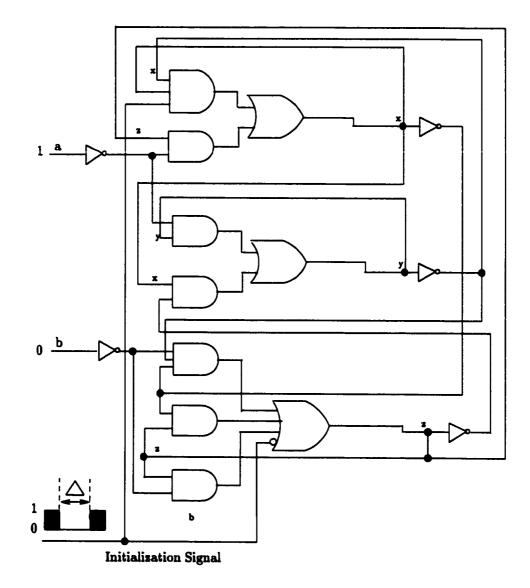

| 6.8        | The initializable logic circuit                                                |

| 6.9  | The initializable logic circuit with reduced area overhead                 | 162  |

|------|----------------------------------------------------------------------------|------|

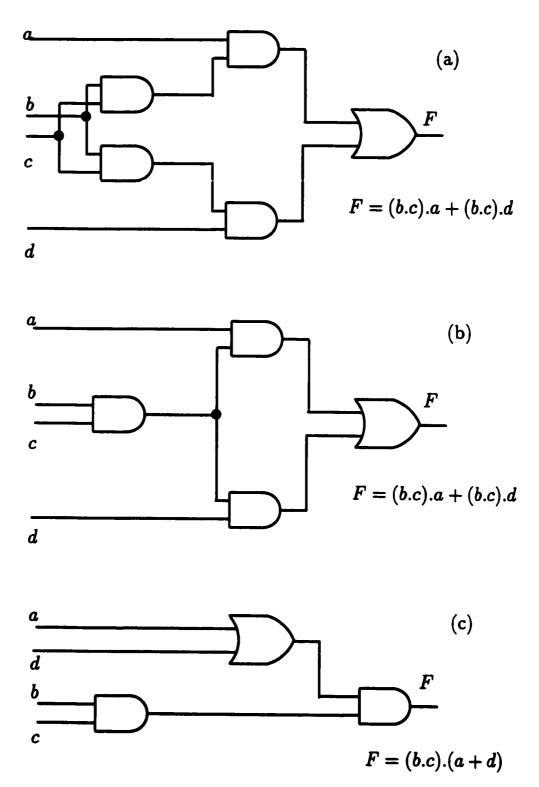

| 7.1  | Two identical circuits, (a) The fault-free circuit, (b) The faulty circuit | .168 |

| 7.2  | Demonstration of Red (Solid) and Green (Dashed) edges                      | 171  |

| 7.3  | Redundant circuit.                                                         | 175  |

| 7.4  | An irredundant circuit is not necessarily minimized in terms of the        |      |

|      | the number of gates or wires                                               | 177  |

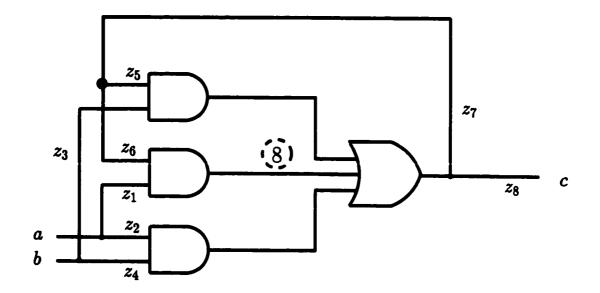

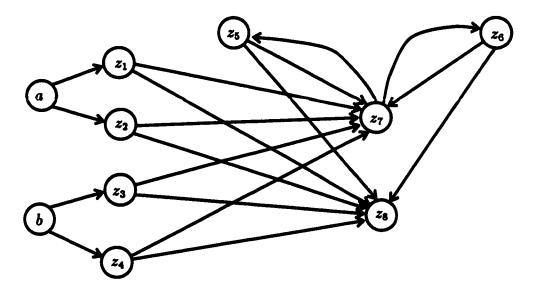

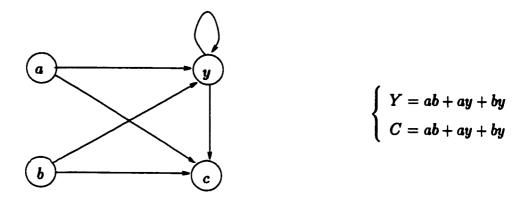

| 7.5  | The majority C-element: the gate-circuit with associated state vari-       |      |

|      | ables                                                                      | 179  |

| 7.6  | Circuit graph used to obtain feedback variable set. Edges are not          |      |

|      | named to simplify the figure                                               | 180  |

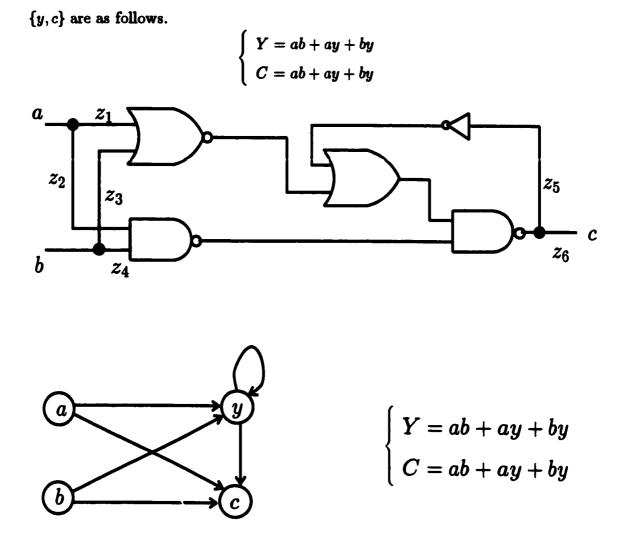

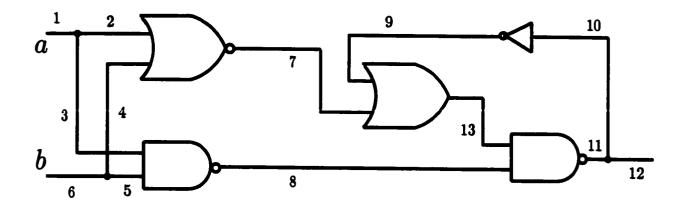

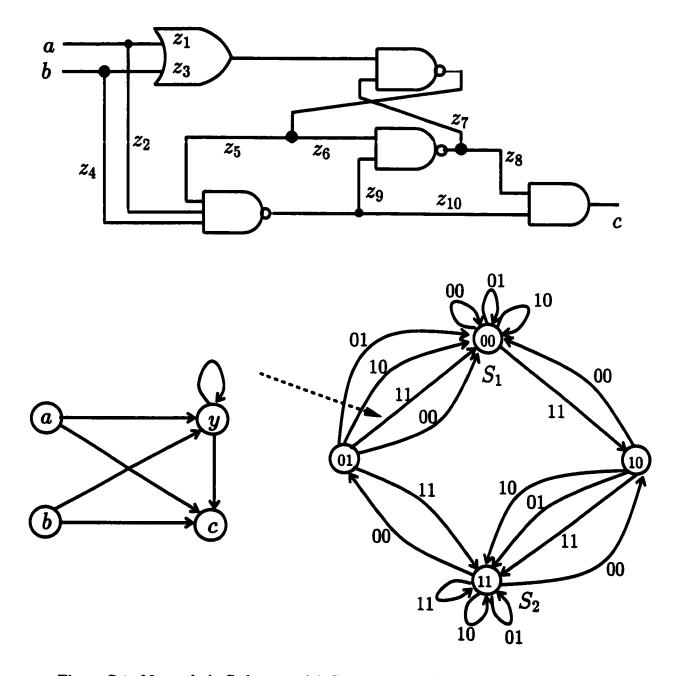

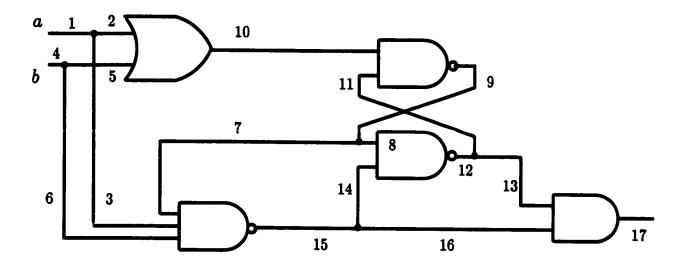

| 7.7  | Network model using $\{y, c\}$                                             | 181  |

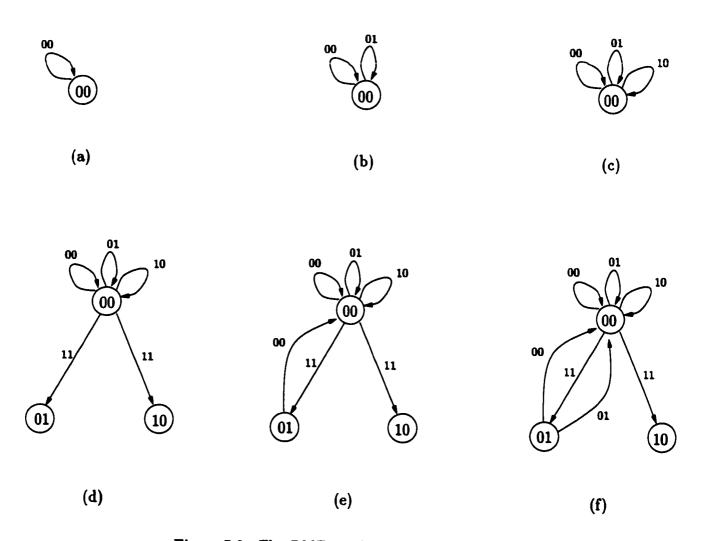

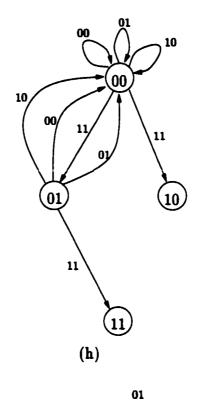

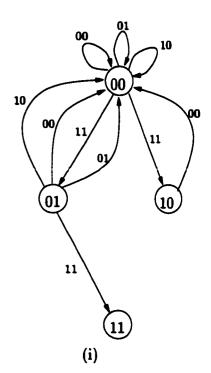

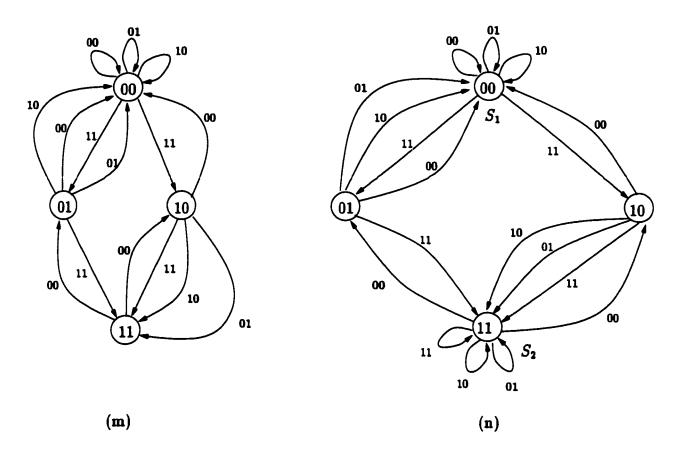

| 7.8  | The BMT graph: steps (a) through (f). $\ldots$ $\ldots$ $\ldots$           | 185  |

| 7.9  | The BMT graph: steps (g) through (l). $\ldots$ $\ldots$ $\ldots$           | 186  |

| 7.10 | The BMT graph: steps $(m)$ and $(n)$                                       | 187  |

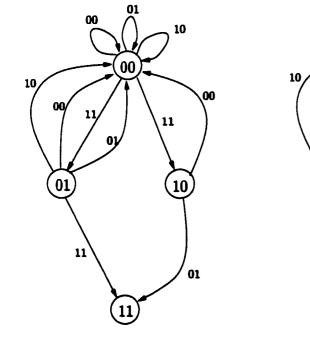

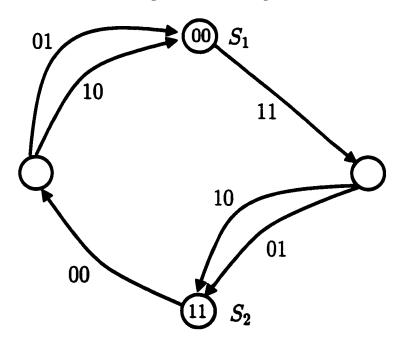

| 7.11 | The BMT graph after removing incorrect and redundant transitions.          | 190  |

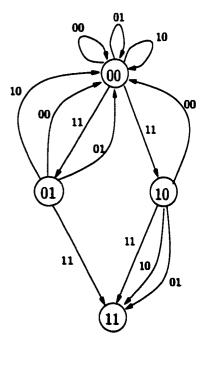

| 7.12 | The BMT graph for the majority C-element at the presence of 8-sa0.         | 192  |

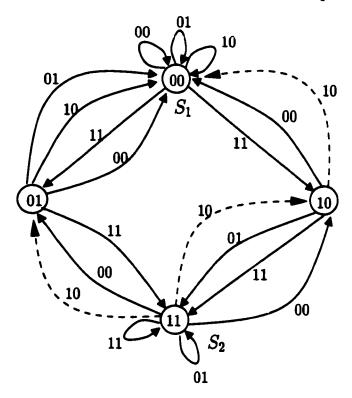

| 7.13 | The component C-element realized using (a) no feedback, (b) compo-         |      |

|      | nent $F$ and feedback variable $y$ connected to the primary output, (c)    |      |

|      | component $F'$ and an internal node of component $F$                       | 202  |

| 7.14 | Different realizations of Khoche C-element.                                | 205  |

| C.1  | The stuck-at fault locations in majority C-element                         | 228  |

| C.2  | Wuu's C-element: (a) Logic circuit, (b) Circuit graph, (c) Network         |     |

|------|----------------------------------------------------------------------------|-----|

|      | model                                                                      | 229 |

| C.3  | Fault locations in Wuu's C-element.                                        | 230 |

| C.4  | Mayevsky's C-element: (a) Gate circuit, (b) Circuit graph, (c) Net-        |     |

|      | work model                                                                 | 232 |

| C.5  | Fault locations in Mayevsky's C-element.                                   | 233 |

| C.6  | Bartkey's C-element (a) The gate circuit, (b) The circuit graph            | 235 |

| C.7  | Bartkey's C-element with $z_4$ , $z_9$ as feedback variables, and c as the |     |

|      | primary output variable                                                    | 236 |

| C.8  | The BMT graph for Bartkey's C-element                                      | 237 |

| C.9  | Fault locations in Bartkey's C-element.                                    | 238 |

| C.10 | (a) NOR-latch logic circuit, (b) The network model, (c) The BMT            |     |

|      | graph, (d) The reduced BMT graph.                                          | 240 |

| C.11 | (a) The logic circuit, (b) The network model, (c) BMT graph                | 242 |

| C.12 | Partial D Flip-flop, (a) The gate circuit, (b) The circuit graph, (c)      |     |

|      | The gate circuit with broken feedback lines                                | 244 |

# Glossary

| ALU    | Arithmetic Logic Unit                |

|--------|--------------------------------------|

| ATGP   | Automatic Test Generation Program    |

| ATPG   | Automatic Test Pattern Generation    |

| BIST   | Built-In Self-Test                   |

| BMT    | Behavioral Model for Testability     |

| BiCMOS | Bipolar CMOS                         |

| CCF    | Combinational Circuit with Forks     |

| CCVS   | Current-Controlled Voltage-Source    |

| CLR    | Clear                                |

| CMOS   | Complementary MOS                    |

| CSCD   | Current Sensing Completion Detection |

| CSP    | Communicating Sequential Processes   |

| CTS    | Complete Test Set (Sequence)         |

| CUT    | Circuit Under Test                   |

| DCC    | Digital Compact Cassette             |

| DFT    | Design-For-Testability               |

| DI     | Delay Insensitive                    |

| FF     | Flip-Flop                            |

| FFCC   | Fork-Free Combinational Circuit      |

| FIFO   | First-In First-Out                   |

|        |                                      |

| FSM  | Finite State Machine                |

|------|-------------------------------------|

| GND  | Ground                              |

| IC   | Integrated Circuit                  |

| KCL  | Kirchoff Voltage Law                |

| KVL  | Kirchoff Current Law                |

| MUX  | Multiplexer                         |

| NP   | Non-linear Programming              |

| PCB  | Printed Circuit Board               |

| PR   | Preset                              |

| PUPD | Pull-Up Pull-Down                   |

| QDI  | Quasi Delay Insensitive             |

| ROM  | Read Only Memory                    |

| SI   | Speed Independent                   |

| STG  | Signal Transition Graph             |

| TTL  | Transistor-Transistol Logic         |

| UIN  | Up-bounded Inertial Delay           |

| UUT  | Unit Under Test                     |

| VLSI | Very-Large Scale Integrated circuit |

### Chapter 1

### Introduction

The VLSI community has witnessed a renewed and growing interest in asynchronous circuit design and testing during the last decade. Asynchronous circuits are attracting increasing interest for future generations of high-speed low-power logic circuits because they facilitate concurrent computation, offer average-case performance and better technology migration potential, and eliminate clock skew<sup>1</sup>.

The potential advantages of asynchronous circuits over their synchronous counterparts are:

1. The power dissipation and the area associated with clock routing has disappeared due to the absence of a global clock in asynchronous circuits. The ac power dissipation on latches is reduced since only those parts of the circuit

<sup>&</sup>lt;sup>1</sup>The variation in the effective arrival time of the clock at different clocked storage elements is called clock skew [165]. These variations may be due to a combination of several effects: different threshold voltages, signal propagation delays on wires, or variation in element delays such as is found when gated clock signals are used to control register loading.

that are actually performing useful work will be active: Internal node capacitors of other latches would not charge or discharge for each controlling signal transition.

- 2. Clock skew is eliminated since there is no global clock.

- 3. Some asynchronous systems have higher modularity. Since there are no global timing requirements, functional blocks may be replaced individually without circuit modification provided that the correct operation of the entire circuit does not depend on the combinations of delays in the new block.

- 4. Designing asynchronous circuits improves average speed performance, since many asynchronous circuits sense when a computation is ended. Therefore, the speed of the entire circuit no longer needs be bounded to the slowest block or the rate of a global signal. In contrast to asynchronous systems, synchronous circuits must wait until all possible computations have been completed before latching the results; this yields in worst-case performance.

- 5. Most asynchronous circuits promise better handling of metastability: a state of unstable equilibrium in which a circuit can remain for an unbounded amount of time. An example of a component where metastability may occur is an arbiter. In a synchronous system a metastable state may last longer than one clock cycle. In this case, incorrect data is sampled and transferred to the next stage, which in turn, might lead to an incorrect output. However, most asynchronous circuits can wait an arbitrarily long time until the circuit element leaves the metastable state.

In spite of their numerous attractive features and the significant work that has been carried out, asynchronous circuits have not been widely used in practice due to the lack of an adequate theory of asynchronous circuits in the past, and the problems with hazards and races. Asynchronous circuits suffer in terms of required area for the following two reasons. First, while hazards are not of concern in synchronous sequential circuits where clock signals exist, any momentary erroneous signal may be troublesome in asynchronous sequential circuits. In order to design hazard-free sequential circuits, we end up using additional gates. Second, there is overhead produced by the handshake circuits which are designed to compensate for the elimination of the global clock signal. The relatively larger components and the handshake circuits both contribute to the overhead, which, in turn, increases density and power consumption. Another disadvantage is that a good portion of the system's time might be spent on producing the handshaking and control signals. As a result, the average speed of an asynchronous circuit designed with previously known methods may be low compared to that of a clocked circuit with a similar function.

Despite the problems listed above, it is unlikely the renewed interest in asynchronous techniques will diminish. It is also unlikely that industry will switch entirely to asynchronous circuit design. It is more likely that asynchronous and synchronous approaches will be developed in areas where they are really advantageous. Asynchronous design is an important research area for the following reasons:

- 1. When a few synchronous circuits with different clock signals are connected to each other through interface circuits, there will always be a need for asynchronous circuits to synchronize among the clocks. An example of this situation is the handshaking procedure of the IEEE-488 bus.

- 2. The advantages gained by designing asynchronous circuits are encouraging even if they are comparable with synchronous circuits in terms of area and

speed. Modularity, elimination of clock skew, and handling metastability are not easy to achieve in synchronous design. For this reason, the attitude is changing now. Designing asynchronous circuits to optimize power dissipation, area, and speed has received considerable attention in the past several years and new design methodologies have been developed specifically for asynchronous circuits [79, 103, 117, 137].

3. A clock is an input signal with periodical transitions. From this point of view any synchronous circuit operates asynchronously. Any design or testing methodology for asynchronous circuits should also be applicable to synchronous circuits by applying a constraint on one of the inputs, i.e., 0-to-1 transitions are equally spaced in time, so are 1-to-0 transitions. Note that the opposite concept is not necessarily true.

Some publications [151,188] have pointed out the possibility of eliminating extra hardware due to handshaking signals. Synchronous circuits use a logic structure which allows hazards and races to occur prior to a transition on the clock line. This same logic structure can be used along with an asynchronous clock signal: i.e., the asynchronous clock signals should also allow hazards and races before a change on the clock line. One such logic structure is micropipelines. In general, there have been many attempts to design asynchronous circuits which have better performance in terms of area and speed than their counterparts [43, 108]. The results obtained through ongoing research are encouraging [69, 70, 175].

#### **1.1 Testing Asynchronous Circuits**

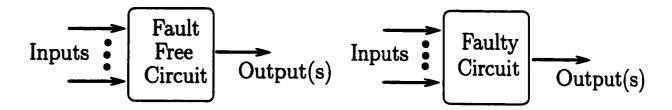

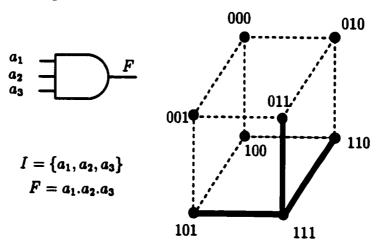

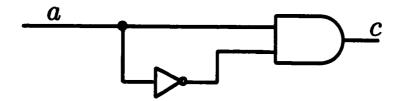

Fabrication errors, fabrication defects, and physical failures may cause abnormal behavior (or simply malfunction) of IC elements. Such abnormalities are called *physical faults*. Therefore, it is not sufficient just to design and to manufacture integrated circuits, and to fabricate millions of devices using advanced integration circuit technology; semiconductor manufacturers and users must also verify that the circuits work as intended. *Testing* of a system is an experiment in which the system is exercised and its resulting response is analyzed to ascertain whether it behaved correctly [2]. The generation of test vectors for a logic circuit is an  $N\mathcal{P}$ -complete problem [66, 88, 93].

A great amount of research has been done to reduce the complexity, the hardware expense, and the execution time of testing synchronous circuits [43,69,70,79, 103,108,117,137,151,175,188]. The testing of combinational circuits has been studied in depth over many years. Testing synchronous sequential circuits is much more difficult, because long test sequences may be needed to excite a given fault and to make it observable. This problem is usually solved in synchronous circuits by using scan design methods [2] which reduce any circuit to a collection of combinational circuits and latches, thus simplifying testing.

Testing techniques for synchronous circuits have failed to be extended to testing asynchronous circuits for the following reasons:

1. The absence of a clock reduces controllability, and testing techniques are often more complex. For example, scan techniques are not easily applicable because one should order scanned logical values to read or to write *serially*. This needs a time constraint on reading from observation points or writing to controlling points. Adding extra input/output test points is sometimes suggested to ease the controllability and observability of variables inside asynchronous circuits.

- 2. Although asynchronous circuits must be designed hazard- and race-free, faults may cause oscillations within the circuit, or may change a hazard- and racefree circuit to a hazardous one. These faults are difficult to detect. Therefore, any testing technique should handle hazards and races if they occur.

- 3. Also, compared to test generation for synchronous circuits, test generation for asynchronous circuits is harder since they tend to have more state holding elements than synchronous circuits.

Therefore, there is a need for a suitable testing method that can address the peculiarities of the asynchronous circuits.

In this dissertation we aim at high *defect coverage* by proposing several designfor-testability (DFT) techniques for digital BiCMOS/CMOS integrated circuits and providing test generation algorithms for asynchronous circuits.

One contribution of this dissertation is a DFT technique for detecting short defects in pull-up/pull-down BiCMOS/CMOS design. We propose an on-line  $I_{DDQ}$ -testable design, which uses the concept of virtual ground, and inspects for any undesired connection between the GND and  $V_{DD}$  nodes. The occurrence of a fault is announced if an unwanted path exists between these two nodes.

The second contribution of this dissertation is a novel circuit for detecting delay faults. The operation of the delay fault checkers is based on observing the time delay between transitions instead of the normally practiced observation of the outputs *at* a specific sampling time. We provide a fully testable CMOS design technique. We also propose concurrent delay fault checkers for asynchronous circuits by deploying synchronous DFT technique.

#### CHAPTER 1. INTRODUCTION

The importance of concurrent fault detection is that an asynchronous circuit which has passed the initial tests is prone to some defects which may occur during the normal operation of the circuit. This scheme eliminates the requirement of test-pattern generation, and the circuit can be tested concurrently with the normal operation.

The third contribution of this dissertation is initialization of asynchronous circuits. We provide a new initialization technique which has little overhead and can often be simplified. This technique does not change the complexity and hazard characteristics of the circuit since we do not re-design it.

The fourth contribution of this dissertation is the generation of test sequences for the detection of single & multiple stuck-at faults in asynchronous circuits. We provide a graphic representation of transitions, which occur in this type of circuit depending on the delays of wires and gates. We derive pieces of complete test sequences. We then link these pieces of test sequences to obtain the complete test sequence. We are never concerned with the actual location of the fault(s) in this process.

The organization of this dissertation is as follows. Chapter 2 contains a summary of design terminologies, explains pull-up/pull-down BiCMOS design, and provides the literature review of existing asynchronous designs. Chapter 3 is concerned with the testing terminology and the fault models used in this dissertation, reviews some related DFT techniques, and provides the literature review of testing techniques for asynchronous circuits. In Chapter 4 the proposed DFT method for detecting short and bridging faults in asynchronous CMOS/BiCMOS circuits is described. Fully testable CMOS design and methods for detecting delay faults in asynchronous circuits are presented in Chapter 5. The related DFT method for initialization of asynchronous sequential circuits is dealt with in Chapter 6. A test generation algorithm for asynchronous sequential circuits is discussed in Chapter 7. The summary of the research, conclusions, and the future directions for the problem of designing a fully testable asynchronous circuit are pointed out in Chapter 8.

### Chapter 2

### **Design Overview**

The organization of this Chapter is as follows. We present the different levels of abstraction in Section 1. PUPD (pull up/pull down) BiCMOS design, which is used throughout this dissertation, is explained in Section 2. Different structures for asynchronous circuits are explained in Section 3. An appropriate formalism for circuit design and a set of primitive modules are discussed in Section 4. Finally, a brief chronology of design methodologies is given in Section 5.

#### 2.1 Levels of Abstraction

The design representation of digital circuits is separated into behavioral, structural, and physical domains [126]. Behavior refers to the functionality of a system or how its components interact with their environment, i.e., the mapping from inputs to outputs. Structure refers to the set of interconnected abstract components that make up the system. Structure is typically described by a netlist. Both behavioral and structural models are realized independently of the implementation technology. Ultimately, the structure must be mapped into a *physical* design, and each abstract component must be replaced with real components depending on the fabrication technology used.

Behavior, structure, and physical design are usually distinguished as the three domains in which hardware can be described. Within each domain is a set of abstraction levels, which are concerned with specified aspects of the system. Note that the level of detail increases from the system level to the circuit level. Items of specific interest within each level of abstraction are:

- System level: The general specification level is often represented by a document written in a natural language. The behavior of a system is described by a set of performance specifications, which define the required operational characteristics for the system. The corresponding structural description contains the components which are required to realize the system: for example, processors, memories, controllers, buses, and switches. In the physical domain, the physical partitions of the system are defined; for example, PCB and chip partitions. Since this level is connected with the overall system structure and information flow, we call it the system level.

- Algorithmic level: At this level, which is sometimes called functional level or instruction-set level, the focus is on the computations performed by an individual processor, the way it maps sequences of inputs to sequences of outputs. In the behavioral domain, the level is expressed in an algebraic notation involving variables and operators, while no explicit reference is made to any physical objects or resources, nor to timing constraints. The description would include the algorithm performed by each process, together with its associated data structures and procedures. In the structural domain, hardware

subsystems would represent the individual processes. The physical description would contain clusters; i.e., functionally related hardware subsystems.

• Register-transfer level: Below the algorithmic level is the register-transfer level (RTL), sometimes called Micro-architecture level. Here the system is viewed as a set of interconnected storage elements and functional blocks. The behavior is described as a series of data transfers and transformations between storage elements (registers or the data path) together with the ordering of the operations and transfers (the control path). The corresponding structural description defines the abstract implementation with a set of functional components; for example, ALUs, adders, MUXs, PLAs, ROMs and registers. Separate structural descriptions would be given for the data paths and their corresponding control paths. It may be possible to implement the structural description, or part of it, directly in silicon using library cells or module generators. The physical description would depend on the target implementation; for example, gate array or standard cell.

The difference between the register-transfer level and the algorithmic level is the level of detail of the specified internal structure. Only the input/output behavior is known at the algorithmic level, but there is no direct relationship between variables and internal registers or between assignment statements and register transfers at this level. The RTL model explicitly involves resource entities (registers, memories) and describes the transfers and operations between these resources and their logic conditions. Busses and structural concepts are not necessarily present.

• Logic level: Next comes the logic level. The behavior is specified by logic equations. This behavioral description would define switching circuits, expressed in terms of combinatorial logic functions, together with finite state machines. A structural description would consist of a netlist of gates, flip-flops and registers. In the physical domain, the structural description would be realized directly in silicon by predefined library cells. In addition, the chip floorplan (a geometrical arrangement of interconnected cells) would be derived.

- Circuit level: Below logic level is the circuit level, which views the system in terms of the individual transistors of which it is composed. In the behavioral domain, the behavior of a library cell would be given in terms of its d.c. and a.c. electrical characteristics. In the structural domain, transistor networks for each cell, specified to the implementation technology, would be defined. These low level networks are structures of blocks which can be easily mapped to the circuit library of a given technology.

- Layout level: Finally, one can go down directly to the layout level where the physical geometry of components is described.

# 2.2 PUPD BiCMOS Logic Gates

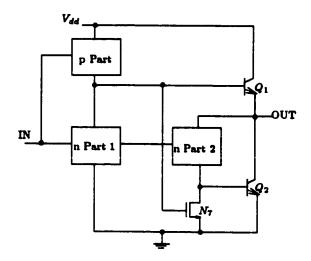

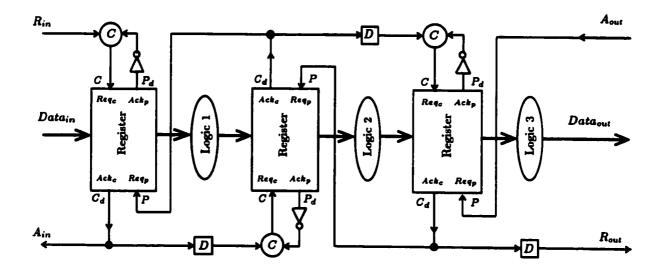

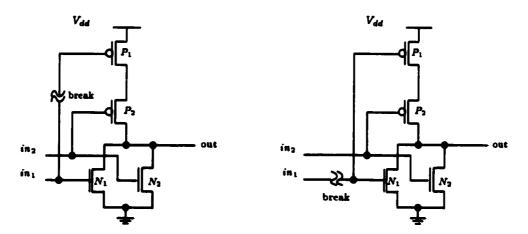

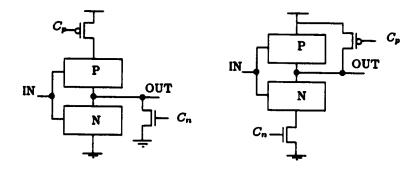

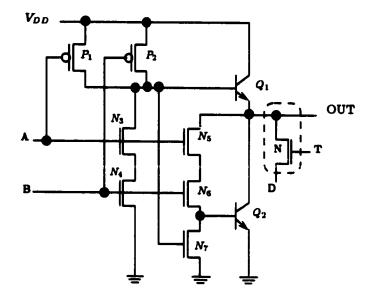

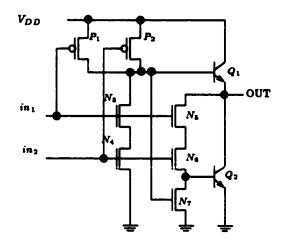

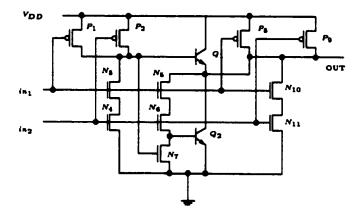

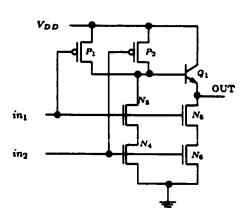

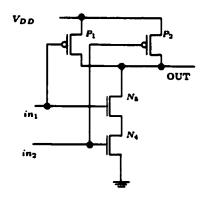

The most common type of VLSI circuits uses CMOS to perform the logic functions, and bipolar transistors to drive the output load. The general structure of a BiCMOS logic gate [11] is shown in Figure 2.1.

It consists of a CMOS logic stage and a bipolar output stage. The CMOS stage performs the logic function and provides proper bias to the output stage. The p-part (of the CMOS stage) consists of parallel/series interconnection of PMOS transistors, determined by the desired logic function. Each of the n-part 1 and n-part 2 is the dual of the p-part and consists of series/parallel interconnection of

Figure 2.1: General structure of a complex BiCMOS logic gate.

Figure 2.2: Typical implementation of a conventional BiCMOS NAND gate.

NMOS transistors. The output stage consists of a pull-up  $(Q_1)$ , and a pull-down  $(Q_2)$  transistor. For normal (fault-free) operation, the CMOS stage ensures that  $Q_1$  and  $Q_2$  do not turn on simultaneously. During a low-to-high output transition,  $N_7$  provides a discharge path for the base of  $Q_2$ , causing it to turn off more quickly. Similarly, during a high-to-low output transition, the n-part 1 provides a discharge path for the base of  $Q_1$ . A typical implementation of a conventional BiCMOS NAND gate is shown in Figure 2.2.

It is expected that in future BiCMOS VLSI systems, the dense logic will be predominantly CMOS [57]. BiCMOS buffers are to be employed for driving the heavily loaded nodes or off-chip load.

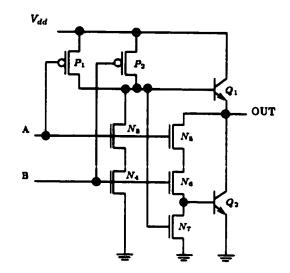

# 2.3 Categories of Digital Circuits

Digital circuits can be classified according to the function used to relate outputs and inputs or the method used to synchronize operations; see Figure 2.3. Digital

Figure 2.3: Categories of digital circuits.

combinational circuits have their outputs uniquely determined by the current circuit inputs. Circuits without feedback are always combinational.

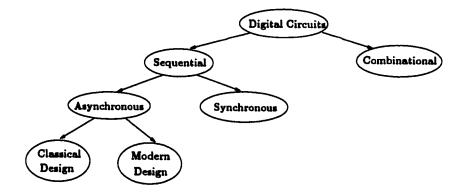

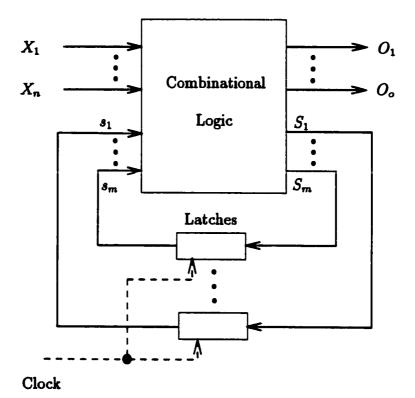

Sequential circuits, on the other hand, contain state variables, which keep the record of input transitions by their present *state*: i.e., the internal state serves to summarize the pertinent history of the circuit. Both the output of a sequential circuit and the next internal state are functions of the current internal states and inputs. Sequential circuits are further classified according to the method used to synchronize operations. Circuits which employ a global clock, a sequence of periodic pulses generated by an independent source, are called *synchronous* while circuits without a clock are called *asynchronous*. Figure 2.4 shows a typical synchronous sequential circuit where the state-holding components are *latches*. All latches are activated simultaneously by a transition on the clock: i.e., between clock pulses, no recognition is taken of the input.

Figure 2.4: Typical synchronous sequential circuit structure.

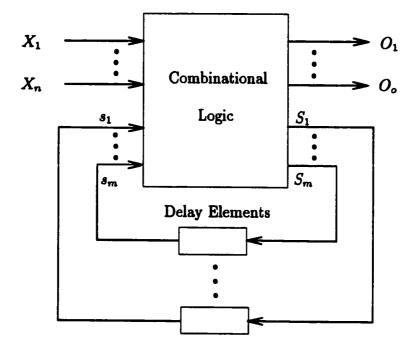

Transitions in asynchronous sequential circuits depend on the delays of components and wires. These delays, although bounded, cannot be precisely determined since they are technology dependent. In this dissertation we address two different asynchronous design methodologies: *classical design* and *modern design*. Boolean algebra constitutes the basic formalism used in designing synchronous and classical asynchronous circuits where only the logic levels of the inputs and outputs are important rather than transitions. Standard basic elements in classical asynchronous design are gates such as AND, OR, XOR, and inverter. A typical classical asynchronous sequential circuit is implemented in Figure 2.5 as a large gate circuit with feedback. Designing classical asynchronous circuits [116] uses the *finite state machine* (FSM) model. The general format used to describe a sequential function,

Figure 2.5: Typical classical asynchronous sequential circuit structure.

which relates output sequences to input sequences, in classical asynchronous circuits is called a flow table [79, 180], which consists of a two-dimensional array. The columns correspond to input states, the rows to internal states, and the entries are ordered pairs representing the next internal state and the current output. A state is stable if the next internal state is the same as the current internal state. Only one stable state is permitted in any row of a primitive flow table [116]. The next step in the synthesis procedure is to find a minimal-state flow table from a primitive flow table. We then select a finite set of binary state variables and assign to each row of the flow table one or more states of these variables. The next step in the synthesis is to obtain truth tables specifying the circuit outputs and next values of the state variables as functions of the current values of the input and state variables. In the last step the truth table is transformed to a Karnaugh-map, from which the logic circuit is designed.

#### **CHAPTER 2. DESIGN OVERVIEW**

A situation in which more than one state variable must change in the course of a transition is called a race condition. If the behavior of the circuit depends on the outcome of the race, then the race is called critical; otherwise it is noncritical. Critical races are not a problem with clocked systems since the clock pulse will go off before any flip-flop can change its state and have that change pass through the delay element to the primary output. Thus the only requirement for the validity of a row assignment is that no code be assigned to two different rows.

Some of the difficulties with the FSM model [39] are that unrestricted input changes are not handled, concurrent behaviors can not be described directly, and the flow table expands exponentially with the number of input signals. Another problem with FSM synthesis is lack of modularity [49]. Although using clock pulses eases the row-assignment and eliminates hazards, the clock frequency must be set to allow for 'worst case' delays and manufacturing tolerances.

There are two basic signaling conventions for communication, control, and data representation in a digital system: level signaling and transition signaling. In level signaling, the voltage level of a signal is meaningful. In transition signaling, however, only change of a signal is significant; an event can be a transition from low to high (i.e. rising transition) or from high to low (i.e. falling transition). Transition signaling does not distinguish between rising or a falling transition.

The environment in classical asynchronous circuits changes the input signals and holds them fixed until the circuit reaches a stable state; after that, the environment is allowed to apply the next change to the input signals. This is called the fundamental mode operation [125].

Modern asynchronous circuits are sensitive to changes in the inputs in addition to their logic levels. Therefore, new approaches, called event-based formalisms, are used which are capable of dealing with transitions (events) in the input and output signals, allowing the input-output mode of operation [29]. In contrast to fundamental mode, input-output mode allows the input to change upon receiving an appropriate response to a previous input change, even if the circuit has not yet stabilized. Some basic event-based formalisms are trace theory [49, 52, 170] and transition graphs such as Petri nets [4, 39, 134, 145]. While the former has a textual representation form, the later has a graphical representation form. Examples of primitive elements in an event-based formalism are WIRE, JOIN, MERGE, TOGGLE, and ARBITER.

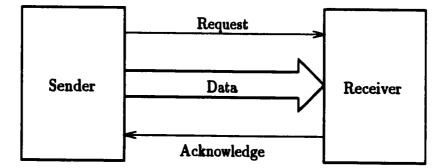

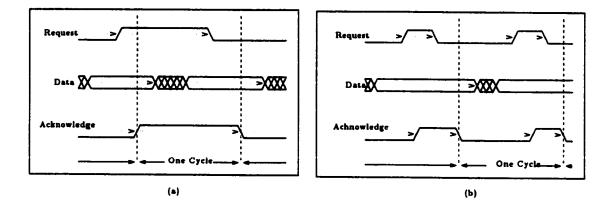

In contemporary asynchronous design, a control signal indicates the validity of the carried data [174]. For instance, each datum, or bundled-data, is accompanied by a control signal which specifies the legitimacy of that bundle of data, see Figure 2.6. When this control signal is activated by a sender, it is regarded as a request to the receiver. The number of data lines is arbitrary, and the request and acknowledge signals can use level (4-phase) signaling or transition (2-phase) signaling. Figure 2.7 shows intervals of data transfer by 2- and 4-phase signaling or handshake. The arrows in the figure indicate the sequence of events.

Figure 2.6: Communication through a bundled data interface.

For narrow communication channels, one wire is used per data value. This is

Figure 2.7: Data transfer in (a) two-phase signaling, and (b) four-phase signaling.

called single-rail encoding. The logic level on data wire indicates which binary value is communicated. Besides the data wire, which indicates what value is communicated, there is one wire which is used to indicate when the data is communicated. This wire is called the data valid wire. This wire can use either two-phase or four phase signaling. In dual-rail encoding, which is a widely used coding scheme, two wires are used for each bit in the binary representation of a number, one wire for the value zero and one wire for the value one. Sending a transition (or a logic one) along the '0' wire implements the communication of a zero, and sending a transition (or a logic one) along the '1' wire implements the communication of a one. Consider an *n*-bit binary number which is about to be transferred to the receiver. If the *j*-th bit is zero, wire 2j is raised, if it is 1, then wire 2j + 1 is raised. In a four-bit wide dual-rail encoded channel where eight wires are used, "0" is encoded as 01010101, and "1" is encoded as 01010110. Either two-phase or four-phase signaling can be used for dual-rail encoding.

Asynchronous circuits may also be classified on the basis of their dependence on component delays. Widely used categories are Delay-Insensitive (DI), Speed-Independent (SI), and Quasi-Delay-Insensitive (QDI) circuits. DI circuits operate correctly independent of gate and wire delays. SI circuits, however, behave correctly no matter how long it takes for the gates in the circuit to respond, but the wire delays are assumed to be 0. QDI circuits function properly independent of the delays of gates and wires with the assumption that the difference in delays on branches of a fork are less than the minimum gate delay in that circuit. Such forks are named *isochronic* forks.

## 2.4 Asynchronous Design

This Section is devoted to an appropriate formalism for circuit design, a set of primitive modules, and micropipelines.

Trace Theory (Program Notation):

The high-level specification for circuits is in a language that is based on Hoare's CSP (Communicating Sequential Processes) [83]. A directed trace structure is represented by a *directed command* similar to a regular expression. A command is composed of input and output alphabets, and special symbols which stand for certain operations. We first briefly define each operation, then we illustrate them by using a simple example.

- Inputs and Outputs: In the representations, input symbols are postfixed by ?, and output symbols are postfixed by ! Some variables are neither inputs nor outputs of the element. They are called *internal symbols*, and denoted without any postfix.

- Transitions: A transition from low voltage to high voltage is denoted by "↑".

A falling transition is denoted by "↓".

- Prefix operator: "**pref**" stands for *prefix-closure*. A set of string,  $S_1 S_2 \cdots S_n$ , is prefix-closed if its initial parts,  $S_1 S_2 \cdots S_i$  for i < n, is allowed.

- Sequential transitions: If transition a happens after transition b, it is shown by ";". This is called the *concatenation* operation. This operation is associative.

- Parallel transitions: The parallel execution of two transitions, a and b, is denoted by "||". This is called the *weaving* operation, and it can be considered as the conjunction of two trace structures, i.e. a function that is in accordance with both functions.

- Selection: The selection command consists of a number of subcommands (i.e., a collection of transitions) and is denoted by the symbol "|". It is sometimes called as *union* operation. Only one subcommand in a union operation is executed. The other subcommands are suspended until the running command is completed.

- Repetition: "\*[]" stands for repetition (of the enclosed). The repetition command also consists of a number of subcommands. This command shows that any repetition of the specified behavior can occur. Zero repetition corresponds to the initial state.

As an example, consider the following composed command:

This is the WIRE specification. First, a transition, rising or falling, happens on the input (a) of this component. Then, the output (b) sends a transition. The

repetition (\*) and the prefix-closure (pref) of this behavior allows the following sequences of transitions:  $\varepsilon$  (empty set), a, ab, aba, abab, etc.

#### Petri Nets:

A Petri net is composed of *places*, represented by circles, *transitions*, represented by bars, and *arcs*, represented by arrows directed from places to transitions or from transitions to places. A transition in a Petri net corresponds to an event, and *firing* the transition corresponds to the occurrence of the event. A transition is enabled if all of its input places contain a token. To fire a transition, tokens are moved from each of its input places to each of its output places. Initial states are shown by assigning tokens to places on the Petri net.

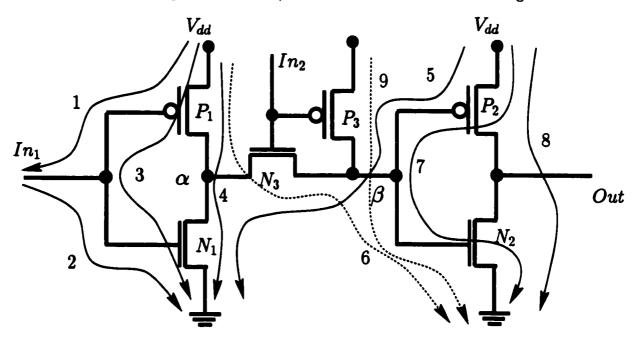

## 2.4.1 Basic Asynchronous Element: An Example

To give an example of how an asynchronous module is specified in terms of commands, trace structures [52], and Petri nets, we describe the function JOIN in this Section.

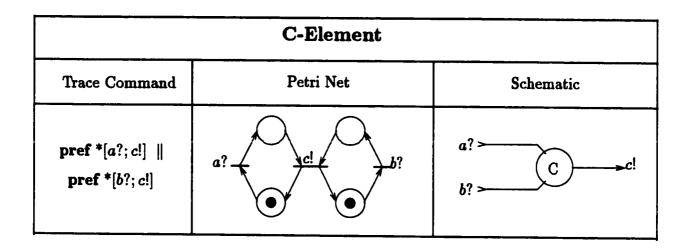

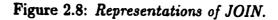

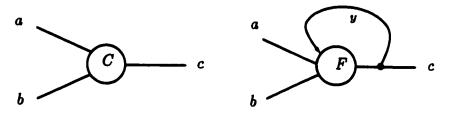

The JOIN component produces an output transition only after both of its inputs have a transition. Whenever both inputs are "0" or "1", the output will also have the same logic value. If the inputs have different states (mismatch), the output will retain its previous state. Figure 2.8 shows the command, Petri net, and schematic of JOIN.

A JOIN operated in a more liberal environment is a C-element. The specification of the C-element is given in the graph of Figure 2.9. The nodes of the graph denote the external states of the C-element. Thus, each node is labeled with a triple  $ab \cdot c$ of binary values, the first two of which are the input values and the third is the output value. The centered dot  $\cdot$  is used for convenience to separate the input and

Figure 2.9: Specification of the C-element.

output parts of the state. A directed edge indicates a transition from one state to another. An edge with two arrowheads is a shorthand for two edges, one in each direction.

The C-element behaves as follows: When the two inputs agree, the output has the common input value. Otherwise, the C-element remembers its previous state. The specification of Figure 2.9 defines the behavior not only of the C-element but also of its environment. For example, consider state  $00 \cdot 0$ ; this state is stable. Here, the environment is allowed to change input a, or input b, or both. If only one input is changed, the new state is still stable. The environment is then allowed to "withdraw" the input and return to the initial state. Once both inputs change, however, the environment must wait for the C-element to respond by changing c. Thus, the C-element is operated in the input/output mode [29]. Once c changes, the environment is again permitted to change a, or b, or both, etc.

### 2.4.2 Micropipelines

This section describes an efficient implementation of asynchronous pipelines modules developed by Sutherland. [174]. This approach can lead to very efficient and fast implementation of arithmetic units.

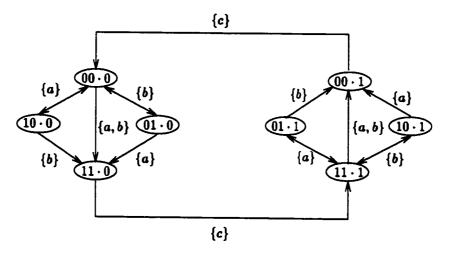

Figure 2.10 shows a micropipeline. Consider that all latches are empty, and all wires, except the inverter outputs, are 0. While the environment puts data on the interface, a transition from 0 to 1 occurs at  $R_{in}$ , passing through all C-elements in series, and emerging on  $R_{out}$  as follows. First, the input data is captured by the first latch as soon as a rising transition happens on C (capture) input. After an appropriate delay to latch the data safely, a rising transition on  $C_d$  is observed, followed by a rising transition on C of the next latch. Assuming the initial state, the empty data on the input of the second register is taken, showing a rising transition on  $C_d$  of the second register, or  $P_d$  of the previous register. This means passing the data latched from the input of the first register to its output. Then, nothing will happen to the first register while transitions can travel on  $C_i$ ,  $C_{d_i}$ ,  $P_i$ ,  $P_{d_i}$  to  $R_{out}$ . Note that the  $C_d$  signal produced by stage *i* plays the role of ack for stage i - 1

and of Req (after an appropriate delay) for stage i + 1. The input data of each register (empty or not) is first latched, then passed to its output, processed by the combinational logic, and is ready at the input of the next stage register. In fact, the data moves one block forward. Note also that the data latched is not allowed to pass from the input of the first register to its output until a transition occurs on P. As mentioned earlier,  $C_d$  and  $P_d$  are copies of the control signals C and P, delayed so that the register completes its response to the control signal transitions.

Figure 2.10: Control and computational parts in Micropipeline structure.

The next transition on  $R_{in}$  is from 1 to 0 which passes through the first two C-elements, but not through the third one. This allows one more data to advance ahead in the micropipeline. Consider an instant when the micropipeline is filled with data. The output side of the micropipeline will not be ready to accept new processed data unless it raises  $A_{out}$ . Until then, the micropipeline will not accept any more data. When a transition on  $A_{out}$  appears, a space in the micropipeline is freed, and a transition on  $A_{in}$  is generated.

The data stored in a micropipeline is processed through the logic blocks between register stages, which are usually assumed to be combinational. Since these blocks slow down the data moving through them, the accompanying control transition must also be delayed, here shown as D. This delay on the control path must be adjusted to allow the combinational logic outputs to settle and the latch setup time to be satisfied. Therefore, it must be at least as large as the worst-case delay of the logic block. However, the overall processing in the pipeline occurs at rates closer to the average processing time than the worst-case time of the entire circuit. This can be best understood by looking at the controlling transitions on C or P as they resemble a non-periodical asynchronous clock. The period of such a clock need not be limited by the maximum worst-case delay of the logic blocks. If we ignore the logic blocks and associated delay elements, we have a simple data FIFO (First-In, First-Out) queue.

Micropipelines are based on two ideas. First, transition signaling or two-phase handshaking is used. Such an approach permits much faster operation than the classical four-phase handshaking at the expense of slightly more complex circuitry. Secondly, bundled data communication protocol is used where control signals define the validity of the data signals. Only the control part must be designed with a delayinsensitive signaling protocol coupled with delay matching for data communication.

There are advantages and disadvantages in designing micropipelines. Due to the registers, hazards of logic blocks in the data path do not interfere with the circuit operation and its effects do not propagate any further. This allows the use of any synchronous structures in micropipelines by replacing the latches and the clock with micropipeline latches and control structures. Micropipelines also benefit from some asynchronous design advantages. For example, they are elastic, in that data can be sent to them and received from them at arbitrary times. The disadvantages are as follows: they do not yet deliver average-case performance for each logic unit, and the delay of the control part must be guaranteed to be larger than the delay in the data part, demanding delay fault testing.

# 2.5 Chronology

In this section we give a brief survey of classical, speed-independent (SI), delayinsensitive (DI), Self-timed (ST), quasi-delay-insensitive (QDI), and micropipeline asynchronous design methodologies.

**Classical Asynchronous Design:**

Huffman [85] was the first to develop the traditional way of designing asynchronous circuits using flow tables. Classical asynchronous circuit design as described by Unger [180] generally places restrictions on the allowed input changes, such as the requirement for fundamental-mode operation that only one input can change at a time, and succeeding input changes must be delayed until the circuit is stable. His method did not allow simultaneous input changes. Synchronizer and arbiter circuits cannot, in general, satisfy these restrictions. Later in 1979 [181], Unger studied possible way of easing this restriction. However, concurrent behaviors cannot be described directly in classical asynchronous circuit design.

It appears at first that the realized circuit should behave as specified in the flow table. However, this is true only under ideal conditions: There are no delays in the logic elements or in the wiring, but only in the feedback lines. If this unrealistic assumption is removed, then several kinds of malfunctions such as hazards become possible. Such transient errors can lead to steady-state errors. There are circuits which neither altering the logic circuit nor altering the state assignment eliminates these malfunctions. The only remedy is to insert adequate delay elements at the output nodes of some gates.

The state assignment is by no means a simple one. Not only must each row be assigned a unique code, but the codes must be so interrelated that no transition involves a non-removable critical race. The difficulties become more evident when we try to minimize the transition time, the number of state variables, and the complexity of the resulting logic circuit. Besides, the flow table expands exponentially with the number of input signals. Another problem with FSM synthesis is lack of modularity.

In 1993, Dill used burst-mode specifications, a class of asynchronous finite-state machine specifications which allows multiple-input changes [194]. Using asynchronous specification style, Nowick *et al.* [139,140] presented an automated design methodology for locally-clocked, globally asynchronous state machine controllers. They then described a heuristic technique for state minimization and optimization to improve implementations and demonstrated the feasibility of their method by designing a cache controller [141,142]. Their technique tends to provide hazard-free logic with multiple-input changes [143].

### Speed-Independent Circuits:

The concept of SI switching circuits was first studied by D. Muller more than four decades ago [133, 136]. SI design makes it possible to guarantee correct operation of a circuit at speeds limited only by actual delays present in the physical devices of the circuit assuming wire delays are zero. A Muller-circuit can generate a ready signal as soon as it has "digested" the previous input and is ready for a new input. Muller also introduced the basic component of parallelism, the C-element. Utilizing C-elements, Muller designed various blocks to implement functions such as delay, AND, XOR, switch, and memory components.

Dill [50,51] was the first to develop an automatic verifier of speed-independent circuits based on a formalism called *trace theory*.

In 1987, Chu presented a synthesis technique for speed-independent circuits based on a high-level graph model of finite automata called STGs (Signal Transition Graphs) [39], a form of *interpreted Petri nets*. STGs can represent ordering and concurrency.

**Delay-Insensitive Circuits:**

Clark [40] and Molnar et al. [41, 135, 159] considered module design and system design using modules as two separate issues. They assumed that the timing behavior of the physical realization of each module is left up to the module designer. They proposed a set of relatively simple, general-purpose delay-insensitive components, called *Macromodules*, from the system level point of view, rather than the circuit level. Working systems can be readily assembled for evaluation and studied from these components without creating any logical problems such as waveform deterioration or power supply interactions. These modules have been successfully used to design input-output devices, registers, and memory units.

Although the concept of DI circuits has existed since the 1960's, it was not formalized until the mid 1980's by Udding [179]. He proved that a set of five conditions are necessary and sufficient for a delay-insensitive specification. Ebergen developed theorems for designing and decomposing a component into delay-insensitive elements and showed that by interconnecting a small set of primitive components delay-insensitive operation for a large class of behaviors can be achieved [52]. In his approach, the behaviors of components are specified by programs written in a notation based on trace theory.

### Self-Timed Circuits:

The term Self-timed circuit was first used by Seitz [165]. By pointing out the problems of system timing, Seitz mentioned that all system events should occur in proper sequence in a self-timed circuit, but nothing ever has to occur at a particular time. A self-timed system is a legal interconnection of elements which may have an internal clock and some delays to perform computations on their input signals. Modules in a self-timed system, however, communicate asynchronously; i.e., signal events at their inputs are regarded as request signals and signal events at their output are completion signals, and each element is allowed to impose an arbitrary delay between the occurrence of input and output signal events. He then noted that a self-timed circuit can use either equipotential (what we call speed-independent today) or delay-insensitive self-timed signaling conventions. The design of selftimed systems was further studied in [105, 176, 193]. Self-checking circuits were also studied by Varshavsky [182] and more recently by Beerel and Meng [15, 16]. The former have presented a formal proof that DI and SI are self-timed circuits. Meng incorporated high-level specifications using STGs to automate the design of asynchronous self-timed circuits [127, 128].

### Quasi-Delay-Insensitive Circuits:

Martin [32, 118, 122, 123] proposed a novel design approach for compiling QDI circuits from CSP-like specifications. In this approach, modules are specified as sequential processes which can be refined into more detailed descriptions. In the final step, these descriptions are replaced with hardware templates which implement the actions of the circuit. Many circuits, including a complete asynchronous microprocessor, were actually implemented using Martin's approach. He also pointed out some of the limitations to the delay-insensitivity of asynchronous circuits [119].

Compiler-based styles have also been successfully used for certain applications such as pipeline controllers by Philips researchers [28].

### Micropipelines:

Special types of modern asynchronous circuits called *micropipelines* were discussed by Sutherland [174]. Micropipelines are simple, elastic, event-driven pipeline structures which consist of a control circuit and a data path structure that may or may not have internal data processing. The communication protocol used in micropipelines is known as the two-phase bundled data convention. Sutherland gave examples of simple micropipelines like a FIFO queue circuit and more complicated ones such as a multiplier, binary to one-out-of-N decoder, and memory controller chips.

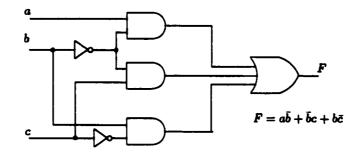

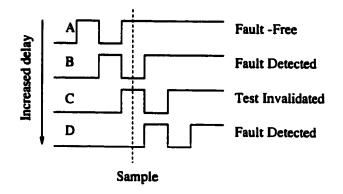

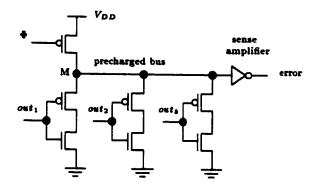

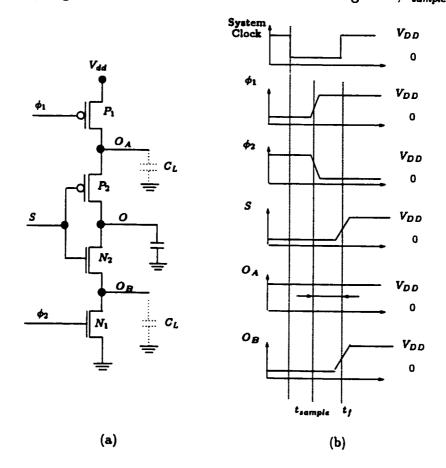

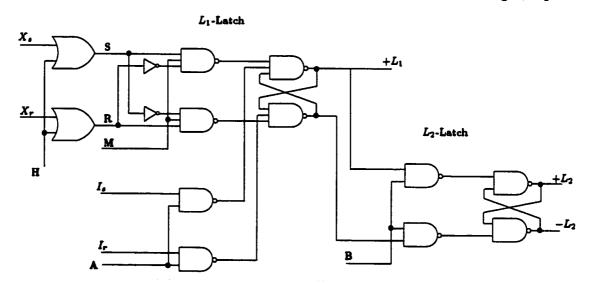

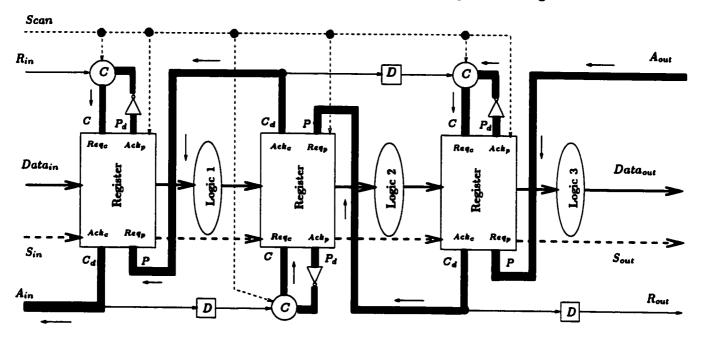

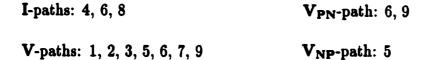

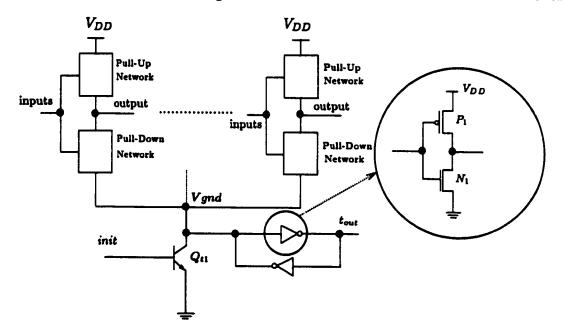

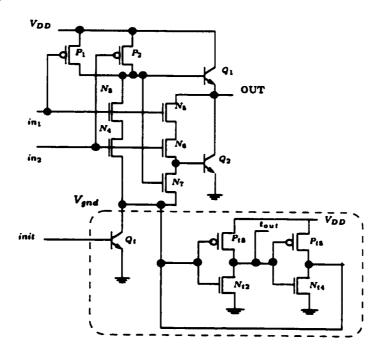

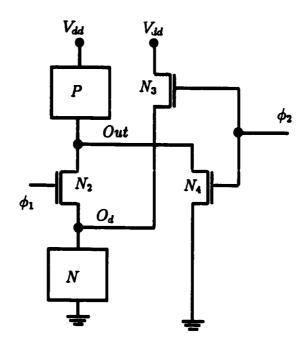

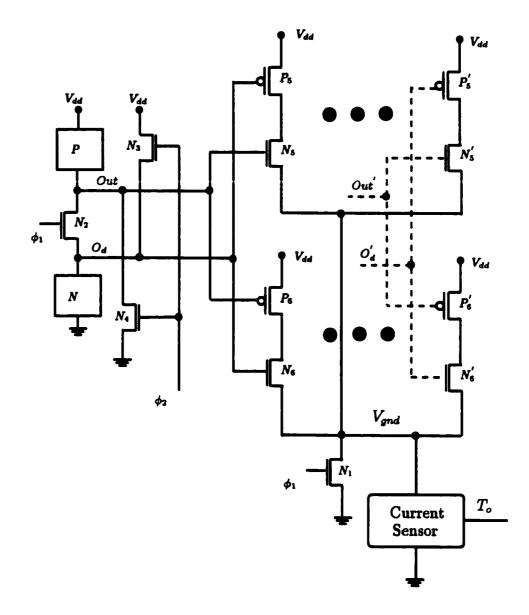

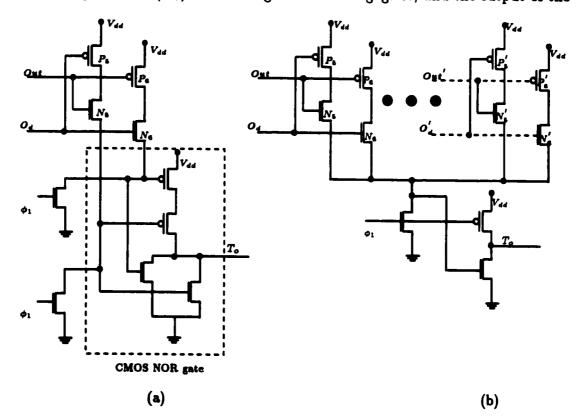

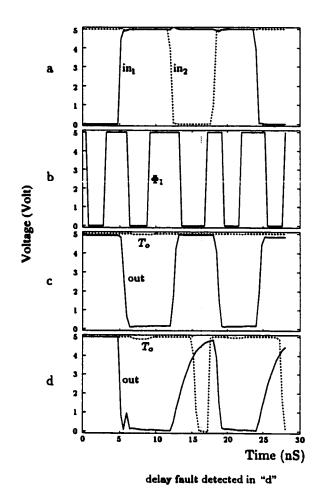

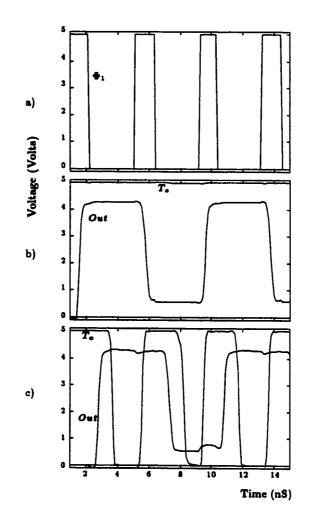

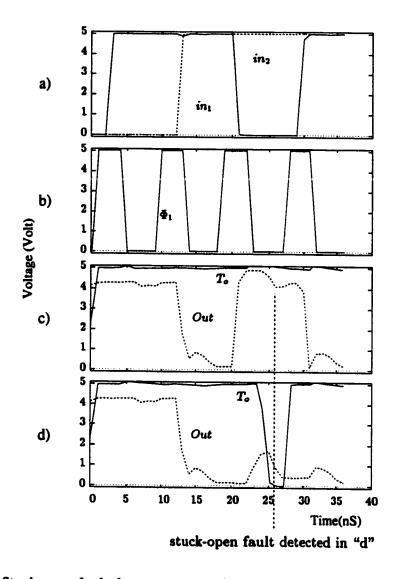

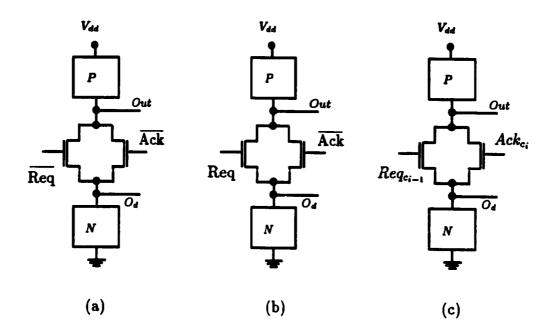

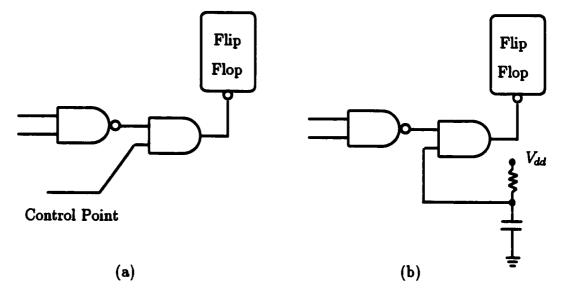

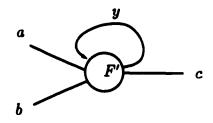

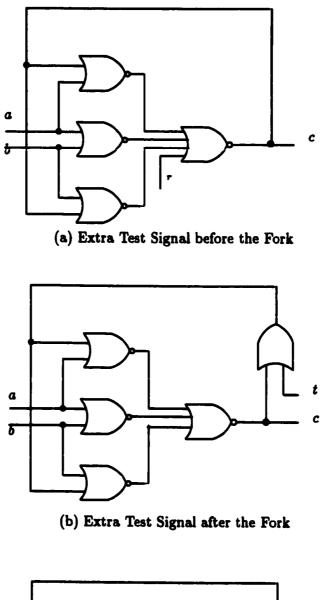

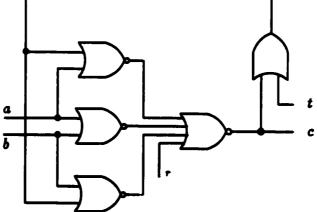

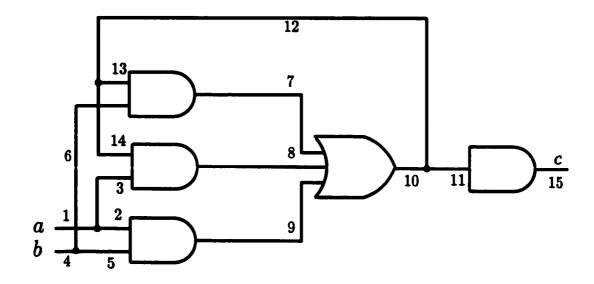

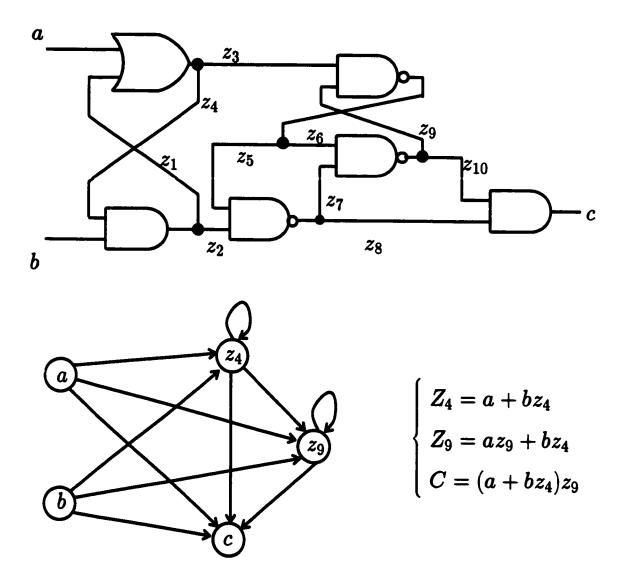

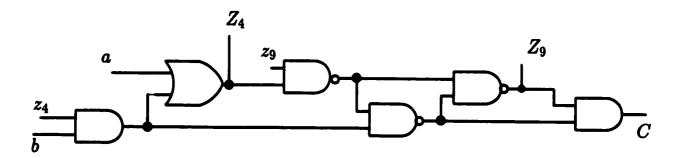

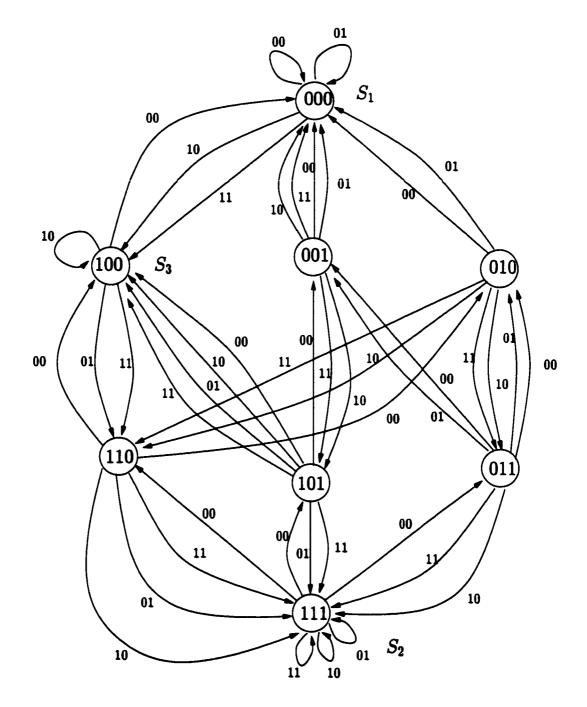

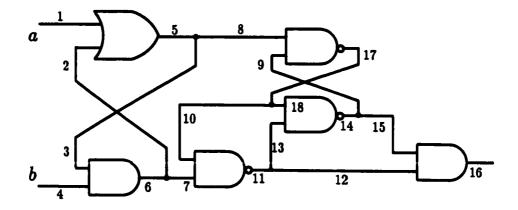

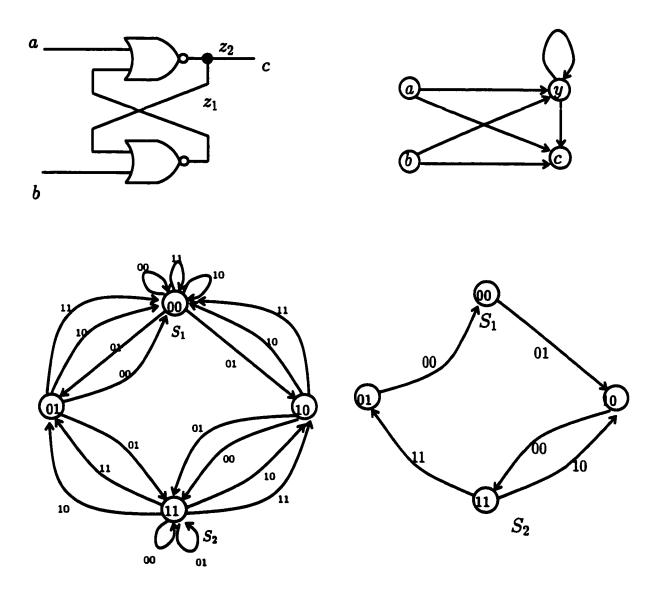

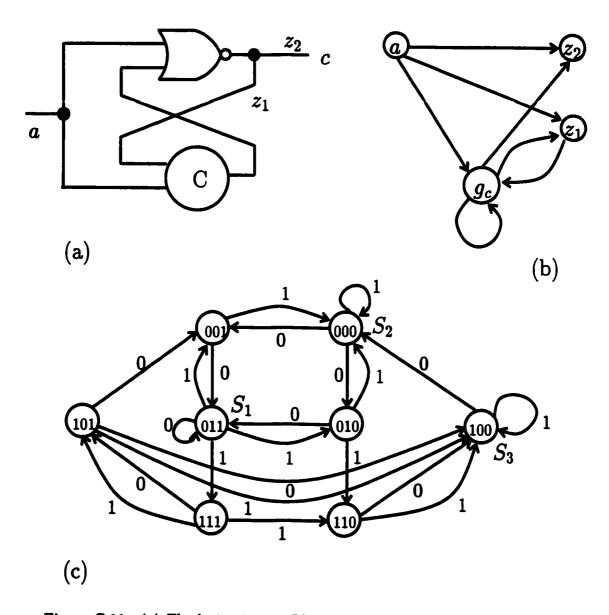

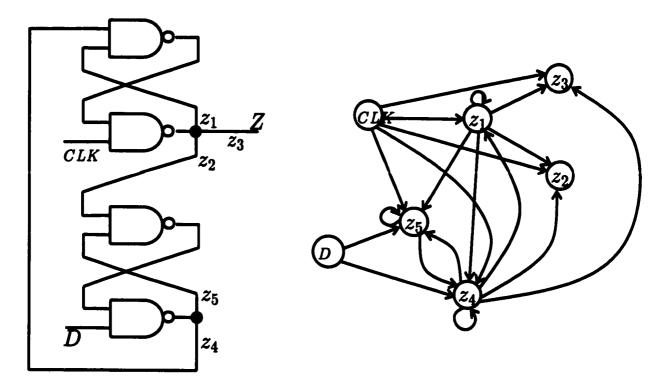

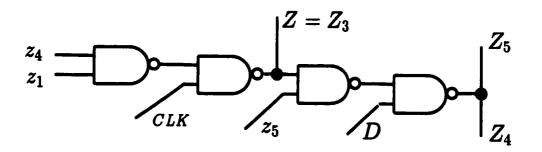

Furber et al. adopted the micropipeline approach in October 1990, and completed an asynchronous ARM processor within the AMULET project [69, 70]. Although their design did not outperform its clocked counterpart, its performance, area, and power dissipation were within a factor of two compared to the synchronous ARM. This is encouraging, though, if one considers the modularity a designer can achieve by asynchronous logic architecture. Work is still being continued to enhance the design. It is not yet clear whether such techniques will be cost-effective.